(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6582616号

(P6582616)

(45) 発行日 令和1年10月2日(2019.10.2)

(24) 登録日 令和1年9月13日(2019.9.13)

(51) Int.CI.

H01L 21/301 (2006.01)

F 1

H01L 21/78

S

請求項の数 2 (全 11 頁)

(21) 出願番号 特願2015-129211 (P2015-129211)

(22) 出願日 平成27年6月26日 (2015.6.26)

(65) 公開番号 特開2017-17072 (P2017-17072A)

(43) 公開日 平成29年1月19日 (2017.1.19)

審査請求日 平成30年6月26日 (2018.6.26)

(73) 特許権者 390002761

キヤノンマーケティングジャパン株式会社

東京都港区港南2丁目16番6号

(74) 代理人 100189751

弁理士 木村 友輔

(72) 発明者 新井 龍彦

東京都港区港南2丁目16番6号 キヤノンマーケティングジャパン株式会社内

(72) 発明者 衣川 貴志

東京都港区港南2丁目16番6号 キヤノンマーケティングジャパン株式会社内

審査官 井上 和俊

最終頁に続く

(54) 【発明の名称】半導体チップの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のチップ領域と、当該複数のチップ領域を分離するためにシリコンが露出している分離領域とを半導体基板の第1の表面上に形成する領域形成工程と、

前記第1の表面の裏面の第2の表面上に、前記分離領域と同じパターンで、前記分離領域の裏面に相当する第2の領域にレジスト膜が残るようにパターンニングするパターンニング工程と、

前記パターンニングされたレジスト膜上を被覆するように電極膜を前記第2の表面上に成膜する成膜工程と、

前記電極膜を成膜した後に、前記第1の表面の、前記露出している前記分離領域のシリコンをプラズマエッチングするエッチング工程と、

10

前記エッチング工程の後に、前記第1の表面側から、前記パターンニングした前記第2の領域に残るレジスト膜を除去する除去工程と、

を含むことを特徴とする半導体チップの分離方法。

## 【請求項 2】

前記電極膜を成膜した後に、前記第2の表面側をダイシングテープに貼り付ける貼付工程と、

を更に含み、

前記ダイシングテープに貼り付けた後に、前記エッチング工程で前記第1の表面から、前記露出している前記分離領域のシリコンをプラズマエッチングし、

20

前記エッチング工程の後に、前記除去工程で前記第1の表面側から、前記パターンニングした前記第2の領域に残るレジスト膜を除去することで、前記ダイシングテープから前記半導体基板を剥離した場合に、前記複数のチップ領域が分離することを特徴とする請求項1に記載の半導体チップの分離方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体チップの製造方法の技術に関する。

【背景技術】

【0002】

近年、半導体デバイスウエハの薄膜化が進み、ウエハ上に製造された多数のチップをダメージなくチップサイズにセパレートするダイシング技術の新しい技術としてプラズマエッチング装置を用いたダイシング技術が検討されている。10

【0003】

このプラズマエッチング装置を用いたダイシング技術を用いた場合、現存のダイシングソーやレーザーダイシングよりも、半導体デバイスウエハへのダメージが少なく、さらに、微細な加工も出来るというメリットがある。

【0004】

通常、プラズマエッチング装置を用いたダイシング技術にはボッシュプロセスというシリコンの深堀エッチング技術を適用するが、このボッシュプロセスでのエッチングプロセスでは、シリコンはエッチングできるが、金属膜はエッチングする事ができないというエッチング特性がある。20

【0005】

上述した半導体デバイスウエハの中には、ウエハの裏面側にも金属膜である裏面電極が形成されている半導体デバイスウエハがあり、裏面側の裏面電極は平坦であるため、表面側からダイシングライン部をボッシュプロセスにより深さ方向にエッチングしても、ダイシングライン部の底にある裏面電極の部分はうまくダイシングすることができない。

【0006】

特許文献1には、半導体ウエハのプラズマダイシング工法の中で、ダイシングライン部において、ダイシングソーのダイシングブレードを用いて、金属層を含む配線形成層を除去して、半導体層（シリコン）を露出する技術が開示されている。30

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2012-124212号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、特許文献1の技術では、プラズマエッチング装置を用いたダイシングを行う前に、半導体層を露出するためにだけに、ダイシングソーを導入する必要があり、コスト増になってしまう。40

【0009】

本発明は、複数のチップ間の裏面電極を分離する際にダイシングソーを用いずに、チップを製造する既存プロセスとプラズマエッチング装置を用いたダイシング技術とを組み合わせてチップ間の裏面電極を、コスト安に分離できる仕組みを提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明は、複数のチップ領域と、当該複数のチップ領域を分離するためにシリコンが露出している分離領域とを半導体基板の第1の表面上に形成する領域形成工程と、前記第150

の表面の裏面の第2の表面上に、前記分離領域と同じパターンで、前記分離領域の裏面に相当する第2の領域にレジスト膜が残るよう<sup>10</sup>にパターンニングするパターンニング工程と、前記パターンニングされたレジスト膜上を被覆するよう<sup>10</sup>に電極膜を前記第2の表面上に成膜する成膜工程と、前記電極膜を成膜した後に、前記第1の表面の、前記露出している前記分離領域のシリコンをプラズマエッティングするエッティング工程と、前記エッティング工程の後に、前記第1の表面側から、前記パターンニングした前記第2の領域に残るレジスト膜を除去する除去工程と、を含むことを特徴とする半導体チップの分離方法。

#### 【発明の効果】

#### 【0012】

本発明により、複数のチップ間の裏面電極を分離する際にダイシングソーを用いずに、チップを製造する既存プロセスとプラズマエッティング装置を用いたダイシング技術とを組み合わせてチップ間の裏面電極を、コスト安に分離できる仕組みを提供することが可能となる。

#### 【図面の簡単な説明】

#### 【0013】

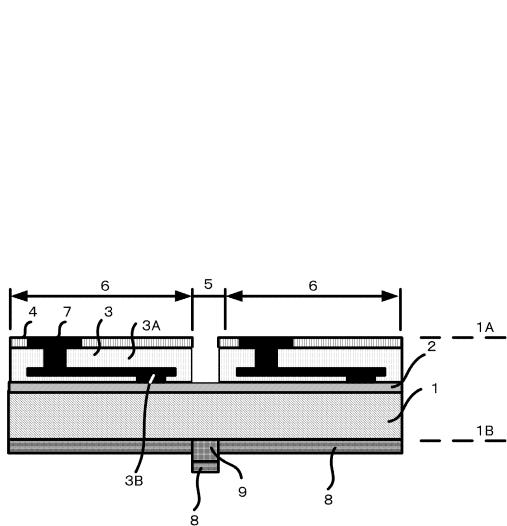

【図1】本発明の実施形態での半導体チップの製造方法での途中の状態を半導体ウエハ1の構造を用いて説明したもの

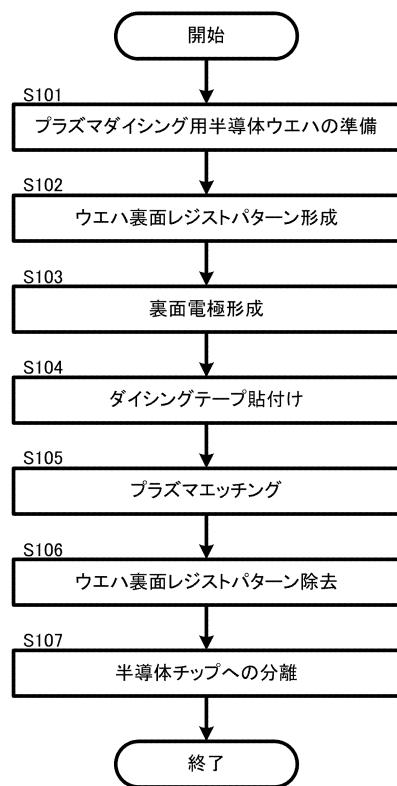

#### 【図2】本発明の第1の実施形態の各工程をステップ毎に記載したフロー チャート

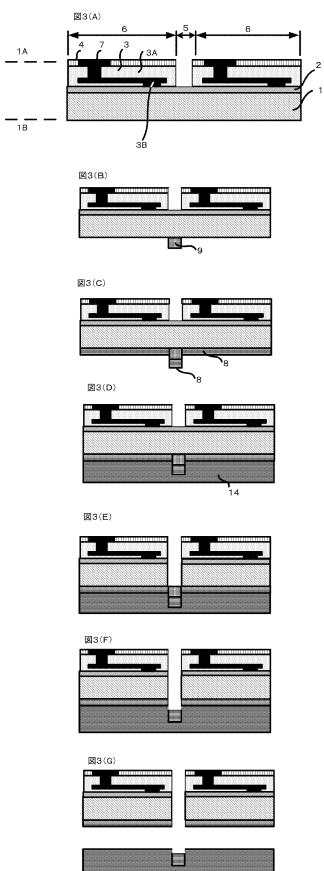

【図3】本発明の第1の実施形態の各工程をステップ毎に半導体ウエハ1の断面図で記載したもの

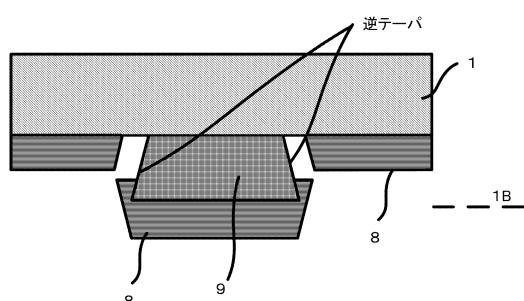

#### 【図4】本発明のパターンニングされたレジスト膜の形状を示したもの

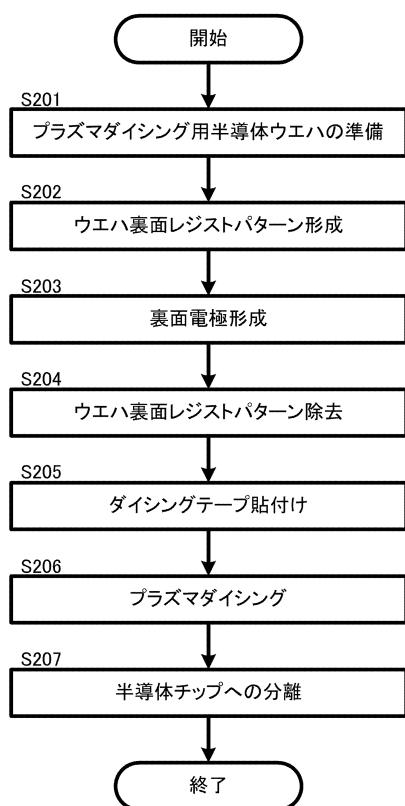

#### 【図5】本発明の第2の実施形態の各工程をステップ毎に記載したフロー チャート

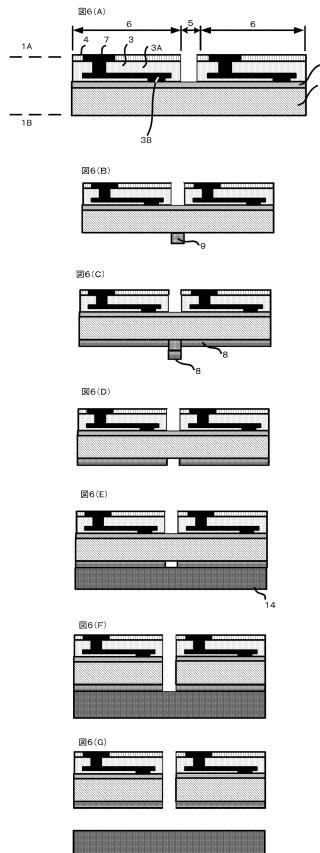

【図6】本発明の第2の実施形態の各工程をステップ毎に半導体ウエハ1の断面図で記載したもの

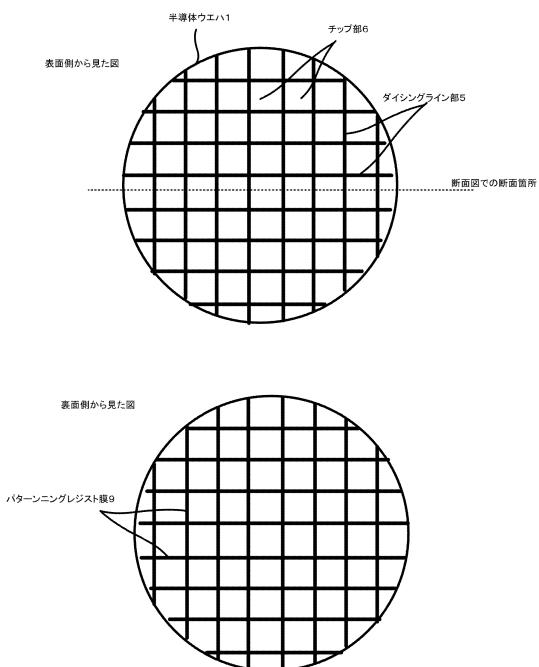

【図7】本発明におけるパターンニング工程後の半導体ウエハ1の表面側と裏面側の状態を示した図

#### 【発明を実施するための形態】

#### 【0014】

以下に、本発明にかかる実施の形態を図面に基づいて詳細に説明する。

図1を説明する。

#### 【0015】

本発明の実施形態での半導体チップの製造方法での途中の状態を半導体ウエハ1の構造を用いて説明したものである。図1の半導体ウエハ1の構造は、図3(C)及び図6(C)の状態と同じものである。なお、本発明で説明する半導体ウエハ1の構造は、半導体ウエハ1を直線に破断した場合の断面図で示している。

#### 【0016】

なお、便宜的に、図の上面側である半導体ウエハ1上にチップ領域がある面を1A(表面側)とし、裏面電極がある面を1B(裏面側)として以降の説明を行う。

以下、層(膜)ごとに説明する。

半導体ウエハ1(例えばSi基板)の表面には、半導体層2(例えばSi膜)があり、この半導体層2の上面側には、配線形成層3が形成されている。

配線形成層3の中には、絶縁層3A(例えばSiO<sub>2</sub>膜)及びこの絶縁層3A内で配線部分を構成する金属層3B(例えばCu膜)とで形成されている。

配線形成層3の部分的な表面にはパッシベーション膜4(例えばSiN膜)が露出している。

#### 【0017】

さらに、配線形成層3の部分的な表面には、配線形成層3の中の金属層3Bに電気的に接続され、外部配線接続用電極として機能するボンディングパッド部7(例えばAl膜)も形成されている。

#### 【0018】

10

20

30

40

50

半導体ウエハ1の表面側には、平面視した場合に格子状であるダイシングライン部5(分割領域)が設けされている。このダイシングライン部5をダイシングすることで、複数のチップ部6(チップ形成領域)6同士をそれぞれ分断することができる。

#### 【0019】

パッシベーション膜4は、半導体ウエハ1の表面側において、チップ部6のボンディングパット部7とダイシングライン部5とを除く、全て領域を覆うように形成されている。

尚、半導体ウエハ1の表面側のパッシベーション膜4の領域は、ボッシュプロセスでのエッティングプロセスによってもエッティングされることはない。

#### 【0020】

半導体ウエハ1の裏面側の裏面電極層8は半導体チップを実装する際の電極として用いられ、単層(例えばAu膜)や積層(例えばAl膜/Ti膜/Ni膜/Au膜)の金属膜で形成されている。

#### 【0021】

このような半導体デバイスウエハをダイシングライン部5において、それぞれのチップ部6を分割することにより、分割された後のチップ部6が個々の半導体デバイスとなる。

図2及び図3を説明する。

図2は、半導体チップの製造方法で必要となる第1の実施形態の各工程をステップ毎に記載したフローチャートである。

図3は、半導体チップの製造方法で必要となる第1の実施形態の各工程をステップ毎に半導体ウエハ1の断面図で記載したものある。

#### (1) 領域形成工程

S101において、図3(A)に示したようなダイシングする前の半導体ウエハ1を準備する。

#### 【0022】

このように領域形成工程では、露出する面が金属膜7やパッシベーション膜4で被覆されている複数のチップ領域6と、この露出する面にシリコン基板1またはシリコン膜2が露出している複数のチップ領域をそれぞれ分断する分断領域5(ダイシングライン部)とを、シリコン基板の第1の表面上にそれぞれ形成する。

#### (2) パターンニング工程

#### 【0023】

S102において半導体ウエハ1の裏面側にレジストコーティング装置10を用いてレジストを塗布する。その後、表面側のダイシングライン部5に対応する裏面側にだけ、レジスト膜が残るように、露光装置11を用いて露光を行い、デベロッパー装置12にてレジスト膜の現像処理を行うことで、図3(B)に示したように裏面側にパターニングされたレジスト膜9を形成する。この時の状態を図7の下図に示す。

#### 【0024】

なお、裏面側にレジスト膜9をパターニングするためには、表面側にダイシングライン部5を形成する場合に用いた、露光装置11用のフォトマスクと同じマスクを使用すればよい。

#### 【0025】

このようにパターニング工程では、複数のチップ領域6が形成されている表面側とは反対面である裏面側上の、分断領域5(ダイシングライン部)のちょうど反対面側に相当する領域に、レジスト膜9が存在するようにパターニングする。

#### (3) 成膜工程

#### 【0026】

S103において、裏面パターニングレジスト9を形成した半導体ウエハ1の裏面上に例えばスパッタリング装置12もしくは真空蒸着装置13にて裏面電極を成膜する。

#### 【0027】

成膜した裏面電極層8は裏面パターニングレジスト9上にも成膜されるが、図3(C)に示したように裏面パターニングレジスト9の側面側の成膜は上面側の成膜と比較して薄

10

20

30

40

50

くなる。

#### 【0028】

ここで成膜工程において、裏面パターニングレジスト9上に裏面電極層8が成膜された状態の裏面パターニングレジスト9近傍の拡大図を図4に示す。具体的には裏面パターニングレジスト9の形状を逆テープ形状にする事で、裏面パターニングレジスト9の側面側には裏面電極層8があまり成膜されない構造にすることができる。

#### 【0029】

このように成膜工程では、パターンニングされたレジスト膜上を被覆するように電極膜8を成膜して、パターンニングされたレジスト膜9により成膜した電極膜8に段差をつけている。

10

#### (4) 貼付工程

#### 【0030】

S104において、図3(D)に示すように、半導体ウエハ1の裏面側をダイシングテーブ14に貼り付ける。このように貼付工程では、成膜工程により段差をつけた裏面側をテーブに貼り付ける。

#### (5) エッチング工程

#### 【0031】

S105において、図3(D)のような状態になった半導体ウエハ1の表面側にプラズマを用いたエッチング処理を行う。具体的にはドライエッチング装置にて、装置内の圧力条件およびガス条件などを切り換えてプラズマを発生させることにより、半導体層2(シリコン膜)に対するエッチング処理を実施する。

20

#### 【0032】

このエッチング工程では、例えばSF6主体のガスを用いてエッチング処理が行われるので、パッシベーション膜4、配線形成層3およびボンディングパッド7がマスクとして機能し、半導体層2(シリコン膜)のエッチング処理が行われる。半導体層2(シリコン膜)のエッチング処理に引き続き、その下のシリコン基板1も深さ方向にエッチング処理が行われる。

#### 【0033】

プラズマエッチングによって、図3(E)に示すようにダイシングライン部5の下にあるシリコン基板1の裏面側まで貫通すると、プラズマの発生を停止させてプラズマエッチングを終了させる。

30

#### 【0034】

第1の実施の形態によれば、例えばSF6主体のガスを用いてエッチング処理を実施するエッチング工程で、エッチングが困難である裏面電極層8をダイシングテーブ14に残した状態にする事ができる。

このようにエッチング工程では、表面側から、プラズマエッチング可能な深さまで、シリコン基板1をエッチングする。

#### (6) 除去工程

#### 【0035】

S106において、図3(E)のような状態になった半導体ウエハ1の表面側にプラズマアッシング装置を用いたアッシング処理を行う。具体的にはドライエッチング装置もしくはアッシング装置にて、装置内の圧力条件およびガス条件などを切り換えてプラズマを発生させることにより、有機膜で裏面パターニングレジストを灰化させることでアッシング処理を実施する。

40

#### 【0036】

この除去工程では、例えばO2主体のガスを用いてレジストアッシング処理が行われ、図3(F)に示すように裏面パターニングレジスト膜9が除去されると、プラズマの発生を停止させてプラズマアッシングを終了させる。

#### 【0037】

第1の実施の形態によれば、例えばO2主体のガスを用いてアッシング処理を実施する

50

除去工程で、プラズマエッティングでは分離である複数のチップ領域の間に存在していた裏面電極層 8 を、ダイシングソーを用いずに分断する事ができる。

さらに、除去工程ではアッシング処理中にボンディングパット 7 上を付着する、例えば C 系の付着物も同時にアッシングする事もできる。

#### 【 0 0 3 8 】

このように除去工程では、エッティング工程の後に、表面側から、分断領域 5 ( ダイシングライン部 ) のちょうど反対面側に相当する領域に存在していたレジスト膜を除去する。

#### ( 7 ) 剥離工程

#### 【 0 0 3 9 】

S 1 0 7 において、レジスト膜 9 を除去した後のシリコン基板 1 を、ダイスピッカ用いてテープから剥離する。例えば、ダイシングテープ上に張り付いたチップの剥離を容易にする為に、UV 光を照射しテープの粘着性を劣化させた物を、ダイスピッカにてトレーに整列、収納する。ダイスピッカは例えばダイシングテープ裏面から押し上げピンを用いて良品チップを持ち上げ、チップ表面から真空吸着法にてチップをピックアップし、トレーに整列、収納する。

図 4 及び図 5 を説明する。

図 4 は、半導体チップの製造方法で必要となる第 2 の実施形態の各工程をステップ毎に記載したフローチャートである。

図 5 は、半導体チップの製造方法で必要となる第 2 の実施形態の各工程をステップ毎に半導体ウエハ 1 の断面図で記載したものである。

#### 【 0 0 4 0 】

前述した第 1 の実施形態では、半導体ウエハ 1 に対して、表面側よりプラズマを用いたエッティング処理を行ってから裏面パターニングレジストに対するアッシング処理を実施する場合について説明したが、変形例として、裏面レジストパターニングに対するアッシング処理を行ってから半導体ウエハ 1 に対して、表面側よりプラズマを用いたエッティング処理を行ってもよく、図 4 及び図 5 及び図 6 を用いて説明する。

#### ( 1 ) 領域形成工程

S 2 0 1 において、図 5 ( A ) に示したようなダイシングする前の半導体ウエハ 1 を準備する。

#### 【 0 0 4 1 】

このように領域形成工程では、露出する面が金属膜 7 やパッシベーション膜 4 で被覆されている複数のチップ領域 6 と、この露出する面にシリコン基板 1 またはシリコン膜 2 が露出している複数のチップ領域をそれぞれ分断する分断領域 5 ( ダイシングライン部 ) とを、シリコン基板の第 1 の表面上にそれぞれ形成する。

#### ( 2 ) パターンニング工程

#### 【 0 0 4 2 】

S 2 0 2 において半導体ウエハ 1 の裏面側にレジストコーティング装置 1 0 を用いてレジストを塗布する。その後、表面側のダイシングライン部 5 に対応する裏面側にだけ、レジスト膜が残るよう、露光装置 1 1 を用いて露光を行い、デベロッパー装置 1 2 にてレジスト膜の現像処理を行うことで、図 5 ( B ) に示したように裏面側にパターニングされたレジスト膜 9 を形成する。この時の状態を図 7 の下図に示す。

#### 【 0 0 4 3 】

なお、裏面側にレジスト膜 9 をパターンニングするためには、表面側にダイシングライン部 5 を形成する場合に用いた、露光装置 1 1 用のフォトマスクと同じマスクを使用すればよい。

#### 【 0 0 4 4 】

このようにパターンニング工程では、複数のチップ領域 6 が形成されている表面側とは反対面である裏面側上の、分断領域 5 ( ダイシングライン部 ) のちょうど反対面側に相当する領域に、レジスト膜 9 が存在するようにパターンニングする。

#### ( 3 ) 成膜工程

10

20

30

40

50

**【0045】**

S203において、裏面パターニングレジスト9を形成した半導体ウエハ1の裏面上に例えばスパッタリング装置12もしくは真空蒸着装置13にて裏面電極を成膜する。

ここで成膜工程において、裏面パターニングレジスト9上に裏面電極層8が成膜された状態の裏面パターニングレジスト9近傍の拡大図を図6に示す。

**【0046】**

具体的には裏面パターニングレジスト9の形状を逆テープ形状にする事で、裏面パターニングレジスト9の側面側には裏面電極層8が形成されない構造にすることができる。

(4) 除去工程

**【0047】**

S204において、図5(C)のような状態になった半導体ウエハ1の裏面側を例えばウエットアッシング装置を用いたアッシング処理を行う。このアッシング工程では、例えば硫酸加水やアンモニア加水を用いたアッシング処理を実施すると、逆テープ形状に形成された裏面パターニングレジスト9の側面から液体が侵入し裏面パターニングレジスト9が溶解すると同時に裏面パターニングレジスト上に成膜された金属膜が除去される。この技術はピールオフとよばれる。

**【0048】**

このように裏面パターンレジスト除去工程では、エッチング工程の前に、裏面側から、分断領域5(ダイシングライン部)のちょうど反対面側に相当する領域に存在していたレジスト膜とその上に生成した裏面電極層同時に除去し、図5(D)のサンプルが完成される。

(5) 貼付工程

**【0049】**

S205において、図5(E)に示すように、半導体ウエハ1の裏面側をダイシングテーブ14に貼り付ける。このように貼付工程では、除去工程により、レジスト膜を除去した裏面側をテーブに貼り付ける。

(6) エッチング工程

**【0050】**

S206において、図5(E)のような状態になった半導体ウエハ1の表面側にプラズマを用いたエッチング処理を行う。具体的にはドライエッチング装置にて、装置内の圧力条件およびガス条件などを切り換えてプラズマを発生させることにより、半導体層2(シリコン膜)に対するエッチング処理を実施する。

**【0051】**

このエッチング工程では、例えばSF6主体のガスを用いてエッチング処理が行われるので、パッシベーション膜4、配線形成層3およびボンディングパッド7がマスクとして機能し、半導体層2(シリコン膜)のエッチング処理が行われる。半導体層2(シリコン膜)のエッチング処理に引き続き、その下のシリコン基板1も深さ方向にエッチング処理が行われる。

**【0052】**

プラズマエッチングによって、図5(F)に示すようにダイシングライン部5の下にあるシリコン基板1の裏面側まで貫通すると、プラズマの発生を停止させてプラズマエッチングを終了させる。

**【0053】**

第2の実施の形態によれば、例えばSF6主体のガスを用いてエッチング処理を実施するエッチング工程で、エッチングが困難である裏面電極層8が存在しない状態で、ダイシング部5を分断する事ができる。

このようにエッチング工程では、表面側から、プラズマエッチング可能な深さまで、シリコン基板1をエッチングする。

(7) 剥離工程

**【0054】**

10

20

30

40

50

S 2 0 7において、レジスト膜9を除去した後のシリコン基板1を、ダイスピッカーを用いてテープから剥離する。例えば、ダイシングテープ上に張り付いたチップの剥離を容易にする為に、UV光を照射しテープの粘着性を劣化させた物を、ダイスピッカーにてトレーに整列、収納する。ダイスピッカーは例えばダイシングテープ裏面から押し上げピンを用いて良品チップを持ち上げ、チップ表面から真空吸着法にてチップをピックアップし、トレーに整列、収納する。

【符号の説明】

【0055】

1 シリコン基板(半導体ウエハ)

1 A 基板の表面側

10

1 B 基板の裏面側

2 半導体層(シリコン膜)

3 配線形成層

3 A 絶縁層

3 B 金属層

4 パッシベーション膜

5 ダイシングライン部(分離領域)

6 チップ部(チップ領域)

7 ボンディングパッド部

8 裏面電極層(金属膜)

20

9 裏面パターニングレジスト(フォトレジスト膜)

1 0 レジストコーラー

1 1 露光装置

1 2 デベロッパー

1 2 スパッタリング装置

1 3 真空蒸着装置

1 4 ダイシングテープ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開昭61-287241(JP,A)

特開2002-093749(JP,A)

特開平08-120443(JP,A)

特開2002-184698(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/301