(12)发明专利

(10)授权公告号 CN 106057797 B

(45)授权公告日 2019.09.27

(21)申请号 201610377205.0

(74)专利代理机构 北京纪凯知识产权代理有限公司 11245

(22)申请日 2011.10.26

代理人 赵蓉民 徐东升

(65)同一申请的已公布的文献号

申请公布号 CN 106057797 A

(51)Int.Cl.

H01L 27/02(2006.01)

(43)申请公布日 2016.10.26

H01L 29/78(2006.01)

(30)优先权数据

H01L 21/336(2006.01)

61/406,640 2010.10.26 US

H01L 21/782(2006.01)

13/281,260 2011.10.25 US

(56)对比文件

(62)分案原申请数据

CN 101383376 A, 2009.03.11,

201180051651.8 2011.10.26

US 2005110081 A1, 2005.05.26,

(73)专利权人 德克萨斯仪器股份有限公司

US 2009256212 A1, 2009.10.15,

地址 美国德克萨斯州

审查员 卫国统

(72)发明人 S·P·彭哈卡 J·林

权利要求书3页 说明书5页 附图6页

(54)发明名称

混合型有源-场间隙延伸漏极MOS晶体管

(57)摘要

一种集成电路(100)包括具有并行交替的有源间隙漂移区和场间隙漂移区的延伸漏极MOS晶体管(102)。延伸漏极MOS晶体管包括在场间隙漂移区上具有场板的栅极。延伸漏极MOS晶体管可以以对称嵌套配置形成。用于形成包含延伸漏极MOS晶体管的集成电路的工艺提供并行交替的有源间隙漂移区和场间隙漂移区，其中栅极在场间隙漂移区上具有场板。

1. 一种集成电路，其包括：

半导体衬底；以及

延伸漏极金属氧化物半导体晶体管即EDMOS晶体管，其包括：

位于所述半导体衬底中的沟道区；

位于所述半导体衬底中的延伸漏极，所述延伸漏极包括漂移区，所述漂移区具有场间隙漂移区和与所述场间隙漂移区交替的有源间隙区，所述漂移区紧靠所述沟道区；

场氧化物结构，其被定位成邻近所述场间隙漂移区且与所述沟道区相对；以及

位于所述延伸漏极上的漏极接触扩散区，所述漏极接触扩散区比所述延伸漏极具有更高的掺杂浓度，并且紧靠所述有源间隙区并与所述场氧化物结构交插。

2. 根据权利要求1所述的集成电路，其中所述延伸漏极在所述场氧化物结构的下面延伸。

3. 根据权利要求1所述的集成电路，其还包括：

栅极介电层，其位于所述沟道区和所述漂移区上方；以及

栅极，其位于所述栅极介电层上，在所述沟道区上方。

4. 根据权利要求3所述的集成电路，其中所述栅极包括场板，所述场板延伸超出所述栅极介电层并延伸到所述场氧化物结构上。

5. 根据权利要求1所述的集成电路，其还包括：

位于所述漏极接触扩散区上的漏极触点，所述漏极触点通过所述场氧化物结构与所述场间隙漂移区隔开。

6. 根据权利要求1所述的集成电路，其还包括：

位于所述漏极接触扩散区上的漏极触点，所述漏极触点内插在两个所述场氧化物结构之间。

7. 根据权利要求1所述的集成电路，其还包括：

位于所述漏极接触扩散区上的第一漏极触点，所述第一漏极触点通过所述场氧化物结构与所述场间隙漂移区隔开；

位于所述漏极接触扩散区上的第二漏极触点，所述第二漏极触点内插在两个所述场氧化物结构之间，并且所述第二漏极触点被定位成比所述第一漏极触点更靠近所述沟道区。

8. 根据权利要求1所述的集成电路，其中至少一个所述场氧化物结构紧靠至少一个所述场间隙漂移区、至少一个所述有源间隙区以及所述漏极接触扩散区。

9. 根据权利要求1所述的集成电路，其中至少一个所述场氧化物结构将至少一个所述场间隙漂移区与所述漏极接触扩散区分开。

10. 根据权利要求1所述的集成电路，其中至少一个所述场氧化物结构接合至少一个所述有源间隙区与所述漏极接触扩散区之间的结区。

11. 一种延伸漏极金属氧化物半导体晶体管即EDMOS晶体管，其包括：

延伸漏极，其包括位于栅极电极的场板下方的场间隙漂移区和与所述场间隙漂移区交替的有源间隙区；

场氧化物元件，每个场氧化物元件位于所述场板中的相应场板下方；以及

漏极接触扩散区，其位于所述延伸漏极上，所述漏极接触扩散区包括多个漏极触点，所述漏极触点的第一子集中的每个漏极触点邻近所述有源间隙区中的相应有源间隙区，并且

所述漏极触点的第二子集中的每个漏极触点邻近所述场氧化物元件中的相应场氧化物元件,所述漏极接触扩散区具有:

第一部分,每个第一部分位于所述有源间隙区中的一个有源间隙区与漏极触点的所述第一子集中的相应漏极触点之间;以及

第二部分,每个第二部分位于所述场氧化物元件中的一个场氧化物元件与漏极触点的所述第二子集中的相应漏极触点之间。

12. 根据权利要求11所述的EDMOS晶体管,其还包括:

位于所述延伸漏极内的介电结构,所述介电结构将所述漏极接触扩散区的至少一个所述第二部分与至少一个所述场间隙漂移区分开,并且所述介电结构接合至少一个所述有源间隙区与所述漏极接触扩散区的至少一个所述第一部分之间的结区。

13. 根据权利要求11所述的EDMOS晶体管,其还包括:

源极区,其与所述延伸漏极相对;

沟道区,其内插在所述源极区和所述延伸漏极之间;

栅极介电层,其位于所述沟道区和所述延伸漏极上方;以及

栅极,其位于所述栅极介电层上,在所述沟道区上方。

14. 根据权利要求13所述的EDMOS晶体管,其中所述栅极包括将所述栅极介电层与所述漏极接触扩散区屏蔽开的场板。

15. 根据权利要求13所述的EDMOS晶体管,其中:

所述栅极介电层不与所述有源间隙区重叠;以及

所述栅极不与所述有源间隙区重叠。

16. 一种集成电路,其包括:

延伸漏极金属氧化物半导体晶体管即EDMOS晶体管,每个EDMOS晶体管包括:

延伸漏极,其包括位于栅极电极的场板下方的场间隙区和位于所述场间隙区之间的有源间隙区;

场氧化物元件,每个场氧化物元件位于所述场板中的相应场板下方;以及

位于所述延伸漏极上面的漏极接触区,所述漏极接触区包括多个漏极触点,所述漏极触点的第一子集中的每个漏极触点邻近所述有源间隙区中的相应有源间隙区,并且所述漏极触点的第二子集中的每个漏极触点邻近所述场氧化物元件中的相应场氧化物元件,所述漏极接触区具有:

第一部分,每个第一部分位于所述有源间隙区中的一个有源间隙区与漏极触点的所述第一子集中的相应漏极触点之间;以及

第二部分,每个第二部分位于所述场氧化物元件中的一个场氧化物元件与漏极触点的所述第二子集中的相应漏极触点之间。

17. 根据权利要求16所述的集成电路,其中每个所述EDMOS晶体管包括:

位于所述延伸漏极内的介电结构,所述介电结构将所述漏极接触扩散区的至少一个所述第二部分与至少一个所述场间隙漂移区分开,并且所述介电结构接合至少一个所述有源间隙区与所述漏极接触扩散区的至少一个所述第一部分之间的结区。

18. 根据权利要求16所述的集成电路,其中每个所述EDMOS晶体管包括:

源极区,其与所述延伸漏极相对;

沟道区，其内插在所述源极区和所述延伸漏极之间；

栅极介电层，其位于所述沟道区和所述延伸漏极上方；以及

栅极，其位于所述栅极介电层上，在所述沟道区上方。

19. 根据权利要求18所述的集成电路，其中所述栅极包括将所述栅极介电层与所述漏极接触扩散区屏蔽开的场板。

20. 根据权利要求18所述的集成电路，其中：

所述栅极介电层不与所述有源间隙区重叠；以及

所述栅极不与所述有源间隙区重叠。

## 混合型有源-场间隙延伸漏极MOS晶体管

[0001] 本申请是于2011年10月26日提交的名称为“混合型有源-场间隙延伸漏极MOS晶体管”的中国专利申请201180051651.8 (PCT/US2011/057843) 的分案申请。

### 技术领域

[0002] 本发明涉及集成电路,更具体地涉及集成电路中的延伸漏极MOS晶体管。

### 背景技术

[0003] 集成电路可以包括延伸漏极金属氧化物半导体(MOS)晶体管,其中在漏极区中的漂移区邻近沟道区,这类晶体管例如横向扩散金属氧化物半导体(LDMOS)晶体管、双扩散金属氧化物半导体(DMOS)晶体管或漏极延伸金属氧化物半导体(DEMOS)晶体管。通常,漂移区中的平均掺杂小于MOS晶体管的源极区中的平均掺杂密度的一半。漂移区由栅极延伸场板覆盖的延伸漏极MOS晶体管(有时被称为场间隙MOS晶体管)可以展示出高于10伏的击穿电压,但由于漏极中的场氧化物元件终止场板,因此在漏极中可能具有不期望大的电阻。在漂移区上没有场板的延伸漏极MOS晶体管(有时称为有源间隙MOS晶体管)由于在栅极边缘处产生热载流子,因此可能不期望地展示出低于10伏的击穿电压和退化的可靠性。

### 发明内容

[0004] 集成电路可以包括具有并行交替的有源间隙漂移区和场间隙漂移区的延伸漏极MOS晶体管。延伸漏极MOS晶体管包括在场间隙漂移区上方具有场板的栅极。可以形成对称嵌套配置的延伸漏极MOS晶体管。公开了形成集成电路的工艺。

### 附图说明

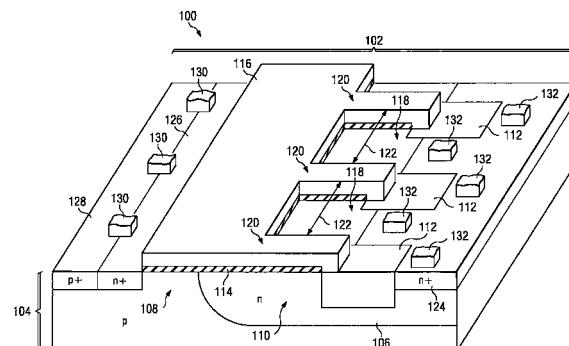

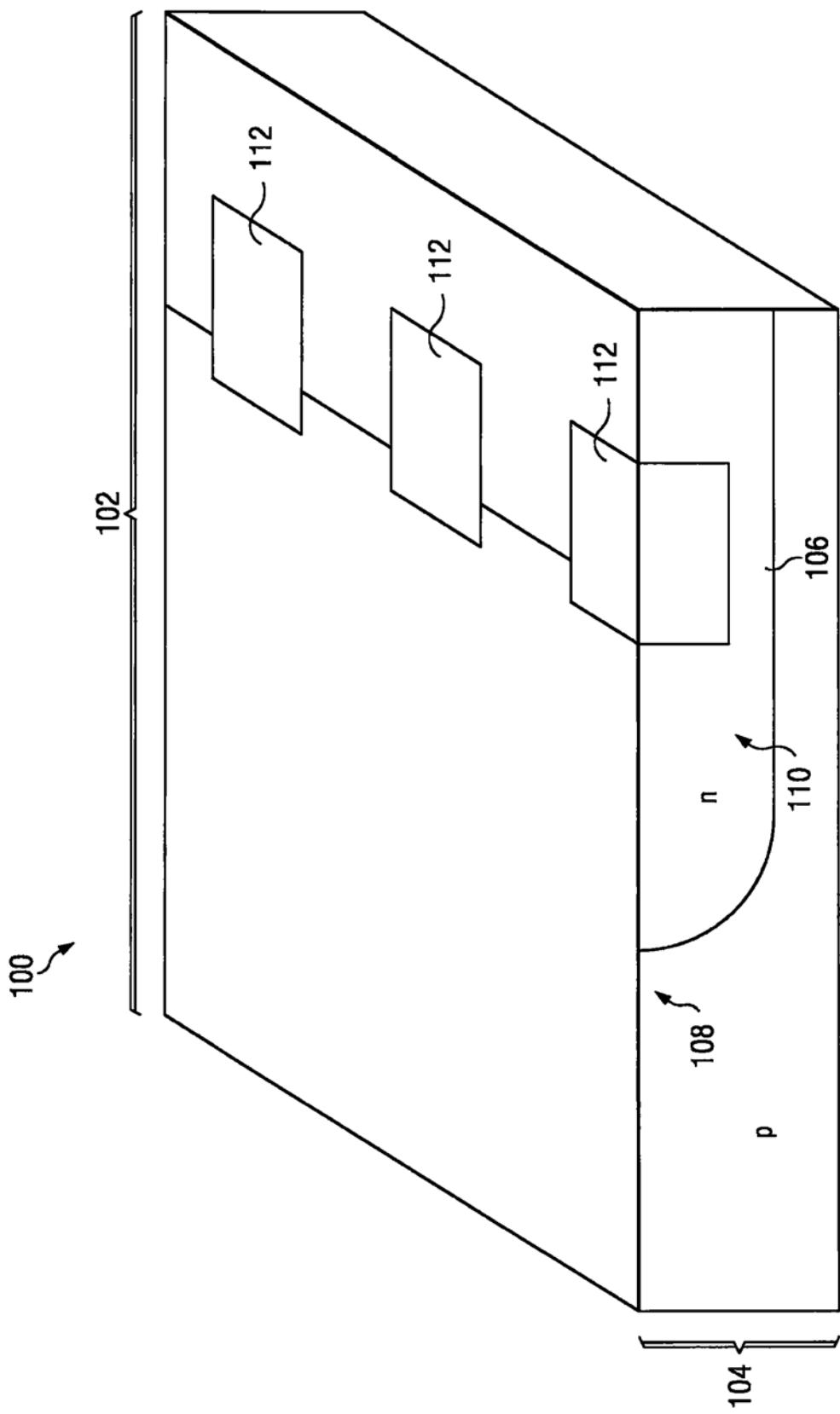

[0005] 图1A和图1B是以连续制造阶段描绘的、包含根据实施例形成的混合型有源-场间隙延伸漏极MOS晶体管的集成电路的透视图。

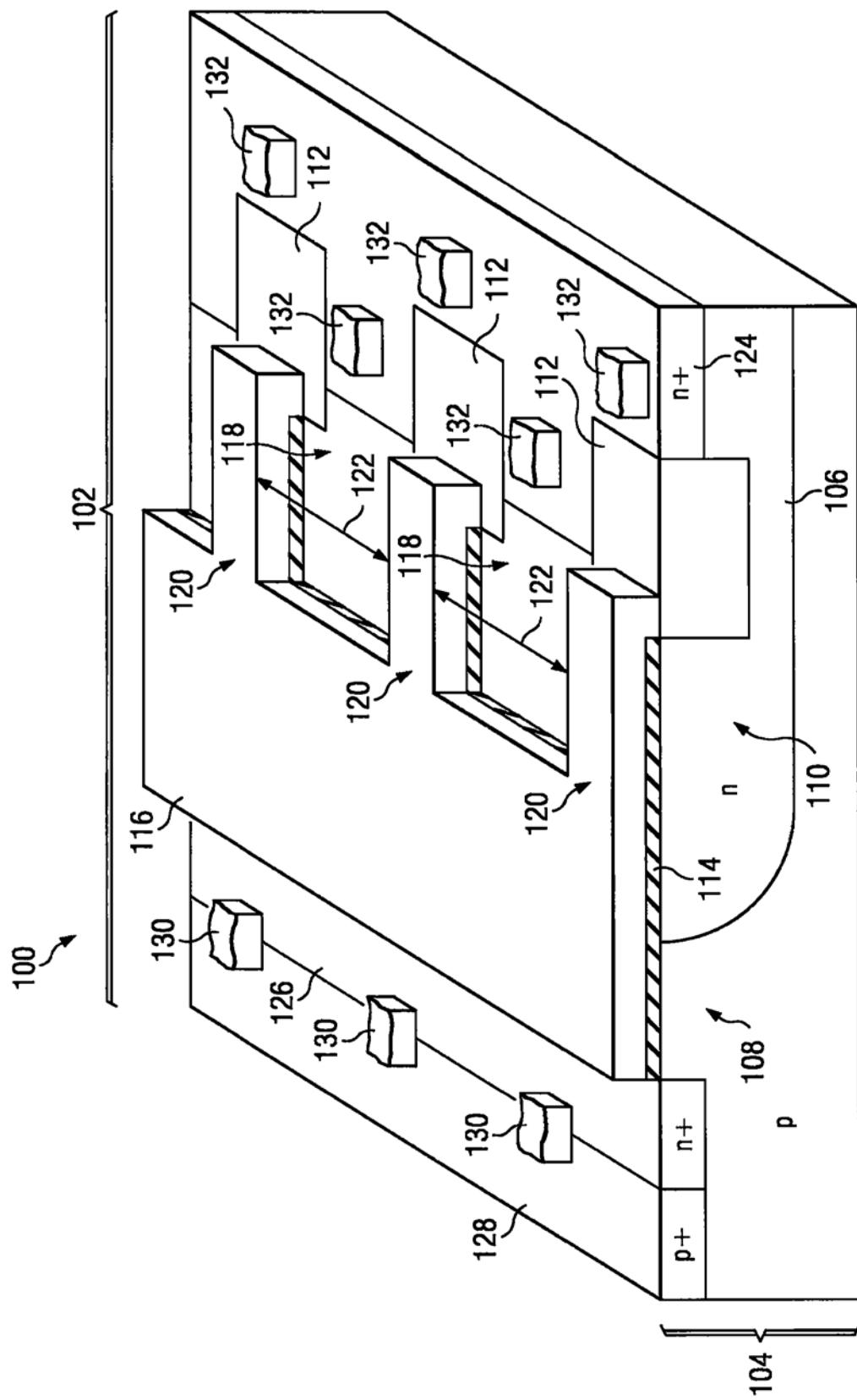

[0006] 图2是包含根据另一个实施例形成的混合型有源-场间隙延伸漏极MOS晶体管的集成电路的透视图。

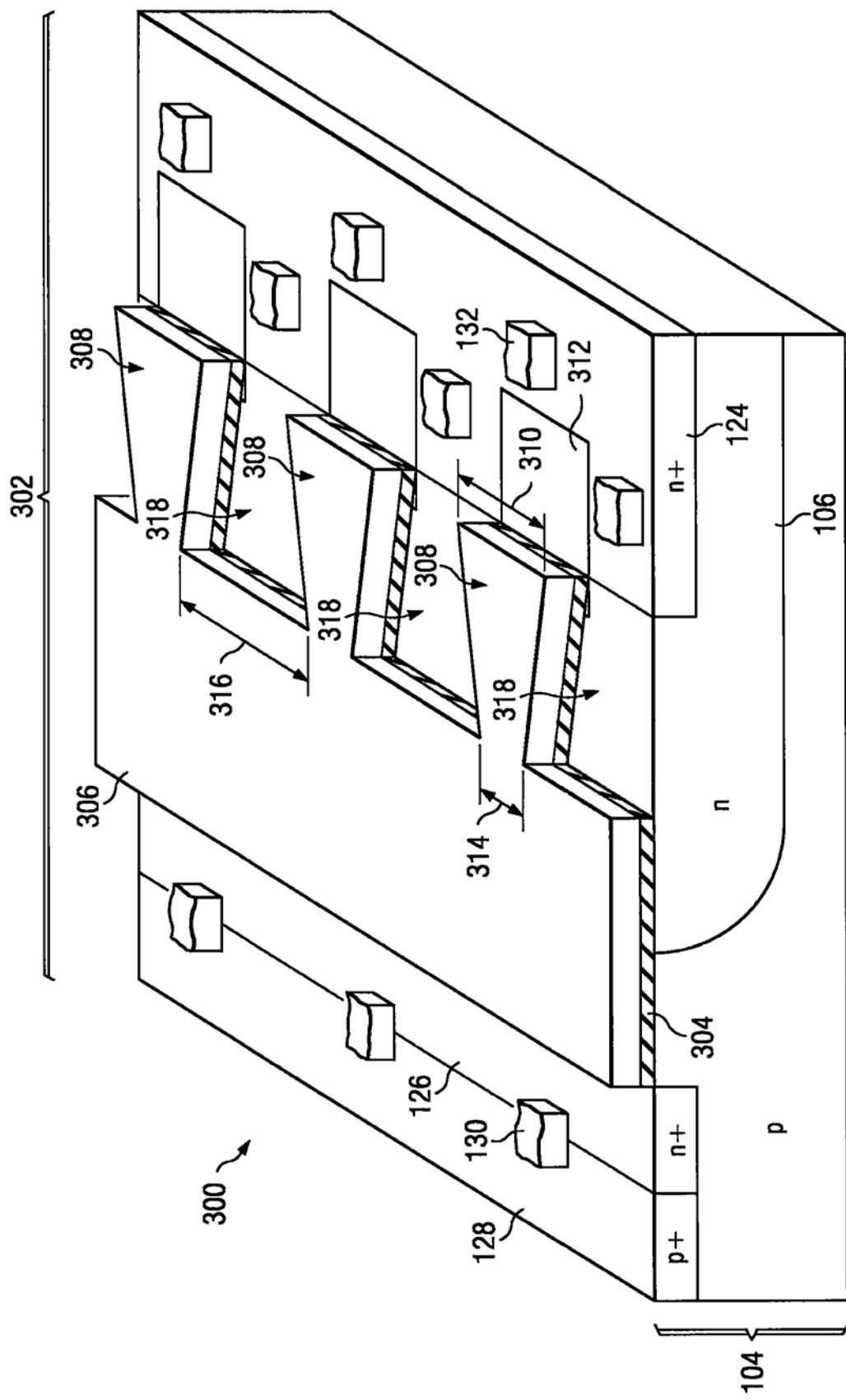

[0007] 图3是包含根据其他实施例形成的混合型有源-场间隙延伸漏极MOS晶体管的集成电路的透视图。

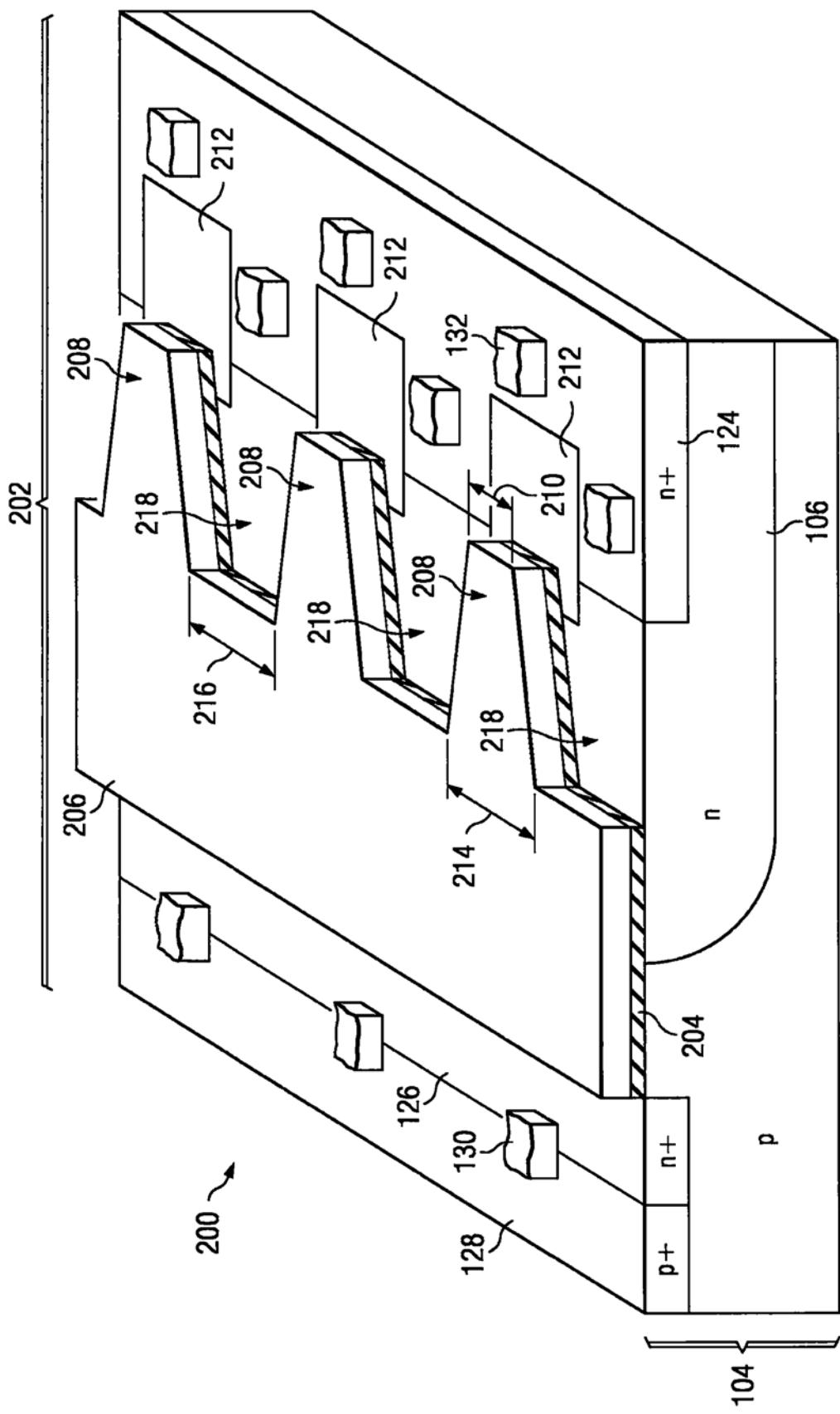

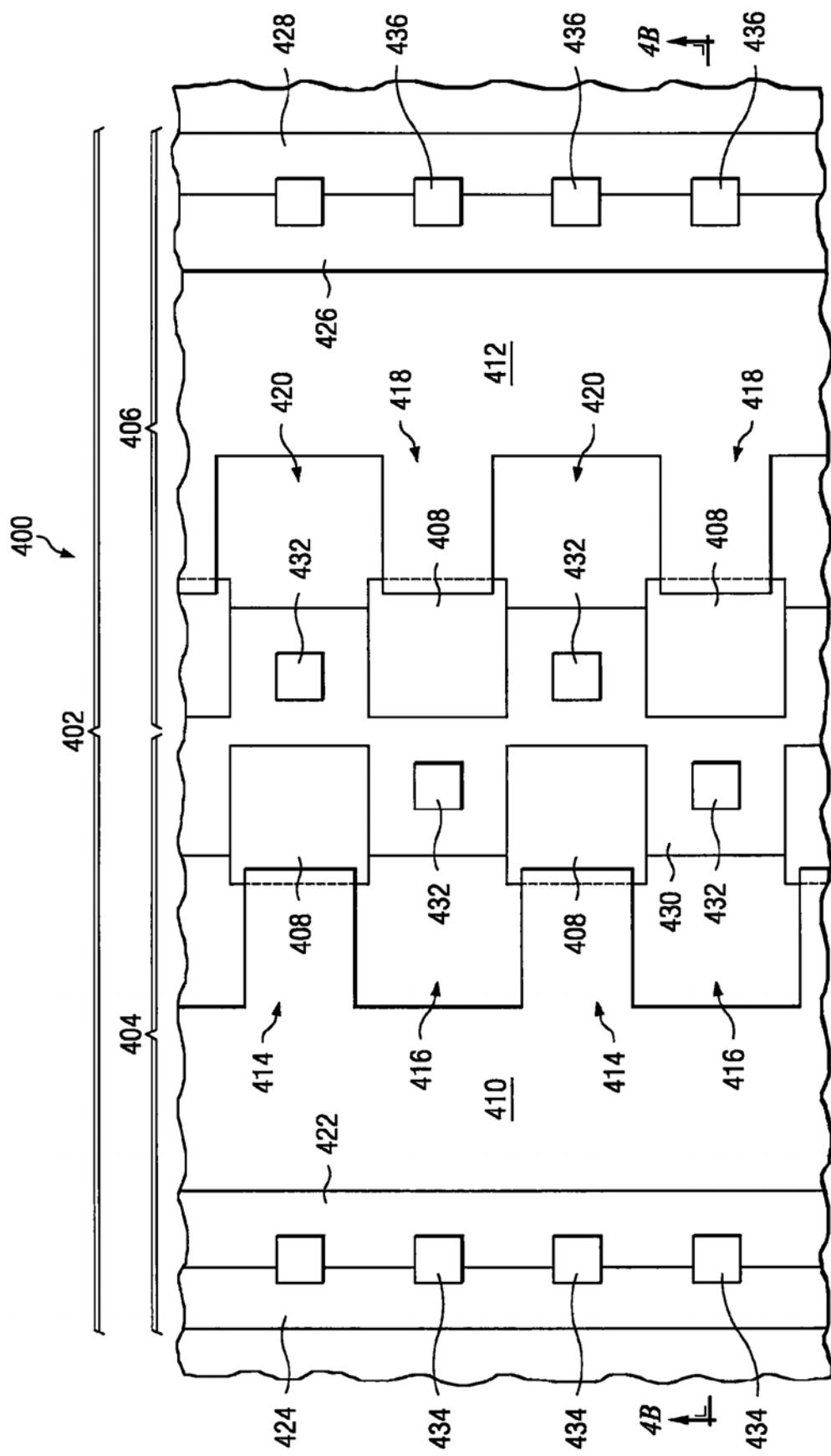

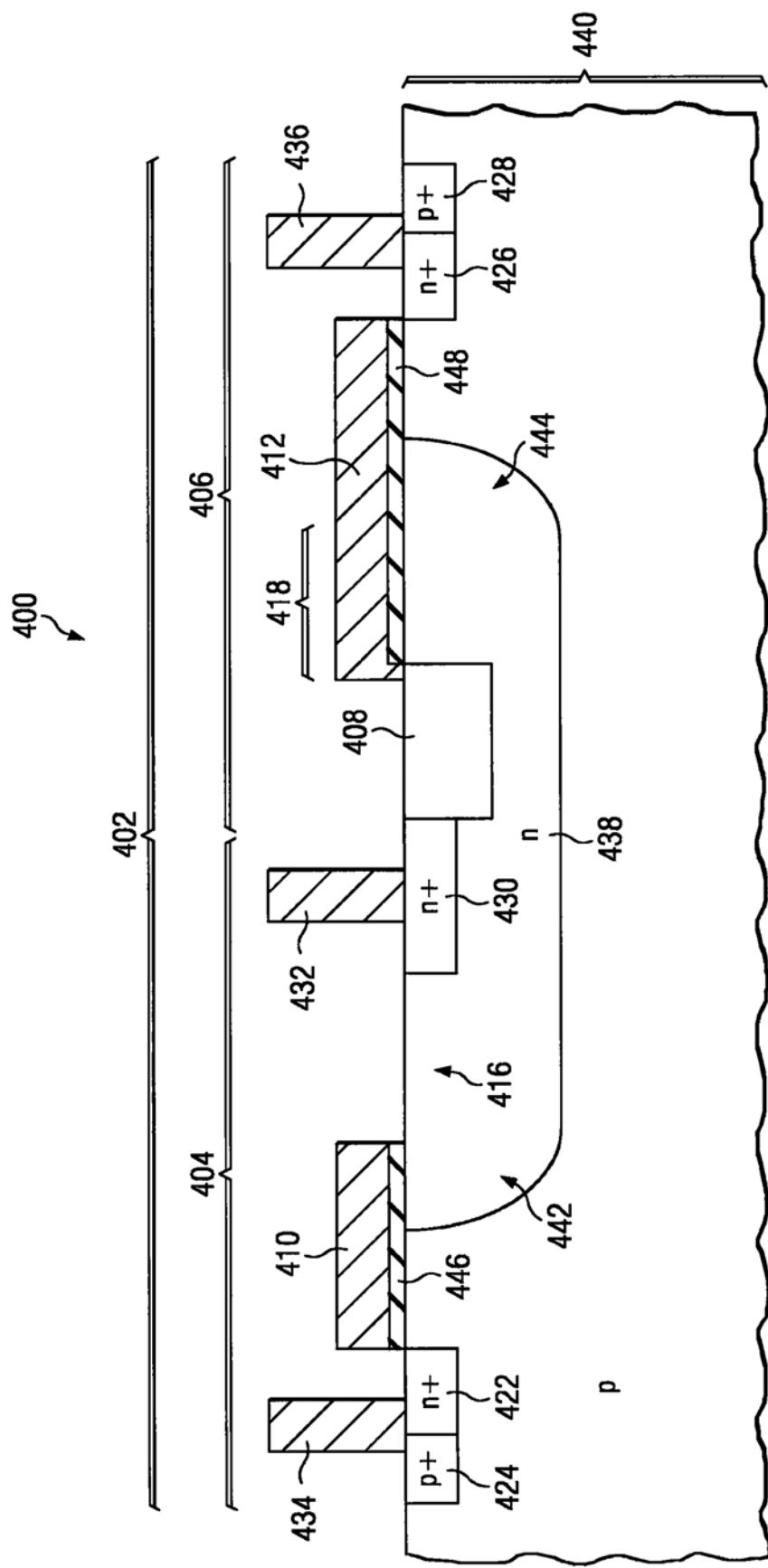

[0008] 图4A和图4B分别是集成电路的顶视图和剖视图,该集成电路包含根据实施例以对称嵌套配置形成的混合型有源-场间隙延伸漏极MOS晶体管。

### 具体实施方式

[0009] 集成电路可以包括具有多个并行交替的有源间隙漂移区和场间隙漂移区的混合型有源-场间隙延伸漏极MOS晶体管。场板是栅极的延伸部分。场板终止于延伸漏极MOS晶体管的漏极中的场氧化物元件。

[0010] 图1A和图1B示出以连续制造阶段描绘的、包含根据实施例形成的混合型有源-场

间隙延伸漏极MOS晶体管102的集成电路100。集成电路100形成在衬底104中和在其上，该衬底可以为单晶硅晶片、绝缘体上硅(SOI)晶片、具有不同晶向区域的混合晶向技术(HOT)晶片或其他适用于制造集成电路100的材料。在衬底104中紧靠延伸漏极MOS晶体管102的沟道区108形成延伸漏极MOS晶体管102的延伸漏极106。延伸漏极106包括漂移区110。延伸漏极106可以由例如包括以下步骤的工艺形成：在衬底104上通过光刻工艺形成光刻胶的离子注入掩模，以便暴露延伸漏极106的区域；将掺杂剂离子注入到衬底104中由离子注入掩模暴露的区域中；移除离子注入掩模；以及对衬底104进行退火，以便激活注入的掺杂剂。在延伸漏极106中邻近漂移区110形成场氧化物元件112。场氧化物112可以是例如主要由250到600纳米厚的二氧化硅构成。场氧化物元件112可以通过如图1A描绘的浅槽隔离(STI)工艺、硅局部氧化(LOCOS)工艺或其他方法形成。STI工艺可以包括以下步骤：在衬底104上形成氧化层；在氧化层上形成氮化硅层；图形化氮化硅层，以便暴露场氧化物112的一区域；在衬底中暴露的区域中刻蚀槽至一合适深度，以便得到期望厚度的场氧化物112；在槽的侧壁和底部上生长热氧化物层；通过化学气相沉积(CVD)、高密度等离子体(HDP)或高纵横比工艺(HARP)用二氧化硅填充槽；从氮化硅层的顶表面去除不需要的二氧化硅；以及去除氮化硅层。LOCOS工艺可以包括以下步骤：在衬底104上形成氧化层；在氧化层上形成氮化硅层；图形化氮化硅层，以便暴露场氧化物112的一区域；在暴露的区域中衬底104的顶表面上生长热氧化层至一合适厚度，以便得到期望厚度的场氧化物112；以及去除氮化硅层。

[0011] 延伸漏极106在场氧化物元件112的下面延伸。在本实施例的替代版本中，可以在形成延伸漏极106之前形成场氧化物元件112。

[0012] 参考图1B，在衬底104上沟道区108和漂移区110上方形成栅极介电层114。栅极介电层114可以是例如二氧化硅、氮氧化硅、氧化铝、氮氧化铝、氧化铪、硅酸铪、铪硅氧氮化物、氧化锆、硅酸锆、锆硅氧氮化物、上述材料的组合或其他绝缘材料的一层或多层。由于在50°C到800°C之间的温度下暴露于含氮的等离子体或含氮的环境气体，因此栅极介电层114可能包括氮。栅极介电层114的厚度可以为每伏栅源偏压2.5到3.0纳米。可以通过多种栅极电介质形成工艺中的任何一种来形成栅极介电层114，例如热氧化、氧化物层的等离子体氮化和/或通过原子层沉积(ALD)的介电材料沉积。

[0013] 在栅极介电层114上形成延伸漏极MOS晶体管102的栅极116，以便暴露漂移区110的有源间隙区118，并且在有源间隙区118间形成延伸至场氧化物元件112上的场板120。栅极116可以通过例如包括以下步骤的工艺形成：在栅极介电层114上方形成栅极材料层，例如多晶的硅，通常被称为多晶硅；利用光刻工艺在栅极材料层上方形成包括光刻胶的栅极刻蚀掩模，以便覆盖栅极116的一区域；通过反应离子刻蚀(RIE)工艺执行栅极刻蚀工艺，RIE工艺从由栅极刻蚀掩模暴露的区域中的栅极材料层去除材料；以及去除栅极刻蚀掩模。

[0014] 漂移区110在场板120下面的区域为场间隙漂移区。本实施例的一个版本中，相邻场板120间的每个有源间隙区118的有源间隙宽度122小于2微米。在其他版本中，每个有源间隙区118的有源间隙宽度122小于1微米。可以在栅极116的侧表面上形成栅极侧壁间隔层。

[0015] 在延伸漏极106中紧靠有源间隙区118和场氧化物元件112形成漏极接触扩散区124。在衬底104中紧靠沟道区108且在延伸漏极106对面形成延伸漏极MOS晶体管102的源极126。漏极接触扩散区124和源极126可以例如通过包括以下步骤的工艺同时形成：通过光刻

工艺在集成电路100的现有顶表面上形成光刻胶的离子注入掩模,以便暴露漏极接触扩散区124的一区域和源极126的一区域;将掺杂剂离子注入到衬底104中由离子注入掩模暴露的区域中;去除离子注入掩模;以及对衬底104进行退火,以便激活注入的掺杂剂。

[0016] 可以在衬底104中形成背栅接触扩散区128,以便与沟道区108电连接。背栅接触扩散区128(如果形成)可以如图1B所描绘地分布,或可以是局部的。背栅接触扩散区128可以例如通过包括以下步骤的工艺形成:通过光刻工艺在集成电路100的现有顶表面上方形成光刻胶的离子注入掩模,以便暴露背栅接触扩散区128的一区域;将掺杂剂离子注入到衬底104中由离子注入掩模暴露的区域中;去除离子注入掩模;以及对衬底104进行退火,以便激活注入的掺杂剂。

[0017] 在源极126上和可选地在背栅接触扩散区128(如果存在)上形成源极触点130。在漏极接触扩散区124上形成漏极触点132。在本实施例的一个版本中,邻近每个有源间隙区118且邻近每个场氧化物元件112,与重叠场氧化物元件112的每个场板120相对地形成每个漏极触点132。触点130和132可以例如通过包括以下步骤的工艺形成:用通过光刻工艺形成的触点光刻胶图形,在衬底104上方预金属介电(PMD)层的顶表面上定义触点区域;通过利用RIE工艺去除PMD层材料来刻蚀触点区域中的接触孔,以暴露衬底104;以及用接触衬垫金属(例如钛)和接触填充金属(通常是钨)来填充接触孔,然后用刻蚀和/或CMP方法从PMD层的顶表面去除接触填充金属。

[0018] 在延伸漏极MOS晶体管102的工作期间,有源间隙区118可以提供通过漂移区110的期望阻抗,而场板120可以减小有源间隙区118中的电场,以便提供期望的高击穿电压和期望水平的热载流子可靠性。

[0019] 在本实施例的一个版本中,延伸漏极MOS晶体管102可以是N沟道,如图1A和图1B所示。在另一个版本中,延伸漏极MOS晶体管102可以是P沟道。

[0020] 图2示出包含根据另一个实施例形成的混合型有源-场间隙延伸漏极MOS晶体管202的集成电路200。在栅极介电层204上形成延伸漏极MOS晶体管202的栅极206,以便具有锥形的场板208。每个锥形场板208在氧化物元件212上方的漏极末端宽度210比每个锥形场板208在锥形场板208的与对应的场氧化物元件212相对的一侧上的源极末端宽度214小至少100纳米。在本实施例的一个版本中,每个有源间隙区218的源极末端有源间隙宽度216小于2微米。在其他版本中,每个有源间隙区218的源极末端有源间隙宽度216小于1微米。每个锥形场板208的漏极末端宽度210和源极末端宽度214是使得有源间隙区的顶表面上的每个点在场间隙漂移区中的相邻场板的一微米范围内。锥形场板208和有源间隙区218的尺寸可以被调整为提供期望的击穿电压值、导通电流和热载流子可靠性。

[0021] 在本实施例的一个版本中,延伸漏极MOS晶体管202可以是N沟道,如图2所示。在另一个版本中,延伸漏极MOS晶体管202可以是P沟道。

[0022] 图3是包含根据其他实施例形成的混合型有源-场间隙延伸漏极MOS晶体管302的集成电路300的透视图。在栅极介电层304上形成延伸漏极MOS晶体管302的栅极306,以便具有倒锥形场板308。每个倒锥形场板308在场氧化物元件312上方的漏极末端宽度310比每个倒锥形场板308在倒锥形场板308的与对应的场氧化物元件312相对的一侧上的源极末端宽度314大至少100纳米。在本实施例的一个版本中,每个有源间隙区318的源极末端有源间隙宽度316小于2微米。在其他版本中,每个有源间隙区318的源极末端有源间隙宽度316小于1

微米。倒锥形场板308和有源间隙区318的尺寸可以被调整为提供期望的击穿电压值、导通电流和热载流子可靠性。

[0023] 在本实施例的一个版本中,延伸漏极MOS晶体管302可以是N沟道,如图3所示。在另一个版本中,延伸漏极MOS晶体管302可以是P沟道。

[0024] 图4A和4B示出包含根据实施例以对称嵌套配置形成的混合型有源-场间隙延伸漏极MOS晶体管402的集成电路400。参考图4A,延伸漏极MOS晶体管402包括第一部分404和第二部分406。在第一部分404和第二部分406中以交替线性配置在延伸漏极MOS晶体管402的延伸漏极中形成场氧化物元件408,如图4所描绘的。延伸漏极在场氧化物元件408下面延伸且横向经过场氧化物元件408,并且延伸漏极包括在第一部分404中的第一漂移区和在第二部分406中的第二漂移区。延伸漏极MOS晶体管402包括在第一部分404中紧靠第一漂移区的第一沟道区,并且包括在第二部分406中紧靠第二漂移区的第二沟道区,使得第二沟道区位于延伸漏极的与第一沟道区相对的一侧。分别在第一漂移区和第一沟道区上方的栅极介电层上,以及在第二漂移区和第二沟道区上方的栅极介电层上形成第一栅极部件410和第二栅极部件412。第一栅极部件410和第二栅极部件412可以在延伸漏极MOS晶体管402的一端或两端处可选地连接。第一栅极部件410包括第一场板414,其延伸到场氧化物元件408上。第一场板414覆盖第一部分404中的第一场间隙漂移区,其与第一有源间隙区416交替。第二栅极部件412包括第二场板418,其延伸到场氧化物元件408上。第二场板418覆盖第二部分406中的第二场间隙漂移区,其与第二有源间隙区420交替。第一场板414与第二有源间隙区420对齐,且第二场板418与第一有源间隙区416对齐。在本实施例的一个版本中,相邻的第一场板414之间的每个第一有源间隙区416的有源间隙宽度和相邻的第二场板418之间的每个第二有源间隙区420的有源间隙宽度小于2微米。在其他版本中,每个第一有源间隙区域416和每个第二有源间隙区420的有源间隙宽度小于1微米。

[0025] 在第一部分404中紧靠第一沟道区且邻近第一栅极部件410形成第一源极422。可以邻近第一源极422形成第一背栅接触扩散区424,以便与第一沟道区电连接。在第二部分406中紧靠第二沟道区且邻近第二栅极部件412形成第二源极426。可以邻近第二源极426形成第二背栅接触扩散区428,以便与第二沟道区电连接。在延伸漏极中紧靠第一有源间隙区416和第二有源间隙区420且紧靠场氧化物元件408形成漏极接触扩散区430。

[0026] 在漏极接触扩散区430上邻近第一有源间隙区416和第二有源间隙区420形成漏极触点432,使得每个漏极触点432提供漏极电流给对应的邻近有源间隙区416或420以及与有源间隙区相对的对应的场间隙漂移区。在本实施例的一个版本中,邻近每个第一有源间隙区416和每个第二有源间隙区420形成漏极触点432。在第一源极422上并且可选地在第一背栅接触扩散区424(如果存在)上形成第一源极触点434。在第二源极426上并且可选地在第二背栅接触扩散区428(如果存在)上形成第二源极触点436。可以调整场氧化物元件408、第一有源间隙区416和第二有源间隙区420、第一场间隙漂移区和第二场间隙漂移区以及漏极接触扩散区430的尺寸和位置,从而降低延伸漏极MOS晶体管402的总面积,同时提供期望的导通电流、期望的击穿电压和期望的热载流子可靠性。

[0027] 参考图4B,延伸漏极438在衬底440中形成,并且包括第一部分404中的第一漂移区442和第二部分406中的第二漂移区444。第一栅极部件410在第一栅极介电层446上形成,第二栅极部件412在第二栅极介电层448上形成。

[0028] 在本实施例的一个版本中，延伸漏极MOS晶体管402可以是n沟道，如图4B中示出。在另一个版本中，延伸漏极MOS晶体管402可以是p沟道。

[0029] 本发明涉及的本领域技术人员应该理解，在不背离本发明的范围的情况下，所描述的示例实施例可以变化，且其它实施例可以实现。

图1A

图1B

图2

图3

图4A

图4B