(12)

## Patentschrift

(21) Deutsches Aktenzeichen: 11 2006 002 913.4

(86) PCT-Aktenzeichen: PCT/US2006/037750

(87) PCT-Veröffentlichungs-Nr.: WO 2007/055817

(86) PCT-Anmelddatag: 26.09.2006

(87) PCT-Veröffentlichungstag: 18.05.2007

(43) Veröffentlichungstag der PCT Anmeldung

in deutscher Übersetzung: 25.09.2008

(45) Veröffentlichungstag

der Patenterteilung: 17.09.2015

(51) Int Cl.: **H01L 21/8229 (2006.01)**

**H01L 29/74 (2006.01)**

**H01L 27/082 (2006.01)**

**H01L 27/102 (2006.01)**

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

11/263,254 31.10.2005 US

(73) Patentinhaber:

Micron Technology, Inc., Boise, Id., US

(74) Vertreter:

Kahler, Käck & Mollekopf, 86899 Landsberg, DE

(72) Erfinder:

**Mouli, Chandra, Boise, Id., US**

(56) Ermittelter Stand der Technik:

**US 7 081 378 B2**

**US 2001 / 0 024 841 A1**

**US 2002 / 0 195 665 A1**

**US 2005 / 0 093 147 A1**

(54) Bezeichnung: **Speicherzelle, Verfahren zu ihrer Herstellung und Speicherzellenmatrix**

(57) Hauptanspruch: Speicherzelle mit:

einem leitenden Ppropfen (22), der in einem Substrat (25)

ausgebildet ist;

einem Thyristor (20), der in dem Substrat (25) angeordnet

und vertikal um den leitenden Ppropfen (22) ausgebildet und

vom leitenden Ppropfen (22) durch ein Dielektrikum (27) iso-

liert ist; und

einem Mittel (62, 64, 70) zum Isolieren der Zelle (10), das auf

einer dem Substrat (25) zugewandten Seite des Thyristors

(20) ausgebildet ist;

wobei ein erster Knoten des Thyristors (20) direkt mit einer

Bitleitung (14) in einer Matrix (50) gekoppelt ist, wobei ein

zweiter Knoten des Thyristors (20) direkt mit einer Wortlei-

tung (12) in der Matrix (50) gekoppelt ist und wobei der lei-

tende Ppropfen (22) direkt mit einem Freigabegate (16) in der

Matrix (50) gekoppelt ist; und

wobei der erste Knoten und der zweite Knoten an einer Flä-

che des Substrats (25) angeordnet sind.

**Beschreibung****GEBIET DER ERFINDUNG**

**[0001]** Diese Erfindung betrifft eine Speicherzellenstruktur auf der Basis eines versenkten Thyristors für eine integrierte Schaltung.

**HINTERGRUND**

**[0002]** Viele verschiedene Arten von Speicherzellenstrukturen existieren auf dem Fachgebiet integrierter Schaltungen, jede mit ihren eigenen Vorteilen und Nachteilen. Eine herkömmliche Zelle eines dynamischen Direktzugriffsspeichers (DRAM) umfasst beispielsweise einen Kondensator zum Speichern von Ladung, die einen logischen "0"- oder "1"-Zustand darstellt, und einen Zugriffstransistor zum Zugreifen auf eine solche Ladung und Senden derselben über eine Bitleitung zu einer Leseschaltung. Eine solche Zellenstruktur ist insofern vorteilhaft, als sie relativ kompakt gemacht werden kann und daher viele solche Zellen in einer gegebenen integrierten Schaltung angeordnet werden können, die sich auf große Mengen von Speicher belaufen.

**[0003]** Nachdem dies gesagt ist, sind herkömmliche DRAM-Zellen nicht optimal. Wie gerade bemerkt, erfordern solche Zellen zwei Elemente pro Zelle – die Kondensatoren und den Zugriffstransistor. Obwohl viele verschiedene DRAM-Zellenkonstruktionen mit dem Ziel der Verringerung der Fläche, die solche Zellen auf der Oberfläche einer integrierten Schaltung einnehmen, existieren, ist die Realität, dass das Unterbringen von zwei Elementen pro Zelle ein signifikantes Größenproblem darstellt.

**[0004]** Bei einem Verfahren zur Herstellung von kleineren Speicherzellen wurde vorgeschlagen, Thyristoren als Speicherelement in einer Speicherzelle zu verwenden. Ein Thyristor umfasst im Wesentlichen zwei Dioden in Reihe oder das, was manchmal als PNPN-Struktur bezeichnet wird, was widerspiegelt, dass das Bauelement durch Dotieren von abwechselnden Polaritäten (P und N) ausgebildet wird. Wie im Stand der Technik bemerkt wurde, können Zellen auf Thyristorbasis verwendet werden, um Ladung selektiv zu speichern, und daher sind solche Zellen als Speicherzellen verwendbar. Ladung kann beispielsweise gespeichert werden, indem bewirkt wird, dass die Übergänge innerhalb der Struktur in Sperrrichtung vorgespannt werden, und eine solche selektive Speicherung kann durch Torsteuerung des Thyristors erleichtert werden.

**[0005]** Selbst Speicherzellenkonstruktionen auf Thyristorbasis sind jedoch nicht optimal. Einige erfordern oder verwenden zusätzlich zum Thyristorgate ein zusätzliches Zugriffstransistorgate zum selektiven Zulassen einer Ladungsübertragung zwischen der Bit-

leitung und dem Thyristor. Solche Zellenstrukturen leiden daher insofern unter demselben Nachteil wie herkömmliche DRAM-Zellen, als sie zwei Bauelemente – einen Zugriffstransistor und den torgesteuerten Thyristor – erfordern. In Zellen auf Thyristorbasis, die keinen Zugriffstransistor aufweisen, nehmen vorherige Strukturen immer noch im Allgemeinen übermäßige Mengen an Fläche auf der Oberfläche der integrierten Schaltung ein, beispielsweise da der Thyristor planar (d.h. horizontal) in dem Substrat der integrierten Schaltung gefertigt ist. Überdies wurde für solche Zellen auf Thyristorbasis, die keine Zugriffstransistoren aufweisen, als Ersatzmittel für herkömmliche SRAM-Zellen geworben, und es wird nicht angenommen, dass solche Zellen als DRAM-Zellen entworfen wurden, die gegenüber SRAM-Zellen in vielen Anwendungen bevorzugt sind. Noch weitere Thyristorstrukturen erfordern, dass das Substrat des Bauelements vom Massesubstrat beispielsweise unter Verwendung eines vergraben Oxids (Box) oder unter Verwendung eines SOI-(Silizium auf Isolator)Substrats isoliert wird. Die Verwendung von solchen spezialisierten Substraten fügt Komplexität und Kosten zur Herstellung der Zelle auf Thyristorbasis hinzu.

**[0006]** Kurz gesagt, das Speicherzellenfachgebiet würde von einer verbesserten Thyristorzellenstruktur profitieren, die in der Funktionalität zu einer DRAM-Zelle ähnlich ist, und eine solche Zellenstruktur wäre klein, würde keine zusätzlichen Bauelemente wie z.B. Zugriffstransistoren erfordern und würde leicht und preiswert hergestellt werden.

**[0007]** Aus der Druckschrift US 2005/0093147 A1 ist beispielsweise die Struktur und die Herstellung einer DRAM Speicherzelle bekannt. Die Druckschrift US 2002/0195665 A1 erklärt ferner die UM-OS-Planartechnologie. Die Anordnung von Speicherzellen in einer Matrix ist in der Druckschrift US 2001/0024841 A1 beschrieben. Ein Verfahren zur Herstellung einer Speicherzelle findet sich in U.S.-Patent US 7 081 378 B2.

**ZUSAMMENFASSUNG**

**[0008]** Die Erfindung ist in den Ansprüchen 1, 8, 15 bzw. 22 definiert. Besondere Ausgestaltungen der Erfindung sind Gegenstand von Unteransprüchen.

**[0009]** Insbesondere wird eine verbesserte Speicherzelle auf der Basis eines versenkten Thyristors offenbart. Die offenbare Zelle umfasst einen leitenden Ppropfen (bzw. Ppropf oder Stopfen), der in die Masse des Substrats versenkt ist und der mit dem Freigabegate der Zelle gekoppelt ist oder dieses umfasst. Vertikal um dieses versenkte Gate ist ein Thyristor angeordnet, dessen Anode (Sourcepol; Bereich vom p-Typ) mit der Bitleitung verbunden ist und dessen Kathode (Drainpol; Bereich vom n-Typ) mit der

Wortleitung verbunden ist. Abgesehen vom versenkten Freigabegate umfasst die offenbarte Zelle kein weiteres Gate wie z.B. einen Zugriffstransistor und ist daher im Wesentlichen ein Bauelement mit einem Transistor. Folglich und wie durch die vertikale Anordnung des Thyristors erleichtert, nimmt die offenbarte Zelle einen geringeren Betrag an Fläche in einer integrierten Schaltung im Vergleich zu einer herkömmlichen DRAM-Zelle ein. Überdies ist die offenbarte Zelle in ihren verschiedenen Ausführungsbeispielen einfach herzustellen und ist leicht zu einer Matrix von Zellen zu konfigurieren. Die Isolation unterhalb der Zelle unterstützt bei der Verbesserung des Datenerhalts der Zelle und verlängert die Zeit, die zwischen dem Zellenauffrischen erforderlich ist.

#### KURZBESCHREIBUNG DER ZEICHNUNGEN

**[0010]** Ausführungsbeispiele der erfindungsgemäßen Aspekte dieser Offenbarung werden am besten mit Bezug auf die folgende ausführliche Beschreibung verstanden, wenn sie in Verbindung mit den zugehörigen Zeichnungen gelesen wird, in denen gilt:

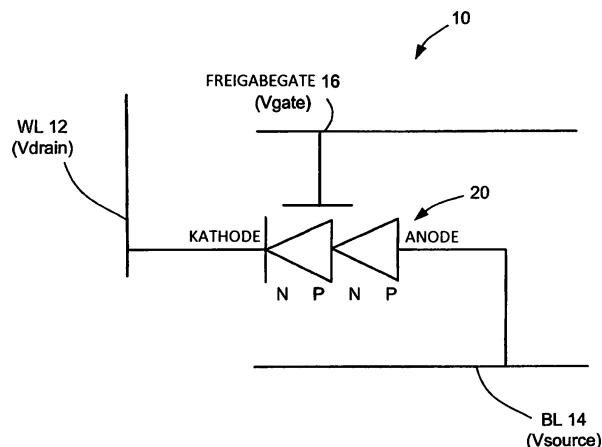

**[0011]** **Fig. 1** stellt ein Diagramm der offenbarten Zelle auf der Basis eines versenkten Thyristors dar.

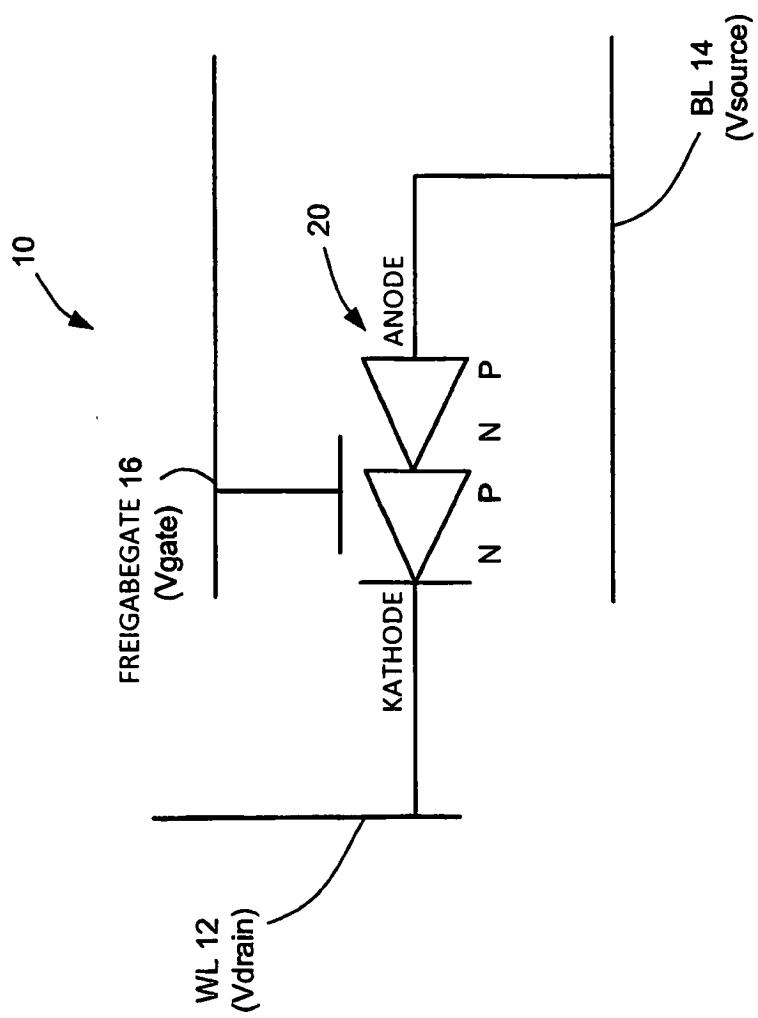

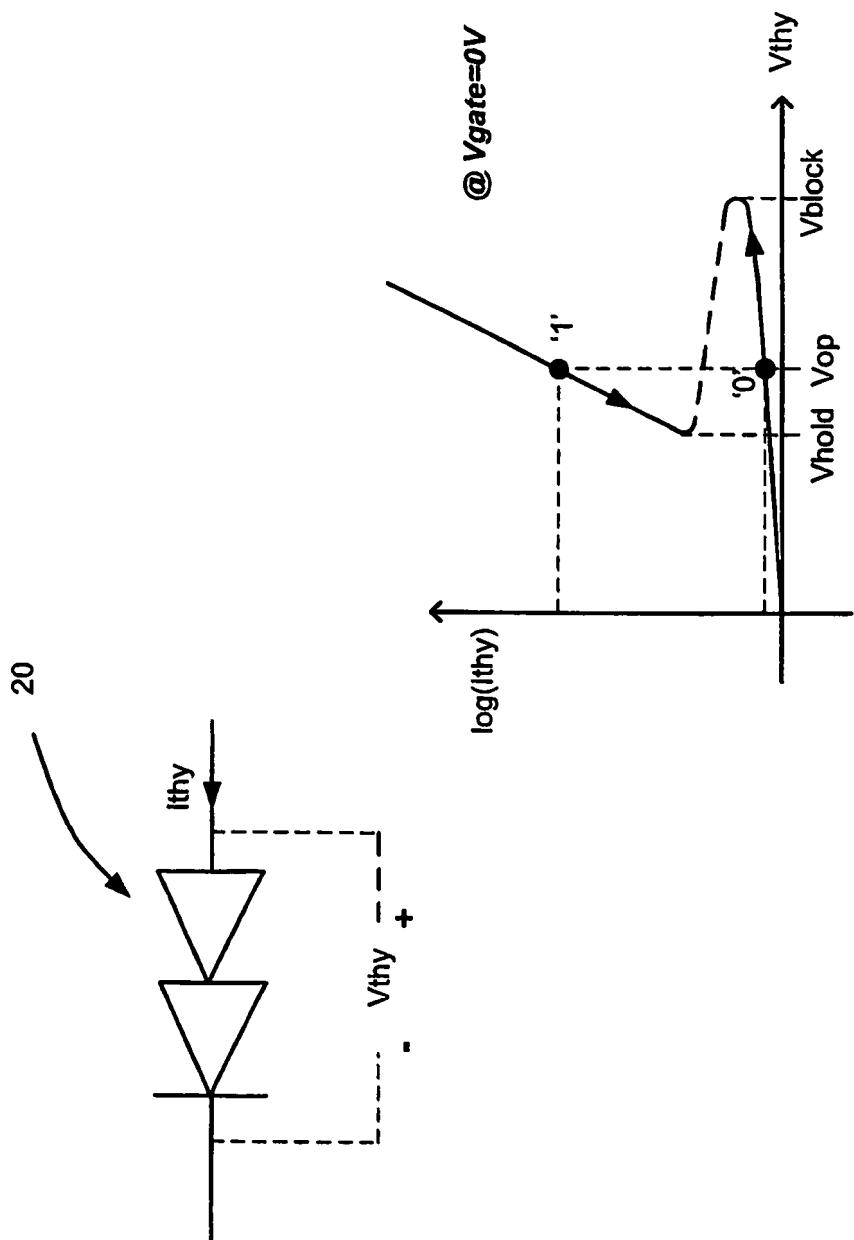

**[0012]** **Fig. 2** stellt ein Ausführungsbeispiel der offenbarten Zelle auf der Basis eines versenkten Thyristors im Querschnitt dar.

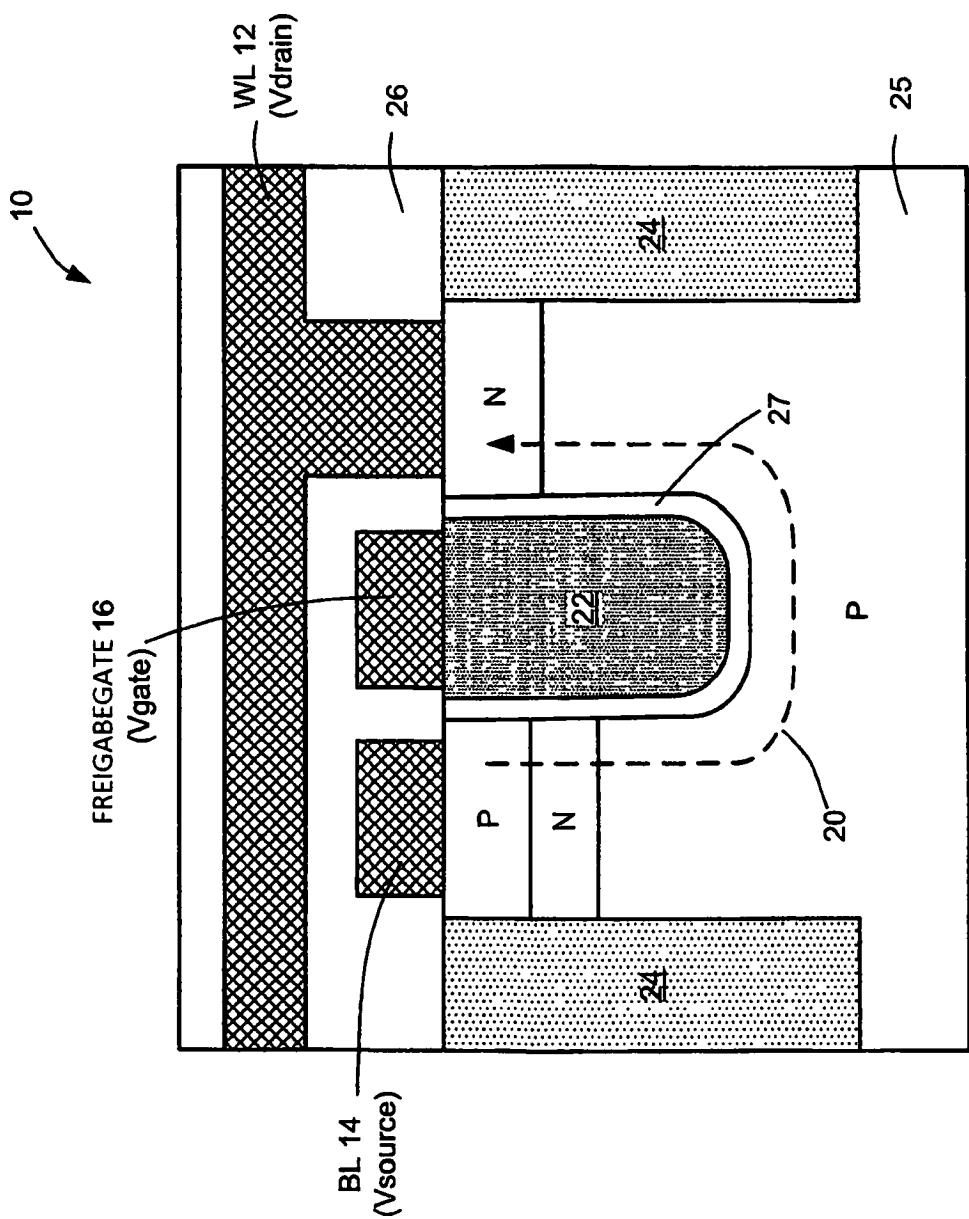

**[0013]** **Fig. 3** stellt die Strom-Spannungs-Kennlinie des Thyristors bei der offenbarten Zelle dar.

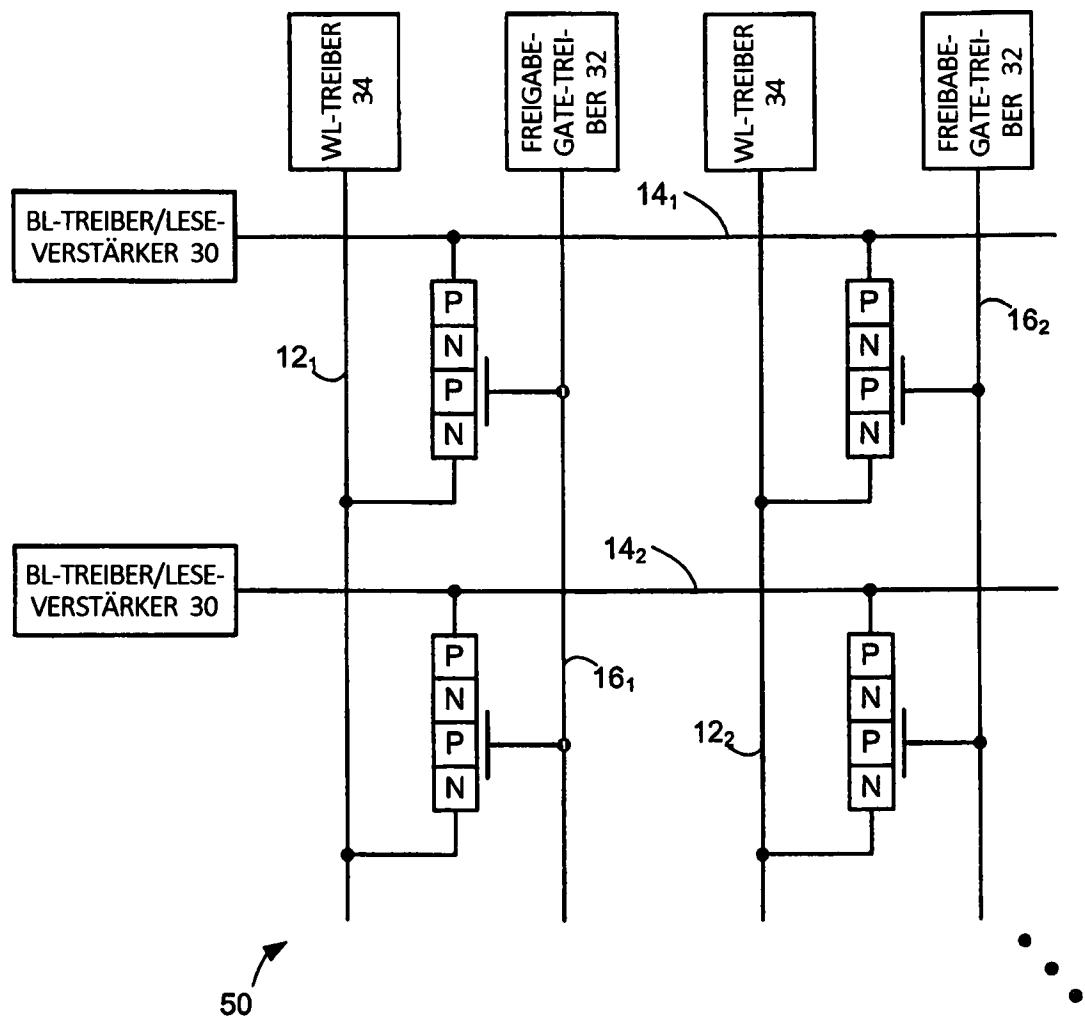

**[0014]** **Fig. 4** stellt eine Matrix der offenbarten Zellen auf der Basis eines versenkten Thyristors mit einer Matrixansteuer- und -leseschaltungsanordnung dar.

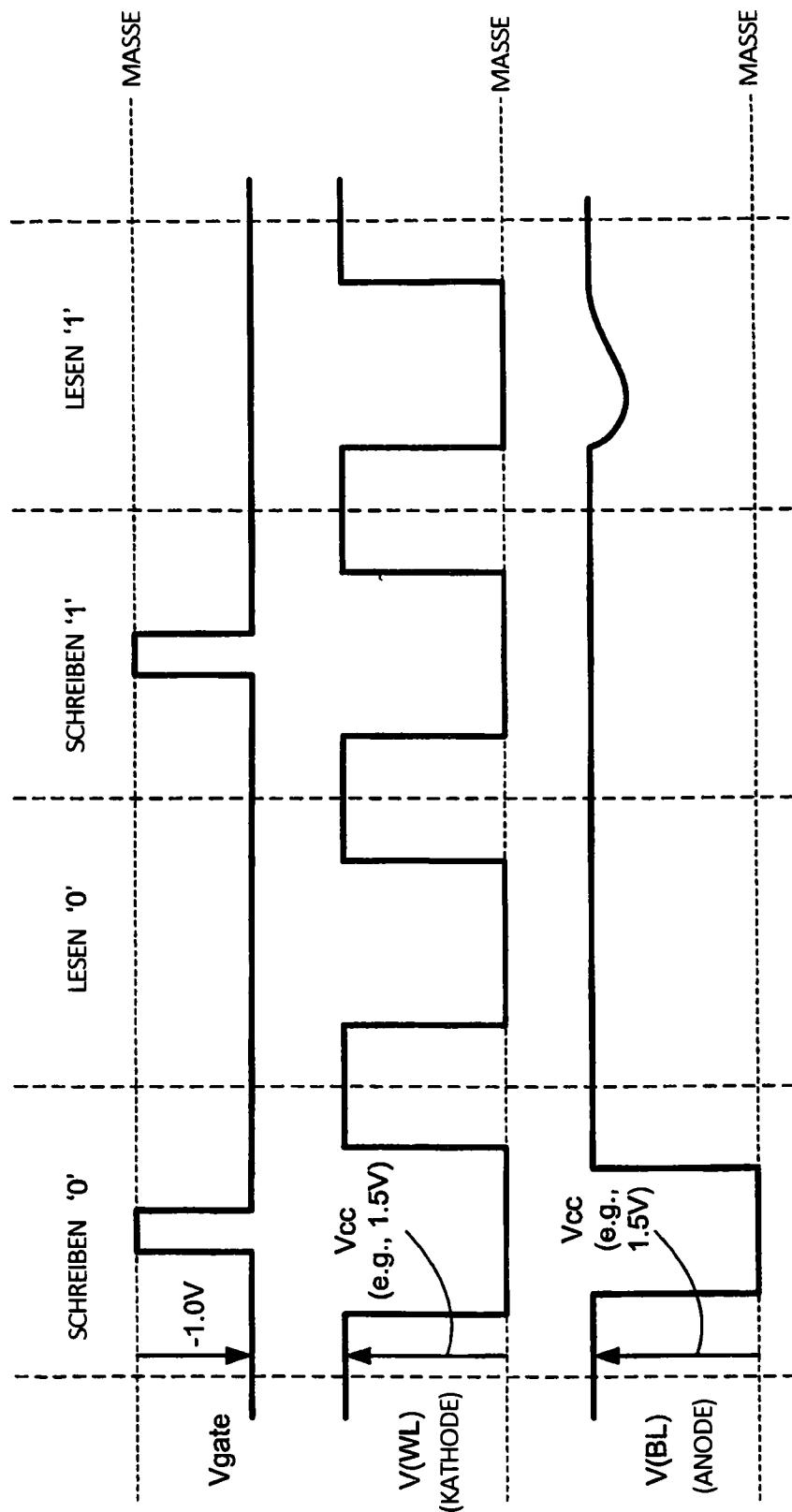

**[0015]** **Fig. 5** stellt beispielhafte Spannungsbedingungen zum Schreiben einer logischen "0" oder "1" in die offenbarte Zelle, zum Lesen der offenbarten Zelle und zum Halten einer Spannung in der offenbarten Zelle dar.

**[0016]** **Fig. 6A–Fig. 6D** stellen einen beispielhaften Prozess zur Herstellung der offenbarten Zelle auf der Basis eines versenkten Thyristors dar.

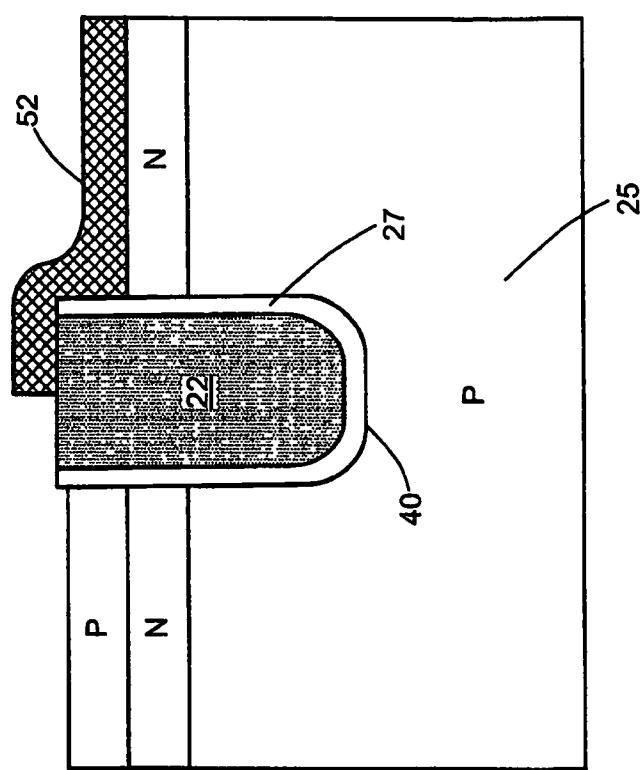

**[0017]** **Fig. 7A–Fig. 7C** stellen einen beispielhaften Prozess zur Herstellung der offenbarten Zelle auf der Basis eines versenkten Thyristors unter Verwendung von epitaxial aufgewachsenem Silizium zum Ausbilden von Bereichen des Thyristors dar.

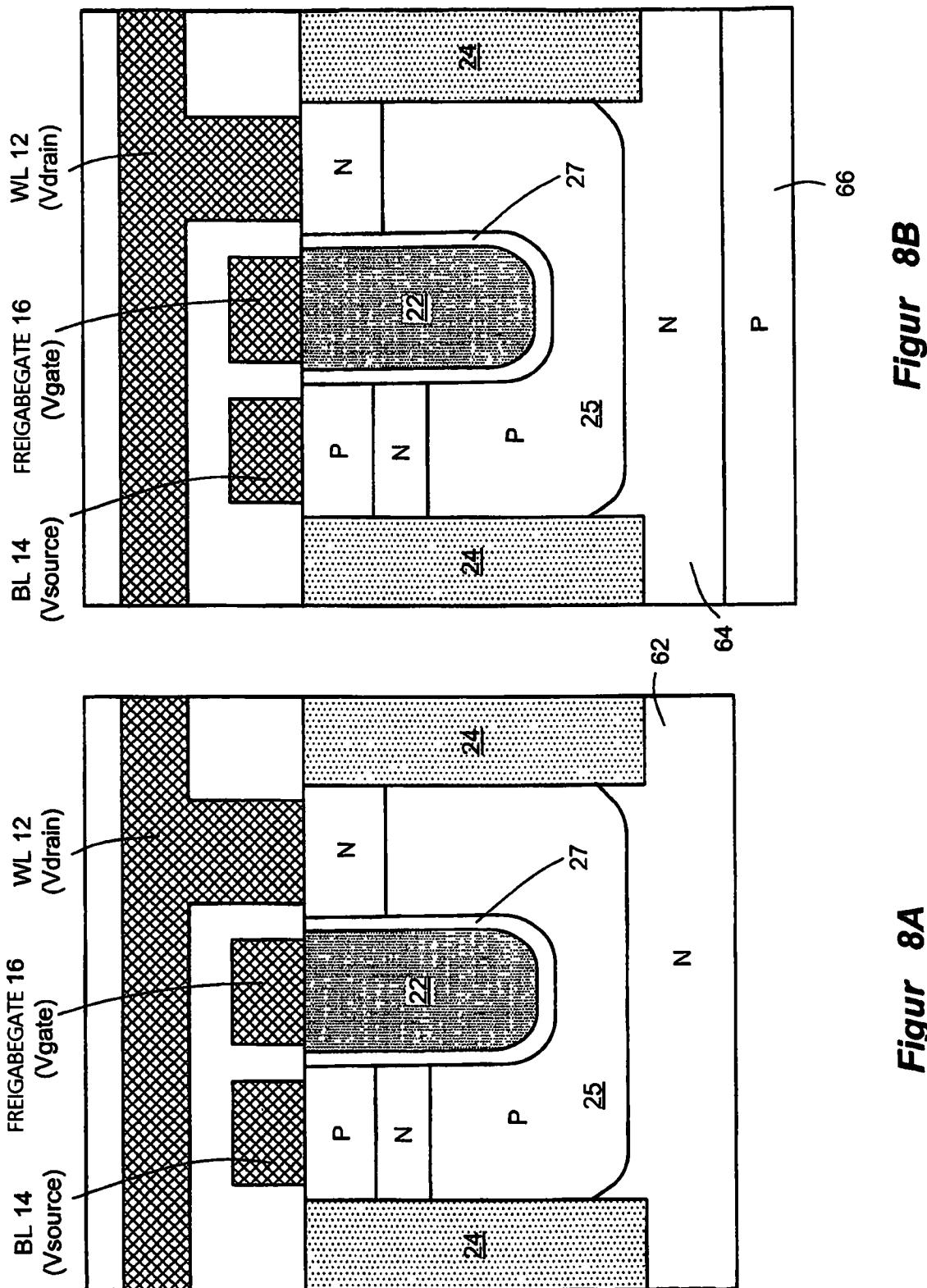

**[0018]** **Fig. 8A–Fig. 8B** stellen einen beispielhaften Prozess für die Herstellung der offenbarten Zelle auf der Basis eines versenkten Thyristors unter Verwendung einer Übergangsisolation unterhalb der Zelle dar.

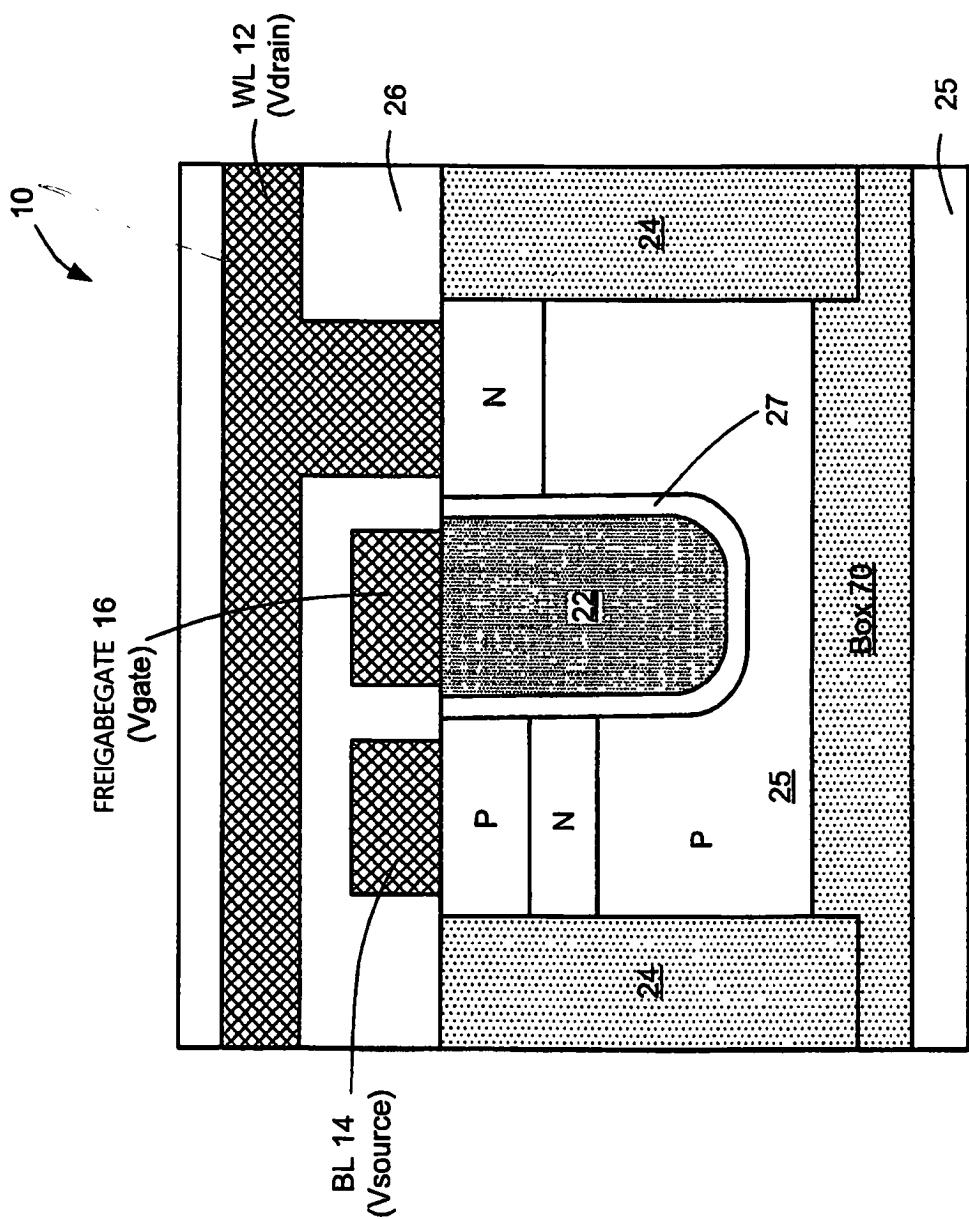

**[0019]** **Fig. 9** stellt einen beispielhaften Prozess zur Herstellung der offenbarten Zelle auf der Basis eines versenkten Thyristors unter Verwendung einer vergrabenen Oxidschicht oder eines SOI-Substrats unterhalb der Zelle dar.

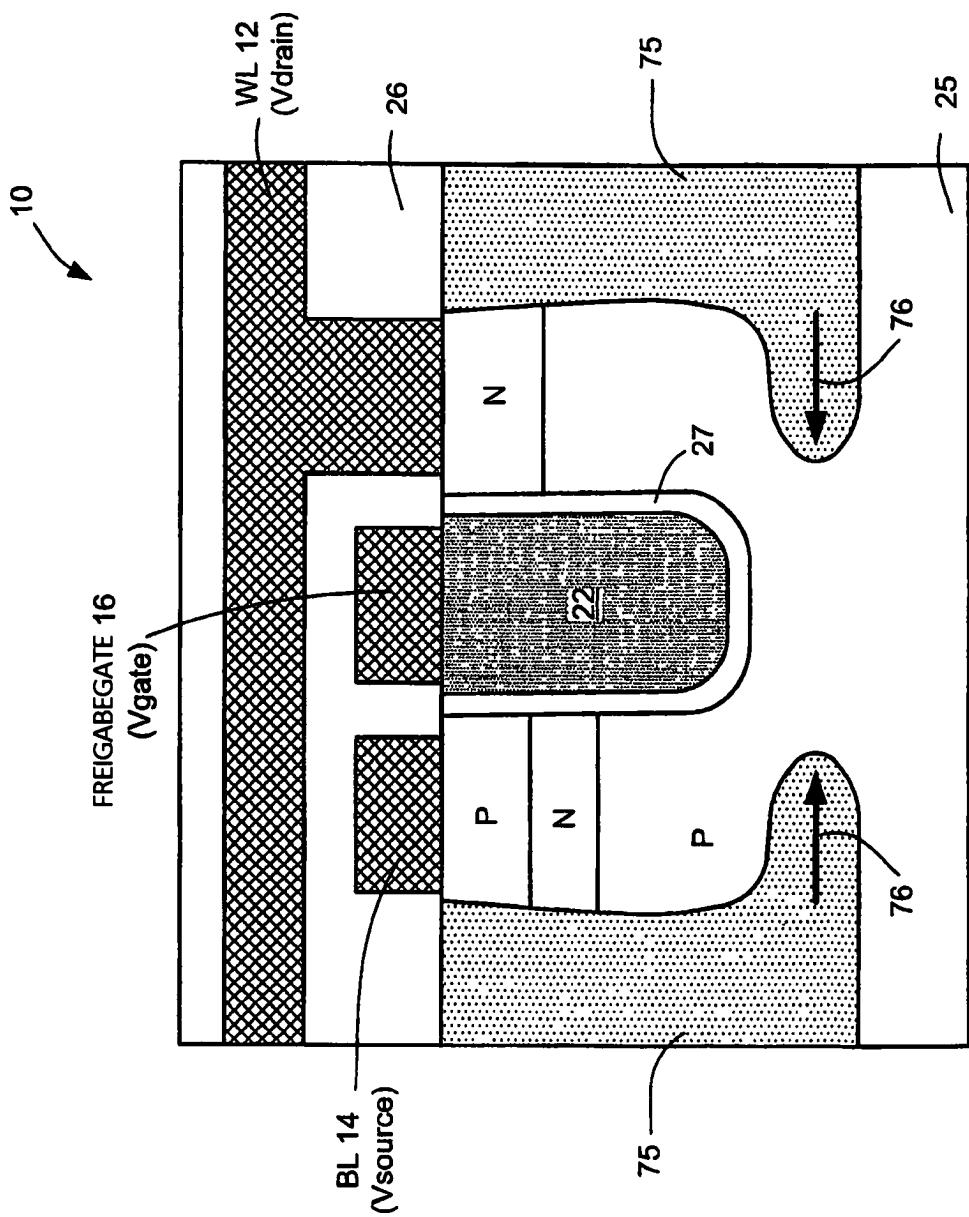

**[0020]** **Fig. 10** stellt einen beispielhaften Prozess zur Herstellung der offenbarten Zelle auf der Basis eines versenkten Thyristors unter Verwendung von Isolationsunterätzungen teilweise unterhalb der Zelle dar.

#### AUSFÜHRLICHE BESCHREIBUNG

**[0021]** Die verbesserte Speicherzelle **10** auf der Basis eines Thyristors ist schematisch in **Fig. 1** gezeigt. Wie zu sehen ist, umfasst die Zelle **10** einen Thyristor **20**, der, wie vorher angegeben, eine PNPN-Struktur ist und daher als zwei in Reihe geschaltete Dioden für eine einfache Erläuterung dargestellt ist. Die Anode oder der Sourcepol des Thyristors **20** (der äußere P-Bereich) ist mit einer Bitleitung **14** gekoppelt. Die Kathode oder der Drainpol des Thyristors **20** (der äußere N-Bereich) ist mit einer Wortleitung **12** gekoppelt. Der Thyristor **20** wird durch ein Freigabegate **16** tor gesteuert.

**[0022]** Wie bereits aus dem Diagramm von **Fig. 1** ersichtlich sein sollte, ist die Zelle **10** in der Konstruktion einfach. Sie erfordert nur ein einzelnes Gate (**16**) und umfasst somit eine Zelle mit einem Transistor, etwa ähnlich zum Zugriffstransistor einer herkömmlichen DRAM-Zelle, jedoch ohne diskreten Speicher kondensator. Überdies und wie in den anschließenden Figuren zu sehen ist, ist der Teil des Thyristors **20** der Zelle auf kompakte Weise in einem herkömmlichen Halbleitersubstrat, z.B. einem p-dotierten Substrat, realisierbar. Die Zelle **10** erfordert keine Substratisolation unter der Zelle, obwohl, wie mit Bezug auf **Fig. 8–Fig. 10** erörtert wird, eine solche Isolation, falls sie verwendet wird, die Leistung der Zelle weiter verbessern kann und die zwischen Auffrischungen der Zelle erforderliche Zeit verlängern kann.

**[0023]** Die Zelle **10** ist vorzugsweise in das Substrat **25** versenkt, wie bei einem Ausführungsbeispiel in **Fig. 2** gezeigt. Insbesondere trifft das Freigabegate **16** auf einen leitenden Ppropfen **22**, der in einem Graben im P-Substrat **25** ausgebildet ist. Ein Gateoxid **27** trennt den Ppropfen **22** vom Substrat **25**, um zu ermöglichen, dass der Thyristor **20** tor gesteuert wird. Wie am Strichlinienpfeil zu sehen ist, ist der Thyristor **20** nicht planar, sondern ist statt dessen vertikal um den Graben in der Form eines "U" ausgebildet. Diese nicht-planare Konfiguration verringert weiter die Menge an Fläche, die die Zelle **10** auf dem Substrat **25** belegt.

**[0024]** Vor dem Erörtern der verschiedenen alternativen Formen, die die Zelle **10** auf der Basis eines versenkten Thyristors annehmen kann, und vor dem

Erörtern der verschiedenen Weisen, auf die die Zelle hergestellt werden kann, wird die Funktionsweise der Zelle kurz mit Bezug auf **Fig. 3** bis **Fig. 5** erörtert. **Fig. 3** zeigt das Prinzip, auf dem die Zelle **10** auf Thyristorbasis arbeitet, mit Bezug auf eine Strom-Spannungs-Kurve. Da dieses Prinzip gut bekannt ist, wird es nur kurz erörtert. Wenn die Spannung über dem Thyristor ( $V_{thy}$ ) eine bestimmte Schwelle ( $V_{block}$ ) überschreitet, werden, wie gezeigt, Minoritätsladungsträger in die Basis (d.h. das Substrat **25**) des Thyristors injiziert und der Thyristor tritt in eine Periode eines negativen differentiellen Widerstandes ein, nach der die Spannung  $V_{thy}$  fällt und der Strom durch den Thyristor ( $I_{thy}$ ) scharf ansteigt. Wenn  $V_{thy}$   $V_{block}$  übersteigt, kann folglich behauptet werden, dass die Zelle auf einen logischen "1"-Zustand programmiert ist und einen merklichen Strom entnimmt. Wenn  $V_{thy}$   $V_{block}$  nicht übersteigt, dann wird der Thyristor nicht ausgelöst und der Strom bleibt relativ niedrig, d.h. ein logischer "0"-Zustand.

**[0025]** Sobald die Spannungen von dem Bauelement entfernt sind, behält die Zelle **10** ihre Ladung für einen kurzen Zeitraum, vielleicht in der Größenordnung von Millisekunden. Dies geschieht aufgrund des Verarmungsbereichs, der sich an den PN-Übergängen der Zelle bildet. Wenn sie über Ladungsinjektion programmiert wird, werden folglich die PN-Übergänge aufgrund der gespeicherten injizierten Minoritätsladung in eine Sperrspannung gebracht, was die Verarmungsbereiche und ihre Kapazität betont. Diese Verarmungsbereichskapazität speichert die injizierte Minoritätsladung, zumindest bis diese Minoritätsladungsträger sich im Substrat **25** rekombinieren. Aufgrund von solchen Rekombinationseffekten kann der Thyristor, wenn er als Zelle verwendet wird, nicht im Gegensatz zu einer Standard-DRAM-Zelle aufgefrischt werden müssen.

**[0026]** In jedem Fall kann nach einer solchen Programmierung eine Betriebsspannung ( $V_{op}$ ) an den Thyristor angelegt und sein Strom überwacht werden, um festzustellen, ob die Zelle auf einen logischen "1"- (hoher Strom) oder einen logischen "0"- (niedriger Strom) Zustand programmiert worden war. Wie ein Fachmann erkennen wird, wird dieses Verhalten des Thyristors **20**, d.h. seine Strom/Spannungs-Kennlinie, selbst beim Anlegen einer kleinen Gatespannung ( $V_{gate}$ ), wie z.B. an das Freigabegate **16**, aufrechterhalten. Da eine positivere Gatespannung zusätzliche Minoritätsladungsträger im P-Substrat **25** bereitstellt, werden folglich die zum Programmieren ( $V_{block}$ ) und Lesen ( $V_{op}$ ) erforderlichen Spannungen mit zunehmender Gatespannung verringert.

**[0027]** **Fig. 4** zeigt, wie die offenbarten Zellen **10** in einer Speichermatrix **50** angeordnet sein können, während **Fig. 5** die verschiedenen Spannungen darstellt, die verwendet werden können, um eine logische "1" oder "0" zu schreiben, um die Zelle zu le-

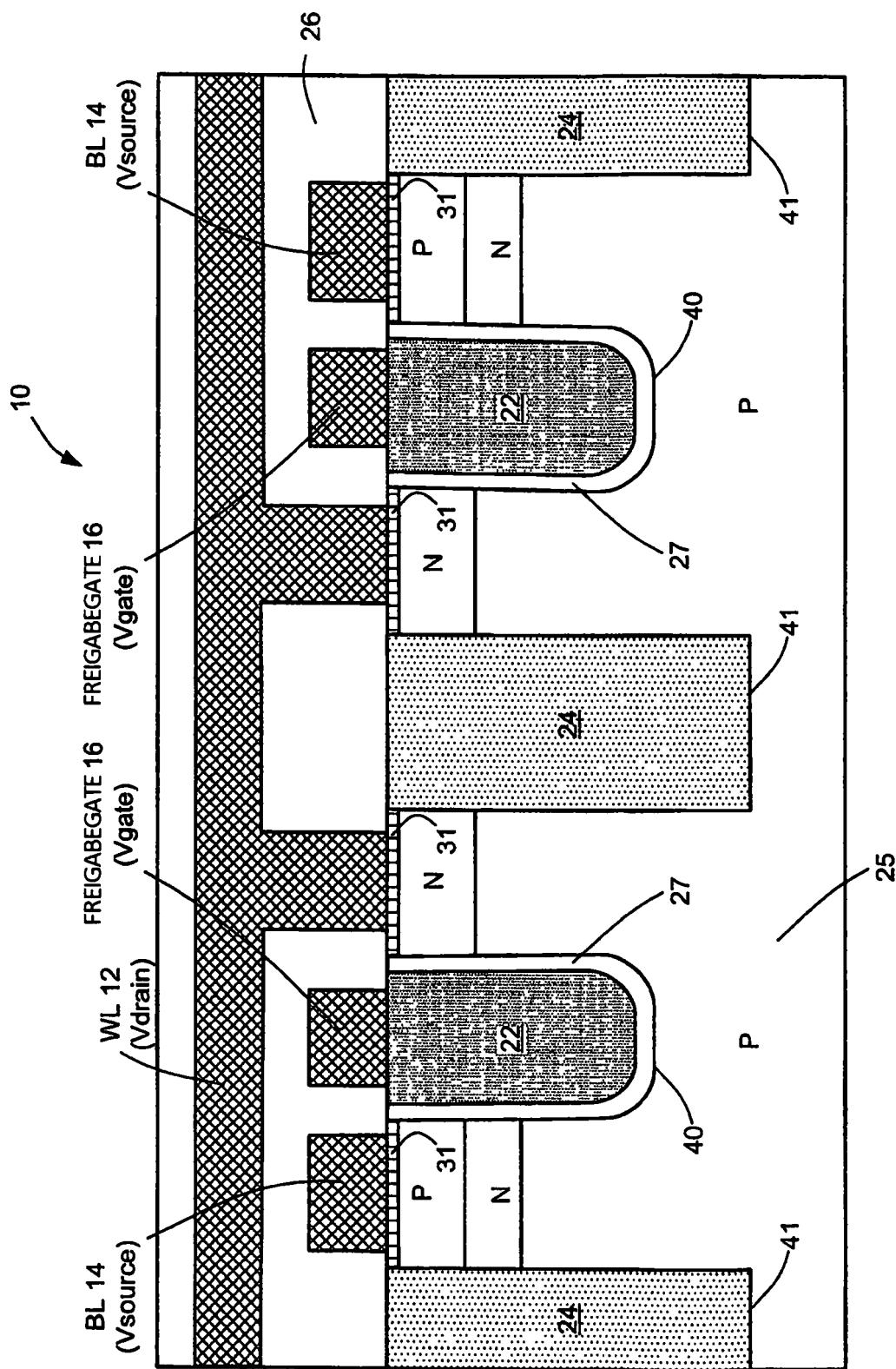

sen und um Daten in der Zelle zu halten. Die Matrix **50** umfasst bei einem Ausführungsbeispiel Bitleitungen **14**, die senkrecht zu den Freigabegates **16** und den Wortleitungen **12** verlaufen, aber dies ist nur willkürlich. Außerdem werden an der Kante der Matrix und wie es in Speicherbauelementen typisch ist, Treiber **30**, **32** und **34** verwendet, um die Bitleitungen, die Freigabegates und die Wortleitungen mit jeweils gewünschten Spannungen anzusteuern. Außerdem umfasst der Bitleitungstreiber **30** einen Leseverstärker, der aktiv ist, wenn der Strom/die Spannung auf einer aktiven Bitleitung erfasst wird. Solche Ansteuer- und Leseschaltungen sind auf dem Fachgebiet des Speicherchipdesigns gut bekannt und könnten eine beliebige Anzahl von geeigneten Schaltungen umfassen.

**[0028]** **Fig. 5** stellt beispielhafte Spannungen dar, die verwendet werden können, um die programmierten Daten in den Zellen **10** zu schreiben, zu lesen und zu halten, und umfassen folglich die Spannungen, die die Treiber **30**, **32**, **34** unter der Steuerung einer geeigneten und typischen Steuerschaltung (nicht dargestellt) erzeugen. Wie zu sehen ist, wird, wenn in die Zelle geschrieben wird, das Freigabegate **16** vorzugsweise auf Masse gehalten, wird jedoch ansonsten auf einem negativen Potential (z.B. -1,0 V), eine Akkumulationsbedingung im P-Kanalteil des Thyristors **20**, gehalten. Wenn das Freigabegate während des Schreibens geerdet wird, tendiert der P-Kanalsbereich im Thyristor **20** zur Inversion mit der Möglichkeit, dass  $V_{block}$  überschritten werden kann oder nicht (siehe **Fig. 3**). Ob  $V_{block}$  überschritten wird, hängt von der Bitleitungsspannung an der Anode relativ zur geerdeten Wortleitungsspannung an der Kathode ab; wenn die Bitleitungsspannung auch geerdet wird, wird  $V_{block}$  nicht überschritten und ein logischer "0"-Zustand wird geschrieben; wenn die Bitleitungsspannung hoch ist, z.B.  $V_{cc} = 1,5$  V, wird  $V_{block}$  überschritten und der Thyristor **20** steuert durch (d.h. speichert), um einen logischen "1"-Zustand zu schreiben. Sobald er geschrieben ist, kann der Logikzustand in der Zelle **10** durch Abtasten des Stroms/der Spannung auf der Bitleitung **14** gelesen werden. Das Lesen kann mit dem Freigabegate **16** auf dem negativen Potential (z.B. -1,0 V) und mit der geerdeten Wortleitung geschehen. Eine logische "0", bei der die Zelle nicht aufgeladen wurde, stört nicht die Bitleitungsspannung und folglich erkennen die Bitleitung-Leseverstärker die Zelle als logische "0". Wenn dagegen eine logische "1" gelesen wird, bewirkt die gespeicherte Ladung, dass die Bitleitungsspannung schwankt, was die Leseverstärker **30** als logische "1" erfassen. Während Perioden, in denen in die Zellen **10** weder geschrieben wird noch diese gelesen werden, können die Daten in den Zellen durch Halten der Wortleitungen und Bitleitungen auf  $V_{cc}$  (z.B. 1,5 V) gehalten werden.

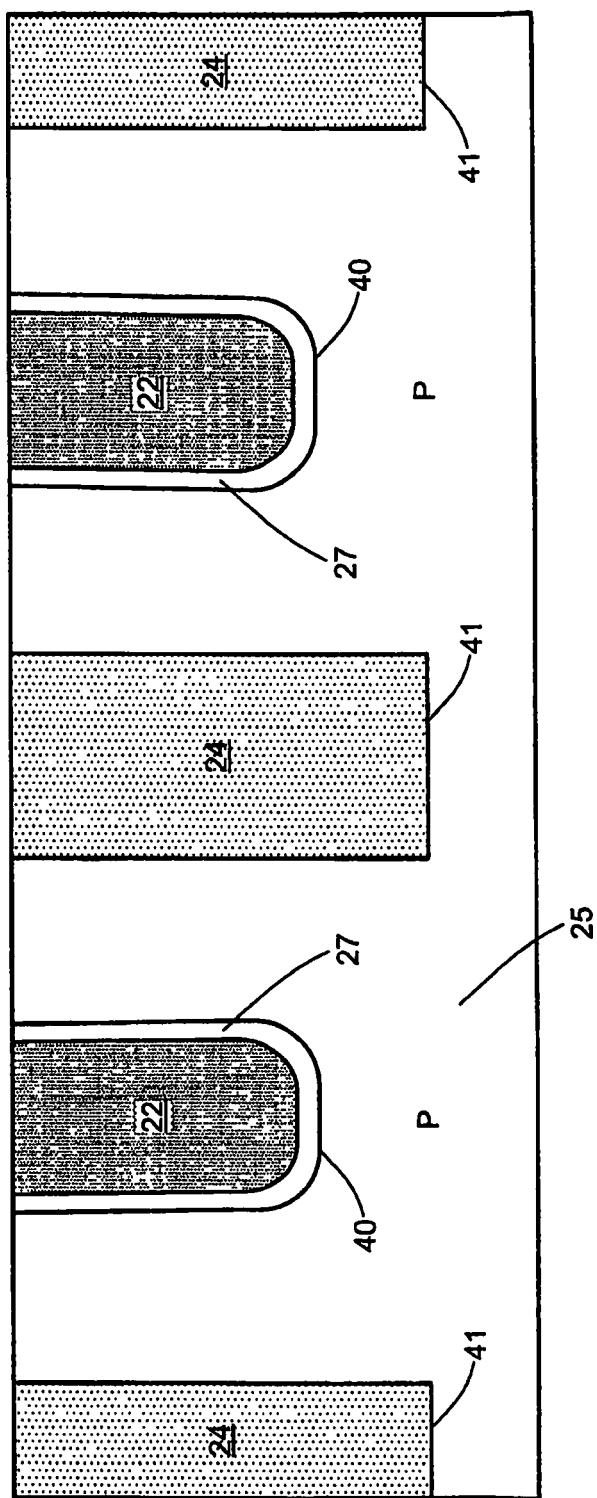

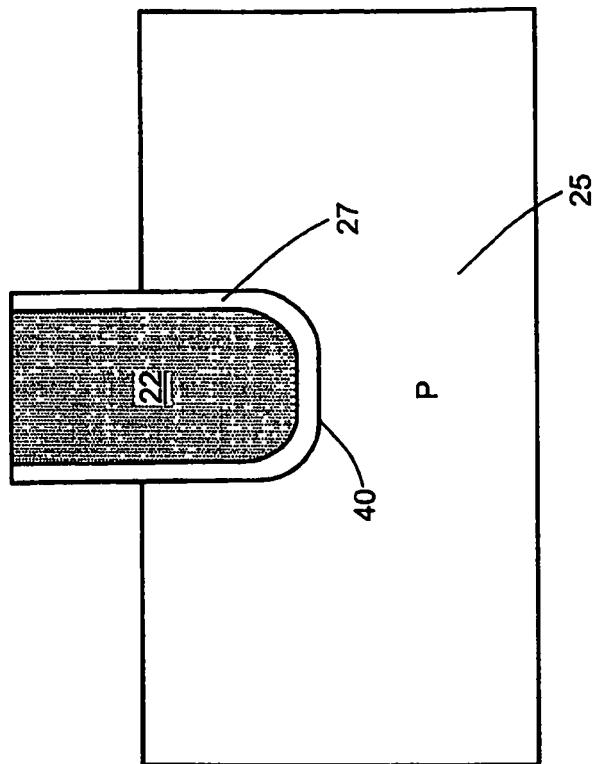

**[0029]** Nachdem die Funktionsweise und Architektur der offenbarten Zelle **10** auf der Basis eines versenkten Thyristors verstanden wurde, wendet sich die Aufmerksamkeit den Themen zu, wie die Zellen **10** auf der Basis eines versenkten Thyristors hergestellt werden können, beginnend mit einem ersten Ausführungsbeispiel, das in den **Fig. 6A–Fig. 6D** gezeigt ist. **Fig. 6A** zeigt zwei benachbarte Zellen **10** im Querschnitt in einer Zwischenstufe der Herstellung. In dieser Stufe wurden verschiedene Standardbearbeitungsschritte durchgeführt und werden daher nur kurz zusammengefasst. Zuerst wurde ein Graben **40** in das P-Substrat **25** geätzt. Nach dem Wachstum oder der Abscheidung eines Gateoxids **27** wird Material für den leitenden Ppropfen **22** abgeschieden, der wie vorstehend angegeben, schließlich mit dem Freigabegate **16** verbunden wird. Bei einem bevorzugten Ausführungsbeispiel kann der leitende Ppropfen **22** dotiertes Polysilizium umfassen, könnte jedoch andere leitende Materialien umfassen, die auch für Substratppropfen verwendet werden, wie z.B. Wolfram, Titan, Silizide, Salizide usw. Nach der Abscheidung des Materials des leitenden Ppropfens **22** kann die Oberfläche des Substrats **25** planarisierter werden, wie z.B. durch chemisch-mechanische Planarisierung (CMP) oder andere bekannte Planarisierungsverfahren.

**[0030]** In einem weiteren Prozessschritt werden Grabenisolationsstrukturen **24** um jede Zelle ausgebildet, um ein Nebensprechen zwischen benachbarten Zellen zu verhindern. Wie gut bekannt ist, umfasst die Ausbildung einer Grabenisolation das Ausbilden eines Grabens **41** im Silizium, das Füllen des Grabens mit einem Dielektrikum (z.B. einem Oxid oder Nitrid) und das Planarisieren der resultierenden Struktur. Wie ein Fachmann erkennen wird, kann die Ausbildung der Grabenisolationsstrukturen **24** auch der Ausbildung des versenkten leitenden Ppropfens **22** vorangehen oder kann teilweise mit der Ausbildung des Ppropfens gleichzeitig erfolgen, beispielsweise indem die Ppropfengräben **40** und Isolationsgräben **41** gleichzeitig ausgebildet werden. In jedem Fall können die bisher offenbarten Herstellungsstufen auf viele verschiedene Weisen unter Verwendung von gut bekannten Prozessen stattfinden.

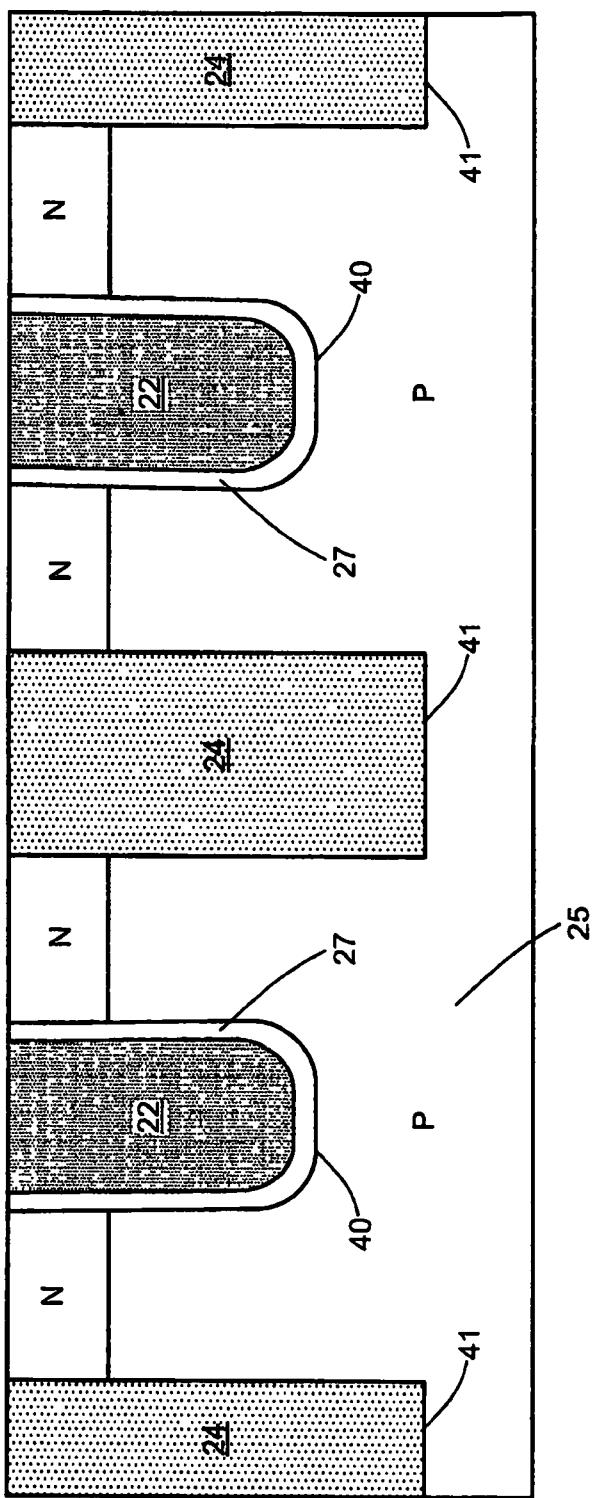

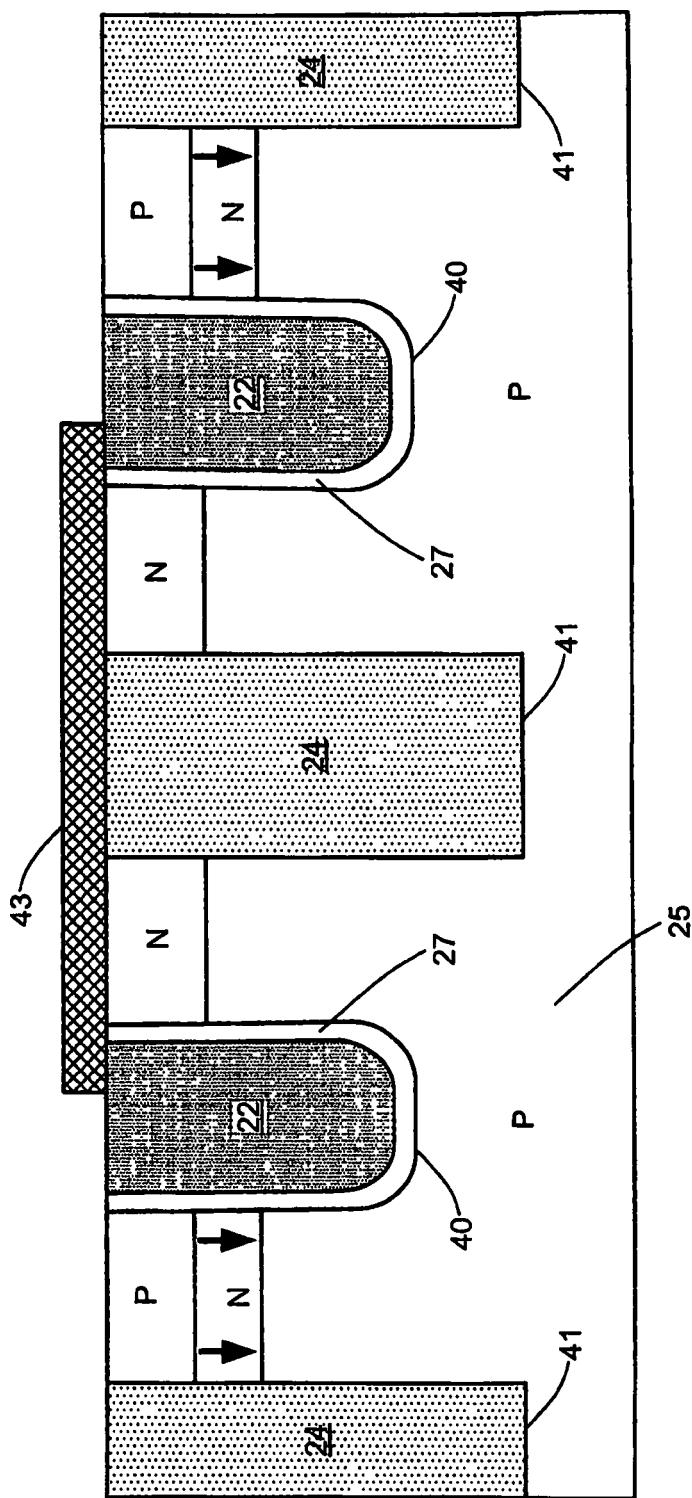

**[0031]** Als nächstes und wie in **Fig. 6B** gezeigt, werden die N-Bereiche des Thyristors **20** ausgebildet. Das Ausbilden solcher Bereiche kann eine unstrukturierte Ionenimplantation eines geeigneten Dotierungsmaterials vom N-Typ (z.B. Phosphor oder Arsen) in der Matrix umfassen. Wie ein Fachmann erkennen wird, beeinflusst die Implantation in den leitenden Ppropfen **22** und die Isolationsstrukturen **24** diese Strukturen nicht.

**[0032]** Danach wird eine harte Maske **43** abgeschieden, strukturiert (z.B. mit Photoresist; nicht gezeigt), und geätzt, um die Kathoden-(d.h. Bitleitungs-)Tei-

le des Thyristors **20** zu bedecken. Die harte Maske **43** kann ein beliebiges Material umfassen, das als Ionenimplantationsmaske geeignet ist, wie z.B. Nitrid. Die Ausrichtung der harten Maske **43** wird durch die seitlichen Abmessungen der Oberseite des leitenden Ppropfens **22** erleichtert und daher kann dieser Maskierungsschritt ohne enge Toleranz durchgeführt werden.

**[0033]** Nach der Ausbildung der harten Maske **43** wird ein weiterer Ionenimplantationsschritt durchgeführt, um die P-Anoden (d.h. Bitleitungen) des Baulements auszubilden. Wie in **Fig. 6C** gezeigt, können nach der Ausbildung der harten Maske **43** die P-Bereiche unter Verwendung einer unstrukturierten Ionenimplantation eines geeigneten Dotierungsmaterials vom P-Typ (z.B. Bor) in der Matrix ausgebildet werden, wobei die harte Maske die N-Bereiche an den Kathoden schützt. Die P-Dotierung geschieht bei diesem Beispiel in einem vorher dotierten N-Bereich. Wie durch die Pfeile in **Fig. 6C** dargestellt, werden jedoch die N-Bereiche unter den neu implantierten P-Bereichen durch den "Emitterschubeffekt", der gut bekannt ist und daher nicht weiter erörtert wird, nach unten in das Substrat getrieben. Wenn die N-Bereiche tief genug ausgebildet wurden, kann alternativ der neu implantierte P-Anodenbereich mit einer geringen Tiefe ohne Bedarf, sich auf den Emitterschubeffekt zu verlassen, implantiert werden.

**[0034]** Danach wird die harte Maske **43** entfernt und eine Standardbearbeitung kann verwendet werden, um die Freigabegates **16**, die Wortleitungen **12** und die Bitleitungen **14** in den dielektrischen Schichten **26** (z.B. Oxiden) auszubilden, wie in **Fig. 6D** gezeigt. Nach dem Entfernen der harten Maske **43** können jedoch die freigelegten Oberseiten der Anoden- und Kathodenbereiche des Thyristors **20** wahlweise mit Silizid **31** beschichtet werden, wie in **Fig. 6D** gezeigt. Eine solche Silizidbeschichtung **31** erzeugt eine Schottky-Barriere, d.h. eine Potentialbarriere, die an der Grenzfläche zwischen einem Metallsilizid und einem dotierten Halbleiterbereich erzeugt wird. Durch Abstimmen des Silizidbeschichtungsprozesses, z.B. über Temperatur, Materialien, Phasentransformationsbedingungen usw., kann die elektrische Leistung dieser Barriere angepasst werden. Da die in den Sourcepol und den Drainpol injizierte Ladung von dieser Potentialbarriere abhängt, bietet die Silizidbeschichtung zusätzliche Optionen beim Entwurf der Thyristoreigenschaften.

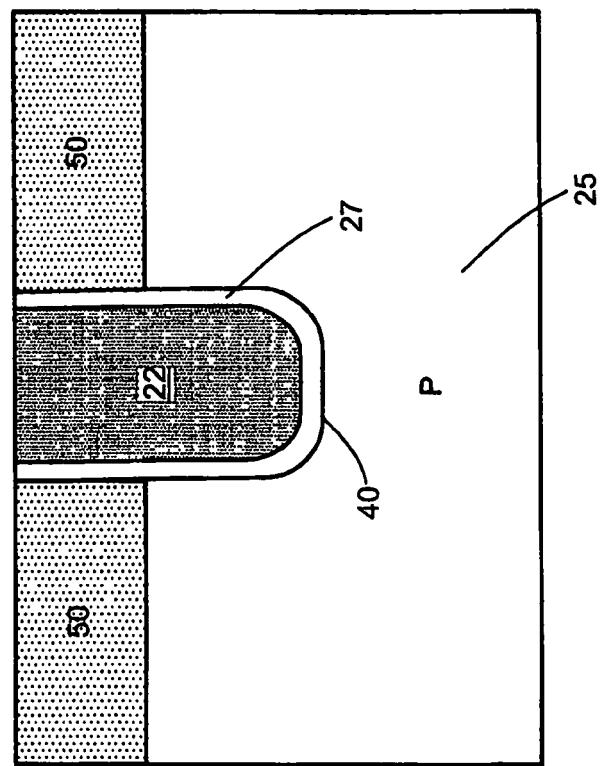

**[0035]** Weitere Ausführungsbeispiele für die Struktur und Herstellung der Zelle **10** auf der Basis eines versenkten Thyristors sind möglich und einige sind in anschließenden Figuren dargestellt. Zuerst offenbaren die **Fig. 7A–Fig. 7C** einen Prozess zur Herstellung der versenkten Zelle **10**, bei dem der Thyristor teilweise unter Verwendung von epitaxial aufgewachsenem Silizium ausgebildet wird. Beginnend mit

**Fig. 7A** wird ein Auflagematerial **50** wie z.B. ein Nitrid auf der Oberfläche des Substrats **25** abgeschieden. Danach wird ein Graben **40** durch die Auflage **50** und das Substrat ausgebildet. Der Graben kann dann mit einem Gateoxid **27** und einem leitenden Ppropfen **22** gefüllt werden, wie vorher beschrieben. Danach wird in **Fig. 7B** die Auflage **50** entfernt. An diesem Punkt werden die N-Bereiche des Thyristors **20** auf der Oberfläche des Substrats **25** ausgebildet, wie in **Fig. 7C** gezeigt. Dies könnte durch Ionenimplantation durchgeführt werden oder die N-Bereiche könnten epitaxial gezüchtet werden. Nach der Ausbildung der N-Bereiche wird eine harte Maske **52** über den Kathoden-(d.h. Bitleitungs-)Teilen des Thyristors **20** ausgebildet. Dies ermöglicht, dass die P-Anode (d.h. Wortleitung) auf dem freigelegten N-Bereich epitaxial gezüchtet wird, an welchem Punkt der Thyristor **20** vollständig ausgebildet ist. Danach wird die harte Maske **52** entfernt und die Bearbeitung fährt fort, um die Wortleitungen, die Freigabegates und die Bitleitungen auszubilden, wie vorstehend erörtert. Ein Fachmann wird erkennen, dass geeignete Epitaxialwachstumsprozesse auf dem Fachgebiet gut bekannt sind, und werden daher nicht weiter erörtert.

**[0036]** Wie vorher angegeben, kann die Isolation unter der Zelle **10** auf der Basis eines versenkten Thyristors ihre Leistung verbessern und kann insbesondere ihren Datenerhalt verbessern und die zwischen Auffrischungen erforderliche Zeit verlängern. Folglich offenbaren nachfolgende Ausführungsbeispiele Arten und Weisen, auf die eine solche Isolation bewirkt werden kann. In **Fig. 8A** wird beispielsweise die P-dotierte Basis des Thyristors (**25**) innerhalb eines N-Substrats **62** ausgebildet. Bei diesem Ausführungsbeispiel ist es bevorzugt, dass das N-Substrat **62** auf eine hohe Spannung (z.B. auf die Leistungsversorgungsspannung  $V_{CC}$ ) vorgespannt wird, um sicherzustellen, dass die zwischen der Thyristorbasis **25** und dem N-Substrat **62** gebildete Diode nicht in Durchlassrichtung vorgespannt und daher isoliert wird. Ein Fachmann wird verstehen, dass ein Kontakt mit dem N-Substrat **62** verwendet werden kann, um die geeignete Vorspannung vorzusehen, obwohl im Querschnitt nicht gezeigt. Bei einem weiteren Ausführungsbeispiel, das in **Fig. 8B** gezeigt ist, wird ein P-Substrat **66** verwendet, aber eine Isolation wird unterhalb der Basis ausgebildet, indem eine N-Potentialmulde **64** ausgebildet wird, und innerhalb dieser Potentialmulde **64** die P-Basis **25** ausgebildet wird. Wiederum würde die N-Potentialmulde **64** vorzugsweise auf eine hohe Spannung vorgespannt werden, um eine Isolation in Bezug auf das P-Substrat **66** (typischerweise geerdet) und die P-Basis **25** des Thyristors **20** vorzusehen, obwohl wieder der Kontakt zur Herstellung einer solchen Vorspannung nicht gezeigt ist.

**[0037]** Ein weiteres Mittel für eine verbesserte Isolation des Thyristors ist in **Fig. 9** gezeigt, in der die

Zelle **10** unter Verwendung einer vergrubenen Oxidschicht (Box **70**) ausgebildet wird. Obwohl es nicht erforderlich ist, ist es bevorzugt, dass die Box-Schicht **70** reich an einem P-Dotierungsmaterial wie z.B. Bor ist, so dass P-Dotierungsmaterialien von der Basis **25** nicht in die Box-Schicht **70** diffundieren und sich auf die Leistung des Thyristors **20** negativ auswirken können. Ein Fachmann wird erkennen, dass viele Verfahren auf dem Fachgebiet zum Ausbilden eines Ausgangssubstrats **25** mit einer Box-Schicht **70** existieren, und daher wird dies nicht weiter erörtert. Außerdem sollte es verständlich sein, dass die Box-Schicht **70** zur Verwendung des Masseisolators eines SOI-(Silizium auf Isolator)Substrats ähnlich ist, das eine ähnliche Leistung zu dem in **Fig. 9** gezeigten Ausführungsbeispiel hätte, und das noch ein weiteres Ausführungsbeispiel der offenbarten Zelle bildet.

**[0038]** **Fig. 10** stellt ein weiteres Ausführungsbeispiel der Zelle **10** auf der Basis eines versenkten Thyristors mit einer verbesserten Isolation unter der Zelle dar. Bei diesem Ausführungsbeispiel umfassen die Isolationsstrukturen **75** Unterätzungen **76**, die, wie ihr Name andeutet, den Thyristor **20** in einem signifikant Teil unterätzen und bei seiner Isolation unterstützen. Die Unterätzungen **76** können durch zuerst Erzeugen eines anisotropen Grabens (z.B. des Grabens **41** von **Fig. 6A**) und dann Unterziehen des Grabens einem Nassätzen, nachdem der Graben ausgebildet wurde, ausgebildet werden. Eine Nassätzlösung aus TMAH (Tetramethylammoniumhydroxid) kann beispielsweise verwendet werden, um die Unterätzung **76** auszubilden. Danach können der Graben und die Unterätzung **76** unter Verwendung eines Niederdruck-Oxiddampf-Abscheidungsprozesses gefüllt werden, wie gut bekannt ist, um die Unterätzungsisolationsstrukturen **75** auszubilden, wie in **Fig. 10** gezeigt.

**[0039]** Ungeachtet dessen, ob die Isolation unter dem Thyristor **20** verwendet wird, sollte erkannt werden, dass die Zelle **10** auf der Basis eines versenkten Thyristors zu einer Zellenkonstruktion führt, die kompakt, leicht herzustellen und leicht zu einer Matrix von Zellen ausgebildet werden kann. Folglich können die offenbarten Zellen verbesserte Zellendichten im Vergleich zu herkömmlichen DRAM-Zellen aufweisen. Insbesondere wird angenommen, dass die offenbarte Zelle **10** eine spezielle Eignung bei Anwendungen eines eingebetteten DRAM hätte, bei denen flüchtige Zellen (die eine Auffrischung erfordern) in ansonsten Standard-Halbleiterchips wie z.B. Mikroprozessoren oder Mikrocontroller integriert werden. Bei solchen Einbettungsanwendungen kann das Auffrischen mit einer größeren Häufigkeit stattfinden, und selbst wenn die offenbarte Zelle **10** eine häufigere Auffrischung als herkömmliche DRAM-Zellen erfordert sollte, würde folglich nicht erwartet werden, dass dies eine beträchtliche Konstruktionseinschränkung verursacht. Es sollte jedoch auch beachtet werden,

dass die offenbarte Zelle sich auch für herkömmliche nicht-eingebettete integrierte Schaltungen eignet.

**[0040]** Obwohl der Thyristor **20**, wie in der offebarten Zelle **10** verwendet, als PNPN-Struktur offebart ist, erkennt ein Fachmann, dass eine NPNP-Struktur ebenso verwendet werden könnte. Bei einer solchen Struktur bilden Elektronen anstelle von Löchern die Majoritätladungsträger, aber die Zelle arbeitet gleichermaßen gut unter der Annahme, dass die den Zellenknoten präsentierten Potentiale von entgegengesetzter Polarität sind. Die Fähigkeit, Thyristoren mit unterschiedlichen Polaritäten zu verwenden, stellt Konstruktionsflexibilität bereit, insbesondere wenn die Verwendung der offebarten Zelle **10** bei einer Anwendung mit Einbettung betrachtet wird.

**[0041]** Es sollte selbstverständlich sein, dass die Begriffe "Anode" und "Kathode" lediglich die Endknotenanschlüsse des Thyristors betreffen, und dass es folglich irrelevant ist, welche von diesen Anschlüssen tatsächlich Strom entnehmen oder liefern.

### Patentansprüche

1. Speicherzelle mit:

einem leitenden Ppropfen (**22**), der in einem Substrat (**25**) ausgebildet ist;

einem Thyristor (**20**), der in dem Substrat (**25**) angeordnet und vertikal um den leitenden Ppropfen (**22**) ausgebildet und vom leitenden Ppropfen (**22**) durch ein Dielektrikum (**27**) isoliert ist; und

einem Mittel (**62, 64, 70**) zum Isolieren der Zelle (**10**), das auf einer dem Substrat (**25**) zugewandten Seite des Thyristors (**20**) ausgebildet ist;

wobei ein erster Knoten des Thyristors (**20**) direkt mit einer Bitleitung (**14**) in einer Matrix (**50**) gekoppelt ist, wobei ein zweiter Knoten des Thyristors (**20**) direkt mit einer Wortleitung (**12**) in der Matrix (**50**) gekoppelt ist und wobei der leitende Ppropfen (**22**) direkt mit einem Freigabegate (**16**) in der Matrix (**50**) gekoppelt ist; und

wobei der erste Knoten und der zweite Knoten an einer Fläche des Substrats (**25**) angeordnet sind.

2. Speicherzelle nach Anspruch 1, welche ferner eine um die Zelle (**10**) ausgebildete Grabenisolierung (**24, 75**) aufweist.

3. Speicherzelle nach Anspruch 2, wobei das Mittel (**62, 64, 70**) eine Isolationsstruktur, die mit der Grabenisolierung (**24, 75**) in Kontakt ist, aufweist.

4. Speicherzelle nach Anspruch 3, wobei die Isolationsstruktur eine vergrabene Oxidschicht (**70**) aufweist.

5. Speicherzelle nach Anspruch 3, wobei die Isolationsstruktur einen massiven Isolator eines SOI-Substrats aufweist.

6. Speicherzelle nach Anspruch 3, wobei die Isolationsstruktur eine in Sperrrichtung vorgespannte Diode aufweist.

7. Speicherzelle nach Anspruch 3, wobei die Isolationsstruktur dielektrische Unterätzungen (**76**) aufweist.

8. Speicherzelle mit:

einem leitenden Ppropfen (**22**), der in einem Substrat (**25**) ausgebildet ist;

einem Thyristor (**20**), der im Substrat (**25**) angeordnet und um den leitenden Ppropfen (**22**) in einer U-Form ausgebildet ist; und

einem Mittel (**62, 64, 70**) zum Isolieren der Zelle (**10**), das auf einer dem Substrat (**25**) zugewandten Seite des Thyristors (**20**) ausgebildet ist;

wobei ein erster Knoten des Thyristors (**20**) direkt mit einer Bitleitung (**14**) in einer Matrix (**50**) gekoppelt ist, wobei ein zweiter Knoten des Thyristors (**20**) direkt mit einer Wortleitung (**12**) in der Matrix (**50**) gekoppelt ist und wobei der leitende Ppropfen (**22**) direkt mit einem Freigabegate (**16**) in der Matrix (**50**) gekoppelt ist.

9. Speicherzelle nach Anspruch 8, welche ferner eine Grabenisolierung (**24, 75**) aufweist, die um die Zelle (**10**) ausgebildet ist.

10. Speicherzelle nach Anspruch 9, wobei das Mittel (**62, 64, 70**) eine Isolationsstruktur, die mit der Grabenisolierung (**24, 75**) in Kontakt ist, aufweist.

11. Speicherzelle nach Anspruch 10, wobei die Isolationsstruktur eine vergrabene Oxidschicht (**70**) aufweist.

12. Speicherzelle nach Anspruch 10, wobei die Isolationsstruktur den massiven Isolator eines SOI-Substrats aufweist.

13. Speicherzelle nach Anspruch 10, wobei die Isolationsstruktur eine in Sperrrichtung vorgespannte Diode aufweist.

14. Speicherzelle nach Anspruch 10, wobei die Isolationsstruktur dielektrische Unterätzungen (**76**) aufweist.

15. Speicherzelle mit:

einem leitenden Ppropfen (**22**), der in einem Graben (**40**) in einem Substrat (**25**) ausgebildet ist, das auf einer ersten Polarität dotiert ist, wobei der leitende Ppropfen (**22**) vom Substrat (**25**) durch eine dielektrische Schicht (**27**) isoliert ist;

einem Thyristor (**20**) mit:

dem Substrat (**25**);

ersten dotierten Bereichen (N) entlang der gegenüberliegenden Seiten des Grabens (**40**), wobei die ersten dotierten Bereiche (N) mit einer zur ersten

Polarität entgegengesetzten zweiten Polarität dotiert sind; und einem zweiten dotierten Bereich (P) entlang nur einer Seite des Grabens (40), wobei der zweite dotierte Bereich (P) über einem der ersten dotierten Bereiche (N) liegt und auf die erste Polarität dotiert ist; und einem Mittel (62, 64, 70) zum Isolieren der Zelle (10), das auf einer dem Substrat (25) zugewandten Seite des Thyristors (20) ausgebildet ist; wobei der erste dotierte Bereich (N) an der dem zweiten dotierten Bereich (P) gegenüberliegenden Seite des Grabens (40) direkt mit einer Wortleitung (12) in einer Matrix (50) gekoppelt ist, wobei der zweite dotierte Bereich (P) direkt mit einer Bitleitung (14) in der Matrix (50) gekoppelt ist und wobei der leitende Ppropfen (22) direkt mit einem Freigabegate (16) in der Matrix (50) gekoppelt ist.

16. Speicherzelle nach Anspruch 15, welche ferner eine um die Zelle (10) ausgebildete Grabenisolierung (24, 75) aufweist.

17. Speicherzelle nach Anspruch 16, wobei das Mittel (62, 64, 70) eine Isolationsstruktur, die mit der Grabenisolierung (24, 75) in Kontakt ist, aufweist.

18. Speicherzelle nach Anspruch 17, wobei die Isolationsstruktur eine vergrabene Oxidschicht (70) aufweist.

19. Speicherzelle nach Anspruch 17, wobei die Isolationsstruktur den massiven Isolator eines SOI-Substrats aufweist.

20. Speicherzelle nach Anspruch 17, wobei die Isolationsstruktur eine in Sperrrichtung vorgespannte Diode aufweist.

21. Speicherzelle nach Anspruch 17, wobei die Isolationsstruktur dielektrische Unterätzungen (76) aufweist.

22. Verfahren zum Ausbilden einer Speicherzelle (10), das in keiner speziellen Reihenfolge aufweist: Ausbilden eines Grabens (40) in einem Substrat (25), das auf eine erste Polarität dotiert ist; Ausbilden eines leitenden Ppropfens (22) in dem Graben (40) mit Seiten, wobei der leitende Ppropfen (22) vom Substrat (25) durch ein Dielektrikum (27) isoliert ist; Ausbilden von ersten dotierten Bereichen (N) entlang der gegenüberliegenden Seiten des Grabens (40), wobei die ersten dotierten Bereiche (N) mit einer zur ersten Polarität entgegengesetzten zweiten Polarität dotiert sind; Ausbilden eines zweiten dotierten Bereichs (P) entlang nur einer Seite des Grabens (40), wobei der zweite dotierte Bereich (P) über einem der ersten dotierten Bereiche liegt (N); und

Ausbilden auf einer dem Substrat (25) zugewandten Seite des Thyristors (20) eines Mittels (62, 64, 70) zum Isolieren der Zelle (10).

23. Verfahren nach Anspruch 22, wobei einer der ersten dotierten Bereiche (N) direkt mit einer Bitleitung (14) in einer Matrix (50) gekoppelt ist, wobei der zweite dotierte Bereich (P) direkt mit einer Wortleitung (12) in der Matrix (50) gekoppelt ist und wobei der leitende Ppropfen (22) direkt mit einem Freigabegate (16) in der Matrix (50) gekoppelt ist.

24. Verfahren nach Anspruch 22, welches ferner das Ausbilden einer Grabenisolierung (27, 75) um die Zelle (10) aufweist.

25. Verfahren nach Anspruch 24, wobei das Mittel (62, 64, 70) eine Isolationsstruktur, die mit der Grabenisolierung (24, 75) in Kontakt ist, aufweist.

26. Verfahren nach Anspruch 22, wobei mindestens einer der ersten Bereiche (N) oder des zweiten Bereichs (P) durch einen Epitaxialprozess ausgebildet wird.

27. Speicherzellenmatrix mit: einer Matrix (50) von Speicherzellen (10), wobei jede der Speicherzellen eine Speicherzelle gemäß Anspruch 1 aufweist; mindestens einem Freigabegate (16), das mit den leitenden Ppropfen (22) einer Vielzahl der Speicherzellen (10) entlang einer ersten Leitung gekoppelt ist; mindestens einer Bitleitung (14), die mit den ersten Knoten einer Vielzahl der Speicherzellen (10) entlang einer zweiten Leitung gekoppelt ist; und mindestens einer Wortleitung (12), die mit den zweiten Knoten einer Vielzahl der Speicherzellen (10) entlang einer dritten Leitung gekoppelt ist.

28. Speicherzellenmatrix mit: einer Matrix (50) von Speicherzellen (10), wobei jede der Speicherzellen eine Speicherzelle gemäß Anspruch 8 aufweist; mindestens einem Freigabegate (16), das mit den leitenden Ppropfen (22) einer Vielzahl der Speicherzellen (10) entlang einer ersten Leitung gekoppelt ist; mindestens einer Bitleitung (14), die mit den ersten Knoten einer Vielzahl der Speicherzellen (10) entlang einer zweiten Leitung gekoppelt ist; und mindestens einer Wortleitung (12), die mit den zweiten Knoten einer Vielzahl der Speicherzellen (10) entlang einer dritten Leitung gekoppelt ist.

29. Speicherzellenmatrix mit: einer Matrix (50) von Speicherzellen (10), wobei jede der Speicherzellen eine Speicherzelle gemäß Anspruch 15 aufweist; mindestens einem Freigabegate (16), das mit den leitenden Ppropfen (22) einer Vielzahl der Speicherzellen (10) entlang einer ersten Leitung gekoppelt ist;

mindestens einer Bitleitung (**14**), die mit einem der gegenüberliegenden ersten dotierten Bereiche (N) einer Vielzahl der Speicherzellen (**10**) entlang einer zweiten Leitung gekoppelt ist; und

mindestens einer Wortleitung (**12**), die mit den zweiten dotierten Bereichen (P) einer Vielzahl der Speicherzellen (**10**) entlang einer dritten Leitung gekoppelt ist.

Es folgen 14 Seiten Zeichnungen

## Anhängende Zeichnungen

Figur 1

*Figur 2*

Figur 3

*Figur 4*

Figur 5

*Figur 6A*

Figur 6B

Figur 6C

Figur 6D

*Figur 7B*

*Figur 7A*

Figur 7C

Figur 8A

Figur 8B

Figur 9

Figur 10