(12)发明专利

(10)授权公告号 CN 107562033 B

(45)授权公告日 2019.05.31

(21)申请号 201710211884.9

(51)Int.CI.

(22)申请日 2017.04.01

G05B 23/02(2006.01)

(65)同一申请的已公布的文献号

申请公布号 CN 107562033 A

(56)对比文件

(43)申请公布日 2018.01.09

TW 230808 B,1994.09.21,

US 2006140114 A1,2006.06.29,

US 2009168800 A1,2009.07.02,

(30)优先权数据

审查员 刘锋

15/198,928 2016.06.30 US

(73)专利权人 赛普拉斯半导体公司

地址 美国加利福尼亚州

(72)发明人 干满寿夫 富田和弘

(74)专利代理机构 北京安信方达知识产权代理

有限公司 11262

代理人 张瑞 郑霞

权利要求书3页 说明书11页 附图15页

(54)发明名称

用于通信的收发器以及用于控制通信的方法

(57)摘要

本发明公开了一种用于通信的收发器以及用于控制通信的方法。用于通信的收发器包括：定时确定器，该定时确定器检测通过时钟信号的脉宽调制生成的且从通信总线输入的总线信号从高电平到低电平的下降；发送数据信号延迟调节器，该发送数据信号延迟调节器确定与第一定时具有预定时间差的第二定时，该总线信号在第一定时处从低电平向高电平上升；编码器，该编码器通过将输出到通信总线的数据信号从高电平变为低电平来延长总线信号的低电平；以及定时调节电路，该定时调节电路在第二定时处将数据信号改变为低电平。

1. 一种用于通信的收发器，包括：

定时确定器，所述定时确定器被配置为检测通过时钟信号的脉宽调制生成的且从通信总线输入的总线信号从高电平到低电平的下降；

发送数据信号延迟调节器，所述发送数据信号延迟调节器被配置为确定与第一定时具有预定时间差的第二定时，所述总线信号在所述第一定时处从所述低电平向所述高电平上升；

编码器，所述编码器被配置为通过将待输出到所述通信总线的数据信号从所述高电平变为所述低电平，延长所述总线信号的低电平；以及

定时调节电路，所述定时调节电路被配置为在所述第二定时将所述数据信号改变为所述低电平。

2. 如权利要求1所述的用于通信的收发器，其中，所述发送数据信号延迟调节器基于谐波水平被降低的频率和自然数来计算所述预定时间差。

3. 如权利要求1所述的用于通信的收发器，还包括：

时钟上升开始检测器，所述时钟上升开始检测器被配置为检测所述总线信号从所述低电平上升的开始；以及

时钟上升开始确定器，所述时钟上升开始确定器被配置为基于由所述时钟上升开始检测器检测到的所述总线信号的定时，确定所述第一定时。

4. 如权利要求1所述的用于通信的收发器，还包括：

第一比较器，所述第一比较器被配置为将所述总线信号的信号电平与第一参考电压进行比较；

第二比较器，所述第二比较器被配置为将所述信号电平与不同于所述第一参考电压的第二参考电压进行比较；以及

时钟上升开始确定器，所述时钟上升开始确定器被配置为基于来自所述第一比较器和所述第二比较器的比较结果，确定所述总线信号从所述低电平上升的开始的定时。

5. 如权利要求1所述的用于通信的收发器，其中，所述发送数据信号延迟调节器确定在所述总线信号的下降之后的所述第二定时。

6. 如权利要求5所述的用于通信的收发器，还包括：

第一比较器，所述第一比较器被配置为将所述总线信号的信号电平与第一参考电压进行比较；

第二比较器，所述第二比较器被配置为将所述信号电平与不同于所述第一参考电压的第二参考电压进行比较；以及

时钟下降终止确定器，所述时钟下降终止确定器被配置为基于来自所述第一比较器和所述第二比较器的比较结果，确定所述总线信号的下降的定时。

7. 如权利要求1所述的用于通信的收发器，其中，所述发送数据信号延迟调节器确定所述第二定时早于所述总线信号从所述低电平上升的开始的定时。

8. 如权利要求1所述的用于通信的收发器，其中，所述发送数据信号延迟调节器确定所述数据信号从所述低电平向所述高电平上升的开始的定时是在所述总线信号的所述下降的定时之后的预定时间长度。

9. 如权利要求1所述的用于通信的收发器，其中，所述收发器被包括在用于时钟扩展外

围接口 (CXPI) 通信中的节点中。

10. 如权利要求9所述的用于通信的收发器,其中,所述收发器用作通过所述通信总线与主节点收发器进行通信的从节点收发器。

11. 一种用于控制收发器通过通信总线进行的通信的方法,所述方法包括:

检测通过时钟信号的脉宽调制生成的且从所述通信总线输入的总线信号从高电平到低电平的下降;

确定与第一定时具有预定时间差的第二定时,所述总线信号在所述第一定时处从所述低电平向所述高电平上升;

通过将待输出到所述通信总线的数据信号从所述高电平变为所述低电平,延长所述总线信号的低电平;以及

在所述第二定时处将所述数据信号改变为所述低电平。

12. 如权利要求11所述的方法,其中,所述预定时间差是基于谐波水平被降低的频率和自然数来计算的。

13. 根据权利要求11所述的方法,还包括:

通过时钟上升开始检测器检测所述总线信号从所述低电平上升的开始;以及

基于由所述时钟上升开始检测器检测到的所述总线信号的定时,确定所述第一定时。

14. 根据权利要求11所述的方法,其中:

所述收发器包括第一比较器和第二比较器;

所述方法还包括:

所述第一比较器将所述总线信号的信号电平与第一参考电压进行比较;

所述第二比较器将所述信号电平与不同于所述第一参考电压的第二参考电压进行比较;以及

基于来自所述第一比较器和所述第二比较器的比较结果,确定所述总线信号从所述低电平上升的开始的定时。

15. 如权利要求11所述的方法,还包括确定所述第二定时在所述总线信号的所述下降之后。

16. 根据权利要求15所述的方法,其中:

所述收发器包括第一比较器和第二比较器;

所述方法还包括:

所述第一比较器将所述总线信号的信号电平与第一参考电压进行比较;

所述第二比较器将所述信号电平与不同于所述第一参考电压的第二参考电压进行比较;以及

基于来自所述第一比较器和所述第二比较器的比较结果,确定所述总线信号的所述下降的定时。

17. 如权利要求11所述的方法,还包括确定所述第二定时早于所述总线信号从所述低电平上升的开始的定时。

18. 如权利要求11所述的方法,还包括确定所述数据信号从所述低电平向所述高电平上升的开始的定时是在所述总线信号的所述下降的定时之后的预定时间长度。

19. 如权利要求11所述的方法,其中,所述收发器被包括在用于时钟扩展外围接口

(CXPI) 通信中的节点中。

20. 如权利要求19所述的方法,其中,所述收发器用作通过所述通信总线与主节点收发器进行通信的从节点收发器。

## 用于通信的收发器以及用于控制通信的方法

### 技术领域

- [0001] 本公开涉及用于通信的收发器以及用于控制通信的方法。

- [0002] 背景

- [0003] 在设置有多个电子可控设备的装置中,在独立控制设备的处理器之间执行通信。例如,诸如汽车的车辆设置有空调、后视镜、电动窗、雨刷以及其他电子可控设备。电子控制这些设备的多个电子控制单元(ECU)安装在车辆中。这些ECU通过总线相互连接,并且根据预定通信协议进行通信。

- [0004] 在ECU之间进行通信的期间,通过在连接ECU的总线中的接线可以发出噪声。发出的噪声根据频带可能影响其他设备。

- [0005] 概述

- [0006] 因此,提供可以降低噪声的影响的用于通信的收发器以及用于控制通信的方法将会是有益的。

- [0007] 为了这个目的,根据本公开的一个方面的用于通信的收发器包括:定时确定器,该定时确定器被配置为检测通过时钟信号的脉宽调制生成的且从通信总线输入的总线信号从高电平到低电平的下降;发送数据信号延迟调节器,该发送数据信号延迟调节器被配置为确定与第一定时具有预定时间差的第二定时,该总线信号在第一定时处从低电平向高电平上升;编码器,该编码器被配置为通过将待输出到通信总线的数据信号从高电平变为低电平来延长总线信号的低电平;以及定时调节电路,该定时调节电路被配置为在第二定时处将数据信号改变为低电平。

- [0008] 在以上的方面中,发送数据信号延迟调节器可以利用以下方程式(1)计算预定时间差:

- [0009]  $t_{\text{diff}} = (2n-1) / (2f_{\text{陷波}})$  (1)

- [0010] 其中,  $t_{\text{diff}}$  是预定时间差,  $f_{\text{陷波}}$  是谐波水平在其处被降低的频率,并且  $n$  是自然数。

- [0011] 以上的方面还可以包括时钟上升开始检测器,该时钟上升开始检测器被配置为检测总线信号从低电平上升的开始;以及时钟上升开始确定器,该时钟上升开始确定器被配置为基于由时钟上升开始检测器检测到的从低电平上升的开始的定时来确定第一定时。

- [0012] 以上的方面还可包括第一比较器,该第一比较器被配置为将总线信号的信号电平与第一参考电压进行比较;第二比较器,该第二比较器被配置为将信号电平与不同于第一参考电压的第二参考电压进行比较;以及时钟上升开始确定器,该时钟上升开始确定器被配置为基于来自第一比较器和第二比较器的比较结果,确定总线信号从低电平上升的开始的定时。

- [0013] 在以上的方面中,发送数据信号延迟调节器可以确定第二定时在总线信号的下降之后。

- [0014] 以上的方面还可包括第一比较器,该第一比较器被配置为将总线信号的信号电平与第一参考电压进行比较;第二比较器,该第二比较器被配置为将信号电平与不同于第一参考电压的第二参考电压进行比较;以及时钟下降终止确定器,该时钟下降终止确定器被

配置为基于来自第一比较器和第二比较器的比较结果,确定总线信号下降的定时。

[0015] 在以上的方面中,发送数据信号延迟调节器可确定第二定时早于总线信号从低电平上升的开始的定时。

[0016] 在以上的方面中,发送数据信号延迟调节器可确定数据信号从低电平向高电平上升的开始的定时是在总线信号下降的定时之后的预定时间长度。

[0017] 在以上的方面中,用于通信的收发器可被包括在用于时钟扩展外围接口通信中的节点中。

[0018] 在以上的方面中,用于通信的收发器可用作通过通信总线与主节点收发器进行通信的从节点收发器。

[0019] 根据本公开的另一个方面的方法是用于控制用于通信的收发器的通信的方法,该收发器通过通信总线进行通信,该方法包括:检测通过时钟信号的脉宽调制生成的且从通信总线输入的总线信号从高电平到低电平的下降;确定与第一定时具有预定时间差的第二定时,该总线信号在该第一定时处从低电平向高电平上升;通过将待输出到通信总线的数据信号从高电平变为低电平,延长总线信号的低电平;以及在该第二定时处将数据信号改变为低电平。

[0020] 在以上的方面中,预定时间差利用以下方程式(2)来计算:

$$t_{\text{diff}} = (2n-1) / (2f_{\text{台阶}}) \quad (2)$$

[0022] 其中,  $t_{\text{diff}}$  是预定时间差,  $f_{\text{台阶}}$  是谐波水平在其处被降低的频率,并且n是自然数。

[0023] 以上的方面还可以包括检测总线信号从低电平上升的开始;以及基于由时钟上升开始检测器检测到的从低电平上升的开始的定时,确定第一定时。

[0024] 在以上的方面中,用于通信的收发器可包括第一比较器和第二比较器;并且以上的方面还可包括第一比较器将总线信号的信号电平与第一参考电压进行比较;第二比较器将信号电平与不同于第一参考电压的第二参考电压进行比较;以及基于来自第一比较器和第二比较器的比较结果,确定总线信号从低电平上升的开始的定时。

[0025] 以上的方面还可包括确定第二定时在总线信号下降之后。

[0026] 在以上的方面中,用于通信的收发器可包括第一比较器和第二比较器;并且以上的方面还可包括第一比较器将总线信号的信号电平与第一参考电压进行比较;第二比较器将信号电平与不同于第一参考电压的第二参考电压进行比较;以及基于来自第一比较器和第二比较器的比较结果,确定总线信号下降的定时。

[0027] 以上的方面还可包括确定第二定时早于总线信号从低电平上升的开始的定时。

[0028] 以上的方面还可包括确定数据信号从低电平向高电平上升的开始的定时是在总线信号下降的定时之后的预定时间长度。

[0029] 在以上的方面中,用于通信的收发器可被包括在用于时钟扩展外围接口通信中的节点中。

[0030] 在以上的方面中,用于通信的收发器可用作通过通信总线与主节点收发器进行通信的从节点收发器。

[0031] 以下实施例的用于通信的收发器以及用于控制通信的方法可以降低噪声的影响。

[0032] 附图简述

[0033] 在附图中:

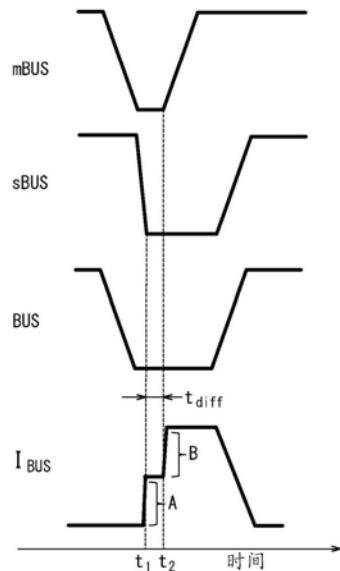

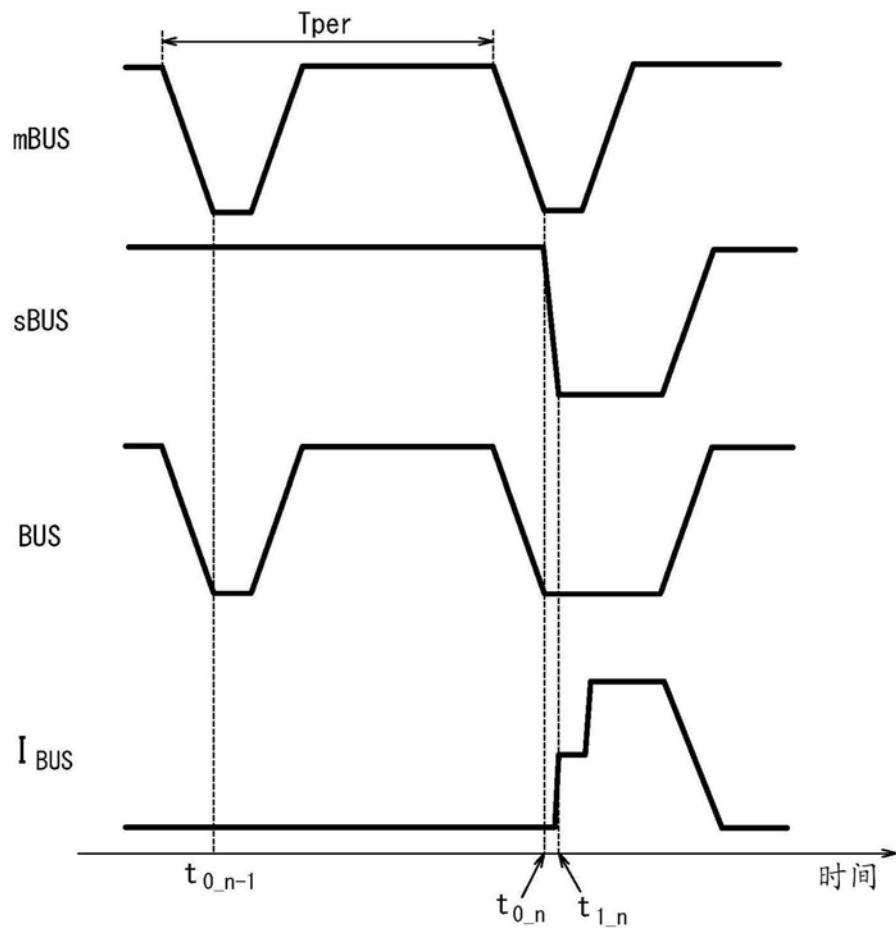

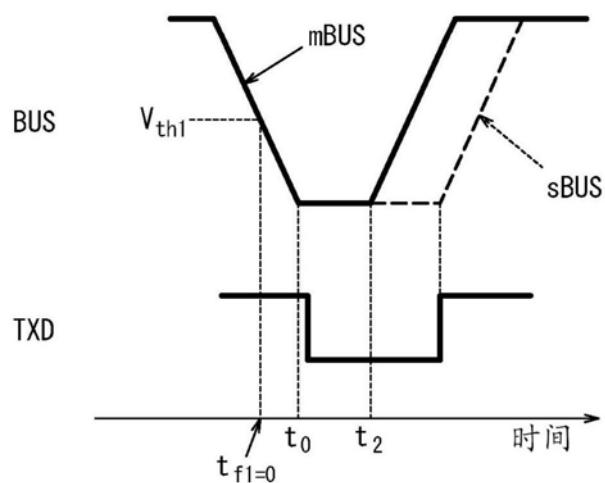

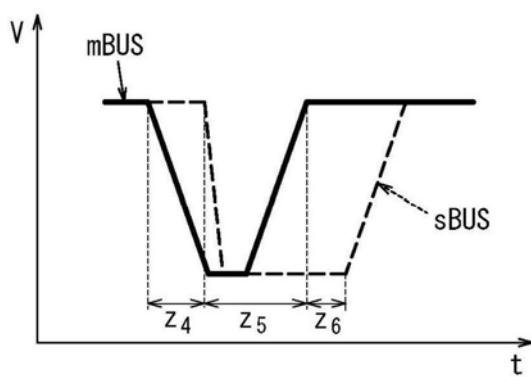

- [0034] 图1示出在从节点的控制和在通信总线中流动的电流之间的关系；

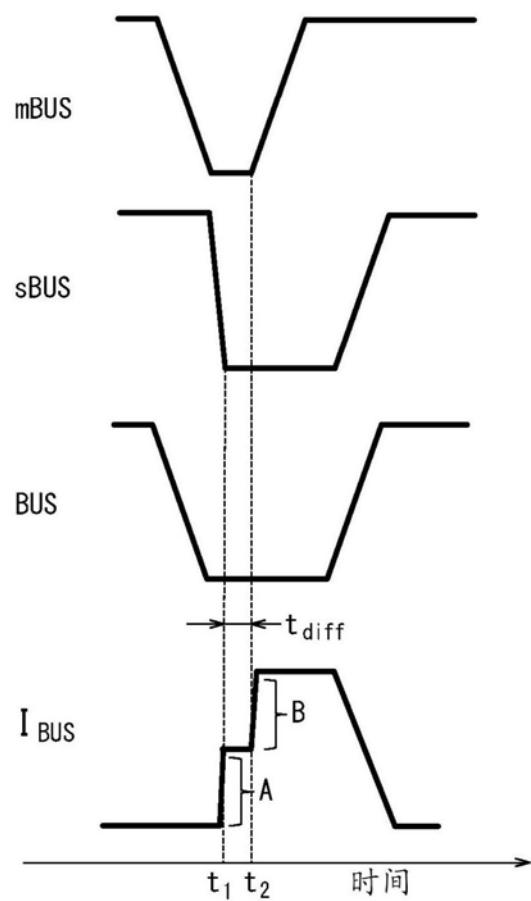

[0035] 图2示出根据所公开的实施例之一的在执行控制时的谐波水平的频谱的示例；

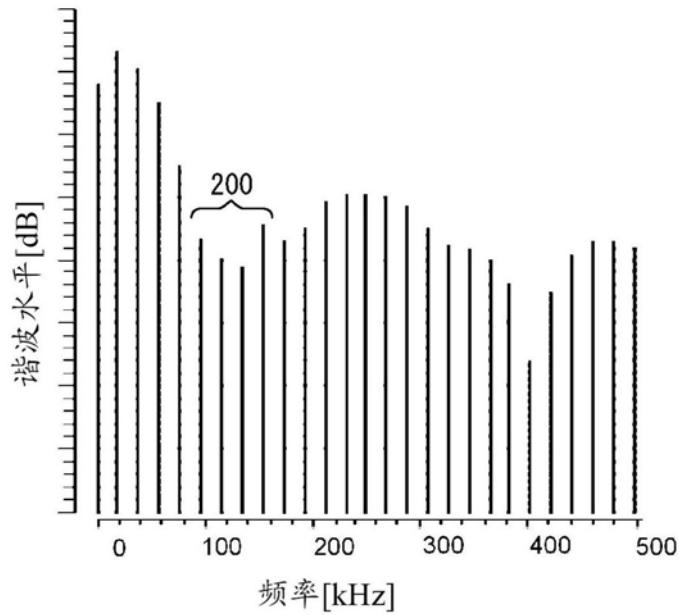

[0036] 图3是示出根据这个实施例的用于通信的收发器的示例的框图；

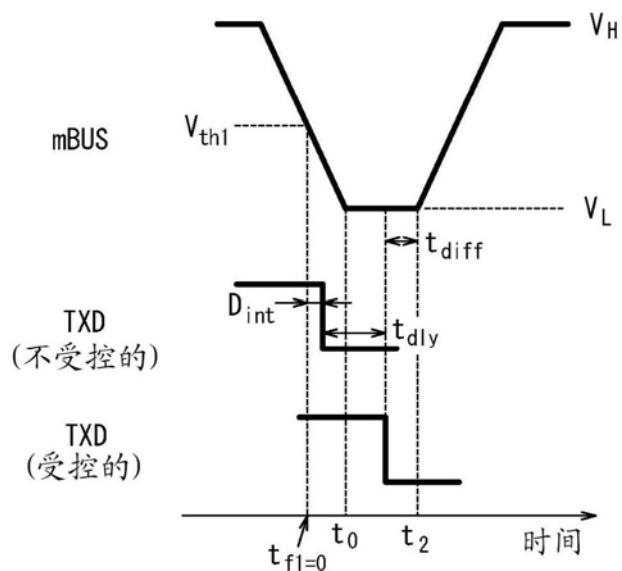

[0037] 图4示出根据这个实施例的采用用于通信的收发器控制发送数据信号的示例；

[0038] 图5示出在从属下降终止早于时钟下降终止时的通信总线的电流的改变；

[0039] 图6是示出根据对这个实施例的修改的用于通信的收发器的示例的框图；

[0040] 图7示出确定图6的用于通信的收发器的上升开始时间和时钟下降终止时间的方法；

[0041] 图8示出图6中的时钟下降终止确定器用于确定时钟下降时间的处理；

[0042] 图9示出图6中的发送数据信号延迟调节器确定延迟时间的方法的示例。

[0043] 图10示出图6中的发送数据信号延迟调节器确定延迟时间的方法的示例。

[0044] 图11示出由图6中的解码器控制的发送数据信号和总线信号。

[0045] 图12示出由图6中的解码器控制的发送数据信号和总线信号。

[0046] 图13示出在上升开始早于从属下降终止时的通信总线的电流的改变；

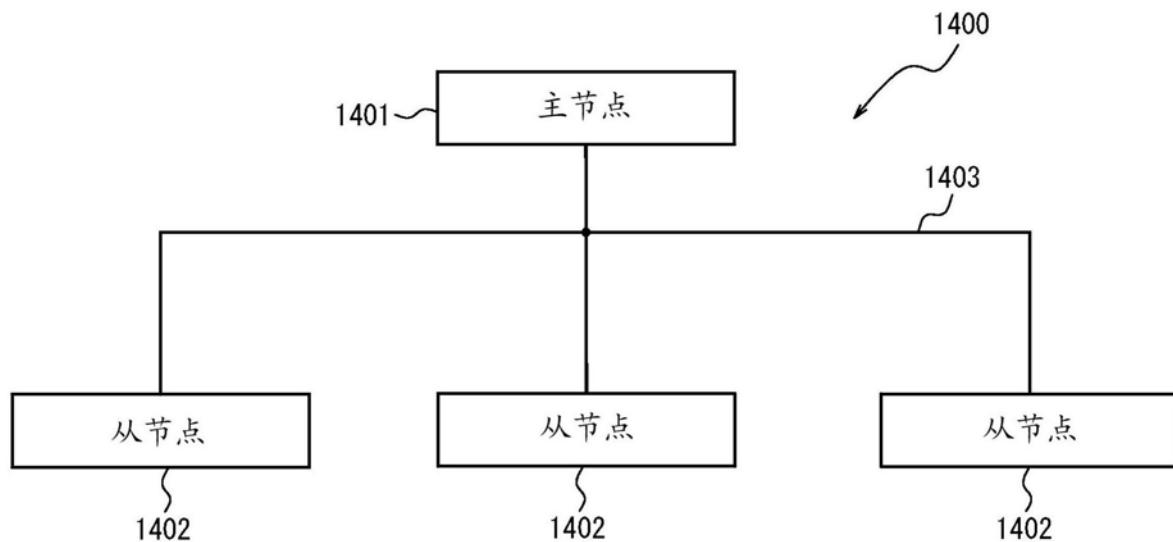

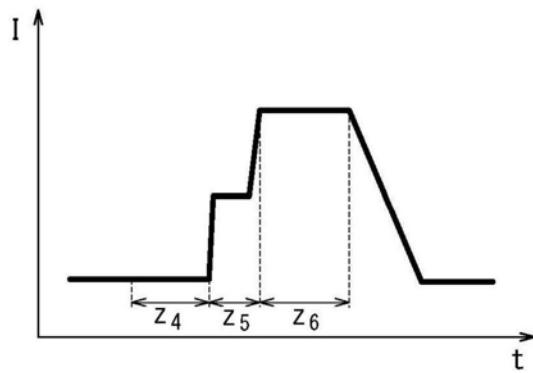

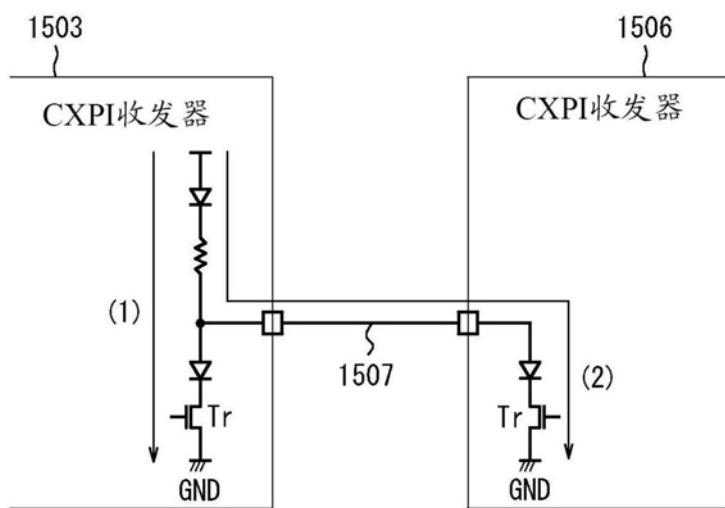

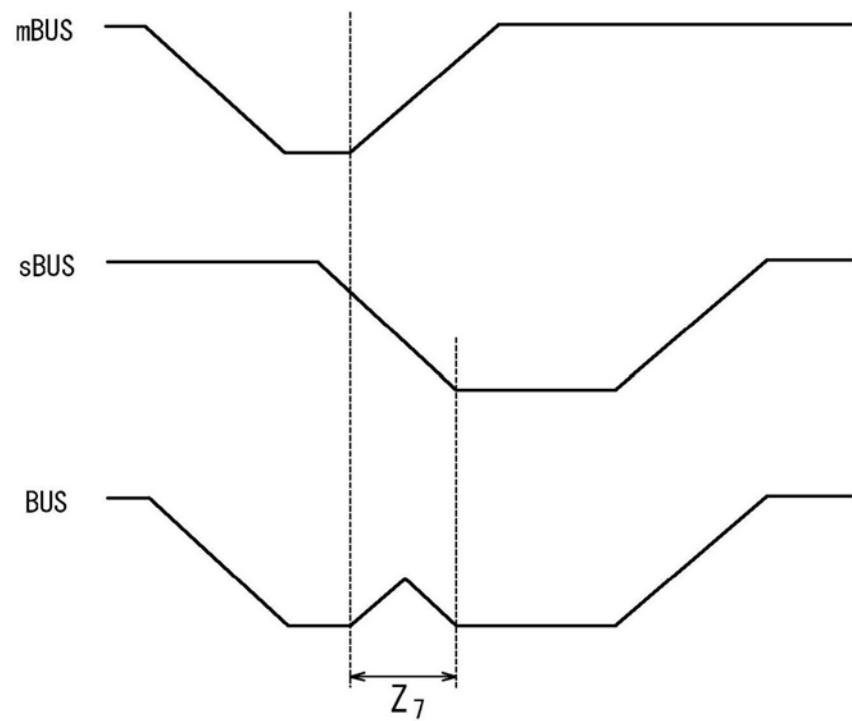

[0047] 图14示出在CXPI通信中的系统结构的示例；

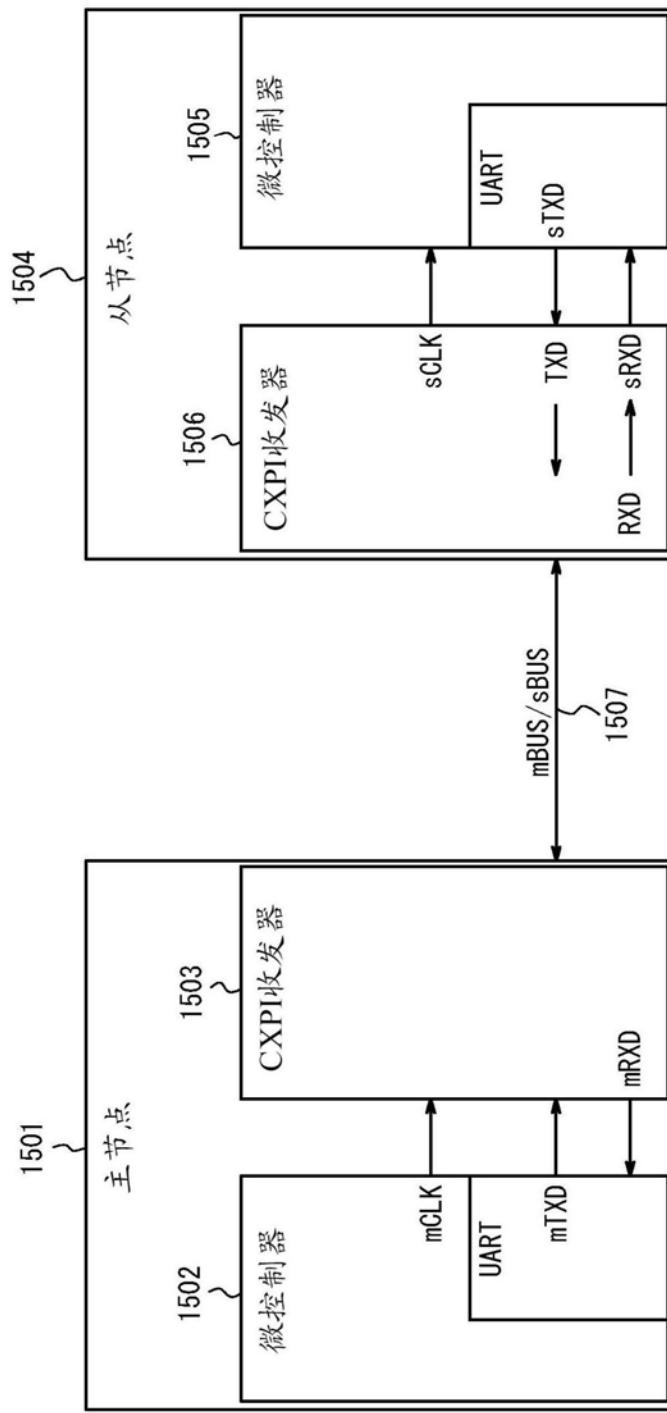

[0048] 图15示出在CXPI通信系统中的电路结构的示例；

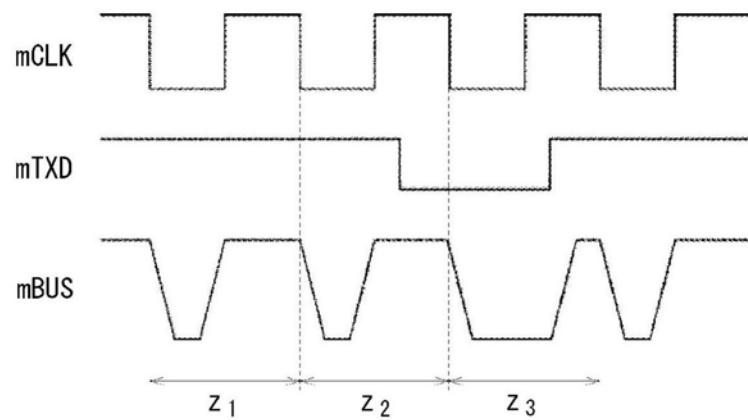

[0049] 图16示出对于在CXPI通信系统中的主节点的波形的示例；

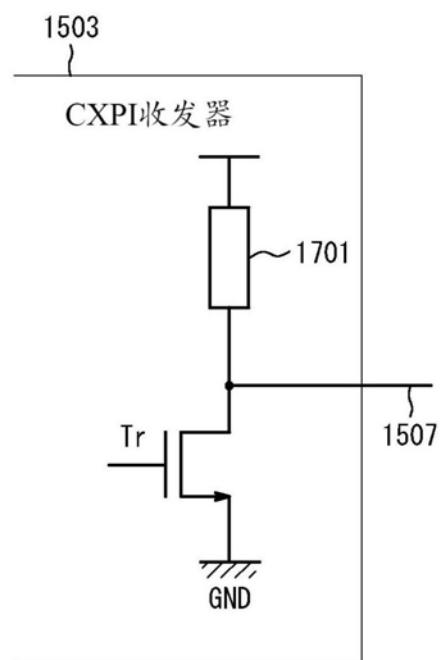

[0050] 图17示出在图15中的主节点的CXPI收发器内的电路的一部分；

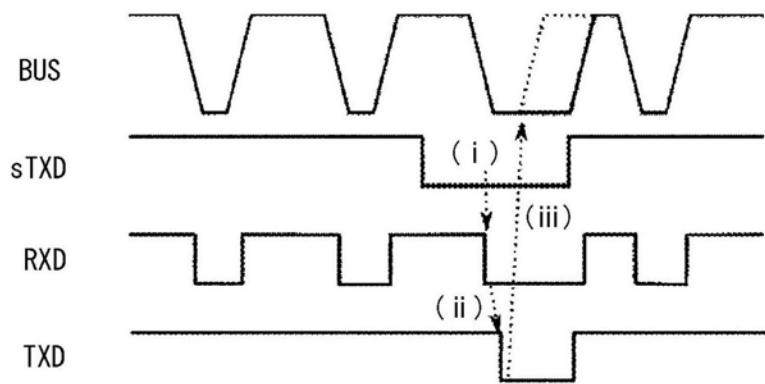

[0051] 图18示出对于在CXPI通信系统中的从节点的波形的示例；

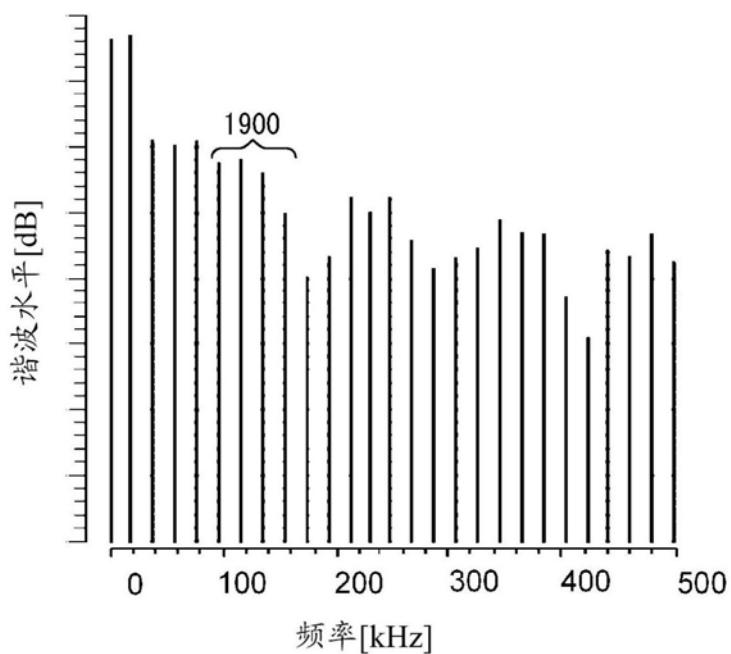

[0052] 图19示出在CXPI通信系统中生成的噪声频谱的示例；

[0053] 图20示出通信总线上的电压的示例；

[0054] 图21示出在通信总线中流动的电流的示例；

[0055] 图22示意性地示出在通信总线中的电流流动的示例；以及

[0056] 图23示出在由主节点输出的总线信号和由从节点输出的总线信号中将下降的倾斜度设置为相同的情况的示例。

[0057] 详细描述

[0058] 在安装在汽车中的ECU之间使用的通信协议的示例包括局域互联网(LIN)、控制器局域网(CAN)以及时钟扩展外围接口(CXPI)。

[0059] 如通过图14中的示例示出的，执行CXPI通信的通信系统1400包括一个主节点1401和多个从节点1402。图14示出具有三个从节点1402的示例。主节点1401通过通信总线1403连接于每个从节点1402。主节点1401和从节点1402例如各自装备有计算机等等。

[0060] 主节点1401是控制每个从节点1402的操作时序的节点。主节点1401以恒定频率向通信总线1403发送总线信号mBUS(参见图15)，该总线信号mBUS变成用于通信的参考。从节点1402采用作为参考时钟的由主节点1401发送的总线信号mBUS发送并且接收数据。

[0061] 图15示出在CXPI通信系统中的电路结构的示例。图15仅示出一个从节点1504，以便简化图示。主节点1501包括微控制器1502和CXPI收发器1503。从节点1504包括微控制器1505和CXPI收发器1506。微控制器1502和1505各自包括通用异步接收器传送器(UART)接口，并且各自向CXPI收发器1503和1506发送信号以及从CXPI收发器1503和1506接收信号。

[0062] 在CXPI通信中，主节点1501通过使时钟信号mCLK经历脉宽调制(PWM)来发送数据。

图16示出对于在CXPI通信系统中的主节点的波形的示例。图16示出从微控制器1502向CXPI收发器1503输出的时钟信号mCLK、从微控制器1502向CXPI收发器1503输出的数据信号mTXD、以及由CXPI收发器1503向通信总线1507输出的总线信号mBUS。

[0063] CXPI收发器1503对时钟信号mCLK执行PWM，以生成呈现对应于数据信号mTXD的逻辑值的信号。通过对时钟信号mCLK执行PWM生成的总线信号mBUS被发送到从节点1504，由此将数据从主节点1501发送到从节点1504。总线信号mBUS具有两个电压电平(高电平和低电平)。总线信号mBUS的高电平和低电平是通过电路(诸如，在图17中示出的电路)生成的，并且被输出到通信总线1507。总线信号mBUS的高电平是由连接于电源线的上拉电阻1701确定的。总线信号mBUS的低电平是通过经由通过输入的数据信号mTXD控制的晶体管Tr连接于接地GND的通信总线1507的输出端子而生成的。

[0064] 在CXPI通信中，输出到通信总线1507的总线信号mBUS的逻辑值是通过总线信号mBUS的低电平(或者高电平)的长度确定的。当总线信号mBUS的低电平的持续时间短于预定时间(例如，在图16中的间隔Z<sub>1</sub>和Z<sub>2</sub>中)的时候，总线信号mBUS的逻辑值是1。当总线信号mBUS的低电平的持续时间长于预定时间(例如，在图16中的间隔Z<sub>3</sub>中)的时候，总线信号mBUS的逻辑值是0。

[0065] CXPI收发器1503对时钟信号mCLK执行PWM，使得当数据信号mTXD处于高电平(如在图16中的间隔Z<sub>1</sub>和Z<sub>2</sub>中所示)的时候，总线信号mBUS呈现逻辑值1。相反，通过延长总线信号mBUS的低电平的持续时间，CXPI收发器1503对时钟信号mCLK执行PWM，使得当数据信号mTXD处于低电平(如在图16中的间隔Z<sub>3</sub>中所示)的时候，总线信号mBUS呈现逻辑值0。以这种方式，CXPI收发器1503通过基于数据信号mTXD控制总线信号mBUS的逻辑值来发送数据。

[0066] CXPI收发器1503从通信总线1507接收由从节点1504发送的总线信号sBUS，并且将通过解码总线信号sBUS获得的数据信号作为接收到的信号mRXD发送到微控制器1502。

[0067] 从节点1504通过将总线信号sBUS与由主节点1501输出的总线信号mBUS组合以生成总线信号BUS来发送数据。在从节点1504输出数据的定时，主节点1501没有发送数据而是以恒定的占空比发送总线信号mBUS，并且从通信总线1507接收由从节点1504发送的总线信号sBUS。在从节点1504输出数据的定时，由主节点1501输出的总线信号mBUS是具有逻辑值1的信号。换句话说，当从节点1504没有输出总线信号sBUS的时候，总线信号BUS呈现逻辑值1。当输出总线信号sBUS的时候，从节点1504配置总线信号sBUS，使得组合的总线信号BUS的逻辑值将会是0。通过从节点1504如此基于总线信号sBUS确定组合的总线信号BUS的逻辑值，可以将数据发送到采集总线信号BUS的主节点1501。

[0068] 图18示出对于在CXPI通信系统中的从节点的波形的示例。图18示出总线信号BUS、由微控制器1505输出的数据信号sTXD、由CXPI收发器1506从总线信号mBUS采集的接收的数据信号RXD以及由CXPI收发器1506向通信总线1507发送的发送数据信号TXD，该总线信号BUS是从从节点1504(CXPI收发器1506)输出的总线信号sBUS和从主节点1501输出的总线信号mBUS的组合。

[0069] 从节点1504经由通信总线1507接收从主节点1501输出的总线信号mBUS，并且进行操作。CXPI收发器1506采集来自通信总线1507的总线信号mBUS的时钟信号sCLK，并且向微控制器1505输出时钟信号sCLK。

[0070] 当向通信总线1507发送数据的时候，从节点1504通过驱动从主节点1501采集的总

线信号mBUS,来通知其他节点开始数据发送。现在描述从节点1504的数据发送。CXPI收发器1506通过在接收到的数据信号RXD中的改变(下降)来检测在总线信号mBUS中的下降,该接收到的数据信号RXD通过在CXPI收发器1506内部的电路生成并且其逻辑值根据总线信号mBUS的行为而改变(图18中的(i))。一旦通过在接收到的数据信号RXD中的下降检测到在总线信号mBUS中的下降,CXPI收发器1506就基于由微控制器1505输出的数据信号sTXD将在CXPI收发器1506内部的电路中生成的发送数据信号TXD的逻辑值控制为0(图18中的(ii))。一旦发送数据信号TXD输入到通信总线1507中,总线信号sBUS的电压就在发送数据信号TXD的逻辑为0的同时降到低电平。因此,作为总线信号mBUS和总线信号sBUS的组合的总线信号BUS的低电平的持续时间被延长(图18中的(iii))。以这种方式,通过被延长的总线信号BUS的低电平,主节点1501可以接收具有延长的低电平的总线信号BUS,由此检测到从从节点1504到主节点1501的数据发送的开始,并且开始接收数据。

[0071] 如以上描述的,当在主节点1501和从节点1504之间执行通信的时候,通过发送和接收信号,可以从通信总线1507发出噪声。从通信总线1507发出的噪声可以影响其他通信。例如,智能钥匙系统受噪声影响。智能钥匙系统是凭借用户拥有的钥匙通过与汽车进行无线通信而对汽车的车门上锁和解锁的系统。例如,当在CXPI通信中将19.2kHz信号用作参考时钟,并且在智能钥匙系统中使用134kHz的时候,134kHz是19.2kHz的7次谐波。因此,如在图19中示出的,在噪声频谱中通过区域1900指示的在134kHz周围(100kHz到160kHz)的谐波水平增加了。因此,智能钥匙系统的无线通信可被CXPI通信阻断。

[0072] 如果尝试通过执行控制以降低总线信号mBUS的转换速率并且使总线信号mBUS平缓地上升和下降来抑制发出噪声,那么当从节点1504发送数据的时候,为了信号的准确性,输入到通信总线1507中的总线信号sBUS的下降优选为有些陡峭。另一方面,如果总线信号sBUS的下降太过陡峭,那么由于在通信总线1507中流动的电流的改变将会生成传导噪声。现在描述在通信总线1507中生成的传导噪声,以及为什么不应使总线信号sBUS的下降太过平缓的原因。

[0073] 图20示出在通信总线1507上的电压信号的示例,并且图21示出在通信总线1507中流动的电流的示例。图22示意性地示出在通信总线1507中的电流流动的示例。

[0074] 当来自从节点1504的总线信号sBUS没有被输入到通信总线1507中,并且来自主节点1501的总线信号mBUS正在下降的时候(图20和图21的间隔Z<sub>4</sub>),电流如在图22的(1)中示出地从CXPI收发器1503中的上拉电阻侧流动到晶体管Tr侧,而没有流动到通信总线1507。

[0075] 如参考图18所描述的,从节点1504将在通信总线1507上的总线信号sBUS的电压电平设置为低电平。因此,一旦将发送数据信号TXD输入到通信总线1507(图20和图21中的间隔Z<sub>5</sub>),电流如通过图22的(1)指示地在CXPI收发器1503中流动,并且还如通过(2)指示地流动到CXPI收发器1506。换句话说,在此时,电流在通信总线1507中流动。当以这种方式从间隔Z<sub>4</sub>过渡到间隔Z<sub>5</sub>的时候,由于电流的改变而生成传导噪声。如在图20中示出的,在此时输入到通信总线1507的总线信号sBUS在下降沿比从主节点1501输出的总线信号mBUS的下降沿具有更为陡峭的倾斜度。因此,出现了电流的突然改变。

[0076] 此外,当由主节点1501输出的总线信号mBUS是高电平并且从从节点1504输出的总线信号sBUS的电压电平保持为低电平的时候(图20和图21中的间隔Z<sub>6</sub>),电流停止流动到CXPI收发器1503的晶体管Tr侧,并且如通过图22中的(2)所指示的,所有的电流从CXPI收发

器1503的上拉电阻侧流动到CXPI收发器1506。因此,当同样从间隔Z<sub>5</sub>过渡到间隔Z<sub>6</sub>的时候,在通信总线1507中流动的电流改变(增加),并且由于电流的改变而因此生成传导噪声。

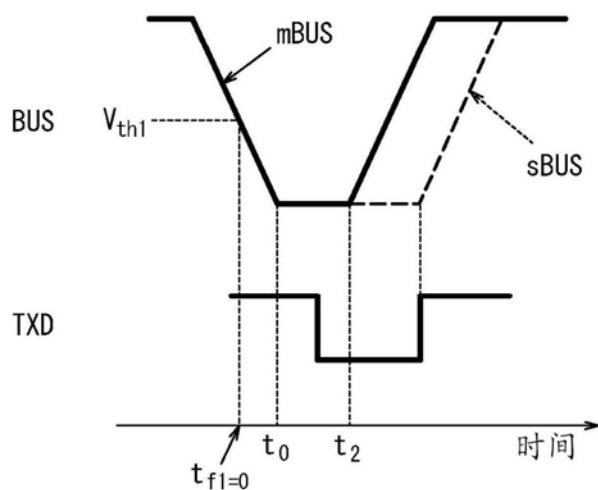

[0077] 图23示出在由主节点1501输出的总线信号mBUS和由从节点1504输出的总线信号sBUS中将下降的倾斜度设置为相同时的情况的示例。当从从节点1504输出的总线信号sBUS的下降的倾斜度平缓的时候,那么在作为来自主节点1501的总线信号mBUS与来自从节点1504的总线信号sBUS的组合的并且在通信总线1507中流动的总线信号BUS中,可以出现间隔Z<sub>7</sub>,其中信号电平与来自主节点1501的总线信号mBUS的上升和来自从节点1504的总线信号sBUS的下降而对应地上升和下降。如果出现在其中信号电平以这种方式上升和下降的间隔Z<sub>7</sub>,那么在主节点1501和从节点1504之间的通信变得不稳定。因此,为了避免出现这一间隔Z<sub>7</sub>,从从节点1504输出的总线信号sBUS的下降优选地具有一定程度的陡度。

[0078] 另一方面,一旦使从从节点1504输出的总线信号sBUS的下降陡峭,就出现如以上描述的传导噪声,其可例如阻断在智能钥匙系统等等中的无线通信。

[0079] 以下参考附图描述用于降低前述传导噪声的影响的实施例。

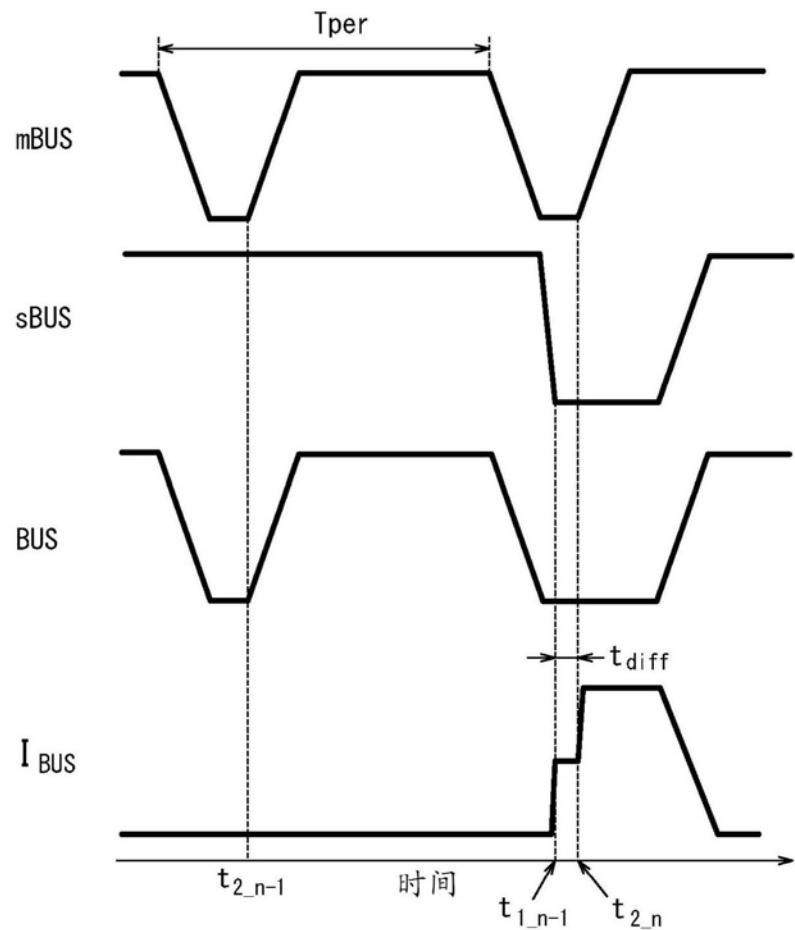

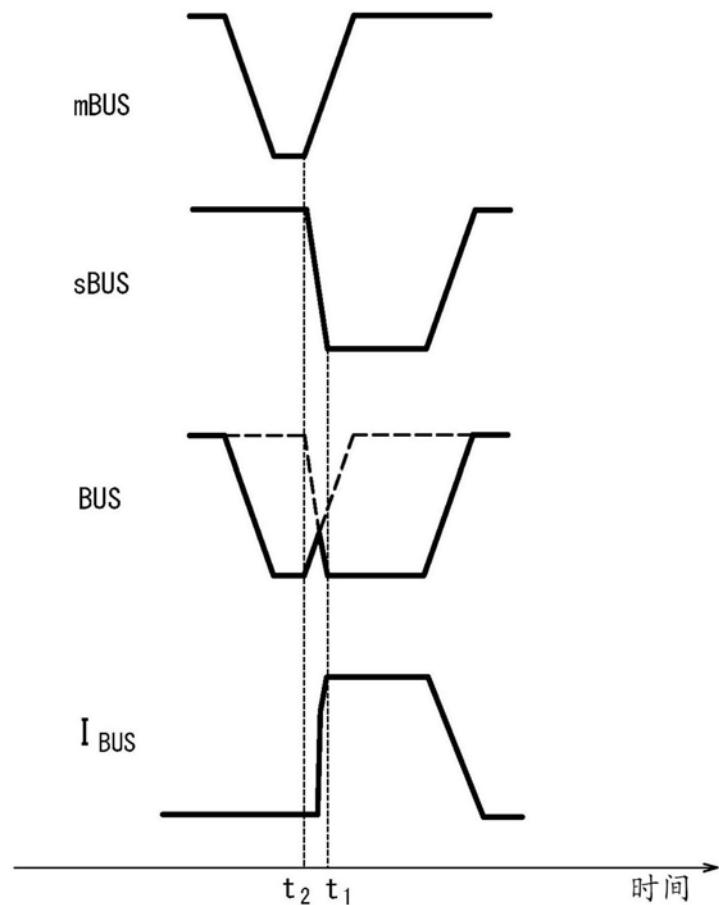

[0080] 首先参考图1描述在这个实施例中支持降低传导噪声的影响的原理。图1示出在通过从节点的控制和在通信总线中流动的电流之间的关系。图1示出由主节点1501输出的总线信号mBUS、由从节点1504输出的总线信号sBUS、作为总线信号mBUS和总线信号sBUS的组合的总线信号BUS、以及在通信总线1507中流动的电流I<sub>BUS</sub>。在图1中,时间t<sub>1</sub>指示在其处来自从节点1504的总线信号sBUS的逻辑值达到0(从属下降终止)的时间点,并且时间t<sub>2</sub>指示在其处来自主节点1501的总线信号mBUS开始从低电平向高电平转移(时钟上升开始)的时间点。

[0081] 如参考图20至22所描述的,由于在从节点1504发送数据时的操作,在通信总线1507中流动的电流I<sub>BUS</sub>改变。在图1中,A段指示由于在图20和图21中的从间隔Z<sub>4</sub>过渡到间隔Z<sub>5</sub>的电流I<sub>BUS</sub>的改变,B段指示由于在图20和图21中的从间隔Z<sub>5</sub>过渡到间隔Z<sub>6</sub>的电流I<sub>BUS</sub>的改变。

[0082] 当时间差t<sub>diff</sub>是预定长度的时候(其中,t<sub>diff</sub>是在时间t<sub>2</sub>和时间t<sub>1</sub>之间的差),那么在指定频带中,电流频谱在A段的分量和电流频谱在B段的分量由于相位关系而抵消。换句话说,在对于A段和B段的每个频带处的频谱的分量中,对于其相位差是π弧度(或者π弧度的奇数倍)的频带的分量相互抵消。

[0083] 现在详细描述在时间差t<sub>diff</sub>和抵消的频率f<sub>陷波</sub>之间的关系。

[0084] 处于预定频率f处的A段和B段的频率分量中的相位差Δ φ通过以下的方程式(3)来表示。

$$\Delta \phi = 2\pi \cdot t_{diff} \cdot f \quad (3)$$

[0086] 为了处于频率f<sub>陷波</sub>处的A段和B段的分量抵消,需要满足相位差Δ φ是π弧度的奇数倍。换句话说,需要满足方程式(4)成立,其中,n是自然数。

$$2\pi \cdot t_{diff} \cdot f_{陷波} = (2n-1)\pi \quad (4)$$

[0088] 对于f<sub>陷波</sub>和t<sub>diff</sub>求解方程式(4),得到以下的方程式(5)和(6)。

$$f_{陷波} = (2n-1) / (2t_{diff}) \quad (5)$$

$$t_{diff} = (2n-1) / (2f_{陷波}) \quad (6)$$

[0091] 因此,通过将时间差t<sub>diff</sub>控制为通过将在其处频谱分量被抵消的频率f<sub>陷波</sub>代入以

上的方程式(6)计算出的值,可以降低处于频率 $f_{\text{谐波}}$ 处的谐波的影响。

[0092] 图2示出根据这个实施例在执行控制时的谐波水平的频谱的示例。图2示出在时间差 $t_{\text{diff}}$ 受控成为以 $f_{\text{谐波}}=134\text{kHz}$ 从方程式(6)计算出的值的时候,谐波水平的频谱。如在图2中示出的,在区域200中指示的 $f_{\text{谐波}}=134\text{kHz}$ 附近的谐波水平相比于图19降低了。因此,可以降低处于 $f_{\text{谐波}}$ 附近频带的传导噪声的影响。在图2中示出的示例中,已描述了 $f_{\text{谐波}}=134\text{kHz}$ 的情况,但是同样在其他频带中,可以通过将时间差 $t_{\text{diff}}$ 控制成为通过方程式(6)计算出的值来降低在频带中的谐波水平。由于在A段和B段之间高度的差(即,电流的波动范围)变得更小,因此增加了谐波水平的降低的影响。

[0093] 图3是示出根据这个实施例的用于通信的从节点收发器(CXPI收发器1506)的示例的框图,其可以降低以上描述的谐波水平。CXPI收发器1506包括模拟块301和逻辑块305。

[0094] 模拟块301包括驱动器302、接收器303以及时钟上升开始检测器304。驱动器302将经由逻辑块305从微控制器1505采集的发送数据信号TXD输入到通信总线1507中。接收器303采集从连接到模拟块301的通信总线1507输入的总线信号mBUS,并且将总线信号mBUS发送到逻辑块305。

[0095] 时钟上升开始检测器304是检测时钟信号开始从低电平向高电平转移的时间点(即,时间 $t_2$ )的电路。时钟上升开始检测器304被配置有例如比较器。当时钟上升开始检测器304配置有比较器的时候,例如总线信号mBUS的低电平电压 $V_L$ 和总线信号mBUS输入到时钟上升开始检测器304中。时钟上升开始检测器304将输入的电压 $V_L$ 与总线信号mBUS的电压进行比较,并且输出表示比较结果的信号。

[0096] 逻辑块305包括解码器306、时钟上升开始确定器307、发送数据信号延迟调节器308和编码器309。解码器306将从接收器303采集的信号的解码的结果发送到微控制器1505。

[0097] 基于从时钟上升开始检测器304采集的时钟上升开始的定时,时钟上升开始确定器307确定了总线信号mBUS开始从低电平转移的时间 $t_2$ 。基于从时钟上升开始确定器307采集的时间 $t_2$ 并且基于目标时间差 $t_{\text{diff}}$ ,发送数据信号延迟调节器308确定用于输入发送数据信号TXD的定时,即,用于降低来自从节点1504的总线信号sBUS的定时。

[0098] 编码器309将从微控制器1505采集的数据信号sTXD转换成PWM信号,并且将发送数据信号TXD输入到驱动器302。在此时,编码器309基于用于由发送数据信号延迟调节器308确定的输入发送数据信号TXD的定时,在预定定时处将发送数据信号TXD输入到驱动器302。

[0099] 参考图4,以下描述了参考图3描述的CXPI收发器1506的控制。类似于图1,图4示出由主节点1501输出的总线信号mBUS、由从节点1504输出的总线信号sBUS、作为总线信号mBUS和总线信号sBUS的组合的总线信号BUS、以及在通信总线1507中流动的电流 $I_{\text{BUS}}$ 。在此描述了CXPI收发器1506在第n个时钟周期通过发送该发送数据信号TXD输出总线信号sBUS的情况的示例。

[0100] 首先,利用时钟上升开始检测器304,CXPI收发器1506检测在第n个周期的前一个周期的第(n-1)个周期处的时钟上升开始的时间 $t_{2,n-1}$ 。利用时钟上升开始确定器307,CXPI收发器1506基于总线信号mBUS的周期 $T_{\text{per}}$ ,还由检测到的时间 $t_{2,n-1}$ 确定第n个时钟上升开始的时间 $t_{2,n}=t_{2,n-1}+T_{\text{per}}$ 。注意,如果可以计算出第n个时钟上升开始的时间 $t_{2,n}$ ,那么CXPI收发器1506不需要检测时间 $t_{2,n-1}$ 。例如,CXPI收发器1506可基于第(n-m)个时钟上升开始的时

间 $t_{2\_n-m}$  (其中 $n>m$ ) 来计算时间 $t_{2\_n}$ 。

[0101] CXPI收发器1506利用发送数据信号延迟调节器308从时间 $t_{2\_n}$ 减去时间差 $t_{diff}$ ,由此计算总线信号sBUS的逻辑值变成0的时间,即,从属下降终止的时间 $t_{1\_n}$ 。CXPI收发器1506将具有逻辑值0的总线信号sBUS调制成PWM信号,使得时间 $t_{1\_n}$ 变成总线信号sBUS的从属下降终止。

[0102] 以这种方式,通过CXPI收发器1506控制对总线信号sBUS的控制的定时,可以降低处于预定频率 $f_{谐波}$ 处的谐波水平。

[0103] 接下来,描述对这个实施例的CXPI收发器1506的修改。在此描述的修改是可以控制以下描述的从属下降终止和总线信号mBUS的下降终止(时钟下降终止)的定时的示例。

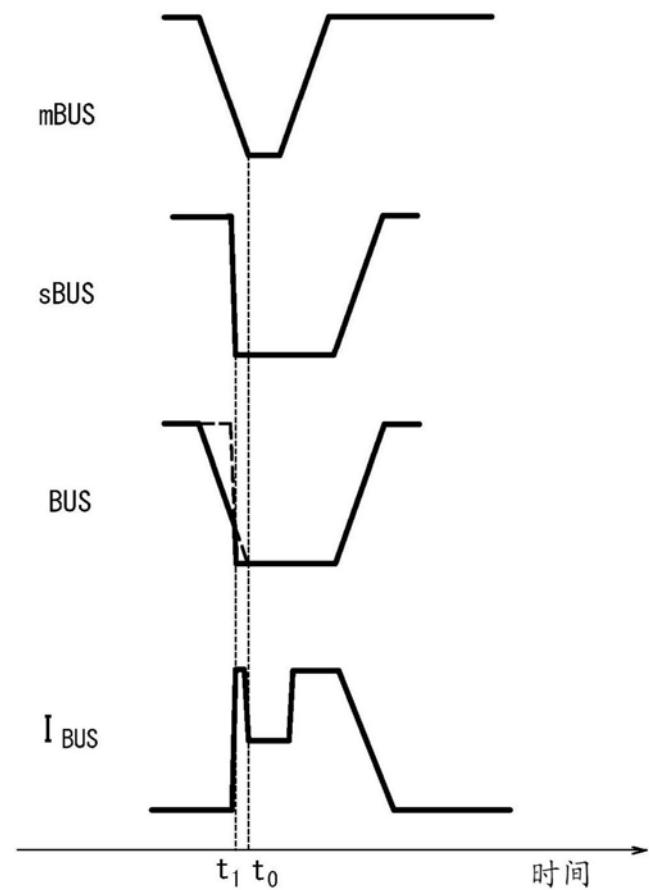

[0104] 图5示出在从属下降终止早于时钟下降终止时的通信总线的电流的改变。如在图5中示出的,当总线信号sBUS的从属下降终止的时间 $t_1$ 早于总线信号mBUS的时钟下降终止的时间 $t_0$ 的时候,那么从时间 $t_1$ 到时间 $t_0$ ,所有的电流从主节点1501的上拉电阻侧经由通信总线1507流动到从节点1504。因此,出现了通信总线1507的电流 $I_{BUS}$ 的改变。传导噪声是由于电流 $I_{BUS}$ 的这个改变而生成的。此时电流 $I_{BUS}$ 的改变的量是在图1中的A段和B段的改变的量的总和。因此,此时对传导噪声的影响与图1中的A段和B段相比增加得更多。因此,从属下降终止的时间 $t_1$ 优选为晚于时钟下降终止的时间 $t_0$ 。

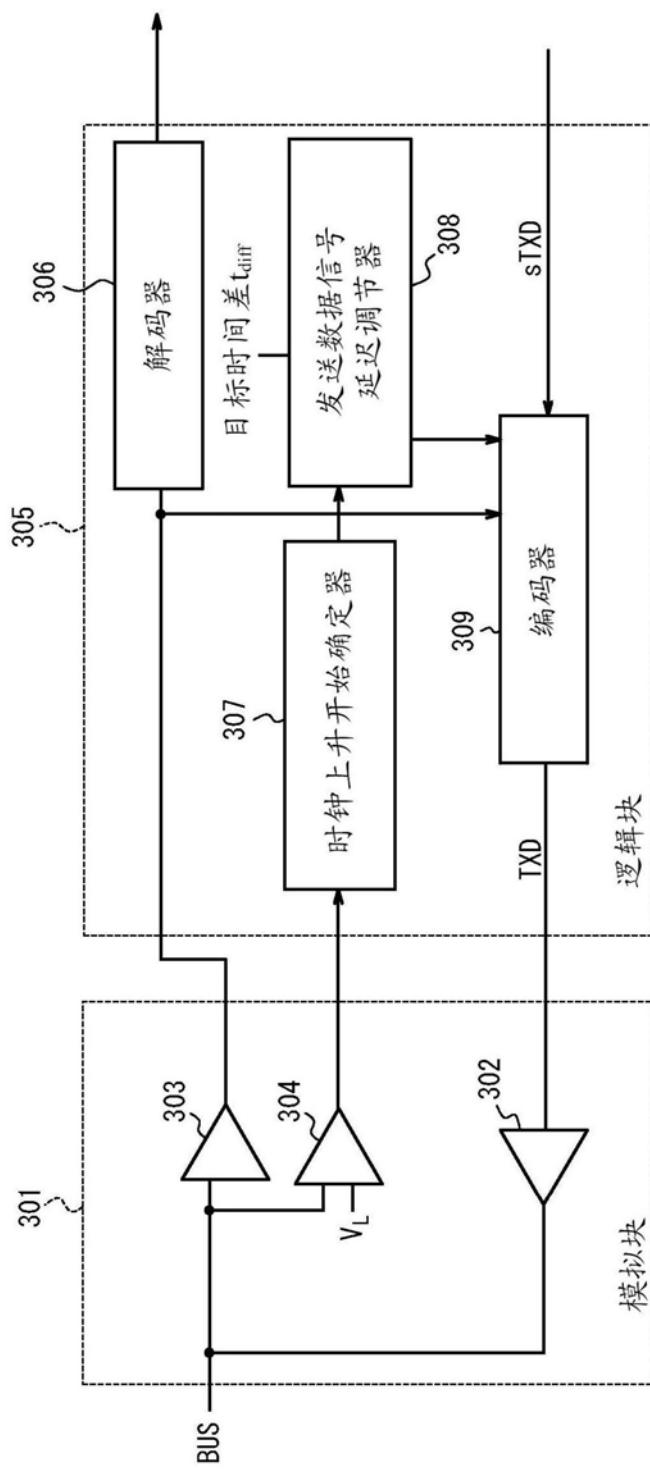

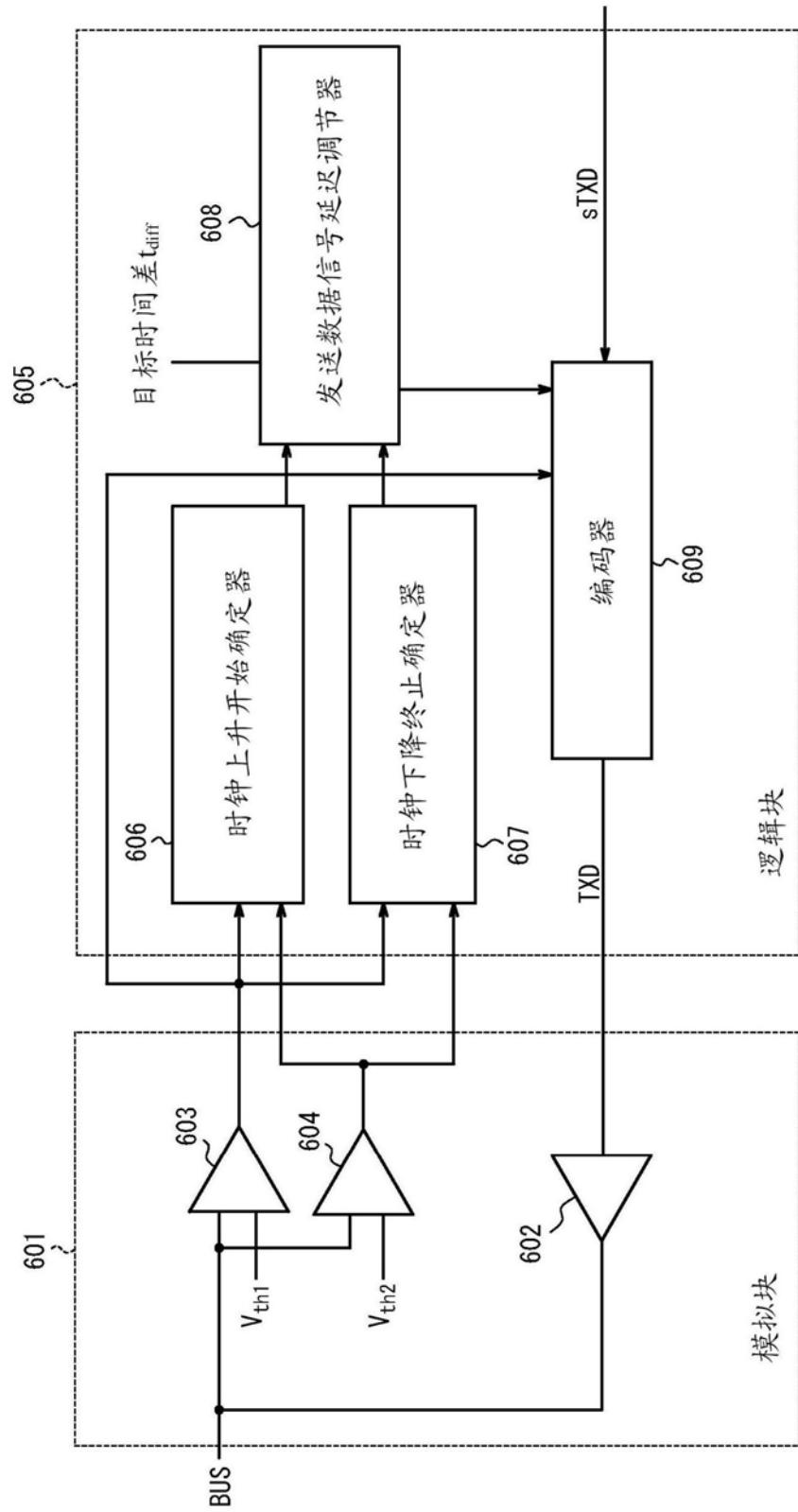

[0105] 图6是示出根据对这个实施例的修改的用于通信的收发器(CXPI收发器1506)的示例的框图。根据这个修改的CXPI收发器1506包括模拟块601和逻辑块605。

[0106] 模拟块601包括驱动器602、第一比较器603以及第二比较器604。驱动器602将从微控制器1505经由逻辑块605采集的发送数据信号TXD输入到通信总线1507中。

[0107] 第一比较器603和第二比较器604输出在逻辑块605中使用的信号,以确定时钟上升开始的时间以及时钟下降终止的时间。来自通信总线1507的总线信号mBUS被输入到第一比较器603和第二比较器604中。此外,第一参考电压 $V_{th1}$ 输入到第一比较器603中,并且第二参考电压 $V_{th2}$ 输入到第二比较器604中。第一参考电压 $V_{th1}$ 和第二参考电压 $V_{th2}$ 均等于或者大于总线信号mBUS的低电平的电压 $V_L$ ,并且等于或者小于总线信号mBUS的高电平的电压 $V_H$ 。在此假设 $V_{th1}>V_{th2}$ 。第一比较器603和第二比较器604分别将第一参考电压 $V_{th1}$ 和第二参考电压 $V_{th2}$ 与总线信号mBUS的电压进行比较,并且输出表示比较结果的信号(比较信号)。

[0108] 逻辑块605包括时钟上升开始确定器606、时钟下降终止确定器607、发送数据信号延迟调节器608以及编码器609。

[0109] 来自第一比较器603和第二比较器604的比较信号被输入到时钟上升开始确定器606和时钟下降终止确定器607中。基于所采集的信号,时钟上升开始确定器606确定总线信号mBUS开始从低电平转移的时间 $t_2$ 。基于所采集的信号,时钟下降终止确定器607确定总线信号mBUS到达低电平的时间 $t_0$ 。以下提供时钟上升开始确定器606和时钟下降终止确定器607确定时间 $t_2$ 和时间 $t_0$ 的方法的细节。

[0110] 基于从时钟上升开始确定器606采集的时间 $t_2$ 、从时钟下降终止确定器607采集的时间 $t_0$ 以及目标时间差 $t_{diff}$ ,发送数据信号延迟调节器608确定用于输入发送数据信号TXD的定时。发送数据信号延迟调节器608执行控制,使得从属下降终止的时间 $t_1$ 比时钟上升开始的时间 $t_2$ 早了时间差 $t_{diff}$ ,这使得期望的谐波水平降低。然而,当时间 $t_1$ 比时钟下降终止的时间 $t_0$ 更早时,由于参考图5描述的原因而生成传导噪声。为了避免这种传导噪声,可以

将从属下降终止的时间  $t_1$  控制为时间  $t_0$  或者晚于时间  $t_0$ 。

[0111] 编码器609将从微控制器1505采集的数据信号sTXD转换成PWM信号，并且将发送数据信号TXD输入到驱动器602。编码器609基于由发送数据信号延迟调节器608确定的用于输入发送数据信号TXD的定时，在预定的定时处将从微控制器1505采集的发送数据信号TXD输入到驱动器602。

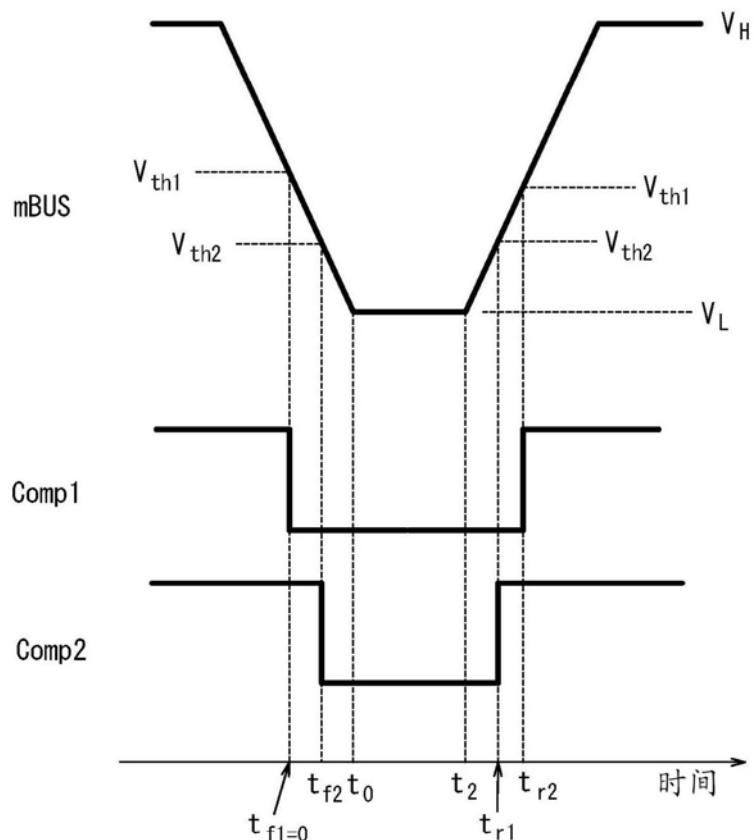

[0112] 现在参考图7描述时钟上升开始确定器606和时钟下降终止确定器607确定时钟上升开始的时间  $t_2$  和时钟下降终止的时间  $t_0$  的方法的细节。图7示出总线信号mBUS、第一比较器603的比较信号Comp1以及第二比较器604的比较信号Comp2。

[0113] 根据第一比较器603的比较信号Comp1和第二比较器604的比较信号Comp2，时钟上升开始确定器606确定在从低电平向高电平过渡的同时，总线信号mBUS到达电压  $V_{th2}$  的时间  $t_{r1}$  以及总线信号mBUS到达电压  $V_{th1}$  的时间  $t_{r2}$ 。基于总线信号mBUS的电压  $V_{th2}$  和  $V_{th1}$  以及时间  $t_{r1}$  和  $t_{r2}$ ，时钟上升开始确定器606可以计算总线信号mBUS改变速率。具体来说，将改变速率计算为  $(V_{th1}-V_{th2}) / (t_{r2}-t_{r1})$ 。基于计算出的改变速率，时钟上升开始确定器606计算总线信号mBUS的电压处于低电平电压  $V_L$  的时间  $t_2$ 。具体来说，时间  $t_2$  是通过以下的方程式(7)计算出的，其中， $V_L=0$ ，并且时间  $t_{r2}$  是参考时间。

$$t_2 = t_{r2} - (t_{r2}-t_{r1}) \cdot V_{th1} / (V_{th1}-V_{th2}) \quad (7)$$

[0115] 根据第一比较器603的比较信号Comp1和第二比较器604的比较信号Comp2，时钟下降终止确定器607确定在从高电平向低电平过渡的同时，总线信号mBUS到达电压  $V_{th1}$  的时间  $t_{f1}$  以及总线信号mBUS到达电压  $V_{th2}$  的时间  $t_{f2}$ 。基于总线信号mBUS的电压  $V_{th1}$  和  $V_{th2}$  以及时间  $t_{f1}$  和  $t_{f2}$ ，时钟下降终止确定器607可以计算总线信号mBUS改变速率。具体来说，将改变速率计算为  $(V_{th2}-V_{th1}) / (t_{f2}-t_{f1})$ 。基于计算出的改变速率，时钟下降终止确定器607计算总线信号mBUS的电压处于低电平电压  $V_L$  的时间  $t_0$ 。具体来说，时间  $t_0$  是通过以下的方程式(8)计算出的，其中， $V_L=0$ ，并且时间  $t_{f1}$  是参考时间。

$$t_0 = (t_{f2}-t_{f1}) \cdot V_{th1} / (V_{th1}-V_{th2}) \quad (8)$$

[0117] 以下描述了参考图6描述的CXPI收发器1506的控制。在此描述了CXPI收发器1506在第n个时钟周期处通过发送该发送数据信号TXD输出总线信号sBUS的情况的示例。

[0118] 首先，CXPI收发器1506利用时钟上升开始确定器606确定在第n个时钟上升开始的时间  $t_{2\_n}$ 。时钟上升开始确定器606的确定方法类似于在图4中描述的方法。因此，在此省略细节。当确定时间  $t_{2\_n}$  的时候，时钟上升开始确定器606可以利用参考图7描述的方法来确定时钟上升开始的时间。

[0119] 接下来，利用时钟下降终止确定器607，CXPI收发器1506确定总线信号mBUS的第n个时钟下降终止的时间  $t_{0\_n}$ 。具体来说，如在图8中示出的，时钟下降终止确定器607检测总线信号mBUS在第n个周期的前一个周期的第(n-1)个周期的时钟下降终止的时间  $t_{0\_n-1}$ 。时钟下降终止确定器607利用参考图7描述的方法来检测时间  $t_{0\_n-1}$ 。利用时钟下降终止确定器607，CXPI收发器1506基于总线信号mBUS的周期  $T_{per}$  还根据检测到的时间  $t_{0\_n-1}$  确定了总线信号mBUS的第n个时钟下降终止的时间  $t_{0\_n} = t_{0\_n-1} + T_{per}$ 。注意，如果可以计算出总线信号mBUS的第n个时钟下降终止的时间  $t_{0\_n}$ ，那么CXPI收发器1506不需要检测时间  $t_{0\_n-1}$ 。例如，CXPI收发器1506可基于总线信号mBUS的第(n-m)个时钟下降终止的时间  $t_{0\_n-m}$  (其中  $n>m$ ) 来计算时间  $t_{0\_n}$ 。

[0120] CXPI收发器1506还利用发送数据信号延迟调节器608来确定发送数据信号TXD的延迟的时间。参考图9和图10提供了发送数据信号延迟调节器608确定延迟时间的方法的细节。

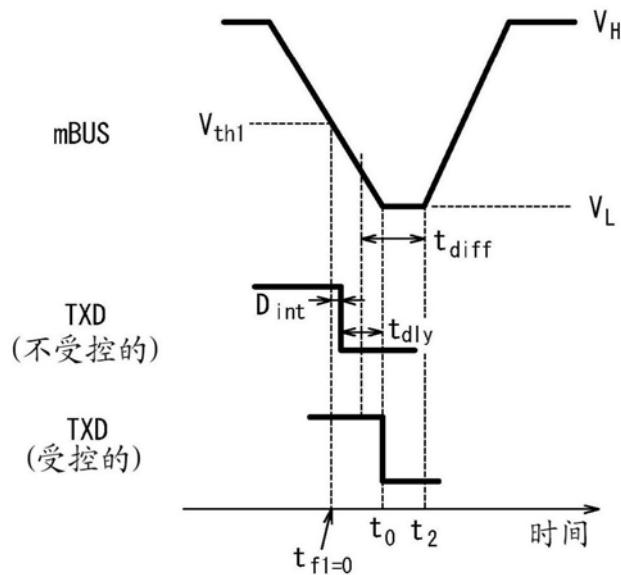

[0121] 图9和图10示出图6中的发送数据信号延迟调节器确定延迟时间的方法的示例。图9和图10示出总线信号mBUS、在不控制输出定时的时候的(不受控的)发送数据信号TXD、以及当控制输出定时的时候的发送数据信号TXD。在此,将在总线信号mBUS下降时电压变成 $V_{th1}$ 的时间 $t_{f1}$ 描述为参考时间。

[0122] 在图9和图10中, $D_{int}$ 是电路内的延迟值,并且包括比较器延迟、内部电路延迟、总线输出延迟等等。此外, $t_{dly}$ 是延迟时间。

[0123] 当时间差 $t_{diff}$ 等于或者小于在时间 $t_2$ 和时间 $t_0$ 之间的时间的时候,即,当 $t_{diff} \leq t_2 - t_0$ 的时候,发送数据信号延迟调节器608通过以下的方程式(9)来确定 $t_{dly}$ 。

$$[0124] t_{dly} = (t_2 - t_{diff}) - D_{int} \quad (9)$$

[0125] 图9示出其中方程式(9)成立的状态的示例。

[0126] 当时间差 $t_{diff}$ 比在时间 $t_2$ 和时间 $t_0$ 之间的时间更长的时候,即,当 $t_{diff} > t_2 - t_0$ 的时候,发送数据信号延迟调节器608将 $t_{dly}$ 确定为满足以下的方程式(10)的值,其中, $t_{min} = t_0 - D_{int}$ 。

$$[0127] t_{dly} > t_{min} \quad (10)$$

[0128] 以这种方式,当 $t_{diff} > t_2 - t_0$ 的时候,通过将 $t_{dly}$ 设置为比 $t_{min}$ 更大的值,可以避免生成参考图5描述的传导噪声。

[0129] 利用编码器609,CXPI收发器1506基于计算出的延迟时间 $t_{dly}$ 来控制发送数据信号TXD。图11和图12示出由图6中的编码器609控制的发送数据信号TXD以及通过将总线信号mBUS和总线信号sBUS进行组合产生的总线信号BUS。图11示出当 $t_{diff} \leq t_2 - t_0$ 时的控制的结果,并且图12示出当 $t_{diff} > t_2 - t_0$ 时的控制的结果。

[0130] 在对应于 $t_{dly}$ 的延迟时间处,编码器609将具有逻辑值0的发送数据信号TXD转换成PWM信号,并且输出结果。在此时,相对于发送数据信号TXD的下降,编码器609执行了对应于 $t_{dly}$ 的时间延迟的控制。另一方面,相对于发送数据信号TXD开始上升(从属上升开始)的时间,编码器609执行控制,使得从时间 $t_{f1}$ 开始的时间长度是恒定的时间长度。假设总线信号mBUS的下降是恒定的,那么编码器609控制发送数据信号在从时间 $t_0$ 开始的恒定的时间长度之后上升。以这种方式,CXPI收发器1506可以在保持总线信号BUS的占空比的同时降低在期望的频带处的谐波水平。

[0131] 如果从属下降终止的时间 $t_1$ 晚于时钟信号开始从低电平向高电平转移的时间 $t_2$ ,那么在通信总线1507中流动的电流如在图13中示出地突然改变,生成传导噪声。因此,时间 $t_1$ 优选为早于时间 $t_2$ 。根据以上描述的实施例和修改,时间 $t_1$ 控制为早于时间 $t_2$ 。

[0132] 虽然本公开的实施例已基于示例并且基于附图进行描述,但是要注意基于本公开的各种改变和修改对于本领域技术人员将会是明显的。因此,这种改变和修改将被理解为被包括在本公开的范围内。例如,被包括在结构组件中的功能等等可以以任何合乎逻辑的一致的方式来重新排序。此外,结构组件等等可以被组合成一个,或者被拆分。

[0133] 例如,在以上描述的实施例和修改中,编码器可以生成PWM信号,并且在CXPI收发器1506中单独提供的定时调节电路可以执行控制,以延迟控制信号的下降沿(从属下降终

止)。在以上描述的实施例和修改中,定时调节电路的功能已被描述为被包括在编码器中。

[0134] 例如以上描述的时钟上升开始确定器307、发送数据信号延迟调节器308、时钟上升开始确定器606、时钟下降终止确定器607以及发送数据信号延迟调节器608可以被配置为其中组合了多个逻辑单元的逻辑电路等等。具体的示例包括在下列各项中的一个或多个:专用集成电路(ASIC)、数字信号处理器(DSP)、数字信号处理设备(DSPD)、可编程逻辑设备(PLD)、现场可编程阵列(FPGA)、处理器、控制器、微控制器以及微处理器或者其组合。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

图17

图18

图19

图20

图21

图22

图23