(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5433220号

(P5433220)

(45) 発行日 平成26年3月5日(2014.3.5)

(24) 登録日 平成25年12月13日(2013.12.13)

(51) Int.Cl.

F 1

|             |           |            |         |

|-------------|-----------|------------|---------|

| HO1L 29/786 | (2006.01) | HO1L 29/78 | 6 1 6 S |

| HO1L 29/417 | (2006.01) | HO1L 29/78 | 6 1 2 C |

| HO1L 29/423 | (2006.01) | HO1L 29/50 | M       |

| HO1L 29/49  | (2006.01) | HO1L 29/58 | G       |

| HO1L 21/768 | (2006.01) | HO1L 21/90 | C       |

請求項の数 10 (全 28 頁) 最終頁に続く

(21) 出願番号

特願2008-305824 (P2008-305824)

(22) 出願日

平成20年12月1日 (2008.12.1)

(65) 公開番号

特開2009-158942 (P2009-158942A)

(43) 公開日

平成21年7月16日 (2009.7.16)

審査請求日 平成23年11月9日 (2011.11.9)

(31) 優先権主張番号 特願2007-312762 (P2007-312762)

(32) 優先日 平成19年12月3日 (2007.12.3)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100103159

弁理士 加茂 裕邦

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 大橋 達也

(56) 参考文献 特開平04-196269 (JP, A)

特開2004-253458 (JP, A)

)

最終頁に続く

(54) 【発明の名称】 半導体装置及びその作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

単結晶半導体基板にイオンを照射することにより、前記単結晶半導体基板に損傷領域を形成し、

前記単結晶半導体基板の表面に第1の配線層を形成し、

前記単結晶半導体基板の表面に第1の絶縁層を形成し、

前記第1の配線層及び前記第1の絶縁層上に第2の絶縁層を形成し、

前記第2の絶縁層と絶縁体でなる基板を接合させ、

前記単結晶半導体基板を前記損傷領域にて分離させることにより、前記絶縁体でなる基板の表面に前記第1の配線層と単結晶半導体層との積層体を形成し、

前記単結晶半導体層を所定の形状に加工することにより、前記第1の配線層の一部を露出させ、

加工した前記単結晶半導体層上にゲート絶縁層を介してゲート電極を形成し、

前記ゲート電極上に第3の絶縁層を形成し、

前記第3の絶縁層に開口部を形成することにより前記第1の配線層の一部を露出させ、

前記第3の絶縁層上に、前記開口部を介して前記第1の配線層と電気的に接続する第2の配線層を形成することを特徴とする半導体装置の作製方法。

## 【請求項 2】

請求項1において、

前記単結晶半導体基板の表面の第1の領域に、前記第1の配線層を形成し、

10

20

前記単結晶半導体基板の表面の前記第1の領域以外の第2の領域に、前記第1の絶縁層を形成することを特徴とする半導体装置の作製方法。

【請求項3】

単結晶半導体基板にイオンを照射することにより、前記単結晶半導体基板に損傷領域を形成し、

前記単結晶半導体基板の表面に第1の配線層及び第1の電極を形成し、

前記単結晶半導体基板の表面に第1の絶縁層を形成し、

前記第1の配線層、前記第1の電極及び前記第1の絶縁層上に第2の絶縁層を形成し、

前記第2の絶縁層と絶縁体でなる基板を接合させ、

前記単結晶半導体基板を前記損傷領域にて分離させることにより、前記絶縁体でなる基板の表面に前記第1の配線層及び前記第1の電極と単結晶半導体層との積層体を形成し、

前記単結晶半導体層を所定の形状に加工することにより、前記第1の配線層の一部と前記第1の電極を露出させ、

加工した前記単結晶半導体層上にゲート絶縁層を介してゲート電極を形成するとともに、前記第1の電極上に前記ゲート絶縁層を介して第2の電極を形成し、

前記ゲート電極及び前記第1の配線層上に第3の絶縁層を形成し、

前記第3の絶縁層に開口部を形成することにより前記第1の配線層の一部を露出させ、

前記第3の絶縁層上に、前記開口部を介して前記第1の配線層と電気的に接続する第2の配線層を形成することを特徴とする半導体装置の作製方法。

【請求項4】

20

請求項3において、

前記単結晶半導体基板の表面の第1の領域に、前記第1の配線層及び前記第1の電極を形成し、

前記単結晶半導体基板の表面の前記第1の領域以外の第2の領域に、前記第1の絶縁層を形成することを特徴とする半導体装置の作製方法。

【請求項5】

請求項1乃至請求項4のいずれか一項において、

前記単結晶半導体層を加工する前に、前記単結晶半導体層にレーザー光を照射することを特徴とする半導体装置の作製方法。

【請求項6】

30

請求項1乃至請求項5のいずれか一項において、

前記第1の配線層を形成する前に、前記単結晶半導体基板に不純物を添加することを特徴とする半導体装置の作製方法。

【請求項7】

請求項1乃至請求項6のいずれか一項において、

加工した前記単結晶半導体層に不純物領域を形成し、

前記第1の配線層の一部は前記不純物領域と接触し、

前記第2の配線層は前記不純物領域と電気的に接続することを特徴とする半導体装置の作製方法。

【請求項8】

40

請求項1乃至請求項7のいずれか一項において、

前記損傷領域を形成した後で前記第1の配線層を形成し、

前記第1の配線層を形成した後で前記第1の絶縁層を形成することを特徴とする半導体装置の作製方法。

【請求項9】

請求項1乃至請求項8のいずれか一項において、

前記第2の絶縁層と前記絶縁体でなる基板を接触させることによって、前記第2の絶縁層と前記絶縁体でなる基板を接合させることを特徴とする半導体装置の作製方法。

【請求項10】

絶縁体でなる基板上の第1の絶縁層と、

50

前記第1の絶縁層上の第1の配線層及び第1の電極と、

前記第1の絶縁層上の、前記第1の配線層及び前記第1の電極が設けられた領域以外の領域に設けられた第2の絶縁層と、

前記第1の配線層及び前記第2の絶縁層上に設けられ、チャネル形成領域と不純物領域を有する単結晶半導体層と、

前記チャネル形成領域上にゲート絶縁層を介して設けられたゲート電極と、

前記第1の電極上に前記ゲート絶縁層を介して設けられた第2の電極と、

前記第1の配線層、前記第2の絶縁層、前記単結晶半導体層、前記第1の電極及び前記第2の電極及び前記ゲート電極を覆う第3の絶縁層と、

前記第3の絶縁層上の第2の配線層と、を有し、

前記第1の配線層と前記不純物領域が電気的に接続されており、

前記第1の配線層と前記第2の配線層が電気的に接続されていることを特徴とする半導体装置。

10

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

半導体装置及びその作製方法に関する。

#### 【背景技術】

#### 【0002】

20

近年、バルク状のシリコンウェハに代わり、SOI (Silicon On Insulator) 基板を使った集積回路が開発されている。絶縁層上に形成された薄い単結晶シリコン層の特長を生かすことで、集積回路中のトランジスタ同士を完全に分離して形成することができ、またトランジスタを完全空乏型とすることができますため、高集積、高速駆動、低消費電力など付加価値の高い半導体集積回路が実現できる。このような、SOI 基板を使ったLSI の開発においては、多層配線技術を用いてチップの面積を縮小することにより、動作周波数を向上し、処理能力の向上が実現されている。

#### 【0003】

また、近年、スマートカット（登録商標）と呼ばれる方法を用いて単結晶シリコン層をガラスからなる支持基板上に形成する方法が提案されている（例えば、特許文献1参照）。ガラス基板はシリコンウェハよりも大面積化が可能であり且つ安価な基板であるため、ガラス基板をベース基板として用いることにより、大面積で安価なSOI 基板を作製することが可能となる。

30

#### 【0004】

しかし、ガラス等の絶縁体でなる基板上の単結晶シリコン層を用いてトランジスタを形成した後、当該トランジスタ上に層間絶縁層を介して配線層を設ける場合、基板のうねり等により当該層間絶縁層の平坦性が十分でないため、配線層の微細化が困難となる。

#### 【0005】

このような配線の微細化の問題に関して、SOIトランジスタの形成に先だって多層配線を作製することにより、微細化された多層配線をSOIトランジスタの下方に作製する技術が提案されている（例えば、特許文献2）。

40

#### 【特許文献1】特開平11-163363号公報

#### 【特許文献2】特開2003-110108号公報

### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0006】

上述したように、平坦性を有する基板上にあらかじめ微細な配線層（下層配線）を形成し、用途に応じてトランジスタの下層と上層に配線層を作りわけることは有効となる。しかし、トランジスタの上層の配線と下層の配線をそれぞれ独立して設けた場合には、配線の自由度が制限される。また、平坦性を有する基板上にあらかじめ微細な配線（下層配線

50

)を形成し、トランジスタの下方に微細化された配線層を設けるだけでは、素子の微細化に限界がある。

**【0007】**

上述した問題に鑑み、トランジスタ等の半導体素子を介して上層と下層に形成された配線層間の良好な接続を可能にし、配線の自由度を向上させた半導体装置及びその作製方法を提供すること目的の一とする。または、微細化された半導体装置及びその作製方法を提供することを目的の一とする。

**【課題を解決するための手段】**

**【0008】**

開示する発明の半導体装置の一は、絶縁体でなる基板上の第1の絶縁層と、第1の絶縁層上に選択的に形成された第1の配線層と、第1の絶縁層上の、第1の配線層が形成された領域以外の領域に形成された第2の絶縁層と、第1の配線層及び第2の絶縁層上に形成され、チャネル形成領域と不純物領域を有する単結晶半導体層と、単結晶半導体層のチャネル形成領域上にゲート絶縁層を介して形成されたゲート電極と、第1の配線層、第2の絶縁層、単結晶半導体層及びゲート電極を覆うように形成された第3の絶縁層と、第3の絶縁層上に形成された第2の配線層と、を有し、第1の配線層と単結晶半導体層の不純物領域が電気的に接続されており、第1の配線層と第2の配線層が電気的に接続されていることを特徴としている。

10

**【0009】**

また、開示する発明の半導体装置の他の一は、絶縁体でなる基板上の第1の絶縁層と、第1の絶縁層上に選択的に形成された第1の配線層及び第1の電極と、第1の絶縁層上の、第1の配線層及び第1の電極が形成された領域以外の領域に形成された第2の絶縁層と、第1の配線層及び第2の絶縁層上に形成され、チャネル形成領域と不純物領域を有する単結晶半導体層と、単結晶半導体層のチャネル形成領域上にゲート絶縁層を介して形成されたゲート電極と、第1の電極上にゲート絶縁層を介して形成された第2の電極と、第1の配線層、第2の絶縁層、単結晶半導体層、第1の電極及び第2の電極、ゲート電極を覆うように形成された第3の絶縁層と、第3の絶縁層上に設けられた第2の配線層と、を有し、第1の配線層と単結晶半導体層の不純物領域が電気的に接続されており、第1の配線層と第2の配線層が電気的に接続されていることを特徴としている。

20

**【0010】**

上記において、第2の配線層は、第3の絶縁層に接して形成され、第3の絶縁層に設けられた開口部において、単結晶半導体層と異なる単結晶半導体層の不純物領域に電気的に接続されている。また、第1の絶縁層は、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素のいずれかを含む層の積層構造を有することが好ましい。

30

**【0011】**

開示する発明の半導体装置の作製方法の一は、単結晶半導体基板にイオンを照射することにより、単結晶半導体基板に損傷領域を形成し、単結晶半導体基板の表面に選択的に第1の配線層を形成し、単結晶半導体基板の表面の、第1の配線層が形成された領域以外の領域に第1の絶縁層を形成し、第1の配線層及び第1の絶縁層と接するように第2の絶縁層を形成し、第2の絶縁層の表面を、絶縁体でなる基板の表面と接触させることにより、第2の絶縁層と絶縁体でなる基板を接合させ、単結晶半導体基板を損傷領域にて分離させることにより、絶縁体でなる基板の表面に第1の配線層と単結晶半導体層との積層体を形成し、単結晶半導体層をパターニングすることにより、第1の配線層の一部を露出させた後、ゲート絶縁層、ゲート電極、第3の絶縁層を順に形成し、第3の絶縁層に開口部を形成することにより第1の配線層の一部を露出させ、第3の絶縁層上に、第1の配線層と電気的に接続する第2の配線層を形成することを特徴としている。

40

**【0012】**

また、開示する発明の半導体装置の作製方法の他の一は、単結晶半導体基板にイオンを照射することにより、単結晶半導体基板に損傷領域を形成し、単結晶半導体基板の表面に選択的に第1の配線層及び第1の電極を形成し、単結晶半導体基板の表面の、第1の配線

50

層及び第1の電極が形成された領域以外の領域に第1の絶縁層を形成し、第1の配線層、第1の電極及び第1の絶縁層と接するように第2の絶縁層を形成し、第2の絶縁層の表面を、絶縁体でなる基板の表面と接触させることにより、第2の絶縁層と絶縁体でなる基板を接合させ、単結晶半導体基板を損傷領域にて分離させることにより、絶縁体でなる基板の表面に第1の配線層及び第1の電極と単結晶半導体層との積層体を形成し、単結晶半導体層をパターニングすることにより、第1の配線層の一部と第1の電極を露出させ、パターニングされた単結晶半導体層、露出した第1の配線層の一部及び第1の電極上にゲート絶縁層を形成し、単結晶半導体層上にゲート絶縁層を介してゲート電極を形成し、第1の電極上にゲート絶縁層を介して第2の電極を形成し、単結晶半導体層、第1の配線層及び第2の電極を覆うように第3の絶縁層を形成し、第3の絶縁層に開口部を形成することにより第1の配線層の一部を露出させ、第3の絶縁層上に、第1の配線層と電気的に接続する第2の配線層を形成することを特徴としている。10

#### 【0013】

上記において、絶縁体でなる基板の表面に形成された単結晶半導体層のパターニング前に、単結晶半導体層にレーザー光を照射することが好ましい。また、第1の配線層を形成する前に、単結晶半導体基板に対してしきい値電圧を制御するための不純物を選択的に添加しても良い。

#### 【発明の効果】

#### 【0014】

上述のように、トランジスタ等の半導体素子を介して上層と下層に形成された配線層間の良好な接続を可能にすることができる。20

#### 【発明を実施するための最良の形態】

#### 【0015】

実施の形態について、図面を用いて以下に説明する。但し、本発明は以下に示す実施の形態の記載内容に限定されず、発明の趣旨から逸脱することなく形態及び詳細を様々に変更し得ることは当業者にとって自明である。また、異なる実施の形態に係る構成は、適宜組み合わせて実施することができる。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を用い、その繰り返しの説明は省略する。また、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指すものとする。30

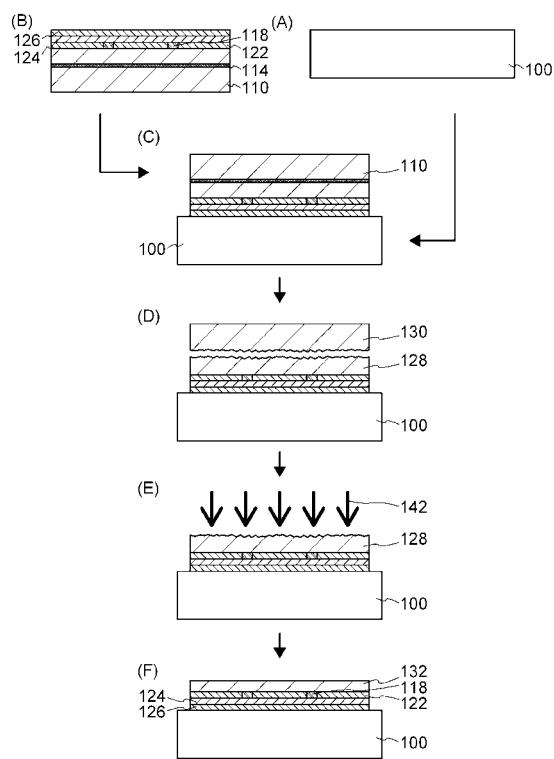

#### 【0016】

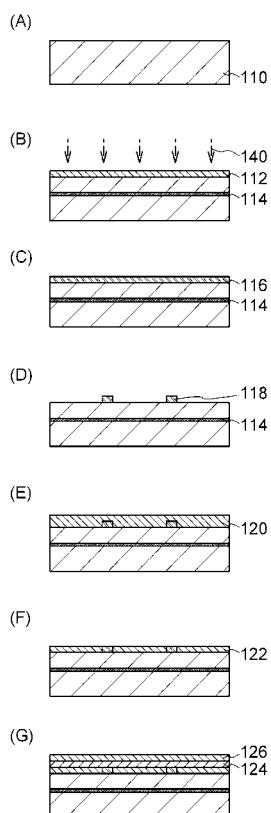

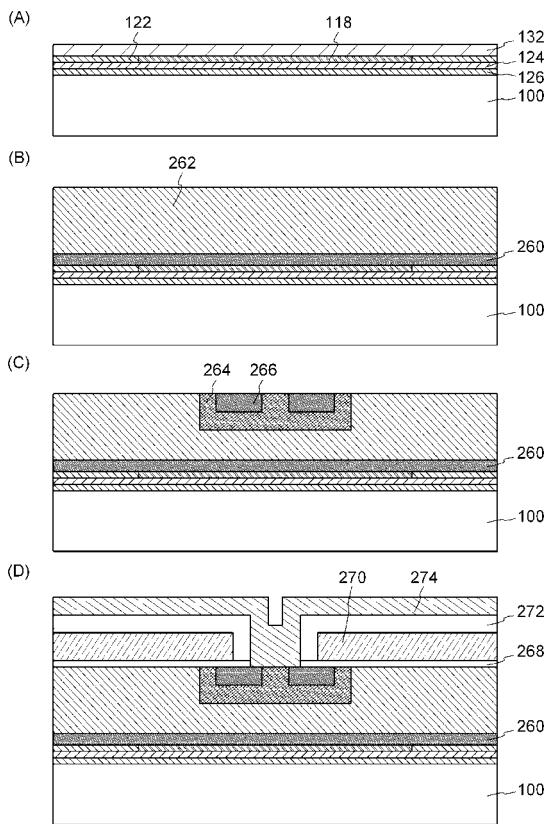

#### (実施の形態1)

本実施の形態では、半導体装置の製造方法の一例について、図1乃至5を参照して説明する。より具体的には、図1を用いてSOI基板の製造方法について説明し、図2乃至図4を用いて半導体装置の製造方法について説明し、図5を用いて上記SOI基板に用いる基板の加工方法について説明する。

#### 【0017】

まず、SOI基板の製造方法について図1を参照して説明する。

#### 【0018】

はじめに、ベース基板100を用意する(図1(A)参照)。ベース基板100には、液晶表示装置などに使用されている透光性を有するガラス基板を用いることができる。ガラス基板としては、歪み点が580以上680以下(好ましくは、600以上680以下)であるものを用いると良い。また、ガラス基板は無アルカリガラス基板であることが好ましい。無アルカリガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。40

#### 【0019】

なお、ベース基板100としては、ガラス基板の他、セラミック基板、石英基板やサファイア基板などの絶縁体でなる基板、珪素などの半導体でなる基板、金属やステンレスなどの導電体でなる基板などを用いることもできる。

#### 【0020】

50

20

30

40

50

本実施の形態においては示さないが、ベース基板100の表面に絶縁層を形成しても良い。該絶縁層を設けることにより、ベース基板100に不純物（アルカリ金属やアルカリ土類金属など）が含まれている場合には、当該不純物が半導体層へ拡散することを防止できる。絶縁層は単層構造でも良いし積層構造でも良い。絶縁層を構成する材料としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素などを挙げることができる。

#### 【0021】

なお、本明細書において、酸化窒化物とは、その組成において、窒素よりも酸素の含有量（原子数）が多いものを示し、例えば、酸化窒化珪素とは、酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以下、珪素が25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の範囲で含まれるものという。また、窒化酸化物とは、その組成において、酸素よりも窒素の含有量（原子数）が多いものを示し、例えば、窒化酸化珪素とは、酸素が5原子%以上30原子%以下、窒素が20原子%以上55原子%以下、珪素が25原子%以上35原子%以下、水素が10原子%以上25原子%以下の範囲で含まれるものという。但し、上記範囲は、ラザフォード後方散乱法（RBS：Rutherford Backscattering Spectrometry）や、水素前方散乱法（HFS：Hydrogen Forward Scattering）を用いて測定した場合のものである。また、構成元素の含有比率の合計は100原子%を超えない。

#### 【0022】

次に、単結晶半導体基板110を用意する。単結晶半導体基板110としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコンなどの第4属元素である半導体基板を用いることができる。もちろん、ガリウムヒ素、インジウムリンなどの化合物半導体でなる基板を用いてもよい。本実施の形態においては、単結晶半導体基板110として、単結晶シリコン基板を用いることとする。単結晶半導体基板110のサイズに制限は無いが、例えば、8インチ（200mm）、12インチ（300mm）、18インチ（450mm）といった円形の半導体基板を、矩形に加工して用いることができる。なお、本明細書において、単結晶とは、結晶構造が一定の規則性を持って形成されており、どの部分においても結晶軸が同じ方向を向いているものをいう。つまり、欠陥の多少については問わないものとする。

#### 【0023】

上記の単結晶半導体基板110に対して各種処理を施して、損傷領域114、配線層118、絶縁層122、絶縁層124、絶縁層126を形成する（図1（B）参照）。各種処理の詳細については後に述べる。なお、損傷領域114はイオンが照射されることにより形成された領域であり、該領域において単結晶半導体基板110を分離することが可能になる。このため、損傷領域114が形成される深さにより、単結晶半導体基板110から分離される単結晶半導体層の厚さが決定されることになる。

#### 【0024】

また、絶縁層126は、貼り合わせにおける接合を形成する層であるから、その表面は、高い平坦性を有することが好ましい。このような絶縁層126としては、例えば、有機シランガスを用いて化学気相成長法により形成される酸化珪素膜を用いることができる。

#### 【0025】

その後、上記のベース基板100と単結晶半導体基板110とを貼り合わせる（図1（C）参照）。具体的には、ベース基板100及び絶縁層126の表面を超音波洗浄などの方法で洗浄した後、ベース基板100の表面と絶縁層126の表面とが接触するように配置する。そして、ベース基板100の表面と絶縁層126の表面とで接合が形成されるように、加圧処理を施す。接合のメカニズムとしては、ファン・デル・ワールス力が関わるメカニズムや、水素結合が関わるメカニズムなどが考えられる。

#### 【0026】

なお、接合を形成する前に、ベース基板100又は絶縁層126の表面を酸素プラズマ処理又はオゾン処理して、その表面を親水性にしても良い。この処理によって、ベース基

10

20

30

40

50

板 100 又は絶縁層 126 の表面に水酸基が付加されるため、接合界面に水素結合を形成することができる。

#### 【0027】

次に、接合されたベース基板 100 及び単結晶半導体基板 110 に対して加熱処理を施して、接合を強固なものとする。この際の加熱温度は、損傷領域 114 における分離が進行しない温度とする必要がある。例えば、400 未満、好ましくは 300 以下とすることができる。加熱処理時間については特に限定されず、処理速度と接合強度との関係から最適な条件を適宜設定すればよい。本実施の形態においては、200、2 時間の加熱処理を施すこととする。ここで、接合に係る領域にマイクロ波を照射して、接合に係る領域のみを局所的に加熱することも可能である。なお、接合強度に問題がない場合は、上記加熱処理を省略しても良い。10

#### 【0028】

次に、単結晶半導体基板 110 を、損傷領域 114 にて、単結晶半導体層 128 と単結晶半導体基板 130 とに分離する（図 1 (D) 参照）。単結晶半導体基板 110 の分離は、加熱処理により行う。該加熱処理の温度は、ベース基板 100 の耐熱温度を目安にすることができる。例えば、ベース基板 100 としてガラス基板を用いる場合には、加熱温度は 400 以上ベース基板 100 の耐熱温度以下とすることが好ましい。なお、本実施の形態においては、600、2 時間の加熱処理を施すこととする。

#### 【0029】

上述のような加熱処理を行うことにより、損傷領域 114 に形成された微小な空孔の体積変化が生じ、損傷領域 114 に亀裂が生ずる。その結果、損傷領域 114 に沿って単結晶半導体基板 110 が分離する。絶縁層 126 はベース基板 100 と接合しているので、ベース基板 100 上には単結晶半導体基板 110 から分離された単結晶半導体層 128 が残存することになる。また、この加熱処理で、ベース基板 100 と絶縁層 126 の接合界面が加熱されるため、接合界面に共有結合が形成され、ベース基板 100 と絶縁層 126 の結合力が一層向上する。20

#### 【0030】

上述のようにして形成された半導体基板において、単結晶半導体層 128 の表面には、分離工程やイオン照射工程による欠陥が存在し、また、その平坦性は損なわれている。このような凹凸のある単結晶半導体層 128 の表面に、薄く、且つ、高い絶縁耐圧のゲート絶縁層を形成することは困難である。そのため、単結晶半導体層 128 の平坦化処理を行う。また、単結晶半導体層 128 に欠陥が存在する場合には、ゲート絶縁層との界面における局在準位密度が高くなるなど、トランジスタの性能及び信頼性に悪影響を与えるため、単結晶半導体層 128 の欠陥を減少させる処理を行う。30

#### 【0031】

本実施の形態において、単結晶半導体層 128 の平坦性向上、および欠陥の低減は、単結晶半導体層 128 にレーザー光 142 を照射することで実現される（図 1 (E) 参照）。レーザー光 142 を単結晶半導体層 128 の上面側から照射することで、単結晶半導体層 128 上面を溶融させる。溶融した後、単結晶半導体層 128 が冷却、固化することで、その上面の平坦性が向上した単結晶半導体層が得られる。本実施の形態においては、レーザー光 142 を用いているため、ベース基板 100 が直接加熱されない。つまり、ベース基板 100 の温度上昇を抑えることができる。このため、ガラス基板のような耐熱性の低い基板をベース基板 100 に用いることが可能である。もちろん、ベース基板の耐熱温度の範囲内における加熱を行う構成としても良い。ベース基板を加熱することにより、比較的低いエネルギー密度のレーザー光を用いる場合であっても、欠陥の低減を効果的に進めることができる。40

#### 【0032】

なお、レーザー光 142 の照射による単結晶半導体層 128 の溶融は、部分溶融とすることが好ましい。完全溶融させた場合には、液相となった後の無秩序な核発生により微結晶化し、結晶性が低下する可能性が高いためである。一方で、部分溶融させることにより50

、溶融されていない固相部分から結晶成長が進行する。これにより、半導体層中の欠陥を減少させることができる。ここで、完全溶融とは、単結晶半導体層128が下部界面付近まで溶融されて、液体状態になることをいう。他方、部分溶融とは、この場合、単結晶半導体層128の上部は溶融して液相となるが、下部は溶融せずに固相のままであることをいう。

#### 【0033】

上記レーザー光の照射には、パルス発振レーザーを用いることが好ましい。これは、瞬間に高エネルギーのパルスレーザー光を発振することができ、部分溶融状態を作り出すことが容易となるためである。発振周波数は、1 Hz以上10 MHz以下程度とすることが好ましい。より好ましくは、10 Hz以上1 MHz以下である。上述のパルス発振レーザーとしては、Arレーザー、Krレーザー、エキシマ(ArF、KrF、XeCl)レーザー、CO<sub>2</sub>レーザー、YAGレーザー、YVO<sub>4</sub>レーザー、YLFレーザー、YAlO<sub>3</sub>レーザー、GdVO<sub>4</sub>レーザー、Y<sub>2</sub>O<sub>3</sub>レーザー、ルビーレーザー、アレキサンドライトレーザー、Ti:Sファイアレーザー、銅蒸気レーザー、金蒸気レーザー等を用いることができる。なお、部分溶融させるためにはパルス発振レーザーを用いることが好ましいが、これに限定して解釈されるものではない。すなわち、連続発振レーザーの使用を除外するものではない。なお、連続発振レーザーとしては、Arレーザー、Krレーザー、CO<sub>2</sub>レーザー、YAGレーザー、YVO<sub>4</sub>レーザー、YLFレーザー、YAlO<sub>3</sub>レーザー、GdVO<sub>4</sub>レーザー、Y<sub>2</sub>O<sub>3</sub>レーザー、ルビーレーザー、アレキサンドライトレーザー、Ti:Sファイアレーザー、ヘリウムカドミウムレーザー等がある。10 20

#### 【0034】

レーザー光142の波長は、単結晶半導体層128に吸収される波長とする必要がある。その波長は、レーザー光の表皮深さ(skin depth)などを考慮して決定すればよい。例えば、250 nm以上700 nm以下の範囲とすることができます。また、レーザー光142のエネルギー密度は、レーザー光142の波長、レーザー光の表皮深さ、単結晶半導体層128の膜厚などを考慮して決定することができます。レーザー光142のエネルギー密度は、例えば、300 mJ/cm<sup>2</sup>以上800 mJ/cm<sup>2</sup>以下の範囲とすればよい。なお、上記エネルギー密度の範囲は、パルス発振レーザーとしてXeClエキシマレーザー(波長：308 nm)を用いた場合の一例である。

#### 【0035】

レーザー光142の照射は、大気雰囲気のような酸素を含む雰囲気、または窒素雰囲気のような不活性雰囲気で行うことができる。不活性雰囲気中でレーザー光142を照射するには、気密性のあるチャンバー内でレーザー光142を照射し、このチャンバー内の雰囲気を制御すればよい。チャンバーを用いない場合は、レーザー光142の被照射面に窒素ガスなどの不活性ガスを吹き付けることで、窒素雰囲気を形成することもできる。30

#### 【0036】

なお、窒素などの不活性雰囲気で行うほうが、大気雰囲気よりも単結晶半導体層128の平坦性を向上させる効果は高い。また、大気雰囲気よりも不活性雰囲気のほうがクラックやリッジの発生を抑える効果が高く、レーザー光142の使用可能なエネルギー密度の範囲が広くなる。なお、レーザー光142の照射は、真空中で行ってもよい。真空中でレーザー光142を照射した場合には、不活性雰囲気における照射と同等の効果を得ることができる。40

#### 【0037】

上述のようにレーザー光142を照射した後には、単結晶半導体層128の膜厚を小さくする薄膜化工程を行っても良い。単結晶半導体層128の薄膜化には、ドライエッチングまたはウェットエッチングの一方、または双方を組み合わせたエッチング処理(エッチバック処理)を適用すればよい。例えば、単結晶半導体層128がシリコン材料からなる層である場合、SF<sub>6</sub>とO<sub>2</sub>をプロセスガスに用いたドライエッチング処理で、単結晶半導体層128を薄くすることができる。

#### 【0038】

なお、本実施の形態においては、レーザー光の照射により平坦化等した後でエッティング処理を行ってもよい、としているが、開示する発明はこれに限定して解釈されるものではない。例えば、レーザー光の照射前にエッティング処理を行ってもよい。この場合には、エッティング処理により半導体層表面の凹凸や欠陥をある程度低減することができる。また、レーザー光の照射前及び照射後の両方に上記処理を適用しても良い。また、レーザー光の照射と上記処理を交互に繰り返しても良い。このように、レーザー光の照射とエッティング処理を組み合わせて用いることにより、半導体層表面の凹凸、欠陥等を著しく低減することができる。もちろん、上述のエッティング処理や加熱処理などを常に用いる必要はない。

#### 【0039】

以上により、表面の平坦性が向上し、欠陥が低減された単結晶半導体層132を有するS0I基板を作製することができる（図1（F）参照）。 10

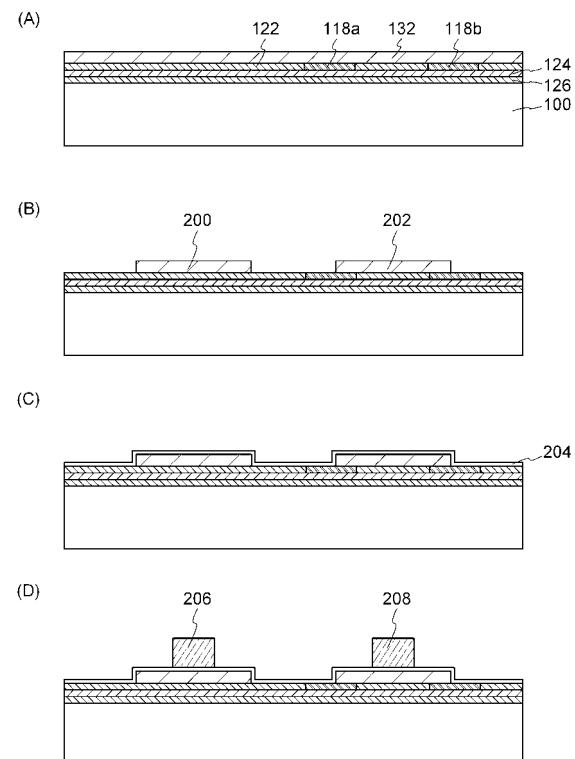

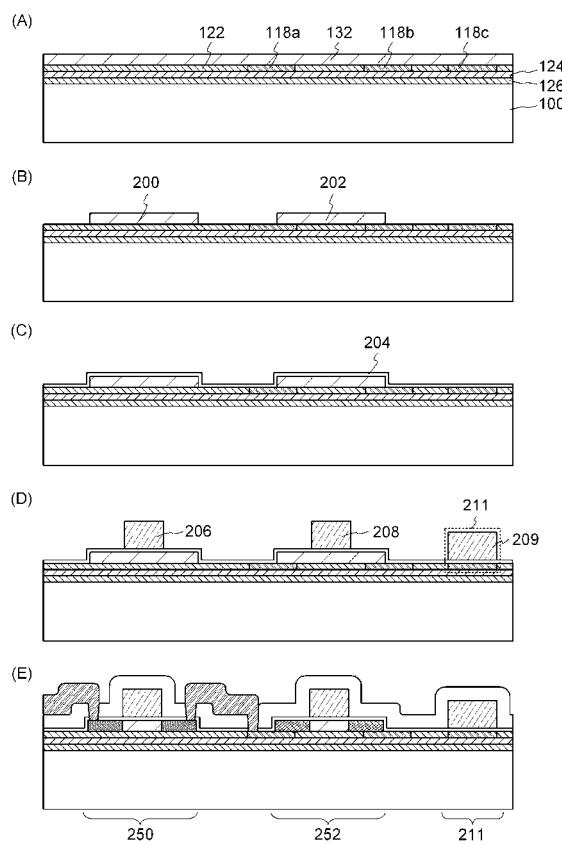

#### 【0040】

次に、上記S0I基板を用いた半導体装置の製造方法について、図2乃至図4を参考して説明する。ここでは、一例として複数のトランジスタからなる半導体装置の作製方法について説明することとする。

#### 【0041】

図2（A）に、上述のS0I基板の一部を拡大した断面図を示す。図2（A）から分かるように、配線層118a及び配線層118bが単結晶半導体層132の下部に設けられており、配線層118a又は配線層118bと、単結晶半導体層132とは接触している。 20

#### 【0042】

単結晶半導体層132には、トランジスタのしきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどのp型を付与する不純物、又は、リン、砒素などのn型を付与する不純物を添加しても良い。不純物を添加する領域、および添加する不純物の種類は、適宜変更することができる。例えば、nチャネル型トランジスタの形成領域にはp型を付与する不純物を添加し、pチャネル型トランジスタの形成領域にはn型を付与する不純物を添加することができる。

#### 【0043】

上記単結晶半導体層132に対してエッティング処理を施すことにより、単結晶半導体層132を島状に分離して単結晶半導体層200及び単結晶半導体層202を形成する（図2（B）参照）。ここで、配線層上に存在する単結晶半導体層の一部を除去することにより、配線層の表面の一部を露出させる。露出させた領域以外においては、配線層と単結晶半導体層との接続が保たれている。本実施の形態においては、配線層118a及び配線層118bは単結晶半導体層202と接触しており、また、一部の領域においてその表面が露出した構成となっているが、開示する発明がこれに限定されるものではない。 30

#### 【0044】

なお、図2（B）では、単結晶半導体層200と単結晶半導体層202と同じ大きさで表しているが、これは模式図にすぎず、単結晶半導体層200と単結晶半導体層202とを同じ大きさとすることに限られない。目的とする半導体素子の特性に合わせて、適宜大きさを変更することができる。 40

#### 【0045】

次に、単結晶半導体層200と単結晶半導体層202を覆うように、ゲート絶縁層204を形成する（図2（C）参照）。ここでは、プラズマCVD法を用いて、酸化珪素膜を単層で形成することとする。その他にも、酸化窒化珪素、窒化酸化珪素、窒化珪素、酸化ハフニウム、酸化アルミニウム、酸化タンタル等を含む膜を、単層構造又は積層構造で形成することによりゲート絶縁層204としても良い。

#### 【0046】

プラズマCVD法以外の作製方法としては、スパッタリング法や、高密度プラズマ処理による酸化または窒化による方法が挙げられる。高密度プラズマ処理は、例えば、ヘリウム、アルゴン、クリプトン、キセノンなどの希ガスと、酸素、酸化窒素、アンモニア、窒 50

素、水素などガスの混合ガスを用いて行う。この場合、プラズマの励起をマイクロ波の導入により行うことで、低電子温度で高密度のプラズマを生成することができる。このような高密度のプラズマで生成された酸素ラジカル（OHラジカルを含む場合もある）や窒素ラジカル（NHラジカルを含む場合もある）によって、半導体層の表面を酸化または窒化することにより、1 nm以上20 nm以下、望ましくは2 nm以上10 nm以下の絶縁層を形成することができる。なお、上述した高密度プラズマ処理による半導体層の酸化又は窒化は固相反応であるため、界面準位密度をきわめて低くすることができるという特徴を有している。

#### 【0047】

或いは、単結晶半導体層200と単結晶半導体層202を熱酸化させることで、ゲート絶縁層204を形成するようにしても良い。このような熱酸化を用いる場合には、耐熱性が比較的高いベース基板を用いることが好ましい。

#### 【0048】

次に、ゲート絶縁層204上に導電層を形成した後、該導電層を所定の形状に加工（パターニング）することで、単結晶半導体層200と単結晶半導体層202の上方にゲート電極206及びゲート電極208を形成する（図2（D）参照）。導電層の形成にはCVD法、スパッタリング法等を用いることができる。導電層は、タンタル、タングステン、チタン、モリブデン、アルミニウム、銅、クロム、ニオブ等の材料を用いて形成することができる。また、上記金属を主成分とする合金材料を用いても良いし、上記金属を含む化合物を用いても良い。または、半導体層に導電性を付与する不純物元素をドーピングした多結晶珪素などを用いて形成しても良い。

#### 【0049】

本実施の形態ではゲート電極206及びゲート電極208を単層の導電層で形成しているが、開示する発明の半導体装置は該構成に限定されない。ゲート電極206及びゲート電極208を2層構造とする場合には、例えば、モリブデン、チタン、窒化チタン等を下層に用い、上層にはアルミニウムなどを用いればよい。3層構造の場合には、モリブデンとアルミニウムとモリブデンの積層構造や、チタンとアルミニウムとチタンの積層構造などを採用するとよい。

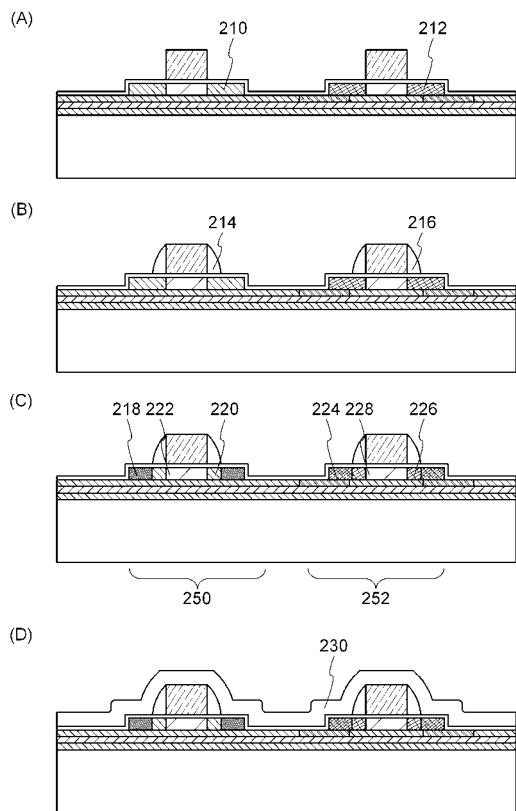

#### 【0050】

次に、ゲート電極206及びゲート電極208をマスクとして、一導電型を付与する不純物元素を単結晶半導体層200及び単結晶半導体層202に添加する（図3（A）参照）。本実施の形態では、単結晶半導体層200にn型を付与する不純物元素（例えばリンやヒ素など）を添加し、単結晶半導体層202にp型を付与する不純物元素（例えばボロンなど）を添加する場合について説明するが、開示する発明はこれに限定されない。なお、n型を付与する不純物元素とp型を付与する不純物元素の添加を選択的に行うためには、n型の不純物を添加する際にはp型の不純物が添加される単結晶半導体層をマスク等で覆い、p型の不純物を添加する際にはn型の不純物が添加される単結晶半導体層をマスク等で覆う。又は、全ての半導体層に、先にp型を付与する不純物元素又はn型を付与する不純物元素の一方を添加した後、一部の半導体層に対して、より高い濃度でp型を付与する不純物元素又はn型を付与する不純物元素の他方を添加するようにしても良い。上記不純物の添加により、単結晶半導体層200に不純物領域210、単結晶半導体層202に不純物領域212が形成される。

#### 【0051】

次に、ゲート電極206の側面にサイドウォール214を、ゲート電極208の側面にサイドウォール216を形成する（図3（B）参照）。サイドウォール214及びサイドウォール216は、例えば、ゲート絶縁層204、ゲート電極206及びゲート電極208を覆うように新たに絶縁層を形成し、該絶縁層に対して垂直方向を主体とした異方性エッチング処理を施すことにより形成することができる。なお、上記の異方性エッチングにより、ゲート絶縁層204を部分的に除去しても良い。例えば、ゲート電極及びサイドウォールの下部に存在するゲート絶縁層以外については除去する構成とすることもできる。

10

20

30

40

50

サイドウォール 214 及びサイドウォール 216 を形成するための絶縁層としては、プラズマ CVD 法やスパッタリング法等により、珪素、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、有機材料などを含む膜を、単層構造又は積層構造で形成すれば良い。本実施の形態では、膜厚 100 nm の酸化珪素膜をプラズマ CVD 法によって形成する。また、エッチングガスとしては、CHF<sub>3</sub> とヘリウムの混合ガスを用いることができる。なお、サイドウォール 214 及びサイドウォール 216 を形成する工程は、これらに限定されるものではない。

#### 【 0052 】

次に、ゲート電極 206 及びサイドウォール 214 並びにゲート電極 208 及びサイドウォール 216 をマスクとして、単結晶半導体層 200 及び単結晶半導体層 202 に一導電型を付与する不純物元素を添加する(図 3(C) 参照)。なお、単結晶半導体層 200 及び単結晶半導体層 202 には、それぞれ先の工程で添加した不純物元素と同じ導電型の不純物元素をより高い濃度で添加する。これにより、単結晶半導体層 200 に、一対の高濃度不純物領域 218 と、一対の低濃度不純物領域 220 と、チャネル形成領域 222 が形成され、単結晶半導体層 202 に、一対の高濃度不純物領域 224 と、一対の低濃度不純物領域 226 と、チャネル形成領域 228 とが形成される。高濃度不純物領域 218 及び高濃度不純物領域 224 はソース領域又はドレイン領域として機能し、低濃度不純物領域 220 及び低濃度不純物領域 226 は LDD (Lightly Doped Drain) 領域として機能する。また、配線層 118a、118b は高濃度不純物領域 224 と接することとなる。もちろん、配線層 118a、118b と低濃度不純物領域 226 が接するように設けてもよい。

#### 【 0053 】

なお、図 3(B) 乃至図 3(D) においては、単結晶半導体層 200 上に形成されたサイドウォール 214 と、単結晶半導体層 202 上に形成されたサイドウォール 216 を同じ大きさで表しているが、これは模式図にすぎず、開示する発明がこれに限定して解釈されるものではない。サイドウォールの大きさに従って LDD 領域の大きさも変化するため、トランジスタが要求される特性に応じてサイドウォール 214 とサイドウォール 216 の大きさを設定すればよい。

#### 【 0054 】

ソース領域及びドレイン領域をさらに低抵抗化するために、単結晶半導体層 200 及び単結晶半導体層 202 の一部をシリサイド化したシリサイド層を形成しても良い。シリサイド化は、半導体層に金属を接触させ、加熱(例えば、GRTA 法、LRTA 法等を用いた加熱)により、半導体層中の珪素と金属とを反応させて行う。本実施の形態においては、単結晶半導体層 202 に接して配線層 118a 及び配線層 118b が設けられているため、これを用いて単結晶半導体層 202 の一部をシリサイド化しても良い。また、レーザー光の照射などによってもシリサイド層を形成することができる。シリサイド化に用いることができる金属材料としては、チタン、ニッケル、タンクステン、モリブデン、コバルト、ジルコニアム、ハフニウム、タンタル、バナジウム、ネオジム、クロム、白金、パラジウム等が挙げられる。

#### 【 0055 】

上述の工程により、単結晶半導体を用いた n チャネル型トランジスタ 250 及び p チャネル型トランジスタ 252 が形成される。なお、図 3(C) に示す段階では、ソース電極又はドレイン電極として機能する配線層は形成されていないが、ソース電極又はドレイン電極として機能する配線層を含めてトランジスタと呼んでもよい。

#### 【 0056 】

次に、n チャネル型トランジスタ 250、p チャネル型トランジスタ 252 を覆うように絶縁層 230 を形成する(図 3(D) 参照)。絶縁層 230 は、例えば、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、窒化アルミニウム、酸化アルミニウムなどの材料を用いて形成することができる。また、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の耐熱性を有する有機材料を用いて形成してもよい。

10

20

30

40

50

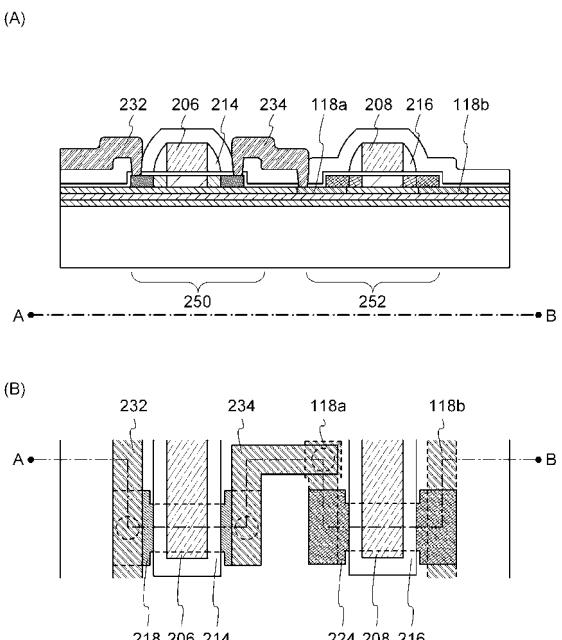

## 【0057】

次に、単結晶半導体層200の表面が一部露出するように絶縁層230にコンタクトホールを形成する。また、同時に、配線層118aの表面が一部露出するように絶縁層230にコンタクトホールを形成する。そして、該コンタクトホールを介して単結晶半導体層200又は配線層118aに接する配線層232、配線層234を形成する(図4(A)参照)。なお、本実施の形態においては、コンタクトホール開口時のエッティングに用いるガスとしてCH<sub>3</sub>F<sub>3</sub>とHeの混合ガスを用いたが、これに限定されるものではない。また、本実施の形態においては示さないが、必要であれば、配線層118bの表面が露出するようにコンタクトホールを形成しても良い。

## 【0058】

配線層232、配線層234は、CVD法やスパッタリング法等により形成することができる。具体的には、アルミニウム、タンゲステン、チタン、タンタル、モリブデン、ニッケル、白金、銅、金、銀、マンガン、ネオジム、炭素、珪素等の材料を用いることができる。また、上記材料を主成分とする合金を用いても良いし、上記材料を含む化合物を用いても良い。また、配線層232、配線層234は、単層構造としても良いし、積層構造としても良い。

## 【0059】

アルミニウムを主成分とする合金の例としては、アルミニウムを主成分として、ニッケルを含むものが挙げられる。また、アルミニウムを主成分とし、ニッケルと、炭素または珪素の一方または両方を含むものを挙げることができる。アルミニウムやアルミニウムシリコン(Al-Si)は抵抗値が低く、安価であるため、配線層232、配線層234を形成する材料として適している。特に、アルミニウムシリコンは、ヒロックの発生を抑制することができるため好ましい。また、珪素の代わりに、アルミニウムに0.5%程度のCuを混入させた材料を用いても良い。

## 【0060】

配線層232、配線層234を積層構造とする場合には、例えば、バリア膜とアルミニウムシリコン膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン膜と窒化チタン膜とバリア膜の積層構造などを採用するとよい。なお、バリア膜とは、チタン若しくはチタンの窒化物、又はモリブデン若しくはモリブデンの窒化物などを用いて形成された膜である。バリア膜の間にアルミニウムシリコン膜を挟むようにすると、ヒロックの発生をより一層抑制することができる。また、還元性の高い元素であるチタンを用いてバリア膜を形成すると、単結晶半導体層200上又は配線層118a上に薄い酸化膜が形成されていたとしても、バリア膜に含まれるチタンが該酸化膜を還元し、配線層232と単結晶半導体層200、及び配線層234と単結晶半導体層200又は配線層118aのコンタクトを良好なものとすることができます。また、バリア膜を複数積層するようにして用いても良い。その場合、例えば、配線層232、配線層234を、下層からチタン、窒化チタン、アルミニウムシリコン、チタン、窒化チタンのように、5層構造又はそれ以上の積層構造とすることもできる。

## 【0061】

なお、配線層232はnチャネル型トランジスタ250の高濃度不純物領域218に接続されている。また、配線層234はnチャネル型トランジスタ250の高濃度不純物領域218及び配線層118aに接続されている。

## 【0062】

図4(A)に示したnチャネル型トランジスタ250及びpチャネル型トランジスタ252の平面図を、図4(B)に示す。ここで、図4(B)のA-Bにおける断面が図4(A)に対応している。ただし、図4(B)においては、簡単のため、ゲート絶縁層204、絶縁層230などの構成要素の一部を省略している。

## 【0063】

なお、本実施の形態においては、nチャネル型トランジスタ250とpチャネル型トランジスタ252が、それぞれゲート電極として機能する電極を1つずつ有する場合を例示

10

20

30

40

50

しているが、開示する発明は該構成に限定されない。作製されるトランジスタは、ゲート電極として機能する電極を複数有し、なおかつ該複数の電極が電気的に接続されているマルチゲート構造を有していても良い。

#### 【0064】

以上により、複数のトランジスタを有する半導体装置を作製することができる。

#### 【0065】

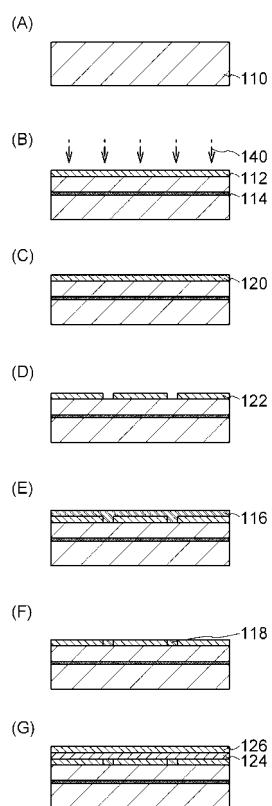

次に、図5を用いてSOI基板の製造に用いる単結晶半導体基板の加工方法について説明する。

#### 【0066】

まず、単結晶半導体基板110を用意する(図5(A)参照)。単結晶半導体基板110の詳細については、半導体基板の製造方法の説明(図1の説明)を参照することができるため、ここでは省略する。10

#### 【0067】

単結晶半導体基板110を洗浄した後、単結晶半導体基板110の表面に絶縁層112を形成する。絶縁層112を設けない構成とすることもできるが、後のイオン照射の際の単結晶半導体基板110の汚染及び表面の損傷を防ぐためには、絶縁層112を設けることが好ましい。絶縁層112の厚さは10nm以上400nm以下とする良い。

#### 【0068】

絶縁層112を構成する材料としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素などを挙げることができる。絶縁層112の形成方法としては、CVD法、スパッタ法、単結晶半導体基板110の酸化(又は窒化)による方法などがある。20

#### 【0069】

次に、絶縁層112を介して、電界で加速されたイオンであるイオンビーム140を単結晶半導体基板110に照射し、単結晶半導体基板110の表面から所定の深さの領域に、損傷領域114を形成する(図5(B)参照)。損傷領域114が形成される領域の深さは、イオンビーム140の加速エネルギーとイオンビーム140の入射角によって制御することができる。なお、損傷領域114は、イオンの平均侵入深さと同程度の深さの領域に形成されることになる。

#### 【0070】

上述の損傷領域114が形成される深さにより、単結晶半導体基板110から分離される単結晶半導体層の厚さが決定される。損傷領域114が形成される深さは、単結晶半導体基板110の表面から50nm以上500nm以下であり、好ましくは50nm以上200nm以下である。30

#### 【0071】

イオンを単結晶半導体基板110に照射する際には、イオン注入装置又はイオンドーピング装置を用いることができる。イオン注入装置では、ソースガスを励起してイオン種を生成し、生成されたイオン種を質量分離して、所定の質量を有するイオン種を被処理物に注入する。イオンドーピング装置は、プロセスガスを励起してイオン種を生成し、生成されたイオン種を質量分離せずに被処理物に照射する。なお、質量分離装置を備えているイオンドーピング装置では、イオン注入装置と同様に、質量分離を伴うイオンの注入を行うこともできる。本明細書において、イオン注入装置又はイオンドーピング装置のいずれか一方を特に用いる必要がある場合にのみそれを明記し、特に明記しないときは、いずれの装置を用いてイオンの照射を行っても良いこととする。40

#### 【0072】

イオンドーピング装置を用いる場合のイオンの照射工程は、例えば、以下の条件で行うことができる。

- ・ 加速電圧 10kV以上100kV以下(好ましくは30kV以上80kV以下)

- ・ ドーズ量  $1 \times 10^{16} / \text{cm}^2$  以上  $4 \times 10^{16} / \text{cm}^2$  以下

- ・ ビーム電流密度  $2 \mu\text{A} / \text{cm}^2$  以上(好ましくは $5 \mu\text{A} / \text{cm}^2$  以上、より好ましくは $10 \mu\text{A} / \text{cm}^2$  以上)

## 【0073】

イオンドーピング装置を用いる場合、イオンの照射工程のソースガスには水素を含むガスを用いることができる。該ガスを用いることによりイオン種として $H^+$ 、 $H_2^+$ 、 $H_3^+$ を生成することができる。水素ガスをソースガスとして用いる場合には、 $H_3^+$ を多く照射することが好ましい。具体的には、イオンビーム140に、 $H^+$ 、 $H_2^+$ 、 $H_3^+$ の総量に対して $H_3^+$ イオンが70%以上含まれるようにすることが好ましい。また、 $H_3^+$ イオンの割合を80%以上とすることがより好ましい。このように $H_3^+$ の割合を高めておくことで、損傷領域114に $1 \times 10^{20}$ atoms/cm<sup>3</sup>以上の濃度で水素を含ませることが可能である。これにより、損傷領域114からの分離が容易になる。また、 $H_3^+$ イオンを多く照射することで、 $H^+$ 、 $H_2^+$ を照射するよりもイオンの照射効率が向上する。つまり、イオン照射にかかる時間を短縮することができる。また、 $H_3^+$ を用いることで、イオンの平均侵入深さを浅くすることができるため、損傷領域114を浅い領域に形成することが可能になる。

## 【0074】

イオン注入装置を用いる場合には、質量分離により、 $H_3^+$ イオンが照射されるようになることが好ましい。もちろん、 $H^+$ や $H_2^+$ を照射してもよい。ただし、イオン注入装置を用いる場合には、イオン種を選択して照射するため、イオンドーピング装置を用いる場合と比較して、イオン照射の効率が低下する場合がある。

## 【0075】

イオン照射工程のソースガスには水素を含むガスの他に、ヘリウムやアルゴンなどの希ガス、フッ素ガスや塩素ガスに代表されるハロゲンガス、フッ素化合物ガス（例えば、BF<sub>3</sub>）などのハロゲン化合物ガスから選ばれた一種または複数種類のガスを用いることができる。ソースガスにヘリウムを用いる場合は、質量分離を行わないことで、He<sup>+</sup>イオンの割合が高いイオンビーム140を作り出すことができる。このようなイオンビーム140を用いることで、損傷領域114を効率よく形成することができる。

## 【0076】

また、複数回のイオン照射工程を行うことで、損傷領域114を形成することもできる。この場合、イオン照射工程毎にソースガスを異なっても良いし、同じソースガスを用いてもよい。例えば、ソースガスとして希ガスを用いてイオン照射を行った後、水素を含むガスをソースガスとして用いてイオン照射を行うことができる。また、初めにハロゲンガス又はハロゲン化合物ガスを用いてイオン照射を行い、次に、水素ガスを含むガスを用いてイオン照射を行うこともできる。

## 【0077】

上記の損傷領域114を形成した後、絶縁層112を除去し、後の配線層となる導電層116を形成する（図5（C）参照）。導電層116は、CVD法やスパッタリング法等により形成することができる。具体的には、アルミニウム、タンゲステン、チタン、タンタル、モリブデン、ニッケル、クロム、ニオブ、白金、銅、金、銀、マンガン、ネオジム、炭素、珪素等の材料を用いることができる。また、上記材料を主成分とする合金を用いても良いし、上記材料を含む化合物を用いても良い。導電層116は、単層構造としても良いし、積層構造としても良い。

## 【0078】

その後、導電層116を所定の形状に加工（パターニング）することで、配線層118を形成する（図5（D）参照）。なお、導電層116及び配線層118の作製工程については、ゲート電極206及びゲート電極208並びに配線層232及び配線層234の作製工程を参照しても良い。

## 【0079】

次に、配線層118を覆うように絶縁層120を形成する（図5（E）参照）。絶縁層120を構成する材料としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化ゲルマニウム、窒化ゲルマニウム、酸化窒化ゲルマニウム、窒化酸化ゲルマニウムなどの、珪素またはゲルマニウムを組成に含む絶縁材料を挙げることができる。また、酸化ア

ルミニウム、酸化タンタル、酸化ハフニウムなどの金属の酸化物、窒化アルミニウムなどの金属の窒化物、酸化窒化アルミニウムなどの金属の酸化窒化物、窒化酸化アルミニウムなどの金属の窒化酸化物を挙げることができる。絶縁層120の形成方法としては、CVD法、スパッタ法などがある。

#### 【0080】

その後、絶縁層120の表面を平坦化した絶縁層122を形成する(図5(F)参照)。後の接合に係る層を平坦に形成するためには、絶縁層120の平坦化を行うことが好ましい。平坦化方法の一例としては、エッチング処理(エッチバック処理)を挙げができる。該エッチング処理は、ドライエッチング又はウェットエッチングのいずれか一方を用いて行っても良いし、双方を組み合わせて用いても良い。また、上述のエッチング処理に加えて、研磨(CMPなど)による平坦化を施すこともできる。もちろん、研磨のみを単独で用いても良い。なお、本実施の形態においては、配線層118の表面と絶縁層122の表面が同一平面上に存在する構成を示しているが、開示する発明がこれに限定されるものではない。例えば、配線層118が絶縁層122に覆われる構成であっても良い。

10

#### 【0081】

次に、絶縁層122上に、絶縁層124及び絶縁層126を形成する(図5(G)参照)。絶縁層124は、不純物元素の半導体層への侵入を抑制できる材料で形成することが好ましい。このような材料としては、例えば、窒化珪素、窒化酸化珪素、窒化アルミニウム、窒化酸化アルミニウムなどを挙げができる。もちろん、酸化珪素、酸化窒化珪素、その他の絶縁材料を用いても良い。

20

#### 【0082】

絶縁層126は、貼り合わせにおける接合を形成する層であるから、その表面は、高い平坦性を有することが好ましい。このような絶縁層126としては、例えば、有機シランガスを用いて化学気相成長法により形成される酸化珪素膜を用いることができる。また、窒化珪素膜を用いても良い。

#### 【0083】

なお、本実施の形態においては、絶縁層122上の絶縁層を二層構造としたが、開示する発明はこれに限定されない。単層構造としても良いし、三層以上の積層構造としても良い。

#### 【0084】

30

以上により、半導体基板の製造に用いられる単結晶半導体基板が得られる。

#### 【0085】

##### (実施の形態2)

本実施の形態では、単結晶半導体基板の加工方法の別の一例について説明する。なお、本実施の形態における単結晶半導体基板の加工方法は、実施の形態1において図5を参照して説明した単結晶半導体基板の加工方法と共通する部分が多い。このため、本実施の形態においては、実施の形態1と相違する部分についてのみ説明することとする。

#### 【0086】

単結晶半導体基板110に損傷領域114を形成するまでの工程(図6(A)、(B)参照)は実施の形態1と同様であるから、ここでは省略することとする。

40

#### 【0087】

損傷領域114を形成した後、絶縁層112を除去し、新たに絶縁層120を形成する(図6(C)参照)。ここで、絶縁層112を除去するのは、イオン照射の際に絶縁層112が損傷する可能性が高いためである。なお、絶縁層112の損傷が問題とならない場合には絶縁層112を除去する必要はない。この場合、絶縁層112上に新たに絶縁層120を形成しても良いし、絶縁層120を形成せずに絶縁層112のみを用いる構成としても良い。

#### 【0088】

絶縁層120を構成する材料としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化ゲルマニウム、窒化ゲルマニウム、酸化窒化ゲルマニウム、窒化酸化ゲルマニ

50

ウムなどの、珪素またはゲルマニウムを組成に含む絶縁材料を挙げることができる。また、酸化アルミニウム、酸化タンタル、酸化ハフニウムなどの金属の酸化物、窒化アルミニウムなどの金属の窒化物、酸化窒化アルミニウムなどの金属の酸化窒化物、窒化酸化アルミニウムなどの金属の窒化酸化物を用いてもよい。絶縁層120の形成方法としては、CVD法、スパッタ法などがある。

#### 【0089】

次に、絶縁層120を所望の形状にパターニングし、溝（開口）が形成された絶縁層122を形成する（図6（D）参照）。該溝は、後に配線層が形成される領域となるため、その深さは、少なくとも一部の領域で単結晶半導体基板にまで到達する深さである必要がある。

10

#### 【0090】

その後、配線層となる導電層116を形成する（図6（E）参照）。導電層116は、CVD法やスパッタリング法等により形成することができる。具体的には、アルミニウム、タンゲステン、チタン、タンタル、モリブデン、ニッケル、クロム、ニオブ、白金、銅、金、銀、マンガン、ネオジム、炭素、珪素等の材料を用いることができる。また、上記材料を主成分とする合金を用いても良いし、上記材料を含む化合物を用いても良い。導電層116は、単層構造としても良いし、積層構造としても良い。

#### 【0091】

その後、導電層116の表面を平坦化すると共に、導電層116を分離して、配線層118を形成する（図6（F）参照）。具体的には、絶縁層122の表面が露出するまで導電層116を研磨する。これにより、導電層116を分離し、絶縁層122の溝に配線層118を形成することができる。平坦化工程の別の一例としては、エッチング処理（エッチバック処理）を挙げることができる。該エッチング処理は、ドライエッチング又はウエットエッチングのいずれか一方を用いて行っても良いし、双方を組み合わせて用いても良い。また、上述のエッチング処理に加えて、CMPによる平坦化を施すこともできる。

20

#### 【0092】

絶縁層124及び絶縁層126を形成する工程（図6（G）参照）については、実施の形態と同様であるからここでは省略する。以上により、SOI基板の製造に用いられる単結晶半導体基板が得られる。

#### 【0093】

30

なお、本実施の形態は上記実施の形態と適宜組み合わせて用いることができる。

#### 【0094】

##### （実施の形態3）

本実施の形態では、上記実施の形態と異なる半導体装置及びその作製方法に関して図7を参照して説明する。

#### 【0095】

まず、上記図1に示すように半導体基板を作製する（図7（A）参照）。ここでは、配線層118a、118bと第1の電極118cが単結晶半導体層132の下部に設けられている。配線層118a、118bと第1の電極118cは同一の工程で設けることができる。

40

#### 【0096】

次に、単結晶半導体層132にエッチング処理を施すことにより、単結晶半導体層132を島状に分離して単結晶半導体層200及び単結晶半導体層202を形成する（図7（B）参照）。

#### 【0097】

ここでは、配線層118a、118b上に存在する単結晶半導体層132の一部を除去することにより配線層118a、118bの表面の一部を露出させ、第1の電極118c上に存在する単結晶半導体層132を除去することにより第1の電極118cを露出させる。なお、配線層118a、118bは、露出させた領域以外においては、単結晶半導体層との接続が保たれている。本実施の形態においては、配線層118a及び配線層118

50

b は単結晶半導体層 202 と接触しており、また、一部の領域においてその表面が露出した構成となっているが、開示する発明がこれに限定されるものではない。

#### 【0098】

次に、単結晶半導体層 200 と単結晶半導体層 202 を覆うように、ゲート絶縁層 204 を形成する（図 7（C）参照）。なお、第 1 の電極 118c 上にもゲート絶縁層 204 が形成される。ここでは、プラズマ CVD 法を用いて、酸化珪素膜を単層で形成する。その他にも、酸化窒化珪素、窒化酸化珪素、窒化珪素、酸化ハフニウム、酸化アルミニウム、酸化タンタル等を含む膜を、単層構造又は積層構造で形成することによりゲート絶縁層 204 としても良い。

#### 【0099】

次に、ゲート絶縁層 204 上に導電層を形成した後、該導電層を所定の形状に加工（パターニング）することで、単結晶半導体層 200 と単結晶半導体層 202 の上方にゲート絶縁層 204 を介してゲート電極 206 及びゲート電極 208 を形成し、第 1 の電極 118c 上にゲート絶縁層 204 を介して第 2 の電極 209 を形成する（図 7（D）参照）。

#### 【0100】

また、第 1 の電極 118c、ゲート絶縁層 204 及び第 2 の電極 209 の積層構造により容量素子 211 を設けることができる。容量素子 211 は、容量素子を構成する絶縁層として膜厚が小さいゲート絶縁層 204 を用いることができるため、トランジスタ上に形成される絶縁層を用いる場合と比較して、サイズを小さくしても同等の容量を形成できる。

#### 【0101】

導電層の形成には CVD 法、スパッタリング法等を用いることができる。導電層は、タンタル、タンゲステン、チタン、モリブデン、アルミニウム、銅、クロム、ニオブ等の材料を用いて形成することができる。また、上記金属を主成分とする合金材料を用いても良いし、上記金属を含む化合物を用いても良い。または、半導体層に導電性を付与する不純物元素をドーピングした多結晶珪素などを用いて形成しても良い。

#### 【0102】

その後、図 3 及び 4 と同様の工程を行うことによって、複数のトランジスタ（n チャネル型トランジスタ 250 及び p チャネル型トランジスタ 252）及び容量素子 211 を有する半導体装置を作製することができる（図 7（E）参照）。なお、本実施の形態では、サイドウォールを設けない構成を示したが、上記実施の形態 1 で示したようにサイドウォールを設けた構成としてもよい。

#### 【0103】

本実施の形態では、トランジスタの下層に配線層だけでなく容量素子を構成する第 1 の電極を設け、当該第 1 の電極上に形成される膜厚が小さいゲート絶縁層を、容量素子を構成する絶縁膜とすることによって、容量素子のサイズを縮小し、半導体装置をより微細化することができる。

#### 【0104】

なお、本実施の形態は上記実施の形態と適宜組み合わせて用いることができる。

#### 【0105】

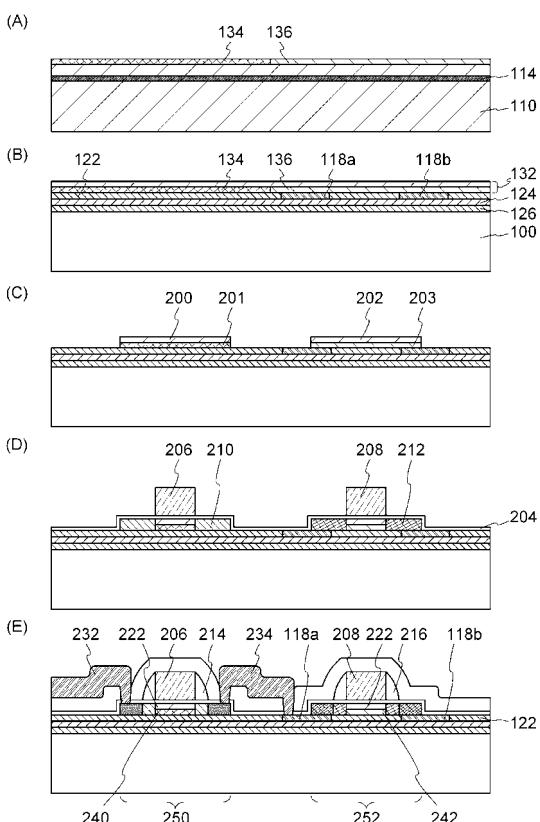

##### （実施の形態 4）

本実施の形態では、上記実施の形態と異なる半導体装置及びその作製方法に関して図 8 を参照して説明する。

#### 【0106】

はじめに、図 5（又は図 6）に示すように単結晶半導体基板を加工するが、本実施の形態では、図 5（又は図 6）における導電層 116 を形成する前に、後のトランジスタのしきい値電圧を制御するための不純物を添加する。本実施の形態では、n チャネル型トランジスタの形成領域には選択的に p 型を付与する不純物を添加し、p チャネル型トランジスタの形成領域には選択的に n 型を付与する不純物を添加することとする。これにより、単結晶半導体基板 110 には不純物が低濃度に添加されるが、その濃度は単結晶半導体基板

10

20

30

40

50

110の表面付近で高くなるようになる。すなわち、単結晶半導体基板110の表面付近に、不純物濃度が相対的に高い領域134( p型不純物領域)及び領域136( n型不純物領域)が形成されるように不純物を添加する(図8( A )参照)。なお、領域134及び領域136はあくまでも模式図であり、実際の不純物濃度は連続的に変化していることは言うまでもない。

#### 【0107】

なお、上記の不純物の添加は、損傷領域114の形成前に行っても良いし、損傷領域114の形成後に行っても良い。また、上記不純物としては、硼素、アルミニウム、ガリウムなどのp型を付与する不純物、又は、リン、砒素などのn型を付与する不純物を用いればよい。

10

#### 【0108】

次に、図5(又は図6)及び図1に示す方法を用いて、ベース基板100上に単結晶半導体層132を有する構成のSOI基板を作製する(図8( B )参照)。これにより、領域134及び領域136が絶縁層122、配線層118a、又は配線層118bと接する構成のSOI基板が形成される。

#### 【0109】

その後、図2乃至4に示す方法を用いてトランジスタを形成する(図8( C )、( D )、( E )参照)。このようにして形成されたnチャネル型トランジスタ250及びpチャネル型トランジスタ252は、そのチャネル形成領域222及びチャネル形成領域228のゲート絶縁層204側には、しきい値制御用の不純物が低濃度に添加されており、チャネル形成領域222及びチャネル形成領域228の絶縁層122側には、相対的に高濃度に不純物が添加された領域240及び領域242を有する。

20

#### 【0110】

以上により、本実施の形態の半導体装置を作製することができる。本実施の形態においては、トランジスタのチャネル形成領域のゲート絶縁層側には、トランジスタのキャリアとは反対の極性を与える不純物が低濃度に添加され、トランジスタのしきい値を制御している。また、チャネル形成領域の絶縁層122側には、トランジスタのキャリアとは反対の極性を与える不純物が相対的に高濃度に添加されている。これにより、ゲート絶縁層204側にチャネルが形成されやすくなり、絶縁層122側にはチャネルが形成されにくくなるため、バックチャネルの発生を抑制し、オフ電流(リーク電流とも言う)を低減することが可能である。特に、トランジスタの微細化が進むにつれ、いわゆる短チャネル効果によりオフ電流の問題が深刻になるが、本実施の形態の如き構成を採用することにより、微細化を進行させてもオフ電流を低減することが可能であるため、優れた特性の半導体装置を提供することができる。

30

#### 【0111】

なお、本実施の形態は上記実施の形態と適宜組み合わせて用いることができる。

#### 【0112】

##### (実施の形態5)

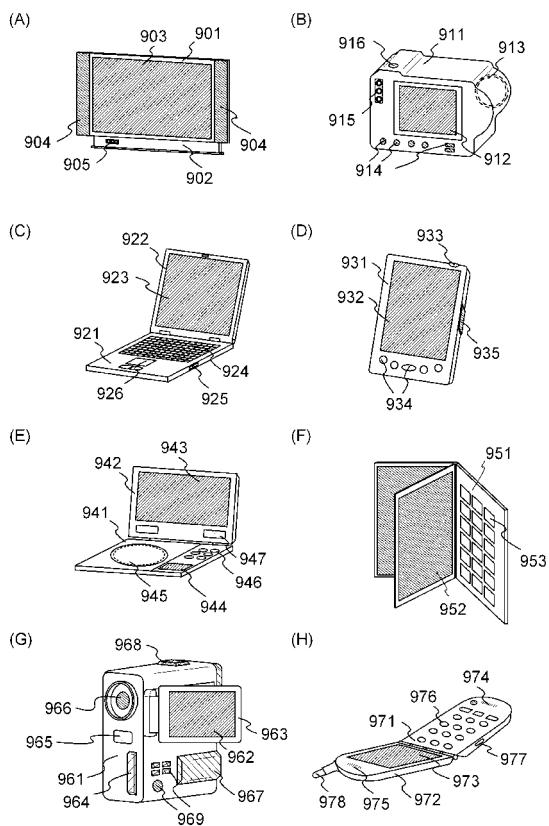

本実施の形態では、半導体装置のうち、特に表示装置を用いた電子機器について、図9及び10を参照して説明する。

40

#### 【0113】

開示する発明の半導体装置(特に表示装置)を用いて作製される電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc (DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。

#### 【0114】

図9( A )はテレビ受像器又はパーソナルコンピュータのモニタである。筐体901、

50

支持台 902、表示部 903、スピーカー部 904、ビデオ入力端子 905 等を含む。表示部 903 には、開示する発明の半導体装置が用いられている。開示する発明により、配線の自由度を向上させ、集積度を向上させた半導体装置を製造することができるため、高性能なテレビ受像器又はパーソナルコンピュータのモニタを提供することができる。

#### 【0115】

図 9 (B) はデジタルカメラである。本体 911 の正面部分には受像部 913 が設けられており、本体 911 の上面部分にはシャッターボタン 916 が設けられている。また、本体 911 の背面部分には、表示部 912、操作キー 914、及び外部接続ポート 915 が設けられている。表示部 912 には、開示する発明の半導体装置が用いられている。開示する発明により、高性能なデジタルカメラを提供することができる。

10

#### 【0116】

図 9 (C) はノート型パーソナルコンピュータである。本体 921 には、キーボード 924、外部接続ポート 925、ポインティングデバイス 926 が設けられている。また、本体 921 には、表示部 923 を有する筐体 922 が取り付けられている。表示部 923 には、開示する発明の半導体装置が用いられている。開示する発明により、高性能なノート型パーソナルコンピュータを提供することができる。

#### 【0117】

図 9 (D) はモバイルコンピュータであり、本体 931、表示部 932、スイッチ 933、操作キー 934、赤外線ポート 935 等を含む。表示部 932 にはアクティブマトリクス表示装置が設けられている。表示部 932 には、開示する発明の半導体装置が用いられている。開示する発明により、高性能なモバイルコンピュータを提供することができる。

20

#### 【0118】

図 9 (E) は画像再生装置である。本体 941 には、表示部 944、記録媒体読み込み部 945 及び操作キー 946 が設けられている。また、本体 941 には、スピーカー部 947 及び表示部 943 それぞれを有する筐体 942 が取り付けられている。表示部 943 及び表示部 944 それぞれには、開示する発明の半導体装置が用いられている。開示する発明により、高性能な画像再生装置を提供することができる。

#### 【0119】

図 9 (F) は電子書籍である。本体 951 には操作キー 953 が設けられている。また、本体 951 には複数の表示部 952 が取り付けられている。表示部 952 には、開示する発明の半導体装置が用いられている。開示する発明により、高性能な電子書籍を提供することができる。

30

#### 【0120】

図 9 (G) はビデオカメラであり、本体 961 には外部接続ポート 964、リモコン受信部 965、受像部 966、バッテリー 967、音声入力部 968、操作キー 969 が設けられている、また、本体 961 には、表示部 962 を有する筐体 963 が取り付けられている。表示部 962 には、開示する発明の半導体装置が用いられている。開示する発明により、高性能なビデオカメラを提供することができる。

#### 【0121】

図 9 (H) は携帯電話であり、本体 971、筐体 972、表示部 973、音声入力部 974、音声出力部 975、操作キー 976、外部接続ポート 977、アンテナ 978 等を含む。表示部 973 には、開示する発明の半導体装置が用いられている。開示する発明により、高性能な携帯電話を提供することができる。

40

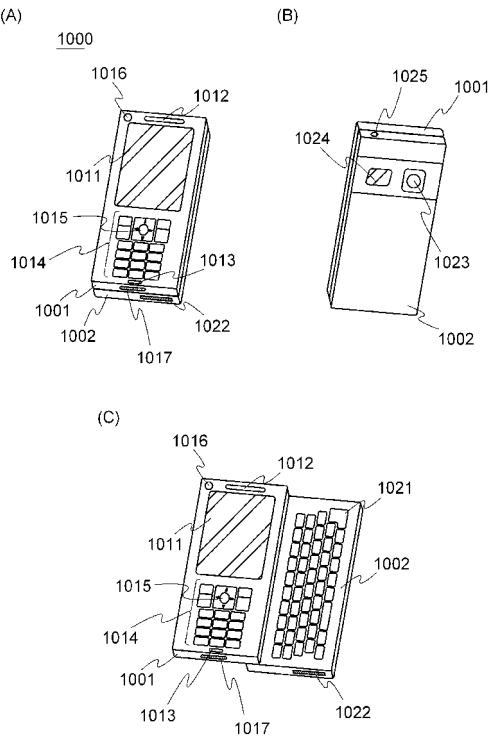

#### 【0122】

図 10 は、電話としての機能と、情報端末としての機能を併せ持った携帯電子機器 100 の構成の一例である。ここで、図 10 (A) は正面図、図 10 (B) は背面図、図 10 (C) は展開図である。携帯電子機器 1000 は、電話と情報端末の双方の機能を備えており、音声通話以外にも様々なデータ処理が可能な、いわゆるスマートフォンと呼ばれる電子機器である。

50

**【 0 1 2 3 】**

携帯電子機器 1000 は、筐体 1001 及び筐体 1002 で構成されている。筐体 1001 は、表示部 1011、スピーカー 1012、マイクロフォン 1013、操作キー 1014、ポインティングデバイス 1015、カメラ用レンズ 1016、外部接続端子 1017 等を備え、筐体 1002 は、キーボード 1021、外部メモリスロット 1022、カメラ用レンズ 1023、ライト 1024、イヤフォン端子 1025 等を備えている。また、アンテナは筐体 1001 内部に内蔵されている。上記構成に加えて、非接触 IC チップ、小型記録装置等を内蔵していてもよい。

**【 0 1 2 4 】**

表示部 1011 には、開示する発明の半導体装置が組み込まれている。なお、表示部 1011 に表示される映像（及びその表示方向）は、携帯電子機器 1000 の使用形態に応じて様々なに変化する。また、表示部 1011 と同一面にカメラ用レンズ 1016 を備えているため、映像を伴う音声通話（いわゆるテレビ電話）が可能である。なお、スピーカー 1012 及びマイクロフォン 1013 は音声通話に限らず、録音、再生等に用いることが可能である。カメラ用レンズ 1023（及び、ライト 1024）を用いて静止画及び動画の撮影を行う場合には、表示部 1011 はファインダーとして用いられることになる。操作キー 1014 は、電話の発信・着信、電子メール等の簡単な情報入力、画面のスクロール、カーソル移動等に用いられる。

**【 0 1 2 5 】**

重なり合った筐体 1001 と筐体 1002 は、スライドし、図 10 (C) のように展開し、情報端末として使用できる。この場合には、キーボード 1021、ポインティングデバイス 1015 を用いた円滑な操作が可能である。外部接続端子 1017 は AC アダプタや USB ケーブル等の各種ケーブルと接続可能であり、充電やコンピュータ等とのデータ通信を可能にしている。また、外部メモリスロット 1022 に記録媒体を挿入し、より大容量のデータの保存及び移動に対応できる。上記機能に加えて、赤外線などの電磁波を用いた無線通信機能や、テレビ受信機能等を有していても良い。開示する発明により、高性能な携帯電子機器を提供することができる。

**【 0 1 2 6 】**

以上の様に、開示する発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。なお、本実施の形態は、上記実施の形態と適宜組み合わせて用いることができる。

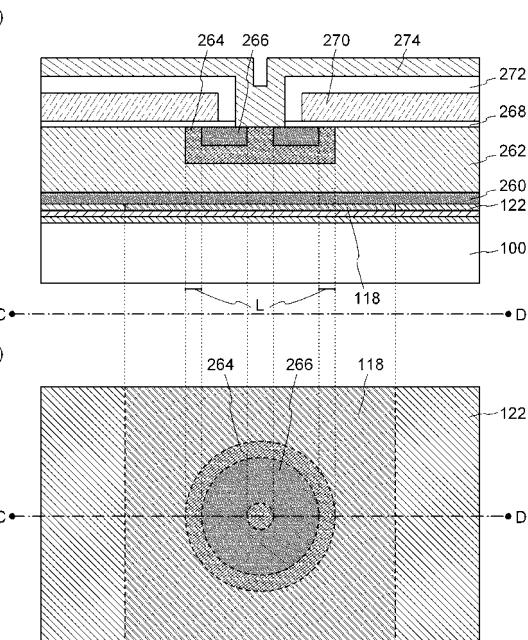

**【 0 1 2 7 】****( 実施の形態 6 )**

本実施の形態では、耐圧を考慮したトランジスタの構成について図 11 と図 12 を用いて説明する。はじめに、図 1、5、6 などに示す方法を用いて SOI 基板を作製する（図 11 (A) 参照）。該 SOI 基板は、ベース基板 100 上に絶縁層 126、絶縁層 124、絶縁層 122 及び配線層 118、単結晶半導体層 132 を順に積層した構造を有している。なお、本実施の形態においては、配線層 118 を部分的に設ける構成としたが、開示する発明はこれに限らず、絶縁層 124 上の全面に配線層 118 を有する構成としても良い。本実施の形態に示すトランジスタにおいて、配線層 118 はドレイン配線（又はソース配線）として機能する。

**【 0 1 2 8 】**

次に、単結晶半導体層 132 に一導電型を付与する不純物元素を添加して後のドレイン領域（又はソース領域）となる半導体層 260 を形成する。本実施の形態では、n 型を付与する不純物元素（例えはリンやヒ素など）を高濃度に添加する。その後、半導体層 260 をシード層としてエピタキシャル成長を利用することにより、当該半導体層 260 上に半導体層 262 を形成する。半導体層 262 は、例えは、CVD 法により気相成長させながら成膜することより形成することができる。また、単結晶半導体層 132 上に非晶質半導体層を形成した後、熱処理（例えは、RTA (Rapid Thermal Anneal) 法による 500 乃至 800 、3 秒乃至 180 秒の熱処理）を行い固相成長によ

10

20

30

40

50

り結晶化させて形成してもよい(図11(B)参照)。

**【0129】**

半導体層262は半導体層260と同様の材料を用いて形成することができ、例えば、単結晶シリコンでなる半導体層260上に、エピタキシャル成長により単結晶シリコンでなる半導体層262を形成することができる。なお、半導体層262の結晶性については、作製の条件によって様々に異ならせることが可能である。このため、半導体層262の結晶性については、特に限定されないものとする。また、半導体層262の厚さは例えば1μm以上とすることができますが、この値は要求される耐圧によって適宜変更することができる。また、半導体層262は低濃度のn型不純物が含有されるように形成する。

**【0130】**

なお、本実施の形態においては、SOI基板を作製した後にn型を付与する不純物元素を添加する構成としたが、開示する発明はこれに限定されない。例えば、n型の単結晶半導体基板を用いてSOI基板を作製することで、不純物元素を添加する工程を省略することもできる。また、半導体層260上にエピタキシャル成長によって半導体層262を形成する構成としたが、単結晶半導体層132を厚く形成することにより、半導体層262の形成を省略する構成としても良い。この場合には、単結晶半導体層132の下部が高濃度になるように、また、単結晶半導体層132の上部が低濃度になるようにn型を付与する不純物元素を添加すればよい。

**【0131】**

その後、半導体層262にp型を付与する不純物元素(例えばボロンなど)及びn型を付与する不純物元素を選択的に添加して、p型領域264及びn型領域266を形成する(図11(C)参照)。ここで、p型領域264の一部は後のチャネル形成領域となる領域であり、n型領域266は後のソース領域(又はドレイン領域)となる領域である。

**【0132】**

p型領域264及びn型領域266を形成した後に、半導体層262上にゲート絶縁層268を形成し、当該ゲート絶縁層268上にゲート電極270を選択的に形成する。ここで、ゲート電極270は、少なくともその一部がn型領域266と重なりを有する構成とすることが好ましい。これにより電界の集中が緩和されるため、耐圧を一層向上することができる。続いて、ゲート電極270を覆うように絶縁層272を形成した後に、当該絶縁層272及びゲート絶縁層268に開口を形成し、n型領域266と電気的に接続された配線層274を形成する(図11(D)参照)。なお、配線層274はソース配線(又はドレイン配線)として機能する。

**【0133】**

以上により、耐圧の高いトランジスタを得ることができる。図12に、本実施の形態におけるトランジスタの平面図と断面図の関係を示す。図12(A)は本実施の形態におけるトランジスタの断面図であり、図12(B)は平面図である。ここで、図12(A)は、図12(B)のC-Dにおける断面に対応している。なお、図12(B)では簡単のため、半導体層262、ゲート絶縁層268、ゲート電極270、絶縁層272、配線層274など、構成要素の一部を省略している。例えば、トランジスタの下方に設けられた配線層118が、トランジスタの上方に設けられた配線層と電気的に接続する構成とすることができる。

**【0134】**

本実施の形態においては、p型領域264及びn型領域266を円形としている(図12(B)参照)が、開示する発明はこれに限定されない。矩形としても良いし、その他の形状であっても良い。なお、本実施の形態にて示したように、p型領域264及びn型領域266を円形にすることで、チャネル長Lを一定にすることができます。これにより、チャネル形成領域における電界の集中を緩和することができるため、トランジスタの耐圧向上につながる。なお、本実施の形態においては半導体層260と接する配線層118を有しているため、大電流を伴うトランジスタの廃熱の効率を向上するという効果も得られる。

## 【0135】

本実施の形態は、上記実施の形態と適宜組み合わせて用いることができる。

## 【図面の簡単な説明】

## 【0136】

- 【図1】半導体基板の製造方法について示す図である。

- 【図2】半導体装置の製造方法について示す図である。

- 【図3】半導体装置の製造方法について示す図である。

- 【図4】半導体装置の製造方法について示す図である。

- 【図5】半導体基板の加工方法について示す図である。

- 【図6】半導体基板の加工方法について示す図である。

- 【図7】半導体装置の製造方法について示す図である。

- 【図8】半導体装置の製造方法について示す図である。

- 【図9】半導体装置を用いた電子機器を示す図である。

- 【図10】半導体装置を用いた電子機器を示す図である。

- 【図11】半導体装置の製造方法について示す図である。

- 【図12】半導体装置の断面図及び平面図である。

10

## 【符号の説明】

## 【0137】

|       |          |    |

|-------|----------|----|

| 100   | ベース基板    |    |

| 110   | 単結晶半導体基板 | 20 |

| 112   | 絶縁層      |    |

| 114   | 損傷領域     |    |

| 116   | 導電層      |    |

| 118   | 配線層      |    |

| 118 a | 配線層      |    |

| 118 b | 配線層      |    |

| 118 c | 第1の電極    |    |

| 120   | 絶縁層      |    |

| 122   | 絶縁層      |    |

| 124   | 絶縁層      | 30 |

| 126   | 絶縁層      |    |

| 128   | 単結晶半導体層  |    |

| 130   | 単結晶半導体基板 |    |

| 132   | 単結晶半導体層  |    |

| 134   | 領域       |    |

| 136   | 領域       |    |

| 140   | イオンビーム   |    |

| 142   | レーザー光    |    |

| 200   | 単結晶半導体層  |    |

| 202   | 単結晶半導体層  | 40 |

| 204   | ゲート絶縁層   |    |

| 206   | ゲート電極    |    |

| 208   | ゲート電極    |    |

| 209   | 電極       |    |

| 210   | 不純物領域    |    |

| 211   | 容量素子     |    |

| 212   | 不純物領域    |    |

| 214   | サイドウォール  |    |

| 216   | サイドウォール  |    |

| 218   | 高濃度不純物領域 | 50 |

|       |              |    |

|-------|--------------|----|

| 2 2 0 | 低濃度不純物領域     |    |

| 2 2 2 | チャネル形成領域     |    |

| 2 2 4 | 高濃度不純物領域     |    |

| 2 2 6 | 低濃度不純物領域     |    |

| 2 2 8 | チャネル形成領域     |    |

| 2 3 0 | 絶縁層          |    |

| 2 3 2 | 配線層          |    |

| 2 3 4 | 配線層          |    |

| 2 4 0 | 領域           |    |

| 2 4 2 | 領域           | 10 |

| 2 5 0 | nチャネル型トランジスタ |    |

| 2 5 2 | pチャネル型トランジスタ |    |

| 2 6 0 | 半導体層         |    |

| 2 6 2 | 半導体層         |    |

| 2 6 4 | p型領域         |    |

| 2 6 6 | n型領域         |    |

| 2 6 8 | ゲート絶縁層       |    |

| 2 7 0 | ゲート電極        |    |

| 2 7 2 | 絶縁層          |    |

| 2 7 4 | 配線層          | 20 |

| 9 0 1 | 筐体           |    |

| 9 0 2 | 支持台          |    |

| 9 0 3 | 表示部          |    |

| 9 0 4 | スピーカー部       |    |

| 9 0 5 | ビデオ入力端子      |    |

| 9 1 1 | 本体           |    |

| 9 1 2 | 表示部          |    |

| 9 1 3 | 受像部          |    |

| 9 1 4 | 操作キー         |    |

| 9 1 5 | 外部接続ポート      | 30 |

| 9 1 6 | シャッターボタン     |    |

| 9 2 1 | 本体           |    |

| 9 2 2 | 筐体           |    |

| 9 2 3 | 表示部          |    |

| 9 2 4 | キーボード        |    |

| 9 2 5 | 外部接続ポート      |    |

| 9 2 6 | ポインティングデバイス  |    |

| 9 3 1 | 本体           |    |

| 9 3 2 | 表示部          |    |

| 9 3 3 | スイッチ         | 40 |

| 9 3 4 | 操作キー         |    |

| 9 3 5 | 赤外線ポート       |    |

| 9 4 1 | 本体           |    |

| 9 4 2 | 筐体           |    |

| 9 4 3 | 表示部          |    |

| 9 4 4 | 表示部          |    |

| 9 4 5 | 部            |    |

| 9 4 6 | 操作キー         |    |

| 9 4 7 | スピーカー部       |    |

| 9 5 1 | 本体           | 50 |

|         |             |    |

|---------|-------------|----|

| 9 5 2   | 表示部         |    |

| 9 5 3   | 操作キー        |    |

| 9 6 1   | 本体          |    |

| 9 6 2   | 表示部         |    |

| 9 6 3   | 筐体          |    |

| 9 6 4   | 外部接続ポート     |    |

| 9 6 5   | リモコン受信部     |    |

| 9 6 6   | 受像部         |    |

| 9 6 7   | バッテリー       |    |

| 9 6 8   | 音声入力部       | 10 |

| 9 6 9   | 操作キー        |    |

| 9 7 1   | 本体          |    |

| 9 7 2   | 筐体          |    |

| 9 7 3   | 表示部         |    |

| 9 7 4   | 音声入力部       |    |

| 9 7 5   | 音声出力部       |    |

| 9 7 6   | 操作キー        |    |

| 9 7 7   | 外部接続ポート     |    |

| 9 7 8   | アンテナ        |    |

| 1 0 0 0 | 携帯電子機器      | 20 |

| 1 0 0 1 | 筐体          |    |

| 1 0 0 2 | 筐体          |    |

| 1 0 1 1 | 表示部         |    |

| 1 0 1 2 | スピーカー       |    |

| 1 0 1 3 | マイクロフォン     |    |

| 1 0 1 4 | 操作キー        |    |

| 1 0 1 5 | ポインティングデバイス |    |

| 1 0 1 6 | カメラ用レンズ     |    |

| 1 0 1 7 | 外部接続端子      |    |

| 1 0 2 1 | キーボード       | 30 |

| 1 0 2 2 | 外部メモリスロット   |    |

| 1 0 2 3 | カメラ用レンズ     |    |

| 1 0 2 4 | ライト         |    |

| 1 0 2 5 | イヤフォン端子     |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【 図 1 2 】

---

フロントページの続き

| (51)Int.Cl.             | F I              |

|-------------------------|------------------|

| H 01L 21/3205 (2006.01) | H 01L 21/88 Q    |

| H 01L 23/532 (2006.01)  | H 01L 21/88 N    |

| H 01L 21/336 (2006.01)  | H 01L 29/78 627D |

| H 01L 21/02 (2006.01)   | H 01L 27/12 B    |

| H 01L 27/12 (2006.01)   | H 01L 21/20      |

| H 01L 21/20 (2006.01)   | H 01L 29/78 627A |

## (58)調査した分野(Int.Cl., DB名)

H 01L 29 / 786

H 01L 21 / 02

H 01L 21 / 20

H 01L 21 / 3205

H 01L 21 / 336

H 01L 21 / 768

H 01L 23 / 532

H 01L 27 / 12

H 01L 29 / 417

H 01L 29 / 423

H 01L 29 / 49