(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5390310号

(P5390310)

(45) 発行日 平成26年1月15日(2014.1.15)

(24) 登録日 平成25年10月18日(2013.10.18)

|                |                              |

|----------------|------------------------------|

| (51) Int.Cl.   | F 1                          |

| G 06 F 15/78   | (2006.01) G 06 F 15/78 510 E |

| G 06 F 3/00    | (2006.01) G 06 F 15/78 510 B |

| H 03 K 19/0175 | (2006.01) G 06 F 3/00 X      |

| G 11 C 11/401  | (2006.01) H 03 K 19/00 101 J |

|                | G 11 C 11/34 362 Z           |

請求項の数 6 (全 10 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2009-206880 (P2009-206880) |

| (22) 出願日  | 平成21年9月8日(2009.9.8)          |

| (65) 公開番号 | 特開2011-59852 (P2011-59852A)  |

| (43) 公開日  | 平成23年3月24日(2011.3.24)        |

| 審査請求日     | 平成24年2月17日(2012.2.17)        |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地 |

| (74) 代理人  | 100103894<br>弁理士 家入 健                                |

| (72) 発明者  | 光明 雅泰<br>神奈川県川崎市中原区下沼部1753番地<br>NECエレクトロニクス株式会社内     |

| (72) 発明者  | 飯塚 洋一<br>神奈川県川崎市中原区下沼部1753番地<br>NECエレクトロニクス株式会社内     |

|           | 審査官 清木 泰                                             |

最終頁に続く

(54) 【発明の名称】半導体集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

データ送信回路と、

前記データ送信回路から送信されたデータを受信するデータ受信回路と、を備え、

前記データ送信回路は、

前記データを出力するか、出力をハイインピーダンス状態にするか、が切り替わるデータ出力回路と、

データ送信時には前記データを出力し、データ送信後にさらに別のデータを送信する場合には、先のデータ送信後から別のデータ送信開始までのデータ送信間隔に基づいて、当該データ送信間隔の期間中、先のデータ送信時に最後に出力したデータを出力し続けるように、前記データ出力回路に対して制御信号を出力する制御回路と、を備え、前記データ送信間隔は、前記データ送信回路が前記データ受信回路に対してデータ送信のコマンドを出力後さらに別のデータ送信のコマンドを出力するまでの期間に基づいて決定される、半導体集積回路。

## 【請求項 2】

前記制御回路は、前記データ送信回路がデータ送信後にさらに別のデータを送信する場合において、前記データ送信間隔が閾値以下である場合にのみ、当該データ送信間隔の期間中、先のデータ送信時に最後に出力したデータを出力し続けるように、前記データ出力回路に対して前記制御信号を出力する、請求項 1 に記載の半導体集積回路。

## 【請求項 3】

10

20

前記制御回路は、前記データ送信回路がデータ送信後にさらに別のデータを送信する場合において、前記データ送信間隔が前記閾値を超える場合、当該データ送信間隔の期間中、前記データ出力回路の出力をハイインピーダンス状態とするように前記制御信号を出力する、請求項2に記載の半導体集積回路。

**【請求項4】**

前記データ送信間隔は、前記データ送信回路が前記データ受信回路に対してデータ送信のコマンドを出力してからデータ送信を開始するまでのレイテンシに基づいて決定される、請求項1～3の何れか一項に記載の半導体集積回路。

**【請求項5】**

前記データ送信間隔は、前記データ送信回路が送信するデータのバースト長に基づいて決定される、請求項1～4の何れか一項に記載の半導体集積回路。

10

**【請求項6】**

前記データ出力回路は、

Pチャネル及びNチャネルMOSトランジスタからなるインバータを有し、

前記データ出力回路の出力をハイインピーダンス状態にする場合には、Pチャネル及びNチャネルMOSトランジスタがオフするように制御され、前記データ出力回路から前記データを出力する場合には、当該データに応じてPチャネル及びNチャネルMOSトランジスタのいずれか一方がオンし他方がオフするように制御される、請求項1～5のいずれか一項に記載の半導体集積回路。

**【発明の詳細な説明】**

20

**【技術分野】**

**【0001】**

本発明は半導体集積回路に関し、特に電源ノイズ低減に関する。

**【背景技術】**

**【0002】**

半導体集積回路において、データ送信回路とデータ受信回路との間のデータ転送に用いられる各信号線上に電源ノイズが発生し、両回路間のデータ転送が正しく行われないという問題がある。

**【0003】**

そのため、データ受信回路がデータを受信するために用いられる信号線上にはODT(On Die Termination)等の電源ノイズを低減する対策が施されている(非特許文献1)。

30

**【先行技術文献】**

**【非特許文献】**

**【0004】**

**【非特許文献1】JEDEC STANDARD, DDR2 SDRAM SPECIFICATION JESD79-2E (Revision of JESD79-2D), April 2008, JEDEC SOLID STATE TECHNOLOGY ASSOCIATION**

**【発明の概要】**

40

**【発明が解決しようとする課題】**

**【0005】**

従来技術では、ODT機能のようにデータ受信回路が受ける電源ノイズを低減する対策は施されているが、データ送信回路が受ける電源ノイズを低減する対策は施されていない。通常、データ送信回路は、データ送信用にスリーステートバッファ等のデータ出力回路を有する。データ送信回路は、制御信号に基づいてデータ出力回路が送信データを出力するか否かを制御する。つまり、データ送信回路は、データ出力回路が送信データを出力するか、出力をハイインピーダンス状態(HiZ)にするか、を制御する。

**【0006】**

しかし、データ送信回路がデータ出力回路の出力をHiZにした場合、それまで電源電

50

圧が供給されていた信号線上に急に電源電圧が供給されなくなるため、電源ノイズが発生する。この電源ノイズが収束する前に、データ送信回路がさらに別のデータを送信するためにデータ出力回路の出力をH i Zからデータ送信状態に切り替えた場合、当該別のデータがこの電源ノイズの影響を受ける。そのため従来技術では、データの送信を精度良く行うことができないという問題があった。

【課題を解決するための手段】

【0007】

本発明にかかる半導体集積回路は、データ送信回路と、前記データ送信回路から送信されたデータを受信するデータ受信回路と、を備え、前記データ送信回路は、前記データを出力するか、出力をハイインピーダンス状態にするか、が切り替わるデータ出力回路と、前記データ出力回路において、データ送信時には前記データを出し、データ送信後にさらに別のデータを送信する場合には、先の前記データ送信後から所定の期間、先の前記データ送信時に最後に出力したデータを出し続けるように、前記データ出力回路に対して制御信号を出力する制御回路と、を備える。

10

【0008】

上述のような回路構成により、電源ノイズを低減することができるため、データの送信を精度良く行うことができる。

【発明の効果】

【0009】

本発明により、データの送信を精度良く行うことが可能な半導体集積回路を提供することができる。

20

【図面の簡単な説明】

【0010】

【図1】本発明の実施の形態1にかかる半導体集積回路を示す図である。

【図2】本発明の実施の形態1にかかる半導体集積回路を示す図である。

【図3】本発明の実施の形態1にかかる半導体集積回路の動作を示すタイミングチャートである。

【発明を実施するための形態】

【0011】

以下では、本発明を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。説明の明確化のため、必要に応じて重複説明は省略される。

30

【0012】

実施の形態1

本発明の実施の形態1について図面を参照して説明する。なお本発明は、データ送信回路と、当該データ送信回路からのデータを受信するデータ受信回路と、を備え、制御信号によってデータ送信回路からのデータ送信が制御される回路に対して適用可能である。本実施の形態では、S o C ( S y s t e m O n C h i p ) 回路と S D R A M ( S y n c h r o n o u s D y n a m i c R a n d o m A c c e s s M e m o r y ) 回路とを備え、両回路間で双方向にデータ転送が行われる信号線（以下、単に双方向用信号線と称す）を介してデータ転送が行われる場合を例に説明する。

40

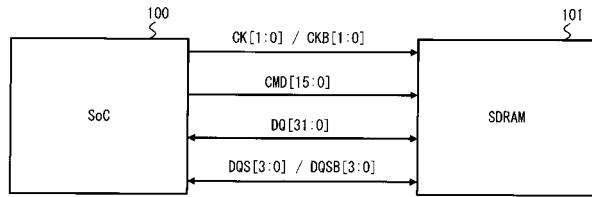

【0013】

図1は、本発明の実施の形態1にかかる半導体集積回路である。図1に示す回路は、S o C回路（データ送信回路）100とS D R A M回路（データ受信回路）101とを備える。これら両回路間のデータ転送は、D D R ( D o u b l e d a t a r a t e ) 規格によって行われている。

【0014】

まず、本実施の形態1の回路構成について説明する。S o C回路100は、2ビット幅のクロックC Kと、クロックC Kの差動信号である2ビット幅のクロックC K Bと、をS D R A M回路101に対して出力する。また、S o C回路100は、S D R A M回路101の各アドレスに対するコマンドが含まれる16ビット幅の制御信号C M Dを、当該S D

50

R A M回路101に対して出力する。なお、S D R A M回路101は、クロックC K / C K Bに同期して制御信号C M Dを取り込む。

【0015】

また、S o C回路100とS D R A M回路101との間では、32ビット幅のデータD Qと、4ビット幅のストローブ信号D Q S及びその差動信号D Q S Bと、が双方向に送受信される。なお、データ受信側となる受信側回路は、ストローブ信号D Q S / D Q S Bに同期して受信データD Qを取り込む。なお便宜上、上記の各信号名は、同時にそれぞれ信号線名も表すものとする。

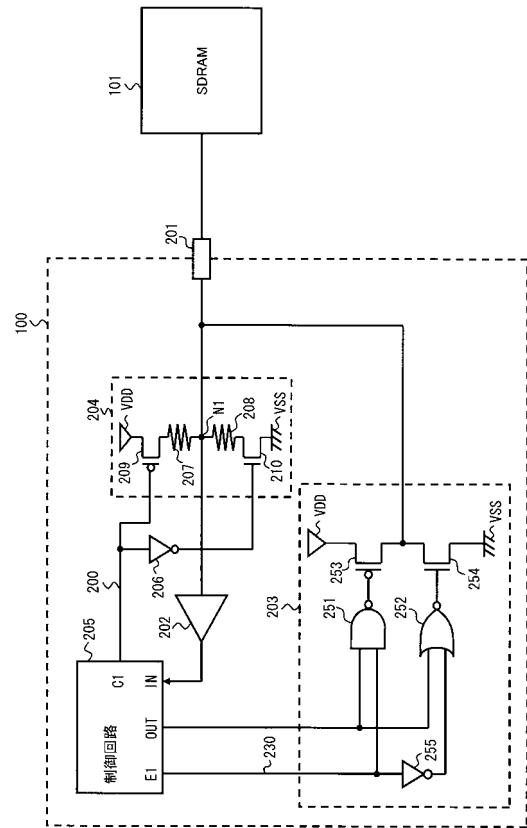

【0016】

図2は、図1の回路のうち、1ビットの双方向用信号線（ストローブ信号線D Q S [ 3 : 0 ] / D Q S B [ 3 : 0 ]，データ信号線D Q [ 31 : 0 ]のうちいずれか1ビットの信号線）とそれに対応する周辺回路のみを図示している。ここでは、この1ビットの双方向用信号線がデータ信号線D Q [ 0 ]である場合を例に説明する。データ信号線D Q [ 0 ]は、前述のようにS o C回路100とS D R A M101との間に接続される。

10

【0017】

S o C回路100は、外部端子201と、バッファ202と、送信データを出力するデータ出力回路203と、O D T機能を有するターミネーション回路204と、データ出力回路203及びターミネーション回路204に対して制御信号を出力する制御回路205と、インバータ206と、を備える。ターミネーション回路204は、抵抗207、208と、スイッチ209、210と、を有する。データ出力回路203は、N A N D回路251と、N O R回路252と、トランジスタ253，254と、を有する。なお、スイッチ209，トランジスタ253はPチャネルM O Sトランジスタであって、スイッチ210，トランジスタ254はNチャネルM O Sトランジスタである場合を例に説明する。

20

【0018】

S o C回路100において、データ信号線D Q [ 0 ]は、外部端子201を介して、バッファ202の入力端子とデータ出力回路203の出力端子とに接続される。

【0019】

また、外部端子201とバッファ202との間にターミネーション回路204が設けられる。ターミネーション回路204において、高電位側電源端子V D Dと、外部端子201とバッファ202とを接続する信号線上のノードN1と、の間にスイッチ209及び抵抗207とが直列に接続される。低電位側電源端子V S SとノードN1との間にスイッチ210と抵抗208とが直列に接続される。より具体的には、スイッチ209のソース端子は高電位側電源端子V D Dに接続される。スイッチ209のドレイン端子は抵抗207の一端に接続される。抵抗207の他端は抵抗208の一端に接続される。抵抗208の他端はスイッチ210のドレイン端子に接続される。スイッチ210のソース端子は低電位側電源端子V S Sに接続される。抵抗207の他端と抵抗208の一端とがノードN1に共通接続される。なお、高電位側電源端子V D DとノードN1との間に直列に接続されたスイッチ209及び抵抗207は、接続関係を入れ替えても良い。同様に低電位側電源端子V S SとノードN1との間に直列に接続されたスイッチ210と抵抗208とは、接続関係を入れ替えても良い。

30

【0020】

バッファ202の出力端子は、制御回路205のデータ入力用の入力端子I Nに接続される。制御回路205の出力端子C 1は、スイッチ209のゲート端子に接続されるとともに、スイッチ210のゲート端子にインバータ206を介して接続される。このような周辺回路の構成は、他の双方向用信号線にも採用されている。なお、制御回路205は各双方向用信号線に共通に設けられる。

40

【0021】

制御回路205のデータ出力用の出力端子O U Tは、データ出力回路203のN A N D回路251の一方の入力端子と、N O R回路252の一方の入力端子と、にそれぞれ接続される。制御回路205の制御信号230出力用の出力端子E 1は、データ出力回路20

50

3 の N A N D 回路 2 5 1 の他方の入力端子に接続されるとともに、インバータ 2 5 5 を介して N O R 回路 2 5 2 の他方の入力端子に接続される。N A N D 回路 2 5 1 の出力端子は、トランジスタ 2 5 3 のゲート端子に接続される。A N D 回路 2 5 2 の出力端子は、トランジスタ 2 5 4 のゲート端子に接続される。トランジスタ 2 5 3, 2 5 4 は、高電位側電源端子 V D D と低電位側電源端子 V S S との間に直列に接続される。つまり、トランジスタ 2 5 3, 2 5 4 によりインバータを構成する。トランジスタ 2 5 3 のドレイン端子とトランジスタ 2 5 4 のドレイン端子とが、バッファ 2 0 2 と外部端子 2 0 1 との間の信号線上のノードに共通接続される。

#### 【 0 0 2 2 】

次に、本実施の形態 1 の動作について説明する。S o C 回路 1 0 0 が S D R A M 回路 1 0 1 からのデータを受信（リード）する場合について説明する。まず、S o C 回路 1 0 0 は、S D R A M 回路 1 0 1 に対して制御信号 C M D を出力する。その後、S D R A M 回路 1 0 1 は、例えば、制御信号 C M D によって指定されたアドレスのデータ D Q とストローブ信号 D Q S / D Q S B を S o C 回路 1 0 0 に対して送信する。このとき、S D R A M 回路 1 0 1 から送信されるデータ D Q は、所定のバースト長を有する。

#### 【 0 0 2 3 】

S o C 回路 1 0 0 は、対応する信号線、外部端子 2 0 1、及びバッファ 2 0 2 を介して各信号を受信する。なお、S o C 回路 1 0 0 は、データ D Q をストローブ信号 D Q S / D Q S B に同期して受信する。S o C 回路 1 0 0 が受信したデータは、制御回路 2 0 5 やその他の周辺回路（不図示）に入力される。S o C 回路 1 0 0 が制御信号 C M D を送信してからデータ D Q の受信を開始するまでの期間をリードレイテンシ（R L ）と称す。

#### 【 0 0 2 4 】

S o C 回路 1 0 0 は、S D R A M 回路 1 0 1 からのデータ受信時において、データ信号線 D Q 上及びストローブ信号線 D Q S / D Q S B 上に発生する電源ノイズを抑制するために対応するターミネーション回路 2 0 4 の O D T 機能をオンする。つまり、S o C 回路 1 0 0 は、制御回路 2 0 5 からの制御信号 2 0 0 に基づいて各ターミネーション回路 2 0 4 に含まれるスイッチ 2 0 9, 2 1 0 をオンする。そして、S o C 回路 1 0 0 は、対応する信号線上のノードを所定の電位（例えば、高電位側電源 V D D の 1 / 2 の電位）にする。それにより、S o C 回路 1 0 0 は、受信データに含まれる電源ノイズを低減し、データの受信を精度良く行うことができる。

#### 【 0 0 2 5 】

さらに S o C 回路 1 0 0 は、制御回路 2 0 5 からの制御信号 2 3 0 に基づいて、データ出力回路 2 0 3 が S D R A M 回路 1 0 1 に対して送信データを出力しないように制御する。つまり S o C 回路 1 0 0 は、L レベルの制御信号 2 3 0 により、データ出力回路 2 0 3 の出力をハイインピーダンス状態（H i Z ）にする。ここで、制御信号 2 3 0 が L レベルの場合、トランジスタ 2 5 3, 2 5 4 はいずれもオフに制御されるため、データ出力回路 2 0 3 の出力は H i Z を示す。それにより S o C 回路 1 0 0 は、データ出力回路 2 0 3 から出力されるデータに影響されることなく、S D R A M 回路 1 0 1 から送信されたデータの受信を精度良く行うことができる。

#### 【 0 0 2 6 】

S o C 回路 1 0 0 が S D R A M 回路 1 0 1 に対してデータを送信（ライト）する場合について説明する。まず、S o C 回路 1 0 0 は、S D R A M 回路 1 0 1 に対して制御信号 C M D を出力する。その後、S o C 回路 1 0 0 は、データ D Q 及びストローブ信号 D Q S / D Q S B を S D R A M 回路 1 0 1 に対して送信する。このとき、S o C 回路 1 0 0 から送信されるデータ D Q は、所定のバースト長を有する。

#### 【 0 0 2 7 】

そして、S D R A M 回路 1 0 1 は、データ D Q をストローブ信号 D Q S / D Q S B に同期して受信する。データ D Q は、例えば、制御信号 C M D によって指定されたアドレスに書き込まれる。なお、S o C 回路 1 0 0 が制御信号 C M D を送信してからデータ D Q の送信を開始するまでの期間をライトレイテンシ（W L ）と称す。

10

20

30

40

50

## 【0028】

SoC回路100は、SDRAM回路101へのデータ送信時において、対応するターミネーション回路204のODT機能をオフする。つまり、SoC回路100は、制御回路205からの制御信号200に基づいて各ターミネーション回路204に含まれるスイッチ209, 210をオフし、データ出力回路203及び外部端子201を介してSDRAM回路101に対して送信するデータの電位を減衰させないようにする。それにより、SoC回路100は、SDRAM回路101へのデータの送信を精度良く行うことができる。

## 【0029】

そしてSoC回路100は、制御回路205からの制御信号230に基づいて、データ出力回路203がSDRAM回路101に対して送信データを出力するように制御する。10つまりSoC回路100は、Hレベルの制御信号230により、データ出力回路203が送信データを出力するように制御する。ここで、制御信号230がHレベルの場合、トランジスタ253, 254は、制御回路205から出力される送信データに応じてオンオフが制御される。それによりSoC回路100は、SDRAM回路101に対してデータの送信を行う。

## 【0030】

このようにSoC回路100は、SoC回路100がSDRAM回路101からのデータを受信するリードモードと、SoC回路100がSDRAM回路101に対してデータを送信するライトモードと、を制御信号CMDによって切り替える。20また、SoC回路100は、1クロックCK周期分のデータ長を有する制御信号CMDを所定の間隔で出力する。

## 【0031】

例えば、SoC回路100は、リード/ライトモードでデータを受信/送信し、その後所定の間隔を置いて、再び同じモードで別のデータを送受信する。あるいは、SoC回路100は、リード/ライトモードでデータを受信/送信し、その後所定の間隔を置いて、当該モードと異なるモードで別のデータを送受信する。このようなデータの送受信が繰り返される。

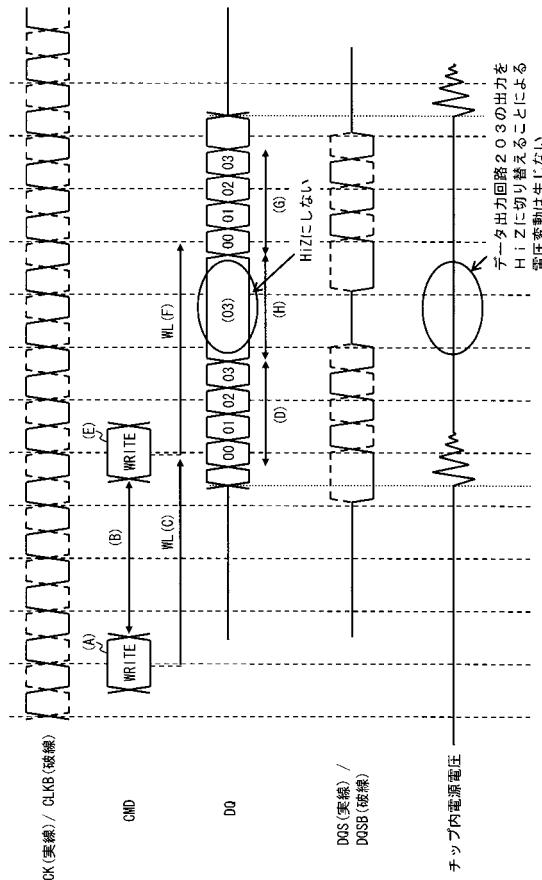

## 【0032】

ここで本実施の形態では、SoC回路100がライトモードでデータを送信し、その後所定の間隔を置いて、再びライトモードで別のデータを送信する場合に特徴を有する。このときの動作について、図3を用いて説明する。30

## 【0033】

まず、SoC回路100は、SDRAM回路101に対して制御信号CMD(図3のA; 以下、単に「ライトコマンドA」と称す)を出力する。SoC回路100は、ライトレイテンシWL(図3のC)の期間を経て、所定のバースト長を有するデータDQ(図3のD)と、それに対応するストローブ信号DQS/DQSBと、をSDRAM回路101に対して送信する。

## 【0034】

ここでSoC回路100は、データを送信する場合、対応するデータ出力回路203から送信データを出力する。40

## 【0035】

SoC回路100は、ライトコマンドAを出力後、所定の間隔(図3のB)を置いて、ライトコマンドE(図3のE)を出力する。SoC回路100は、ライトレイテンシWL(図3のF)の期間を経て、所定のバースト長を有するデータDQ(図3のG)と、それに対応するストローブ信号DQS/DQSBと、をSDRAM回路101に対して送信する。

## 【0036】

このとき、制御回路205は、ライトコマンド(A, E)の間隔Bと、ライトレイテンシWL(C, F)と、データDQのバースト長(D, G)と、に基づいて、データDQが50

転送されていない期間 (H) を算出する。それにより、制御回路 205 は、データ DQ が転送されていない期間 (H) 、データ出力回路 203 から送信データを出力するか否かを判定する。そして制御回路 205 は、その判定結果に基づいてデータ出力回路 203 に対して制御信号 230 を出力する。

【0037】

期間 (H) が予め設定されたしきい値以下の場合には、期間 (H) 中、データ出力回路 203 はデータ DQ (D) の最後のデータ (図 3 のデータ 03) を出力し続ける。一方、期間 (H) が予め設定されたしきい値を超える場合には、期間 (H) 中、データ出力回路 203 は出力を H i Z に切り替える。

【0038】

ライトモードが連続する場合において、データ転送が行われない期間 (例えば、図 3 の H) 中、データ出力回路 203 が最後に出力したデータを出力し続けた場合、データ出力回路 203 の出力側の信号線上には、データ出力回路 203 が出力を H i Z へ切り替えることによる電源ノイズは発生しない。そのため SoC 回路 100 は、従来問題となっていた電源ノイズの影響を低減し、データの送信を精度良く行うことができる。

10

【0039】

一方、ライトモードが連続する場合において、データ転送が行われない期間 (例えば、図 3 の H) がしきい値を超える場合、データ転送が行われない期間中、データ出力回路 203 は出力を H i Z に切り替える。ここで、データ転送が行われない期間が長いため、データ出力回路 203 の出力状態が切り替わることによって発生する信号線上の電源ノイズは収束する。そのため、SoC 回路 100 は、この電源ノイズの影響を受けることなく、再びデータ出力回路 203 から送信データを出力することができる。つまり、SoC 回路 100 は、電源ノイズの影響を低減し、データの送信を精度良く行うことができる。なお、データ出力回路 203 の出力を H i Z に切り替えるタイミングは、次のデータ送信が開始されるまでに電源ノイズが収束するのであればいつでも良い。

20

【0040】

このように、本実施の形態にかかる半導体集積回路は、データ送信回路 (例えば SoC 回路 100) が連続してデータを送信する場合において、データ送信の間隔に応じて当該データ送信回路に備えられたデータ出力回路 (例えばデータ出力回路 203) の出力を制御する。つまり、データ送信の間隔に応じて、データ出力回路 203 が送信データを出力し続けるか、出力を H i Z に切り替えるか、を制御する。それにより、本実施の形態にかかる半導体集積回路は、電源ノイズの影響を低減し、データの送信を精度良く行うことができる。

30

【0041】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。上記実施の形態では、SoC 回路 100 が SDRAM 回路 101 に対してデータを送信する場合について説明したが、これに限られない。SDRAM 回路 101 が SoC 回路 100 に対してデータを送信する場合にも本発明を適用可能である。その場合、上記実施の形態で示したデータ出力回路 203 の場合と同様に、SDRAM 回路 101 に備えられたデータ出力回路を制御する必要がある。

40

【0042】

また上記実施の形態では、データ送信回路 (例えば SoC 回路 100) が連続してデータを送信する場合において、制御回路 205 が、アドレスコマンド間隔、ライトレイテンシ W L、データ DQ のバースト長、に基づいて制御信号 (例えば制御信号 230) を出力する場合について説明したが、これに限られない。データ送信間隔に基づいてデータ出力回路 203 の制御が可能であれば、上記情報のうち少なくとも 1 つの情報 (例えばアドレスコマンド間隔) に基づいて制御信号 (例えば制御信号 230) を出力するような回路構成にも適宜変更可能である。

【0043】

また上記実施の形態では、データ出力回路 203 の出力側の信号線が双方向用信号線で

50

ある場合を例に説明したが、これに限られない。データ出力回路 203 の出力側の信号線が、データ送信用の信号線である場合にも適用可能である。

【0044】

また、ターミネーション回路は上記実施の形態に示す回路に限られない。所定の電位（例えば、高電位側電源 VDD の 1/2 の電位）を有する電源端子と、対応する信号線上のノードと、の間に直列に接続された抵抗及びスイッチを有する回路構成にも適宜変更可能である。さらに上記実施の形態では、ターミネーション回路を備えた場合を例に説明したが、ターミネーション回路を備えない回路構成にも適宜変更可能である。

【0045】

また上記実施の形態では、半導体集積回路が 1 つの SDRAM 回路を備えた場合について説明したが、これに限られない。半導体集積回路が複数の SDRAM 回路を備えた回路構成にも適宜変更可能である。 10

【符号の説明】

【0046】

|     |            |    |

|-----|------------|----|

| 100 | SOC 回路     | 20 |

| 101 | SDRAM 回路   |    |

| 200 | 制御信号       |    |

| 201 | 外部端子       |    |

| 202 | バッファ       |    |

| 203 | データ出力回路    |    |

| 204 | ターミネーション回路 |    |

| 205 | 制御回路       |    |

| 206 | インバータ      |    |

| 207 | 抵抗         |    |

| 208 | 抵抗         |    |

| 209 | スイッチ       |    |

| 210 | スイッチ       |    |

| 230 | 制御信号       |    |

| 251 | NAND 回路    | 30 |

| 252 | NOR 回路     |    |

| 253 | トランジスタ     |    |

| 254 | トランジスタ     |    |

| 255 | インバータ      |    |

【図1】

【図2】

【図3】

---

フロントページの続き

(56)参考文献 特開平04-085791(JP, A)

特開2009-129522(JP, A)

特開平07-182078(JP, A)

特開2000-295087(JP, A)

特開2006-040318(JP, A)

特開2007-193431(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 15 / 78

G 06 F 3 / 00

H 03 K 19 / 00 - 19 / 082

H 03 K 19 / 094 - 19 / 096

G 11 C 11 / 401 - 11 / 56

G 11 C 14 / 00

G 06 F 12 / 00 - 12 / 06

G 06 F 13 / 16 - 13 / 18