(19) 日本国特許庁 (JP)

(12) 公表特許公報(A)

(11) 特許出願公表番号

特表2009-543470

(P2009-543470A)

(43) 公表日 平成21年12月3日(2009.12.3)

|                             |            |         |

|-----------------------------|------------|---------|

| (51) Int.Cl.                | F 1        |         |

| <b>H03K 23/66</b> (2006.01) | H03K 23/66 | D       |

| <b>H03K 23/00</b> (2006.01) | H03K 23/00 | 1 O 1 E |

| <b>H03K 21/00</b> (2006.01) | H03K 21/00 | J       |

| <b>H03L 7/18</b> (2006.01)  | H03L 7/18  | Z       |

テーマコード (参考)

5J106

審查請求 有 予備審查請求 未請求 (全 25 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2009-518531 (P2009-518531) |

| (86) (22) 出願日 | 平成19年6月27日 (2007. 6. 27)     |

| (85) 翻訳文提出日   | 平成21年1月29日 (2009. 1. 29)     |

| (86) 國際出願番号   | PCT/US2007/072215            |

| (87) 國際公開番号   | W02008/002968                |

| (87) 國際公開日    | 平成20年1月3日 (2008. 1. 3)       |

| (31) 優先権主張番号  | 60/817, 572                  |

| (32) 優先日      | 平成18年6月28日 (2006. 6. 28)     |

| (33) 優先権主張国   | 米国 (US)                      |

| (31) 優先権主張番号  | 11/560, 973                  |

| (32) 優先日      | 平成18年11月17日 (2006. 11. 17)   |

| (33) 優先権主張国   | 米国 (US)                      |

(71) 出願人 595020643

クワアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100108855

弁理士 蔡田 昌俊

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

最終頁に続く

(54) 【発明の名称】 低電力のモジュラス分周器ステージ

(57)【要約】

モジュラス分周器ステージ(MDS)は、第1と第2のステージを含んでいる。MDSは、MDSが2分割モードまたは3分割モードのいずれで動作するかを決定するモジュラス除数制御信号Sを受信する。MDSのステージは、他のMDSからフィードバック・モジュラス制御信号も受信する。MDSは、2分割モードの場合、フィードバック・モジュラス制御信号にかかわらず、2で分割(分周)する。電力を節約して使用するため、MDSステージが2分割モードで動作するとき、第1のステージには電力が供給されない。MDSは、3分割モードの場合、フィードバック・モジュラス制御信号に依存して2または3のいずれかで分周する。電力消費をさらに減らすため、MDSステージが3分割モードにあるにもかかわらず2分割動作を行っているとき、第1のステージには電力が供給されない。第1のステージが電力供給されていないとき、電力ダウントランジスタは、第1のステージの出力を適正な論理レベルに維持する。

### 【選択図】

3

## 【特許請求の範囲】

## 【請求項 1】

(a) 入力信号を3で分周するためにモジュラス分周期ステージ(MDS)を使用すること ここにおいて前記MDSは第1および第2のステージを含み、ここにおいて前記MDSは前記入力信号を2または3のいずれかで分周するように制御することが可能である、

(b) 前記MDSの前記第2のステージの電源を切ることなく前記MDSの前記第1のステージの電源を切ること、および

(c) ステップ(b)の前記電源を切ることの後、前記第1のステージの電源が切られているとき前記入力信号を2で分周するために前記MDSを使用すること

を備える方法。

10

## 【請求項 2】

ステップ(a)の前記使用することは、

前記MDSへのフィードバック・モジュラス制御信号のパルスを受信すること、および

前記フィードバック・モジュラス制御信号の前記パルスを検出するために、およびクロック飲み込み制御パルスをアサートするために、前記第1のステージを使用すること 前記クロック飲み込み制御パルスは、前記第2のステージに前記第2のステージによって行われるトグル動作を中断させる

を含む、請求項1に記載の方法。

## 【請求項 3】

前記第1のステージは、前記クロック飲み込み制御パルスを信号導線によって前記第2のステージに供給し、前記クロック飲み込み制御パルスは、第1のデジタル論理のレベルのパルスであり、および前記信号導線は、前記MDSの前記第1のステージの電源が切られているとき第2のデジタル論理のレベルに維持される、請求項2に記載の方法。

20

## 【請求項 4】

前記信号導線は、前記MDSの前記第1のステージの電源が切られているとき前記信号導線を接地結合するトランジスタを制御することによって、前記第2のデジタル論理のレベルに維持される、請求項3に記載の方法。

## 【請求項 5】

(d) ステップ(c)の前記使用することの後、前記MDSの前記第1のステージの電源を入れること、およびその後ステップ(a)を繰り返すこと

30

をさらに備える、請求項2に記載の方法。

## 【請求項 6】

ステップ(d)において前記第1のステージの前記電源を入れることは、前記後続のステップ(a)において前記入力信号を前記3で分周することに先立つ1つの入力信号クロック周期より前に開始される、請求項5に記載の方法。

## 【請求項 7】

前記MDSは、2分割モードまたは3分割モードのいずれかにおいて動作可能であり、

前記2分割モードにおいて前記MDSは、フィードバック・モジュラス制御信号の値にかかわらず、前記入力信号を2で分周し、

前記3分割モードにおいて前記MDSは、前記フィードバック・モジュラス制御信号の値に依存して、2または3のいずれかで前記入力信号を分周し、および

40

ステップ(c)の前記2で分周することは、前記MDSが前記2分割モードにおいて動作しているときに行われる、

請求項1に記載の方法。

## 【請求項 8】

前記MDSは、2分割モードまたは3分割モードのいずれかにおいて動作可能であり、

前記2分割モードにおいて前記MDSは、フィードバック・モジュラス制御信号の値にかかわらず、前記入力信号を2で分周し、

前記3分割モードにおいて前記MDSは、前記フィードバック・モジュラス制御信号の値に依存して、2または3のいずれかで前記入力信号を分周し、および

50

ステップ(c)の前記2で分周することは、前記MDSが前記3分割モードにおいて動作しているときに実行される、

請求項1に記載の方法。

【請求項9】

前記MDSは、CML (current mode logic)の中の少なくとも一部において実現される、請求項1に記載の方法。

【請求項10】

前記第1のステージは、一定の量のフリップフロップ回路構成および供給電圧導線を備え、およびステップ(b)の前記電源を切ることは、前記一定の量のフリップフロップ回路構成を前記供給電圧導線から分離することを含む、請求項1に記載の方法。

10

【請求項11】

入力クロック信号を2または3のいずれかで分周し、1つの出力クロック信号を出力する第1のモジュラス分周器ステージ(MDS)を備える多重モジュラス分周器であって、前記第1のMDSステージは、

前記第1のMDSが3で分周することになっているときクロック飲み込み制御パルスを出力する第1のステージ ここにおいて前記第1のステージは、前記MDSが2で分周している時間の少なくとも一部において電源が切られている、および

前記第1のMDSが2で分周しているときトグルする第2のステージ 前記第2のステージは、前記出力クロック信号を出力し、前記第2のステージは、前記MDSが3で分周するように前記クロック飲み込み制御パルスの受信に基づいてトグル動作を中断する、

20

を備える、多重モジュラス分周器。

【請求項12】

前記第1のMDSから前記出力クロック信号を受信し、およびフィードバック・モジュラス制御信号を出力する第2のモジュラス分周器ステージ(MDS)をさらに備える、請求項11に記載の多重モジュラス分周器であって、

前記第1のMDSの前記第1のステージは、前記第2のMDSから前記フィードバック信号を受信する ここにおいて前記MDSの前記第1のステージは、前記フィードバック・モジュラス制御信号を受信することに反応して前記クロック飲み込み制御パルスを出力する、

請求項11に記載の多重モジュラス分周器。

30

【請求項13】

前記第1のMDSは、2分割モードまたは3分割モードのいずれかにおいて動作可能であり、前記2分割モードにおいて前記第1のMDSは、前記第2のMDSから受信される前記フィードバック・モジュラス制御信号の値にかかわらず、前記入力信号を2で分周し、

前記3分割モードにおいて前記MDSは、前記第2のMDSから受信される前記フィードバック・モジュラス制御信号の値に依存して、前記入力信号を2または3のいずれかで分周し、および

前記第1のステージの電源が切られている間の前記時間の前記少なくとも一部は、前記第1のMDSが前記2分割モードにある時間である、

請求項11に記載の多重モジュラス分周器。

40

【請求項14】

前記第1のMDSは、2分割モードまたは3分割モードのいずれかにおいて動作可能であり、前記2分割モードにおいて前記第1のMDSは、前記第2のMDSから受信される前記フィードバック・モジュラス制御信号の値にかかわらず、前記入力信号を2で分周し、

前記3分割モードにおいて前記MDSは、前記第2のMDSから受信される前記フィードバック・モジュラス制御信号の値に依存して、前記入力信号を2または3のいずれかで分周し、および

前記第1のステージの電源が切られている間の前記時間の前記少なくとも一部は、前記第1のMDSが前記3分割モードにある時間である、

請求項11に記載の多重モジュラス分周器。

50

【請求項15】

前記MDSの前記第1のステージは、

前記第1のMDSの前記第1のステージが前記クロック飲み込み制御パルスを前記第1のMDSの前記第2のステージに供給する信号導線、および

前記MDSの前記第1のステージの電源が切られているとき前記信号導線を接地導線に結合するトランジスタ

を備える、請求項11に記載の多重モジュラス分周器。

【請求項16】

前記第1のMDSの前記第1のステージは、

一定の量のフリップフロップ回路構成、

供給電圧導線、および

10

前記第1のMDSの前記第1のステージの電源が切られるとき前記一定の量のフリップフロップ回路構成を前記供給電圧導線から分離し、および前記第1のMDSの前記第1のステージに電源が入れられるとき前記一定の量のフリップフロップ回路構成を前記供給電圧導線と結合する回路構成

を備える、請求項11に記載の多重モジュラス分周器。

【請求項17】

クロック入力ノード、データ入力ノードおよびデータ出力ノードを有する第1のフリップフロップ、

前記第1のフリップフロップの前記データ入力ノードの上に信号を出力する第1のNOR回路 前記第1のNOR回路は、第1の入力リード、第2の入力リード、および第3の入力リードを有し、ここにおいて前記第1のNOR回路の前記第1の入力リードの上にはモジュラス除数制御信号が存在し、ここにおいて前記第1のNOR回路の前記第2の入力リードの上にはフィードバック・モジュラス制御信号が存在する、

クロック入力ノード、データ入力ノードおよびデータ出力ノードを有する第2のフリップフロップ 前記第2のフリップフロップの前記クロック入力ノードは、前記第1のフリップフロップの前記クロック入力ノードと結合されている、および

前記第2のフリップフロップの前記データ入力ノードの上に信号を出力する第2のNOR回路 前記第2のNOR回路は、第1の入力リードおよび第2の入力リードを有し、ここにおいて前記第2のNOR回路の前記第1の入力リードは、前記第1のフリップフロップの前記データ出力ノードと結合されており、およびここにおいて前記第2のNOR回路の前記第2のデータ入力リードは、前記第2のフリップフロップから出力されるデータ出力信号を受信するよう結合されている、

ここにおいて、前記第2のフリップフロップがトグルフリップフロップとして機能しているかつ前記第2のフリップフロップの前記クロック入力ノード上の入力信号を2で分周している時間の間ずっと前記第1のフリップフロップは電源が切られ、およびここにおいて、前記第1のフリップフロップ、前記第1のNOR回路、前記第2のフリップフロップおよび前記第2のNOR回路がいっしょに動作して前記入力信号を3で分周している時間の間ずっと前記第1のフリップフロップは電源が入れられる、

を備える回路。

【請求項18】

前記第2のフリップフロップは、第2のデータ出力ノードを有し、ここにおいて前記第2のフリップフロップから前記第2のNOR回路の前記第2のデータ入力リードの上に出力される前記データ出力信号は、前記第2のフリップフロップの前記第2のデータ出力ノード上の信号である、請求項17に記載の回路。

【請求項19】

前記回路は、多重モジュラス分周器のモジュラス分周器ステージ(MDS)であって、前記多重モジュラス分周器は、複数の他のモジュラス分周器ステージを含み、ここにおいて前記他のモジュラス分周器ステージは、前記第1のNOR回路の前記第2の入力リードの上に前記フィードバック・モジュラス制御信号を供給する、請求項17に記載の回路。

【請求項20】

20

30

30

40

50

前記回路は、多重モジュラス分周器のモジュラス分周器ステージ(MDS)であって、前記多重モジュラス分周器は、入力クロック信号をある除数値で分周し、および出力クロック信号を出力し、

前記除数値は、複数のモジュラス除数制御信号によって決定され、および

前記第1のNOR回路の前記第1の入力リードの上に存在する前記モジュラス除数制御信号は、前記複数のモジュラス除数制御信号の1つである、

請求項17に記載の回路。

【請求項 21】

制御入力リード、クロック入力リード、およびデータ出力リードを有するフリップフロップステージ ここにおいて前記フリップフロップステージは、そのクロック入力リードへのクロック入力信号を受信し、および前記制御入力リードの上に第1のデジタル論理レベルが存在するときトグリングをし、ここにおいて前記トグリングは、特定の時刻に前記制御入力リードの上に第2のデジタル論理レベルが存在するとき中断される 、および

フィードバック・モジュラス制御信号を検出するための、および前記フリップフロップの前記トグリングが前記クロック入力信号の1つの周期にわたって中断されるように前記特定の時刻において前記制御入力リードへのクロック飲み込み制御パルスをアサートするための手段 前記クロック飲み込み制御パルスは、前記第2のデジタル論理レベルのパルスであり、ここにおいて前記手段は、前記フィードバック・モジュラス制御信号の前記検出の前は実質的に電力が供給されず、前記フィードバック・モジュラス制御信号の前記検出の間および前記クロック飲み込み制御パルスの前記アサートの間はずっと電力が供給され、および次に前記クロック飲み込み制御パルスの後は実質的に電力が供給されない 、

を備えるモジュラス分周器ステージ。

【請求項 22】

前記特定の時刻は、前記クロック入力信号の遷移が起きる時刻であり、

前記フリップフロップステージは、1つのフリップフロップを含み、および

前記トグリングは、前記クロック入力信号遷移に反応して前記フリップフロップが状態を変えることを妨げることによって中断される、

請求項21に記載のモジュラス分周器ステージ。

【発明の詳細な説明】

【関連技術】

【0001】

[米国特許法 (35U.S.C.) 第119条に基づく優先権主張]

本件特許出願は、本願の譲渡人に譲渡され、参照によって本件明細書に明白に組み込まれる、2006年6月28日付けの「Low power modulus divider stage」という名称の米国仮出願第60/817,572号に基づいて優先権を主張するものである。

【技術分野】

【0002】

ここに開示される実施形態は、多重モジュラス分周器 (multi-modulus divider: MMD) に関係し、特にMMDのモジュラス分周器ステージ(modulus divider stage: MDS)における消費電力を低減することに関係する。

【背景情報】

【0003】

セルラ電話内部の受信機および送信機の回路構成は、典型的には1つまたは複数の局部発振器を含んでいる。局部発振器の機能は、選ばれた周波数の信号を出力することである。セルラ電話内部のそのような局部発振器は、例えば、安定的でかつ比較的低周波(例えば20MHz)の信号を水晶発振器から受信して、選ばれた比較的高周波(例えば900MHz)の出力信号を生成する位同期ループ(a phase-locked loop: PLL)を含んでいる。PLLのフィードバックループは、水晶発振器からの信号と位相および周波数を同じくするある低周波の信号を得るために、前記高周波信号を受信しそれを分割する周波数分割器(分周器)を含んでいる。本件明細書において「多重モジュラス分周器」と呼ばれるあるタイプの

10

20

30

40

50

分周器は、上記分周器を実現するためにしばしば使用される。分周器の高周波動作のために、分周器の回路構成は、望ましからざる大量の電力を消費する可能性がある。局部発振器内の分周器によって消費される電力の量を減らすための技術および方法が望まれている。

【発明の要約】

【0004】

多重モジュラス分周器 (MMD) は、入力信号SINを除数値DVで分周し、出力信号SOUTを生成する。MMDは、当該MMDを形成するために一体的にチェーン結合された複数のモジュラス分周器ステージ(MDS)を含んでいる。各MDSは、最後のMDSを除き、チェーン結合における次のMDSからフィードバック・モジュラス制御信号を受信する。各MDSはまた、モジュラス除数制御信号Sを受信する。ある特定のMDSのためのモジュラス除数制御信号Sが第1のデジタル論理値である場合、当該MDSは2分割モード (divide-by-two mode) で動作し、そうでない場合は、3分割モード (divide-by-three mode) で動作する。

10

【0005】

各MDSは、第1のステージおよび第2のステージを含んでいる。第1の新規な態様にしたがって、MDSが2分割モードで動作しているとき第1のステージの出力は遷移しないことが認識される。MDSの消費電力を低減するため、第1のステージは、2分割モードの動作の間ずっと電力が供給されない (unpowered)。

【0006】

第2の新規な態様にしたがって、3分割モード動作の間の第1のステージの機能は、フィードバック・モジュラス制御信号を検出すること、および第2のステージに3分割動作を行わせるために適切な時に第2のステージの制御入力リード上に「クロック飲み込み制御パルス」(後述)を供給することであることが認識される。MMDの典型的な動作において、3分割モードにあるMDSステージが実際に3分割動作を行うことはめったに起きない。したがって、MDSが3分割モードにあって、かつ第2のステージが2分割動作を行っているとき、第1のステージの電源を切ることによって、前記第2の新規な態様にしたがって消費電力を節約することができる。

20

【0007】

1つの新規な態様と一致しているある方法は、次の3つのステップ(a)-(c)を含んでいる。

(a) 入力信号を3で分周するためにモジュラス分周器ステージ(MDS)を使用すること。使用されるMDSは、入力信号を2または3のいずれかで分周することを制御することが可能であり、および第1のステージおよび第2のステージを含んでいる。

(b) MDSの第2のステージの電源を切ることなく、第1のステージの電源を切ること。

(c) ステップ(b)の電源切り (powering-down) の後、第1のステージの電源が切られているとき入力信号を2で分周するためにMDSを使用すること。この方法の1つの例において、MDSが2で分周しているとき、第1のステージは電力を供給される必要がない。MDSは、MDSが2で分周するかまたは3で分周するかのいずれか1つをモジュラス制御信号によって制御されているところの3分割モードにある。3分割動作が予想されるとき、第1のステージは、電力が供給され、およびその後3分割動作の間ずっと電力が供給される状態が維持される。3分割動作の完了後、第1のステージは、電源が切られ、その後の2分割動作の間ずっと電力が供給されない状態を続けるということになる。

30

【0008】

以上は、本件発明の要約であって、必要による単純化、一般化および詳細の省略を内包している。結果的に、当業者は、本要約が单なる例示であって、いかなる意味においても限定することを意図しているものではないことを正しく認識するであろう。本件明細書において説明されるデバイスおよび/またはプロセスは、もっぱらクレームによって定義されているところ、その他の態様、発明的特徴および利点は、本件明細書において記される非限定的な詳細な説明において明白なものとなるであろう。

40

【図面の簡単な説明】

【0009】

50

【図1】1つの新規な態様と一致しているあるモバイル通信デバイス(この例ではセルラ電話)の簡略図である。

【図2】図1のモバイル通信デバイスの内部の無線周波数(RF)トランシーバ集積回路の図である。

【図3】図2のRFトランシーバ集積回路の中の局部発振器の図である。

【図4】図3の局部発振器の分周器の図である。この分周器は、多重モジュラス分周器(MMD)である。

【図5】図4のMMDの入力バッファ141の図である。

【図6】図4のMMDの出力同期装置149の簡略図である。

【図7】図4の7ステージのMMDが所望の除数で分割を行うためにはS[6:0]の値が何でなければならないかを示す方程式を記している。 10

【図8】図4のMMDの1つのMDSのブロック図である。

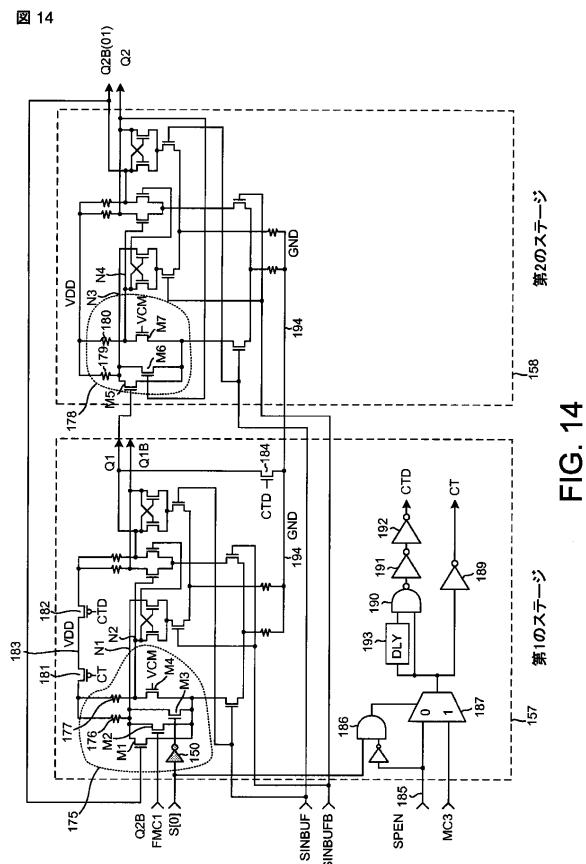

【図9】図8のMDSが入力信号SINBUFを2で分周するためにどう動作することができるかを例示する図である。

【図10】図9のMDSの動作における信号を例示する波形図である。

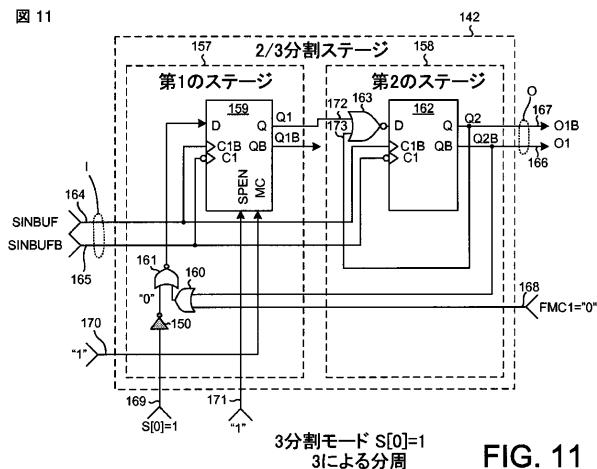

【図11】図8のMDSが入力信号SINBUFを3で分周するためにどう動作することができるかを例示する図である。

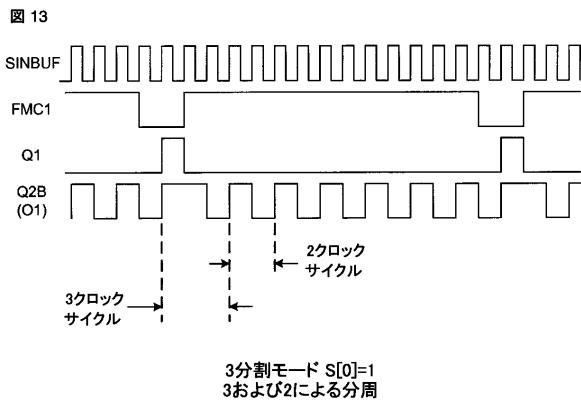

【図12】図11のMDSの動作における信号を例示する波形図である。

【図13】図4のMMDの第1のMDS 142が3分割モードで動作しているときの入力信号FMC1およびSINBUFならびに出力信号Q1およびQ2Bの代表的波形図である。 20

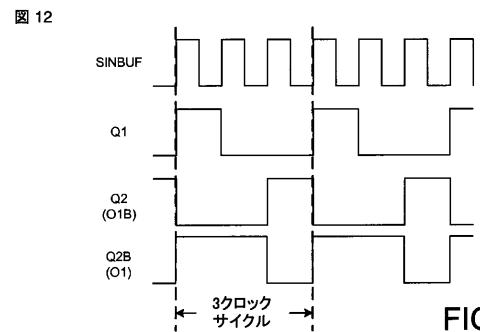

【図14】図4のMDS 142の詳細なトランジスタレベルの回路図である。

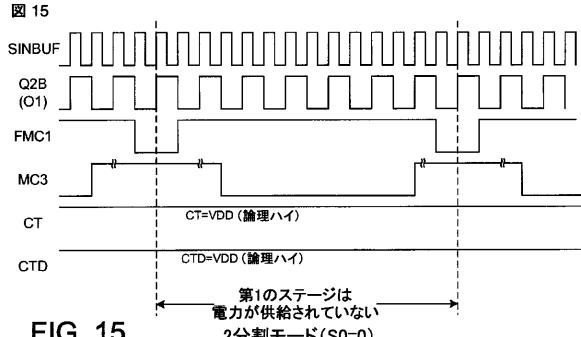

【図15】図14のMDSが2分割モードにあるときの動作を例示する簡略波形図である。

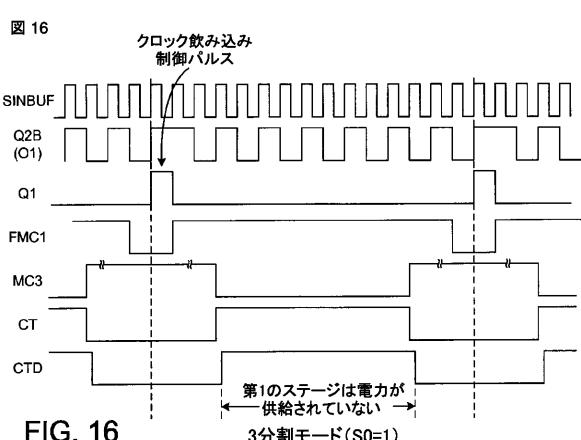

【図16】図14のMDSが3分割モードにあるときの動作を例示する簡略波形図である。

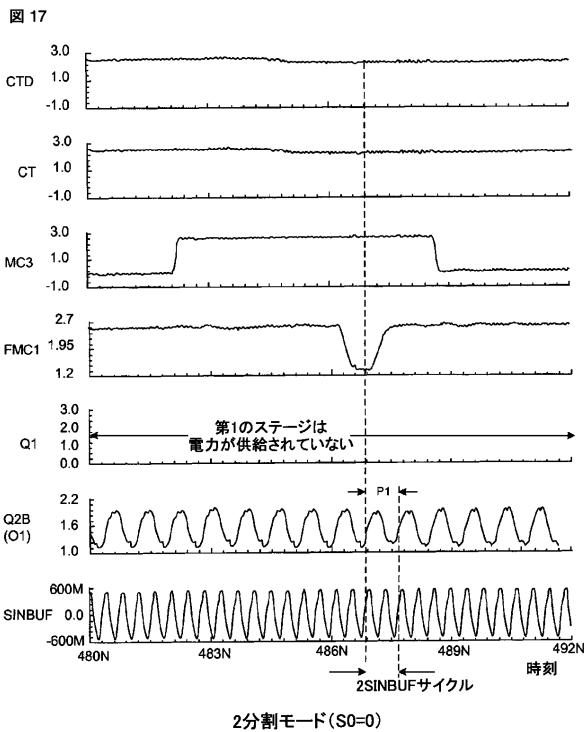

【図17】図14のMDSが2分割モードにあるときの動作の詳細な波形図である。

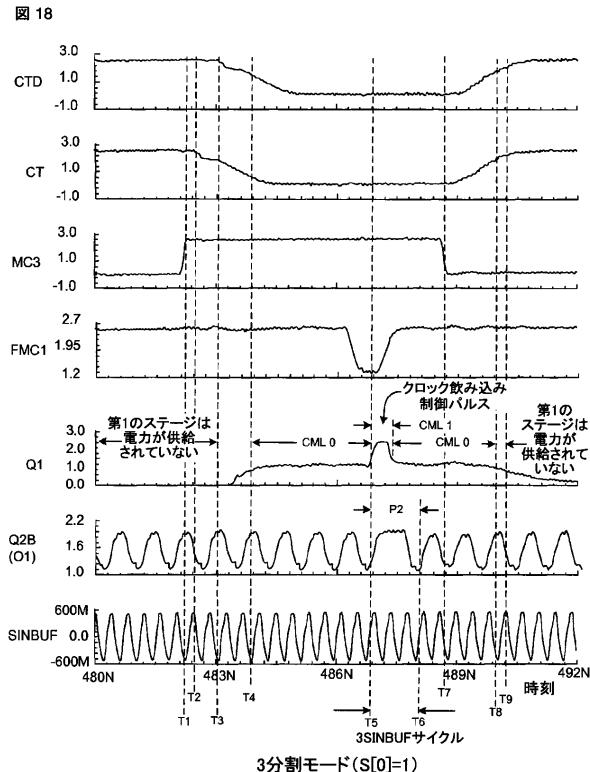

【図18】図14のMDSが3分割モードにあるときの動作の詳細な波形図である。

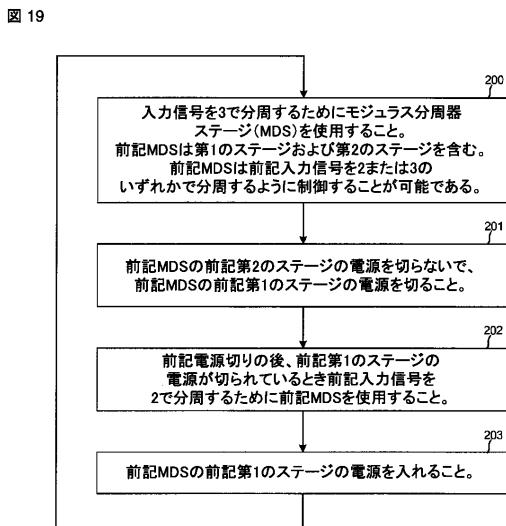

【図19】1つの新規な態様と一致しているある方法の流れ図である。

【詳細な説明】

【0010】

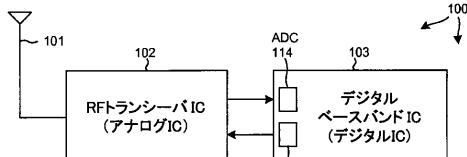

図1は、1つの新規な態様と一致しているあるモバイル通信デバイス100の簡略図である。モバイル通信デバイス100は、この場合、セルラ電話である。セルラ電話100は、アンテナ101、およびいくつかの集積回路を含んでいる。これらは、新規な無線周波数(RF)トランシーバ集積回路102、およびデジタルベースバンド集積回路103を含んでいる。デジタルベースバンド集積回路103は、主にデジタル回路構成を含み、またデジタルプロセッサを含んでいる。デジタルベースバンド集積回路103の一例は、クアルコム社から利用可能であるMSM6280である。新規なRFトランシーバ集積回路102は、アナログ信号を処理するための回路を含んでいる。 30

【0011】

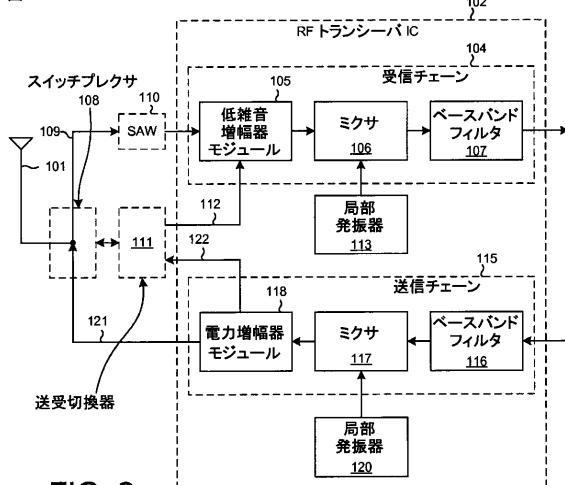

図2は、図1のRFトランシーバ集積回路102のより詳細な図である。受信機の「信号チェーン」104は、低雑音増幅器(LNA)モジュール105、ミクサ106、およびベースバンドフィルタ107を含んでいる。GSM(Global System for Mobile Communications)モードでの受信の場合、アンテナ101上の信号は、スイッチプレクサ108を通過し、その後バス109を通過し、SAW 110を通過してLNA 105にいたる。CDMA(符号分割多重接続方式)モードでの受信の場合、アンテナ101上の信号は、スイッチプレクサ108を通過し、送受切換器111を通過し、およびバス112を通過してLNA 105にいたる。すべてのモードにおいて、LNA 105は、高周波信号を増幅する。局部発振器(LO)113は、適切な周波数の局部発振器信号をミクサ106に供給し、その結果、受信機は、適切な周波数の信号を受信するように調整される。ミクサ106は、前記高周波信号をある低周波信号に復調する。好ましくない高周波雑音は、ベースバンドフィルタ107によってフィルタされる。ベースバンドフィルタ107のアナログ出力は、デジタルベースバンド集積回路103のアナログ・デジタル変換器(ADC)114に供給される。ADC 114は、アナログ信号をデジタル情報に変換する。そのデジタル情報は、その後 40

50

、ベースバンド集積回路103のデジタルプロセッサによってさらに処理される。

【0012】

送信機の「信号チェーン」115は、ベースバンドフィルタ115、ミクサ117および電力増幅器モジュール118を含んでいる。送信されるべきデジタル情報は、デジタルベースバンド集積回路103内のデジタル・アナログ変換器(DAC)119によってアナログ信号に変換される。その結果のアナログ信号は、RFトランシーバ集積回路102のベースバンドフィルタ116に供給される。ベースバンドフィルタ116は、好ましくない高周波雑音を取り除く。ミクサ117は、ベースバンドフィルタ116の出力を高周波搬送波に変調する。局部発振器(LO)120は、局部発振器信号をミクサ117に供給し、その結果、前記高周波搬送波は、使用されているチャンネルに対して正しい周波数を持つようになる。ミクサ117の高周波出力は、その後、電力増幅器モジュール118によって増幅される。GSMモード送信の場合、電力増幅器モジュール118は、バス121を介し、スイッチブレクサ108を通過し、アンテナ101上に信号を出力する。CDMAモード送信の場合、電力増幅器モジュール118は、バス122を介して送受切換器111に信号を出力する。信号は、送受切換器111を通過し、スイッチブレクサ108を通過し、アンテナ101にいたる。非二重通信(例えばGSM)および二重通信(例えばCDMA1X)の両方を可能にする送受切換器111およびスイッチブレクサ108の使用は普通である。図2の特定の回路は、本件明細書において例示の目的のために提供される1つの可能性のある実装にすぎない。

10

【0013】

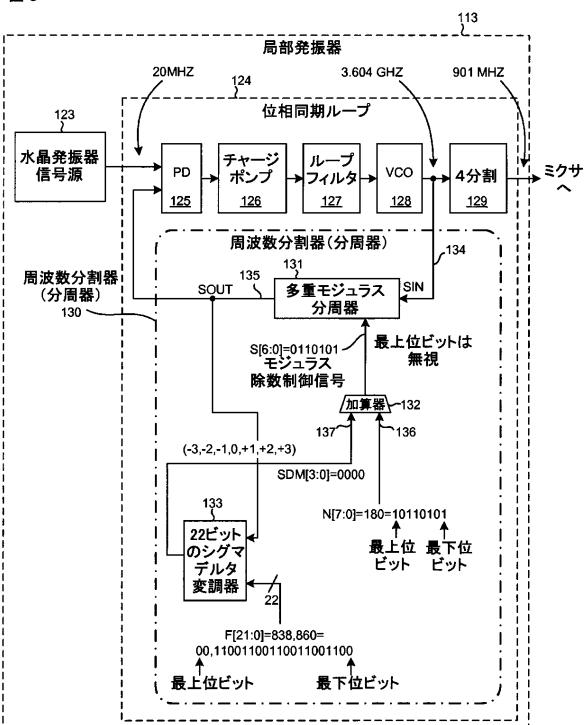

局部発振器113および120の動作は、受信機の局部発振器(LO)113の動作に関連して以下で説明される。図3は、局部発振器113のより詳細な図である。局部発振器113は、水晶発振器信号源123および断片的N位相同期ループ(PLL)124を含んでいる。現在の例において、水晶発振器信号源123は、外部の水晶発振器モジュールへの接続である。代替的に、水晶発振器信号源は、RFトランシーバ集積回路の上に配置される発振器である。ここで、水晶は集積回路102の外部にあるが、集積回路102の端子を介して発振器に取り付けられている。

20

【0014】

PLL 124は、位相検出器(PD)125、チャージポンプ126、ループフィルタ127、電圧制御発振器(VCO)128、信号調整出力分周器129、および新規な分周器130(「ループ分周器」と呼ばることもある)を含んでいる。分周器130は、第1の比較的高い周波数F1の分周器入力信号SINを受信し、その信号を除数Dで分周し、および第2の比較的低い周波数F2の分周器出力信号SOUTを出力する。分周器130の複数のカウントサイクルにわたって、PLLがロックされているとき $F2=F1/D$ である。ロックされているとき、SOUT信号の周波数F2および位相は、水晶発振器信号源123から供給される基準クロック信号の周波数および位相と一致する。

30

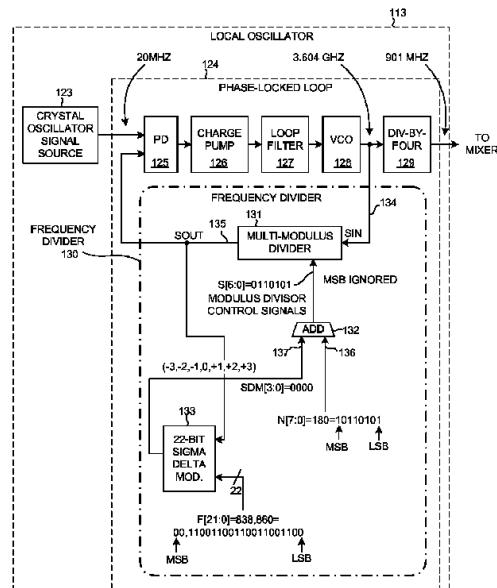

【0015】

分周器130は、新規な多重モジュラス分周器(MMD)131、加算器132、およびシグマデルタ変調器133を含んでいる。分周器134は、1つのカウントサイクルにおいて入力ノード134上の分周器入力信号SINを値DVで分周し、出力ノード135の上に分周器出力信号SOUTを生成する。値DVは、加算器132の第1のデジタル入力ポート136上の第1のデジタル値および加算器132の第2のデジタル入力ポート137上の第2のデジタル値の和である。シグマデルタ変調器133は、MMDの複数のカウントサイクルにわたって $F2=F1/D$ となるように、第2のデジタル入力ポート137上の値を時間とともに変える。

40

【0016】

[多重モジュラス分周器のハイレベルの説明]

図4は、図3のMMD 131のより詳細な図である。MMD 131は、入力バッファ141、7つの多重モジュラス分周器ステージ(MDSステージ)142-148、および1つの出力同期装置149を含んでいる。最初の3つのMDSのステージ142-144は、CML(current mode logic)において実装される。最後の4つのMDSのステージ145-148は、CMOS(相補型金属酸化物半導体)論理において実装される。インバータ150-153は、CMOS論理の信号およびレベルからCML論理の信号およ

50

びレベルへのインパートおよびコンパートの両方を行う。図4の各MDSステージは、モジュラス除数制御信号Sおよびフィードバック・モジュラス制御信号FMCの値に依存して2または3のいずれかで分周することができる。ここで、文字FMCは、「フィードバック・モジュラス・コントロール」を表わす。MMD 131が全体として分周する除数値DVは、7つのSモジュラス除数制御信号S[6:0]の値によって決定される。

#### 【0017】

図5は、図4の入力バッファ141のより詳細な図である。2つのインバータの各々は、CML論理を用いて実現される。信号線は1本の信号線として例示されているが、例示されている信号線の各々は、実際には2本の物理的信号線を表わしている。CML論理において使用される信号は、差分信号である。

10

#### 【0018】

図6は、図4の出力同期装置149のより詳細な図である。出力同期装置149は、出力ノード135上にMMD出力信号SOUTを生成するために、セルフタイミング技術を利用する。普通の同期装置(「リタイミング回路」と呼ばれることがある)において、MMDへ向かう高速MMD入力信号は、一般にMMD出力信号におけるジッタを低減することを目的としてMMD出力信号を同期させるために使用される信号である。同期化をするためにそのような高速信号を使用することは、同期装置が大量の電力を消費する原因となる。1つの有利な態様において、図4のモジュラス制御信号MC1Bは、所望の出力信号SOUTの周期が遷移すべきときにハイに遷移する低ジッタ信号であることが認識される。しかしながら、低ジッタのモジュラス制御信号MC1Bは、所望のSOUT信号の50/50のデューティサイクルを有していない(信号MC1は、図4の導線155の上の信号MC1Bの論理的反転である)。MDS出力信号01-07の1つまたは複数を論理的に組み合わせることによって、所望の信号SOUTの周期の前半にローを維持し、かつ所望の信号SOUTの周期のほぼ真ん中の時に初めてハイに遷移する信号を生成することが可能であることも認識される。したがって、図6の実施形態において、フリップフロップ154をセットするために、フリップフロップ154のアクティブローのセット入力リード(SB)にモジュラス制御信号MC1が供給される。低ジッタ信号MC1がハイからローに遷移すると、信号SOUTは所望の時刻において非同期的にハイにセットされる。ブロック156は、組み合わせ論理を表わしている。現在の例において、06は、所望のSOUT信号の周期の前半にローであって、その後、ハイに遷移する信号である。06(この実施形態において06はブロック156を通る)のローからハイへの遷移は、フリップフロップ154をクロックする働きをし、そのことによって、デジタル論理のロー(digital logic low)をクロックで取り込む。フリップフロップ154から出力される結果としての信号SOUTは、所望の周波数を有し、かつ約50/50のデューティサイクルを有する所望の信号である。SOUTの立ち上がりエッジは、MMD入力信号に関して低ジッタを有している。高速MMD入力信号(SINBUF)は、同期化においては使用されないので、通常の同期装置と比べると、消費電力をより低減する。フリップフロップ154をセットするためにMC1を使用するかわりに、モジュラス制御信号MC2、MC3またはMC4のうちの対応する1つを使用することもできたかもしれない。MC2は、MC1より周波数が低いコンテンツであるが、SINBUFに関連するジッタをより多く有している。フリップフロップ154をセットするためにより低い周波数コンテンツ信号MC2を使用することは、同期装置の消費電力を減らすことになるが、結果として信号SOUTがより多くのジッタを有することになる。1つの新規な態様において、図6の回路は、消費電力とジッタの間にトレードオフを持つことを可能にし、MMDが適用される特定のアプリケーションのためにベストの折衷点を選択することを可能にする。

20

30

40

#### 【0019】

図7は、MMD131が所望の除数値DVで分周を行うためにモジュラス除数制御信号S[6:0]は何であるべきかを示す方程式を記している。例えば、MMD 131が除数値181で分周することになっているのであれば、S[6:0]は値[0110101]であるべきである。

#### 【0020】

##### [MDSステージのハイレベルの説明]

図8は、図4のMMD 134の第1のMDSステージ142の簡略図である。第1のMDSステージ142は

50

、他のMDSステージ143-148の構造を代表する構造を有している。第1のMDS 142は、第1のステージ157および第2のステージ158を含んでいる。第1のステージ157は、D型フリップフロップ159、ORゲート160、NORゲート161およびインバータ150を含んでいる。図8のORゲート160、NORゲート161およびインバータ150は、図4のORゲート160、NORゲート161およびインバータ150と同じである。以下においてさらに詳しく説明されるように、ゲート160および161の機能性は、フリップフロップ159がCMLフリップフロップである場合、フリップフロップ159の回路構成に組み入れられることができる。

#### 【0021】

第2のステージ158は、D型フリップフロップ162およびNORゲート163を含んでいる。以下においてさらに詳しく説明されるように、ゲート163の機能性は、フリップフロップ162がCMLフリップフロップである場合、フリップフロップ162の回路構成に組み入れられることができる。MDSステージ142は、入力リード1の164および165の上で入力信号SINBUFを受信し、および出力リード0の166および167の上に出力信号01を出力する。入力リード168は、第2のMDSステージ143からフィードバック・モジュラス制御信号FMC1を受信するための入力リードである。入力リード169は、MDS 142が「2分割モード」であるかまたは「3分割モード」であるかを決定するモジュラス除数制御信号S[0]を受信するための入力リードである。入力リード170および171は、以下においてさらに詳しく説明されるように、フリップフロップ159の電源を切ったり入れたりするための信号を受信するために使用される。動作中、モジュラス除数制御信号S[0]がデジタル論理のローであれば、MDSステージ142は「2分割モード」にある。反対に、モジュラス除数制御信号S[0]がデジタル論理のハイであれば、MDS 142は「3分割モード」にある。3分割モードにおいて、MDS 142は、フリップフロップ162の状態およびフィードバック・モジュラス制御信号FMC1の論理レベルに依存して、2または3のいずれかで分周を行う。もしフィードバック・モジュラス制御信号FMC1およびフリップフロップ162からのQ2B信号出力の両方がデジタル論理ローレベルであれば、MDS 142は、入力信号SINBUFの次の3つの周期の間ずっと3で分周する。もしフィードバック・モジュラス制御信号FMC1およびフリップフロップ162からのQ2B信号出力の両方がデジタル論理ローレベルであるというのでなければ、ステージ142は2で分周する。

#### 【0022】

図9は、モジュラス除数制御信号S[0]がデジタル論理ローレベルである場合、MDSステージ142はどのようにして2で分周するかを例示する回路図である。S[0]がデジタル論理ローである場合、NORゲート161は、他の信号値にかかわらず、デジタル論理ローを出力する。したがって、NORゲート161は、フリップフロップ159のD入力リードの上にデジタル論理ローを出力する。フリップフロップ159がクロックされるのにともなって、フリップフロップ159には、D入力リード上のデジタル論理ローがクロックによって繰り返して入力されるので、フリップフロップ159のQ1信号出力は、デジタル論理ローレベルに維持される。したがって、図9のNORゲート163の上部の入力リード172の上の「0」で示されるように、NORゲート163の上部の入力リード172の上には、デジタル論理ローが続けて存在する。したがって、フリップフロップ162により出力されるQ信号は、NORゲート163の下部の入力リード173を通り、NORゲート163を通り、フリップフロップ162のD入力リードへと再通信される。この信号バスは、図9において破線174で示される。フリップフロップ162のQ出力リードがNORゲート163を通ってフリップフロップ162のD入力リードに結合されているため、このフィードバックループは、インバータとして機能し、フリップフロップ162は、トグルフリップフロップとして動作する。したがって、第2のステージ158のフリップフロップ162は、トグルして入力リード164および165の上の入力信号を2で分周し、および出力リード166および167の上に結果としての信号を出力する。これとは対照的に、第1のステージ157のフリップフロップ159は、状態を変えず、ただNORゲート163の上部の入力リード172の上でデジタル論理のロー値を保持するだけである。

#### 【0023】

図10は、MDSステージ142が2分割モードにあるときの動作を示す簡略波形図である。上において説明されたように、第1のステージのフリップフロップ159からのQ1信号出力は、

10

20

30

40

50

状態を変えない。第2のステージのフリップフロップ162は、入力信号SINBUFを2で分周するためトグルする。

【0024】

図11は、モジュラス除数制御信号S[0]がデジタル論理のハイレベルである場合、MDS 142はどのようにして入力リード164および165上の入力信号SINBUFを3で分周するかを例示する回路図である。はじめに、フリップフロップ159はデジタル論理ローの状態に記憶設定されていると仮定せよ。またフリップフロップ162はデジタル論理ハイの状態に記憶設定されていると仮定せよ。したがって、信号Q1はデジタル論理ローの値であり、信号Q2はデジタル論理ハイの値である。またはじめに、フィードバック制御信号FMC1はデジタル論理のローレベルであると仮定せよ。S[0]がデジタル論理のハイの値であって、FMC1がデジタル論理のロー値であって、およびフリップフロップ162からのQ2B信号出力がデジタル論理のローレベルであるから、NORゲート161は、フリップフロップ159のD入力リードの上にデジタル論理のハイレベルを出力する。フリップフロップ159によって出力されるQ1信号がデジタル論理のローレベルであるから、NORゲート163は、フリップフロップ162によって出力される信号Q2の値を反転する。したがって、フリップフロップをクロックするSINBUF信号の次の立ち上がりエッジの際、第1のステージのフリップフロップ159は、デジタル論理のハイレベルをクロックで取り込み、その結果、信号Q1はデジタル論理のハイレベルになる。同時に、フリップフロップ162は、デジタル論理のロー値をクロックで取り込み、その結果、信号Q2はデジタル論理のロー値になり、信号Q2Bはデジタル論理のハイ値になる。

10

20

30

40

【0025】

そのクロックエッジの後、信号Q2Bは、デジタル論理のハイレベルである。したがって、NORゲート160は、デジタル論理のハイ値を出力し、およびNORゲート161は、デジタル論理のロー値を出力する。クロック信号SINBUFの次の立ち上がりエッジの際、フリップフロップ159は、このデジタル論理ロー値をクロックで取り込む。したがって、信号Q1は、デジタル論理のローレベルに遷移する。クロック信号のこの立ち上がりエッジの前には、フリップフロップ162のD入力にデジタル論理のローが存在した。クロック信号SINBUFの立ち上がりエッジの際、フリップフロップ162は、信号Q2をデジタル論理のローにドライブすることを続ける。信号Q2Bは、デジタル論理のハイ値のままである。したがって、第2のステージ158のフリップフロップ162のトグリングは、効果的に中断され、およびフリップフロップ162から出力される信号Q2Bは、2つのSINBUF周期にわたってデジタル論理ハイ値のままである、ということがわかる。

【0026】

クロック信号のこの立ち上がりエッジの後、フリップフロップ159によって出力されるQ1信号は、デジタル論理のローである。NORゲート163は、信号Q2を反転し、そのQ2の反転信号をフリップフロップ162のD入力リード上に供給する機能を再び実行する。Q2信号は、デジタル論理ローの論理レベルを有している。したがって、クロック信号SINBUFの次の立ち上がりエッジの際、フリップフロップ162はトグリングを再開し、その結果、信号Q2はデジタル論理のハイ値に遷移する。Q1はもうデジタル論理のロー値であり、およびQ2はデジタル論理のロー値であるから、カウントサイクルはかくして繰り返す。したがって、第2のステージ158の制御入力リード上のデジタル論理ローレベルの信号がフリップフロップ162のトグリングを可能にするという意味において、NORゲート163の上部入力リードは第2のステージ158の「制御入力リード」であるところ、Q2信号がデジタル論理ロー値であるときのこの制御入力リード上のデジタル論理ハイレベル信号は、トグリング動作を中断し、およびSINBUFの次の立ち上がりエッジの後、Q2信号をデジタル論理のロー値に維持することが認識される。

【0027】

図12は、S[0]=1およびFMC1=0であるときのMDSステージ142の動作を示す簡略波形図である。入力リード164上の入力信号SINBUFの周期は、出力リード166上の出力信号Q2Bの周期の3倍である。

50

## 【0028】

図11の動作の実例において、フィードバック・モジュラス制御信号FMC1は、デジタル論理のロー値であることに注意せよ。もし反対にフィードバック・モジュラス制御信号FMC1がデジタル論理のハイ値であれば、他の信号S[0]およびQ2Bの値にかかわらず、NORゲート161によって出力される信号は、デジタル論理のロー値になる。もしFMC1がデジタル論理のハイ値であったら、フリップフロップ159はデジタル論理のロー値をクロックで取り込むことになり、フリップフロップの出力信号Q1はデジタル論理のロー値となり、第2のステージはトグルフリップフロップとして動作することになる。したがって、デジタル論理のハイ値であるフィードバック・モジュラス制御信号FMC1は、S[0]の値にかかわらず、MDSステージ142に2で分周することを強制する。しかしながら、もしフィードバック・モジュラス制御信号FMC1がデジタル論理のロー値であれば、MDSステージは、S[0]の値に依存して、2で分周するかまたは3で分周するかのいずれかを行う。

10

## 【0029】

図13は、MDSステージ142が図4のMMD131において動作しているときの第2のステージの入力信号FMC1およびSINBUFおよび出力信号Q1およびQ2Bの代表的波形の図である。S[0]=1であるから、MDSステージ142は、3分割モードにある。図に示されているように、フィードバック制御信号FMC1は、大部分の時間において、デジタル論理のハイ値にある。図11からわかるように、ORゲート160は、デジタル論理ハイ値を出力し、またNORゲート161は、信号の値にかかわらず、デジタル論理ロー値を出力する。その結果、フリップフロップ159のD入力リードには、デジタル論理ロー値が存在する。したがって、このデジタル論理ロー値は、クロックでフリップフロップ159に取り込まれて、NORゲート163の上部の入力リード172の上に現れる。したがって、NORゲート163は、信号Q2の値を反転し、その信号Q2の反転したものをフリップフロップ162のD入力リード上に提供する機能を実行する。したがって、第2のステージ158は、トグルフリップフロップとして機能する。第2のステージによって出力されるQ2B信号の周期は、入力クロック信号SINBUFの周期の2倍である。したがって、本回路は、MDSステージが3分割モードにあるという事実にもかかわらず、大部分の時間において、2で分周する。

20

## 【0030】

もし図13に示されているように、MMD131の上位のMDSステージの動作によってフィードバック制御信号FMC1がデジタル論理のロー値にパルスされるとすると、信号Q2Bがデジタル論理のローレベルにあるとき、ORゲート160は、デジタル論理のロー値を出力し、およびNORゲート161の両方の入力リードの上には、デジタル論理のロー値が現れることになる。NORゲート161は、デジタル論理のハイ値を出力する。SINBUFの次の立ち上がりエッジの際、フリップフロップ159は、このデジタル論理のハイ値をクロックで取り込む。このことは、図12に関して上で説明されたように、NORゲート163の上部の入力リード172をデジタル論理のハイ値にする。SINBUFの次の立ち上がりエッジの際、第2のステージ158のフリップフロップ162はトグリングを行わず、フリップフロップ162には論理ローの値がクロックで取り込まれる。このデジタル論理ロー値は、SINBUFの立ち上がりエッジの前にフリップフロップ162がそうであったとの同じ状態である。したがって、フリップフロップ162のトグリングは中断される。しかし、Q2BはSINBUFの立ち上がりエッジの前はデジタル論理のハイレベルであったため、Q1信号は、元のデジタル論理のローレベルに遷移する。図13に見られるように、信号FMC1も元のデジタル論理ハイ値に遷移する。SINBUFの次の立ち上がりエッジの際、第2のステージ158のフリップフロップ162は、トグリングを再開する。なぜなら、NORゲート163の上部の入力リード172上にデジタル論理のローが存在するからである。したがって、信号Q2は、デジタル論理のハイに遷移し、信号Q2Bはデジタル論理ローに遷移する。したがって、FMC1をローパルスにすることによって、MDSステージ142は、図13の波形図に示されるように3分割動作を行うことができる。そうでない場合、MDSステージ142は、2分割動作を行なう。図4のMMD回路がフィードバック制御信号FMC1を生成する前記方法のために、たとえMDS 142が「3分割モード」にあるとしても、MDS 142は、単に時おり3分割動作を行うのみである。

30

40

50

## 【 0 0 3 1 】

## [ MDSステージのローレベルの回路の説明 ]

図14は、CML論理において実現されるMDS 142のより詳細なトランジスタレベルの回路図である。破線175は、図8の第1のステージ157のトランジスタレベル構造を囲んでいる。破線178は、図8の第2のステージ158のトランジスタレベル構造を囲んでいる。図8のORゲート160、インバータ150およびNORゲート161の論理は、第1のステージ157のフリップフロップのCML構造に組み込まれている。図14の破線175は、この論理を囲んでいる。ノードN1は、第1のステージ157のフリップフロップ159の第1のステージのデータノードである。ノードN2は、差分比較ノードである。NチャネルのプルダウントランジスタM1、M2およびM3のいずれか1つは、ノードN1をプルダウンするために伝導性状態にさせられることができる。M1、M2およびM3のいずれもが伝導性状態でない場合、プルアップ抵抗器176は、ノードN1をデジタル論理ハイ値に維持する。プルアップ抵抗器177は、差分比較ノードN2のためのプルアップ抵抗器である。トランジスタM4のゲート上のバイアス電圧VCMは、ノードN2にバイアスをかける。ノードN1上の電圧が差分比較ノードN2上の電圧より低い場合、フリップフロップの第1のステージは、第1の状態にセットされる。反対にノードN1上の電圧が差分比較ノードN2上の電圧より高い場合、フリップフロップの第1のステージは、第2の状態にセットされる。したがって、破線175内の構造は、Q2B、FMC1およびS[0]の論理的反転の3つの信号入力を有するワイヤードNORタイプの構造である。

## 【 0 0 3 2 】

図8のNORゲート163の論理は、第2のステージ158のフリップフロップのCML構造に組み込まれている。図14における破線178は、この論理を囲んでいる。NチャネルのトランジスタM5およびM6は、ノードN3をプルダウンできるプルダウントランジスタである。抵抗器179は、ノードN3のためのプルアップ抵抗器である。バイアス電圧VCMは、トランジスタM7を制御して、差分比較ノードN4にバイアスをかける。抵抗器180は、差分比較ノードN4のためのプルアップ抵抗器である。ノードN3上の電圧が差分比較ノードN4上の電圧より低い場合、フリップフロップの第1のステージは、第1の状態にセットされる。反対にノードN3上の電圧が差分比較ノードN4上の電圧より高い場合、フリップフロップの第1のステージは、第2の状態にセットされる。したがって、破線178内の構造は、Q1およびQ2の2つの信号入力を有するワイヤードNORタイプの構造である。

## 【 0 0 3 3 】

第1のステージ157のフリップフロップ159は、フリップフロップが状態遷移をしないように無力化する(disable)ことができ、このことによって、フリップフロップがクロックされるときフリップフロップによって消費される電力を低減することができる。供給電圧VDD電源導線183からCML回路構成のさまざまプルアップ抵抗器にいたる供給電流バスの上に、2つのPチャネルのトランジスタ181および182が置かれている。もし信号CTおよびCTD(遅れたCT)がデジタル論理のハイ値であれば、これら2つのトランジスタ181および182は、非伝導性になる。もしトランジスタ181および182が非伝導性になると、供給電圧VDD導線183は、フリップフロップの回路構成から分離される。

## 【 0 0 3 4 】

もしこのようにして第1のステージ157のフリップフロップが無力化されかつ電力が供給されないことになったとしても、第1のステージ157の出力Q1が値未定のままフロート状態で放置されることがあってはならない。それゆえ、無力化信号CTDがデジタル論理のハイであればQ1出力ノードを接地導線194に結合するためのNチャネル電力ダウントランジスタ184が提供される。Q1出力ノードを接地導線194に結合することによって、Q1信号は、第1のステージ157の電源が切られている間ずっとデジタル論理のローレベルの状態を維持する。

## 【 0 0 3 5 】

入力リード185上の電力使用可能オーバーライド信号(power enable override signal)SPENは、アクティブな信号である。SPENがデジタル論理のハイであれば、ANDゲート186は、デジタル論理のローを出力し、そのことによって、結果として、2入力1出力のマルチ

10

20

30

40

50

プレクサ187は、その上部のデータ入力リードの上のデジタル論理のハイを選択することになる。このデジタル論理のハイ値は、インバータ189によって反転され、その結果、信号CTは、デジタル論理のローレベルになるように強制され、その状態が維持される。このことによって、その他の制御信号S[0]およびMC3の値にかかわらず、第1のステージ157は、使用可能にされ(enabled)かつ電力が供給された状態で維持されることになる。同様にして、マルチプレクサ187によって出力されるデジタル論理のローレベルによって、信号CTDは、デジタル論理のローレベルで維持されることになる。このゆえに、SPENは「電力使用可能オーバーライド信号」と呼ばれる。

#### 【0036】

図9および10に関連して上で説明したように、MDS 142が2分割モードにあるとき、MDS 142の第1のステージ157は状態遷移をしないということが認識される。より正確に言えば、第1のステージ157によって出力されるQ1信号は、図10に示されるようにつねにデジタル論理のローレベルにある。1つの新規な態様において、もしMDS 142が2分割モードにあって、かつSPENがアサート(assert)されていない すなわちデジタル論理のローレベルにある のであれば、第1のステージ157のフリップフロップは、無力化され、かつ電力が供給されない。電力ダウントランジスタ184は、伝導性にされ、そのことによって、所望のデジタル論理のロー値を第1のステージ157のQ1出力リードの上に接続する。このことが起きるのは、S[0]がデジタル論理のローであれば、ANDゲート186が2入力1出力のマルチプレクサ187の選択入力リードの上にデジタル論理のローを出力するからである。したがって、マルチプレクサ187は、マルチプレクサの上部データ入力リード(「0」と表記)をマルチプレクサの出力リードに結合する。SPENがデジタル論理のローであるから、デジタル論理のロー値は、マルチプレクサ187を通過し、インバータ189によって反転され、その結果、信号CTは、デジタル論理のハイ値になる。もしCTがデジタル論理のハイ値であれば、トランジスタ181は非伝導性であり、電力ダウントランジスタ184は伝導性である。同様にして、マルチプレクサ187がデジタル論理のローを出力している場合、NANDゲート190はデジタル論理のレベルハイを出力し、インバータ191はデジタル論理レベルのローを出力し、およびインバータ192はデジタル論理レベルのハイを出力する。したがって、信号CTがトランジスタ181を非伝導性にすると、その後まもなく信号CTDはデジタル論理のハイに遷移し、トランジスタ182は非伝導性にされる。したがって、供給電圧VDD導線183は、フリップフロップに流れ込む供給電流の変動幅を低減するために時差的方法によって第1のステージ157のプルアップ抵抗器から分断される。CTおよびCTDがデジタル論理レベルのハイ値であるとき、第1のステージ157は、無力化されかつ電力が供給されない。

#### 【0037】

図15は、SPENがデジタル論理のローレベルであるときの2分割モード(S[0]=0)におけるMDS 142の動作を例示する簡略波形図である。信号CTおよびCTDは、デジタル論理のハイレベルである。したがって、たとえ第2のステージ158が、電力を供給されている状態を維持し、SINBUF入力信号を2で分周するために機能するとしても、MDS142の第1のステージ157は、無力化されかつ電力が供給されない。

#### 【0038】

MDS 142の第1のステージ157は、「3分割モード」(S[0]=1)で動作しているとき、3分割動作の始まりにおいて状態を遷移するだけであるということも認識される。もしMDS 142が3分割モードにあるにもかかわらず3分割動作を行うように制御されていないとする。フリップフロップ159によって出力されるQ1信号は、デジタル論理ローレベルを維持する。

#### 【0039】

図16は、大部分の時間においてフィードバック制御信号FMC1はMDS142が3分割動作を行うように制御しないという典型的なシナリオにおける3分割モード((S[0]=1)のMDS142の動作を例示する簡略波形図である。したがって、MDS 142は、大部分の時間において2分割動作を行う。第1のステージ157のフリップフロップのただ一つの機能は、信号FMC1がデジタル論理のローレベルになるときを検出し、NORゲート163の上部の入力リード172上に信

10

20

30

40

50

号Q1のハイパルスをアサートすることである(図11参照)。図11および12に関して上で説明されたように、NORゲート163の上部入力リード172上にデジタル論理のハイ値をアサートすると、NORゲート163は、第2のステージのフリップフロップ162のD入力リード上にデジタル論理のロー値をアサートすることになる。このことは、第2のステージのフリップフロップ162に、SINBUFの次の立ち上がりエッジの際にデジタル論理のロー値をクロックを取り込ませる。その結果、第2のステージのフリップフロップ162は、クロック信号の次の遷移の際にQ2B出力信号(01)をデジタル論理のローレベルにトグルするかわりに、もう1つのクロックサイクルにわたってQ2B出力信号をデジタル論理のハイ値で維持することを強制される。1つの入力クロック周期にわたって2分割動作を中断すること、およびFMC1信号に反応してもう1つのクロック信号にわたってその状態を維持することを第2のステージに強制することを「クロックの飲み込み」(clock swallowing)と呼ぶことがある。Q1のハイパルスは、第2のステージ158にクロックの飲み込み動作を行わせるので、それゆえ「クロック飲み込み制御パルス」と呼ばれる。クロックの飲み込みを開始するローパルスのFMC1を検出すること、およびその結果としての「クロック飲み込み制御パルス」の生成は、第1のステージ157の機能である。

10

## 【0040】

MMD 331のMDSステージの動作によって、モジュラス制御信号MC3は、FMC1のローパルスの前の数クロック周期(a few clock periods)のところでハイに遷移し、かつFMC1のローパルスの後の数クロック周期のところでローに再遷移する信号である。したがって、モジュラス制御信号MC3は、第1のステージ157に電力を供給するために便利に使われ、その結果、第1のステージ157は、電力が供給され、FMC1のローパルスが第1のステージの上に受信される前に信号Q1の適正なロー値を出力しているということになる。FMC1のローパルスが受信されるとき、今は電力が供給されている第1のステージ157は、FMC1のこのローパルスを検出することができ、図16に例示されているように、Q1のクロック飲み込み制御パルスを生成することができる。図16に示されているように、第1のステージ157が信号Q1のクロック飲み込み制御パルスを出力し、かつ第1のステージ157がQ1信号の値をデジタル論理のロー値に戻した後にのみ、MC信号はデジタル論理のロー値に復帰する。信号MC3のデジタル論理ローレベルは、プルダウントランジスタ184をオンにすることによって、電力が供給されていない第1のステージのQ1出力を適正なデジタル論理のローレベルに保持するためには使用することもできる(図14参照)。信号MC3が第1のステージ157に電力が供給されるときを制御するために使用される場合、(図16の波形参照)第1のステージ157は、それがFMC1のローパルスを捕捉すべき時の前に電力が供給され、それがQ1のクロック飲み込み制御パルスを出力すべき時間の総計の間ずっと電力が供給されている状態を維持し、それが信号Q1の値をデジタル論理のローレベルに戻した後まもなくして電源が切られ、およびトランジスタ184がオンにされることによって、第1のステージ157は、それが電力を供給されていないとき信号Q1の値を適正なデジタル論理のロー値に保持する。したがって、1つの新規な実施形態において、信号CTおよびCTDは、MC3信号の論理的反転であるようにさせられる。

20

## 【0041】

図14に戻り、もしS[0]がデジタル論理のハイレベル(3分割モード)であって、かつ電力オーバーライド信号SPENがアサートされていない(SPEN=0)のであれば、ANDゲート186は、デジタル論理のハイ値を出力する。2入力1出力のマルチプレクサ187の選択入力上のデジタル論理ハイ値は、マルチプレクサ187に下部のデータ入力リードを選択させる。マルチプレクサ187の下部のデータ入力リード(「1」と表記)に供給される信号MC3は、マルチプレクサ187を通過し、インバータ189によって反転させられて信号CTを生成する。マルチプレクサ187からの出力としての信号MC3は、遅延素子193および論理ゲート190ならびにインバータ191および192を通過し、その結果として、信号CTDは、図16に示されるような信号CTの遅延バージョンになる。信号CTおよびCTDがデジタル論理のロー値であるとき、第1のステージ157のフリップフロップは、電力が供給される。CTおよびCTD信号がデジタル論理のハイ値であるとき、第1のステージ157のフリップフロップは、電力が供給されな

30

40

50

い。第1のステージが実際に2分割モードの動作を行っているときに3分割モードの第2のステージ157に電力を供給しないことによって、MMD 131の消費電力が低減される。

【0042】

図17は、MDS 142が2分割モードにあるとき（S[0]はデジタル論理のローである）の図14のMDS 142の動作のより詳細な波形図である。電力使用可能オーバーライド信号SPENは、アサートされていない。S[0]=0であるから、信号CTおよびCTDは、デジタル論理のハイ値である。第1のステージ157のフリップフロップは、電力が供給されておらず、およびそのQ1出力信号は、導電性の電力ダウントランジスタ184によって接地電位に保たれている。第2のステージ158のフリップフロップは、繰り返してトグルし、そのことによって、入力信号SINBUFを2で分周する。出力信号Q2Bの周期P1は、入力信号SINBUFの周期の2倍であることに注意せよ。

10

【0043】

図18は、MDSステージ142が3分割モードである（S[0]=1）ときの図14のMDSステージ142の動作のより詳細な波形図である。電力使用可能オーバーライド信号SPENは、アサートされていない。時刻T1の前、モジュラス制御信号MC3は、デジタル論理のローであって、そのことによって、信号CTおよびCTDにデジタル論理のハイ値を持たせ、および第1のステージを電源が切られた状態のままにしておく。Q1とラベルづけられている波形は、第1のステージ157の電源が切られている時を示している。時刻T1において、フィードバック・モジュラス制御信号MC3は、ハイに遷移する。MC3のハイ値は、マルチプレクサ187およびインバータ189を通過し（図14参照）、その結果、信号CTは、時刻T2からスタートするデジタル論理ロー値に強制的にさせられる。CTとラベルづけられている波形に示されるように、信号電圧は、比較的ゆっくり減少していく。MC3のハイ値はまた、遅延素子193、NANDゲート190、インバータ191およびインバータ192を通過し、その結果、信号CTDは、時刻T3からスタートするデジタル論理のロー値に強制的にさせられる。信号Q1の電圧は、時刻T4まで、適正なデジタル論理のロー値に対応するある電圧まで増加することがわかる。第1のステージ157は、時刻T4までに電源が入れられると考えられる。その後、図18の波形図における486ナノ秒の前後において、フィードバック・モジュラス制御信号FMC1は、デジタル論理のロー値をパルスする。図14の回路の第1のステージ157は、この時点では電力が供給されていてかつ機能しているが、時刻T5において上記デジタル論理のロー値をクロックで取り込む。その結果は、第1のステージのQ1出力がデジタル論理ハイ値へ遷移することであり、そのことによって、「クロック飲み込み制御パルス」を生成する。図18のQ1波形におけるラベル「CML1」は、上記デジタル論理ハイ値を表示している。クロック飲み込み制御パルスは、第2のステージ158が次のSINBUFサイクルにわたってトグリングを中断し、もってSINBUFの1つのクロックサイクルを「飲み込む」ことを引き起す。第2のステージ158のQ2B出力は、それが時刻T5の前に行なったようにトグルすることを継続するのではなく、1つの追加的なSINBUFクロックサイクルにわたってデジタル論理のハイ値を維持することに注意せよ。信号Q1のデジタル論理値は、デジタル論理のローレベルに復帰する。時刻T5から時刻T6までのMDSステージ142の周期P2は、3つのSINBUFクロック周期である。時刻T6で終了する3分割動作の後、第2のステージ158は、2分割トグリング動作に復帰する。時刻T7において、モジュラス制御信号MC3は、デジタル論理ローレベルに遷移し、そのことによって、CTおよびCTD信号をそれぞれ時刻T8およびT9までにそれらのデジタル論理ハイ値に復帰させる。信号CTおよびCTDがそれらのデジタル論理ハイ値に戻ると、第1のステージは再び電源が切られ、トランジスタ184は再び導電性になる。その結果、第1のステージのQ1出力は、適正なデジタル論理ローレベルに保持される。図14のMDSアーキテクチャを利用する図4のMMDの1つの特定の実施形態において、上において説明したようにCMLのMDSステージの第1のステージに電力を供給しないことは、結果として、MMD電力供給電流消費の20パーセントの減少をもたらす。電力供給電流消費におけるこの減少は、MMDの周波数分解能を下げるうことなく、またはMMDの低いスプリスアス雜音性能を犠牲にすることなく、達成される。

20

【0044】

30

40

50

図19は、1つの新規な態様に一致するある方法の流れ図である。モジュラス分周器ステージ(MDS)は、入力信号を2または3のいずれかで分周することを制御することが可能である。MDSは、第1のステージおよび第2のステージを持っている。図14のMDSは、第1のステージおよび第2のステージを持っている適切なMDSの一例である。最初に、MDSは入力信号を3で分周するために使用される(ステップ200)。MDSが3で分周しているとき、第1のステージおよび第2のステージの両方に電力が供給されている。次に、第2のステージの電源を切ることなく、第1のステージの電源が切られる(ステップ201)。1つの例において、MDSは、第1のステージの電源が切られている間ずっと入力信号を2で分周していく。この電源切り(power-down)の後、第1のステージが電源が切られている状態にあるとき入力信号を2で分周するためにMDSが使用される(ステップ202)。第1のステージが電源が切られている状態にあるときMDSが入力信号を2で分周することが終わると、MDSの第1のステージは電源が入れられる(ステップ203)。1つの例において、この電源入れ(powering-up)は、MDSによってこれから行なわれるべき3分割動作を予期して行われる。処理フローは、ステップ200に復帰し、その結果、MDSは、入力信号を3で分周するために使用される。

#### 【0045】

ある特定の実施形態が指図の目的のために説明されているが、本件特許文献の教示は、一般的適用可能性を有し、上で説明された特定の実施形態に限定されるものではない。上に記された電力節約技術は、CMOSおよびCML以外の論理アーキテクチャを使用する回路に適用することができる。CML対CMOSの中で実現される図4のMMDの部分は、変更されることができる。1つの実施形態において、MDS 144の出力とMDS 145の入力の間に1つのバッファが配置されている。図6のフリップフロップ154のSB入力カーリードにいたるMC1信号バスの中に、同じタイプのバッファが配置されている。このタイプのバッファは、4つのNチャネル電界効果トランジスタM1-M4、2つのプルダウン抵抗器R1およびR2、およびコンデンサC1を含んでいる。M1およびM2のドレインは、VDDに接続される。M1のソースは、M4のゲートおよびM3のドレインに接続される。M2のソースは、M3のゲートおよびM4のドレインに接続される。R1は、M3のソースと接地の間で接続される。R2は、M4のソースと接地の間で接続される。M3および/またはM4のゲートに結合されるプルアップ抵抗器はない。バッファへの信号入力(入力信号IN)は、M1のゲートに供給される。この入力信号の反転(入力信号INB)は、M2のゲートに供給される。コンデンサC1の1つの端子はM3のソースに結合され、またその端子はM4のソースに結合される。バッファは、2つの出力ノードを持っている。出力ノードの1つは、M1のソースである。出力ノードの他方は、M2のソースである。これらのノードは、隣接する導線LINE1およびLINE2を介して、駆動されている負荷と(容量結合ではなく)直接的に結合されている。1つの実施形態において、LINE1は、負荷中のNチャネルのトランジスタM5のゲートと直接接続されている。LINE2は、負荷中のもう1つのNチャネルのトランジスタM6のゲートと直接接続されている。負荷と容量的に結合される通常のCML駆動装置とは対照的に、上で開示されたバッファは、負荷と直接的に接続されている(DC結合)。バッファは、負荷の動作点に自動的にバイアスをかける。M5のゲート上のDCバイアス電圧は、M4のゲート・ソース間電圧とR2における降下電圧の和に概ね等しくなるように自己バイアスされている。このバイアスによって、バッファおよび負荷のバイアス点は同じであり、またバッファは負荷に対して容量的に結合される必要がなく、むしろ負荷と直接接続されている。駆動装置が負荷に対して容量結合されている従来のCML駆動装置において、比較的低周波数の信号(例えば10メガヘルツ以下の周波数の信号)は、容量結合における容量を通過することに困難性がある。そのような信号の90パーセントは、回路によって拒絶される可能性がある。したがって、そのような低周波数の信号の場合、負荷における信号の強度は小さくなっている。結果として、そのような低周波数信号が回路動作の間にバッファを通過することになっている場合、従来の回路は役に立たない可能性がある。上で説明された直接結合バッファにおいては、バッファ/負荷間の直接接続のために低周波数信号中のエネルギーがより多く転送され、またバッファは低周波数のコンポーネント(例えば5キロヘルツまでの周波数)を有する信号が回路動作の間にバッファを通過することになっている場合にその効用を発揮する。従来のバッファ回路の容量を省く

10

20

30

40

50

ことによって、回路全体のサイズは、バッファと負荷の間の接続の長さと同様に、より小さいものにされる。接続をより短くかつより小さくすることができる。接続の寄生容量もより少なくなる。死の領域が救われる。回路動作の間にバッファがこれらの寄生容量を駆動する必要がないために、従来のバッファに比べて、消費電力が低減される。

【0046】

図6の出力同期装置は、高速MMD入力信号を使用せずに同期化する出力同期装置の一例にすぎない。他の例において、信号MC1およびMC1Bは、CMLラッチのセットおよびリセット入力リードに供給される。CMLラッチのQ出力リードは、D型フリップフロップのクロック入力リードに結合される。フリップフロップのD入力は、デジタル論理のローに保たれる。図4の06信号の論理的反転は、フリップフロップの非同期セット入力リード(SB)に結合される。SOUT信号は、フリップフロップのQ出力リード上に出力される。今説明した回路にくわえて、MC1を使用して所望の信号SOUTの1つのエッジを生成し、またMDS出力信号を使用してSOUTの次のエッジを生成するその他の回路を使用することができる。

10

【0047】

したがって、以下に記される請求項の範囲から逸脱することなく、上で説明された特定の実施形態のさまざまな特徴のさまざまな修正、翻案、および組み合わせを実施することが可能である。

【図1】

図1

FIG. 1

【図2】

図2

FIG. 2

【図3】

図3

FIG. 3

【図 1 1】

FIG. 11

【図 1 3】

FIG. 13

【図 1 2】

FIG. 12

【図 1 4】

FIG. 14

【図 1 5】

FIG. 15

【図 1 6】

FIG. 16

【図17】

【図18】

【図19】

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2007/072215 |

|---------------------------------------------------|

|                                                       |

|-------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>INV. H03K23/00 |

|-------------------------------------------------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| According to International Patent Classification (IPC) or to both national classification and IPC |

|---------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| B. FIELDS SEARCHED |

|--------------------|

|                                                                                                   |

|---------------------------------------------------------------------------------------------------|

| Minimum documentation searched (classification system followed by classification symbols)<br>H03K |

|---------------------------------------------------------------------------------------------------|

|                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------|

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched |

|-------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------|

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used) |

|----------------------------------------------------------------------------------------------------------------------------|

|                             |

|-----------------------------|

| EPO-Internal, WPI Data, PAJ |

|-----------------------------|

|                                        |

|----------------------------------------|

| C. DOCUMENTS CONSIDERED TO BE RELEVANT |

|----------------------------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                             | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | JP 04 318390 A (NIPPON ELECTRIC CO)<br>9 November 1992 (1992-11-09)<br>the whole document                                                      | 1-22                  |

| A         | JP 11 003131 A (NIPPON ELECTRIC CO)<br>6 January 1999 (1999-01-06)<br>the whole document                                                       | 1-22                  |

| A         | SU 771 880 A1 (GREKHNEV VLADIMIR A [SU];<br>GILENOV VLADIMIR N; PAVLYUCHENKOV NIKOLAJ<br>P) 15 October 1980 (1980-10-15)<br>the whole document | 1-22                  |

|                                                                                     |

|-------------------------------------------------------------------------------------|

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. |

|-------------------------------------------------------------------------------------|

|                                                              |

|--------------------------------------------------------------|

| <input checked="" type="checkbox"/> See patent family annex. |

|--------------------------------------------------------------|

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the International filing date

- \*L\* document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the International filing date but later than the priority date claimed

\*T\* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

\*&\* document member of the same patent family

|                                                           |

|-----------------------------------------------------------|

| Date of the actual completion of the international search |

|-----------------------------------------------------------|

|                                                    |

|----------------------------------------------------|

| Date of mailing of the international search report |

|----------------------------------------------------|

|                  |

|------------------|

| 21 November 2007 |

|------------------|

|            |

|------------|

| 28/11/2007 |

|------------|

|                                      |

|--------------------------------------|

| Name and mailing address of the ISA/ |

|--------------------------------------|

|                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax (+31-70) 340-3016 |

|------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |

|--------------------|

| Authorized officer |

|--------------------|

|                    |

|--------------------|

| VILLAFUERTE ABREGO |

|--------------------|

1

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/US2007/072215

| Patent document cited in search report | Publication date | Patent family member(s) | Publication date |

|----------------------------------------|------------------|-------------------------|------------------|

| JP 4318390                             | A 09-11-1992     | NONE                    |                  |

| JP 11003131                            | A 06-01-1999     | JP 3000965 B2           | 17-01-2000       |

| SU 771880                              | A1 15-10-1980    | NONE                    |                  |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,LV,MC,MT,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BH,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,SV,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

(特許庁注：以下のものは登録商標)

1. GSM

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100100952

弁理士 風間 鉄也

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100070437

弁理士 河井 将次

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 ナラソング、チューチャーン

アメリカ合衆国、カリフォルニア州 92677、ラグナ・ニゲル、デヘニー 24

(72)発明者 ス、ウェンジュン

アメリカ合衆国、カリフォルニア州 92131、サン・ディエゴ、バリーストック・コート 1

0 7 3 3

F ターΔ(参考) 5J106 AA04 BB10 CC01 CC24 CC41 CC53 DD23 DD32 DD43 DD48

GG08 HH01 JJ05 KK40 PP03 QQ12