**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.<sup>6</sup>

H03M 1/02

(45) 공고일자 1999년03월20일

(11) 등록번호 특0169082

(24) 등록일자 1998년10월08일

|             |                                                                                                                                    |             |              |

|-------------|------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|

| (21) 출원번호   | 특1997-705129                                                                                                                       | (65) 공개번호   | 특1998-701733 |

| (22) 출원일자   | 1997년07월28일                                                                                                                        | (43) 공개일자   | 1998년06월25일  |

| (62) 원출원    | 특허 특1989-700516                                                                                                                    |             |              |

| 번역문제출일자     | 원출원일자 : 1989년03월23일                                                                                                                | 심사청구일자      | 1993년07월22일  |

| (86) 국제출원번호 | PCT/US 88/02499                                                                                                                    | (87) 국제공개번호 | W0 89/01264  |

| (86) 국제출원일자 | 1988년07월22일                                                                                                                        | (87) 국제공개일자 | 1989년02월09일  |

| (81) 지정국    | EP 유럽특허 : 오스트리아 벨기에 스위스 리히텐슈타인 독일 스웨덴<br>프랑스 영국 이탈리아 룩셈부르크 네덜란드                                                                    |             |              |

| (30) 우선권주장  | 국내특허 : 오스트레일리아 브라질 핀란드 일본 대한민국 러시아<br>7/077,496 1987년07월24일 미국(US)<br>7/110,002 1987년10월19일 미국(US)<br>7/110,201 1987년10월19일 미국(US) |             |              |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 특허권자 | 모토로라 인크.                                             |

| (72) 발명자  | 미합중국 60196 일리노이주 샤움버그 이스트 알곤퀸로드 1303<br>헬퍼리취 리차드 제이. |

| (74) 대리인  | 미합중국 91320 캘리포니아주 뉴베리 파크 도니갈 애비뉴 154<br>장수길, 이병호     |

**심사관 : 정연용**

**(54) 아날로그/디지털 데이터 저장 시스템**

**요약**

아날로그-디지털 저장 시스템을 갖는 아날로그 통신 시스템은 송신기와, 아날로그 성분을 전달하는 최소한 하나의 원격 수신기를 포함한다. 그 송신기 및 수신기에는 상이한 레이트로 전송된 신호의 아날로그 성분을 전송, 수신 및 기록과 재생하기 위한 회로가 제공되어 있다. 그러한 시스템은 보존 전송 시간에 대해서 높은 레이트로 아날로그 메시지를 전송하고, 낮은 가정 레이트로 메시지를 기록 및 재생하는데 적합하게 되어 있다. 그러한 시스템은 특정 수신기 또는 수신기 그룹에 특정된 어드레스 코드를 인식하도록 프로그램될 수 있고, 어드레스 코드 없이 인입신호에 의해 간단히 활성화시켜 인에이블 신호를 출력하는 디코더를 포함한다. 그 디코더는 메시지가 저장된 RAM의 메모리 섹터에 상응하는 메모리 섹터에 기록 및 재생 레이트를 저장하기 위한 레이트 메모리를 포함한다. 그 시스템은 보존 메모리에 아날로그 성분의 신호를 디지털 형태로 변환하고, 아날로그 포맷으로 재생을 위해 디지털 신호를 아날로그 포맷으로 재변환하기 위한 회로를 더 포함한다. 그 시스템은 인입 아날로그 신호를 정취하고 저장된 메시지를 재생하기 위한 증폭기 수단을 더 포함한다.

## 대표도

## 명세서

### [발명의 명칭]

아날로그/디지털 데이터 저장 시스템

### [기술 분야]

본 발명은 통신 시스템에 관한 것으로, 특히 소정 속도로 아날로그 신호를 전송하고, 이 전송된 아날로그 신호를 디지털 적으로 저장하기 위해 디지털 신호로 변환시키며, 전송된 데이터를 상이한 속도로 재생하기 위해 검색(retrieval)하여 아날로그 포맷으로 재변환하기 위한 시스템에 관한 것이다.

### [배경 기술]

종래 기술로써 여러 이유로 인해 직접 연락할 수 없는 사람에게 메시지를 남길 수 있는 다양한 형태의 페이징(paging) 시스템 및 무선-작동(radio-operated) 시스템이 있다. 예를 들어, 다수의 페이징 시스템들은 가입자(subscriber)의 어드레스 코드와 함께 통상적으로 디지털 형태로 메시지들이 가입자에 대해서 대기(queued) 및 전송(transmitted)되는 매우 복잡한 중앙 처리 장치(central processing facility)를 이용하여 동작한다. 그러한 서비스를 위하여 가입자는 페이징 유니트를 휴대하는데, 그 페이징 유니트는 그 유니트에 대한 어드레스 코드가 선행되는 메시지를 수신할 때 작동되도록(activate) 미리 프로그램 되어 있다. 그로 인해, 그 페이저(pager)는 통상적으로 가청음을 발생하여 메시지가 수신 및 저장되는 것을 가입자에게 알린다. 그 메시지는 페이저 메모리 내에 배치되고, 통상적으로 LED 또는 LCD 디스플레이 스크린 상에 디스플레이 메시지 형태로 검색된다. 이러한 시스템은 효율적이고 디지털 메시지를 보내는 데 거의 전송 시간(air time)을 필요로 하지 않지만, 전송된 메시지는 필연적으로 제한된 지속 기간(limited duration)이 존재하고, 통상적으로 가입자가 가장 가까운 전화기로 가서 메시지 발신자에게 전화를 걸도록 되어 있다. 게다가, 전송된 메시지들이 순전히 전화 번호와 같은 숫자가 아닌 경우, 즉, 숫자와 글자를 포함하는(alphanumeric) 메시지의 경우에는 전송될 숫자 및 글자 메시지를 입력시키기 위해서 특수한 단말기(terminal)가 필요하게 되고, 이러한 형태의 페이징 시스템은 고가의 컴퓨터화된 중앙 메시지 장치가 요구된다.

또한, 미리 프로그램된 수신기에 의해 수신되는 어드레스 코드가 선행하는 오디오(audio) 메시지를 아날로그 형태로 전송하는 송신기를 이용하는 다른 페이징 시스템도 이용할 수 있다. 그러한 메시지는 수신 즉시 재생(play)되고, 일부 유니트에서는 반복 재생(replay)을 위해 메시지가 테이프 카셋트에 기록될 수 있다. 이러한 형태의 페이저는 통상적으로 비교적 부피가 크고, 테이프 레코더의 기계부를 구동시키기 위해 상당히 큰 전력을 필요로하게 된다.

전화 통신 분야에 있어서, 호출된 당사자가 전화 응답을 할 수 없다는 것을 표시하여 나중에 재생하기 위해 메시지를 기록하도록 호출자에게 메시지를 플레이해 주기 위한 1개 이상의 테이프 카셋트를 갖춘 응답기(answering machine)가 사용될 수 있다. 비록, 그러한 응답기가 단일 라인을 이용하여 용이하게 사용할 수 있고, 가격도 점점 적절해져 가고 있지만, 이러한 장치들은 통상적으로 전화기 회로부 자체의 일부로서 이용될 수 없고, 대부분의 현존하는 응답기들은 부피가 크며, 상당한 공간을 차지한다. 더욱이, 다중-라인(multi-line) 사업용 전화기 및 공통라인(common-line) 기록에 쉽게 이용될 수 없다.

또 다른 메시지 서비스 형태는 소위 음성 정상 검색 시스템(voice storage retrieval system: VMS)이 있는데, 그러한 시스템에서는 음성 메시지를 중앙 메시지 저장 장치에 기억시킬 수 있으며, 가입자는 메시지를 검색하기 위해 특정 코드로 사용하여 중앙 컴퓨터의 메모리를 액세스할 수 있다. 그와 같은 시스템은 메시지를 처리 및 저장하기 위해 중앙 시스템 장치에 강력한 컴퓨터를 필요로 한다는 관점에서 비용이 많이 들고, 또한 가입자가 메시지를 수신하기 위해서 전화기를 찾아야 하기 때문에 사용이 불편하다. 또한, 수신인의 부주의로 메시지를 검사하지 못하면 메시지가 적시에 수신되지 않을 수 있다.

경찰 및 소방 통신, 비상 통신 등의 경우와 같은 쌍방향 무선 통신(two way radio communication) 분야에 있어서, 수신자가 때때로 이동 유니트로부터 떨어져 있는 경우에, 대부분의 시스템들은 조작자가 이동 유니트로부터 떨어져 있는 동안에 들어오는 메시지를 수신하기 위해, 이동 수신기에 패치(patch:접속)될 수 있는 휴대용 수신기, 즉 워키-토키를 사용한다. 이러한 장치들은 가격이 비싸고, 대부분의 경우, 신뢰성이 있고 가격이 저렴한 메시지 저장 시스템이 이동 유니트에 사용할 수 있는 경우에는 전적으로 불필요하게 된다. 조작자가 이동 유니트로부터 떨어져 있을 때 미리 기록된 메시지를 전송하고 들어오는 메시지를 기록하기 위한 전화 응답기와 유사한 소정의 시스템들이 사용될 수 있다. 이 시스템들은 부피가 크고, 신뢰성이 없으며, 무선 통신이 관련하여 호환성이 없다.(inflexible)는 것이 알려져 있다.

더욱 정교한 시스템이 버크(Burke) 등의 미국 특허 제 4,468,813호 및 버크 등의 미국 특허 제 4,495,647호에 공포되어 있다. 이 시스템은 이동 유니트에 디지털 형태의 명령 프로그램 패킷(command program packet)을 보내는 기지 유니트(base unit)를 필요로 하고, 이동 유니트는 아날로그 형태의 메시지를 수신하기 위해 명령 프로그램에 응답하도록 프로그램되어 있다. 이동 유니트는 명령 프로그램에 응답하여 메시지를 디지털 형태로 변환하여 저장시키고, 기지 유니트에 의해 디지털 형태로 보낸 종료 명령에 응답하여 이동 유니트 기록 시스템은 작동을 중지한다(deactivated). 이동 유니트의 조작자는 디지털 메시지를 아날로그 형태로 반복 재생(replay) 할 수 있다. 상기 미국 특허에 기술된 것과 같은 시스템에서는 명령 프로그램 패킷 및 종료 코드 신호를 발생시킬 수 있는 복잡한 인코딩 시스템이 기지 송신기(base transmitter)에 필요하다. 더욱이, 기지 송신기는 상기 특허에 기술된 형태로 명령 패킷을 전송할 수 있어야 한다. 또한, 이동 유니트는 명령에 기술된 형태로 명령 프로그램 패킷을 수신 및 디코딩(decoding)하여, 자체 명령 프로그램 패킷을 기지 유니트로 다시 전송할 수 있어야 한다. 이러한 시스템에 사용되는 이동 유니트는 2개의 별도의 전원(power supplies)이 필요하며, 이는 페이저 등과 같은 휴대용 수신기용으로서는 부적합하다.

또한, 통신 분야, 특히 무선 통신 분야에서는, 전송 시간을 최소로 유지하는 것이 바람직하다. 무선 통신에서는, 가용 채널들은 혼잡하게 되어 있기 때문에, 전송 시간(air time)에 대해서 상당한 경쟁이 되고 있다. 따라서, 디지털 포맷이 보다 적은 전송 시간을 필요로 하기 때문에, 대부분의 페이징 시스템은 디지털 포맷으로 메시지를 전송한다. 그러나, 수신된 메시지들은 작은 LED 및 LCD 디스플레이 스크린 상에 디스플레이되는 짧은 기록 메시지로 제한되고, 이들 메시지는 통상적으로 가입자로 하여금 전화기로 가서 메시지 발신자를 호출하게 하는 형태로 제한된다. 이러한 시스템은 메시지의 용량이 제한될 뿐만 아니라 송신기의 부품이 고가이며, 통상적으로 디지털 데이터를 전송하고, 가입자를 위해 아날로그 메시지를 저장하기 위한 중앙 집중화된 컴퓨터 메시지 장치가 요구된다.

따라서, 아날로그 메시지를 원격 유니트(remote unit)에 직접 전송하기 위한 시스템으로서, 전송 시간(air time)을 절약하기 위해 아날로그 메시지들을 고속으로 전송하고, 원격 유니트에서 수신 및 기록하여 가정 상태로 복원하기 위해 저속으로 재생(playback)시키는 시스템을 제공하는 것이 매우 바람직하다. 당연한 결과로서, 소정의 아날로그 데이터를 저속으로 전송하고 다시 가정 포맷으로 복귀시키기 위하여 메시지를 고속으로 재생하는 것이 바람직하다. 이러한 전송 절차는 통상적으로 전송되는 데이터의 충실도(fidelity)에 악영향을 미치는 전화선을 통해 음악 및 그 이외의 다른 고충실도(high fidelity)아날로그 데이터를 전송하는 경우에 유리하게 실행된다. 이러한 경우에, 데이터의 충실도를 유지하면서 충실도의 손상없이 정상 속도로 다시 재생하기 위하여 데이터를 저속으로 전송하는 것이 바람직하다.

#### [발명의 요약]

본 발명에 따라, 음성 메시지(voice message)가 뒤따르는 어드레스 코드(address code)를 포함하는 통신 패킷(communication packet)을 선택적으로 어드레싱하여 전송하는 1개 이상의 송신국(transmitting station)과, 대응하는 미리 설정되어 저장된 어드레스를 각각 갖고 있는 수신국(receiving station)으로서, (1)상기 통신 패킷에 응답하는 수신 회로, (2)상기 수신 회로에 접속되어, 상기 통신 패킷에 응답하여 기록 인에이블 신호(record enable signal)를 발생하는 디코더, 및 (3)제1데이터 레이트(first data rate)로 상기 기록 인에이블 신호에 응답하여 상기 통신 패킷의 상기 음성 메시지를 저장하기 위한 디지털 메모리를 각각 포함하는 2개 이상의 수신국을 포함하는 디지털 음성 저장 통신 시스템을 제공하는데, 여기서, 디지털 데이터를 아날로그 데이터로 변환시키기 위한 신호 변환 회로(signal converting circuit)와, 상기 제1데이터 레이트와 상이한 제2데이터 레이트로 상기 디지털 메모리로부터 상기 저장된 음성 메시지를 나타내는 데이터를 클럭킹(clocking)하기 위한 타이밍 회로(timing circuit)를 더 포함하는 것을 특징으로 한다.

본 발명에 따라, 음성 메시지를 포함하는 아날로그 신호들이 제1데이터 레이트로 전송 및 수신되고, 디지털 포맷으로 변환되며, 검색을 위해 디지털 포맷으로 메모리 내에 저장되고, 아날로그 포맷으로 재변환되며, 원활 때 제2데이터 레이트로 재생되는 페이징 시스템, 전화기, 다중 선로 전화기(multi-line telephones), 셀룰러(cellular) 전화기, 구내 및 원격 전송 시스템(interior and telemetry system), 쌍방향 무선 장치 등과 같은 통신 시스템에 쉽게 적용되는 아날로그-디지털 데이터 저장 시스템이 제공된다.

본 발명의 데이터 저장 시스템은 저렴한 비용으로 혼존하는 전화기 및 무선장비에 용이하게 설치되면서, 매우 낮은 전력으로 동작된다. 이러한 데이터 저장 시스템은, 예를 들어 디지털 코드, 톤(tone), 이중-톤 다중 주파수(dual-tone multiple frequency : DTMF)와 같은 임의의 종래의 아날로그 또는 디지털 어드레스 인코더에 의해 작동되기에 적합하고, 음성 작동(voice activated : VOX)될 수도 있다. 본 발명에 따른 시스템의 사용은 특수 변형된 송신기가 전혀 필요치 않다. 또한, 메시지 수신 이후에 회로부를 비작동(deactivate)시키기 위한 수단은 데이터 저장 시스템 자체 내에 포함되고 있고, 어드레스 코드를 제외(이는 바람직하지만 중요한 것은 아님)하고, 수신 유니트에서 메시지의 수신과 기록을 제어하기 위한 명령 데이터의 패킷 및 수신 유니트를 비작동시키기 위해 메시지의 종료부에서 종료 코드(termination code)를 전송할 필요가 없다.

본 발명에 따른 아날로그-디지털 데이터 저장 시스템은 적합한 송신기로부터 아날로그 성분(analog component)을 전달하는 인입 신호(incoming signal)를 수신 하기 위한 수신기 수단(receiver means)을 포함한다. 바람직하게는 특정한 데이터 메모리 시스템에 지정된 지정 어드레스 코드(designed address

code)가 아날로그 신호를 선행한다. 본 시스템은 후술하고 도시하는 바와 같이 인에이블 신호(논리하이)를 발생하여 시스템 회로부를 작동시키기 위해 인입 신호에 의해 작동되는 인에이블 수단을 더 포함한다. 이러한 인에이블 수단은 특정한 수신기 또는 수신기 그룹에 지정된 어드레스 코드를 인식하도록 프로그램된 디코더를 포함할 수 있다. 또한, 그러한 인에이블 수단은, VOX 회로의 경우와 같이, 어드레스 코드 없는 인입 신호에 의해 작동되어 인에이블 신호를 발생할 수도 있다. 또한, 본 시스템은 인입 아날로그 데이터를 디지털 포맷으로 변환시키기 위한 변환 수단과, 변환된 디지털 데이터를 저장하기 위한 메모리 수단을 포함한다. 그러한 변환 수단은 디지털 신호를 아날로그 포맷으로 재변환시키기 위한 회로부를 더 포함한다. 디코더 수단으로부터의 인에이블 신호에 응답하여 변환 수단 및 디지털 메모리 저장 수단을 작동시키기 위한 제어 수단이 제공된다. 바람직한 실시예에 있어서, 제어 수단은 메시지 종료 또는 미리 설정된 기간 이후에 변환 수단 및 메모리 수단을 비작동 상태로 만들도록 동작한다. 임의의 저장된 메시지를 아날로그 포맷으로 재생하기 위해 변환 수단 및 메모리 수단을 작동시키기 위한 스위칭 수단이 포함된다. 본 시스템은 기록 및 재생 모드(record and playback modes)를 수동으로 작동시키기 위한 스위칭 수단과, 인입 아날로그 신호의 청취 및 저장된 메시지의 재생을 위한 증폭기 수단을 더 포함한다.

본 발명의 시스템은 단일-라인 및 다중-라인 전화 시스템, 인터콤(intercom)시스템과 같은 유선 통신 시스템 및 무선 통신 시스템에 용이하게 적용될 수 있다. 그러므로, 본 발명의 시스템은 페이징 시스템, 쌍방 무선 장치, 셀룰러 전화기, 종래의 전화 인터콤 시스템 및 원격 전송 시스템에 이용될 수 있다. 본 발명의 바람직한 형태에 있어서, 본 시스템은 고속으로 전송되는 아날로그 메시지를 수신하고, 메모리로부터 검색 후에 이러한 메시지들을 재생시켜, 이동하는 조작자(operator)에 의해 메시지를 알 수 있도록 적용된다. 이러한 방식으로, 무선 전송 시간(air transmission time)은 상당히 단축되는데, 이는 할당된 주파수들이 제한되고, 다수의 가입자들이 그 시스템을 사용하는 페이징 시스템과 같이 무선 주파수들이 혼잡한 분야에서는 결정적으로 중요하다.

본 발명의 한 실시예에 따르면, 본 시스템은 데이터 입력용 제어 터미널과 통신하면서 아날로그 메시지 발신용 송신기와 통신하는 송신 버퍼(transmission buffer)를 구비하는 송신기 수단을 포함한다. 본 시스템은 송신기와 호환 가능한(compatible)하면서 신호를 수신하기 위한 수신기를 포함하는 수신기 그룹(receiver group)을 더 포함하고, 수신된 신호를 메모리에 저장하고, 메모리로부터 신호를 검색하여, 이용 가능한 포맷(usable format)으로 변환시키기 위한 회로부를 더 포함한다. 신호를 메모리에 저장하기 이전에 또는, 메모리로부터 신호를 검색한 이후지만, 재생하기 이전에 신호 레이트를 변환할 수 있다는 것을 알 수 있다. 또한, 신호는 제1레이트로 전송되고, 제2레이트로 전송되고, 제2레이트로 기록되며, 제3레이트로 재생될 수 있다. 송신기 버퍼에서 인코딩 수단은 메시지가 특정 수신기에 전송될 수 있도록 수신기 그룹에 의해 인식될 수 있는 어드레스 코드를 인코딩하는 것이 바람직하다.

본 발명의 시스템은 단일-라인 및 다중-라인 전화 시스템 및 인터콤 시스템과 같은 유선 통신 시스템뿐만 아니라 무선 통신 시스템에 용이하게 적용될 수 있다. 특히, 본 시스템은 페이징 시스템 및 원격 전송 시스템에 유용하고, 고충실도가 요구되는 음악 및 그 이외의 다른 데이터를 전송하기 위한 시스템에 유용하다. 본 발명의 시스템은 시판중인 페이징 장치와 같은 종래의 송신 및 수신 장비에 용이하게 설치되는 회로부를 사용한다.

### [도면의 간단한 설명]

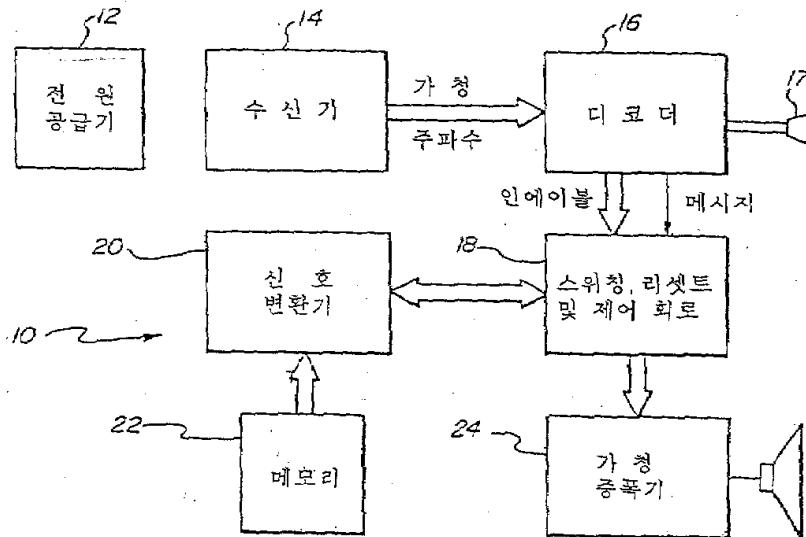

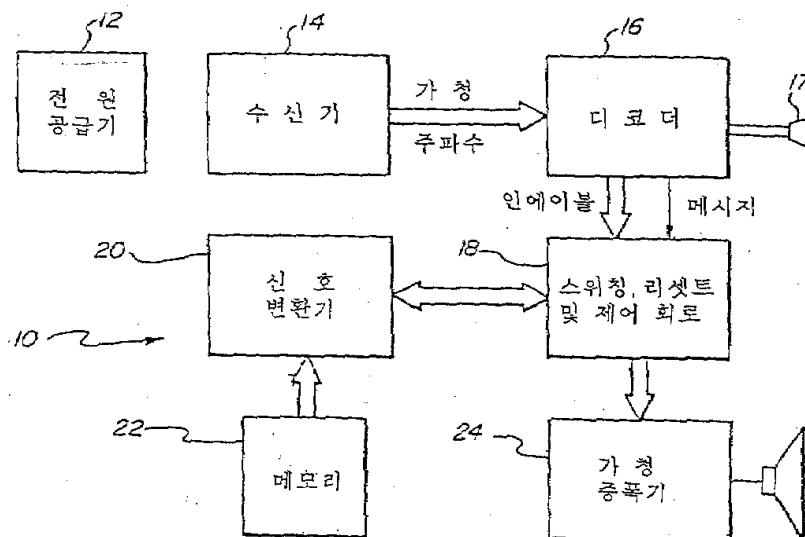

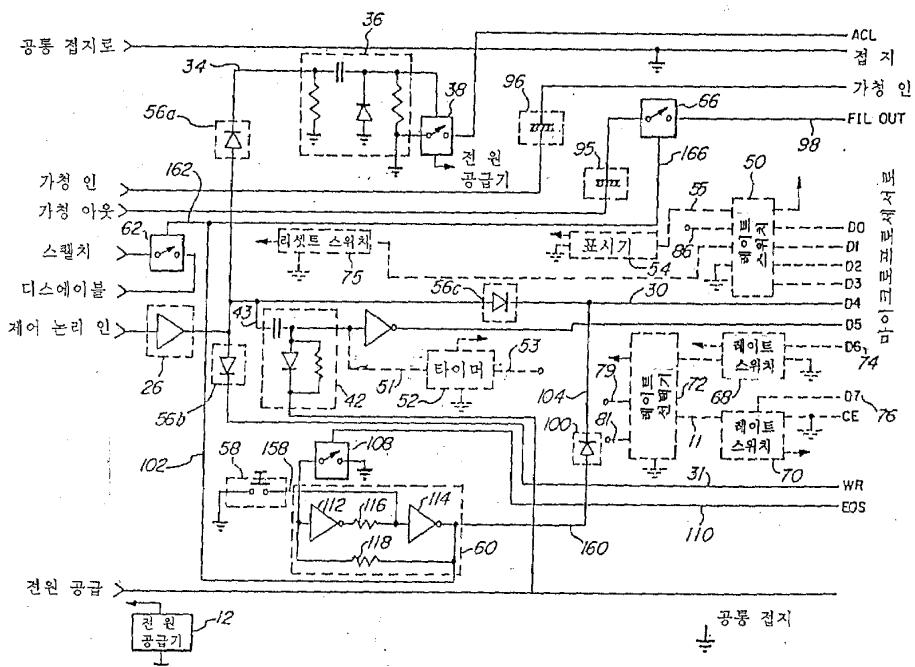

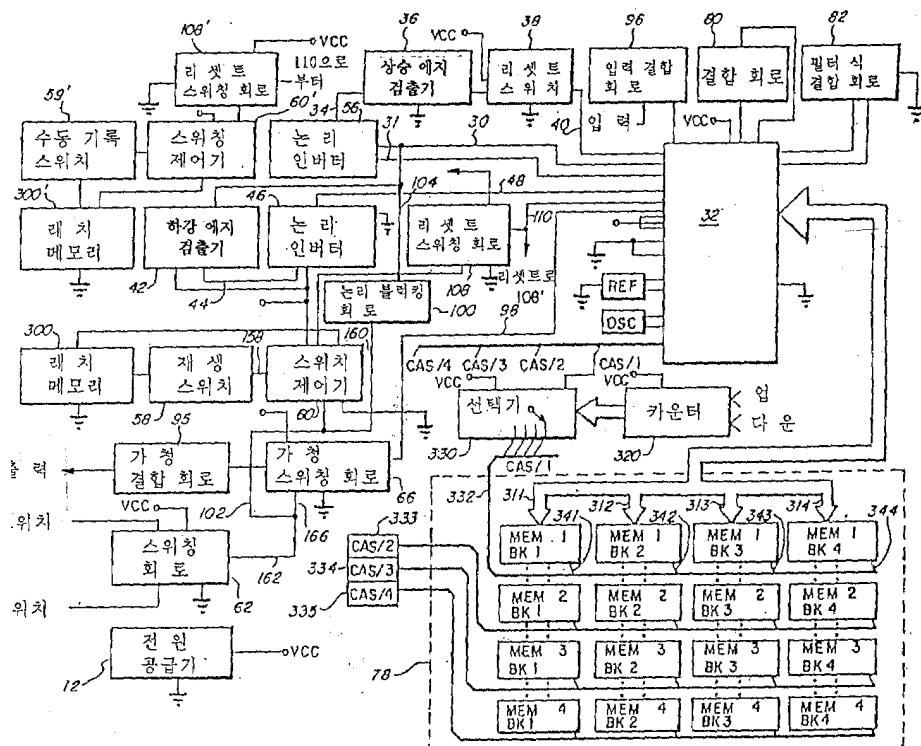

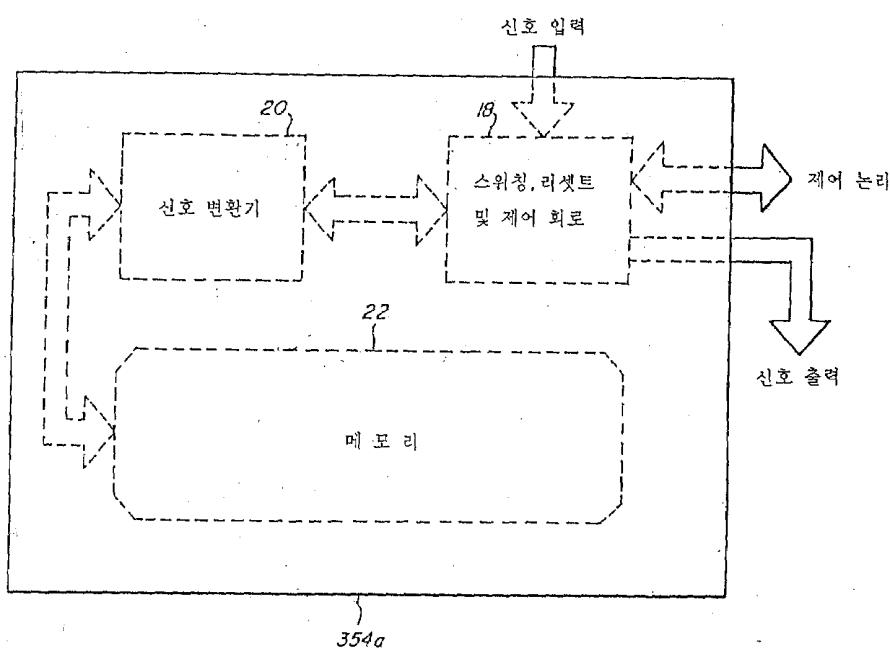

제1도는 본 발명에 따른 디지털 음성 저장 시스템의 블록도이다.

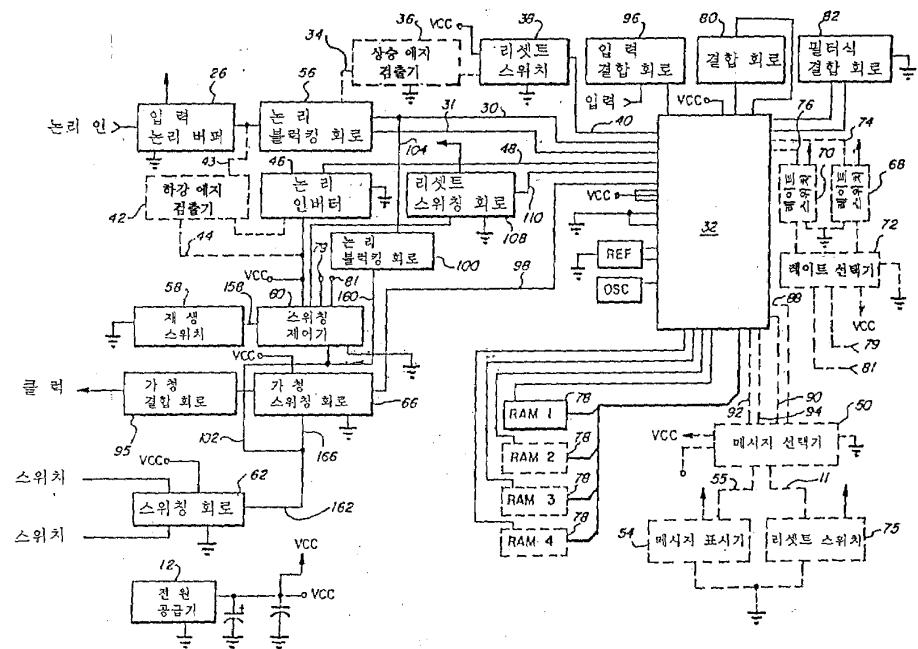

제2도는 제1도의 오디오 변환 회로, 스위칭 회로 및 제어 회로의 개략도이다.

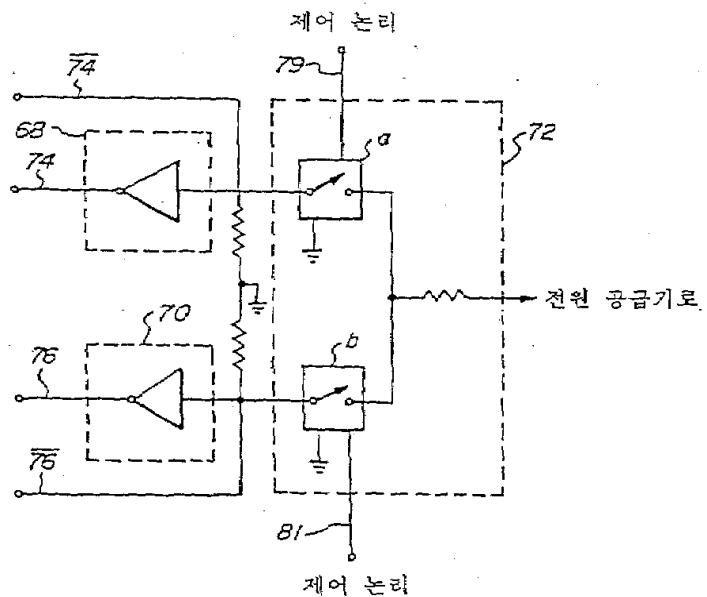

제3도는 제2도의 스위칭 회로를 보다 상세하게 도시한 개략도이다.

제4도는 메시지 레이트 제어 회로부를 설명하는 제2도의 스위칭 부의 일부 개략도이다.

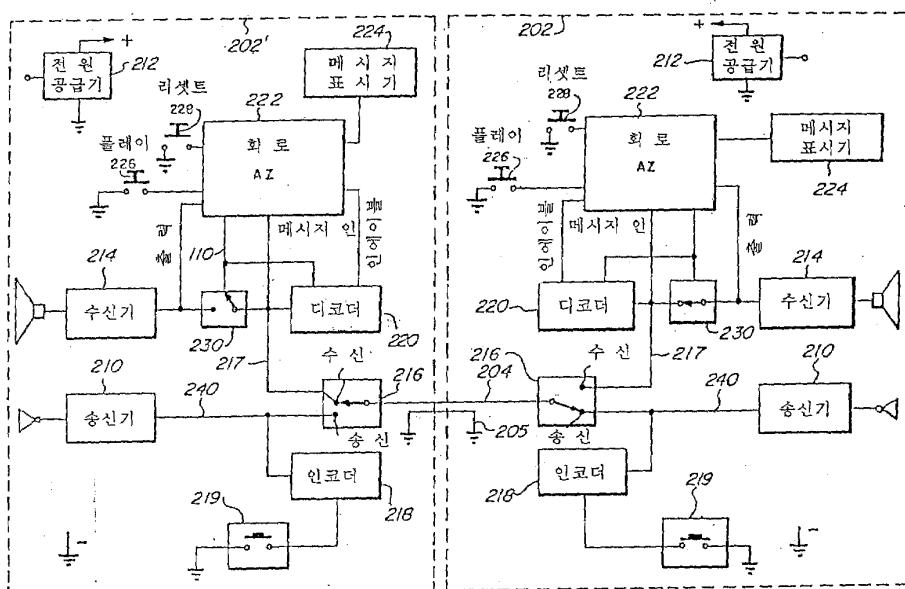

제5도는 본 발명의 음성 저장 메모리 시스템을 사용하는 인터콤 시스템의 블록도이다.

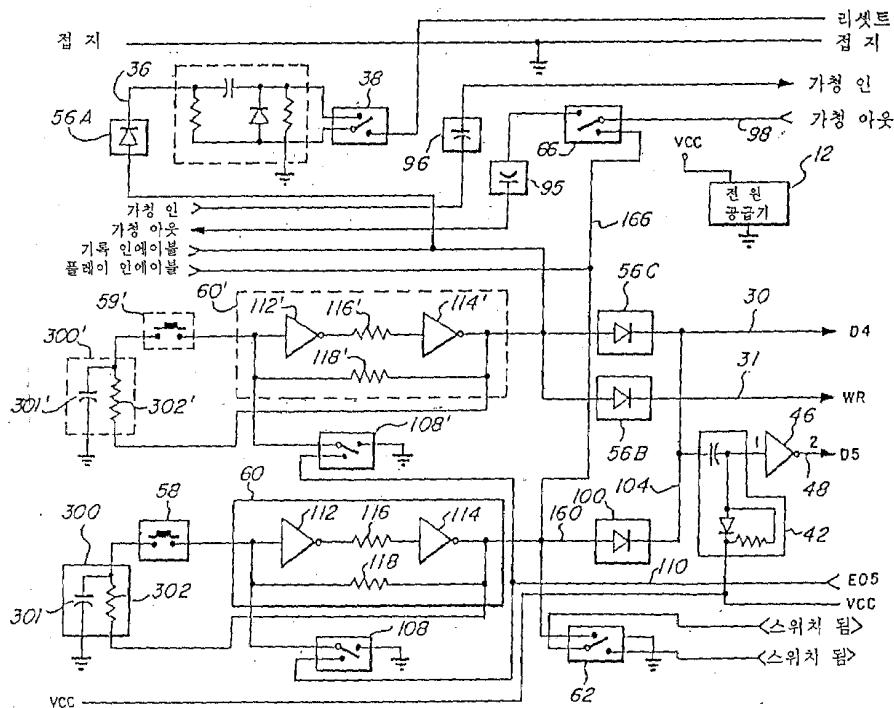

제6도는 기록 기능의 수동 작동용 회로를 설명하는 제2도의 스위칭 회로의 개략도이다.

제7도는 증가된 램(RAM)을 도시한 제2도와 유사한 회로부의 개략도이다.

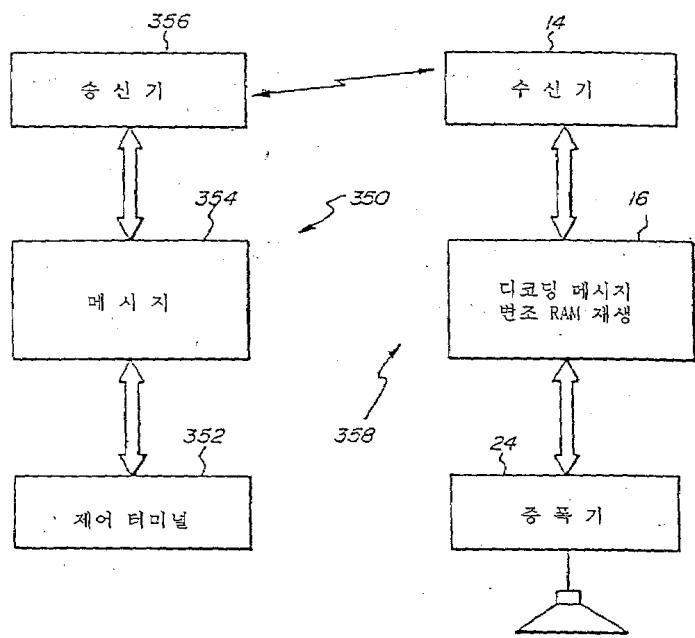

제8도는 본 발명의 가변 레이트 전송 및 재생의 특성을 갖는 아날로그 메시지 페이징 시스템의 블록도이다.

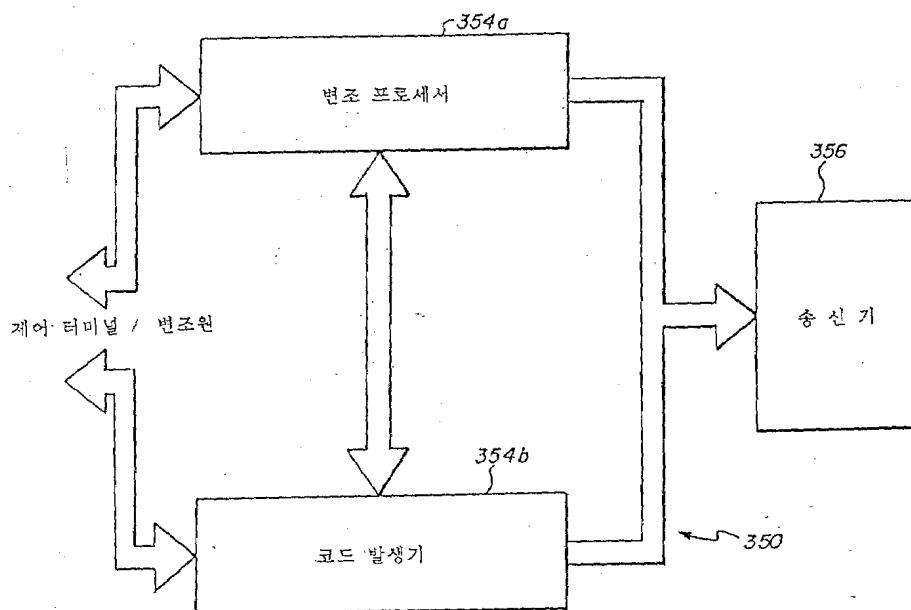

제9도는 본 발명에 따른 송신기 그룹의 블록도이다.

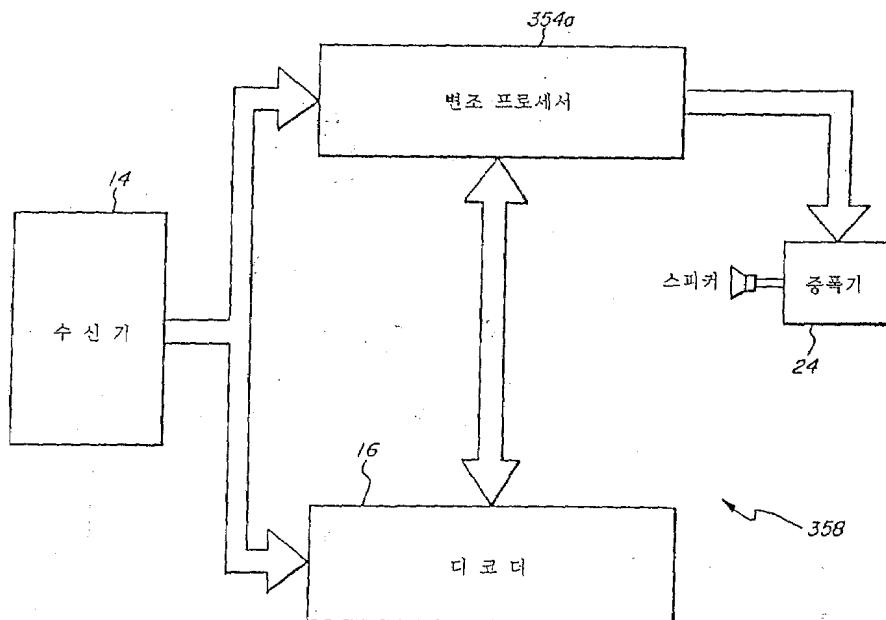

제10도는 본 발명에 따른 수신기 그룹의 블록도이다.

제11도는 송신기 그룹과 수신기 그룹에 사용된 변조 프로세서 회로부의 블록도이다.

제12도는 변조 프로세서의 회로부의 개략도이다.

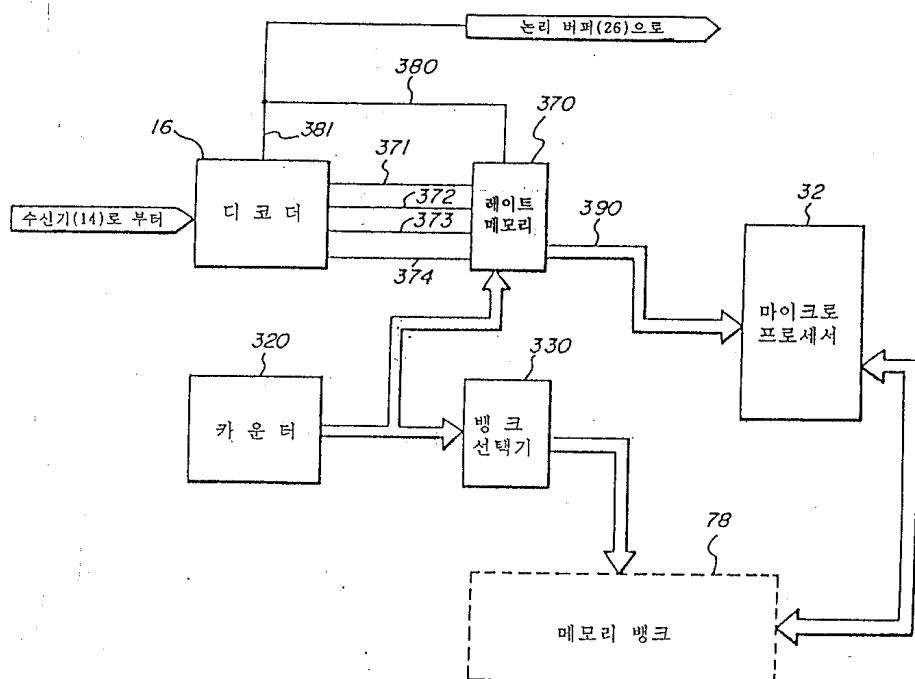

제13도는 수신기 그룹 디코더 회로부의 개략도이다.

### [양호한 실시예의 상세한 설명]

이하, 첨부 도면을 참조하면 본 발명에 대해서 설명하기로 한다.

제1도를 참조하면, 전체적으로 10으로 표시되는, 본 발명에 따라 구성된 아날로그-디지털 데이터 메모리 시스템이 도시되어 있는데, 이 시스템은 전원(12) 및 인입 신호를 수신하기 위한 수신기 수단(14)을 포함한다. 수신기 수단(14)은 오디오 페이징 시스템 또는 쌍방향 무선 시스템에 사용되는 것과 같은 무선 수신기로 구성될 수 있거나, 전화기 또는 전화기와 유사한 형태의 장치로 구성될 수 있다. 또한, 송신기(도시하지 않음)도 시스템(10)내에 포함될 수 있다. 수신기 수단에 의해 수신되는 여러 인입 신호는 임의의 호환 가능한 송신 장치(도시되지 않음)로부터 전송되고, 이 송신 장치는 후술하는 바와 같이 음성 저장 시스템(10)의 수신기 수단(14)으로 사용하기 위해 특수하게 변형될 필요는 없다. 이 송신 매체(transmitting medium)는 예를 들어 무선(radio), 적외선 또는 광섬유(fiber optic)와 같이 유/무선 모두

가능하다. 인에이블 수단(16)은 인입 메시지 신호가 시스템(10)에 어드레스 되는지를 결정하기 위해 인입 신호를 디코더 어드레스와 비교하기 위한 디코더 회로를 갖추고 있다. 이 인에이블 수단(16)은, 예를 들어 디지털 코드, 톤 코드 또는 이중-톤 다중 주파수(DTMF)와 같은 다양한 형태의 인코드된 어드레스를 모니터하도록 변형될 수 있다. 수신된 신호 코드가 디코더 어드레스와 정합(match)되면, 디코더(16)는 음성 저장 시스템(10)의 기록/저장 기능을 작동시키는 인에이블 신호(펄스 또는 연속 신호)를 발생한다. 인입 메시지에 따른 어드레스 코드를 반드시 사용해야 하는 것은 아니지만, 필요에 따라 인에이블 장치는 단순히 오디오 메시지 수신시에 인에이블 신호를 발생하는 음성-작동식 장치(voice activated device)가 될 수 있다. 본 발명의 한 실시예에 있어서, 디코더(16)는 인입 아날로그 신호가 지속되는 동안 연속적인 인에이블 신호를 발생하도록 설계되어 있고, 그 인에이블 신호는 아날로그 신호의 종료시에 종료된다. 디코더(16)로부터의 인에이블 신호의 종료는 아래에 보다 상세히 설명하는 방식으로, 회로부의 다른 부분에 이용되는데, 시스템(10)의 회로를 비작동(deactivate)시켜 대기 모드(dtandby mode)로 복귀시키는데 이용된다. 본 발명의 또 다른 실시예에 있어서, 디코더(16)는 시스템(10)에 어드레스된 인입 메시지를 감시할 때 단일 펄스를 발생하고, 초기의 인에이블 펄스로부터의 미리 설정된 기간 경과 이후에 시스템을 대기 모드로 복귀시키는 타이머 수단이 제공된다.

시스템(10)의 회로를 스위칭, 리셋팅 및 제어하기 위한 제어 수단(18)은 디코더(16)로부터의 인에이블 신호에 응답하여 음성 저장 시스템(10)의 여러회로를 제어하고 작동시킨다. 인입 신호는 신호 변환 수단(20)은 전달되어 아날로그 포맷에서 디지털 포맷으로 변환되고, 디지털 형태로 메모리 수단(22)에 저장된다. 또한, 제어 수단(18)은 인에이블 신호와 무관하게 음성 저장 시스템(10)을 작동시키는 스위칭 회로를 포함하는데, 그 스위칭 회로는 저장된 메시지를 메모리로부터 재호출(recall)하고, 반복 재생(replay)을 위해, 메시지를 디지털 포맷에서 아날로그 포맷으로 재변환시킨다.

오디오 증폭기 수단(audio amplifier means : 24)은 오디오 메시지, 즉 인입 메시지와 메모리로부터 검색된 메시지 모두를 모니터하기 위해 제공된다. 입력 수단(17)은 수신기 조작자에 따라 변환 및 저장을 위해 제어 수단(18)에 메시지를 직접 입력시키기 위해 제공된다.

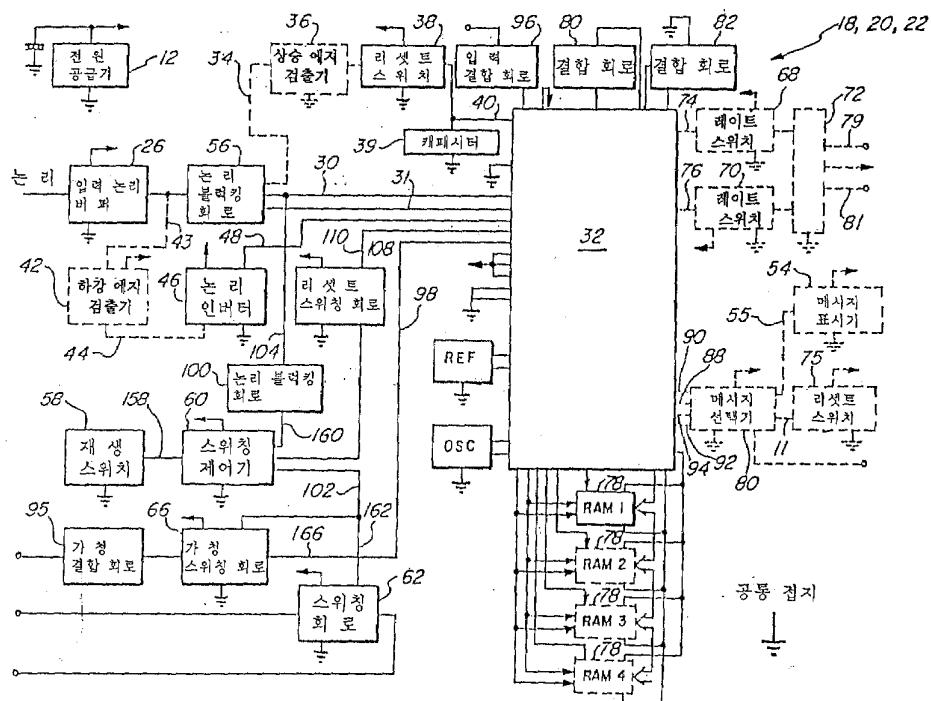

제2도를 참조하면, 제1도에 도시한 데이터 메모리 시스템(10)의 제어 수단(18), 신호 변환 수단(20) 및 메모리 수단(22) 내에 사용된 회로의 개략도가 도시되어 있다. 도2에 도시한 바와 같이, 시스템(10)의 임의 선택적 특성(features)은 가상선(phantom)으로 도시되어 있는데, 이 시스템(10)은 그 임의 선택적 특성에 관계 없이도 작동할 수 있고, 회로내에 포함되는 특정한 선택적 특성의 선택에 있어서는 시스템이 설치된 수신기의 특성 및 시스템용으로 선택된 작동 파라미터에 따라 선택됨을 알 수 있다.

전원 공급기(12)는 임의의 적당한 전력원을 포함하지만, 최소한 3V의 전위를 갖는 것이 바람직하다. 제어 수단(18)은 입력 논리 버퍼(26) 및 논리 블록킹 회로(lologic blocking circuit : 56)를 통해 디코더(16) (도시되지 않음)와 전기적으로 통신한다. 종래의 다이오드로 설계된 논리 블록킹 회로(56)는 개시 라인(start line)(30) 및 기록/재생 라인(record/play line : 31)을 통해 마이크로프로세서(32)에 인에이블 신호(논리 하이)를 분배한다. 인에이블 수단(16)이 아날로그 신호 지속 기간 중에 연속적 논리 하이 상태를 발생시키는 형태로 되어 있을 때, 논리 하이의 종료로서 표시되는 것처럼, 아날로그 신호 종료시에 시스템(10)을 대기 모드로 자동 복귀시키기 위한 회로부를 포함하는 것이 매우 바람직하다. 이러한 목적을 위해, 하강 에지 검출기(trailing edge detector, 42)는 정지 라인(48)을 통해 마이크로프로세서(32)에 접속된 논리 인버터(46)에 접속되는데, 그 목적 및 동작에 대해서는 상세하기 후술한다. 출력 아날로그 신호는 종래 설계의 아날로그 출력 결합부(analog output coupling, 95)를 통해 마이크로프로세서(32)로부터 출력된다. 마이크로프로세서(32)에는 라인(98)에 의해 오디오 스위치(66)가 접속되어, 기록 모드 동안에 인입 아날로그 신호를 모니터한다. 임의 발신자가 이미 메모리 내에 있는 메시지 위해 기록할 수 있도록 시스템(10)을 자동으로 리셋팅할 수 있도록 하기 위하여, 논리 블록킹 회로(56)로부터 라인(34)에 의해 논리 하이 상태를 전달하는 상승 에지 검출기(positive edge detector, 36)를 포함할 수 있다. 그 상승 에지(leading edge) 검출기(36)는 종래 설계로 되어 있고, 리셋트 스위치(38), 캐패시터(39) 및 리셋트 라인(40)을 통해 마이크로프로세서(32)에 접속된다.

재생 스위치(playback switch, 58)가 스위칭 제어기(60)에 접속되어 있는데, 그 스위칭 제어기(60)는 재생 모드를 개시하기 위한 스위치(58)의 작동에 의해 반전될 때까지 라인(102 및 160)에서의 출력이 통상적으로 로우(low : 낮은 전압) 상태로 되는 종래 설계의 쌍안정(bi-stable)[2-안정(two-stable)상태] 회로 내의 저항기(116 및 118)에 의해 결합된 인버터(112) 및 인버터(114)로 구성되며, 이는 제3도에 더욱 명확히 도시되어 있다. 스위칭 제어기(60)의 출력은 리셋트 스위치(108)에 의해 그의 통상적인 로우 상태로 반전될 때까지 하이 상태를 유지한다.

디지털 -아날로그 변환 및 아날로그-디지털의 재변환은 마이크로프로세서(32)에 의해 달성된다. 마이크로프로세서(32)는 Toshiba 제품인 모델 번호 T6668과 같은 시판중인 설계로 되어 있고, 아날로그-디지털 변환 및 디지털 -아날로그 재변환용 회로부가 제공되어 있다. 이러한 변환 회로는 본 기술 분야에 공지되어 있고, 내부 시간 베이스(internal time base)를 발생하고, 각각의 시간 베이스 세그먼트(segment)내의 소정의 미리 설정된 지점에서 아날로그 신호 입력을 샘플링(sampling)한 다음, 샘플링 기간동안에 얻어진 샘플 레벨(sample level)에 응답하여 디지털 출력을 발생함으로써 작동한다. 마이크로프로세서(32)는 총 1024 K 비트(bit) 메모리를 위한 최대 4개까지의 256K 비트의 침(RAM 1-4)(78)과 통시하도록 되어 있다. 도2에 도시한 본 발명의 실시예에 있어서, 시스템(10)은, 모두 4개의 RAM 침(78)을 사용할 때, 8K bps의 비트 레이트로 오디오 메시지를 최대 128초까지 저장할 수 있다. 시스템(10)이 구술 유니트(dictating unit)로서 사용될 경우와 같이, 수신기 조작자가 상당한 양의 메시지 기록을 실행하고자 할 경우에는 필요에 따라 부수적인 메모리 뱅크(memory banks)들이 추가될 수 있다.

동작에 있어서, 아날로그 메시지, 즉 오디오 또는 데이터는 송신기(도시되지 않음)로부터 수신기 수단(14)(제1도에 도시)에 전송된다. 이 메시지는 유선 또는 무선과 같은 임의의 적당한 수단에 의해 송신될 수 있는데, 양호하게는 톤, DTMF, 디지털 등과 같은 임의의 공통적으로 사용되는 형태의 지정된 어드레스 코드가 선행된다. 수신기 수단(14)에 의해 수신된 아날로그 신호는, 적당히 지정된 코드가 존재하거나 인에이블 수단(16)이 VOX 회로인 경우에 입력 논리 버퍼(26)를 통해 논리 블록킹 회로(56)에 인에이블 신호(논리 하이)를 출력하는 인에이블 수단(16)에 전송된다. 전술한 본 발명의 실시예에 있어서, 디코더(16)

는 인입 아날로그 신호의 지속 기간동안 연속적인 논리 하이 상태를 발생하는 형태로 되어 있다. 이 논리 하이 신호는 논리 블록킹 회로(56), 개시 라인(30) 및 기록/재생 라인(31)을 통해 마이크로프로세서(32)로 전달된다. 부수적으로, 논리 블록킹 회로(56)는 논리 하이 신호를 라인(34)을 통해 상승 에지 검출기(36)에 전송하고, 그 검출기는 펄스를 발생하여 리셋트 스위치(38)를 폐쇄(close)시킨다. 이 폐쇄된 상태에서, 리셋트 스위치(38)는 캐패시터(39)를 방전시켜, 순간적으로 리셋트 라인(40)을 논리 로우 상태로 되게 하여, 새로운 메시지를 수신하기 위해 메이크로프로세서(32)를 초기화하고 메모리를 리셋트 시킨다. 설명을 위하여, 오디오(가정) 메시지로서 기재되어 있는 인입 아날로그 신호는 입력 오디오 결합부(input audio coupling : 96)를 통해 마이크로프로세서(32)의 아날로그-디지털 변환 회로에 전송된다. 아날로그 신호가 디지털 포맷으로 변환된 이후에, 변환된 신호는 메모리 내에 저장되기 위해 RAM 칩(78)으로 전송된다. 아날로그 신호의 수신이 중단되면, 인에이블 신호는 하강 에지 검출기(42)를 작동시키는 논리 하이 상태를 종료시켜, 논리 로우 상태로 되게 한다. 이러한 논리 로우 상태는 라인(44)을 통해 논리 인버터(46)에 표시되고, 논리 인버터(46)는 논리 로우 상태를 논리 하이 상태로 반전시키고, 논리 하이 상태는 정지 라인(48)을 통해 마이크로프로세서(32)에 전달되어 변환 및 기록 프로세스를 종료시킨다. 이러한 논리 하이 상태의 종료는 개시 라인(30) 및 기록/재생 라인(31)을 최초의 대기 모드의 논리 로우 상태로 복귀시켜, 시스템(10)을 전력이 거의 소모되지 않는 대기 모드가 되게 한다.

RAM(78)에 저장된 디지털 메시지를 검색 및 재생하기 위하여, 수신기 조작자는 재생 스위치(58)를 작동시켜, 스위칭 제어기(60)가 라인(160), 논리 블록킹 회로(100), 라인(104) 및 개시 라인(30)을 통해 마이크로프로세서(32)에 논리 하이 신호를 발생시켜서 재생 스위치의 재생 기능을 작동시키도록 한다.

동시에, 스위칭 제어기(60)는 논리 하이 신호를 라인(102)을 통해 출력하여 스위치(62 및 66)를 동시에 폐쇄시킨다. 아날로그 포맷으로 재변환된 신호는 라인(98)에 의해 마이크로프로세서(32)로부터 가정 스위치(66) 및 출력 가정 결합기(95)를 통해 증폭기 수단(24)(제1도에 도시)에 보내진다. 메시지의 재현과 재생 완료시에, 마이크로프로세서(32)는 논리 하이 신호를 라인(110)을 통해 리셋트 스위치(108)에 보낸다. 리셋트 스위치(108)는 스위칭 제어기(60)를 그의 원래의 상태로 리셋트하여, 그 출력을 논리 로우 상태로 복귀시키며, 스위치(66 및 62)를 개방 위치로 복귀시키게 된다. 이때, 시스템(10)은 대기 모드에 있게 되고, 변환 및 저장을 위해 새로운 인입 신호를 수신할 준비를 한다.

그러므로, 지금까지 설명된 본 발명의 실시예에 있어서, 메모리내의 메시지를 보호하기 위한 수단이 없고, 적절하게 어드레스된 인입 신호 수신시에 시스템은 자동적으로 리셋트되며, 그 인입 신호는 메모리내에 이미 존재하는 임의의 메시지 또는 데이터 위에 변환 및 저장된다는 것을 알 수 있다. 그러나, 시스템(10)은 선택적 리셋트 회로부 또는 메모리가 재생되지 않은 메시지 또는 데이터로 꽉 채워진 후 메시지 기록 및 변환 모드를 개시하려면 작동되어야 하는 수동 리셋트 회로, 메모리 어드레스 선택 회로부의 추가 및 메모리 확장에 의해, 메모리 내에 일련의 메시지를 저장하고 저장된 메시지를 보호하도록 용이하게 변형될 수 있다.

제2도에 도시한 바와 같이, 상승 에지 검출기(36)는 시스템(10)으로부터 제거되고, 리셋트 스위치(38)는 전술한 방식으로 메모리 내에 이미 저장된 자료 상에 기록하도록 메모리를 리셋트하기 위해 마이크로프로세서(32)를 재개시키기(reinitiate) 위해 수동으로 작동된다. 메모리를 확장하기 위해 최대 3개의 부가적인 RAM 칩(78) (RAM 2, RAM3 및 RAM4로 표시됨)이 포함될 수 있다. 제3도에 명확하게 도시된 바와 같이. 표준 4-비트 코드 카운터 회로인 메모리 어드레스 선택기(50)가 마이크로프로세서(32)에 접속되어, 16개의 상이한 4-비트 어드레스 조합들의 선택이 가능하게 된다. 그러나, 본 기술 분야에서 공지된 바와 같이 2-비트 카운터 회로 또는 수동 선택기(manual selector)와 같은 다른 어드레스 선택기 회로가 사용될 수도 있다는 것을 알 수 있을 것이다. 메시지 어드레스 선택기(50)는 논리 블록킹 회로(56)로부터 논리 하이 상태를 수신하기 위해 개시 라인(30)에 접속된다. 시스템(10)은 각각의 메모리 뱅크가 채워질 때까지 다수의 메시지들을 기록하기 위해서 더 이상의 리셋트 동작을 필요로 하지 않는데, 메모리 뱅크가 채워지면 정지인에이블 신호가 마이크로프로세서(32)내에서 생성되고 이 뱅크에 대한 메모리는 리셋트될 때까지 보호된다. 메모리 내에 저장된 메시지의 재생을 위해 초기 어드레스 설정으로 메시지 어드레스를 리셋트시키기 위해 수동 리셋트 스위치(75)가 제공된다. 이 회로에서 상승 에지 검출기(36)가 삭제된 경우 메시지 재생은, 새로운 인입 아날로그 신호를 수신하고 이미 RAM 내에 있는 메시지 상에 기록하도록 마이크로프로세서(32)를 리셋트시키기 위해, 이미 기술된 방식으로 리셋트 스위치(38)가 수동 작동되어 리셋트 라인(40)을 방전시켜야 하는 것을 제외하고는 이미 기술한 방식으로 일어난다.

(제3도에 도시한) 본 발명의 다른 형태에서는, 시스템(10)은 선택적으로 하강 에지 검출기(42) 대신에 타이머(52)를 사용할 수 있다. 특히, 디코더(16)가 적절히 어드레스된 인입 신호에 응답하여 단일 펄스를 생성하는 형태로 되어 있을 때 타이머를 사용할 필요가 있다.

입력 논리 버퍼(26)로부터 논리 하이 상태를 수신하기 위해 라인(53)을 라인(43)에 접속시킴으로써, 타이머(52)는 논리 하이 상태에 의해 동작이 개시되고, 사전 설정된 시간이 경과하면 타이머(52)는 논리 인버터(46)에 네가티브 펄스(negative pulse)를 생성하고, 논리 인버터는 이미 기술한 방식으로 시스템(10)을 대기 모드로 만들기 위해 정지 라인(48)에 논리 하이 신호를 인가한다.

제2도에 도시한 바와 같이, 시스템(10)은 신호 도달을 알리고 메모리 공간이 충만(full) 상태라는 것을 표시하는 메시지 표시기(message indicator, 54)를 포함할 수도 있다. 메시지 표시기(54)는 광, LED 또는 가정 톤을 발생시키기 위한 장치로 될 수 있다. 이러한 장치들은 본 기술 분야에 공지되어 있고, 그 자체로는 본 발명의 일부를 형성하지는 않는다.

제2도 및 제3도에 도시한 시스템(10)의 실시예는 시스템이 하나의 비트 레이트(bit rate)로 메시지를 수신, 변환 및 기록할 수 있고, 이와 상이한 비트 레이트로 메시지를 재생할 수 있게 하는 기록/재생 레이트 회로부(record/playback rate circuitry)를 선택적으로 포함한다. 초당 최대 비트 레이트는 시스템 내에 사용된 특정한 마이크로프로세서에 의해 결정된다.

제4도에 명확히 도시되어 있는 바와 같이, 레이트 회로부(rate circuitry)는 라인(74 및 76)에 의해 마이크로프로세서(32)에 각각 접속되는 인버터(68 및 70)를 포함한다. 레이트 선택기 스위치(72a 및 72b)를 포함하는 레이트 선택기(72)는 인버터(68 및 70)에 접속된다. 제3도에 도시되어 있는 바와 같이, 레이트

선택기(72)는 재생 속도를 제어하기 위해 라인(79)들에 의해 라인(160)에서 스위칭 제어기(60)의 출력에 접속된다.

도시한 바와 같이, 레이트 선택기 스위치(72a 및 72b)는 모두 개방(open) 상태이고, 인버터(68 및 70)에서는 로우(상태) 입력 및 하이(상태) 출력을 생성하므로, 라인(74 및 76)은 하이 상태로 된다. 이 상태에서는 마이크로프로세서는 동일한 속도, 즉 이 경우에는 32K bps로 기록 및 재생을 하게 된다. 재생 스위치(58)(제2도 및 제3도에 도시)가 폐쇄되면, 스위칭 제어기(60)로부터의 하이(상태) 출력은 라인(79)을 통해 레이트 선택기에 전달되고, 이에 따라 레이트 선택기 스위치(72a)가 작동되고 폐쇄되며, 따라서 인버터(68)의 입력이 하이(상태)가 된다. 이와 같은 구성(configuration)하에서는, 인버터(68)의 출력이 로우 상태이므로, 라인(74)이 로우 상태가 되고, 반면에 인버터(70)의 출력이 하이 상태이므로, 라인(76)이 하이 상태가 된다. 이와 같은 구성 하에서, 마이크로프로세서 16K bps의 속도로 메시지를 재생하게 된다. 비트 레이트 출력은 2-비트 코드에 의해 선택되므로, 기록 및 재생 중에 레이트 선택기 스위치(72a 및 72b) (라인 79 및 81)의 위치에 따라 4가지 레이트가 선택될 수 있다.

시스템(10)의 동작 모드를 수동으로 제어하여 수신기 조작자가 메시지를 재생하게 하고, 임의의 지점에서 재생을 중단(interrupt)시켜 부가의 메시지 또는 데이터를 수신하도록 시스템(10)을 대기 모드로 복귀시키도록 할 수 있다.

제6도를 참조하면, 전형적인 설계의 용량성 메모리 회로(capacitive memory circuit, 300)는 캐패시터(301) 및 저항기(302)로 구성된다. 이 용량성 메모리 회로(300)는 재생 스위치(58) 및 스위칭 제어기(60)에 접속되어 스위치(58)가 일시적으로 폐쇄될 때마다 라인(160)의 출력 상태가 변화되도록 한다. 재생 스위치(58)가 폐쇄되면, 스위칭 제어기(60)의 라인(160)은 하이 상태로 되어, 라인(104) 및 라인(30)상의 논리 하이 상태를 마이크로프로세서(32) (제2도에 도시)에 분배하여 시스템을 재생 모드로 작동시키게 된다. 스위치(58)가 두 번째로 폐쇄되면 논리 하이에서 로우 상태로의 라인(상태) 전이(transition)를 발생시키고 이것이 하강 에지 검출기(42)에 전달된다. 하강 에지 검출기(42)는 신호를 개시하여 논리 인버터(46)에 전달하고, 논리 인버터는 논리 하이 상태로 상기 신호를 반전시키며, 반전된 신호는 정지 라인(48)을 통해 마이크로프로세서(32)에 전달되어 전술한 바와 같이 기록 및 데이터 변환 모드는 종료되고 시스템(10)은 대기 모드로 복귀된다.

기술한 바와 같이, 본 발명의 시스템은 전자 스크래치 패드(scratch pad)로서 사용하기에 적합하므로, 조작자는 조작자가 재생하기 위하여, 또는 이 시스템이 쌍방향 통신에 사용되는 경우에는 나중에 방송(broadcast) 하기 위해 메시지를 메모리 내에 구술할 수 있을 것이다. 이 수동 기록 특징은, 수동 기록 스위치(59)에 접속되는 제2용량성 메모리 회로(300'), 제2스위칭 제어기(60') 및 제2리셋트 스위치(108')에 의해 제공된다. 도시한 바와 같이, 수동 기록 회로는 수동 재생회로와 상보적이다.(complement). 그러나, 수동 기록 스위치를 폐쇄시키면, 스위칭 회로는 라인(34)을 통해 하이(상태)의 신호를 상승 에지 검출기(36)에 인가시키게 되는데, 이에 따라 상승 에지 검출기(36)는 앞서 기술한 바와 같이 마이크로프로세서가 메시지를 수신하도록 초기화하기 위해 펄스를 생성한다. 이 메시지는 제어 회로부(18)와 교신하는 마이크로폰(17)(제1도에 도시됨)을 통해 입력된다.

제7도는 시스템(10)의 RAM(78)의 바람직한 배치의 계통도를 도시한 것이다. RAM(78)은 종래 설계의 4개의 RAM칩을 각각 포함하는 4개의 뱅크(311, 312, 313 및 314)를 포함한다. 그러나, 메모리 용량을 증가시키기 위해 부가적인 RAM칩들을 이들 RAM뱅크에 추가시킬 수도 있고 부가적인 RAM뱅크들을 추가할 수 있다. 카운터 회로(32) 및 RAM 뱅크 선택기(330)는 인입 데이터 및 메시지를 RAM에 어드레스 하고 저장된 자료를 RAM으로부터 재호출하기 위해 제공된다.

도시한 카운터 회로(320)는 뱅크 선택기(330)에 결합된 2진 출력을 갖는 업-다운(up-down) 카운터이다. 뱅크 선택기(330)는 CAS1 라인(라인(332)]을 거쳐 마이크로프로세서에 접속되고, 라인(341, 342, 343 및 344)에 의해 RAM 뱅크(311, 312, 313 및 314)에 각각 접속된다. 부가적인 CAS 라인(333, 334 및 335)이 CAS1 라인[라인(332)]과 동일한 방식으로 메모리 확장을 부가적인 RAM 뱅크 선택기에 배치될 수 있다.

바람직한 실시예에서, 카운터(320)는 기록 및 변환 모드에 응답하여서 업 카운트를, 재생 기능에 응답하여 다운 카운트를 생성하는 방식으로 배치된다. 이러한 배치 하에서는, 최종적으로 기록된 메시지가 가장 먼저 재생된다. 그러므로, 기록 및 변환 동작 중에, 카운터(320)는 기록 및 변환 모드가 개시될 때 제어 회로(18)로부터 하나의 펄스를 수신하고, 이에 따라 카운터(320)는 수신된 각 펄스에 응답하여 2진 코드로 카운트-업된다. 2진 코드의 카운트는 뱅크 선택기(330)에 전달되고, 이에 응답하여, 뱅크 선택기(330)는 카운터(320)로부터의 각 카운트에 의해 제1RAM 뱅크(311) 또 뒤이어 제2RAM 뱅크(312)를 선택한다. 재생 모드 개시 시에는, 카운터는 다운 입력 터미널에서 펄스를 수신하여, 그 결과 카운터(320)가 2진 코드로 카운트다운하고, 그 이진 코드는 뱅크 선택기(330)에 전달된다. 재생을 위한 RAM 뱅크 선택은 메시지를 수신하는 최종 RAM 뱅크로부터 시작된다. 기록 또는 재생 기능 중에, 마이크로프로세서(32)의 CAS1 라인(332)은 지정된 RAM 뱅크로 스위치 된다.

동작시에는, 다수의 메시지들이 각 뱅크의 각 메모리내에 저장될 수 있다. 사용된 마이크로프로세서는 정적(dtatic) 또는 동적(dynamic) 형태일 수 있다. 정적 형태의 마이크로프로세서와 정적 형태의 RAM을 사용하고 동적 형태의 마이크로프로세서와 동적 형태의 RAM을 같이 사용하는 것이 바람직하다.

제5도를 참조하면, 본 발명에 따른 아날로그-디지털 데이터 저장 시스템을 사용한 전화 시스템이 도시되어 있다. 도시한 실시예에서, 2개의 송신기/수신기(전체로서, 202 및 202'로 표시)는 상호 통신을 위해 하나의 선(204) 및 공통 접지(205)에 의해 접속된다. 각각의 송신기/수신기(202 및 202')는 종래의 전화기의 경우와 같이 전원 공급기(212), 수신기 수단(214) 및 송신기 수단(210)을 포함한다. 송신/수신 스위치(send/receive switch)(216)(통화를 위해서는 누름)는, 송신 중에 송신기 회로를 형성하고, 메시지 수신 중에는 송신기 회로(222)를 차단하고, 수신기(214)로의 회로를 완결시키기 위해 각 송신기/수신기(202 및 202')내에 제공된다. 송신/수신 스위치(216)는 단지 도시하기 위한 것이고, 인터컴 또는 전화 시스템의 동작을 위해 이러한 스위치를 필요로 하지 않는 완전 듀플렉스 인터컴 시스템(full duplex intercom system), 전화 시스템 및 전화 인터컴 시스템이 사용 가능하다.

인코더(218) 및 인코더 스위치(219)는 라인 (240)을 통해 송신시(210)에 접속된다. 인코더(218)는 전술한

형태의 어느 것이라도 될 수 있고, 바람직하게는 대부분의 전화 시스템 내에 사용되는 DTMF 형태로 될 수 있다. 또한, 수신기/송신기(202 및 202')는 제1도, 제2도 및 제3도와 관련하여 상술한 형태의 아날로그-디지털 데이터 저장 시스템(222)에 접속되는 디코더(220)를 포함한다. 송신기(202와 202')는 메시지가 수신되어 메모리 내에 배치된 것을 표시하도록 작동되는 메시지 표시기(224)를 포함한다. 재생 스위치(226) 및 리셋트 스위치(228)는 각각의 회로(222)용으로 제공되고, 전용 스위치(private switch)(230)는 기록되고 있는 메시지는 들리지 않도록 송신기/수신기(202 및 202')의 수신기(214)를 고도록(out of circuit) 작용한다. 재생 스위치(226)는 보조 인에이를 출력(extra enable output)(도시되지 않음)으로 대체할 수 있어, 재생 기능은 전환기의 키패드(key pad)(도시되지 않음)를 통해 개인 식별 코드(personal identification code)를 입력시킴으로써 작동한다.

인터컴 시스템의 동작은 제5도에 도시되어 있는데, 송신기/수신기(202)는 스위치(216)에 의해 전송하도록 설정되어, 송신기/수신기(202)의 송신기(210)와 송신기/수신기(202')의 수신기(214) 간의 회로를 배선(204)에 의해 완성하게 된다. 송신기/수신기(202')의 수신 모드에서 송신/수신 스위치(216)는 배선(204)으로부터 아날로그-디지털 저장 회로(222)까지의 회로를 라인(217)을 통해 완성하게 된다. 기록을 위해 메시지를 송신기/수신기(202)로부터 송신기/수신기(202')까지 보내기 위해, 발신자(sender)는 인코더 스위치(218)를 작동시키도록 송신기/수신기(202)의 인코더 스위치(219)를 작동시키고, 인코더(218)를 작동시키도록 송신기/수신기(202)의 인코더 스위치(219)를 작동시키고, 인코더(218)은 송신기/수신기(202')에 송신 코드를 발생시킨다. 상술한 바와 같이, 인코더 스위치(219)는 바람직하게는 발신자가 송신기/수신기(202')용으로 미리 프로그램된 코드를 입력시킬 수 있도록 전화기의 키패드 또는 이와 유사한 자리를 포함하게 된다. 송신기/수신기(202')가 수신용으로 설정되어 송신/수신 스위치는 송신기 회로를 차단하고 수신기 회로를 형성하게 된다. 도시한 바와 같이, 전용 스위치(230)는 개방 위치에 있으므로, 회로(222)에서 수신된 메시지들은 수신기(214)를 통해 재생되는 것이 아니라, 후술한 방식으로만 기록된다.

인에이를 신호 생성 회로(디코더 ; 220)는 메시지 어드레스를 감지하고, 송신기/수신기(202')에 어드레스된 경우에는, 논리 하이 상태를 발생시키고 논리 하이 상태는 인에이를 라인(221)을 통해 데이터 저장 회로(222)에 전송되어 제2도 및 제3도에 관련하여 기술한 방식으로 회로(222)를 작동시킨다. 아날로그 메시지의 디지털 형태로의 변환 및 기록은 제2도 및 제3도에 관련하여 상술한 방식으로 회로부(222)에 의해 실행된다. 메시지 종료부에서는 라인(110)은 그의 통상적인 논리 하이 상태로 복귀하고, 스위칭(230)은 수신기 회로를 재형성하기 위해 폐쇄된다. 메시지는 메모리내의 메시지들이 아날로그 형태로 재변환되어 수신기(214)에 출력되도록 재생 회로부를 개시시키는 재생 스위치(226)를 작동시킴으로써 재생될 수 있다.

원격 유니트 사용자가 인에이를 (신호생성) 회로(220)를 작동시키기에 적합한 코드를 공급받는 한, 메시지는 임의의 유니트로부터 송신기/수신기(202 또는 202')내에 전송, 저장 및 재생될 수 있다는 것을 알 수 있을 것이다. 전술한 바와 같이, 송신기/수신기(202 및 202')는 쌍방향 무선 장치 또는 그 외에 광학적으로 동작하는 것과 같은 다른 무선 송신기/수신기를 포함할 수 있고, 제1도내지 제3도과 관련하여 도시되고 기술된 음성 저장 시스템(10)은 이러한 송신기/수신기 내에 용이하게 설치될 수 있다는 것을 알 수 있을 것이다.

본 명세서 내에 기술된 바와 같이, 본 발명의 음성 저장 시스템은 쌍방향 무선 장치, 전화기, 인터컴, 이동전화기 등과 같은 다양한 통신 시스템내에 사용될 수 있다. 본 발명의 음성 저장 시스템은 페이징 시스템 외에 의학용 기록 및 산업용 모니터링에, 전자식 노트패드(note pad)등으로 응용될 수 있다. 본 발명의 시스템은 제조시에 여러 수신기 및 송신기/수신기에 용이하게 결합될 수 있고, 기존의 종래의 수신기 및 송신기/수신기내에 애드-온 아이템(add-on item ; 첨가 장치)으로서 사용될 수 있다. 본 발명의 시스템은 전력 소모가 적으므로, 원격 수신기가 작고 가벼우며 필연적으로 전원 공급이 제한되는 페이징 시스템에 사용하기에 특히 적합하다.

제8도를 참조하면, 소정 속도로 데이터를 아날로그 형태로 전송하고 상이한 속도로 메시지를 수신 및 재생하기 위한 아날로그 통신 시스템이 도시되어 있다. 이 시스템은 어드레스 데이터 및 메시지 전송 레이트 데이터를 포함하는 데이터의 입력용 제어 터미널(352), 메시지 변조 및 코드 생성 수단(354) 및 송신기 수단(356)으로 구성되는 송신기 그룹(350)을 포함한다. 데이터는 제어 터미널(352)로부터 메시지 변조 및 코드 생성 수단(354)에 입력되는데, 이 수단(354)내에서 입력 메시지가 임시로 저장되고, 어드레스 및 속도 레이트 코드 데이터가 생성되며, 아날로그 메시지가 선택된 전송 레이트로 변조된다. 변조된 아날로그 메시지로 구성되고 어드레스 코드와 메시지의 저장 및 재생 레이트를 제어하기 위한 코드가 선행하는 전송 패킷은 전송을 위해 송신기 수단(356)에 보내진다. 송신기 수단(356)은 예를 들어, 무선 주파수, 적외선 또는 주파수의 전송과 같은 무선식, 또는 전화기에 의한 것과 같은 하드-와이어식(hard-wired)으로 될 수 있다.

전송된 데이터는 송신기 수단(356)으로부터의 신호를 수신할 수 있는 수신기 수단(14)을 포함하는 수신기 그룹(358)에 의해 포착된다. 수신된 신호는 기록 및 재생 레이트 코드들이 처리되는 디코딩 및 변조 수단(16)에 전송되고, 전송된 어드레스 코드는 미리 프로그램된 어드레스 코드와 비교된다. 전송된 어드레스 코드 데이터가 수신기 그룹(358)의 기 설정된 어드레스 코드와 일치하면, 이 레이트 코드는 이후의 기록 및 재생 레이트의 제어를 위해 레이트 메모리 내로 입력된다. 상술한 바와 같이, 수신기 그룹(358)은 기록된 데이터의 재생을 위해 증폭기 및 스피커 수단(24)도 포함한다.

송신기 그룹(350)과 수신기 그룹(358) 양쪽에 대한 코딩, 디코딩 및 신호 변조 기능들은, 송신기 그룹(358)에 대해서는 신호 입력 및 제어 명령이 제어 터미널(352)로부터 도출되는데 반하여, 수신기 그룹에 대한 신호 입력은 수신기(14)로부터 유도되고 제어명령이 디코딩 및 변조 수단(16)의 회로부로부터 도출된다는 것을 제외하고는 유사하다. 또한, 송신기 그룹(350)의 인코딩 회로부는 종래의 설계로 되어 있으므로, 예를 들어 디지털 코드 생성기, 톤 코드 또는 이중-톤 다중 주파수(DTMF) 코드 생성기와 같은 다양한 코드 생성기들을 사용하여 좋은 결과를 얻을 수 있다. 단지 결정적인 것은 수신기 그룹(358)의 디코딩 회로부는 송신기 그룹(350)의 코드 생산기 회로부와 호환성이 있어야 한다는 것이다. 기재한 바와 같이, 전송된 코드는 메시지가 수신되어 특정한 지정된 수신기 그룹(358)에 저장되도록 제어 터미널(352)로부터 입력되는 어드레스를 포함할 것이다. 그러나, 반드시 어드레스 코드를 전송된 신호와 함께 사용해야

하는 것은 아니고, 전술한 바와 같이 수신기 그룹(358)의 기록 회로부를 작동시키는 음성-작동식장치로도 수신기 그룹(358)을 작동시킬 수 있다.

제9도는 송신기 그룹(350)의 동작이 도시되어 있는데, 이 도면내에서, 메시지 변조 및 코드 생성 회로부(354)는 메시지 변조 프로세서(354a) 및 코드 생성기(354b)용 회로부를 포함하는 것으로서 개략적으로 도시되어 있다. 대기하고 있는 (in queue) 다수의 페이징 메시지들을 갖고 있는 컴퓨터가 될 수 있는 제어 터미널(352)은 아날로그 메시지를 변조 프로세서(354a)에 인가하고, 어드레스와 레이트 코드를 코드 생성기(354b)에 인가한다. 코드 생성기(354b)는 기록 및 레이트용으로 적당한 코드를 생성하고, 메시지가 변조 포르세서(354a)에 보유되는 동안에 전송을 위하여 송신기(356)에 발생한다. 또한, 제어 터미널(352)은 아날로그 메시지가 전송되는 레이트를 결정하는 변조 프로세서(354a)에 명령이 발생되고, 어드레스 및 재생 레이트 코드의 전송을 바로 뒤따라 아날로그 메시지가 전송용 지정 레이트로 송신기에 전달된다. 제10도에 명확히 도시되어 있는 바와 같이, 수신기 그룹(358)은 전송된 어드레스 코드를 수신기(14)에서 수신하고, 이것을 디코더 회로부(16)에 전달하여, 어드레스 코드들이 정합하는 경우에는 변조 프로세서(354a)에 작동 명령(activation command)을 발생하게 된다. 또한, 디코더 회로부(16)는 기록 레이트를 제어하기 위해 기록 레이트 명령에 대응하는 신호를 변조 프로세서 회로부(354a)에 보낸다. 전송된 아날로그 메시지 신호는 수신기(14)로부터 변조 프로세서(354a)에 전송되어 데이터가 바람직하게는 디지털 포맷으로 변환되어 메모리 내에 저장된다. 수신기 그룹 조작자에 의해 재생 기능이 작동되면, 재생 레이트 명령은 후술할 방식으로 디코더(16)에 의해 생성되고, 메시지는 메모리로부터 재호출되어, 아날로그 포맷으로 재변환되며, 증폭기 및 스피커 수단(24)을 통해 명령 레이트로 반복 재생된다.

송신기 그룹(350)의 변조기 프로세서(354a)와 수신기 그룹(358)의 변조기 프로세서(354a)의 회로부는 매우 유사하여, 그 프로세서들은 전송 또는 수신에 이용되든지 거의 동일한 방식으로 동작한다. 회로부는 본질적으로 3가지 기능, 즉 회로 제어 및 스위칭, 메모리 변환, 및 신호 변환을 수행한다. 제11도에 도시한 바와 같이, 변조 프로세서 회로는 메모리(22), 스위칭 및 제어논리 명령에 응답하여 리셋트 및 제어 기능을 실행하기 위한 제어 회로부(18), 및 상세히 상술한 바와 같이 신호 내에 포함된 데이터를 저장하기 위해 아날로그에서 디지털로 변환시키고 전송 또는 재생하기 위해 디지털에서 아날로그로 변환시키기 위한 신호 변환기 회로부(20)를 포함한다.

제12도 및 제13도를 참조하여, 제9도 및 제10도에 도시한 변조기 프로세서 회로부(354a)의 제어수단(18), 신호 변환 수단(20) 및 메모리 수단(22) 내에 사용된 회로부의 개략도가 도시되어 있다. 오디오란 용어는 전체적으로 프로세스되고 있는 데이터를 지정하기 위해 사용되지만, 본 발명은 오디오 메시지의 전송에만 국한되지 않고, 다른 데이터 유형 및 재생 형태들 또한 이 시스템 내에서 사용된다는 것을 알 수 있을 것이다.

제12도 및 제13도에 도시한 바와 같이, 송신기 그룹(350)의 변조기 프로세서 회로부(354a) 내에 사용되지 않는 일부 특징들이 수신기 그룹(358)의 변조기 프로세서 회로부(354a) 내에 존재한다. 변조기 프로세서 회로부에 대해서는 수신기 그룹(358)의 변조 프로세서(354a)에 관련하여 설명되어 있다. 그러나, 달리 특정되지 않는 한, 이 설명은 송신기 그룹(350)의 변조 프로세서(354a)의 회로부에도 동일하게 적용된다.

시스템이 상이한 비트 레이트로 메시지를 수신, 기록 및 재생할 수 있게 하는 전술한 바와 같은 재생 레이트 회로부는 제12도에 명확히 도시되고 있고, 더욱 상세하게 후술된다. 이 레이트 회로부는 각각 라인(74 및 76)에 의해 마이크로프로세서(32)에 접속되는 레이트 스위치(인버터)(68 및 70)를 포함한다. 레이트 선택기(72)는 인버터(68 및 70)의 출력에 의해 동작된다. 또한, 레이트 선택기(72)는 재생 속도를 제어하기 위해 라인(79 및 81)에 의해 스위칭 제어기(60)의 출력에 접속된다. 송신기 그룹(350)의 변조 프로세서(354a) 내에서, 재생 레이트(즉, 전송 레이트)는 제어 터미널(352)의 제어 하에 있으므로, 인버터(68 및 70) 및 레이트 선택기(72)와 그의 관련 회로부는 사용되지 않는다.

디코더(16)는 기록 및 재생 레이트가 고정되어 메시지들이 항상 동일한 레이트로 전송되는 경우에서와 같이 고정된 기록 및 재생 레이트 코드를 생성하도록 사전 설정될 수 있다. 그러나, 호환성을 높이기 위하여, 디코더(16)는 상이한 기록 및 재생 레이트의 코드를 생성하도록 적용되어 동일한 수신기 그룹이 상이한 레이트로 전송된 별도 메시지를 수신, 기록 및 재생할 수 있도록 하는 것이 더 바람직하다.

동작에 있어서, 전송될 데이터는 송신기는 그룹(350)의 변조 프로세서(354a)의 메모리(22)에 입력되고, 전송 명령을 계속 기다린다.(held pending). 그 전송 명령은 코드 생성기(354b)에 보내지고, 다음에 송신기(356)에 보내지는 어드레스 코드 및 레이트 코드를 포함한다. 레이트 코드 및 전송 명령을 바로 뒤따라, 여러 명령들이 마이크로프로세서(32)에 보내지고, 메시지는 메모리(22)로부터 검색되어, 명령에 따른 재생 레이트로 송신기에 다시 재생된다. 메시지 데이터를 디지털화된 포맷으로 메모리 내에 저장하기 위해 신호 변환기 회로부(20)가 사용되는 경우에, 송신기(356)에 전달되기 이전에 이 데이터를 아날로그 포맷으로 재변환시키기 위해 동일 회로부가 사용된다는 것을 알 수 있다.

아날로그 메시지는, 오디오이건 데이터이건 송신기(356)에 의해 수신기(14)에 전송된다. 메시지는 톤, DTM, 디지털 등과 같은 통상적으로 사용된 임의의 형태의 지정된 어드레스 코드를 뒤따르고, 레이트 코드를 포함하여, 또 메시지 코드 종료부를 포함할 수도 있다.

동일 부분에 동일 부호가 명기된 도13을 참조하여, 디코더(16)는 이 디코더(16)와 라인(371-374)에 의해 교신하는 레이트 메모리(370)를 둘으로써 메모리 내에 저장된 각각의 메시지마다 상이한 기록 및 재생 레이트 코드를 생성하도록 적용된다. 라인(371)은 레이트 메모리(370)를 작동시켜 라인(373 및 374)을 통해 디코더(16)로부터 재생 레이트 코드 출력을 수신하도록 하는 인에이블 라인이다. 재생 레이트 코드는 카운터(320)에 의해 지정된 레이트 메모리(370)의 한 섹터 내에 저장되고, 카운터(320)는 또한 메시지를 저장한 RAM(78)의 대응하는 섹터(sector)를 선택한다. 재생 레이트 코드가 디코드되어 메모리(370) 내에 저장된 후에는 라인(371)은 디스에이블(disable) 되고, 라인(372)은 인에이블 된다. 디코더(16)는 기록 속도 레이트를 디코드하여, 라인(373 및 374)을 통해 레이트 메모리(370)의 기록 레이트 메모리 섹터에 인가된다. 그후, 라인(372)은 디스에이블 되고, 디코더(16)로부터의 라인(381)은 인에이블 된다. 라인(381)은 제12도에 관련하여 기술한 바와 같이 작동하는 입력 논리 버터(26)를 통해 이 시스템의 기록 및 재생 회로부를 작동시킨다. 라인(381)이 인에이블 될 때 메모리로부터 기록 속도를 선택하도록 레이브에

모리(370)를 작동시키기 위해, 라인(380)은 레이트 메모리 (370)를 인에이블 라인(381)에 결합시킨다. 이 기록 속도 코드는 버스(390)를 통해 메모리로부터 마이크로프로세서(32)의 레이트 입력에 전달된다. 전술한 바와 같이, 기록 명령이 디코더(16)에 의해 생성되며, 라인(381)은 디스에이블된다.

재생을 위해, 카운터(320)는 전술한 바와 같이 레이트 메모리(370)로부터의 대응 재생 레이트 코드와 함께 RAM(78)로부터 적합한 섹터를 선택한다. 재생 중에는, 라인(380)은 디스에이블 되어, 재생 레이트를 설정하기 위해 라인(390)을 통해 마이크로프로세서(32)의 레이트 회로에 전송되는 재생 레이트 코드를 레이트 메모리(370)가 생성하도록 한다.

재생레이트 코드는 코드에 관련되는 메시지가 저장되는 RAM(78) 내에 섹터에 대응하는 레이트 메모리(370)의 섹터 내에 저장된다. 이와 같은 방식으로, 저장된 메시지들을 상응하는 재생 레이트 코드와 정합되기 때문에, 메시지는 적절한 레이트로 재생된다.

상이한 레이트로 전송 및 재생할 수 있는 능력은 전송 시간을 상당히 단축시킬 수 있으므로, 아날로그 메시지 페이징 시스템을 실용적으로 되게 한다. 부가적으로, 전화 라인을 통해 전송되어야 하는 데이터는 메시지의 충실도를 유지하기 위해 저속으로 전송되고, 후에 충실도 손실없이 그의 정상 속도로 재생될 수 있다.

송신기 그룹의 변조 프로세서(354a)용으로는 메모리 어드레스 회로가 필요하지 않는데, 그 이유는 메시지 저장이 제어 터미널(352)에 의해 제어되기 때문이다.

지금까지, 본 발명의 양호한 실시예에 관련하여 기술하였으므로, 본 발명은 그 원리 및 범위를 벗어나지 않고서 여러 가지 형태로 변형 및 변경될 수 있다는 것이 이해될 것이다.

### (57) 청구의 범위

#### 청구항 1

디지털 음성 저장 통신 시스템에 있어서: (Ⅰ)음성 메시지가 뒤따르는 어드레스 코드를 포함하는 통신 패킷을 선택적으로 어드레싱하여 송신하는 1개 이상의 송신국; 및 (Ⅱ)대응하는 미리 설정되어 저장된 어드레스를 갖는 2개 이상의 수신국으로, (i)상기 통신 패킷을 전달(carrying)하는 인입 신호(incoming signal)를 수신하기 위한 수신기 회로: (ii)상기 수신기 회로에 접속되어, 상기 인입 신호에 의해 전달된 상기 통신 패킷에 응답하는 기록 인에이블 신호를 발생하는 디코더 회로부로서, 상기 미리 설정되어 저장된 어드레스를 상기 통신 패킷 어드레스 코드와 비교하여 그 비교 결과에 응답하여 상기 기록 인에이블 신호를, 상기 송신기로부터의 별도의 기록 인에이블 신호를 참조하지 않고, 자동으로 발생하기 위한 비교기를 포함하는 디코더 회로부; (iii)상기 기록 인에이블 신호에 응답하여 상기 통신 패킷의 상기 음성 메시지를 저장하기 위한 디지털 메모리; 및 (iv)재생하기 위해, 상기 디지털 메모리에 저장된 디지털 데이터를 아날로그 데이터로 변환시키기 위한 신호 변환 회로를 각각 포함하는 2개 이상의 수신국을 포함하는 디지털 음성 저장 통신 시스템.

#### 청구항 2

제1항에 있어서, 상기 디코더 회로부는 상기 기록 인에이블 신호가 중단될 때 상기 디지털 메모리를 작동 중지(deactivate) 시키기 위한 회로부를 더 포함하는 디지털 음성 저장 통신 시스템.

#### 청구항 3

제1항에 있어서, 상기 수신기 회로에 응답하고 상기 기록 인에이블 신호의 에지에 반응하여(sensitive to an edge), 상기 디지털 메모리가 새로운 음성 메시지를 기록할 수 있도록 상기 디지털 음성 저장 통신 시스템을 자동으로 리셋트하여 초기화하기 위한 에지 검출기(edge detector)를 부가적으로 포함하는 디지털 음성 저장 통신 시스템.

#### 청구항 4

제1항에 있어서, 이전에 저장된 메시지 위에(over previously stored messages)기록되는 것으로부터 상기 메모리를 보호하기 위하여, 사용 가능한 메모리 공간을 나타내는 정보를 저장하기 위한 메모리 어드레스 선택기를 부가적으로 포함하는 디지털 음성 저장 통신 시스템.

#### 청구항 5

제2항에 있어서, 상기 디코더 회로부는 메시지의 종료를 감지할 때(upon sensing the completion of a message) 상기 인에이블 신호를 종료시키는 디지털 음성 저장 통신 시스템.

#### 청구항 6

제2항에 있어서, 타이머를 부가적으로 포함하고, 상기 디코더는 상기 타이머에 응답하여 기설정된 시간이 종료될 때(upon expiration of a preset period of time) 상기 인에이블 신호를 종료시켜서, 상기 디지털 메모리가 새로운 음성 메시지를 기록할 수 있도록 디지털 음성 저장 통신 시스템.

#### 청구항 7

제1항에 있어서, 상기 디코더 회로부는 상기 인입 음성 메시지가 지속되는 동안 연속으로 상기 기록 인에이블 신호를 발생하는 디지털 음성 저장 통신 시스템.

#### 청구항 8

제1항에 있어서, 상기 디코더 회로부는 음성 작동되어(voice actuated)상기 인입 음성 메시지에 응답하여 상기 기록 인에이블 신호를 발생하는 디지털 음성 저장 통신 시스템.

**청구항 9**

제1항에 있어서, 상기 신호 변환 회로는 상기 통신 패킷의 상기 음성 메시지를 아날로그 포맷에서 디지털 포맷으로 변환하는 디지털 음성 저장 통신 시스템.

**청구항 10**

제1항에 있어서, 상기 통신 패킷은 명령 데이터를 부가적으로 포함하고, 상기 어드레스 코드와 상기 명령 데이터 뒤에는 실제로 지연 없이 상기 통신 데이터 패킷 내의 상기 음성 메시지가 따르는 디지털 음성 저장 통신 시스템.

**청구항 11**

제1항에 있어서, 상기 통신 패킷은 가변성 길이를 갖는 음성 메시지를 포함하는 디지털 음성 저장 통신 시스템.

**청구항 12**

제11항에 있어서, 상기 디지털 메모리는 상이한 길이를 갖는 디지털 음성 메시지들을 순차적으로 저장하는 디지털 음성 저장 통신 시스템.

**청구항 13**

제1항에 있어서, 상기 신호 변환 회로는 상기 기록 인에이블 신호가 지속되는 동안 작동하는 디지털 음성 저장 통신 시스템.

**청구항 14**

제1항에 있어서, 상기 디지털 메모리에 저장된 상기 음성 메시지를 검색하고, 상기 신호 변환 회로를 작동시키기(activate) 위한 조작자 작동 재생 스위치(operator activated playback switch)를 부가적으로 포함하는 디지털 음성 저장 통신 시스템.

**청구항 15**

제14항에 있어서, 상기 신호 변환 회로에 의한 변환을 위해 상기 음성 메시지를 상기 디지털 메모리로부터 선택하기 위한 스위치를 부가적으로 포함하는 디지털 음성 저장 통신 시스템.

**청구항 16**

제4항에 있어서, 상기 메모리 어드레스 선택기는 상기 디지털 메모리내에 임의 다른 저장된 메시지보다 더 오래 머물렀던(has resided) 기록된 음성 메시지를 삭제하기 위한 신호를 발생하는 디지털 음성 저장 통신 시스템.

**청구항 17**

제1항에 있어서, 상기 디지털 메모리는 상기 음성 메시지를 소리내지 않고(silently)기록하는 디지털 음성 저장 통신 시스템.

**도면****도면1**

## 도면2

### 도면3

## 도면4

## 도면5

## 도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13