등록특허 10-2390961

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년04월27일

(11) 등록번호 10-2390961

(24) 등록일자 2022년04월21일

- (51) 국제특허분류(Int. Cl.)

*H01L 29/786* (2006.01) *H01L 21/02* (2006.01)

*H01L 21/324* (2017.01) *H01L 21/383* (2006.01)

*H01L 21/477* (2006.01) *H01L 27/12* (2006.01)

*H01L 29/26* (2006.01) *H01L 29/49* (2006.01)

*H01L 29/66* (2006.01)

- (52) CPC특허분류

*H01L 29/7869* (2013.01)

*H01L 21/02554* (2013.01)

- (21) 출원번호 10-2021-7042310(분할)

- (22) 출원일자(국제) 2011년04월07일

심사청구일자 2021년12월23일

- (85) 번역문제출일자 2021년12월23일

- (65) 공개번호 10-2021-0158885

- (43) 공개일자 2021년12월31일

- (62) 원출원 특허 10-2021-7028710

원출원일자(국제) 2011년04월07일

심사청구일자 2021년09월07일

- (86) 국제출원번호 PCT/JP2011/059224

- (87) 국제공개번호 WO 2011/132590

국제공개일자 2011년10월27일

- (30) 우선권주장

JP-P-2010-100197 2010년04월23일 일본(JP)

- (56) 선행기술조사문헌

JP2004200638 A

JP2007298973 A

US20080224142 A1

전체 청구항 수 : 총 5 항

심사관 : 최정민

## (54) 발명의 명칭 반도체 장치의 제작 방법

**(57) 요 약**

산화물 반도체를 이용한 반도체 장치에 안정된 전기적 특성을 부여하여, 고신뢰성화하는 것을 목적으로 한다. 제 1 절연막을 형성하고, 제 1 절연막상에, 소스 전극 및 드레인 전극, 및 소스 전극 및 드레인 전극과 전기적으로 접속하는 산화물 반도체막을 형성하고, 산화물 반도체막에 열처리를 실시하여 산화물 반도체막중의 수

(뒷면에 계속)

**대 표 도** - 도2

소 원자를 제거하고, 수소 원자가 제거된 산화물 반도체막에 산소 도핑 처리를 실시하여, 산화물 반도체막중에 산소 원자를 공급하고, 산소 원자가 공급된 산화물 반도체막상에 제 2 절연막을 형성하고, 제 2 절연막상의 산화물 반도체막과 중첩하는 영역에 게이트 전극을 형성하는 반도체 장치의 제작 방법이다.

(52) CPC특허분류

*H01L 21/324* (2013.01)

*H01L 21/383* (2013.01)

*H01L 21/477* (2013.01)

*H01L 27/1225* (2013.01)

*H01L 29/263* (2013.01)

*H01L 29/4908* (2013.01)

*H01L 29/66742* (2013.01)

*H01L 29/66969* (2013.01)

*H01L 29/78603* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

채널 형성 영역에 실리콘을 갖는 제 1 트랜지스터와,

산화물 반도체막을 갖는 제 2 트랜지스터와,

용량 소자를 포함하고,

상기 제 1 트랜지스터의 제 1 게이트 전극은 상기 용량 소자의 한쪽 전극에 전기적으로 접속되고,

상기 제 1 트랜지스터의 상기 제 1 게이트 전극은 상기 제 2 트랜지스터의 소스 전극 및 드레인 전극 중 하나에 전기적으로 접속되고,

상기 제 1 게이트 전극은 상기 채널 형성 영역 위에 제 1 절연막을 개재하여 제공되고,

상기 제 2 트랜지스터의 제 2 게이트 전극은 상기 산화물 반도체막 위에 제 2 절연막을 개재하여 제공되고,

상기 소스 전극 및 상기 드레인 전극은 상기 산화물 반도체막 아래에 접하여 제공되고,

상기 제 2 게이트 전극, 상기 산화물 반도체막, 상기 소스 전극 및 상기 드레인 전극은 상기 채널 형성 영역 및 상기 제 1 게이트 전극의 위쪽에 위치하고,

상기 용량 소자의 한쪽 전극은 상기 제 2 게이트 전극과 동일한 층으로 이루어진 도전막인, 반도체 장치.

#### 청구항 2

채널 형성 영역에 실리콘을 갖는 제 1 트랜지스터와,

산화물 반도체막을 갖는 제 2 트랜지스터와,

용량 소자를 포함하고,

상기 제 1 트랜지스터의 제 1 게이트 전극은 상기 용량 소자의 한쪽 전극에 전기적으로 접속되고,

상기 제 1 트랜지스터의 상기 제 1 게이트 전극은 상기 제 2 트랜지스터의 소스 전극 및 드레인 전극 중 하나에 전기적으로 접속되고,

상기 제 1 게이트 전극은 상기 채널 형성 영역 위에 제 1 절연막을 개재하여 제공되고,

상기 제 2 트랜지스터의 제 2 게이트 전극은 상기 산화물 반도체막 위에 제 2 절연막을 개재하여 제공되고,

상기 소스 전극 및 상기 드레인 전극은 상기 산화물 반도체막 아래에 접하여 제공되고,

상기 제 2 게이트 전극, 상기 산화물 반도체막, 상기 소스 전극 및 상기 드레인 전극은 상기 채널 형성 영역 및 상기 제 1 게이트 전극의 위쪽에 위치하고,

상기 용량 소자는 상기 채널 형성 영역과 중첩되는 영역을 갖는, 반도체 장치.

#### 청구항 3

제 1 항 또는 제 2 항에 있어서,

상기 산화물 반도체막은, 인듐(In), 갈륨(Ga), 및 아연(Zn)을 포함하는, 반도체 장치.

#### 청구항 4

제 1 항 또는 제 2 항에 기재된 반도체 장치는 휴대 전화인, 반도체 장치.

#### 청구항 5

제 1 항 또는 제 2 항에 기재된 반도체 장치는 휴대 정보 단말인, 반도체 장치.

### 발명의 설명

#### 기술 분야

[0001] 반도체 장치 및 반도체 장치의 제작 방법에 관한 것이다.

[0002] 또한, 본 명세서 중에 있어서 반도체 장치란, 반도체 특성을 이용함으로써 기능할 수 있는 장치 전반을 가리키며, 전기 광학 장치, 반도체 회로 및 전자기기는 모두 반도체 장치이다.

#### 배경기술

[0003] 절연 표면을 갖는 기판상에 형성된 반도체 박막을 이용하여 트랜지스터를 구성하는 기술이 주목받고 있다. 그 트랜지스터는 집적회로(IC)나 화상 표시장치(표시장치)와 같은 전자 디바이스에 넓게 응용되고 있다. 트랜지스터에 적용 가능한 반도체 박막으로서 실리콘계 반도체 재료가 널리 알려져 있지만, 그 외의 재료로서 산화물 반도체가 주목받고 있다.

[0004] 예를 들면, 트랜지스터의 활성층으로서 전자 캐리어 농도가  $10^{18}/\text{cm}^3$  미만인 인듐(In), 갈륨(Ga), 및 아연(Zn)을 포함한 비정질 산화물을 이용한 트랜지스터가 개시되어 있다(특히 문헌 1 참조).

#### 선행기술문헌

##### 특허문헌

[0005] (특허문헌 0001) 일본 특개 2006-165528호 공보

#### 발명의 내용

##### 해결하려는 과제

[0006] 그러나, 산화물 반도체는 디바이스 제작 공정에 있어서, 전자 공여체를 형성하는 수소나 물의 혼입 등이 생기면, 그 전기 전도도가 변화할 우려가 있다. 이러한 현상은, 산화물 반도체를 이용한 트랜지스터에 있어서 전기적 특성의 변동 요인이 된다.

[0007] 상술한 문제를 감안하여, 산화물 반도체를 이용한 반도체 장치에 안정된 전기적 특성을 부여하여, 고신뢰성화하는 것을 목적인 하나로 한다.

##### 과제의 해결 수단

[0008] 산화물 반도체막을 갖는 트랜지스터의 제작 공정에 있어서, 열처리에 의한 탈수화 또는 탈수소화 처리, 및 산소 도핑 처리를 실시한다. 적어도, 산화물 반도체막을 갖는 트랜지스터의 제작 공정에 있어서, 산소 도핑 처리를 실시한다.

[0009] 개시하는 발명의 일 태양은, 제 1 절연막을 형성하고, 제 1 절연막상에, 소스 전극 및 드레인 전극, 및 소스 전극 및 드레인 전극과 전기적으로 접속하는 산화물 반도체막을 형성하고, 산화물 반도체막에 열처리를 실시하여 산화물 반도체막중의 수소 원자를 제거하고, 수소 원자가 제거된 산화물 반도체막에 산소 도핑 처리를 실시하여, 산화물 반도체막중에 산소 원자를 공급하고, 산소 원자가 공급된 산화물 반도체막상에 제 2 절연막을 형성하고, 제 2 절연막상의 산화물 반도체막과 중첩하는 영역에 게이트 전극을 형성하는 반도체 장치의 제작 방법이다.

[0010] 개시하는 발명의 다른 일 태양은, 성분으로서 산소 원자를 포함한 제 1 절연막을 형성하고, 제 1 절연막에 산소 도핑 처리를 실시하여 제 1 절연막에 산소 원자를 공급하고, 제 1 절연막상에, 소스 전극 및 드레인 전극, 및 소스 전극 및 드레인 전극과 전기적으로 접속하는 산화물 반도체막을 형성하고, 산화물 반도체막에 열처리를 실시하여 산화물 반도체막중의 수소 원자를 제거하고, 수소 원자가 제거된 산화물 반도체막에 산소 도핑 처리를 실시하여, 산화물 반도체막중에 산소 원자를 공급하고, 산소 원자가 공급된 산화물 반도체막상에, 성분으로서

산소 원자를 포함한 제 2 절연막을 형성하고, 제 2 절연막에 산소 도핑 처리를 실시하여 제 2 절연막에 산소 원자를 공급하고, 제 2 절연막상의 산화물 반도체막과 중첩하는 영역에 게이트 전극을 형성하는 반도체 장치의 제작 방법이다.

[0011] 또한 상기에 있어서, 화학량론비의 1배를 넘어 2배까지의 비율의 산소 원자가 포함되도록, 산화물 반도체막에 도핑 처리를 실시하는 경우가 있다. 또한, 제 1 절연막 또는 제 2 절연막으로서 산화물 반도체막의 성분 원소를 포함한 절연막을 형성하는 경우가 있다. 또한, 제 1 절연막 또는 제 2 절연막으로서 산화물 반도체막의 성분 원소를 포함한 절연막과 해당 절연막의 성분 원소와는 다른 원소를 포함한 막을 형성하는 경우가 있다. 또한, 제 1 절연막 또는 제 2 절연막으로서 산화 갈륨을 포함한 절연막을 형성하는 경우가 있다. 또한, 제 1 절연막 또는 제 2 절연막으로서 산화 갈륨과 산화 갈륨과는 다른 재료를 포함한 막을 형성하는 경우가 있다. 또한 본 명세서에 있어서, 「산화 갈륨」이라고 하는 용어는, 특별히 언급하지 않는 한, 성분 원소로서의 산소와 갈륨을 의미하는 것이며, 산화 갈륨의 태양에 한정하는 취지로 이용하지 않는다. 예를 들면, 「산화 갈륨을 포함한 절연막」이라고 하는 경우에는, 「산소와 갈륨을 포함한 절연막」과 같이 바꾸어 읽는 것이 가능하다.

[0012] 또한, 상기에 있어서, 게이트 전극을 덮도록, 질소를 함유하는 절연막을 형성하는 경우가 있다. 이와 같이, 상방에, 수소의 함유가 없거나, 또는 극히 적은 질화 실리콘 등을 이용한 절연막을 형성하는 경우에는, 첨가된 산소가 외부로 방출되는 것을 막고, 게다가, 외부로부터의 수소나 물의 흡입을 막는 것이 가능하다. 이 점에 있어서, 해당 절연막의 중요성은 높다고 말할 수 있다.

[0013] 또한, 상기의 「산소 도핑」이란, 산소(적어도, 산소 라디칼, 산소 원자, 산소 이온중의 어느 것인가를 포함한다)를 벌크에 첨가하는 것을 말한다. 또한 해당 「벌크」라고 하는 용어는, 산소를, 박막 표면뿐만 아니라 박막 내부에 첨가하는 것을 명확하게 하는 취지로 이용하고 있다. 또한, 「산소 도핑」에는, 플라즈마화한 산소를 벌크에 첨가하는 「산소 플라즈마 도핑」이 포함된다.

[0014] 상기의 산소 도핑 처리에 의해, 산화물 반도체막의 막중(벌크중), 절연막의 막중(벌크중), 산화물 반도체막과 절연막의 계면중의 어느 것인가에는 적어도 화학량론비를 넘는 양의 산소가 존재한다. 산소의 양은, 바람직하게는 화학량론비의 1배를 넘어 4배까지(4배 미만), 보다 바람직하게는, 1배를 넘어 2배까지(2배 미만)이다. 여기서, 화학량론비를 넘는 산소 과잉의 산화물이란, 그것이, 예를 들면,  $In_aGa_bZn_cSi_dAl_eMg_fO_g$ (a, b, c, d, e, f, g $\geq$ 0)로 나타내어질 때,  $2g>3a+3b+2c+4d+3e+2f$ 를 만족하는 산화물을 말한다. 또한 산소 도핑 처리에 의해 첨가된 산소는, 산화물 반도체의 격자간에 존재하는 경우도 있다.

[0015] 또한, 적어도 탈수화, 탈수소화한 후의 산화물 반도체막중의 수소보다도 첨가되는 산소의 양이 많아지도록 한다. 적어도 상기 구성중의 어느 것인가에 있어서 첨가되는 산소의 양이 수소보다 많으면, 그것이 확산하여, 다른 불안정성의 원인의 수소와 반응함에 의해 수소를 고정화(비가동 이온화)할 수가 있다. 즉, 신뢰성상의 불안정성을 줄이거나, 또는 충분히 줄일 수가 있다. 또한, 산소를 과잉으로 함으로써 산소 결손에 기인하는 스레솔드 전압(Vth)의 편차를 저감함과 동시에, 스레솔드 전압의 시프트량( $\Delta Vth$ )을 저감할 수가 있다.

[0016] 또한, 산화물 반도체막의 막중(벌크중), 절연막의 막중(벌크중), 산화물 반도체막과 절연막의 계면중의 2개소 이상에 상술한 양의 산소가 존재하면 보다 바람직하다.

[0017] 또한, 결함(산소 결손)이 없는 산화물 반도체라면, 화학량론비에 일치한 양의 산소가 포함되어 있으면 좋지만, 트랜지스터의 스레솔드 전압의 변동을 억제하는 등의 신뢰성을 확보하기 위해서는, 산화물 반도체에는, 화학량론비를 넘는 양의 산소가 포함되어 있는 것이 바람직하다. 마찬가지로 결함(산소 결손)이 없는 산화물 반도체라면, 기초막을 산소 과잉의 절연막으로 할 필요는 없지만, 트랜지스터의 스레솔드 전압의 변동을 억제하는 등의 신뢰성을 확보하기 위해서는, 산화물 반도체층에 산소 결손 상태는 생길 수 있는 것을 고려하여, 기초막을 산소 과잉의 절연막으로 하는 것이 바람직하다.

[0018] 여기서, 상술한 「산소 플라즈마 도핑」처리에 의해, 벌크중에 산소가 첨가되는 모습을 나타낸다. 또한 산소를 일성분으로서 포함한 산화물 반도체막중에 산소 도핑 처리를 실시하는 경우, 일반적으로, 산소 농도의 증감을 확인하는 것은 곤란하다. 따라서, 여기에서는, 실리콘 웨이퍼를 이용하여, 산소 도핑 처리의 효과를 확인하였다.

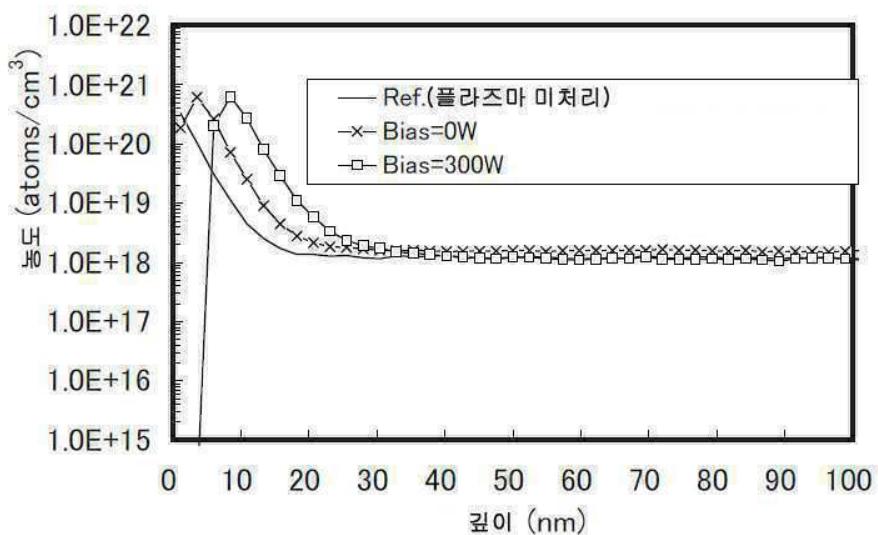

[0019] 산소 도핑 처리는, 유도 결합 플라즈마(ICP: Inductively Coupled Plasma) 방식을 이용하여 실시하였다. 그 조건은, ICP 전력 800 W, RF 바이어스 전력 300 W 또는 0 W, 압력 1.5 Pa, 산소 가스 유량 75 sccm, 기판 온도 70°C다. 도 15에, SIMS(Secondary Ion Mass Spectrometry) 분석에 의한 실리콘 웨이퍼의 깊이 방향의 산소

농도 프로파일을 나타낸다. 도 15에 있어서, 종축은 산소 농도를 나타내고, 횡축은 실리콘 웨이퍼 표면으로부터의 깊이를 나타낸다.

[0020] 도 15로부터, RF 바이어스 전력이 0 W의 경우 및 300 W의 경우의 어느 것에 있어서도, 산소가 첨가되어 있는 것을 확인할 수 있다. 또한, RF 바이어스 300 W의 경우는, RF 바이어스 0 W의 경우와 비교하여, 산소가 보다 깊게 첨가되는 것을 확인할 수 있다.

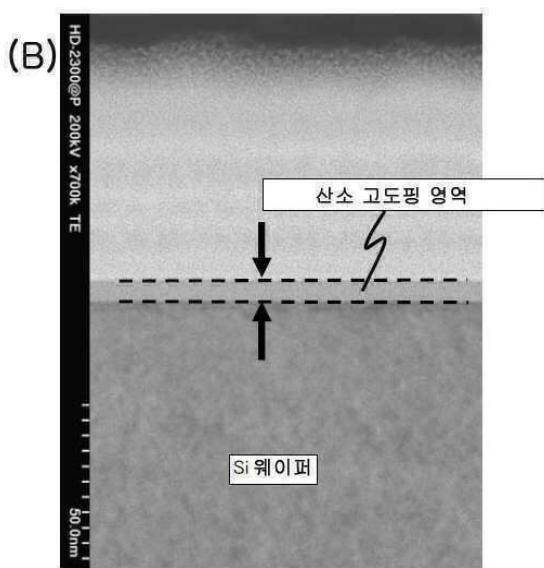

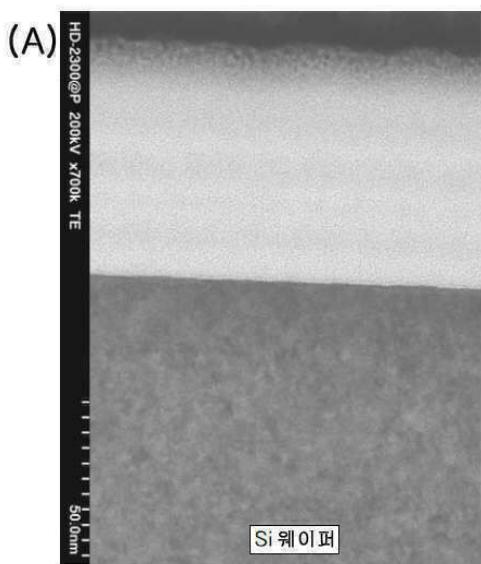

[0021] 다음으로, 산소 도핑 처리를 실시하기 전과 산소 도핑을 실시한 후의 실리콘 웨이퍼의 단면을 STEM(Scanning Transmission Electron Microscopy)으로 관찰한 결과를 도 16에 나타낸다. 도 16(A)은, 산소 도핑 처리를 실시하기 전의 STEM상이며, 도 16(B)은, 상술한 RF 바이어스 전력 300 W의 조건으로 산소 도핑 처리를 실시한 후의 STEM상이다. 도 16(B)에 나타내는 바와 같이, 산소 도핑을 실시함에 의해, 실리콘 웨이퍼에 산소고도핑 영역이 형성되어 있는 것을 확인할 수 있다.

[0022] 이상과 같이, 실리콘 웨이퍼에 대하여 산소 도핑을 실시함으로써, 실리콘 웨이퍼에 산소가 첨가되는 것이 나타났다. 이 결과에 의해, 산화물 반도체막에 있어서 산소 도핑을 실시함에 의해서도, 산화물 반도체막에 산소를 당연히 첨가할 수 있는 것을 이해할 수 있다.

[0023] 개시하는 발명의 일 태양인 상술한 구성의 효과는, 다음과 같이 생각하면 이해가 용이하다. 다만, 이하의 설명은, 어디까지나 한가지 고찰에 지나지 않는다는 것을 부기한다.

[0024] 게이트 전극에 플러스의 전압을 인가하면, 산화물 반도체막의 게이트 전극측으로부터 백채널측(게이트 절연막과 반대측)으로 전계가 발생하기 때문에, 산화물 반도체막중에 존재하는 플러스의 전하를 갖는 수소이온이 백채널 측으로 이동하여, 산화물 반도체막과 절연막과의 계면중에서 산화물 반도체막측으로 축적한다. 축적한 수소이온으로부터 절연막중의 전하 포획 중심(수소 원자, 물, 혹은 오염물 등)에 플러스의 전하가 이동함으로써, 산화물 반도체막의 백채널 측에는 마이너스의 전하가 축적된다. 즉, 트랜지스터의 백채널 측으로 기생 채널이 발생하여, 스레솔드 전압이 마이너스측으로 시프트하여, 트랜지스터가 노멀리온(normally on)의 경향을 나타낸다.

[0025] 상기한 바와 같이, 절연막중의 수소 또는 물 등의 전하 포획 중심이 플러스의 전하를 포획하여, 절연막중에 플러스의 전하가 이동함으로써 트랜지스터의 전기적 특성이 변동하기 때문에, 트랜지스터의 전기적 특성의 변동을 억제하기 위해서는, 절연막중에 이러한 전하 포획 중심이 존재하지 않거나, 또는 그 함유량이 적은 것이 중요하다. 따라서, 절연막의 성막에는, 성막시에 수소 함유량이 적은 스퍼터법을 이용하는 것이 바람직하다. 스퍼터법에 의해 성막된 절연막은, 그 막중에 전하 포획 중심이 존재하지 않거나, 또는 적고, CVD법 등에 의해 성막하였을 경우와 비교하여 플러스의 전하의 이동이 일어나기 어렵다. 따라서, 트랜지스터의 스레솔드 전압의 시프트를 억제하여, 트랜지스터를 노멀리 오프(normally off)로 할 수가 있다.

[0026] 또한, 탑게이트형의 트랜지스터에 있어서는, 기초가 되는 절연막상에 산화물 반도체막을 형성한 후, 열처리를 실시함으로써, 산화물 반도체막에 포함되는 물 또는 수소를 제거하는 것과 동시에, 절연막중에 포함되는 물 또는 수소도 제거할 수가 있다. 따라서, 절연막중에는, 산화물 반도체막중을 이동해 온 플러스의 전하를 포획하기 위한 전하 포획 중심이 적다. 이와 같이, 산화물 반도체막으로의 탈수화 또는 탈수소화를 위한 열처리는, 산화물 반도체막에 부가하여, 산화물 반도체막의 하층에 존재하는 절연막에 대하여도 행해지기 때문에, 탑게이트형의 트랜지스터에 있어서는, 기초가 되는 절연막은 플라즈마 CVD법 등의 CVD법을 이용하여 성막되어 있어도 상관없다.

[0027] 또한, 게이트 전극에 마이너스의 전압을 인가하면, 백채널측으로부터 게이트 전극측으로 전계가 발생하기 때문에, 산화물 반도체막중에 존재하는 수소이온이 게이트 절연막측으로 이동하여, 산화물 반도체막과 게이트 절연막과의 계면중 산화물 반도체막측으로 축적한다. 또한, 이에 의해 트랜지스터의 스레솔드 전압은 마이너스측으로 시프트한다.

[0028] 또한, 전압을 0으로서 방치하면, 전하 포획 중심으로부터 플러스의 전하가 해방되어 트랜지스터의 스레솔드 전압이 플러스측으로 시프트하여, 초기 상태로 돌아오거나, 또는 경우에 따라서는 초기 상태보다 플러스측으로 시프트한다. 이 현상은, 산화물 반도체막중으로 이동하기 쉬운 이온이 존재하고 있다는 것을 시사하고 있으며, 가장 작은 원자인 수소가 가장 이동하기 쉬운 이온이 된다고 고찰할 수가 있다.

[0029] 또한, 산화물 반도체막이 광을 흡수함으로써, 광 에너지에 의해 산화물 반도체막중의 금속 원소(M)와 수소 원자(H)와의 결합(M-H결합이라고도 표기한다)이 끊어진다. 또한 파장이 400 nm 전후의 광 에너지와 금속 원소 및 수소 원자의 결합 에너지와는 대략 일치하고 있다. 산화물 반도체막중의 금속 원소와 수소 원자와의 결합이 끊어진 트랜지스터에 음의 게이트 바이어스를 가하면, 금속 원소로부터 이탈한 수소이온이 게이트 전극 측으로 끌

어 당겨질 수 있기 때문에 전하의 분포가 변화하고, 트랜지스터의 스레숄드 전압은 마이너스 측으로 시프트하여, 노멀리온의 경향을 나타낸다.

[0030] 또한, 트랜지스터로의 광조사와 음의 게이트 바이어스의 인가에 의해 게이트 절연막 계면으로 이동한 수소이온은, 전압의 인가를 정지하면 원래대로 돌아간다. 이것은, 산화물 반도체막중의 이온 이동의 대표적인 예로서 이해할 수 있다.

[0031] 이러한, 전압 인가에 의한 전기적 특성의 변동(BT열화) 또는 광조사에 의한 전기적 특성의 변동(광열화)에의 대책은, 산화물 반도체막으로부터 수소 원자 또는 물 등의 수소 원자를 포함한 불순물을 철저하게 배제하여, 산화물 반도체막을 고순도화하는 것이 가장 중요하다. 전하 밀도가  $10^{15} \text{ cm}^{-3}$ , 즉, 단위면적 당의 전하가  $10^{10} \text{ cm}^{-2}$ 의 경우, 그 전하는 트랜지스터 특성에 영향을 주지 않거나 또는 영향을 준다고 하더라도 매우 적다. 따라서, 전하 밀도는  $10^{15} \text{ cm}^{-3}$  이하인 것이 바람직하다. 만일, 산화물 반도체막에 포함되는 수소 중에, 10%의 수소가 산화물 반도체막중을 이동하는 경우, 수소의 농도는  $10^{16} \text{ cm}^{-3}$  이하인 것이 바람직하다. 게다가 디바이스 완성 후에 수소가 외부에서 침입하는 것을 막기 위해서, 스퍼터법에 따라서 성막한 질화 실리콘막을 패시베이션막으로서 이용하여 트랜지스터를 덮는 것이 바람직하다.

[0032] 게다가 산화물 반도체막중에 포함되는 수소에 대하여, 과잉의 산소를 도핑함((수소 원자의 수)«(산소 라디칼의 수) 또는, (산소 이온의 수)로 한다)으로써, 산화물 반도체막으로부터 수소 또는 물을 배제할 수가 있다. 구체적으로는, 고주파(RF)를 이용하여 산소를 플라즈마화하고, 기판 바이어스를 크게 하여, 산소 라디칼, 산소 이온을 기판상의 산화물 반도체막에 도핑 또는 첨가하여, 산화물 반도체막중에서는 잔존하는 수소보다 산소를 많게 한다. 산소의 전기 음성도는 3.0로서 전기 음성도가 약 2.0인 산화물 반도체막중의 금속(Zn, Ga, In)보다 크기 때문에, 수소에 대하여 산소를 과잉으로 함유시킴으로써, M-H기로부터 수소를 빼앗아, OH기를 형성한다. 또한 이 OH기는, M와 결합하여 M-O-H기를 형성할 수 있다.

[0033] 또한, 산화물 반도체막의 산소의 함유량이, 화학량론비보다 과잉이 되도록 산소를 도핑하는 것이 보다 바람직하다. 예를 들면, 산화물 반도체막으로서 In-Ga-Zn-O계 산화물 반도체막을 이용하는 경우, 산소의 도핑 등에 의해 산소의 비율을 화학량론비의 1배를 넘어 2배까지(2배 미만)로 하는 것이 보다 바람직하다. 예를 들면, In-Ga-Zn-O계 산화물 반도체의 단결정의 화학량론비를 In:Ga:Zn:O=1:1:1:4로 하면, 조성이 In<sub>x</sub>Ga<sub>1-x</sub>Zn<sub>0.5</sub>O<sub>3</sub>로 나타내어지는 산화물 반도체 박막에 있어서, X는 4를 넘어 8 미만으로 하는 것이 보다 바람직하다. 따라서, 산화물 반도체막에 있어서 산소의 함유량은 수소의 함유량보다 커진다.

[0034] 광 에너지나 BT스트레스에 의해, M-H기로부터 수소가 이탈해 열화의 원인이 되지만, 상술한 도핑에 의해 산소를 주입하는 경우, 주입된 산소가 수소이온과 결합하여 OH기가 된다. OH기는, 결합 에너지가 크기 때문에, 트랜지스터에 광조사나 BT스트레스가 가해져도 수소이온을 방출하지 않고, 또한 수소이온보다 질량도 크기 때문에, 산화물 반도체막중을 이동하기 어렵다. 따라서, 산소의 도핑에 기인하여 형성되는 OH기는, 트랜지스터의 열화의 원인이 되지 않던지, 또는 열화의 원인을 줄일 수가 있다.

[0035] 또한, 산화물 반도체막의 막두께를 크게 할수록, 트랜지스터의 스레숄드 전압이 불규칙해지는 경향이 확인되고 있다. 이것은, 산화물 반도체막중의 산소 결함이 스레숄드 전압의 변동의 한 요인이며, 막두께가 커질수록 그 산소 결함이 증가하기 때문이라고 추측할 수 있다. 본 발명의 일 태양과 관련되는 트랜지스터에 있어서 산화물 반도체막에 산소를 도핑하는 공정은, 산화물 반도체막으로부터의 수소 또는 물의 배제뿐만 아니라, 막중의 산소 결함의 보충에 대하여도 유효하다. 따라서, 본 발명의 일 태양과 관련되는 트랜지스터는, 스레숄드 전압의 편차도 제어할 수가 있다.

[0036] 또한, 산화물 반도체막을 사이에 끼워서, 산화물 반도체막과 동종의 성분으로 이루어지는 금속 산화물막을 마련하는 구성도, 전기적 특성의 변동 방지에 효과적이다. 산화물 반도체막과 동종의 성분으로 이루어지는 금속 산화물막으로서, 구체적으로는, 산화물 반도체막의 성분 원소로부터 선택되는 1종 또는 복수의 금속 원소의 산화물을 포함한 막을 이용하는 것이 바람직하다. 이러한 재료는 산화물 반도체막과의 상성(相性)이 좋고, 산화물 반도체막을 사이에 끼워서 그 금속 산화물막을 마련함으로써, 산화물 반도체막과의 계면 상태를 양호하게 유지할 수가 있다. 즉, 상술한 재료를 이용한 금속 산화물막을, 산화물 반도체막과 접하는 절연막으로서 마련함으로써, 그 금속 산화물막과 산화물 반도체막과의 계면 및 그 근방으로의 수소이온의 축적을 억제 또는 방지할 수가 있다. 따라서, 산화물 반도체막을 사이에 끼워서, 예를 들면, 산화 실리콘막 등의 산화물 반도체막과는 다른 성분으로 이루어지는 절연막을 마련했을 경우와 비교하여, 트랜지스터의 스레숄드 전압에 영향을 주는 산화

물 반도체막 계면의 수소 농도를 충분히 저감할 수가 있다.

[0037] 또한, 그 금속 산화물막으로서는, 산화 갈륨막을 이용하는 것이 바람직하다. 산화 갈륨은, 밴드갭(Eg)이 크기 때문에, 산화 갈륨막에 의해 산화물 반도체막을 사이에 끼워으로써, 산화물 반도체막과 금속 산화물막과의 계면에서, 에너지 장벽이 형성되어 그 계면에 있어서 캐리어의 이동은 방해할 수 있다. 따라서, 캐리어는 산화물 반도체로부터 금속 산화물로 이동하는 일 없이, 산화물 반도체막중을 이동한다. 한편, 수소이온은, 산화물 반도체와 금속 산화물과의 계면을 통과하여, 금속 산화물과 절연막과의 계면 부근에 축적한다. 만일, 절연막과의 계면 근방에 수소이온이 축적되었다고 하여도, 금속 산화물막으로서의 산화 갈륨막에는 캐리어가 흐를 수 있는 기생 채널이 형성되지 않기 때문에, 트랜지스터의 스레숄드 전압에 대한 영향을 주지 않거나, 또는 그 영향이 극히 적다. 또한 산화 갈륨과 In-Ga-Zn-O계의 재료를 접촉시켰을 경우의 에너지 장벽은, 전도대측에서 약 0.8 eV가 되며, 가전자대측에서 약 0.9 eV가 된다.

[0038] 개시하는 발명의 일 태양과 관련되는 트랜지스터는, 산소 도핑 처리에 의해, 산화물 반도체막에 접하는 절연막 중, 산화물 반도체막중, 또는 이러한 계면 근방중의 적어도 어느 하나에 산소의 함유량을 증대시키는 것을 기술 사상으로 하는 것이다.

[0039] 산화물 반도체막으로서 인듐을 포함한 산화물 반도체 재료를 이용하는 경우, 인듐과 산소의 결합력은 비교적 약하기 때문에, 산화물 반도체막에 접하는 절연막에 실리콘 등의 산소와의 결합력이 보다 강한 재료가 포함되는 경우에, 열처리에 의해 산화물 반도체막중의 산소가 빠져버려서, 산화물 반도체막의 계면 근방에 산소 결손이 형성될 우려가 있다. 그렇지만, 개시하는 발명의 일 태양과 관련되는 트랜지스터는, 산화물 반도체막에 과잉의 산소를 공급함으로써, 산소 결손의 형성을 억제할 수가 있다.

[0040] 여기서, 트랜지스터의 제작 공정에 있어서 산소 도핑 처리를 실시한 다음에는, 산화물 반도체막 또는 산화물 반도체막에 접하는 절연막에 함유되는, 화학량론비보다 과잉의 산소량이 각종에서 다른 경우가 있다. 과잉의 산소량이 다른 상태에서는, 각종의 산소의 화학 페텐셜이 다르며, 화학 페텐셜의 차이는 트랜지스터의 제작 공정에 있어서의 열처리 등으로, 평형 상태에 가까워지거나, 또는 평형 상태가 된다고 생각된다. 이하에서는, 평형 상태에 있어서의 산소의 분포에 대하여 검토한다.

[0041] 어느 온도 T, 압력 P에서의 평형 상태란, 전계의 깁스의 자유에너지 G가 최소가 되는 상태이며, 이하의 식(1)으로 나타내어진다.

## 수학식 1

$$\begin{aligned} G(N_a, N_b, N_c, \dots, T, P) = & \\ G^{(1)}(N_a, N_b, N_c, \dots, T, P) + G^{(2)}(N_a, N_b, N_c, \dots, T, P) + G^{(3)}(N_a, N_b, N_c, \dots, T, P) & \\ \dots \dots (1) \end{aligned}$$

[0042] [0043] 식(1)에 있어서,  $G^{(1)}$ ,  $G^{(2)}$ ,  $G^{(3)}$ 는, 각종의 깁스의 자유에너지를 나타낸다. 또한,  $N_a$ ,  $N_b$ ,  $N_c$ 는 입자수를 나타내며, a, b, c는 입자의 종류를 나타낸다. 입자 a가 i층으로부터 j층으로  $\delta N_a^{(j)}$ 만큼 이동했을 경우, 깁스의 자유에너지의 변화는, 이하의 식(2)과 같이 된다.

## 수학식 2

$$\delta G = -\frac{\partial G^{(i)}}{\partial N_a^{(i)}} \delta N_a^{(j)} + \frac{\partial G^{(j)}}{\partial N_a^{(j)}} \delta N_a^{(i)} \quad \dots \dots (2)$$

[0044]

[0045] 여기서,  $\delta G$ 가 0, 즉 이하의 식(3)이 성립될 때, 계가 평형 상태가 된다.

### 수학식 3

$$\frac{\partial G^{(i)}}{\partial N_a^{(i)}} = \frac{\partial G^{(j)}}{\partial N_a^{(j)}} \quad \dots \dots (3)$$

[0046]

[0047] 집스의 자유에너지의 입자수 미분은, 화학 퍼텐셜에 상당하므로, 평형 상태에 있어서, 입자의 화학 퍼텐셜이 모든 층에서 동일해진다.

[0048] 즉, 구체적으로는, 절연막과 비교하여 산화물 반도체막에 산소가 과잉으로 포함되어 있는 경우, 절연막에서는 산소의 화학 퍼텐셜이 상대적으로 작고, 산화물 반도체막에서는 화학 퍼텐셜이 상대적으로 큰 상태가 되어 있다.

[0049] 그리고, 트랜지스터의 제작 공정에 있어서 열처리를 실시함으로써, 계 전체(여기에서는, 산화물 반도체막과 거기에 접하는 절연막)가 충분히 고온이 되어, 원자의 층내 및 층간의 확산이 일어나게 되면, 화학 퍼텐셜이 같아지도록 산소의 이동이 일어난다. 즉, 산화물 반도체막의 산소가 절연막으로 이동함으로써, 산화물 반도체막의 화학 퍼텐셜이 작아지고, 절연막의 화학 퍼텐셜이 커진다.

[0050] 따라서, 산소 도핑 처리에 의해 산화물 반도체막에 과잉으로 공급된 산소는, 그 후의 열처리에 의해 계내의 화학 퍼텐셜을 평형 상태로 함으로써, 확산하여, 절연막(계면을 포함한다)에 공급된다. 이 때문에, 산화물 반도체막에 과잉의 산소가 충분히 존재하는 경우에는, 산화물 반도체막에 접하는 절연막(계면을 포함한다)도 산소 과잉으로 할 수 있다.

[0051] 따라서, 절연막이나 절연막과의 계면에 있어서의 산소 부족 결함을 보상하는데 충분한 양(산소 부족 결함을 보상하여도 여유가 있는 과잉의 양)의 산소를 산화물 반도체막중에 공급해 두는 것에는 큰 의의가 있다고 말할 수 있다.

### 발명의 효과

[0052] 열처리에 의한 탈수화 또는 탈수소화 처리, 및 산소 도핑 처리된 산화물 반도체막을 갖는 트랜지스터는, 바이어스-열스트레스(BT) 시험 전후에도 트랜지스터의 스페인드 전압의 변화량이 저감되어 있어, 안정된 전기 특성을 갖는 신뢰성이 높은 트랜지스터를 실현할 수 있다.

[0053] 또한, 개시하는 발명의 일 태양에 의해, 전기 특성이 양호하여 신뢰성이 높은 트랜지스터를 갖는 여러 가지 반도체 장치를 제작할 수가 있다.

### 도면의 간단한 설명

[0054]

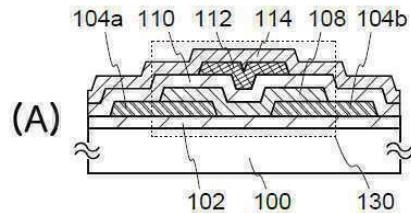

도 1은 반도체 장치의 일 형태를 설명하는 도.

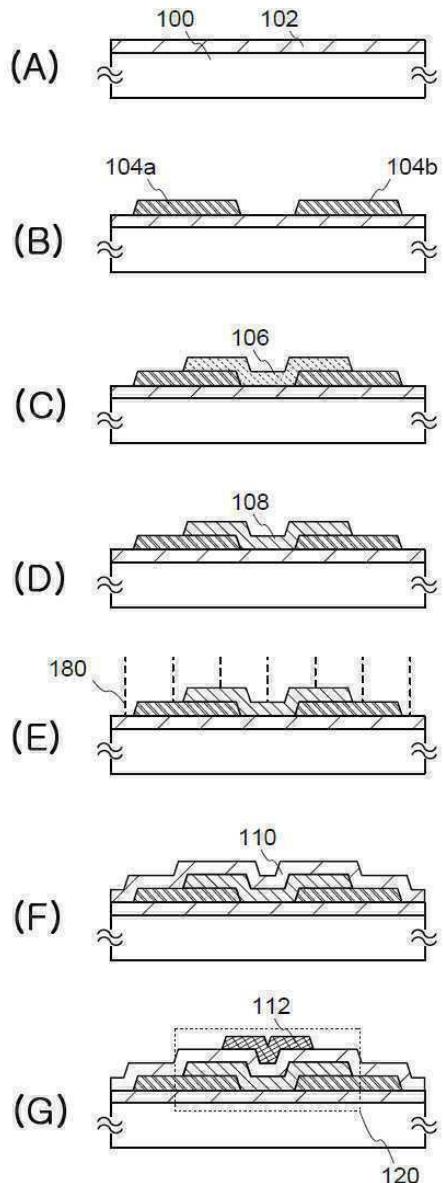

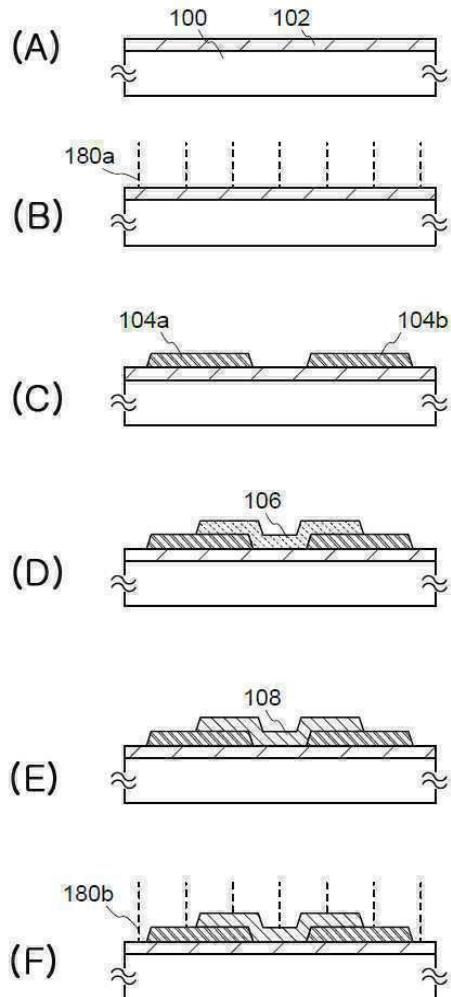

도 2는 반도체 장치의 제작 방법의 일 형태를 설명하는 도.

도 3은 반도체 장치의 형태를 설명하는 도.

도 4는 반도체 장치의 제작 방법의 일 형태를 설명하는 도.

도 5는 반도체 장치의 제작 방법의 일 형태를 설명하는 도.

도 6은 반도체 장치의 제작 방법 일 형태를 설명하는 도.

도 7은 반도체 장치의 단면도, 표면도 및 회로도.

도 8은 반도체 장치의 일 형태를 설명하는 도.

도 9는 반도체 장치의 일 형태를 설명하는 도.

도 10은 반도체 장치의 일 형태를 설명하는 도.

도 11은 반도체 장치의 일 형태를 설명하는 도.

도 12는 반도체 장치의 일 태양을 설명하는 도.

도 13은 전자기기를 나타내는 도.

도 14는 전자기기를 나타내는 도.

도 15는 SIMS의 측정 결과를 나타내는 도.

도 16은 단면 STEM상을 설명하는 도.

도 17은 플라즈마 장치의 표면도 및 단면도.

### 발명을 실시하기 위한 구체적인 내용

[0055]

이하에서는, 본 명세서에 개시하는 발명의 실시형태에 대하여 도면을 이용하여 상세하게 설명한다. 다만, 본 명세서에 개시하는 발명은 이하의 설명에 한정되지 않고, 그 형태 및 상세를 여러 가지로 변경할 수 있다는 것은, 당업자라면 용이하게 이해된다. 또한, 본 명세서에 개시하는 발명은 이하에 나타내는 실시형태의 기재 내용에 한정하여 해석되는 것은 아니다.

[0056]

또한, 본 명세서 등에 있어서의 「제 1」, 「제 2」, 「제 3」 등의 서수사는, 구성요소의 혼동을 피하기 위해서 불인 것이며, 수적으로 한정하는 것이 아니라는 것을 부기한다.

[0057]

(실시형태 1)

[0058]

본 실시형태에서는, 반도체 장치 및 반도체 장치의 제작 방법에 대하여, 도 1 내지 도 3을 이용하여 설명한다.

[0059]

<반도체 장치의 구성예>

[0060]

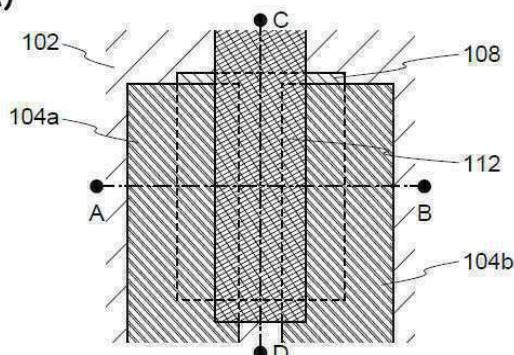

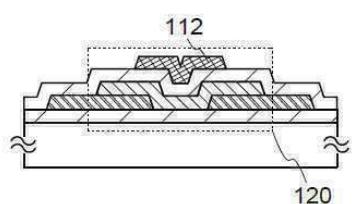

도 1에는, 트랜ジ스터(120)의 구성예를 나타낸다. 여기서, 도 1(A)은 평면도이며, 도 1(B) 및 도 1(C)은 각각, 도 1(A)에 있어서의 A-B 단면 및 C-D 단면과 관련되는 단면도이다. 또한 도 1(A)에서는 번잡하게 되는 것을 피하기 위해, 트랜ジ스터(120)의 구성요소의 일부(예를 들면, 게이트 절연막(110) 등)를 생략하고 있다.

[0061]

도 1에 나타내는 트랜ジ스터(120)는, 기판(100)상의 절연막(102), 소스 전극(104a), 드레인 전극(104b), 산화물 반도체막(108), 게이트 절연막(110), 게이트 전극(112)을 포함한다.

[0062]

도 1에 나타내는 트랜ジ스터(120)에 있어서, 산화물 반도체막(108)은, 산소 도핑 처리를 한 산화물 반도체막이다. 산소 도핑 처리를 함으로써, 신뢰성이 높아진 트랜ジ스터(120)가 실현된다.

[0063]

<반도체 장치의 제작 공정예>

[0064]

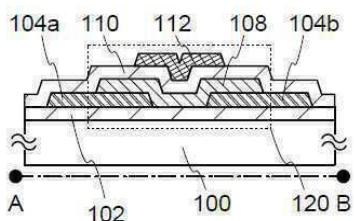

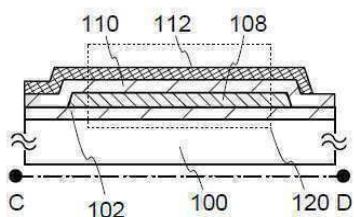

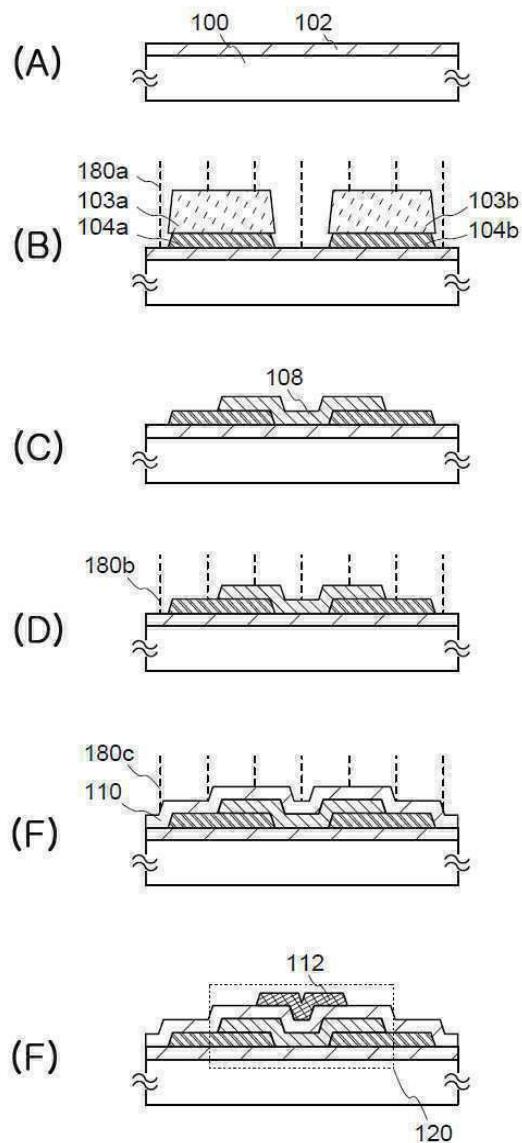

이하, 도 2를 이용하여, 도 1에 나타내는 반도체 장치의 제작 공정의 일 예를 설명한다.

[0065]

우선, 기판(100)상에 절연막(102)을 형성한다(도 2(A) 참조).

[0066]

기판(100)의 재질 등에 큰 제한은 없지만, 적어도, 후의 열처리에 견디는 정도의 내열성을 갖고 있을 것이 필요하다. 예를 들면, 유리 기판, 세라믹 기판, 석영 기판, 사파이어 기판 등을, 기판(100)으로서 이용할 수가 있다. 또한, 실리콘이나 탄화 실리콘 등의 단결정 반도체 기판, 다결정 반도체 기판, 실리콘 게르마늄 등의 화합물 반도체 기판, SOI 기판 등을 적용하는 것도 가능하고, 이러한 기판상에 반도체소자가 마련된 것을, 기판(100)으로서 이용하여도 괜찮다.

[0067]

또한, 기판(100)으로서 가요성 기판을 이용하여도 괜찮다. 가요성 기판상에 트랜ジ스터를 마련하는 경우, 가요성 기판상에 직접적으로 트랜ジ스터를 만들어도 괜찮고, 다른 기판에 트랜ジ스터를 형성한 후, 이를 박리하고, 가요성 기판에 전치(轉置)하여도 좋다. 또한 트랜ジ스터를 박리하고, 가요성 기판에 전치하기 위해서는, 상기 다른 기판과 트랜지스터와의 사이에 박리층을 형성하면 좋다.

[0068]

절연막(102)은 기초로서 기능하는 절연막이다. 구체적으로는, 절연막(102)에는, 산화 실리콘, 질화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화 갈륨, 이들의 혼합 재료 등을 이용하면 좋다. 또한, 절연막(102)은, 상술한 재료를 포함한 절연막의 단층 구조로 하여도 좋고, 적층 구조로 하여도 좋다.

[0069]

절연막(102)의 제작 방법에 특별히 한정은 없다. 예를 들면, 플라즈마 CVD법이나 스퍼터링법 등의 성막 방법을 이용하여 절연막(102)을 제작할 수가 있다. 또한 수소나 물 등이 혼입하기 어렵다고 하는 점에서는, 스퍼터링 법이 매우 적합하다.

- [0070] 또한, 절연막(102)에는, 후에 형성되는 산화물 반도체막과 동종의 성분으로 이루어지는 절연 재료를 이용하면 특히 바람직하다. 이러한 재료는 산화물 반도체막과의 상성이 좋고, 이를 절연막(102)에 이용함으로써, 산화물 반도체막과의 계면 상태를 양호하게 유지할 수가 있기 때문이다. 여기서, 「산화물 반도체막과 동종의 성분」이란, 산화물 반도체막의 성분 원소로부터 선택되는 1종 또는 복수의 원소를 의미한다. 예를 들면, 산화물 반도체막이 In-Ga-Zn-O계의 산화물 반도체 재료에 의해 구성되는 경우, 동종의 성분으로 이루어지는 절연 재료로서는 산화 갈륨 등이 있다.

- [0071] 또한, 절연막(102)을 적층 구조로 하는 경우에는, 산화물 반도체막과 동종의 성분으로 이루어지는 절연 재료로 이루어지는 막(이하, 막a)과, 막a의 성분 재료와는 다른 재료를 포함한 막(이하, 막b)의 적층 구조로 하면 더욱 좋다. 막a와 막b를 산화물 반도체막층으로부터 순서대로 적층한 구조로 함으로써, 전하는 막a와 막b의 계면의 전하 포획 중심에 우선적으로 포획되기(산화물 반도체막과 막a의 계면과의 비교) 때문에, 산화물 반도체막의 계면에서의 전하 포획을 충분히 억제할 수가 있게 되어, 반도체 장치의 신뢰성이 향상하기 때문이다.

- [0072] 또한, 이러한 적층 구조로서는, 산화 갈륨막과 산화 실리콘막의 적층 구조나, 산화 갈륨막과 질화 실리콘막의 적층 구조 등을 적용할 수가 있다.

- [0073] 그 다음으로, 절연막(102)상에, 소스 전극 및 드레인 전극(이와 동일한 층에서 형성되는 배선을 포함한다)을 형성하기 위한 도전막을 형성하고, 해당 도전막을 가공하여, 소스 전극(104a) 및 드레인 전극(104b)을 형성한다(도 2(B) 참조). 또한 여기서 형성되는 소스 전극(104a)의 단부와 드레인 전극(104b)의 단부의 간격에 의해, 트랜지스터의 채널장(L)이 결정되게 된다.

- [0074] 소스 전극(104a) 및 드레인 전극(104b)에 이용하는 도전막으로서는, 예를 들면, Al, Cr, Cu, Ta, Ti, Mo, W로부터 선택된 원소를 포함한 금속막, 또는 상술한 원소를 성분으로 하는 금속 질화물막(질화 티탄막, 질화 몰리브덴막, 질화 텅스텐막) 등이 있다. 또한, Al, Cu 등의 금속막의 하측 또는 상측중의 한쪽 또는 양쪽에 Ti, Mo, W 등의 고용접 금속막 또는 이들의 금속 질화물막(질화 티탄막, 질화 몰리브덴막, 질화 텅스텐막)을 적층시킨 도전막을 이용하여도 좋다.

- [0075] 또한, 소스 전극(104a) 및 드레인 전극(104b)에 이용하는 도전막은, 도전성의 금속 산화물로 형성하여도 좋다. 도전성의 금속 산화물로서는 산화 인듐( $In_2O_3$ ), 산화 주석( $SnO_2$ ), 산화 아연( $ZnO$ ), 산화 인듐 산화 주석 합금 ( $In_2O_3-SnO_2$ , ITO로 약기한다), 산화 인듐 산화 아연 합금( $In_2O_3-ZnO$ ) 또는 이들의 금속 산화물 재료에 산화 실리콘을 포함시킨 것을 이용할 수가 있다.

- [0076] 도전막의 가공은, 레지스트 마스크를 이용한 에칭에 의해 실시할 수가 있다. 해당 에칭에 이용하는 레지스트 마스크 형성시의 노광에는, 자외선이나 KrF 레이저광이나 ArF 레이저광 등을 이용하면 좋다.

- [0077] 또한, 채널장(L)=25 nm 미만의 노광을 실시하는 경우에는, 예를 들면, 수 nm~수 10 nm로 극히 좁은 초자외선(Extreme Ultraviolet)을 이용하여, 레지스트 마스크 형성시의 노광을 실시하면 좋다. 초자외선에 의한 노광은, 해상도가 높고 초점심도도 크다. 따라서, 후에 형성되는 트랜지스터의 채널장(L)을 미세화하는 것이 가능하고, 회로의 동작 속도를 높일 수가 있다.

- [0078] 또한, 이른바 다계조 마스크에 의해 형성된 레지스트 마스크를 이용하여 에칭 공정을 실시하여도 괜찮다. 다계조 마스크를 이용하여 형성된 레지스트 마스크는, 복수의 막두께를 갖는 형상이 되며, 애설에 의해 더욱 형상을 변형시킬 수가 있기 때문에, 다른 패턴으로 가공하는 복수의 에칭 공정에 이용하는 것이 가능하다. 이 때문에, 한 장의 다계조 마스크에 의해, 적어도 2종류 이상의 다른 패턴에 대응하는 레지스트 마스크를 형성할 수가 있다. 즉, 공정의 간략화가 가능해진다.

- [0079] 다음으로, 절연막(102)상에, 소스 전극(104a) 및 드레인 전극(104b)과 접하는 산화물 반도체막을 형성하고, 해당 산화물 반도체막을 가공하여 섬 형상의 산화물 반도체막(106)을 형성한다(도 2(C) 참조).

- [0080] 산화물 반도체막은, 수소나 물 등이 혼입하기 어려운 방법으로 제작하는 것이 바람직하다. 예를 들면, 스팍터링법 등을 이용하여 제작할 수가 있다. 또한, 산화물 반도체막의 두께는, 3 nm 이상 30 nm 이하로 하는 것이 바람직하다. 산화물 반도체막을 너무 두껍게 하면 (예를 들면, 막두께를 50 nm 이상), 트랜지스터가 노멀리온이 되어 버릴 우려가 있기 때문이다.

- [0081] 산화물 반도체막에 이용하는 재료로서는, 예를 들면, 인듐을 함유하는 산화물 반도체 재료나, 인듐 및 갈륨을 함유하는 산화물 반도체 재료 등이 있다.

- [0082] 또한, 산화물 반도체막에 이용하는 재료로서는, 4원계 금속 산화물인 In-Sn-Ga-Zn-O계의 재료나, 3원계 금속 산화물인 In-Ga-Zn-O계의 재료, In-Sn-Zn-O계의 재료, In-Al-Zn-O계의 재료, Sn-Ga-Zn-O계의 재료, Al-Ga-Zn-O계의 재료, Sn-Al-Zn-O계의 재료나, 2원계 금속 산화물인 In-Zn-O계의 재료, Sn-Zn-O계의 재료, Al-Zn-O계의 재료, Zn-Mg-O계의 재료, Sn-Mg-O계의 재료, In-Mg-O계의 재료, In-Ga-O계의 재료나, 단원계 금속 산화물인 In-O계의 재료, Sn-O계의 재료, Zn-O계의 재료 등이 있다. 또한, 상기의 재료에 산화 규소를 포함시켜도 괜찮다. 여기서, 예를 들면, In-Ga-Zn-O계의 재료란, 인듐(In), 갈륨(Ga), 아연(Zn)을 갖는 산화물막이라는 의미이며, 그 조성비는 특별히 묻지 않는다. 또한, In와 Ga와 Zn 이외의 원소를 포함하고 있어도 괜찮다.

- [0083] 또한, 산화물 반도체막은, 화학식  $InM_0_3(ZnO)_m$  ( $m>0$ )로 표기되는 재료를 이용한 박막으로 할 수가 있다. 여기서, M은, Ga, Al, Mn 및 Co로부터 선택된 1종 또는 복수의 금속 원소를 나타낸다. 예를 들면, M으로서 Ga, Ga 및 Al, Ga 및 Mn, 또는 Ga 및 Co 등을 이용할 수가 있다.

- [0084] 또한, 산화물 반도체막으로서 In-Zn-O계의 재료를 이용하는 경우, 이용하는 타겟의 조성비는, 원자수비로,  $In:Zn=50:1\sim1:2$ (몰비)로 환산하면  $In_2O_3:ZnO=25:1\sim1:4$ , 바람직하게는  $In:Zn=20:1\sim1:1$ (몰비)로 환산하면  $In_2O_3:ZnO=10:1\sim1:2$ , 더욱 바람직하게는  $In:Zn=15:1\sim1.5:1$ (몰비)로 환산하면  $In_2O_3:ZnO=15:2\sim3:4$ 으로 한다. 예를 들면, In-Zn-O계 산화물 반도체의 형성에 이용하는 타겟은, 원자수비가  $In:Zn:X:Y:Z$  일때,  $Z>1.5X+Y$ 로 한다.

- [0085] 본 실시형태에서는, 산화물 반도체막을, In-Ga-Zn-O계의 산화물 반도체 성막용 타겟을 이용한 스퍼터링법에 의해 형성한다.

- [0086] In-Ga-Zn-O계의 산화물 반도체 성막용 타겟으로서는, 예를 들면, 조성비로서  $In_2O_3:Ga_2O_3:ZnO=1:1:1$ [몰비]의 산화물 반도체 성막용 타겟을 이용할 수가 있다. 또한 타겟의 재료 및 조성을 상술한 것에 한정할 필요는 없다. 예를 들면,  $In_2O_3:Ga_2O_3:ZnO=1:1:2$ [몰비]의 조성비의 산화물 반도체 성막용 타겟을 이용할 수도 있다.

- [0087] 산화물 반도체 성막용 타겟의 충전율은, 90% 이상 100% 이하, 바람직하게는 95% 이상 99.9% 이하로 한다. 충전율이 높은 산화물 반도체 성막용 타겟을 이용함으로써, 성막한 산화물 반도체막은 치밀한 막으로 할 수가 있기 때문이다.

- [0088] 성막의 분위기는, 희가스(대표적으로는 아르곤) 분위기하, 산소 분위기하, 또는 희가스와 산소의 혼합 분위기하 등으로 하면 좋다. 또한, 산화물 반도체막으로의 수소, 물, 수산기, 수소화물 등의 혼입을 막기 위해서, 수소, 물, 수산기, 수소화물 등의 수소 원자를 포함한 불순물이 충분히 제거된 고순도 가스를 이용한 분위기로 하는 것이 바람직하다.

- [0089] 보다 구체적으로는, 예를 들면, 산화물 반도체막은 다음과 같이 형성할 수가 있다.

- [0090] 우선, 감압 상태로 유지된 성막실내에 기관(100)을 유지하고, 기관 온도를  $100^{\circ}\text{C}$  이상  $600^{\circ}\text{C}$  이하, 바람직하게는  $200^{\circ}\text{C}$  이상  $400^{\circ}\text{C}$  이하로 한다. 기관(100)이 가열된 상태로 성막을 실시함으로써, 산화물 반도체막에 포함되는 불순물 농도를 저감할 수가 있기 때문이다. 또한, 스퍼터링에 의한 산화물 반도체막의 손상을 경감할 수가 있기 때문이다.

- [0091] 다음으로, 성막실내의 잔류 수분을 제거하면서, 수소 및 물 등의 수소 원자를 포함한 불순물이 충분히 제거된 고순도 가스를 도입하고, 상기 타겟을 이용하여 기관(100)상에 산화물 반도체막을 성막한다. 성막실내의 잔류 수분을 제거하기 위해서는, 배기 수단으로서 크라이오 펌프, 이온 펌프, 티탄 서블리메이션(sublimation) 펌프 등의 흡착형의 진공 펌프를 이용하는 것이 바람직하다. 또한, 배기 수단은, 터보 분자 펌프에 콜드 트랩을 부가한 것이라도 괜찮다. 크라이오 펌프를 이용하여 배기한 성막실은, 예를 들면, 수소 분자나, 물( $H_2O$ ) 등의 수소 원자를 포함한 화합물(보다 바람직하게는 탄소 원자를 포함한 화합물도) 등이 제거되어 있기 때문에, 해당 성막실에서 성막한 산화물 반도체막에 포함되는 불순물의 농도를 저감할 수 있다.

- [0092] 성막 조건의 일 예로서 기관과 타겟의 사이와의 거리를 100 mm, 압력을 0.6 Pa, 직류(DC) 전원을 0.5 kW, 성막 분위기를 산소(산소 유량 비율 100%) 분위기로 할 수가 있다. 또한 월스 직류 전원을 이용하면, 성막시의 분말상 물질(파티클, 쓰레기라고도 한다)의 발생을 경감할 수 있고 막두께의 불규칙도 작아지기 때문에 바람직하다.

- [0093] 산화물 반도체막의 가공은, 원하는 형상의 마스크를 산화물 반도체막상에 형성한 후, 해당 산화물 반도체막을 에칭함으로써 실시할 수가 있다. 상술한 마스크는, 포토리소그래피 등의 방법을 이용하여 형성할 수가 있다.

또는, 잉크젯법 등의 방법을 이용하여 마스크를 형성하여도 좋다.

[0094] 또한, 산화물 반도체막의 예칭은, 건식 예칭이라도 습식 예칭이라도 좋다. 물론, 이들을 조합하여 이용하여도 괜찮다.

[0095] 그 후, 산화물 반도체막(106)에 대하여 열처리를 실시하여, 고순도화된 산화물 반도체막(108)을 형성한다(도 2(D) 참조). 이 열처리에 의해 산화물 반도체막(106) 중의, 수소(물이나 수산기를 포함한다)를 제거하고, 산화물 반도체막의 구조를 정돈하여 에너지갭중의 결함 준위를 저감할 수가 있다. 상기 열처리의 온도는, 250°C 이상 650°C 이하, 바람직하게는 450°C 이상 600°C 이하다. 또한 상기 열처리의 온도는, 기판의 왜곡점 미만으로 하는 것이 바람직하다.

[0096] 열처리는, 예를 들면, 저항 발열체 등을 이용한 전기로에 피처리물을 도입하고, 질소 분위기하, 450°C, 1시간의 조건으로 실시할 수가 있다. 이 동안, 산화물 반도체막(106)은 대기에 접하지 않게 하여, 물이나 수소의 혼입이 생기지 않도록 한다.

[0097] 열처리 장치는 전기로에 한정되지 않고, 가열된 가스 등의 매체로부터의 열전도, 또는 열복사에 의해, 피처리물을 가열하는 장치를 이용하여도 좋다. 예를 들면, LRTA(Lamp Rapid Thermal Anneal) 장치, GRTA(Gas Rapid Thermal Anneal) 장치 등의 RTA(Rapid Thermal Anneal) 장치를 이용할 수가 있다. LRTA 장치는, 할로겐 램프, 메탈할라이드 램프, 크세논 아크 램프, 카본 아크 램프, 고압 나트륨 램프, 고압 수은 램프 등의 램프로부터 발하는 광(전자파)의 복사에 의해 피처리물을 가열하는 장치다. GRTA 장치는, 고온의 가스를 이용하여 열처리를 실시하는 장치다. 가스로서는, 아르곤 등의 희가스, 또는 질소와 같은, 열처리에 의해 피처리물과 반응하지 않는 불활성 기체가 이용된다.

[0098] 예를 들면, 상기 열처리로서, 가열된 불활성 가스 분위기중에 피처리물을 투입하고, 몇 분간 가열한 후, 해당 불활성 가스 분위기로부터 피처리물을 취출하는 GRTA 처리를 실시하여도 괜찮다. GRTA 처리를 이용하면 단시간에서의 고온 열처리가 가능해진다. 또한, 피처리물의 내열 온도를 넘는 온도 조건이라도 적용이 가능해진다. 또한 처리중에, 불활성 가스를, 산소를 포함한 가스로 전환하여도 좋다. 산소를 포함한 분위기에서 열처리를 실시함으로써, 산소 결손에 기인하는 에너지갭중의 결함 준위를 저감할 수가 있기 때문이다.

[0099] 또한, 불활성 가스 분위기로서는, 질소, 또는 희가스(헬륨, 네온, 아르곤 등)를 주성분으로 하는 분위기이며, 물, 수소 등이 포함되지 않는 분위기를 적용하는 것이 바람직하다. 예를 들면, 열처리 장치에 도입하는 질소나, 헬륨, 네온, 아르곤 등의 희가스의 순도를, 6 N(99.9999%) 이상, 바람직하게는 7 N(99.99999%) 이상(즉, 불순물 농도가 1 ppm 이하, 바람직하게는 0.1 ppm 이하)로 한다.

[0100] 어쨌든, 상기 열처리에 의해 불순물을 저감하여, i형(진성) 반도체 또는 i형에 극히 가까운 산화물 반도체막을 형성함으로써, 극히 뛰어난 특성의 트랜지스터를 실현할 수가 있다.

[0101] 그런데, 상술한 열처리에는 수소나 물 등을 제거하는 효과가 있기 때문에, 해당 열처리를, 탈수화 처리나, 탈수소화 처리 등이라고 부를 수도 있다. 해당 탈수화 처리나, 탈수소화 처리는, 예를 들면, 산화물 반도체막을 섬형상으로 가공하기 전 등의 타이밍에서 실시하는 것도 가능하다. 또한, 이러한 탈수화 처리, 탈수소화 처리는, 1회에 한정하지 않고 여러 차례 실시하여도 좋다.

[0102] 다음으로, 산화물 반도체막(108)에 대하여, 산소(180)에 의한 처리(산소 도핑 처리나, 산소 플라즈마 도핑 처리라고도 한다)를 실시한다(도 2(E) 참조). 여기서, 산소(180)에는, 적어도, 산소 라디칼, 산소 원자, 산소 이온 중의 한쪽이 포함되어 있다. 산화물 반도체막(108)에 산소 도핑 처리를 실시함으로써, 산화물 반도체막(108)중, 산화물 반도체막(108) 계면 균방, 또는 산화물 반도체막(108)중 및 그 계면 균방에 산소를 함유시킬 수가 있다. 이 경우, 산소의 함유량은, 산화물 반도체막(108)의 화학량론비를 넘는 정도, 바람직하게는, 화학량론비의 1배를 넘어 2배까지(1배보다 크고 2배 미만)로 한다. 혹은, 산소의 함유량은, 단 결정의 경우의 산소의 양을 Y로 하여, Y를 넘는 정도, 바람직하게는, Y를 넘어 2Y까지로 할 수도 있다. 혹은, 산소의 함유량은, 산소 도핑 처리를 실시하지 않는 경우의 산화물 반도체막중의 산소의 양 Z를 기준으로 하여, Z를 넘는 정도, 바람직하게는, Z를 넘어 2Z까지로 할 수도 있다. 또한 상술한 바람직한 범위에 상한이 존재하는 것은, 산소의 함유량을 너무 많이 하면, 수소흡장합금(수소저장합금)과 같이, 오히려 산화물 반도체막(108)이 수소를 취입해 버릴 우려가 있기 때문이다. 또한 산화물 반도체막에 있어서 산소의 함유량은 수소의 함유량 보다 커진다.

[0103] 결정 구조가  $\text{InGaO}_3(\text{ZnO})_m$  ( $m > 0$ )로 표현되는 재료의 경우, 예를 들면, M=1( $\text{InGaZnO}_4$ )의 결정 구조를 기준으로 하

면,  $InGaZnO_x$ 에 있어서  $x$ 는 4를 넘어 8까지, 또한  $m=2$ ( $InGaZn_2O_5$ )의 결정 구조를 기준으로 하면,  $InGaZn_2O_x$ 에 있어서  $x$ 는 5를 넘어 10까지가 허용된다. 또한 이러한 산소 과잉 영역은, 산화물 반도체의 일부(계면을 포함한다)에 존재하고 있으면 좋다.

[0104] 또한, 산화물 반도체막에 있어서, 산소는 주된 성분의 하나이다. 이 때문에, 산화물 반도체막중의 산소 농도를, SIMS(Secondary Ion Mass Spectroscopy) 등의 방법을 이용하여, 정확하게 추측하는 것은 어렵다. 즉, 산화물 반도체막에 산소가 의도적으로 첨가되었는지 아닌지를 판별하는 것은 곤란하다고 말할 수 있다.

[0105] 그런데, 산소에는  $^{17}O$ 나  $^{18}O$ 라고 하는 동위체가 존재하고, 자연계에 있어서의 이러한 존재 비율은 각각 산소 원자 전체의 0.037%, 0.204%정도인 것이 알려져 있다. 즉, 산화물 반도체막중에 있어서의 이들 동위체의 농도는, SIMS 등의 방법에 의해 추측할 수가 있는 정도가 되기 때문에, 이들의 농도를 측정함으로써, 산화물 반도체막중의 산소 농도를 보다 정확하게 추측하는 것이 가능한 경우가 있다. 따라서, 이들의 농도를 측정함으로써, 산화물 반도체막에 의도적으로 산소가 첨가되었는지 아닌지를 판별하여도 좋다.

[0106] 예를 들면,  $^{18}O$ 의 농도를 기준으로 이용하면, 산화물 반도체막에 있어서, 산소가 첨가된 영역에 있어서의 산소의 동위체의 농도  $D1(^{18}O)$ 과, 산소가 첨가되어 있지 않은 영역에 있어서의 산소의 동위체의 농도  $D2(^{18}O)$ 의 사이에는,  $D1(^{18}O) > D2(^{18}O)$ 가 성립한다고 말할 수 있다.

[0107] 또한, 산화물 반도체막에 첨가되는 산소( $^{18}O$ )의 적어도 일부는, 산화물 반도체 중에서 미결합손을 갖는 것이 바람직하다. 미결합손을 가짐에 의해, 막중에 잔존할 수 있는 수소와 결합하여 수소를 고정화(비가동 이온화)할 수가 있기 때문이다.

[0108] 상술한 산소(180)는, 플라즈마 발생 장치나 오존 발생 장치에 의해 발생시킬 수가 있다. 보다 구체적으로는, 예를 들면, 반도체 장치에 대하여 애칭 처리를 실시할 수가 있는 장치나, 레지스트 마스크에 대하여 애성을 실시할 수가 있는 장치 등을 이용하여 산소(180)을 발생시켜, 산화물 반도체막(108)을 처리할 수가 있다.

[0109] 또한, 산소의 첨가를 보다 매우 적합하게 실시하기 위해서는, 기판에는 전기적인 바이어스를 인가해 두는 것이 바람직하다.

[0110] 또한, 산소 도핑 처리를 실시한 산화물 반도체막(108)에 열처리(온도 150°C~470°C)를 실시하여도 괜찮다. 해당 열처리에 의해, 산소 또는 산화물 반도체 재료가 수소와 반응함으로써 생성된 물, 수산화물 등을 산화물 반도체 막으로부터 제거할 수가 있다. 열처리는, 물, 수소 등이 충분히 저감된 질소, 산소, 초건조공기(CRDS(캐비팅 다운 레이저 분광법) 방식의 노점계를 이용하여 측정했을 경우의 수분량이 20 ppm(노점 환산으로 -55°C) 이하, 바람직하게는 1 ppm 이하, 바람직하게는 10 ppb 이하의 공기), 희가스(아르곤, 헬륨 등) 등의 분위기하에서 실시하면 좋다. 또한, 산소 도핑 처리와 열처리를 반복하여 실시하여도 좋다. 해당 처리를 반복하여 실시함으로써, 트랜ジ스터의 신뢰성을 더욱 높일 수가 있다. 또한 반복의 회수는 적절히 설정할 수가 있다.

[0111] 다음으로, 산화물 반도체막(108)의 일부와 접하고, 또한 소스 전극(104a) 및 드레인 전극(104b)을 덮는 게이트 절연막(110)을 형성한다(도 2(F) 참조).

[0112] 게이트 절연막(110)은, 절연막(102)과 마찬가지로 형성할 수가 있다. 즉, 게이트 절연막(110)은, 산화 실리콘, 질화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화 갈륨, 이들의 혼합 재료 등을 이용하여 형성하면 좋다. 다만, 트랜지스터의 게이트 절연막으로서 기능하는 것을 고려하여, 산화 하프늄, 산화 탄탈륨, 산화 이트륨, 하프늄 실리케이트( $HfSi_xO_y$  ( $x>0$ ,  $y>0$ )), 질소가 첨가된 하프늄 실리케이트( $HfSi_xO_y$  ( $x>0$ ,  $y>0$ )), 질소가 첨가된 하프늄 알루미네이트( $HfAl_xO_y$  ( $x>0$ ,  $y>0$ )), 등의 비유전률이 높은 재료를 채용하여도 좋다.

[0113] 또한, 절연막(102)과 마찬가지로, 적층 구조를 채용하여도 좋다. 이 경우에는, 산화물 반도체막과 동종의 성분으로 이루어지는 절연 재료로 이루어지는 막(이하, 막a)과, 막a의 성분 재료와는 다른 재료를 포함한 막(이하, 막b)의 적층 구조로 하면 더욱 좋다. 막a와 막b를 산화물 반도체막으로부터 순서대로 적층한 구조로 함으로써, 전하는 막a와 막b의 계면의 전하 포획 중심에 우선적으로 포획되기(산화물 반도체막과 막a의 계면과의 비교) 때문에, 산화물 반도체막의 계면에서의 전하 포획을 충분히 억제할 수가 있게 되어, 반도체 장치의 신뢰성이 향상하기 때문이다.

[0114] 또한, 이러한 적층 구조로서는, 산화 갈륨막과 산화 실리콘막의 적층 구조나, 산화 갈륨막과 질화 실리콘막의

적층 구조 등을 적용할 수가 있다.

[0115] 상술한 게이트 절연막(110)의 형성 후에는, 열처리를 실시하는 것이 바람직하다. 해당 열처리의 온도는, 250°C 이상 700°C 이하, 바람직하게는 450°C 이상 600°C 이하다. 또한 해당 열처리의 온도는, 기판의 왜곡점 미만으로 하는 것이 바람직하다.

[0116] 상기 열처리는, 질소, 산소, 초건조공기(물의 함유량이 20 ppm 이하, 바람직하게는 1 ppm 이하, 바람직하게는 10 ppb 이하의 공기), 또는 희가스(아르곤, 헬륨 등)의 분위기하에서 실시하면 좋지만, 상기 질소, 산소, 초건조공기, 또는 희가스 등의 분위기에는, 물, 수소 등이 포함되지 않는 것이 바람직하다. 또한, 열처리 장치에 도입하는 질소, 산소, 또는 희가스의 순도는, 6 N(99.9999%) 이상(즉 불순물 농도를 1 ppm 이하)으로 하는 것이 바람직하고, 7 N(99.99999%) 이상(즉 불순물 농도를 0.1 ppm 이하)으로 하면, 보다 바람직하다.

[0117] 본 실시형태와 관련되는 상기의 열처리에 있어서는, 산화물 반도체막(108)과 게이트 절연막(110)이 접한 상태로 가열된다. 따라서, 상술한 탈수화(또는 탈수소화) 처리에 의해 감소해 버릴 가능성이 있는 산소를, 산화물 반도체막(108)에 공급하는 것도 가능하다. 이런 의미에서, 해당 열처리를, 가산화(가산소화)라고 부를 수도 있다.

[0118] 또한, 가산화를 목적으로 하는 열처리의 타이밍은, 산화물 반도체막(108)의 형성 후라면 특별히 한정되지 않는다. 예를 들면, 게이트 전극의 형성 후에 가산화를 목적으로 하는 열처리를 실시하여도 좋다. 또는, 탈수화 등을 목적으로 하는 열처리에 이어서 가산화를 목적으로 하는 열처리를 실시하여도 좋고, 탈수화 등을 목적으로 하는 열처리에 가산화를 목적으로 하는 열처리를 겸하게 하여도 좋고, 가산화를 목적으로 하는 열처리에 탈수화 등을 목적으로 하는 열처리를 겸하게 하여도 좋다.

[0119] 상술한 바와 같이, 탈수화 등을 목적으로 하는 열처리와 산소 도핑 처리 또는 가산화를 목적으로 하는 열처리를 적용함으로써, 산화물 반도체막(108)을 불순물이 최대한 포함되지 않게 고순도화할 수가 있다. 고순도화된 산화물 반도체막(108)중에는 도너에 유래하는 캐리어가 극히 적다(제로에 가깝다).

[0120] 그 후, 게이트 전극(112)을 형성한다(도 2(G) 참조). 게이트 전극(112)은, 몰리브덴, 티탄, 탄탈륨, 텉스텐, 알루미늄, 동, 네오디뮴, 스칸듐 등의 금속재료 또는 이들을 주성분으로 하는 합금 재료를 이용하여 형성할 수가 있다. 또한 게이트 전극(112)은, 단층 구조로 하여도 좋고, 적층 구조로 하여도 좋다.

[0121] 또한, 게이트 전극(112)의 형성 후에는, 절연막을 형성하여도 좋다. 해당 절연막은, 예를 들면, 산화 실리콘, 질화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화 갈륨, 이들의 혼합 재료 등을 이용하여 형성할 수가 있다. 특히, 절연막으로서 질화 실리콘막을 이용하는 경우에는, 첨가된 산소의 외부로의 방출을 막을 수가 있음과 동시에, 산화물 반도체막(108)으로의 외부로부터의 수소 등의 혼입을 효과적으로 억제할 수가 있기 때문에 매우 적합하다. 또한, 소스 전극(104a)이나 드레인 전극(104b), 게이트 전극(112) 등과 접속되는 배선을 형성하여도 좋다.

[0122] 이상의 공정으로 트랜지스터(120)가 형성된다.

[0123] 또한, 상술한 설명은, 섬 형상으로 가공되고 고순도화된 산화물 반도체막(108)에 대하여 산소 도핑 처리를 실시하는 예에 대한 것이지만, 개시하는 발명의 일 태양은 이에 한정되지 않는다. 예를 들면, 고순도화 및 산소 도핑 처리를 실시한 후에, 산화물 반도체막을 섬 형상으로 가공하여도 좋고, 소스 전극(104a) 및 드레인 전극(104b)을 형성한 후에 산소 도핑 처리를 실시하여도 좋다.

[0125] <반도체 장치의 변형예>

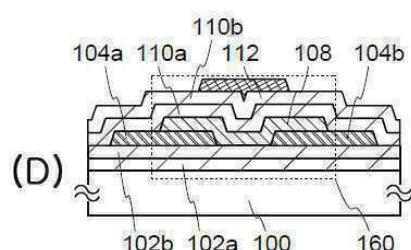

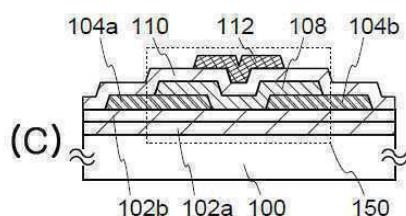

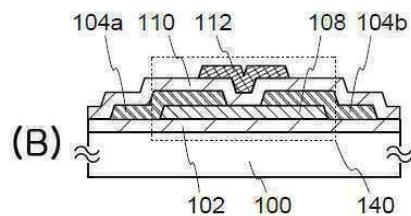

[0126] 도 3(A) 내지 도 3(D)에는, 도 1에 나타내는 트랜지스터(120)의 변형예로서, 트랜지스터(130), 트랜지스터(140), 트랜지스터(150), 및 트랜지스터(160)의 단면도를 나타낸다.

[0127] 도 3(A)에 나타내는 트랜지스터(130)는, 절연막(102), 소스 전극(104a), 드레인 전극(104b), 산화물 반도체막(108), 게이트 절연막(110), 게이트 전극(112)을 포함하는 점에서, 트랜지스터(120)와 공통되고 있다. 트랜지스터(130)와 트랜지스터(120)의 차이는, 상술한 구성요소를 덮는 절연막(114)의 유무이다. 즉, 트랜지스터(130)는, 절연막(114)을 갖고 있다. 그 외의 구성요소에 대해서는 도 1의 트랜지스터(120)와 동일하기 때문에, 자세한 것은, 도 1에 관한 기재를 참조할 수가 있다.

[0128] 도 3(B)에 나타내는 트랜지스터(140)는, 상술한 각 구성요소를 포함하는 점에서, 도 1에 나타내는 트랜지스터(120)와 공통되고 있다. 트랜지스터(140)와 트랜지스터(120)의 차이는, 소스 전극(104a) 및 드레인 전극(104b)에 대한 구조이다. 트랜지스터(140)는, 소스 전극(104a) 및 드레인 전극(104b)을 형성하는 재료로, 상술한 재료를 사용하는 반면, 트랜지스터(120)는, 소스 전극(104a) 및 드레인 전극(104b)을 형성하는 재료로, 상술한 재료를 사용하지 않고, 다른 재료를 사용하는 것이다.

b)과, 산화물 반도체막(108)의 적층 순서이다. 즉, 트랜지스터(120)에서는, 소스 전극(104a) 및 드레인 전극(104b)이 먼저 형성되는데 반하여, 트랜지스터(140)에서는, 산화물 반도체막(108)이 먼저 형성된다. 그 외의 구성요소에 대해서는, 도 1과 같다. 또한 트랜지스터(130)처럼, 절연막(114)을 갖는 구성으로 하여도 좋다.

[0129] 도 3(C)에 나타내는 트랜지스터(150)는, 상술한 각 구성요소를 포함하는 점에서, 도 1에 나타내는 트랜지스터(120)와 공통되고 있다. 트랜지스터(150)와 트랜지스터(120)의 차이는, 기판(100)측의 절연막에 있다. 즉, 트랜지스터(150)에서는, 절연막(102a)과 절연막(102b)의 적층 구조를 구비하고 있다. 그 외의 구성요소에 대해서는, 도 1(B)과 같다.

[0130] 이와 같이, 절연막(102a)과 절연막(102b)의 적층 구조로 함에 의해, 전하는 절연막(102a)과 절연막(102b)의 계면의 전하 포획 중심에 우선적으로 포획되기 때문에, 산화물 반도체막(108)의 계면에서의 전하 포획을 충분히 억제할 수가 있게 되어, 반도체 장치의 신뢰성이 향상한다.

[0131] 또한, 절연막(102b)은 산화물 반도체막(108)과 동종의 성분으로 이루어지는 절연 재료로 이루어지는 막으로 하고, 절연막(102a)은 절연막(102b)의 성분 재료와는 다른 재료를 포함한 막으로 하는 것이 바람직하다. 예를 들면, 산화물 반도체막(108)이 In-Ga-Zn계의 산화물 반도체 재료에 의해 구성되는 경우, 동종의 성분으로 이루어지는 절연 재료로서는 산화 갈륨 등이 있다. 이 경우, 산화 갈륨막과 산화 실리콘막의 적층 구조나, 산화 갈륨막과 질화 실리콘막의 적층 구조 등을 적용할 수가 있다.

[0132] 도 3(D)에 나타내는 트랜지스터(160)는, 상술한 각 구성요소를 포함하는 점에서, 도 1에 나타내는 트랜지스터(120)와 공통되고 있다. 트랜지스터(160)와 트랜지스터(120)의 차이는, 기판(100)측의 절연막 및 게이트 절연막에 있다. 즉, 트랜지스터(160)에서는, 절연막(102a)과 절연막(102b)의 적층 구조를 구비하고, 또한 게이트 절연막(110a)과 게이트 절연막(110b)의 적층 구조를 구비하고 있다. 그 외의 구성요소에 대해서는, 도 1과 같다.

[0133] 이와 같이, 절연막(102a)과 절연막(102b)의 적층 구조로 하고, 게이트 절연막(110a)과 게이트 절연막(110b)의 적층 구조로 함에 의해, 전하는 절연막(102a)과 절연막(102b)이나, 게이트 절연막(110a)과 게이트 절연막(110b)의 계면에 우선적으로 포획되기 때문에, 산화물 반도체막(108)의 계면에서의 전하 포획을 충분히 억제할 수가 있게 되어, 반도체 장치의 신뢰성이 향상한다.

[0134] 또한, 절연막(102b)이나 게이트 절연막(110a)(즉, 산화물 반도체막(108)과 접하는 절연막)은 산화물 반도체막(108)과 동종의 성분으로 이루어지는 절연 재료로 이루어지는 막으로 하고, 절연막(102a)이나 게이트 절연막(110b)은, 절연막(102b)이나 게이트 절연막(110a)의 성분 재료와는 다른 재료를 포함한 막으로 하는 것이 바람직하다. 예를 들면, 산화물 반도체막(108)이 In-Ga-Zn계의 산화물 반도체 재료에 의해 구성되는 경우, 동종의 성분으로 이루어지는 절연 재료로서는 산화 갈륨 등이 있다. 이 경우, 산화 갈륨막과 산화 실리콘막의 적층 구조나, 산화 갈륨막과 질화 실리콘막의 적층 구조 등을 적용할 수가 있다.

[0135] 본 실시형태와 관련되는 트랜지스터는, 열처리에 의해, 수소, 물, 수산기 또는 수소화물(수소화합물이라고도 한다) 등의 수소 원자를 포함한 불순물을 산화물 반도체로부터 배제하고, 또한 불순물의 배제 공정에서 감소할 우려가 있는 산소를 공급함으로써, 고순도화 및 i형(진성)화를 위한 산화물 반도체막을 이용하고 있다. 이와 같이 고순도화된 산화물 반도체막을 포함한 트랜지스터는, 스레숄드 전압 등의 전기적 특성 변동이 억제되어 있어 전기적으로 안정하다.

[0136] 특히, 산소 도핑 처리에 의해 산화물 반도체막중의 산소의 함유량을 증대시킴으로써, 전기적 바이어스 스트레스나 열스트레스에 기인하는 열화를 억제하여, 광에 의한 열화를 저감할 수가 있다.

[0137] 이와 같이, 개시하는 발명의 일 태양에 의해, 신뢰성이 뛰어난 트랜지스터를 제공하는 것이 가능하다.

[0138] 이상, 본 실시형태에 나타내는 구성, 방법 등은, 다른 실시형태에 나타내는 구성, 방법 등과 적절히 조합하여 이용할 수가 있다.

[0139] (실시형태 2)

[0140] 본 실시형태에서는, 반도체 장치의 제작 방법의 다른 예에 대하여, 도 4 및 도 5를 이용하여 설명한다.

[0141] <반도체 장치의 구성예>

[0142] 본 실시형태의 제작 방법으로 제작되는 반도체 장치의 구성은, 앞의 실시형태의 트랜지스터(120)와 같다. 즉, 기판(100)상의 절연막(102), 소스 전극(104a), 드레인 전극(104b), 산화물 반도체막(108), 게이트 절연막

(110), 게이트 전극(112)을 포함한다(도 1 참조).

[0143] 앞의 실시형태에서도 설명한 것처럼, 트랜지스터(120)에 있어서, 산화물 반도체막(108)은, 산소 도핑 처리를 한 산화물 반도체막이다. 게다가 본 실시형태에서는, 절연막(102) 및 게이트 절연막(110)에 대해서도 산소 도핑 처리를 하고 있다. 이러한 산소 도핑 처리에 의해, 더욱 신뢰성이 높아진 트랜지스터(120)가 실현된다. 또한 앞의 실시형태와 마찬가지로, 구성을 변경한 트랜지스터를 제작할 수도 있다(도 3(A) 내지 도 3(D) 참조).

[0144] <반도체 장치의 제작 공정 예>

[0145] 이하, 도 4 및 도 5를 이용하여, 상술한 반도체 장치의 제작 공정의 일 예를 설명한다.

[0146] 우선, 기판(100)상에 절연막(102)을 형성한다(도 4(A) 참조).

[0147] 기판(100)의 재질 등에 큰 제한은 없지만, 적어도, 후의 열처리에 견디는 정도의 내열성을 갖고 있는 것이 필요하다. 예를 들면, 유리 기판, 세라믹 기판, 석영 기판, 사파이어 기판 등을, 기판(100)으로서 이용할 수가 있다. 또한, 실리콘이나 탄화 실리콘 등의 단결정 반도체 기판, 다결정 반도체 기판, 실리콘 게르마늄 등의 화합물 반도체 기판, SOI 기판 등을 적용하는 것도 가능하고, 이러한 기판상에 반도체소자가 마련된 것을, 기판(100)으로서 이용하여도 괜찮다.

[0148] 또한, 기판(100)으로서 가요성 기판을 이용하여도 괜찮다. 가요성 기판상에 트랜지스터를 마련하는 경우, 가요성 기판상에 직접적으로 트랜지스터를 만들어도 괜찮고, 다른 기판에 트랜지스터를 형성한 후, 이를 박리하고, 가요성 기판에 전치하여도 좋다. 또한 트랜지스터를 박리하고, 가요성 기판에 전치하기 위해서는, 상기 다른 기판과 트랜지스터와의 사이에 박리층을 형성하면 좋다.

[0149] 절연막(102)은 기초로서 기능하는 절연막이다. 구체적으로는, 절연막(102)에는, 산화 실리콘, 질화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화 갈륨, 이들의 혼합 재료 등을 이용하면 좋다. 또한, 절연막(102)은, 상술한 재료를 포함한 절연막의 단층 구조로 하여도 좋고, 적층 구조로 하여도 좋다.

[0150] 절연막(102)의 제작 방법에 특별히 한정은 없다. 예를 들면, 플라즈마 CVD법이나 스퍼터링법 등의 성막 방법을 이용하여 절연막(102)을 제작할 수가 있다. 또한 수소나 물 등이 흡입하기 어렵다고 하는 점에서는, 스퍼터링 법이 매우 적합하다.

[0151] 또한, 절연막(102)에는, 후에 형성되는 산화물 반도체막과 동종의 성분으로 이루어지는 절연 재료를 이용하면 특히 바람직하다. 이러한 재료는 산화물 반도체막과의 상성이 좋고, 이를 절연막(102)에 이용함으로써, 산화물 반도체막과의 계면 상태를 양호하게 유지할 수가 있기 때문이다. 여기서, 「산화물 반도체막과 동종의 성분」이란, 산화물 반도체막의 성분 원소로부터 선택되는 1종 또는 복수의 원소를 의미한다. 예를 들면, 산화물 반도체막이 In-Ga-Zn계의 산화물 반도체 재료에 의해 구성되는 경우, 동종의 성분으로 이루어지는 절연 재료로서는 산화 갈륨 등이 있다.

[0152] 또한, 절연막(102)을 적층 구조로 하는 경우에는, 산화물 반도체막과 동종의 성분으로 이루어지는 절연 재료로 이루어지는 막(이하, 막a)과, 막a의 성분 재료와는 다른 재료를 포함한 막(이하, 막b)의 적층 구조로 하면 더욱 좋다. 막a와 막b를 산화물 반도체막층으로부터 순서대로 적층한 구조로 함으로써, 전하는 막a와 막b의 계면의 전하 포획 중심에 우선적으로 포획되기(산화물 반도체막과 막a의 계면과의 비교) 때문에 산화물 반도체막의 계면에서의 전하 포획을 충분히 억제할 수가 있게 되어, 반도체 장치의 신뢰성이 향상하기 때문이다.

[0153] 또한, 이러한 적층 구조로서는, 산화 갈륨막과 산화 실리콘막의 적층 구조나, 산화 갈륨막과 질화 실리콘막의 적층 구조 등을 적용할 수가 있다.

[0154] 다음으로, 절연막(102)에 대하여, 산소(180a)에 의한 처리(산소 도핑 처리나, 산소 플라즈마 도핑 처리라고도 한다)를 실시한다(도 4(B) 참조). 산소(180a)에는, 적어도, 산소 라디칼, 산소 원자, 산소 이온중의 어느 것인가가 포함되어 있다. 절연막(102)에 산소 도핑 처리를 실시함으로써, 절연막(102)중에 산소를 함유시킬 수가 있으며, 후에 형성되는 산화물 반도체막(108)중, 산화물 반도체막(108) 계면 근방, 또는 산화물 반도체막(108) 중 및 그 계면 근방에 산소를 함유시킬 수가 있다. 이 경우, 절연막(102)중의 산소의 함유량은, 절연막(102)의 화학량론비를 넘는 정도, 바람직하게는, 화학량론비의 1배를 넘어 4배까지(1배보다 크고 4배 미만), 보다 바람직하게는, 1배를 넘어 2배까지(1배보다 크고 2배 미만)로 한다. 혹은, 산소의 함유량은, 단결정의 경우의 산소의 양을 Y로 하여, Y를 넘는 정도, 바람직하게는, Y를 넘어 4Y까지 할 수도 있다. 혹은, 산소의 함유량은, 산소 도핑 처리를 실시하지 않는 경우의 절연막중의 산소의 양 Z를 기준으로 하여, Z를 넘는 정도, 바람직하게는,

Z를 넘어 4Z까지로 할 수도 있다.

[0155] 예를 들면, 조성이  $GaO_x$  ( $x>0$ )로 표현되는 산화 갈륨을 이용하는 경우, 단결정의 산화 갈륨은  $Ga_2O_3$ 이므로, x는 1.5를 넘어 6까지(즉 Ga의 1.5배를 넘어 6배까지)가 허용된다. 또한, 예를 들면, 조성이  $SiO_x$  ( $x>0$ )로 표현되는 산화 실리콘을 이용하는 경우,  $SiO_2$ (즉 O가 Si의 2배)이면, x는 2를 넘어 8까지(즉 Si의 2배를 넘어 8배까지)가 허용된다. 또한 이러한 산소 과잉 영역은, 절연막의 일부(계면을 포함한다)에 존재하고 있으면 좋다.

[0156] 또한, 절연막에 첨가되는 산소(180a)의 적어도 일부는, 산화물 반도체에 공급된 후, 산화물 반도체 중에서 미결합손을 갖는 것이 바람직하다. 미결합손을 가짐에 의해, 막중에 잔존할 수 있는 수소와 결합하여 수소를 고정화(비가동 이온화)할 수가 있기 때문이다.

[0157] 상술한 산소(180a)는, 플라즈마 발생 장치나 오존 발생 장치에 의해 발생시킬 수가 있다. 보다 구체적으로는, 예를 들면, 반도체 장치에 대하여 에칭 처리를 실시할 수가 있는 장치나, 레지스트 마스크에 대하여 애싱을 실시할 수가 있는 장치 등을 이용하여 산소(180a)를 발생시켜, 절연막(102)을 처리할 수가 있다.

[0158] 또한, 산소의 첨가를 보다 매우 적합하게 실시하기 위해서는, 기판에는 전기적인 바이어스를 인가해 두는 것이 바람직하다.

[0159] 그 다음으로, 절연막(102)상에, 소스 전극 및 드레인 전극(이와 동일한 층에서 형성되는 배선을 포함한다)을 형성하기 위한 도전막을 형성하고, 해당 도전막을 가공하여, 소스 전극(104a) 및 드레인 전극(104b)을 형성한다(도 4(C) 참조). 또한 여기서 형성되는 소스 전극(104a)의 단부와 드레인 전극(104b)의 단부의 간격에 의해, 트랜지스터의 채널장(L)이 결정되게 된다.

[0160] 소스 전극(104a) 및 드레인 전극(104b)에 이용하는 도전막으로서는, 예를 들면, Al, Cr, Cu, Ta, Ti, Mo, W로부터 선택된 원소를 포함한 금속막, 또는 상술한 원소를 성분으로 하는 금속 질화물막(질화 티탄막, 질화 몰리브덴막, 질화 텉스텐막) 등이 있다. 또한, Al, Cu 등의 금속막의 하측 또는 상측중의 한쪽 또는 양쪽에 Ti, Mo, W 등의 고용점 금속막 또는 이들의 금속 질화물막(질화 티탄막, 질화 몰리브덴막, 질화 텉스텐막)을 적층시킨 도전막을 이용하여도 좋다.

[0161] 또한, 소스 전극(104a) 및 드레인 전극(104b)에 이용하는 도전막은, 도전성의 금속 산화물로 형성하여도 좋다. 도전성의 금속 산화물로서는 산화 인듐( $In_2O_3$ ), 산화 주석( $SnO_2$ ), 산화 아연( $ZnO$ ), 산화 인듐 산화 주석 합금 ( $In_2O_3-SnO_2$ , ITO로 약기한다), 산화 인듐 산화 아연 합금( $In_2O_3-ZnO$ ) 또는 이들의 금속 산화물 재료에 산화 실리콘을 포함시킨 것을 이용할 수가 있다.

[0162] 도전막의 가공은, 레지스트 마스크를 이용한 에칭에 의해 실시할 수가 있다. 해당 에칭에 이용하는 레지스트 마스크 형성시의 노광에는, 자외선이나 KrF 레이저광이나 ArF 레이저광 등을 이용하면 좋다.

[0163] 또한, 채널장(L)이 25 nm 미만인 노광을 실시하는 경우에는, 예를 들면, 수 nm~수 10 nm로 극히 파장이 짧은 초자외선(Extreme Ultraviolet)을 이용하여, 레지스트 마스크 형성시의 노광을 실시하면 좋다. 초자외선에 의한 노광은, 해상도가 높고 초점심도도 크다. 따라서, 후에 형성되는 트랜지스터의 채널장(L)을 미세화하는 것이 가능하고, 회로의 동작 속도를 높일 수가 있다.

[0164] 또한, 이른바 다계조 마스크에 의해 형성된 레지스트 마스크를 이용하여 에칭 공정을 실시하여도 괜찮다. 다계조 마스크를 이용하여 형성된 레지스트 마스크는, 복수의 막두께를 갖는 형상이 되며, 애싱에 의해 더욱 형상을 변형시킬 수가 있기 때문에, 다른 패턴으로 가공하는 복수의 에칭 공정에 이용하는 것이 가능하다. 이 때문에, 한 장의 다계조 마스크에 의해, 적어도 2종류 이상의 다른 패턴에 대응하는 레지스트 마스크를 형성할 수가 있다. 즉, 공정의 간략화가 가능해진다.

[0165] 다음으로, 절연막(102)상에, 소스 전극(104a) 및 드레인 전극(104b)과 접하는 산화물 반도체막을 형성하고, 해당 산화물 반도체막을 가공하여 섬 형상의 산화물 반도체막(106)을 형성한다(도 4(D) 참조).

[0166] 산화물 반도체막은, 수소나 물 등이 혼입하기 어려운 방법으로 제작하는 것이 바람직하다. 예를 들면, 스퍼터링법 등을 이용하여 제작할 수가 있다. 또한, 산화물 반도체막의 두께는, 3 nm 이상 30 nm 이하로 하는 것이 바람직하다. 산화물 반도체막을 너무 두껍게 하면 (예를 들면, 막두께를 50 nm 이상), 트랜지스터가 노멀리온이 되어 버릴 우려가 있기 때문이다.

- [0167] 산화물 반도체막에 이용하는 재료로서는, 4원계 금속 산화물인 In-Sn-Ga-Zn-0계의 재료나, 3원계 금속 산화물인 In-Ga-Zn-0계의 재료, In-Sn-Zn-0계의 재료, In-Al-Zn-0계의 재료, Sn-Ga-Zn-0계의 재료, Al-Ga-Zn-0계의 재료, Sn-Al-Zn-0계의 재료나, 2원계 금속 산화물인 In-Zn-0계의 재료, Sn-Zn-0계의 재료, Al-Zn-0계의 재료, Zn-Mg-0계의 재료, Sn-Mg-0계의 재료, In-Mg-0계의 재료, In-Ga-0계의 재료나, 단원계 금속 산화물인 In-0계의 재료, Sn-0계의 재료, Zn-0계의 재료 등이 있다. 또한, 상기의 재료에 산화 규소를 포함시켜도 괜찮다. 여기서, 예를 들면, In-Ga-Zn-0계의 재료란, 인듐(In), 갈륨(Ga), 아연(Zn)을 갖는 산화물막이라는 의미이며, 그 조성비는 특별히 묻지 않는다. 또한, In와 Ga와 Zn 이외의 원소를 포함하고 있어도 괜찮다.

- [0168] 또한, 산화물 반도체막은, 화학식  $InMO_3(ZnO)_m$  ( $m > 0$ )로 표기되는 재료를 이용한 박막으로 할 수가 있다. 여기서, M은, Ga, Al, Mn 및 Co로부터 선택된 1종 또는 복수의 금속 원소를 나타낸다. 예를 들면, M으로서 Ga, Ga 및 Al, Ga 및 Mn, 또는 Ga 및 Co 등을 이용할 수가 있다.

- [0169] 또한, 산화물 반도체막으로서 In-Zn-0계의 재료를 이용하는 경우, 이용하는 타겟의 조성비는, 원자수비로,  $In:Zn=50:1\sim1:2$ (몰비)로 환산하면  $In_2O_3:ZnO=25:1\sim1:4$ , 바람직하게는  $In:Zn=20:1\sim1:1$ (몰비)로 환산하면  $In_2O_3:ZnO=10:1\sim1:2$ , 더욱 바람직하게는  $In:Zn=15:1\sim1.5:1$ (몰비)로 환산하면  $In_2O_3:ZnO=15:2\sim3:4$ 으로 한다. 예를 들면, In-Zn-0계 산화물 반도체의 형성에 이용하는 타겟은, 원자수비가  $In:Zn:X:Y:Z=1:1:X:Y:Z$ 일 때,  $Z > 1.5X+Y$ 로 한다.

- [0170] 본 실시형태에서는, 산화물 반도체막을, In-Ga-Zn-0계의 산화물 반도체 성막용 타겟을 이용한 스퍼터링법에 의해 형성한다.

- [0171] In-Ga-Zn-0계의 산화물 반도체 성막용 타겟으로서는, 예를 들면, 조성비로서  $In_2O_3:Ga_2O_3:ZnO=1:1:1$ [몰비]의 산화물 반도체 성막용 타겟을 이용할 수가 있다. 또한 타겟의 재료 및 조성을 상술한 것에 한정할 필요는 없다. 예를 들면,  $In_2O_3:Ga_2O_3:ZnO=1:1:2$ [몰비]의 조성비의 산화물 반도체 성막용 타겟을 이용할 수도 있다.

- [0172] 산화물 반도체 성막용 타겟의 충전율은, 90% 이상 100% 이하, 바람직하게는 95% 이상 99.9% 이하로 한다. 충전율이 높은 산화물 반도체 성막용 타겟을 이용함으로써, 성막한 산화물 반도체막은 치밀한 막으로 할 수가 있기 때문이다.

- [0173] 성막의 분위기는, 희가스(대표적으로는 아르곤) 분위기하, 산소 분위기하, 또는 희가스와 산소의 혼합 분위기하 등으로 하면 좋다. 또한, 산화물 반도체막으로의 수소, 물, 수산기, 수소화물 등의 혼입을 막기 위해서, 수소, 물, 수산기, 수소화물 등의 수소 원자를 포함한 불순물이 충분히 제거된 고순도 가스를 이용한 분위기로 하는 것이 바람직하다.

- [0174] 또한, 산화물 반도체막의 성막 시에, 절연막(102)중의 산소가 산화물 반도체막에 공급되는 일이 있다. 이와 같이, 절연막(102)에 산소를 첨가해 둠으로써, 산소가 충분히 첨가된 산화물 반도체막을 제작하는 것이 가능하다.

- [0175] 보다 구체적으로는, 예를 들면, 산화물 반도체막은 다음과 같이 형성할 수가 있다.

- [0176] 우선, 감압 상태로 유지된 성막실내에 기판(100)을 유지하고, 기판 온도를  $100^{\circ}\text{C}$  이상  $600^{\circ}\text{C}$  이하 바람직하게는  $200^{\circ}\text{C}$  이상  $400^{\circ}\text{C}$  이하로 한다. 기판(100)이 가열된 상태로 성막을 실시함으로써, 산화물 반도체막에 포함되는 불순물 농도를 저감할 수가 있기 때문이다. 또한, 스퍼터링에 의한 산화물 반도체막의 손상을 경감할 수가 있기 때문이다.

- [0177] 다음으로, 성막실내의 잔류 수분을 제거하면서, 수소 및 물 등의 수소 원자를 포함한 불순물이 충분히 제거된 고순도 가스를 도입하고, 상기 타겟을 이용하여 기판(100)상에 산화물 반도체막을 성막한다. 성막실내의 잔류 수분을 제거하기 위해서는, 배기 수단으로서 크라이오 펌프, 이온 펌프, 티탄 서블리메이션 펌프 등의 흡착형의 진공 펌프를 이용하는 것이 바람직하다. 또한, 배기 수단은, 터보 분자 펌프에 콜드 트랩을 부가한 것이라도 괜찮다. 크라이오 펌프를 이용하여 배기한 성막실은, 예를 들면, 수소 분자나, 물( $H_2O$ ) 등의 수소 원자를 포함한 화합물(보다 바람직하게는 탄소 원자를 포함한 화합물도) 등이 제거되어 있기 때문에, 해당 성막실에서 성막한 산화물 반도체막에 포함되는 불순물의 농도를 저감할 수 있다.

- [0178] 성막 조건의 일 예로서 기판과 타겟의 사이와의 거리를 100 mm, 압력을 0.6 Pa, 직류(DC) 전원을 0.5 kW, 성막 분위기를 산소(산소 유량 비율 100%) 분위기로 할 수가 있다. 또한 펄스 직류 전원을 이용하면, 성막시의 분말상 물질(파티클, 쓰레기라고도 한다)의 발생을 경감할 수 있고, 막두께의 편차도 작아지기 때문에 바람직하다.

- [0179] 산화물 반도체막의 가공은, 원하는 형상의 마스크를 산화물 반도체막상에 형성한 후, 해당 산화물 반도체막을 예칭함으로써 실시할 수가 있다. 상술한 마스크는, 포토리소그래피 등의 방법을 이용하여 형성할 수가 있다. 또는, 잉크젯법 등의 방법을 이용하여 마스크를 형성하여도 좋다.

- [0180] 또한, 산화물 반도체막의 예칭은, 건식 예칭이라도 습식 예칭이라도 좋다. 물론, 이들을 조합하여 이용하여도 괜찮다.

- [0181] 그 후, 산화물 반도체막(106)에 대하여 열처리를 실시하여, 고순도화된 산화물 반도체막(108)을 형성한다(도 4(E) 참조). 이 열처리에 의해 산화물 반도체막(106)중의, 수소(물이나 수산기를 포함한다)를 제거하고, 산화물 반도체막의 구조를 정돈하여 에너지캡중의 결함 준위를 저감할 수가 있다. 또한, 이 열처리에 의해, 절연막(102)중의 산소가 산화물 반도체막에 공급되는 일이 있다. 상기 열처리의 온도는, 250°C 이상 650°C 이하, 바람직하게는 450°C 이상 600°C 이하다. 또한 상기 열처리의 온도는, 기판의 왜곡점 미만으로 하는 것이 바람직하다.

- [0182] 열처리는, 예를 들면, 저항 발열체 등을 이용한 전기로에 피처리물을 도입하고, 질소 분위기하, 450°C, 1시간의 조건으로 실시할 수가 있다. 이 동안, 산화물 반도체막(106)은 대기에 접하지 않게 하여, 물이나 수소의 혼입이 생기지 않도록 한다.

- [0183] 열처리 장치는 전기로에 한정되지 않고, 가열된 가스 등의 매체로부터의 열전도, 또는 열복사에 의해, 피처리물을 가열하는 장치를 이용하여도 좋다. 예를 들면, LRTA(Lamp Rapid Thermal Anneal) 장치, GRTA(Gas Rapid Thermal Anneal) 장치 등의 RTA(Rapid Thermal Anneal) 장치를 이용할 수가 있다. LRTA 장치는, 할로겐 램프, 메탈할라이드 램프, 크세논 아크 램프, 카본 아크 램프, 고압 나트륨 램프, 고압 수은 램프 등의 램프로부터 발하는 광(전자파)의 복사에 의해, 피처리물을 가열하는 장치다. GRTA 장치는, 고온의 가스를 이용하여 열처리를 실시하는 장치다. 가스로서는, 아르곤 등의 희가스, 또는 질소와 같은, 열처리에 의해 피처리물과 반응하지 않는 불활성 기체가 이용된다.

- [0184] 예를 들면, 상기 열처리로서 가열된 불활성 가스 분위기중에 피처리물을 투입하고, 몇 분간 가열한 후, 해당 불활성 가스 분위기로부터 피처리물을 취출하는 GRTA 처리를 실시하여도 괜찮다. GRTA 처리를 이용하면 단시간에서의 고온 열처리가 가능해진다. 또한, 피처리물의 내열 온도를 넘는 온도 조건이라도 적용이 가능해진다. 또한 처리중에, 불활성 가스를, 산소를 포함한 가스로 전환하여도 좋다. 산소를 포함한 분위기에서 열처리를 실시함으로써, 산소 결손에 기인하는 에너지캡중의 결함 준위를 저감할 수가 있기 때문이다.

- [0185] 또한, 불활성 가스 분위기로서는, 질소, 또는 희가스(헬륨, 네온, 아르곤 등)를 주성분으로 하는 분위기이며, 물, 수소 등이 포함되지 않는 분위기를 적용하는 것이 바람직하다. 예를 들면, 열처리 장치에 도입하는 질소나, 헬륨, 네온, 아르곤 등의 희가스의 순도를, 6 N(99.9999%) 이상, 바람직하게는 7 N(99.99999%) 이상(즉, 불순물 농도가 1 ppm 이하, 바람직하게는 0.1 ppm 이하)로 한다.

- [0186] 어쨌든, 상기 열처리에 의해 불순물을 저감하여, i형(진성) 반도체 또는 i형에 극히 가까운 산화물 반도체막을 형성함으로써, 극히 뛰어난 특성의 트랜지스터를 실현할 수가 있다.

- [0187] 그런데, 상술한 열처리에는 수소나 물 등을 제거하는 효과가 있기 때문에, 해당 열처리를, 탈수화 처리나, 탈수소화 처리 등이라고 부를 수도 있다. 해당 탈수화 처리나, 탈수소화 처리는, 예를 들면, 산화물 반도체막을 섬형상으로 가공하기 전 등의 타이밍에서 실시하는 것도 가능하다. 또한, 이러한 탈수화 처리, 탈수소화 처리는, 1회에 한정하지 않고 여러 차례 실시하여도 좋다.

- [0188] 다음으로, 산화물 반도체막(108)에 대하여, 산소(180b)에 의한 처리를 실시한다(도 4(F) 참조). 산소(180b)에는, 적어도, 산소 라디칼, 산소 원자, 산소 이온중의 어느 것인가가 포함되어 있다. 산화물 반도체막(108)에 산소 도핑 처리를 실시함으로써, 산화물 반도체막(108)중, 산화물 반도체막(108) 계면 근방, 또는 산화물 반도체막(108)중 및 그 계면 근방에 산소를 함유시킬 수가 있다. 이 경우, 산소의 함유량은, 산화물 반도체막(108)의 화학량론비를 넘는 정도, 바람직하게는, 화학량론비의 1배를 넘어 2배까지(1배보다 크고 2배 미만)로 한다. 혹은, 산소의 함유량은, 단결정의 경우의 산소의 양을 Y로 하여, Y를 넘는 정도, 바람직하게는, Y를 넘어 2Y까지 할 수도 있다. 혹은, 산소의 함유량은, 산소 도핑 처리를 실시하지 않는 경우의 산화물 반도체막중의 산소의 양 Z를 기준으로 하여, Z를 넘는 정도, 바람직하게는, Z를 넘어 2Z까지로 할 수도 있다. 또한 상술한 바람직한 범위에 상한이 존재하는 것은, 산소의 함유량을 너무 많이 하면, 수소흡장합금(수소저장합금)과 같이, 오히려 산화물 반도체막(108)이 수소를 취입해 버릴 우려가 있기 때문이다.

- [0189] 결정 구조가  $InGaO_3(ZnO)_m$  ( $m>0$ )로 표현되는 재료의 경우, 예를 들면,  $M=1$ ( $InGaZnO_4$ )의 결정 구조를 기준으로 하면,  $InGaZnO_x$ 에 있어서  $x$ 는 4를 넘어 8까지, 또한  $m=2$ ( $InGaZn_2O_5$ )의 결정 구조를 기준으로 하면,  $InGaZn_2O_x$ 에 있어서  $x$ 는 5를 넘어 10까지가 허용된다. 또한 이러한 산소 과잉 영역은, 산화물 반도체막의 일부(계면을 포함한다)에 존재하고 있으면 좋다.

- [0190] 또한, 산화물 반도체막에 첨가되는 산소(180b)의 적어도 일부는, 산화물 반도체 중에서 미결합손을 갖는 것이 바람직하다. 미결합손을 가짐에 의해, 막중에 잔존할 수 있는 수소와 결합하여 수소를 고정화(비가동 이온화) 할 수가 있기 때문이다.

- [0191] 상술한 산소(180b)는, 플라즈마 발생 장치나 오존 발생 장치에 의해 발생시킬 수가 있다. 보다 구체적으로는, 예를 들면, 반도체 장치에 대하여 에칭 처리를 실시할 수가 있는 장치나, 레지스트 마스크에 대하여 애성을 실시할 수가 있는 장치 등을 이용하여 산소(180b)를 발생시켜, 산화물 반도체막(108)을 처리할 수가 있다.

- [0192] 또한, 산소의 첨가를 보다 매우 적합하게 실시하기 위해서는, 기판에는 전기적인 바이어스를 인가해 두는 것이 바람직하다.

- [0193] 또한, 산소 도핑 처리를 실시한 산화물 반도체막(108)에 열처리(온도 150°C~470°C)를 실시하여도 괜찮다. 해당 열처리에 의해, 산소 또는 산화물 반도체 재료가 수소와 반응함으로써 생성된 물, 수산화물 등을 산화물 반도체 막으로부터 제거할 수가 있다. 열처리는, 물, 수소 등이 충분히 저감된 질소, 산소, 초건조공기(수분량이 20 ppm 이하, 바람직하게는 1 ppm 이하, 바람직하게는 10 ppb 이하의 공기), 희가스(아르곤, 헬륨 등) 등의 분위기 하에서 실시하면 좋다. 또한, 산소 도핑 처리와 열처리를 반복하여 실시하여도 좋다. 해당 처리를 반복하여 실시함으로써, 트랜지스터의 신뢰성을 더욱 높일 수가 있다. 또한 반복의 회수는 적절히 설정할 수가 있다.

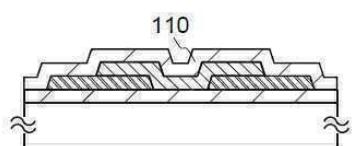

- [0194] 다음으로, 산화물 반도체막(108)의 일부와 접하고, 또한 소스 전극(104a) 및 드레인 전극(104b)을 덮는 게이트 절연막(110)을 형성한다(도 5(A) 참조).

- [0195] 게이트 절연막(110)은, 절연막(102)과 마찬가지로 형성할 수가 있다. 즉, 게이트 절연막(110)은, 산화 실리콘, 질화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화 갈륨, 이들의 혼합 재료 등을 이용하여 형성하면 좋다. 다만, 트랜지스터의 게이트 절연막으로서 기능하는 것을 고려하여, 산화 하프늄, 산화 탄탈륨, 산화 이트륨, 하프늄 실리케이트( $HfSi_{x,y}$  ( $x>0$ ,  $y>0$ )), 질소가 첨가된 하프늄 실리케이트( $HfSi_{x,y}$  ( $x>0$ ,  $y>0$ )), 질소가 첨가된 하프늄 알루미네이트( $HfAl_x O_y$  ( $x>0$ ,  $y>0$ )), 등의 비유전률이 높은 재료를 채용하여도 좋다.

- [0196] 또한, 절연막(102)과 마찬가지로, 적층 구조를 채용하여도 좋다. 이 경우에는, 산화물 반도체막과 동종의 성분으로 이루어지는 절연 재료로 이루어지는 막(이하, 막a)과, 막a의 성분 재료와는 다른 재료를 포함한 막(이하, 막b)의 적층 구조로 하면 더욱 좋다. 막a와 막b를 산화물 반도체막측으로부터 순서대로 적층한 구조로 함으로써, 전하는 막a와 막b의 계면의 전하 포획 중심에 우선적으로 포획되기(산화물 반도체막과 막a의 계면과의 비교) 때문에 산화물 반도체막의 계면에서의 전하 포획을 충분히 억제할 수가 있게 되어, 반도체 장치의 신뢰성이 향상하기 때문이다.

- [0197] 또한, 이러한 적층 구조로서는, 산화 갈륨막과 산화 실리콘막의 적층 구조나, 산화 갈륨막과 질화 실리콘막의 적층 구조 등을 적용할 수가 있다.

- [0198] 상술한 게이트 절연막(110)의 형성 후에는, 열처리를 실시하는 것이 바람직하다. 해당 열처리의 온도는, 250°C 이상 700°C 이하, 바람직하게는 450°C 이상 600°C 이하다. 또한 해당 열처리의 온도는, 기판의 왜곡점 미만으로 하는 것이 바람직하다.

- [0199] 상기 열처리는, 질소, 산소, 초건조공기(물의 함유량이 20 ppm 이하, 바람직하게는 1 ppm 이하, 바람직하게는 10 ppb 이하의 공기), 또는 희가스(아르곤, 헬륨 등)의 분위기하에서 실시하면 좋지만, 상기 질소, 산소, 초건조공기, 또는 희가스 등의 분위기에는, 물, 수소 등이 포함되지 않는 것이 바람직하다. 또한, 열처리 장치에 도입하는 질소, 산소, 또는 희가스의 순도는, 6 N(99.9999%) 이상(즉 불순물 농도를 1 ppm 이하)으로 하는 것이 바람직하고, 7 N(99.99999%) 이상(즉 불순물 농도를 0.1 ppm 이하)으로 하면, 보다 바람직하다.

- [0200] 본 실시형태와 관련되는 상기의 열처리에 있어서는, 산화물 반도체막(108)과 절연막(102)나 게이트 절연막(110)이 접한 상태로 가열된다. 따라서, 상술한 탈수화(또는 탈수소화) 처리에 의해 감소해 버릴 가능성이 있는 산소를, 절연막(102) 등으로부터 산화물 반도체막(108)으로 공급하는 것도 가능하다. 이런 의미에서, 해당 열처리를, 가산화(가산소화)라고 부를 수도 있다.

- [0201] 또한, 가산화를 목적으로 하는 열처리의 타이밍은, 산화물 반도체막(108)의 형성 후라면 특별히 한정되지 않는다. 예를 들면, 게이트 전극의 형성 후에 가산화를 목적으로 하는 열처리를 실시하여도 좋다. 또는, 탈수화 등을 목적으로 하는 열처리에 이어서 가산화를 목적으로 하는 열처리를 실시하여도 좋고, 탈수화 등을 목적으로 하는 열처리에 가산화를 목적으로 하는 열처리를 겸하게 하여도 좋고, 가산화를 목적으로 하는 열처리에 탈수화 등을 목적으로 하는 열처리를 겸하게 하여도 좋다.

- [0202] 상술한 바와 같이, 탈수화 등을 목적으로 하는 열처리와 산소 도핑 처리 또는 가산화를 목적으로 하는 열처리를 적용함으로써, 산화물 반도체막(108)을, 불순물이 최대한 포함되지 않게 고순도화할 수가 있다. 고순도화된 산화물 반도체막(108)중에는 도너에 유래하는 캐리어가 극히 적다(제로에 가깝다).

- [0203] 다음으로, 게이트 절연막(110)에 대하여, 산소(180c)에 의한 처리를 실시한다(도 5(B) 참조). 산소(180c)에는, 적어도, 산소 라디칼, 산소 원자, 산소 이온중의 어느 것인가가 포함되어 있다. 게이트 절연막(110)에 산소 도핑 처리를 실시함으로써, 게이트 절연막(110)중, 산화물 반도체막(108)중, 산화물 반도체막(108) 계면 근방, 또는 산화물 반도체막(108)중 및 그 계면 근방에 산소를 함유시킬 수가 있다. 이 경우, 게이트 절연막(110)중의 산소의 함유량은, 게이트 절연막(110)의 화학량론비를 넘는 정도, 바람직하게는, 화학량론비의 1배를 넘어 4배 까지(1배보다 크고 4배 미만), 보다 바람직하게는, 1배를 넘어 2배까지(1배보다 크고 2배 미만)로 한다. 혹은, 산소의 함유량은, 단결정의 경우의 산소의 양을 Y로 하여, Y를 넘는 정도, 바람직하게는, Y를 넘어 4Y까지 할 수도 있다. 혹은, 산소의 함유량은, 산소 도핑 처리를 실시하지 않는 경우의 게이트 절연막중의 산소의 양 Z를 기준으로 하여, Z를 넘는 정도, 바람직하게는, Z를 넘어 4Z까지로 할 수도 있다.

- [0204] 예를 들면, 조성이  $GaO_x$  ( $x>0$ )로 표현되는 산화 갈륨을 이용하는 경우, 단결정의 산화 갈륨은  $Ga_2O_3$ 이므로, x는 1.5를 넘어 6까지(즉 Ga의 1.5배를 넘어 6배까지)가 허용된다. 또한, 예를 들면, 조성이  $SiO_x$  ( $x>0$ )로 표현되는 산화 실리콘을 이용하는 경우,  $SiO_2$ (즉 0가 Si의 2배)이면, x는 2를 넘어 8까지(즉 Si의 2배를 넘어 8배까지)가 허용된다. 또한 이러한 산소 파잉 영역은, 절연막의 일부(계면을 포함한다)에 존재하고 있으면 좋다.

- [0205] 또한, 절연막에 첨가되는 산소(180c)의 적어도 일부는, 산화물 반도체에 공급된 후, 산화물 반도체 중에서 미결합손을 갖는 것이 바람직하다. 미결합손을 가짐에 의해, 막중에 잔존할 수 있는 수소와 결합하여 수소를 고정화(비가동 이온화)할 수가 있기 때문이다.

- [0206] 상술한 산소(180c)는, 플라즈마 발생 장치나 오존 발생 장치에 의해 발생시킬 수가 있다. 보다 구체적으로는, 예를 들면, 반도체 장치에 대하여 애칭 처리를 실시할 수가 있는 장치나, 레지스트 마스크에 대하여 애싱을 실시할 수가 있는 장치 등을 이용하여 산소(180c)를 발생시켜, 게이트 절연막(110)을 처리할 수가 있다.

- [0207] 또한, 산소의 첨가를 보다 매우 적합하게 실시하기 위해서는, 기관에는 전기적인 바이어스를 인가해 두는 것이 바람직하다.

- [0208] 또한, 상술한 산소 도핑 처리의 뒤에는, 열처리를 실시하여도 좋다. 이 열처리에 의해, 충분한 양의 산소를 산화물 반도체막에 공급하는 것이 가능하다. 해당 효과를 얻기 위한 열처리의 타이밍은, 상술한 산소 도핑 처리 후라면 언제라도 상관없다. 또한, 산소 도핑 처리와 열처리를 반복하여 실시하여도 좋다. 해당 처리를 반복하여 실시함으로써, 트랜지스터의 신뢰성을 더욱 높일 수가 있다. 또한 반복의 회수는 적절히 설정할 수가 있다.

- [0209] 그 후, 게이트 전극(112)을 형성한다(도 5(C) 참조). 게이트 전극(112)은, 몰리브덴, 티탄, 탄탈륨, 텅스텐, 알루미늄, 동, 네오디뮴, 스칸듐 등의 금속재료 또는 이들을 주성분으로 하는 합금 재료를 이용하여 형성할 수가 있다. 또한 게이트 전극(112)은, 단층 구조로 하여도 좋고, 적층 구조로 하여도 좋다.

- [0210] 또한, 게이트 전극(112)의 형성 후에는, 절연막을 형성하여도 좋다. 해당 절연막은, 예를 들면, 산화 실리콘, 질화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화 갈륨, 이들의 혼합 재료 등을 이용하여 형성할 수가 있다. 특히, 절연막으로서 질화 실리콘막을 이용하는 경우에는, 첨가된 산소의 외부로의 방출을 막을 수가 있음과 동시에, 산화물 반도체막(108)으로의 외부로부터의 수소 등의 혼입을 효과적으로 억제할 수가 있기 때문에 매우 적합하다. 또한, 소스 전극(104a)이나 드레인 전극(104b), 게이트 전극(112) 등과 접속되는 배선을 형성하여도 좋다.

- [0211] 이상의 공정으로 트랜지스터(120)가 형성된다.

- [0212] 또한, 상술한 설명은, 절연막(102), 산화물 반도체막(108), 및 게이트 절연막(110)의 모두에 산소 도핑 처리를

적용하는 예에 대한 것이지만, 개시하는 발명의 일 태양은 이에 한정되지 않는다. 예를 들면, 절연막(102) 및 산화물 반도체막(108)에 산소 도핑 처리를 적용하여도 좋고, 산화물 반도체막(108) 및 게이트 절연막(110)에 산소 도핑 처리를 적용하여도 좋다.

[0213] 본 실시형태와 관련되는 트랜지스터는, 열처리에 의해, 수소, 물, 수산기 또는 수소화물(수소화합물이라고도 한다) 등의 수소 원자를 포함한 불순물을 산화물 반도체로부터 배제하고, 또한 불순물의 배제 공정에서 감소할 우려가 있는 산소를 공급함으로써, 고순도화 및 i형(진성)화를 위한 산화물 반도체막을 이용하고 있다. 이와 같이 고순도화된 산화물 반도체막을 포함한 트랜지스터는, 스레숄드 전압 등의 전기적 특성 변동이 억제되어 있어 전기적으로 안정하다.

[0214] 특히, 산소 도핑 처리에 의해 산화물 반도체막중의 산소의 함유량을 증대시킴으로써, 전기적 바이어스 스트레스나 열스트레스에 기인하는 열화를 억제하여, 광에 의한 열화를 저감할 수가 있다.

[0215] 이와 같이, 개시하는 발명의 일 태양에 의해, 신뢰성이 뛰어난 트랜지스터를 제공하는 것이 가능하다.

[0216] 이상, 본 실시형태에 나타내는 구성, 방법 등은, 다른 실시형태에 나타내는 구성, 방법 등과 적절히 조합하여 이용할 수가 있다.

[0217] (실시형태 3)

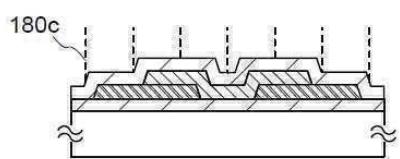

[0218] 본 실시형태에서는, 반도체 장치의 제작 방법의 다른 예에 대하여, 도 6을 이용하여 설명한다.

[0219] <반도체 장치의 구성예>

[0220] 본 실시형태의 제작 방법으로 제작되는 반도체 장치의 구성은, 앞의 실시형태의 트랜지스터(120)와 같다. 즉, 기판(100)상의 절연막(102), 소스 전극(104a), 드레인 전극(104b), 산화물 반도체막(108), 게이트 절연막(110), 게이트 전극(112)을 포함한다(도 1 참조).

[0221] 앞의 실시형태에서도 설명한 것처럼, 트랜지스터(120)에 있어서, 산화물 반도체막(108)은, 산소 도핑 처리를 한 산화물 반도체막이다. 또한, 본 실시형태에서는, 절연막(102) 및 게이트 절연막(110)에 대해서도 산소 도핑 처리를 하고 있다. 이러한 산소 도핑 처리에 의해, 더욱 신뢰성이 높아진 트랜지스터(120)가 실현된다. 게다가 본 실시형태에 있어서의 절연막(102)에 대한 산소 도핑 처리는, 소스 전극(104a) 및 드레인 전극(104b)의 형성에 이용하는 마스크(103a) 및 마스크(103b)의 제거의 공정을 겸하고 있다. 이러한 프로세스를 채용함으로써, 공정의 간략화에 의한 제조비용의 저감을 꾀할 수가 있다. 또한 앞의 실시형태와 마찬가지로, 구성을 변경한 트랜지스터를 제작할 수도 있다(도 3(A) 내지 도 3(D) 참조).

[0222] <반도체 장치의 제작 공정예>

[0223] 이하, 도 6을 이용하여, 상술한 반도체 장치의 제작 공정의 일 예를 설명한다. 또한 제작 공정의 기본적인 내용은 앞의 실시형태와 같기 때문에, 이하에서는 차이점에 대하여 설명하기만 한다.

[0224] 우선, 기판(100)상에 절연막(102)을 형성한다(도 6(A) 참조). 자세한 것은, 도 4(A)에 관한 기재를 참조하면 좋다.

[0225] 그 다음으로, 절연막(102)상에, 소스 전극 및 드레인 전극(이와 동일한 층에서 형성되는 배선을 포함한다)을 형성하기 위한 도전막을 형성하고, 해당 도전막을, 마스크(103a) 및 마스크(103b)를 이용하여 가공하여, 소스 전극(104a) 및 드레인 전극(104b)을 형성한다. 그리고, 절연막(102)에 대하여, 산소(180a)에 의한 처리(산소 도핑 처리나, 산소 플라즈마 도핑 처리라고도 한다)를 실시한다(도 6(B) 참조). 소스 전극(104a) 및 드레인 전극(104b)을 형성하기 위한 공정의 자세한 것은, 도 4(C)에 관한 기재를 참조하면 좋다. 여기서, 상술한 산소 도핑 처리는, 마스크(103a) 및 마스크(103b)의 제거 공정을 겸하는 것이다.

[0226] 산소(180a)에는, 적어도, 산소 라디칼, 산소 원자, 산소 이온중의 어느 것인가가 포함되어 있다. 절연막(102)에 산소 도핑 처리를 실시함으로써, 절연막(102)중에 산소를 함유시킬 수가 있어 후에 형성되는 산화물 반도체막(108)중, 산화물 반도체막(108) 계면 균방, 또는 산화물 반도체막(108)중 및 그 계면 균방에 산소를 함유시킬 수가 있다. 이 경우, 산소의 함유량은, 절연막(102)의 화학량론비를 넘는 정도, 바람직하게는, 화학량론비의 1배를 넘어 4배까지(1배보다 크고 4배 미만), 보다 바람직하게는, 1배를 넘어 2배까지(1배보다 크고 2배 미만)로 한다. 혹은, 산소의 함유량은, 단결정의 경우의 산소의 양을 Y로 하여, Y를 넘는 정도, 바람직하게는, Y를 넘어 4Y까지 할 수도 있다. 혹은, 산소의 함유량은, 산소 도핑 처리를 실시하지 않는 경우의 절연막중의 산소의 양 Z를 기준으로 하여, Z를 넘는 정도, 바람직하게는, Z를 넘어 4Z까지로 할 수도 있다.

- [0227] 예를 들면, 조성이  $GaO_x$  ( $x>0$ )로 표현되는 산화 갈륨을 이용하는 경우, 단결정의 산화 갈륨은  $Ga_2O_3$ 이므로,  $x$ 는 1.5를 넘어 6까지(즉 Ga의 1.5배를 넘어 6배까지)가 허용된다. 또한, 예를 들면, 조성이  $SiO_x$  ( $x>0$ )로 표현되는 산화 실리콘을 이용하는 경우,  $SiO_2$ (즉 O가 Si의 2배)이면,  $x$ 는 2를 넘어 8까지(즉 Si의 2배를 넘어 8배까지)가 허용된다. 또한 이러한 산소 과잉 영역은, 절연막의 일부(계면을 포함한다)에 존재하고 있으면 좋다.

- [0228] 또한, 절연막에 첨가되는 산소(180a)의 적어도 일부는, 산화물 반도체에 공급된 후, 산화물 반도체 중에서 미결합손을 갖는 것이 바람직하다. 미결합손을 가짐에 의해, 막중에 잔존할 수 있는 수소와 결합하여 수소를 고정화(비가동 이온화)할 수가 있기 때문이다.

- [0229] 상술한 산소(180a)는, 플라즈마 발생 장치나 오존 발생 장치에 의해 발생시킬 수가 있다. 보다 구체적으로는, 예를 들면, 레지스트 마스크에 대하여 애싱을 실시할 수가 있는 장치 등을 이용하여 산소(180a)를 발생시켜, 절연막(102)을 처리할 수가 있다.

- [0230] 해당 산소 도핑 처리에 의해 마스크(103a) 및 마스크(103b)가 제거된다. 다만, 통상의 마스크 제거 공정과는 달리, 해당 공정은 산소의 첨가를 목적으로 하는 것이기 때문에, 기판에는 강한 바이어스를 인가해 두는 것이 바람직하다.

- [0231] 또한, 해당 산소 도핑 처리에 의해, 절연막(102)중에는, 산소가 고농도로 존재하는 영역과 산소가 저농도로 존재하는 영역이 형성된다. 구체적으로는, 절연막(102)의, 소스 전극(104a) 및 드레인 전극(104b)에 덮이지 않은 영역이, 산소가 고농도로 존재하는 영역이 되고, 소스 전극(104a) 및 드레인 전극(104b)에 덮여 있는 영역이, 산소가 저농도로 존재하는 영역이 된다.

- [0232] 다음으로, 절연막(102)상에, 소스 전극(104a) 및 드레인 전극(104b)과 접하는 산화물 반도체막을 형성하고, 해당 산화물 반도체막을 가공하여 섬 형상의 산화물 반도체막을 형성한다. 그리고, 그 후, 섬 형상의 산화물 반도체막에 있어서 열처리를 실시하여, 고순도화된 산화물 반도체막(108)을 형성한다(도 6(C) 참조). 해당 공정의 자세한 것은, 도 4(D) 및 도 4(E)에 관한 기재를 참조하면 좋다.

- [0233] 다음으로, 산화물 반도체막(108)에 대하여, 산소(180b)에 의한 처리를 실시한다(도 6(D) 참조). 자세한 것은, 도 4(F)에 관한 기재를 참조하면 좋다.

- [0234] 다음으로, 산화물 반도체막(108)의 일부와 접하고, 또한 소스 전극(104a) 및 드레인 전극(104b)을 덮는 게이트 절연막(110)을 형성한다. 그리고, 그 후, 게이트 절연막(110)에 대하여, 산소(180c)에 의한 처리를 실시한다(도 6(E) 참조). 자세한 것은, 도 5(A) 및 도 5(B)에 관한 기재를 참조하면 좋다.

- [0235] 그 후, 게이트 전극(112)을 형성한다(도 6(F) 참조). 자세한 것은, 도 5(C)에 관한 기재를 참조하면 좋다.

- [0236] 또한, 게이트 전극(112)의 형성 후에는, 절연막을 형성하여도 좋다. 해당 절연막은, 예를 들면, 산화 실리콘, 질화 실리콘, 산화 알루미늄, 질화 알루미늄, 산화 갈륨, 이들의 혼합 재료 등을 이용하여 형성할 수가 있다. 특히, 절연막으로서 질화 실리콘막을 이용하는 경우에는, 첨가된 산소의 외부로의 방출을 막을 수가 있음과 동시에, 산화물 반도체막(108)으로의 외부로부터의 수소 등의 혼입을 효과적으로 억제할 수가 있기 때문에 매우 적합하다. 또한, 소스 전극(104a)이나 드레인 전극(104b), 게이트 전극(112) 등과 접속되는 배선을 형성하여도 좋다.

- [0237] 이상의 공정으로 트랜지스터(120)가 형성된다.

- [0238] 또한, 상술한 설명은, 절연막(102), 산화물 반도체막(108), 및 게이트 절연막(110)의 모두에 산소 도핑 처리를 적용하는 예에 대한 것이지만, 개시하는 발명의 일 태양은 이에 한정되지 않는다. 예를 들면, 절연막(102) 및 산화물 반도체막(108)에 산소 도핑 처리를 적용하여도 좋다.

- [0239] 본 실시형태와 관련되는 트랜지스터는, 열처리에 의해, 수소, 물, 수산기 또는 수소화물(수소화합물이라고도 한다) 등의 수소 원자를 포함한 불순물을 산화물 반도체로부터 배제하고, 또한 불순물의 배제 공정에서 감소할 우려가 있는 산소를 공급함으로써, 고순도화 및 i형(진성)화를 꾀한 산화물 반도체막을 이용하고 있다. 이와 같이 고순도화된 산화물 반도체막을 포함한 트랜지스터는, 스레숄드 전압 등의 전기적 특성 변동이 억제되어 있어 전기적으로 안정하다.

- [0240] 특히, 산소 도핑 처리에 의해 산화물 반도체막 중의 산소의 함유량을 증대시킴으로써, 전기적 바이어스 스트레

스나 열스트레스에 기인하는 열화를 억제하여, 광에 의한 열화를 저감할 수가 있다.

[0241] 게다가 본 실시형태와 관련되는 제작 방법에서는, 공정이 간략화되고 있기 때문에 제조와 관련되는 비용을 억제 할 수가 있다.

[0242] 이와 같이, 개시하는 발명의 일 태양에 의해, 제조비용을 낮게 억제하면서, 신뢰성이 뛰어난 트랜지스터를 제공하는 것이 가능하다.

[0243] 이상, 본 실시형태에 나타내는 구성, 방법 등은, 다른 실시형태에 나타내는 구성, 방법 등과 적절히 조합하여 이용할 수가 있다.

[0244] (실시형태 4)

[0245] 본 실시형태에서는, 산소 도핑 처리에 이용할 수가 있는 플라즈마 장치(애성 장치라고도 부른다)의 예를 설명한다. 또한 이 장치는, 예를 들면, 제 5세대 이후의 대형의 유리 기판 등에 대응할 수가 있는 점에서, 이온 주입 장치 등보다 공업적으로 적합하다.

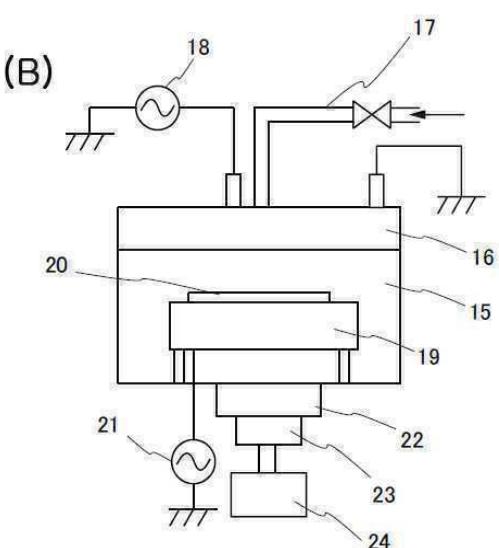

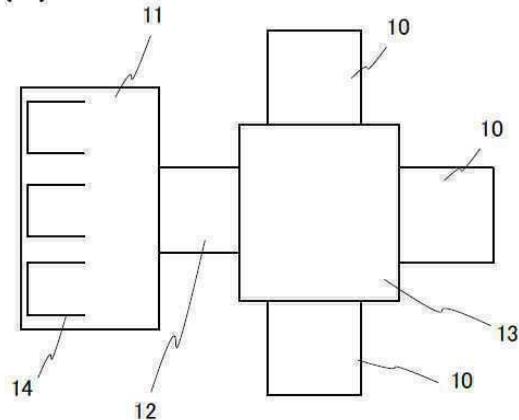

[0246] 도 17(A)은, 단일 웨이퍼 멀티챔버 설비의 표면도의 일 예를 나타낸다. 도 17(B)은, 산소 플라즈마 도핑을 실시하는 플라즈마 장치(애성 장치라고도 부른다)의 단면도의 일 예를 나타낸다.

[0247] 도 17(A)에 나타내는 단일 웨이퍼 멀티챔버 설비는, 도 17(B)에 나타내는 플라즈마 장치(10)를 3개 가지며, 피처리 기판을 수용하는 카셋트 포트(14)를 3개 갖는 기판 공급실(11)이나, 로드 록크실(load lock chamber)(12)이나, 반송실(13) 등을 갖고 있다. 기판 공급실에 공급된 기판은, 로드 록크실(12)과 반송실(13)을 통하여 플라즈마 장치(10)내의 진공 챔버(15)에 반송되어 산소 플라즈마 도핑이 실시된다. 산소 플라즈마 도핑이 종료된 기판은, 플라즈마 장치(10)로부터 로드 록크실(12)과 반송실(13)을 통하여 기판 공급실(11)에 반송된다. 또한 기판 공급실(11) 및 반송실(13)에는, 피처리 기판을 반송하기 위한 반송 로보트가 각각 배치되어 있다.

[0248] 도 17(B)을 참조하면, 플라즈마 장치(10)는, 진공 챔버(15)를 구비하고 있다. 진공 챔버(15)의 상부에는, 복수의 가스 송풍구와 플라즈마 발생원인 ICP 코일(16)(유도 결합 플라즈마 코일)이 배치되어 있다.

[0249] 가스 송풍구는, 플라즈마 장치(10)의 표면으로부터 보아서 중앙 부분에 12개 배치되어 있다. 각각의 가스 송풍구는, 산소 가스를 공급하기 위한 가스 공급원과 가스 유로(17)를 통하여 접속되어 있으며, 가스 공급원은, 매스 플로우 콘트롤러 등을 구비하여, 원하는 유량(0보다 많고 1000 sccm 이하)으로 가스 유로(17)에 대하여 산소 가스를 공급할 수가 있다. 가스 공급원으로부터 공급되는 산소 가스는, 가스 유로(17)로부터 12개의 가스 송풍구를 통하여 진공 챔버(15)내에 공급된다.

[0250] ICP 코일(16)은, 복수개의 띠형상의 도체를 나선 형상으로 배치하여 이루어진다. 각 도체의 일단은, 임피던스 조정을 위한 매칭 회로를 통하여 제 1 고주파 전원(18)(13.56 MHz)에 전기적으로 접속되고, 타단은 접지되어 있다.

[0251] 진공 챔버의 하부에는, 하부 전극으로서 기능하는 기판 스테이지(19)가 배치되어 있다. 기판 스테이지(19)에 마련된 정전 척(electrostatic chuck) 등에 의해, 기판 스테이지 상에 피처리 기판(20)이 착탈 가능하게 유지된다. 기판 스테이지(19)에는, 가열 기구로서 히터, 냉각 기구로서 He가스 유로를 구비하고 있다. 기판 스테이지는, 기판 바이어스 전압 인가용의 제 2 고주파 전원(21)(3.2 MHz)에 접속되어 있다.

[0252] 또한, 진공 챔버(15)에는 배기구가 마련되며, 자동 압력 제어 밸브(22)(Automatic Pressure Control valve, APC라고도 부른다)가 구비되어 있다. APC는 터보 분자 펌프(23)에 접속되며, 게다가 터보 분자 펌프(23)를 통하여 드라이 펌프(24)에 접속된다. APC는 진공 챔버내의 압력 제어를 실시하며, 터보 분자 펌프(23) 및 드라이 펌프(24)는 진공 챔버(15)내를 감압한다.

[0253] 다음으로, 도 17(B)에 나타내는 진공 챔버(15)내에 플라즈마를 발생시켜, 피처리 기판(20)에 마련되어 있는 산화물 반도체막, 기초 절연막 또는 게이트 절연막에 산소 플라즈마 도핑을 실시하는 일 예를 나타낸다.

[0254] 우선, 터보 분자 펌프(23) 및 드라이 펌프(24) 등을 작동시켜, 진공 챔버(15)내를 원하는 압력으로 유지한 후, 피처리 기판(20)을 진공 챔버(15)내의 기판 스테이지에 설치한다. 또한 기판 스테이지에 유지하는 피처리 기판(20)에는 적어도 산화물 반도체막 또는 기초 절연막을 구비하는 것으로 한다. 본 실시형태에서는, 진공 챔버(15)내의 압력을 1.33 Pa로 유지한다. 또한 산소 가스를 가스 송풍구로부터 진공 챔버(15)내에 공급하는 유량을 250 sccm으로 설정한다.

- [0255] 그 다음으로, 제 1 고주파 전원(18)으로부터 ICP 코일(16)에 고주파 전력을 인가하여, 플라즈마를 발생시킨다. 그리고, 플라즈마를 발생시킨 상태를 일정시간(30초 이상 600초 이하) 유지한다. 또한 ICP 코일(16)에 인가하는 고주파 전력은, 1 kW 이상 10 kW 이하로 한다. 본 실시형태에서는, 6000 W로 한다. 이때, 제 2 고주파 전원(21)으로부터 기판 스테이지에 기판 바이어스 전압을 인가하여도 괜찮다. 본 실시형태에서는 기판 바이어스 전압 인가에 이용하는 전력을 1000 W로 한다.

- [0256] 본 실시형태에서는, 플라즈마를 발생시킨 상태를 60초 유지한 후, 피처리 기판(20)을 진공 챔버(15)로부터 반출 한다. 이렇게 하여, 피처리 기판(20)에 마련되어 있는 산화물 반도체막, 기초 절연막 또는 게이트 절연막에 산소 플라즈마 도핑을 실시할 수가 있다.

- [0257] 이상, 본 실시형태에 나타내는 구성, 방법 등은, 다른 실시형태에 나타내는 구성, 방법 등과 적절히 조합하여 이용할 수가 있다.

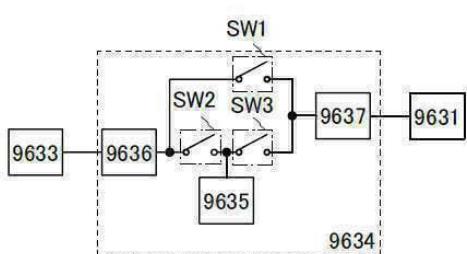

- [0258] (실시형태 5)

- [0259] 본 실시형태에서는, 반도체 장치의 일 예로서 기억 매체(메모리 소자)를 나타낸다. 본 실시형태에서는, 실시형태 1 내지 실시형태 3 등에서 나타내는 산화물 반도체를 이용한 트랜지스터와, 산화물 반도체 이외의 재료를 이용한 트랜지스터를 동일 기판상에 형성한다.

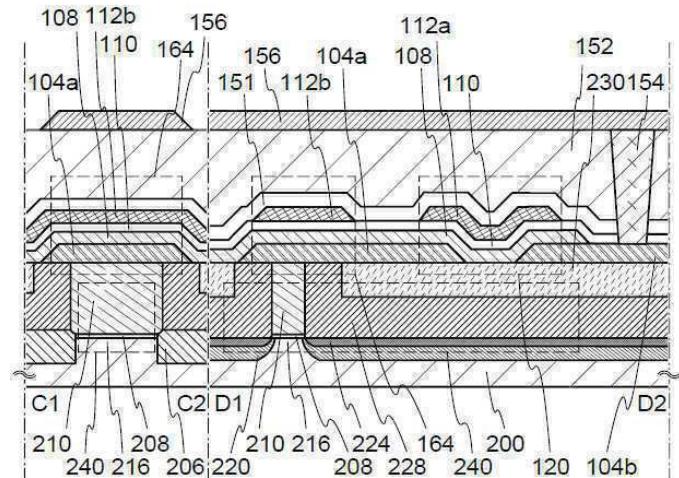

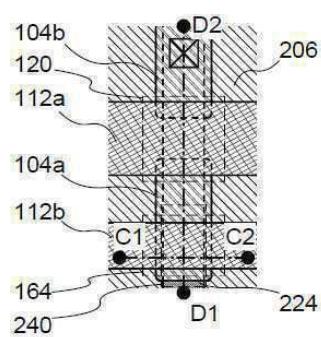

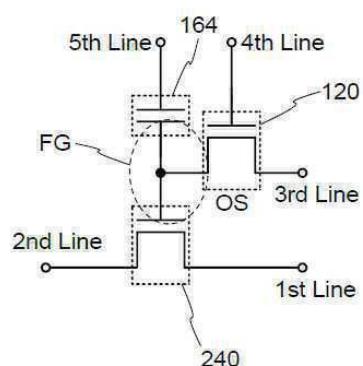

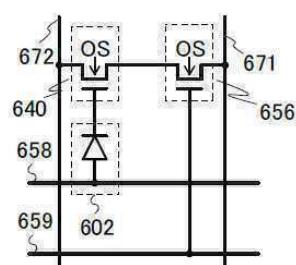

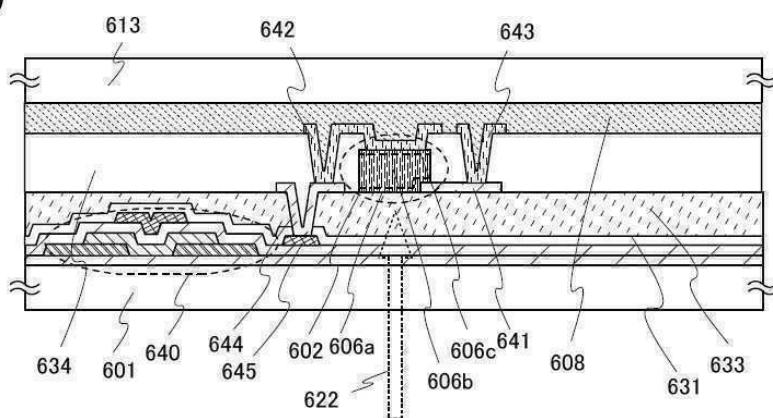

- [0260] 도 7은, 반도체 장치의 구성의 일 예이다. 도 7(A)에는, 반도체 장치의 단면을, 도 7(B)에는, 반도체 장치의 평면을 각각 나타낸다. 여기서, 도 7(A)은, 도 7(B)의 C1-C2 및 D1-D2에 있어서의 단면에 상당한다. 또한, 도 7(C)에는, 상기 반도체 장치를 메모리 소자로서 이용하는 경우의 회로도의 일 예를 나타낸다. 도 7(A) 및 도 7(B)에 나타나는 반도체 장치는, 하부에 제 1 반도체 재료를 이용한 트랜지스터(240)를 가지며, 상부에 실시형태 1에서 나타낸 트랜지스터(120)를 갖는다. 또한 트랜지스터(120)는, 제 2 반도체 재료로서 산화물 반도체를 이용하고 있다. 본 실시형태에서는, 제 1 반도체 재료를 산화물 반도체 이외의 반도체 재료로 한다. 산화물 반도체 이외의 반도체 재료로서는, 예를 들면, 실리콘, 게르마늄, 실리콘 게르마늄, 탄화 실리콘, 또는 갈륨 비소 등을 이용할 수가 있으며, 단결정 반도체를 이용하는 것이 바람직하다. 그 밖에, 유기 반도체 재료 등을 이용하여도 괜찮다. 이러한 반도체 재료를 이용한 트랜지스터는, 고속 동작이 용이하다. 한편, 산화물 반도체를 이용한 트랜지스터는, 그 특성에 의해 장시간의 전하 유지를 가능하게 한다.

- [0261] 또한, 본 실시형태에 있어서는, 트랜지스터(120)를 이용하여 기억 매체를 구성하는 예를 나타내지만, 트랜지스터(120)에 대신하여, 실시형태 1 또는 실시형태 2에서 나타낸 트랜지스터(130), 트랜지스터(140), 트랜지스터(150) 및 트랜지스터(160) 등을 적용 가능하다는 것은 말할 필요도 없다.

- [0262] 도 7에 있어서의 트랜지스터(240)는, 반도체 재료(예를 들면, 실리콘 등)를 포함한 기판(200)에 마련된 채널 형성 영역(216)과, 채널 형성 영역(216)을 사이에 두도록 마련된 불순물 영역(220)과, 불순물 영역(220)에 접하는 금속 화합물 영역(224)과, 채널 형성 영역(216)상에 마련된 게이트 절연막(208)과, 게이트 절연막(208)상에 마련된 게이트 전극(210)을 갖는다.

- [0263] 반도체 재료를 포함한 기판(200)은, 실리콘이나 탄화 실리콘 등의 단결정 반도체 기판, 다결정 반도체 기판, 실리콘 게르마늄 등의 화합물 반도체 기판, SOI 기판 등을 적용할 수가 있다. 또한 일반적으로 「SOI 기판」은, 절연 표면상에 실리콘 반도체막이 마련된 구성의 기판을 말하지만, 본 명세서 등에 있어서는, 절연 표면상에 실리콘 이외의 재료로 이루어지는 반도체막이 마련된 구성의 기판도 포함한다. 즉, 「SOI 기판」이 갖는 반도체 막은, 실리콘 반도체막에 한정되지 않는다. 또한, SOI 기판에는, 유리 기판 등의 절연 기판상에 절연막을 통하여 반도체막이 마련된 구성의 것이 포함되는 것으로 한다.

- [0264] 기판(200)상에는 트랜지스터(240)를 둘러싸도록 소자분리 절연막(206)이 마련되어 있고, 트랜지스터(240)를 덮도록 절연막(228) 및 절연막(230)이 마련되어 있다. 또한 고집적화를 실현하기 위해서는, 도 7(A)에 나타내는 바와 같이 트랜지스터(240)가 사이드월 절연막을 갖지 않는 구성으로 하는 것이 바람직하다. 한편, 트랜지스터(240)의 특성을 중시하는 경우에는, 게이트 전극(210)의 측면에 사이드월 절연막을 마련하여, 불순물 농도가 다른 영역을 포함한 불순물 영역(220)을 마련하여도 좋다.

- [0265] 트랜지스터(240)는 실리콘, 게르마늄, 실리콘 게르마늄, 탄화 실리콘, 또는 갈륨 비소 등을 이용하여 제작할 수가 있다. 이러한 트랜지스터(240)는, 고속 동작이 가능하다고 하는 특징을 갖는다. 이 때문에, 해당 트랜지스터를 읽기용의 트랜지스터로서 이용함으로써, 정보의 읽기를 고속으로 실시할 수가 있다.

- [0266] 트랜지스터(240)를 형성한 후, 트랜지스터(120) 및 용량 소자(164)의 형성전의 처리로서 절연막(228)이나 절연

막(230)에 CMP 처리를 실시하여, 게이트 전극(210)의 표면을 노출시킨다. 게이트 전극(210)의 표면을 노출시키는 처리로서는, CMP 처리 외에 에칭 처리 등을 적용하는 것도 가능하지만, 트랜지스터(120)의 특성을 향상시키기 위해서, 절연막(228)이나 절연막(230)의 표면은 가능한 한 평坦하게 해 두는 것이 바람직하다.

[0267] 다음으로, 게이트 전극(210), 절연막(228), 절연막(230) 등의 위에 도전막을 형성하고, 그 도전막을 선택적으로 에칭하여, 소스 전극(104a), 드레인 전극(104b)을 형성한다.

[0268] 도전막은, 스팍터법을 비롯한 PVD법이나, 플라즈마 CVD법 등의 CVD법을 이용하여 형성할 수가 있다. 또한, 도전막의 재료로서는, Al, Cr, Cu, Ta, Ti, Mo, W으로부터 선택된 원소나, 상술한 원소를 성분으로 하는 합금 등을 이용할 수가 있다. Mn, Mg, Zr, Be, Nd, Sc중의 어느 것, 또는 이들을 복수 조합한 재료를 이용하여도 괜찮다.

[0269] 도전막은, 단층 구조라도 좋고, 2층 이상의 적층 구조로 하여도 좋다. 예를 들면, 티탄막이나 질화 티탄막의 단층 구조, 실리콘을 포함한 알루미늄막의 단층 구조, 알루미늄막상에 티탄막이 적층된 2층 구조, 질화 티탄막상에 티탄막이 적층된 2층 구조, 티탄막과 알루미늄막과 티탄막이 적층된 3층 구조 등을 들 수 있다. 또한 도전막을, 티탄막이나 질화 티탄막의 단층 구조로 하는 경우에는, 테이퍼 형상을 갖는 소스 전극(104a), 및 드레인 전극(104b)으로의 가공이 용이하다라는 메리트가 있다.

[0270] 상부의 트랜지스터(120)의 채널 길이(L)는, 소스 전극(104a), 및 드레인 전극(104b)의 하단부의 간격에 의해 결정된다. 또한 채널장(L)이 25 nm 미만인 트랜지스터를 형성하는 경우에 이용하는 마스크 형성의 노광을 실시할 때에는, 수 nm~수 10 nm와 파장의 짧은 초자외선을 이용하는 것이 바람직하다.

[0271] 다음으로, 소스 전극(104a), 및 드레인 전극(104b)을 덮도록 산화물 반도체막을 형성한 후, 해당 산화물 반도체막을 선택적으로 에칭하여 산화물 반도체막(108)을 형성한다. 산화물 반도체막은, 실시형태 1에 나타내는 재료 및 형성 프로세스를 이용한다.

[0272] 다음으로, 산화물 반도체막(108)에 접하는 게이트 절연막(110)을 형성한다. 게이트 절연막(110)은, 실시형태 1에 나타내는 재료 및 형성 프로세스를 이용한다.

[0273] 다음으로, 게이트 절연막(110)상에 있어서 산화물 반도체막(108)과 중첩하는 영역에 게이트 전극(112a)을 형성하고, 소스 전극(104a)과 중첩하는 영역에 전극(112b)을 형성한다.

[0274] 게이트 절연막(110)의 형성 후에는, 불활성 가스 분위기하, 또는 산소 분위기하에서 열처리(가산화 등이라고도 부른다)를 실시하는 것이 바람직하다. 열처리의 온도는, 200°C 이상 450°C 이하, 바람직하게는 250°C 이상 350°C 이하다. 예를 들면, 질소 분위기하에서 250°C, 1시간의 열처리를 실시하면 좋다. 열처리를 실시함에 의해, 트랜지스터의 전기적 특성의 편차를 경감할 수가 있다.

[0275] 또한, 가산화를 목적으로 하는 열처리의 타이밍은 이에 한정되지 않는다. 예를 들면, 게이트 전극의 형성 후에 가산화를 목적으로 하는 열처리를 실시하여도 좋다. 또한, 탈수화 등을 목적으로 하는 열처리에 이어서 가산화를 목적으로 하는 열처리를 실시하여도 좋고, 탈수화 등을 목적으로 하는 열처리에 가산화를 목적으로 하는 열처리를 겹하게 하여도 좋다.

[0276] 상술한 바와 같이, 탈수화 등을 목적으로 하는 열처리와 산소 도핑 처리 또는 가산화를 목적으로 하는 열처리를 적용함으로써, 산화물 반도체막(108)을, 불순물이 최대한 포함되지 않게 고순도화할 수가 있다.

[0277] 게이트 전극(112a) 및 전극(112b)은, 게이트 절연막(110)상에 도전막을 형성한 후에, 해당 도전막을 선택적으로 에칭함으로써 형성할 수가 있다.

[0278] 다음으로, 게이트 절연막(110), 게이트 전극(112a), 및 전극(112b)상에, 절연막(151) 및 절연막(152)을 형성한다. 절연막(151) 및 절연막(152)은, 스팍터법이나 CVD법 등을 이용하여 형성할 수가 있다. 또한, 산화실리콘, 산질화 실리콘, 질화 실리콘, 산화 하프늄, 산화 알루미늄, 산화 갈륨 등의 무기 절연 재료를 포함한 재료를 이용하여 형성할 수가 있다.

[0279] 다음으로, 게이트 절연막(110), 절연막(151), 및 절연막(152)에, 드레인 전극(104b)에까지 달하는 개구를 형성한다. 해당 개구의 형성은, 마스크 등을 이용한 선택적인 에칭에 의해 행해진다.

[0280] 그 후, 상기 개구에 전극(154)을 형성하고, 절연막(152)상에 전극(154)에 접하는 배선(156)을 형성한다.

- [0281] 전극(154)은, 예를 들면, 개구를 포함한 영역에 PVD법이나 CVD법 등을 이용하여 도전막을 형성한 후, 에칭 처리나 CMP라고 하는 방법을 이용하여, 상기 도전막의 일부를 제거함에 의해 형성할 수가 있다.

- [0282] 배선(156)은, 스퍼터법을 비롯한 PVD법이나, 플라즈마 CVD법 등의 CVD법을 이용하여 도전막을 형성한 후, 해당 도전막을 패터닝함으로써 형성된다. 또한, 도전막의 재료로서는, Al, Cr, Cu, Ta, Ti, Mo, W로부터 선택된 원소나, 상술한 원소를 성분으로 하는 합금 등을 이용할 수가 있다. Mn, Mg, Zr, Be, Nd, Sc중의 어느 것, 또는 이들을 복수 조합한 재료를 이용하여도 괜찮다. 자세한 것은, 소스 전극(104a) 또는 드레인 전극(104b) 등과 같다.

- [0283] 이상에 의해, 고순도화된 산화물 반도체막(108)을 이용한 트랜지스터(120), 및 용량 소자(164)가 완성된다. 용량 소자(164)는, 소스 전극(104a), 산화물 반도체막(108), 게이트 절연막(110), 및 전극(112b)으로 구성된다.

- [0284] 또한, 도 7의 용량 소자(164)에서는, 산화물 반도체막(108)과 게이트 절연막(110)을 적층시킴으로써, 소스 전극(104a)과 전극(112b)의 사이의 절연성을 충분히 확보할 수가 있다. 물론, 충분한 용량을 확보하기 위해서, 산화물 반도체막(108)을 갖지 않는 구성의 용량 소자(164)를 채용하여도 좋다. 게다가 용량이 불필요한 경우는, 용량 소자(164)를 마련하지 않는 구성으로 하는 것도 가능하다.

- [0285] 도 7(C)에는, 상기 반도체 장치를 메모리 소자로서 이용하는 경우의 회로도의 일 예를 나타낸다. 도 7(C)에 있어서, 트랜지스터(120)의 소스 전극 또는 드레인 전극의 한쪽과, 용량 소자(164)의 전극의 한쪽과, 트랜지스터(240)의 게이트 전극은 전기적으로 접속되어 있다. 또한, 제 1 배선(1st Line:소스선이라고도 부른다)과 트랜지스터(240)의 소스 전극은, 전기적으로 접속되며, 제 2 배선(2nd Line:비트선이라고도 부른다)과 트랜지스터(240)의 드레인 전극은, 전기적으로 접속되어 있다. 제 3 배선(3rd Line:제 1 신호선이라고도 부른다)과 트랜지스터(120)의 소스 전극 또는 드레인 전극의 다른 쪽은, 전기적으로 접속되어 있다. 또한, 제 4 배선(4th Line:제 2 신호선이라고도 부른다)과 트랜지스터(120)의 게이트 전극은, 전기적으로 접속되어 있다. 그리고, 제 5 배선(5th Line:word line라고도 부른다)과 용량 소자(164)의 전극의 다른쪽은 전기적으로 접속되어 있다.

- [0286] 산화물 반도체를 이용한 트랜지스터(120)는, 오프 전류가 극히 작다고 하는 특징을 갖고 있기 때문에, 트랜지스터(120)를 오프 상태로 함으로써, 트랜지스터(120)의 소스 전극 또는 드레인 전극의 한쪽과, 용량 소자(164)의 전극의 한쪽과, 트랜지스터(240)의 게이트 전극이 전기적으로 접속된 노드(이하, 노드(FG))의 전위를 극히 장시간에 걸쳐서 유지하는 것이 가능하다. 그리고, 용량 소자(164)를 가짐에 의해, 노드(FG)에 주어진 전하의 유지가 용이하게 되며, 또한 유지된 정보의 읽기가 용이하게 된다.

- [0287] 반도체 장치에 정보를 기억시키는 경우(쓰기)는, 우선 제 4 배선의 전위를, 트랜지스터(120)가 온 상태가 되는 전위로 하여, 트랜지스터(120)를 온 상태로 한다. 이에 의해, 제 3 배선의 전위가, 노드(FG)에 공급되어 노드(FG)에 소정량의 전하가 축적된다. 여기에서는, 서로 다른 2개의 전위 레벨을 주는 전하(이하, 로우(Low) 레벨 전하, 하이(High) 레벨 전하라고 한다)중의 어느 것이 주어지는 것으로 한다. 그 후, 제 4 배선의 전위를, 트랜지스터(120)가 오프 상태가 되는 전위로 하여, 트랜지스터(120)를 오프 상태로 함에 의해, 노드(FG)가 부유상태가 되기 때문에, 노드(FG)에는 소정의 전하가 유지된 채의 상태가 된다. 이상과 같이, 노드(FG)에 소정량의 전하를 축적 및 유지시킴으로써, 메모리 셀에 정보를 기억시킬 수가 있다.

- [0288] 트랜지스터(120)의 오프 전류는 극히 작기 때문에, 노드(FG)에 공급된 전하는 장시간에 걸쳐서 유지된다. 따라서, 리프레시 동작이 불필요하게 되던지, 또는 리프레시 동작의 빈도를 극히 낮게 하는 것이 가능해져서, 소비전력을 충분히 저감할 수가 있다. 또한, 전력의 공급이 없는 경우라도, 장기에 걸쳐 기억 내용을 유지하는 것이 가능하다.

- [0289] 기억된 정보를 읽어내는 경우(읽기)는, 제 1 배선에 소정의 전위(정전위)를 준 상태에서, 제 5 배선에 적절한 전위(읽기 전위)를 주면, 노드(FG)에 유지된 전하량에 따라서, 트랜지스터(240)는 다른 상태를 취한다. 일반적으로, 트랜지스터(240)를 n채널형으로 하면, 노드(FG)에 High 레벨 전하가 유지되고 있는 경우의 트랜지스터(240)의 걸보기 스레숄드(V<sub>th\_H</sub>)는, 노드(FG)에 Low 레벨 전하가 유지되고 있는 경우의 트랜지스터(240)의 걸보기 스레숄드(V<sub>th\_L</sub>)보다 낮아지기 때문이다. 여기서, 걸보기 스레숄드란, 트랜지스터(240)를 「온 상태」로 하기 위해서 필요한 제 5 배선의 전위를 말하는 것으로 한다. 따라서, 제 5 배선의 전위를 V<sub>th\_H</sub>와 V<sub>th\_L</sub>의 중간의 전위 V<sub>0</sub>로 함에 의해, 노드(FG)에 유지된 전하를 판별할 수 있다. 예를 들면, 쓰기에 있어서, High 레벨 전하가 주어져 있었을 경우에는, 제 5 배선의 전위가 V<sub>0</sub> (>V<sub>th\_H</sub>)가 되면, 트랜지스터(240)는 「온 상태」로 된다. Low 레벨 전하가 주어져 있었을 경우에는, 제 5 배선의 전위가 V<sub>0</sub> (<V<sub>th\_L</sub>)가 되어도, 트랜지스터(240)

0)는 「오프 상태」인 상태다. 이 때문에, 제 5 배선의 전위를 제어하여, 트랜지스터(240)의 온 상태 또는 오프 상태를 읽어냄(제 2 배선의 전위를 읽어냄)으로써, 기억된 정보를 읽어낼 수가 있다.

[0290] 또한, 기억시킨 정보를 고쳐 쓰는 경우에 있어서는, 상기 쓰기에 의해 소정량의 전하를 유지한 노드(FG)에, 새로운 전위를 공급함으로써, 노드(FG)에 새로운 정보와 관련되는 전하를 유지시킨다. 구체적으로는, 제 4 배선의 전위를, 트랜지스터(120)가 온 상태가 되는 전위로 하여, 트랜지스터(120)를 온 상태로 한다. 이에 의해, 제 3 배선의 전위(새로운 정보와 관련되는 전위)가 노드(FG)에 공급되어 노드(FG)에 소정량의 전하가 축적된다. 그 후, 제 4 배선의 전위를 트랜지스터(120)가 오프 상태가 되는 전위로 하여, 트랜지스터(120)를 오프 상태로 함에 의해, 노드(FG)에는, 새로운 정보와 관련되는 전하가 유지된 상태가 된다. 즉, 노드(FG)에 제 1 쓰기에 의해 소정량의 전하가 유지된 상태에서, 제 1 쓰기와 동일한 동작(제 2 쓰기)을 실시함으로써, 기억시킨 정보를 덮어쓰기하는 것이 가능하다.

[0291] 본 실시형태에서 나타내는 트랜지스터(120)는, 고순도화되어 진성화된 산화물 반도체막(108)을 이용함으로써, 트랜지스터(120)의 오프 전류를 충분히 저감할 수가 있다. 또한, 산화물 반도체막(108)을 산소 파이의 층으로 함으로써, 트랜지스터(120)의 전기적 특성 변동이 억제되어 있어 전기적으로 안정한 트랜지스터로 할 수가 있다. 그리고, 이러한 트랜지스터를 이용함으로써, 극히 장기에 걸쳐 기억 내용을 유지하는 것이 가능하여, 신뢰성이 높은 반도체 장치를 얻을 수 있다.

[0292] 또한, 본 실시형태에 있어서 나타내는 반도체 장치에서는, 트랜지스터(240)와 트랜지스터(120)를 중첩시킴으로써, 집적도가 충분히 높여진 반도체 장치가 실현된다.

[0293] 이상, 본 실시형태에 나타내는 구성, 방법 등은, 다른 실시형태에 나타내는 구성, 방법 등과 적절히 조합하여 이용할 수가 있다.

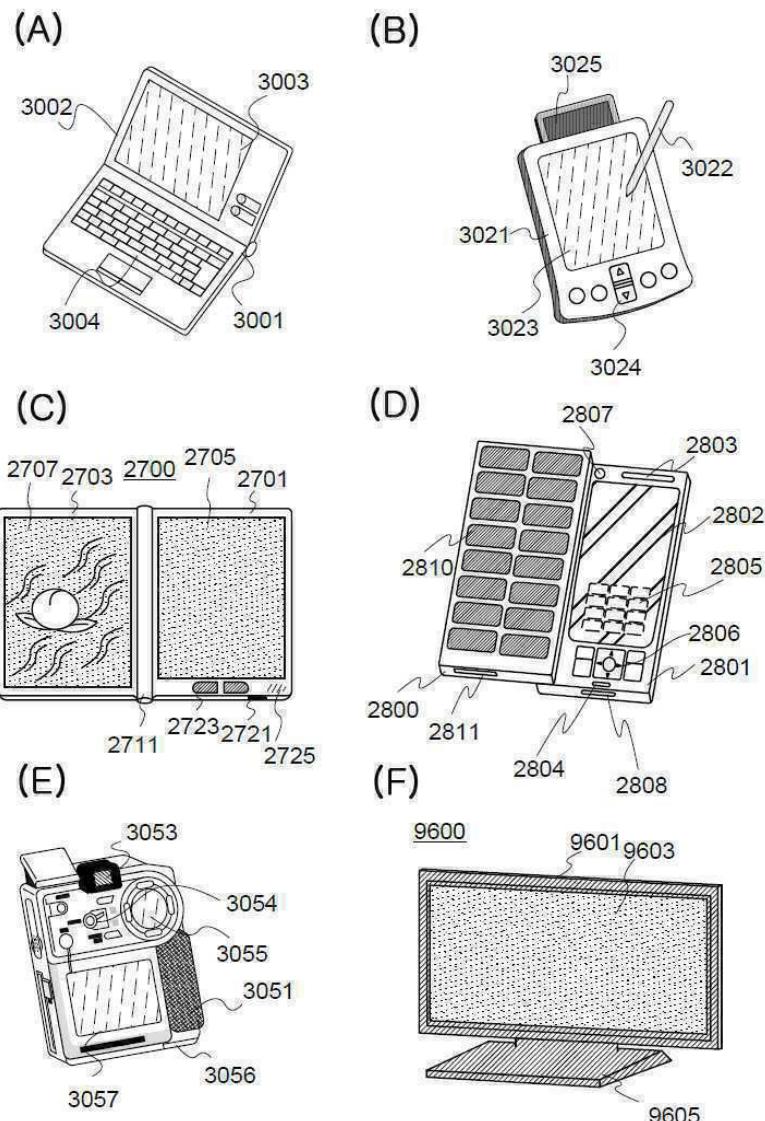

[0294] (실시형태 6)

[0295] 실시형태 1 내지 실시형태 3에서 예시한 트랜지스터를 이용하여 표시 기능을 갖는 반도체 장치(표시장치라고도 한다)를 제작할 수가 있다. 또한, 트랜지스터를 포함한 구동 회로의 일부 또는 전체를, 화소부와 동일 기판상에 일체로 형성하여 시스템온 패널을 형성할 수가 있다.

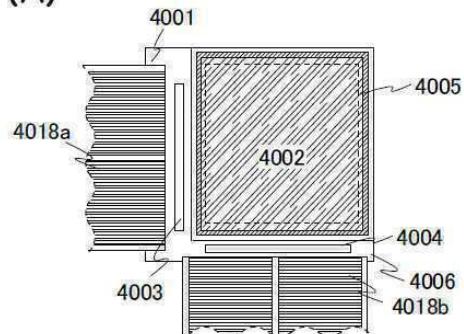

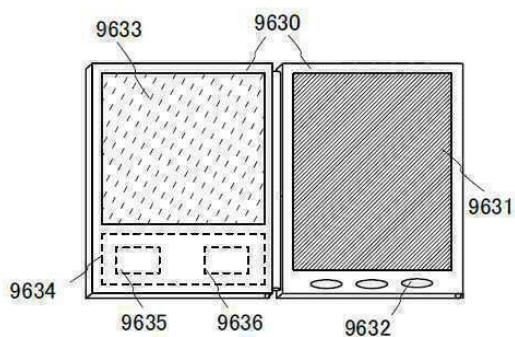

[0296] 도 8(A)에 있어서, 제 1 기판(4001)상에 마련된 화소부(4002)를 둘러싸도록 하여, 시일재(4005)가 마련되며, 제 2 기판(4006)에 의해 봉지되어 있다. 도 8(A)에 있어서는, 제 1 기판(4001)상의 시일재(4005)에 의해 둘러싸여 있는 영역과는 다른 영역에, 별도로 준비된 기판상에 단결정 반도체막 또는 다결정 반도체막으로 형성된 주사선 구동 회로(4004), 신호선 구동 회로(4003)가 실장되어 있다. 또한, 별도로 형성된 신호선 구동 회로(4003)와, 주사선 구동 회로(4004) 또는 화소부(4002)에 주어지는 각종 신호 및 전위는, FPC(Flexible printed circuit)(4018a), FPC(4018b)로부터 공급되고 있다.

[0297] 도 8(B) 및 도 8(C)에 있어서, 제 1 기판(4001)상에 마련된 화소부(4002)와 주사선 구동 회로(4004)를 둘러싸도록 하여, 시일재(4005)가 마련되어 있다. 또한, 화소부(4002)와 주사선 구동 회로(4004) 위에 제 2 기판(4006)이 마련되어 있다. 따라서, 화소부(4002)와 주사선 구동 회로(4004)는, 제 1 기판(4001)과 시일재(4005)와 제 2 기판(4006)에 의해, 표시 소자와 함께 봉지되어 있다. 도 8(B) 및 도 8(C)에 있어서는, 제 1 기판(4001)상의 시일재(4005)에 의해 둘러싸여 있는 영역과는 다른 영역에, 별도로 준비된 기판상에 단결정 반도체막 또는 다결정 반도체막으로 형성된 신호선 구동 회로(4003)가 실장되어 있다. 도 8(B) 및 도 8(C)에 있어서는, 별도로 형성된 신호선 구동 회로(4003)와, 주사선 구동 회로(4004) 또는 화소부(4002)에 주어지는 각종 신호 및 전위는, FPC(4018)로부터 공급되고 있다.

[0298] 또한, 실시형태는 도 8(A) 내지 도 8(C)에서 도시한 구성에 한정되지 않는다. 신호선 구동 회로의 일부 또는 주사선 구동 회로의 일부만을 별도로 형성하여 실장하여도 좋다.

[0299] 또한, 별도로 형성한 구동 회로의 접속 방법은, 특별히 한정되는 것은 아니고, COG(Chip On Glass) 방법, 와이어 본딩 방법, 혹은 TAB(Tape Automated Bonding) 방법 등을 이용할 수가 있다. 도 8(A)은, COG 방법에 의해 신호선 구동 회로(4003), 주사선 구동 회로(4004)를 실장하는 예이며, 도 8(B)은, COG 방법에 의해 신호선 구동 회로(4003)를 실장하는 예이며, 도 8(C)은, TAB 방법에 의해 신호선 구동 회로(4003)를 실장하는 예이다.

[0300] 또한, 표시장치는, 표시 소자가 봉지된 상태에 있는 패널과, 그 패널에 콘트롤러를 포함한 IC 등을 실장한 상태에 있는 모듈을 포함한다.

[0301] 또한, 본 명세서 중에 있어서의 표시장치란, 화상 표시 디바이스, 표시 디바이스, 혹은 광원(조명 장치 포함한

다)을 나타낸다. 또한, 커넥터, 예를 들면, FPC 혹은 TAB 테이프 혹은 TCP가 장착된 모듈, TAB 테이프나 TCP의 끝에 프린트 배선판이 마련된 모듈, 또는 표시 소자에 COG 방식에 의해 IC(집적회로)가 직접 실장된 모듈도 모두 표시장치에 포함하는 것으로 한다.

[0302] 또한, 제 1 기판상에 마련된 화소부 및 주사선 구동 회로는, 트랜지스터를 복수 갖고 있으며, 실시형태 1 내지 실시형태 3에서 예시한 트랜지스터를 적용할 수가 있다.

[0303] 표시장치에 마련되는 표시 소자로서는 액정 소자(액정 표시 소자라고도 한다), 발광소자(발광 표시 소자라고도 한다)를 이용할 수가 있다. 발광소자는, 전류 또는 전압에 의해 휘도가 제어되는 소자를 그 범주에 포함하고 있으며, 구체적으로는 무기 EL(Electro Luminescence) 소자, 유기 EL소자 등이 포함된다. 또한, 전자 잉크 등, 전기적 작용에 의해 콘트라스트가 변화하는 표시 매체도 적용할 수가 있다.

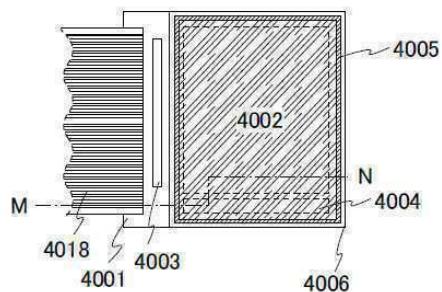

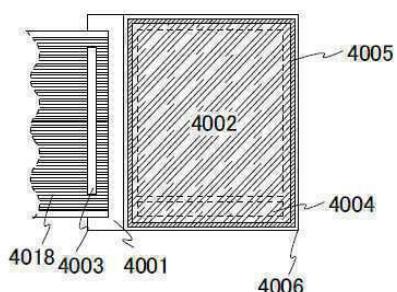

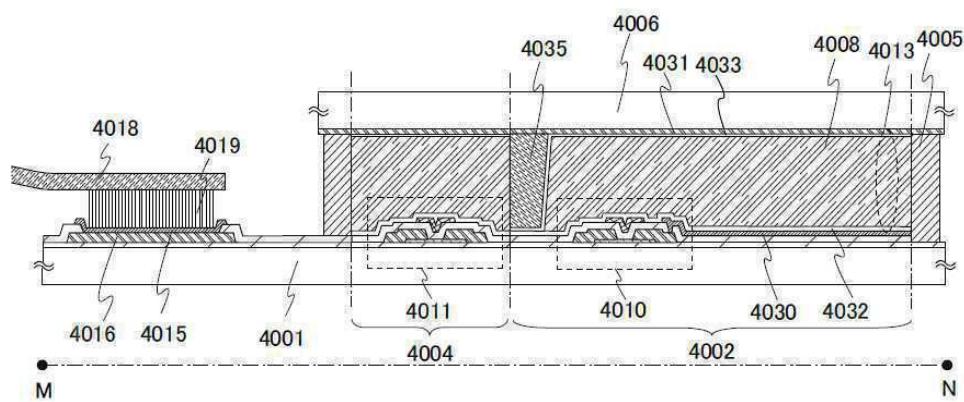

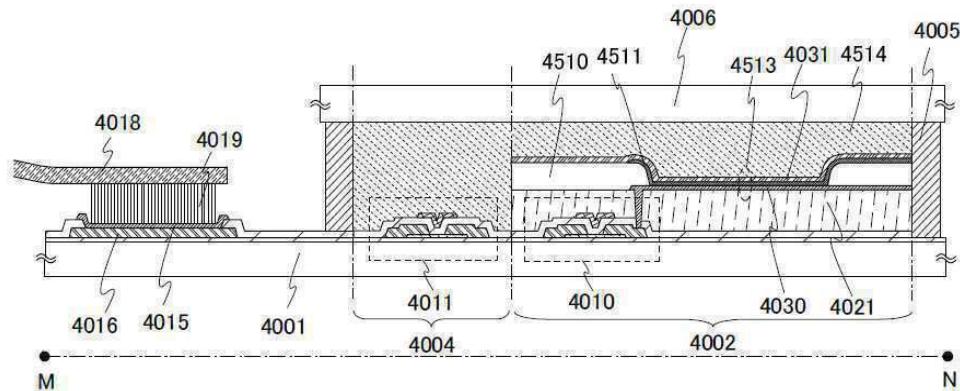

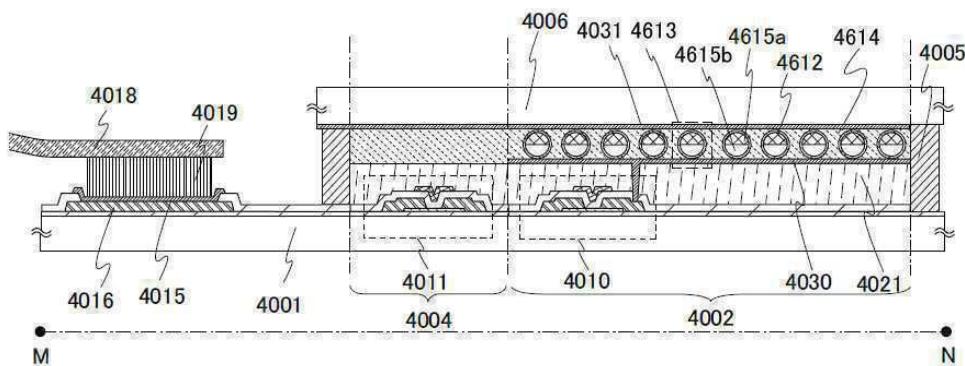

[0304] 반도체 장치의 일 형태에 대하여, 도 9 내지 도 11을 이용하여 설명한다. 도 9 내지 도 11은, 도 8(B)의 M-N에 있어서의 단면도에 상당한다.

[0305] 도 9 내지 도 11에서 나타내는 바와 같이, 반도체 장치는 접속 단자 전극(4015) 및 단자 전극(4016)을 갖고 있으며, 접속 단자 전극(4015) 및 단자 전극(4016)은 FPC(4018)가 갖는 단자와 이방성 도전막(4019)을 통하여 전기적으로 접속되어 있다.

[0306] 접속 단자 전극(4015)은, 제 1 전극층(4030)과 동일한 도전막으로부터 형성되며, 단자 전극(4016)은, 트랜지스터(4010), 트랜지스터(4011)의 소스 전극 및 드레인 전극과 동일한 도전막으로 형성되어 있다.

[0307] 또한 제 1 기판(4001)상에 마련된 화소부(4002)와 주사선 구동 회로(4004)는, 트랜지스터를 복수 갖고 있으며, 도 9 내지 도 11에서는, 화소부(4002)에 포함되는 트랜지스터(4010)와 주사선 구동 회로(4004)에 포함되는 트랜지스터(4011)를 예시하고 있다. 도 10 및 도 11에서는, 트랜지스터(4010), 트랜지스터(4011)상에, 절연층(4021)이 마련되어 있다.

[0308] 본 실시형태에서는, 트랜지스터(4010), 트랜지스터(4011)로서, 실시형태 1 내지 실시형태 3중의 어딘가에 나타낸 트랜지스터를 적용할 수가 있다. 트랜지스터(4010), 트랜지스터(4011)는, 전기적 특성 변동이 억제되어 있어 전기적으로 안정하다. 따라서, 도 9 내지 도 11에서 나타내는 본 실시형태의 반도체 장치로서 신뢰성이 높은 반도체 장치를 제공할 수가 있다.

[0309] 화소부(4002)에 마련된 트랜지스터(4010)는 표시 소자와 전기적으로 접속하여 표시 패널을 구성한다. 표시 소자는 표시를 실시할 수가 있으면 특별히 한정되지 않고, 여러 가지 표시 소자를 이용할 수가 있다.

[0310] 도 9에 표시 소자로서 액정 소자를 이용한 액정표시장치의 예를 나타낸다. 도 9에 있어서, 표시 소자인 액정 소자(4013)는, 제 1 전극층(4030), 제 2 전극층(4031), 및 액정층(4008)을 포함한다. 또한 액정층(4008)을 가운데 끼우도록 배향막으로서 기능하는 절연막(4032), 절연막(4033)이 마련되어 있다. 제 2 전극층(4031)은 제 2 기판(4006)측에 마련되며, 제 1 전극층(4030)과 제 2 전극층(4031)은 액정층(4008)을 통하여 격충하는 구성으로 되어 있다.

[0311] 또한, 기둥 형상의 스페이서(4035)는 절연막을 선택적으로 에칭함으로써 얻어지며, 액정층(4008)의 막두께(셀 갭)를 제어하기 위해서 마련되어 있다. 또한 스페이서의 형상은, 기둥 형상에 한정되는 것은 아니고, 예를 들면, 구형상의 스페이서를 이용하고 있어도 좋다.

[0312] 표시 소자로서 액정 소자를 이용하는 경우, 서모트로픽 액정, 저분자 액정, 고분자 액정, 고분자 분산형 액정, 강유전성 액정, 반강유전성 액정 등을 이용할 수가 있다. 이러한 액정 재료는, 조건에 따라서, 콜레스테릭상 (cholesteric phase), 스멕티상(smectic phase), 큐빅상, 키랄네마틱, 등방상 등을 나타낸다.

[0313] 또한, 배향막을 이용하지 않는 블루상을 나타내는 액정을 이용하여도 괜찮다. 블루상은 액정상의 하나로서, 콜레스테릭 액정을 온도상승해 가면, 콜레스테릭상으로부터 등방상으로 전이하기 직전에 발현하는 상이다. 블루상은 좁은 온도 범위에서 밖에 발현하지 않기 때문에, 온도 범위를 개선하기 위해서 수 중량% 이상의 키랄제를 혼합시킨 액정 조성물을 액정층에 이용한다. 블루상을 나타내는 액정과 키랄제를 포함한 액정 조성물은, 응답 속도가 1 msec 이하로 짧고, 광학적 등방성이기 때문에 배향 처리가 불필요하고, 시야각 의존성이 작다. 또한, 배향막을 마련하지 않아도 좋기 때문에 러빙 처리도 불필요해지기 때문에, 러빙 처리에 의해 발생되는 정전 파괴를 방지할 수가 있어 제작 공정 중의 액정표시장치의 불량이나 파손을 경감할 수가 있다. 따라서, 액정표시장치의 생산성을 향상시키는 것이 가능해진다.

- [0314] 또한, 액정 재료의 고유 저항율은,  $1 \times 10^9 \Omega \cdot \text{cm}$  이상이며, 바람직하게는  $1 \times 10^{11} \Omega \cdot \text{cm}$  이상이며, 더욱 바람직하게는  $1 \times 10^{12} \Omega \cdot \text{cm}$  이상이다. 또한 본 명세서에 있어서의 고유 저항율의 값은, 20°C에서 측정한 값으로 한다.

- [0315] 액정표시장치에 마련되는 보유 용량의 크기는, 화소부에 배치되는 트랜지스터의 리크 전류 등을 고려하여, 소정의 기간, 전하를 유지할 수 있도록 설정된다. 고순도의 산화물 반도체막을 갖는 트랜지스터를 이용함으로써, 각 화소에 있어서의 액정 용량에 대하여 1/3 이하, 바람직하게는 1/5 이하의 용량의 크기를 갖는 보유 용량을 마련하면 충분하다.

- [0316] 본 실시형태에서 이용하는 고순도화된 산화물 반도체막을 이용한 트랜지스터는, 오프 상태에 있어서의 전류치(오프 전류치)를 낮게 할 수가 있다. 따라서, 화상 신호 등의 전기신호의 유지 시간을 길게 할 수가 있어 전원온 상태에서는 쓰기 간격도 길게 설정할 수 있다. 따라서, 리프레시 동작의 빈도를 줄일 수가 있기 때문에, 소비 전력을 억제하는 효과를 나타낸다.

- [0317] 또한, 본 실시형태에서 이용하는 고순도화된 산화물 반도체막을 이용한 트랜지스터는, 비교적 높은 전계 효과 이동도를 얻을 수 있기 때문에, 고속 구동이 가능하다. 따라서, 액정표시장치의 화소부에 상기 트랜지스터를 이용함으로써, 고화질의 화상을 제공할 수가 있다. 또한, 상기 트랜지스터는, 동일 기판상에 구동 회로부 또는 화소부로 구별해서 만들어서 제작할 수가 있기 때문에, 액정표시장치의 부품 점수를 삭감할 수가 있다.

- [0318] 액정표시장치에는, TN(Twisted Nematic) 모드, IPS(In-Plane-Switching) 모드, FFS(Fringe Field Switching) 모드, ASM(Axially Symmetric aligned Micro-cell) 모드, OCB(Optical Compensated Birefringence) 모드, FLC(Ferroelectric Liquid Crystal) 모드, AFLC(AntiFerroelectric Liquid Crystal) 모드 등을 이용할 수가 있다.

- [0319] 또한, 노멀리블랙형의 액정표시장치, 예를 들면, 수직 배향(VA) 모드를 채용한 투과형의 액정표시장치로 하여도 좋다. 여기서, 수직 배향 모드란, 액정 표시 패널의 액정 분자의 배열을 제어하는 방식의 일종이며, 전압이 인가되어 있지 않을 때에 패널면에 대하여 액정 분자가 수직 방향을 향하는 방식이다. 수직 배향 모드로서는, 몇 가지 들 수 있지만, 예를 들면, MVA(Multi-Domain Vertical Alignment) 모드, PVA(Patterned Vertical Alignment) 모드, ASV(Advanced Super View) 모드 등을 이용할 수가 있다. 또한, 화소(픽셀)를 몇 개의 영역(서브 픽셀)으로 나누고, 각각 다른 방향으로 분자를 쓰러뜨리도록 설계되어 있는 멀티 도메인화 혹은 멀티 도메인 설계라고 하는 방법을 이용할 수가 있다.

- [0320] 또한, 표시장치에 있어서, 블랙 매트릭스(차광층), 편광 부재, 위상차 부재, 반사 방지 부재 등의 광학 부재(광학 기판) 등은 적절히 마련한다. 예를 들면, 편광 기판 및 위상차이 기판에 의한 원 편광을 이용하여도 괜찮다. 또한, 광원으로서 백라이트, 사이드라이트 등을 이용하여도 괜찮다.

- [0321] 또한, 백라이트로서 복수의 발광 다이오드(LED)를 이용하여, 시간 분할 표시 방식(필드 시퀀셜 구동 방식)을 실시하는 것도 가능하다. 필드 시퀀셜 구동 방식을 적용함으로써, 칼라 필터를 이용하는 일 없이, 칼라 표시를 실시할 수가 있다.

- [0322] 또한, 화소부에 있어서의 표시 방식은, 프로그래시브 방식이나 인터레이스 방식 등을 이용할 수가 있다. 또한, 칼라 표시할 때에 화소로 제어하는 색 요소로서는, RGB(R는 빨강, G는 초록, B는 파랑을 나타낸다)의 삼색에 한정되지 않는다. 예를 들면, RGBW(W는 흰색을 나타낸다), 또는 RGB에, 엘로우, 시안, 마젠타 등을 한 색 이상 추가한 것이 있다. 또한 색 요소의 도트마다 그 표시 영역의 크기가 차이가 나도 괜찮다. 다만, 본 발명은 칼라 표시의 표시장치에 한정되는 것은 아니고, 흑백 표시의 표시장치에 적용할 수도 있다.

- [0323] 또한, 표시장치에 포함되는 표시 소자로서 전계 발광을 이용하는 발광소자를 적용할 수가 있다. 전계 발광을 이용하는 발광소자는, 발광재료가 유기 화합물인지, 무기 화합물인지에 따라서 구별되며, 전자는 유기 EL소자, 후자는 무기 EL소자로 불리고 있다.

- [0324] 유기 EL소자는, 발광소자에게 전압을 인가함에 의해, 한 쌍의 전극으로부터 전자 및 정공이 각각 발광성의 유기 화합물을 포함하는 층에 주입되어 전류가 흐른다. 그리고, 그들 캐리어(전자 및 정공)가 재결합함에 의해, 발광성의 유기 화합물이 여기 상태를 형성하고, 그 여기 상태가 기저 상태로 돌아올 때에 발광한다. 이러한 메커니즘으로부터, 이러한 발광소자는, 전류 여기형의 발광소자로 불린다.

- [0325] 무기 EL소자는, 그 소자 구성에 따라서, 분산형 무기 EL소자와 박막형 무기 EL소자로 분류된다. 분산형 무기

EL소자는, 발광재료의 입자를 바인더중에 분산시킨 발광층을 갖는 것이며, 발광 메카니즘은 도너 준위와 억셉터 준위를 이용하는 도너-억셉터 재결합형 발광이다. 박막형 무기 EL소자는, 발광층을 유전체층으로 사이에 끼워 넣고, 게다가 이를 전극으로 사이에 끼운 구조이며, 발광 메카니즘은 금속 이온의 내각 전자 천이를 이용하는 국재형(局在型) 발광이다. 또한 여기에서는, 발광소자로서 유기 EL소자를 이용하여 설명한다.

[0326] 발광소자는 발광을 취출하기 위해서 적어도 한 쌍의 전극중의 한쪽이 투명하면 좋다. 그리고, 기판상에 트랜지스터 및 발광소자를 형성하고, 기판과는 반대측의 면으로부터 발광을 취출하는 표면 사출이나, 기판측의 면으로부터 발광을 취출하는 하면 사출이나, 기판측 및 기판과는 반대측의 면으로부터 발광을 취출하는 양면 사출 구조의 발광소자가 있으며, 어느 사출 구조의 발광소자라도 적용할 수가 있다.

[0327] 도 10에 표시 소자로서 발광소자를 이용한 발광 장치의 예를 나타낸다. 표시 소자인 발광소자(4513)는, 화소부(4002)에 마련된 트랜지스터(4010)와 전기적으로 접속되어 있다. 또한 발광소자(4513)의 구성은, 제 1 전극층(4030), 전계 발광층(4511), 제 2 전극층(4031)의 적층 구조이지만, 도시한 구성에 한정되지 않는다. 발광소자(4513)로부터 취출하는 광의 방향 등에 맞추어, 발광소자(4513)의 구성은 적절히 바꿀 수가 있다.

[0328] 격벽(4510)은, 유기 절연 재료, 또는 무기 절연 재료를 이용하여 형성한다. 특히 감광성의 수지 재료를 이용하며, 제 1 전극층(4030)상에 개구부를 형성하고, 그 개구부의 측벽이 연속한 곡률을 가지고 형성되는 경사면이 되도록 형성하는 것이 바람직하다.

[0329] 전계 발광층(4511)은, 단수의 층으로 구성되어 있어도, 복수의 층이 적층되도록 구성되어 있어도 어느 쪽이라도 좋다.

[0330] 발광소자(4513)에 산소, 수소, 수분, 이산화탄소 등이 침입하지 않도록, 제 2 전극층(4031) 및 격벽(4510)상에 보호막을 형성하여도 좋다. 보호막으로서는, 질화 실리콘막, 질화 산화 실리콘막, DLC(Diamond-Like Carbon)막 등을 형성할 수가 있다. 또한, 제 1 기판(4001), 제 2 기판(4006), 및 시일재(4005)에 의해 봉지된 공간에는 충전재(4514)가 마련되어 밀봉되어 있다. 이와 같이 외기에 노출되지 않게 기밀성이 높고, 탈가스가 적은 보호 필름(부착 필름, 자외선 경화 수지 필름 등)이나 커버재로 패키징(봉입)하는 것이 바람직하다.

[0331] 충전재(4514)로서는, 질소나 아르곤 등의 불활성인 기체 외에, 자외선 경화 수지 또는 열경화 수지를 이용할 수가 있으며, PVC(폴리비닐 클로라이드), 아크릴, 폴리아미드, 에폭시 수지, 실리콘 수지, PVB(폴리비닐부티랄) 또는 EVA(에틸렌 비닐 아세테이트)를 이용할 수가 있다. 예를 들면 충전재로서 질소를 이용하면 좋다.

[0332] 또한, 필요하면, 발광소자의 사출면에 편광판, 또는 원편광판(타원 편광판을 포함한다), 위상차판( $\lambda/4$ 판,  $\lambda/2$ 판), 칼라 필터 등의 광학 필름을 적절히 마련하여도 좋다. 또한, 편광판 또는 원편광판에 반사 방지막을 마련하여도 좋다. 예를 들면, 표면의 요철에 의해 반사광을 확산하고, 빛 반사를 저감할 수 있는 안티글레어 처리를 실시할 수가 있다.

[0333] 또한, 표시장치로서 전자 잉크를 구동시키는 전자 페이퍼를 제공하는 것도 가능하다. 전자 페이퍼는, 전기 영동 표시장치(전기 영동 디스플레이)라고도 불리고 있으며, 종이와 같은 읽기 쉬움, 다른 표시장치에 비해 저소비 전력, 얇고 가벼운 형상으로 하는 것이 가능하다는 이점을 갖고 있다.

[0334] 전기 영동 표시장치는, 여러 가지 형태가 생각될 수 있지만, 플러스의 전하를 갖는 제 1 입자와, 마이너스의 전하를 갖는 제 2 입자를 포함한 마이크로 캡슐이 용매 또는 용질에 복수 분산된 것이며, 마이크로 캡슐에 전계를 인가함으로써, 마이크로 캡슐중의 입자를 서로 반대 방향으로 이동시켜 한쪽 측으로 집합한 입자의 색만을 표시하는 것이다. 또한 제 1 입자 또는 제 2 입자는 염료를 포함하며, 전계가 없는 경우에 이동하지 않는 것이다. 또한, 제 1 입자의 색과 제 2 입자의 색은 서로 다른 것(무색을 포함한다)으로 한다.

[0335] 이와 같이, 전기 영동 표시장치는, 유전상수가 높은 물질이 높은 전계 영역으로 이동하는, 이른바 유전영동적 효과를 이용한 디스플레이이다.

[0336] 상기 마이크로 캡슐을 용매중에 분산시킨 것이 전자 잉크로 불리는 것이며, 이 전자 잉크는 유리, 플라스틱, 옷감, 종이 등의 표면에 인쇄할 수가 있다. 또한, 칼라 필터나 색소를 갖는 입자를 이용함에 의해 칼라 표시도 가능하다.

[0337] 또한, 마이크로 캡슐중의 제 1 입자 및 제 2 입자는, 도전체 재료, 절연체 재료, 반도체 재료, 자성 재료, 액정 재료, 강유전성 재료, 일렉트로루미네스цен트 재료, 일렉트로크로믹 재료, 자기영동재료로부터 선택된 1종의 재료, 또는 이들의 복합재료를 이용하면 좋다.

- [0338] 또한, 전자 페이퍼로서, 트위스트볼 표시 방식을 이용하는 표시장치도 적용할 수가 있다. 트위스트볼 표시 방식이란, 흰색과 흑색으로 구별하여 칠해진 구형 입자를 표시 소자에 이용하는 전극층인 제 1 전극층 및 제 2 전극층의 사이에 배치하여, 제 1 전극층 및 제 2 전극층에 전위차를 발생시킨 구형 입자의 방향을 제어함에 의해 표시를 실시하는 방법이다.

- [0339] 도 11에, 반도체 장치의 일 형태로서 액티브 매트릭스형의 전자 페이퍼를 나타낸다. 도 11의 전자 페이퍼는, 트위스트볼 표시 방식을 이용한 표시장치의 예이다.

- [0340] 트랜지스터(4010)와 접속하는 제 1 전극층(4030)과, 제 2 기판(4006)에 마련된 제 2 전극층(4031)의 사이에는 흑색 영역(4615a) 및 백색 영역(4615b)을 가지며, 주위에 액체로 채워져 있는 캐비티(4612)를 포함한 구형 입자(4613)가 마련되어 있으며, 구형 입자(4613)의 주위는 수지 등의 충전재(4614)로 충전되어 있다. 제 2 전극층(4031)이 공통 전극(대향 전극)에 상당한다. 제 2 전극층(4031)은 공통 전위선과 전기적으로 접속된다.

- [0341] 또한, 도 9 내지 도 11에 있어서, 제 1 기판(4001), 제 2 기판(4006)으로서는, 유리 기판 외에, 가요성을 갖는 기판도 이용할 수가 있으며, 예를 들면, 투광성을 갖는 플라스틱 기판 등을 이용할 수가 있다. 플라스틱으로서는, FRP(Fiberglass-Reinforced Plastics) 판, PVF(폴리비닐 플루오라이드) 필름, 폴리에스테르 필름 또는 아크릴 수지 필름을 이용할 수가 있다. 또한, 알루미늄 호일을 PVF 필름이나 폴리에스테르 필름으로 사이에 끼운 구조의 시트를 이용할 수도 있다.

- [0342] 절연층(4021)은, 무기 절연 재료 또는 유기 절연 재료를 이용하여 형성할 수가 있다. 또한 아크릴 수지, 폴리아미드, 벤조시클로부텐계 수지, 폴리아미드, 에폭시 수지 등의, 내열성을 갖는 유기 절연 재료를 이용하면, 평탄화 절연막으로서 매우 적합하다. 또한, 상기 유기 절연 재료 외에, 저유전율 재료(low-k재료), 실록산계 수지, PSG(인 유리), BPSG(인 봉소 유리) 등을 이용할 수가 있다. 또한 이러한 재료로 형성되는 절연막을 복수 적층시킴으로써, 절연층을 형성하여도 좋다.

- [0343] 절연층(4021)의 형성법은, 특별히 한정되지 않고, 그 재료에 따라서, 스퍼터링법, 스플 코트법, 딥핑법, 스프레이 도포, 액적 토출법(잉크젯법 등), 스크린 인쇄, 익셋 인쇄 등을 적용할 수가 있다. 롤 코팅, 커텐 코팅, 나이프 코팅 등을 이용하여 절연층(4021)을 형성할 수도 있다.

- [0344] 표시장치는, 광원 또는 표시 소자로부터의 광을 투과시켜 표시를 실시한다. 따라서, 광이 투과하는 화소부에 마련되는 기판, 절연막, 도전막 등의 박막은 모두 가시광선의 파장 영역의 광에 대하여 투광성으로 한다.

- [0345] 표시 소자에 전압을 인가하는 제 1 전극층 및 제 2 전극층(화소 전극층, 공통 전극층, 대향 전극층 등이라고도 한다)에 있어서는, 취출하는 광의 방향, 전극층이 마련되는 장소, 및 전극층의 패턴 구조에 따라서 투광성, 반사성을 선택하면 좋다.