(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-502114

(P2005-502114A)

(43) 公表日 平成17年1月20日(2005.1.20)

(51) Int.C1.<sup>7</sup>

G06F 1/04

G06F 1/32

F 1

G06F 1/04 301C

G06F 1/00 332Z

テーマコード(参考)

5B011

5B079

審査請求 未請求 予備審査請求 有 (全 67 頁)

(21) 出願番号 特願2003-525432 (P2003-525432)

(86) (22) 出願日 平成14年8月29日 (2002.8.29)

(85) 翻訳文提出日 平成16年2月27日 (2004.2.27)

(86) 國際出願番号 PCT/US2002/027666

(87) 國際公開番号 WO2003/021409

(87) 國際公開日 平成15年3月13日 (2003.3.13)

(31) 優先権主張番号 60/315,655

(32) 優先日 平成13年8月29日 (2001.8.29)

(33) 優先権主張国 米国(US)

(71) 出願人 501144003

アナログ・デバイシズ・インコーポレーテッド

アメリカ合衆国マサチューセッツ州ノーウッド, ワン・テクノロジー・ウェイ (番地なし)

(74) 代理人 100102842

弁理士 葛和 清司

(72) 発明者 ビルク, パッレ

デンマーク王国 ディーケー-9260

ジストラップ、クローネン 34

(72) 発明者 ゾーレンセン, ヨアルン

デンマーク王国 ディーケー-9600

アールス、ブーラーヴェイ 35

最終頁に続く

(54) 【発明の名称】動的電圧制御方法および装置

## (57) 【要約】

プロセッサのクロック周波数要求を特定し、このクロック周波数要求を支援する電圧要求を特定する、動的電力コントローラが提供される。この動的電力コントローラは、クロック周波数要求および電圧要求によって定義される電力状態に、プロセッサを遷移させる。特に、電圧要求によって示される電圧レベルがプロセッサに供給されるとともに、周波数要求によって示される周波数分配がプロセッサのクロック信号に提供される。

**【特許請求の範囲】****【請求項 1】**

複数の周波数で動作可能な少なくとも 1 つのクロック信号を有する、少なくとも 1 つのプロセッサを含むシステムにおいて、

前記少なくとも 1 つのプロセッサのクロック周波数要求を特定するステップと、

前記クロック周波数要求を支援するための電圧要求を特定するステップと、

前記クロック周波数要求に応じて、前記少なくとも 1 つのクロック信号を動作させるステップと、

前記電圧要求に応じて、前記少なくとも 1 つのプロセッサに供給する電圧を提供するステップとを含む、動的電力制御方法。

10

**【請求項 2】**

電圧要求を特定するステップが、クロック周波数要求の最大の最小クロック周波数を特定するステップを含む、請求項 1 に記載の方法。

**【請求項 3】**

少なくとも 1 つのプロセッサに供給される現行電圧と、電圧要求に応じた電圧との間の電圧差の符号を特定するステップをさらに含む、請求項 1 に記載の方法。

**【請求項 4】**

電圧差の符号が正の場合に、電圧要求に応じて少なくとも 1 つのプロセッサに供給する電圧を提供するステップを、クロック周波数要求に応じて少なくとも 1 つのクロック信号を動作させるステップの前に遂行する、請求項 3 に記載の方法。

20

**【請求項 5】**

電圧差の符号が負の場合に、クロック周波数要求に応じて少なくとも 1 つのクロック信号を動作させるステップを、電圧要求に応じて少なくとも 1 つのプロセッサに供給する電圧を提供するステップの前に遂行する、請求項 3 に記載の方法。

**【請求項 6】**

少なくとも 1 つのプロセッサが、複数のクロックドメインを有し、各クロックドメインが、前記少なくとも 1 つのプロセッサの、複数の構成要素に、複数の周波数でクロック信号を提供し、かつ

クロック周波数要求を特定するステップが、前記複数のクロックドメインのそれぞれにおいて必要とされる最小クロック周波数を特定することを含む、請求項 1 に記載の方法。

30

**【請求項 7】**

複数のクロックドメインのそれぞれにおいて必要とされる、最小クロック周波数を比較するステップをさらに含む、請求項 6 に記載の方法。

**【請求項 8】**

比較をするステップが、複数のクロックドメインのそれぞれにおいて必要とされる最小クロック周波数を比較して、前記複数のクロックドメインが必要とする最大の最小クロック周波数を特定することを含む、請求項 7 に記載の方法。

**【請求項 9】**

電圧要求を特定するステップが、最大最小クロック周波数から前記電圧要求を特定することを含む、請求項 8 に記載の方法。

40

**【請求項 10】**

少なくとも 1 つのプロセッサが複数のクロックドメインを有し、各クロックドメインが前記プロセッサの複数の構成要素にクロック信号を提供し、各クロック信号が少なくとも 1 つの関連する周波数を有するとともに、

クロック周波数要求を特定するステップが、前記複数のクロックドメインのそれぞれを動作可能にする必要があるかどうかを判定することを含む、請求項 1 に記載の方法。

**【請求項 11】**

電圧要求を特定するステップが、動作可能にする必要のあるクロックドメインの、少なくとも 1 つの関連する周波数に基づいて、電圧要求を特定するステップを含む、請求項 10 に記載の方法。

50

**【請求項 1 2】**

複数の周波数で動作する少なくとも1つのクロック信号を含むプロセッサであって、前記少なくとも1つのクロック信号を受け取る1つまたは複数の構成要素と、前記プロセッサのクロック周波数要求を同定する少なくとも1つの構成要素に結合されたコントローラであって、前記プロセッサのクロック周波数要求に基づいて電圧要求を特定するとともに、前記クロック周波数要求および前記電圧要求によって定義される電力状態への遷移を順序づける、前記コントローラとを含む、前記プロセッサ。

**【請求項 1 3】**

コントローラが複数のレジスタによって少なくとも1つの構成要素に結合され、前記複数のレジスタがプロセッサのクロック周波数要求を示す情報を記憶する、請求項12に記載のプロセッサ。 10

**【請求項 1 4】**

コントローラが、複数のレジスタに結合されたコンパレータを含み、該コンパレータが、前記複数のレジスタ内に記憶された情報に基づいて電圧要求を特定するように構成されている、請求項13に記載のプロセッサ。

**【請求項 1 5】**

プロセッサが、1つまたは複数のクロック動作構成要素に提供されて、複数の周波数で動作する複数のクロック信号を含む、請求項14に記載のプロセッサ。

**【請求項 1 6】**

複数のレジスタが、複数のクロック信号の、それぞれのクロック周波数要求に対応する値を記憶する、請求項15に記載のプロセッサ。 20

**【請求項 1 7】**

コンパレータが、複数のレジスタ内に記憶された最大値を特定し、その結果としてクロック周波数要求を特定する、請求項16に記載のプロセッサ。

**【請求項 1 8】**

コントローラが、複数の電圧値を記憶するメモリをさらに含む、請求項14に記載のプロセッサ。

**【請求項 1 9】**

コンパレータが、複数のレジスタ内に記憶された情報を、プロセッサのクロック周波数要求を支援するのに十分な電圧値を記憶する、メモリ内の場所にマッピングする、請求項18に記載のプロセッサ。 30

**【請求項 2 0】**

コントローラが、クロック周波数要求および電圧要求によって定義される電力状態への遷移を順序づける有限状態機械を含む、請求項19に記載のプロセッサ。

**【請求項 2 1】**

有限状態機械が、メモリから得られた電圧値を受け取り、プロセッサに供給されている現行電圧レベルと前記得られた電圧値との差の符号を特定する、請求項20に記載のプロセッサ。

**【請求項 2 2】**

差の符号が正のときには、有限状態機械は、得られた電圧値で動作するようにプロセッサを遷移させ、次いでクロック周波数要求で動作するようにプロセッサを遷移させる、請求項21に記載のプロセッサ。 40

**【請求項 2 3】**

差の符号が負のときには、有限状態機械は、クロック周波数要求で動作するようにプロセッサを遷移させ、次いで得られた電圧値で動作するようにプロセッサを遷移させる、請求項21に記載のプロセッサ。

**【請求項 2 4】**

少なくとも1つのクロック信号が複数のクロック信号を含み、1つまたは複数のクロック動作構成要素が複数のクロック動作構成要素を含む、請求項13に記載のプロセッサ。

**【請求項 2 5】**

複数のレジスタが、複数のクロック動作構成要素のそれぞれが必要とする、複数のクロック信号のそれぞれに対する周波数値を記憶する、請求項 2 4 に記載のプロセッサ。

【請求項 2 6】

複数のレジスタが、複数のクロック動作構成要素のそれぞれが複数のクロック信号のそれぞれを必要とするかどうかを示す、2進値を記憶する、請求項 2 4 に記載のプロセッサ。

【請求項 2 7】

複数のクロック信号を有するプロセッサへの電力を動的に制御するコントローラであって、

、前記プロセッサのクロック周波数要求を示す情報を記憶する複数のレジスタと、

該複数のレジスタに結合されたコンパレータであって、前記複数のレジスタに記憶された

前記情報に基づいて電圧要求を特定するように構成された、前記コンパレータと、

前記コンパレータに結合されて、前記プロセッサを、前記クロック周波数要求および前記

電圧要求によって定義される電力状態に遷移させるように構成されたシーケンサとを含む

、前記コントローラ。

【請求項 2 8】

複数のレジスタが、プロセッサの複数の構成要素が必要とする複数の周波数値を記憶する

、請求項 2 7 に記載のコントローラ。

【請求項 2 9】

複数のレジスタのそれぞれが、プロセッサに供給される複数のクロック信号のそれぞれに

対するビットを含み、該ビットが、それに対応するクロック信号を動作可能にする必要が

あるかどうかを示す、請求項 2 7 に記載のコントローラ。

【請求項 3 0】

コンパレータが、複数の電圧値を記憶するメモリを含み、前記コンパレータは複数のレジ

スタに記憶された複数の周波数値を、前記複数の周波数値によって示されるクロック周波

数要求を支援するのに十分な電圧値を記憶するメモリの場所にマッピングする、請求項 2

8 に記載のコントローラ。

【請求項 3 1】

コンパレータがプログラマブル論理配列を含み、前記コンパレータは複数のレジスタに記

憶された複数の周波数値をプログラマブル論理配列への入力にマッピングするように適合

されており、前記プログラマブル論理配列は、クロック周波数要求を支援するのに必要な

電圧値を示す、シーケンサへの出力を提供するようにプログラムされている、請求項 2 8

に記載のコントローラ。

【請求項 3 2】

シーケンサが有限状態機械である、請求項 2 7 に記載のコントローラ。

【請求項 3 3】

複数の構成要素をさらに含むプロセッサと組み合わせた、請求項 2 7 に記載のコントロ

ーラ。

【請求項 3 4】

複数の構成要素のそれぞれが、複数のレジスタのそれぞれ 1 つを介して、前記構成要素の

クロック周波数要求を示す、請求項 3 3 に記載の組合せ。

【請求項 3 5】

複数のレジスタが、複数のクロック信号のそれぞれに対応するビットを含む、請求項 2 7

に記載の組合せ。

【請求項 3 6】

複数の構成要素のそれぞれが、複数のレジスタの少なくとも 1 つと関連し、かつ前記複数

の構成要素のそれぞれは、複数のクロック信号のそれぞれに対応するビットを介して、そ

れぞれのクロック信号が必要かどうかを示す、請求項 3 5 に記載の組合せ。

【請求項 3 7】

複数のクロック信号で動作する複数の構成要素を有する少なくとも 1 つのプロセッサと、

該少なくとも 1 つのプロセッサに、変更可能なレベルの電圧を供給するように適合された

10

20

30

40

50

電源と、

前記複数のクロック信号の周波数を制御するように適合されたクロックコントローラと、前記電源および前記クロックコントローラに接続されて、前記少なくとも1つのプロセッサを監視して前記少なくとも1つのプロセッサのクロック周波数要求を特定するとともに前記クロック周波数要求に基づいて電圧要求を特定し、かつ前記電源および前記クロックコントローラを、前記クロック周波数要求および前記電圧要求によって定義される電力状態に遷移させる、動的電力コントローラとを含む、デバイス。

【請求項38】

複数のクロック信号が、システムクロック信号を含む、請求項37に記載の低電力デバイス。

10

【請求項39】

クロックコントローラが、位相同期ループ(PLL)周波数倍器を含み、システムクロック信号と同期した高周波クロック信号を提供する、請求項38に記載の低電力デバイス。

【請求項40】

複数のクロック信号が、システムクロック信号および高周波クロック信号から導かれる、請求項39に記載の低電力デバイス。

【発明の詳細な説明】

【0001】

本出願は、35U.S.C. § 119(e)の下で、2001年8月29日に出願されたアレンらの「デジタルベースバンドプロセッサ(Allen, et al., "DIGITAL BASEBAND PROCESSOR")」という名称の米国特許出願第60/315,655号の優先権を主張するものである。前記出願の全文を、本明細書に参照により組み入れる。

20

発明の分野

本発明は、プロセッサの電力消費の低減に関し、より具体的には、プロセッサのクロック周波数要求およびそれに対応する電圧要求を特定することによって、プロセッサに供給する電圧レベルを、処理状態および/または計算要求に基づいて、動的に制御する方法および装置に関する。

【0002】

発明の背景

30

電力消費および管理は、プロセッサ、デジタルデバイス、コンピュータシステムなどの開発者にとっての設計関心事である。セルラー電話、ラップトップコンピュータ、パーソナルデジタルアシスタント(PDA)、およびその他の携帯用およびハンドヘルド式デバイスなどのバッテリー給電デバイスにおいて、電力消費は、デバイスを再充電かつ/または代替電源に接続しなくてはならなくなる前に、デバイスが動作できる時間の長さに対して重要な因子になることがある。そのために、電力消費はこれらのデバイスの利用性に大きな影響を与える。

【0003】

コンピュータシステムおよび/またはデバイスによっては、電力制御によって2値の電力状態が供給されて、第1の電力状態がアイドルプロセッサに対応し、第2の電力状態がアクティブプロセッサに対応するものもある。しかしながら、デジタルデバイス中のプロセッサは、多様なアクティブ処理状態を有し、例えば、処理状態を支援するために異なる電力レベルを必要とする計算需要を伴うことがある。

40

しかしながら、従来式の電力制御方法は、プロセッサの異なる電力需要を考慮することができない。したがって、プロセッサの計算要求に応じて、デバイスは、そのプロセッサの計算タスクおよび/またはファンクションを実行するのに要する電力を超える、電力を消費している可能性がある。

【0004】

発明の概要

本発明の一実施態様は、少なくとも1つのプロセッサを有するシステムにおける動的電力

50

制御の方法を含み、この少なくとも 1 つのプロセッサは、複数の周波数で動作可能な、少なくとも 1 つのクロック信号を含む。前記方法は、前記少なくとも 1 つのプロセッサのクロック周波数要求を特定するステップと、前記クロック周波数要求を支援するための電圧要求を特定するステップと、前記クロック周波数要求に応じて、前記少なくとも 1 つのクロック信号を動作させるステップと、前記電圧要求に応じて、前記少なくとも 1 つのプロセッサに電圧を供給するステップとを含む。

【 0 0 0 5 】

本発明による別の一実施態様は、複数の周波数で動作する少なくとも 1 つのクロック信号を含むプロセッサを含む。該プロセッサは、前記少なくとも 1 つのクロック信号を受け取る 1 つまたは複数のクロック動作構成要素と、少なくとも 1 つの構成要素に結合されて、前記プロセッサのクロック周波数要求を決定するコントローラであって、前記プロセッサのクロック周波数要求に基づいて電圧要求を特定するとともに、前記クロック周波数要求および前記電圧要求によって定義される電力状態への遷移を順序づける、前記コントローラとを含む。

10

【 0 0 0 6 】

本発明による別の一実施態様は、プロセッサへの電力を動的に制御するコントローラをふくむ。該コントローラは、前記プロセッサのクロック周波数要求を示す情報を記憶する複数のレジスタと、該複数のレジスタに結合されたコンパレータであって、前記複数のレジスタに記憶された前記情報に基づいて電圧要求を特定するように構成された、前記コンパレータと、前記コンパレータに結合されたシーケンサであって、前記プロセッサを、前記クロック周波数要求および前記電圧要求によって定義される電力状態に遷移させるように構成された前記シーケンサとを含む。

20

【 0 0 0 7 】

本発明による別の一実施態様は、複数のクロック信号で動作する複数のクロック動作構成要素を有する少なくとも 1 つのプロセッサと、該少なくとも 1 つのプロセッサに、変更可能な電圧を供給するように適合された電源と、前記複数のクロック信号の周波数を制御するように適合されたクロックコントローラと、前記電源および前記クロックコントローラに接続された動的電力コントローラであって、前記少なくとも 1 つのプロセッサを監視して前記少なくとも 1 つのプロセッサのクロック周波数要求を特定するとともに前記クロック周波数要求に基づいて電圧要求を特定するように適合され、かつ前記電源および前記クロックコントローラを、前記クロック周波数要求および前記電圧要求によって定義される電力状態に遷移させるように構成された、動的電力コントローラとを含む、低電力デバイスを含む。

30

【 0 0 0 8 】

詳細な説明

多くのデバイス、特に複数のバッテリ給電デバイスにおいて、そのデバイスのプロセッサが過剰な電力を消費する時間を低減することが有利である。より低い電力状態においても、プロセッサの計算タスク、機能、および動作が実行可能であり、かつ / または処理需要が満足されるときに、プロセッサは、過剰な電力を消費していると考えられる。「プロセッサ」の用語は、論理動作、計算タスク、制御機能などを実行する、任意の装置を全般的に意味するものである。プロセッサは、1 つまたは複数のサブシステム、構成要素、および / または他のプロセッサを含むことがある。プロセッサは、通常、クロック信号を使用してデータをラッチし、論理状態を前進させ、かつ / または順序づけし、計算および論理動作を同期させ、かつ / またはその他のタイミング機能を提供する、様々な論理構成要素を含む。

40

【 0 0 0 9 】

本出願者は、デバイスの電力消費は、デバイスのプロセッサに供給される電圧の 2 乗に関係し、プロセッサが動作する周波数に比例することを見出した。デバイスの電力消費は次のように表すことができる。

$$P_D = c V^2 F \quad (式 1)$$

50

ここで、

$V$  = デバイスに供給される電圧（すなわち、 $V_{dd}$  と  $Gnd$  の差）、

$F$  = 周波数（例えば、デバイスのクロック周波数）、

$c$  =  $V$  および  $F$  で動作する回路によって決まる定数である。

【0010】

さらに、本出願者は、プロセッサを動作させるのに要する電圧は、クロック周波数またはプロセッサに供給かつ分配されている周波数の関数であることを認識した。したがって、デバイスの電力消費を低減する1つの方法は、プロセッサに供給されるクロック信号の周波数を動的に調整することによって、プロセッサのクロック周波数要求を反映する方法である。

「クロック周波数要求」という用語は、プロセッサのタスク、機能、および／または計算要求を支援するのに要する、プロセッサに供給されるクロック周波数またはクロック周波数の組を、全般的に意味する。一般に、クロック周波数要求より低い周波数を有するクロック信号（単数または複数）は、論理ゲート、フリップフロップ、その他のクロック動作回路、およびクロック信号が供給される構成要素を動作させるのに十分ではなく、かつ要求される時間内にタスクを完了するには不十分であり、かつ／またはプロセッサの1つまたは複数の動作を実行することができない。

【0011】

上述のように、プロセッサが必要とする電圧は、プロセッサに提供され、かつ分配されるクロック周波数またはクロック周波数の組（すなわち、クロック周波数要求）の関数とすることができる。そのために、プロセッサの計算需要が低いときには、プロセッサのクロック周波数要求は低くてもよい。したがって、クロック周波数要求を支援するのに必要な電圧、すなわち電圧要求を、それに応じて低減することができる。

【0012】

「電圧要求」という用語は、所与のクロック周波数要求を支援するために、プロセッサに供給される電圧のレベル（単数または複数）を全般的に意味する。特に、電圧要求は、クロック動作構成要素に誤動作（例えば、メモリアクセス障害、タイミング違反、重要な速度バスの遅延など）を起こさせることなく、クロック周波数要求に応じて、プロセッサの様々なクロック信号をドライブするのに十分な、電圧値またはレベルを示す。あるクロック周波数要求を支援する電圧レベルは多数（例えば、ある最小電圧を超える電圧）あるが、電圧要求とは、一般に、クロック周波数要求の要件により厳密に合致する電圧レベルを意味する。

【0013】

プロセッサへの計算需要が時間とともに変化すると、クロック信号周波数とプロセッサに供給される電圧レベルの両方を低減する（すなわち、プロセッサがより低い電力状態に遷移することができる）機会が生ずることがある。すなわち、デバイスの電力消費は、プロセッサの処理要求を反映して動的に調整することが可能である。したがって、本発明による一実施態様は、プロセッサのクロック周波数要求を同定し、かつ、この同定されたクロック周波数を支援するためにプロセッサに供給される電圧を調整することを含む。

【0014】

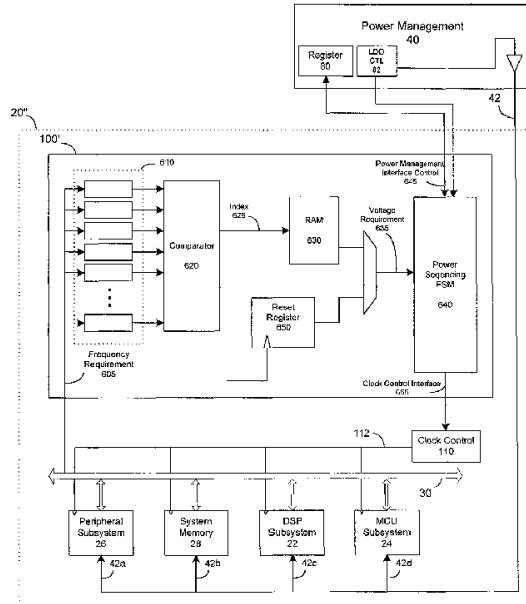

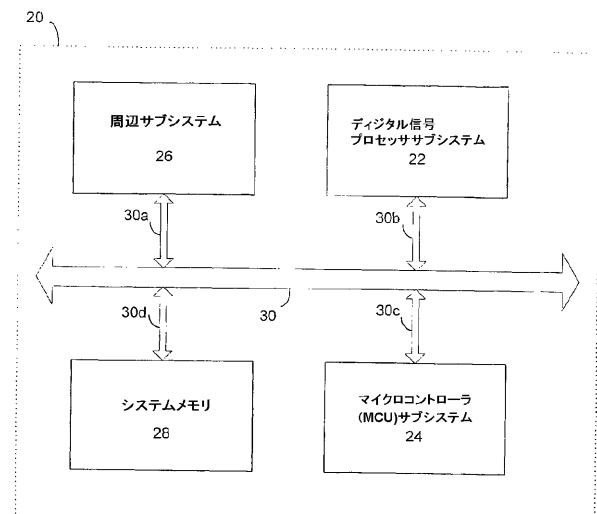

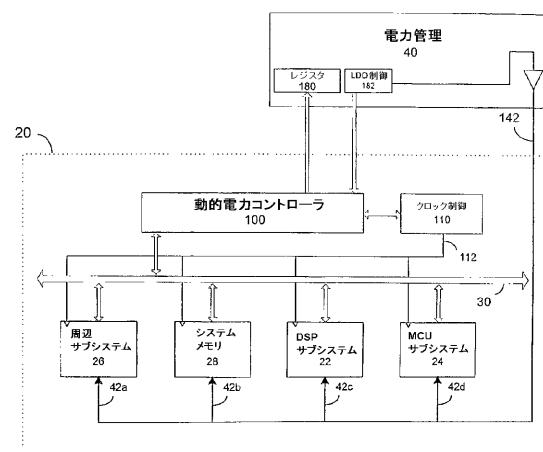

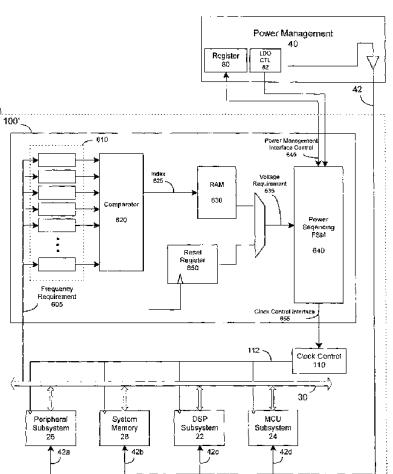

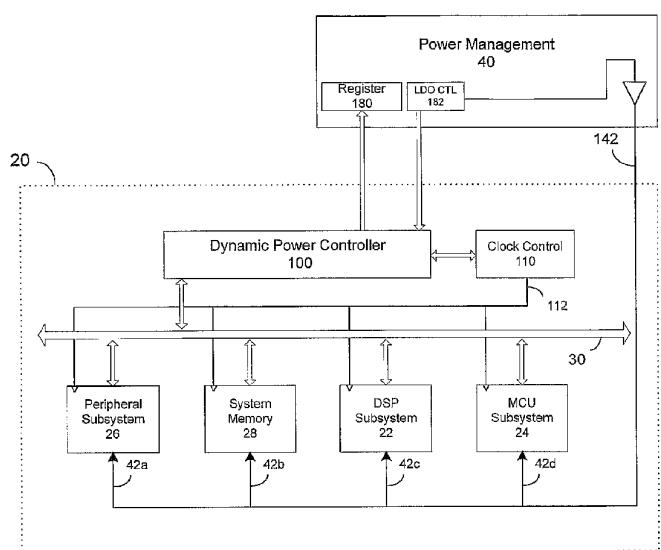

図1は、例示的なプロセッサ20のブロック図を示す。プロセッサ20は、例えば、单一半導体チップ上に製作することができる。プロセッサ20は、デジタル信号プロセッサ（DSP）サブシステム22、マイクロコントローラ（MCU）サブシステム24、システムメモリ28、および周辺サブシステム26を含む。これらのプロセッサの様々なサブシステムは、オペランドおよび命令、アドレスおよび／または制御信号などの、様々な構成要素間でデータを伝達および／または転送するための、システムバス30に接続されている。

【0015】

DSP22には、高速デジタル信号プロセッサを含めることができる。デジタル信号プロセッサの動作には、リアルタイム性能、計算集中型であり、かつしばしば時間が重要

10

20

30

40

50

因子となるタスク、頻繁なメモリアクセスなどの特徴がある。MCUサブシステム24は、例えば、様々な制御機能、座標系事象、実行システムソフトウェアなどを実行するとともに、DSPよりも低いクロック周波数で動作することができる。システムメモリ28は、プロセッサ20の様々なサブシステムが共有するメモリリソースを提供する、RAMのようなオンチップメモリとすることができます。周辺サブシステム26には、プロセッサが、オフチップデバイスまたはその他のプロセッサと通信するために必要な、様々なインターフェイスおよびロジックを含めることができます。例えば、周辺サブシステム26は、オフチップ電力管理チップと通信するか、またはオフチップメモリにアクセスすることができます。さらに、周辺サブシステムには、シリアル、赤外線通信（IrDA）、ユニバーサルシリアルバス（USB）、SIMインターフェイスなどの、様々な通信標準をサポートするためのインターフェイスを含めることができます。10

#### 【0016】

本明細書において、図1に示すプロセッサ、および類似の変形態様を、本発明の様々な態様を示し、それを実証するために用いるが、本明細書の全体を通して示す、すべての構成要素およびプロセッサのサブシステムは、単に例示的なものであることを理解すべきである。本発明は、プロセッサの実装における構成要素の数、タイプまたは構成に限定されることも、またはそれによって限定されるものでもない。時間とともに変化するクロック周波数要求を有する、任意のデバイス、プロセッサおよび/または論理回路は、本発明の範囲に入るものと考えられる。

#### 【0017】

例として、DSPサブシステム22には、スクラッチメモリ、コプロセッサ、割込みコントローラ、専用バスなどを含む、多様な構成要素を含めることができます。DSPサブシステム自体の様々な構成要素は、独立の周波数要求を有することがある。同様に、MCUサブシステム24および周辺サブシステム26などの他のプロセッサ構成要素は、様々なクロック周波数要求を含むことがある。したがって、プロセッサのクロック周波数要求は、頻繁に変化する、すなわち、プロセッサのアクティブ状態は多数の動作モードを有する可能性がある。

#### 【0018】

したがって、プロセッサ20は、時間とともに変化するクロック周波数要求を有する可能性がある。例えば、動作モードによっては、DSPはアイドル状態にある可能性がある。そのために、ある種の計算タスクを実行するのにDSPが必要とする高周波クロック信号は、そのような動作モードにおいては必要ではないことがある。「動作モード」という用語は、プロセッサの特定のクロック周波数要求を発生させる、プロセッサの様々な構成要素の処理状態または処理状態の組を特徴づけるものである。一般に、動作モードとは、プロセッサの処理状態を特徴づけるものであり、処理状態において、異なる電力状態に遷移することが可能である。30

#### 【0019】

プロセッサに対して、それが必要とする様々なクロック信号を提供するために、本明細書においてはシステムクロックと呼ぶ、1つの低周波クロックが、クロック基準としてプロセッサに設けられることが多い。プロセッサが必要とする様々なクロック周波数は、システムクロックから生成されて、プロセッサのサブシステムおよび/または構成要素に適切に分配される。プロセッサが必要とする、さまざまなクロック周波数は、位相同期ループ（PLL）倍増器によって生成して、プロセッサの構成要素に分配するクロック信号が、共通基準クロックと同相となるようにすることができます。すなわち、プロセッサ中に分配されるクロック信号は、同期されている。40

#### 【0020】

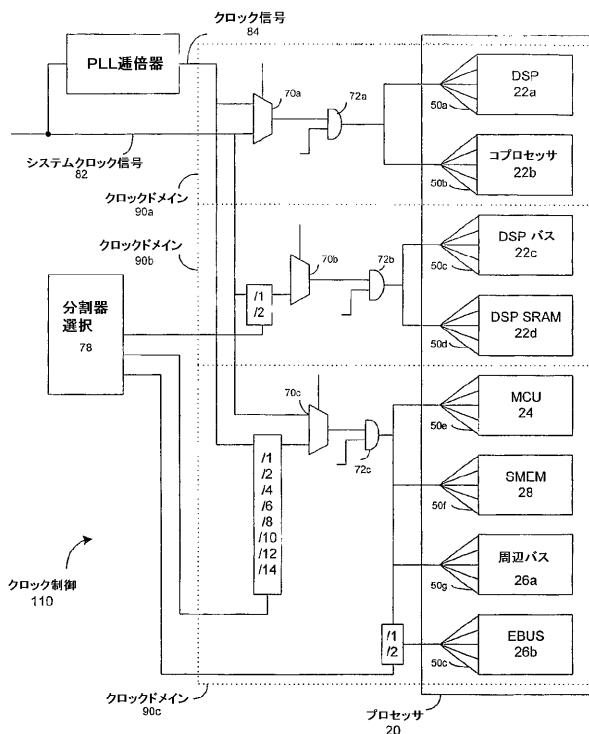

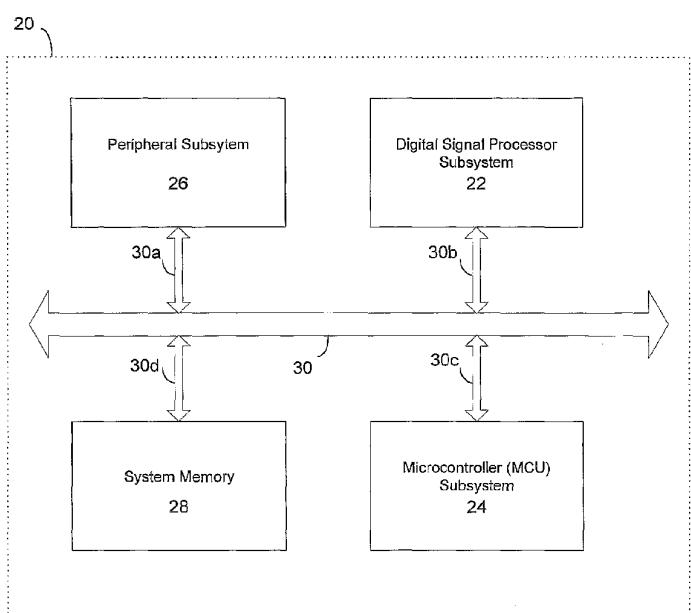

図2は、例えば、要求される周波数においてクロック信号をプロセッサ20の様々な構成要素に分配する、例示的なシステムクロッキング方式を示す。プロセッサ20の一部とすることのできる例示的な構成要素を図2に示してあり、それには、DSP22a、コプロセッサ22b、DSPバス22c（例えば、DSPサブシステム22を相互接続する専用

バス)、D S P S R A M 2 2 d (例えば、キャッシュ、スクラッチメモリ、など)、M C U 2 4 a、システムメモリ (S M E M) 2 8、周辺バス 2 6 a、および外部バス (E B U S) 2 6 b が含まれる。クロックドメインという用語は、クロック信号、およびそのクロック信号が通常、動作する 1 組の周波数を、全般的に意味する。一般に、あるクロックドメイン内で動作する構成要素は、それぞれのクロックドメインの、前記 1 組の周波数で動作する、1 つまたは複数のクロック動作要素 (例えば、論理ゲート、フリップフロップなど) を有することになる。1 つの構成要素は、複数のクロックドメインで動作することが可能であり、また逆に、1 つのクロックドメインは、複数の構成要素にサービスを行うことができる。

## 【0021】

10

プロセッサ 2 0 が必要とする様々なクロック信号およびクロック信号周波数は、クロック制御 1 1 0 の構成要素によって供給、分配される。特に、クロック制御 1 1 0 は、システムクロック信号 8 2 およびシステム P L L 適倍器 1 1 4 を含む。システムクロック信号 8 2 、または単にシステムクロックは、プロセッサに分配される様々な他のクロック信号を同期する基準として提供される。システム P L L 適倍器 1 1 4 は、システムクロック信号 8 2 を受け取り、高周波クロック信号 8 4 を提供して、それをシステムクロック信号と同期してロックする。通常、クロック信号 8 4 は、システムクロックのいくつかの倍数である。

## 【0022】

20

図 2 は、システムクロック信号 8 2 および P L L クロック信号 8 4 から生成される 3 つの主要なクロックドメインである、クロックドメイン 9 0 a、クロックドメイン 9 0 b 、およびクロックドメイン 9 0 c を示す。プロセッサ 2 0 の構成要素は、これらのクロックドメイン内で動作する。例えば、D S P 2 2 a およびコプロセッサ 2 2 b は、クロックドメイン 9 0 a で動作が可能である。D S P バス 2 2 c および D S P S R A M は、クロックドメイン 9 0 b 内で動作が可能である。M C U 2 4 a、S M E M 2 8 、周辺バス 2 6 a 、および外部バス (E B U S) 2 6 b は、クロックドメイン 9 0 c 内で動作が可能である。各クロックドメイン内のクロック信号は、様々な選択、分割、およびゲート論理によって提供されて、複数のクロックツリー 5 0 a ~ 5 0 h を介してプロセッサの構成要素に分配される。例えば、クロック制御 1 1 0 は、クロックドメインのそれぞれにマルチプレクサ (例えば、それぞれマルチプレクサ 7 0 a、7 0 b、および 7 0 c) を含み、これらのマルチプレクサは、対応するクロックドメインにおいて構成要素を動作させるためにクロック信号 8 4 が必要かどうかを独立して選択することができる。あるいは、クロック信号 8 4 をバイパスして、システムクロック信号 8 2 を、プロセッサの適当な構成要素に供給することができる。

30

## 【0023】

さらに、クロック制御 1 1 0 は、プロセッサのクロック周波数要求に合致させる目的で、プロセッサの構成要素に低い周波数を提供するために、クロック信号 8 4 の周波数を分割することができる。特に、分割器 6 2 および 6 4 は、クロック信号 8 4 の周波数を、周波数において低減することを可能にする。例えば、分割器 6 2 は、システム P L L 適倍器からのクロック信号が選択されるとき、クロックドメイン 9 0 b 内で動作するクロック動作構成要素に、クロック信号 8 4 の半分の周波数を有するクロック信号を提供することができる。同様に、分割器 6 4 は、クロックドメイン 9 0 c 内で動作しているクロック動作構成要素に、2、4、6、8、10、12 および 14 の倍数で減少させた周波数を有するクロック信号を供給することができる。分割器 6 2、6 4 は、例えば、N 分割カウンタ (divide-by-n counter) 、またはクロック信号の周波数を低減するための、それと等価な構成要素とすることができます。それぞれのクロックドメインに対して選択される、様々な分割器係数 (divider factor) を、例えば分割器選択 (divider select) 6 6 によって選択することができる。

40

## 【0024】

図に示すクロッキング方式において、電力が消費されている複数の段階がある。システム

50

P L L 遅倍器 114 には、例えば、クロック信号 84 を生成するために、電圧制御発振器 (VCO) を含めることができる。当該技術においては知られているように、電圧制御発振器では、発振器に電圧が供給されて、供給された電圧に比例する周波数を有する信号を生成する。したがって、クロック信号 84 を生成するのに消費される電力は、生成されている周波数に比例する。

【0025】

さらに、プロセッサの様々なクロック動作回路、論理ゲート、フリップフロップなどにクロック信号を提供するために、プロセッサの構成要素および／またはサブシステム内に、クロック分配ツリーまたは単にクロックツリーを設けてある。例えば、クロックツリー 50a は、クロックドメイン 90a のクロック信号をドライブして、それを D S P 22a の低レベル構成要素に分配する。同様に、クロックツリー 50e は、クロックドメイン 90c のクロック信号をドライブして、それを M C U 24a の低レベル論理構成要素に分配する。様々なクロックツリーに充電するためには電力が必要であり、したがって、関連する構成要素がアイドル状態にあるときにクロックツリーを動作不能にすれば、電力を節約することができる。さらに、より細い細分性 (granularity) で電力消費を制御するため、すなわち、クロックツリー分配ネットワークのある部分のゲートを閉じるために、さらなるクロックゲート論理を、クロックツリー内に含めることができる。

【0026】

そのように、プロセッサのクロック周波数要求を認識することによって、クロック制御 100 は、過剰なクロック周波数が生成されているときに、その間隔を低減するように周波数分配を構成することができる。さらに、クロック制御 110 は、プロセッサのクロック周波数要求に応じて、様々なクロックツリーまたはクロックツリーの部分の動作不能化を制御することができる。

図 2 に示すクロッキング方式は、単に例示的なものであり、プロセッサが必要とする様々なクロック信号を制御し、プロセッサの構成要素および／またはサブシステムに分配することのできる、1つの方式を示すことを意図するものであることを理解すべきである。しかしながら、当業者であれば、特定の組のクロッキング要求を満足する、様々なクロッキング方式を思いつくであろう。例えば、システムクロックは、P L L 遅倍器が供給するクロック信号で多重化された状態で示してある。しかしながら、システムクロックは、P L L クロック信号と独立した別個のクロックドメインと考えて、分配することもできる。システムクロッキング方式に対する特定の設計選択は、限定的なものではなく、様々な変更形態、修正形態、および改善形態を、本発明の範囲内で考慮することができる。

【0027】

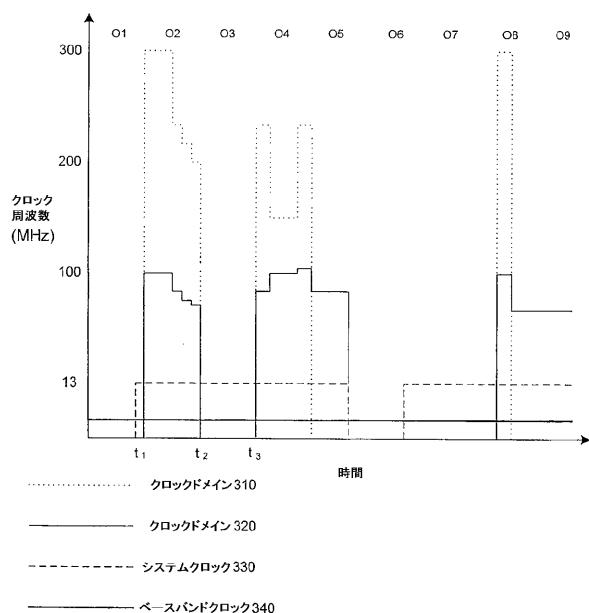

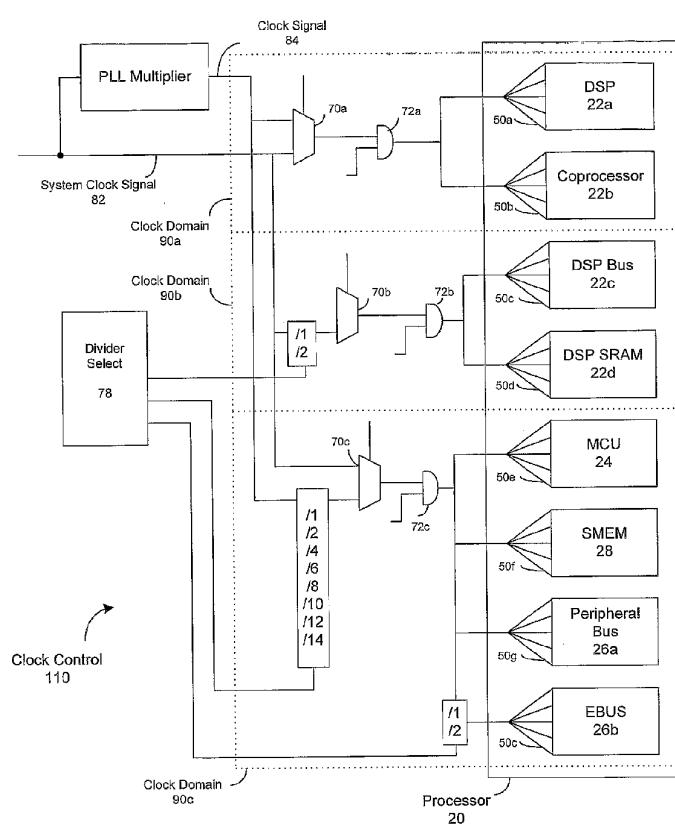

図 3 は、プロセッサに分配された様々なクロック周波数の、時間による変化を示す図である。プロット 300 は、あるベースバンドプロセッサのシステムクロッキング方式における、4つのクロックドメインの例示的な周波数値が、時間とともに変化するのを示す。図 3 に示す例示的なクロック周波数要求関数を生成するベースバンドプロセッサは、図 1 に示すプロセッサ 20 と類似のものでもよい。点線で示したクロックドメイン 310 および、実線で示したクロックドメイン 320 は、それぞれ図 2 のクロックドメイン 90a および 90c と同等にすることができる。破線で示すクロックドメイン 330 は、例えば、システムクロックドメインとすることができる。さらに、ベースバンドプロセッサは、太線で示すベースバンドクロックドメイン 340 を含み、プロセッサの適当な構成要素にベースバンドクロックを供給する。無線通信に使用されるプロセッサは、低周波ベースバンドクロックを介して動作する、外部デバイス、特に遠隔デバイスと同期されることが多い。

【0028】

プロット 300 上部の横方向につけてあるラベルは、01 から 09 で示した一連の動作モードである。この動作モードは、任意の数の方法で区別することができる、プロセッサの設計と所望の細分性のレベルに依存することを理解すべきである。例えば、クロックドメインの 1 つにおける、周波数のそれぞれの変化を、異なる動作モードと考えることができる。

10

20

30

40

50

動作モード 0 1 において、唯一の動作可能なクロックは、ベースバンドクロック 3 4 0 である。その他のすべてのクロックは、動作不能にすることができる。例えば、ベースバンドプロセッサがセルラー電話で使用されている場合には、例えば動作モード 1 は、セルラー電話がオンであるが、使用されていないとき（すなわち、スタンバイモードにおいて）に発生することが考えられる。例えば、ある時刻  $t_1$  において、DSP の処理電力を要求する事象が発生する。このような場合には、システムクロック 3 3 0 は動作可能にされ、PLL に供給されて、このPLL が最大クロック速度を生成する。第 2 の動作モードへの遷移をトリガーする事象には、クロックドメイン 3 1 0 および 3 2 0 における構成要素からの処理が必要となる可能性がある。そのような場合には、すべてのクロックツリーを動作可能にすることができる。時間とともに性能要求が低下し、クロック周波数を低減できる（例えば、システムPLL 通過器から生成されるクロック信号の周波数が低減できる）可能性がある。

10

20

30

40

#### 【 0 0 2 9 】

時刻  $t_2$  において、クロックドメイン 3 1 0 より 3 2 0 を必要とするタスク（単数または複数）が完了すると、プロセッサの計算要求が低下する。このような場合には、システムPLL 通過器はバイパスされて、システムクロックおよびベースバンドクロックだけが動作可能にされる。時刻  $t_3$  において、処理要求によって、動作モード 0 4 に示すアクティブクロックドメインの構成がもたらされる、別の事象が発生する可能性がある。同様に、動作モード 0 5 ~ 0 9 は、図 2 に示す対応するクロック要求を発生させる、さらに別の処理状態を示す。

20

#### 【 0 0 3 0 】

したがって、計算需要が時間とともに変化すると、処理要求の低下によって、クロック信号周波数を低減できる機会がもたらされる。さらに、あるクロックドメインは、ある動作モード中には不十分であり、その結果関連するクロックツリーを動作不能にすることができる。変化するクロック周波数要求に応答して、プロセッサに供給される電圧は、クロック周波数要求の変化要求を支援するために調整することができる。このように、クロック周波数要求が低下すると、電圧要求を低減することができる。

30

40

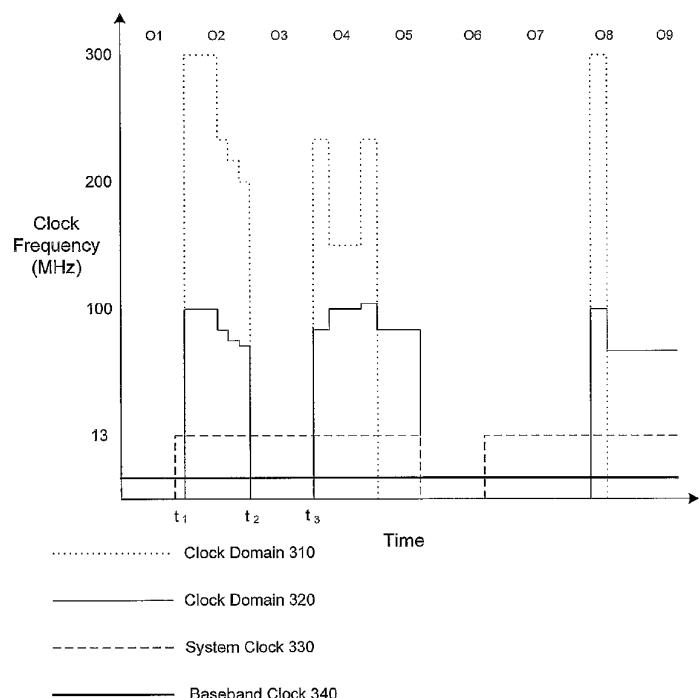

#### 【 0 0 3 1 】

本出願者は、プロセッサのクロック周波数要求を監視することによって、プロセッサに供給される電圧を動的に制御し、その結果として、プロセッサに要求を超える電圧が供給される、プロセッサの時間を短くすることができますことをつきとめて、それを理解した。図 4 は、動的電力制御（DPC）機能を有するプロセッサ 2 0 ' を含む、本発明による一実施態様を示す。説明の目的で、プロセッサ 2 0 ' には、図 1 に関係して示して記述したサブシステムを含めてある。

30

40

#### 【 0 0 3 2 】

プロセッサ 2 0 ' の動作中に、サブシステムに対する計算需要は、時間とともに変化する可能性がある。したがって、プロセッサのクロック周波数要求も、様々な構成要素およびサブシステムが異なる処理状態に遷移するにつれて、変化する可能性がある。動的電力コントローラ（DPC）1 0 0 は、プロセッサ 2 0 ' の様々なサブシステムと通信するために、システムバス 3 0 に接続することができる。動的電力コントローラ 1 0 0 は、代替方法として、適当な相互接続を有する共有レジスタなどの、その他の様々な方法によって、サブシステムと通信してもよい。

図 4 において、プロセッサ 2 0 ' は、オフチップ電力管理 4 0 によって電力を供給される。電力管理 4 0 は、オフチップで存在するように示してあるが、別の選択肢としては、プロセッサと同一の半導体チップ上に配置してもよい。電力管理 4 0 は、通常、電力を受け取る構成要素によって指定される電圧レベルを提供して、電力源とすることのできる、任意の構成要素とすることができる。例えば、電力管理 4 0 には、ある特定の電圧レベルを要求するために、アクセスして書き込むことのできる読み取り / 書込みレジスタを含めることができる。

50

#### 【 0 0 3 3 】

D P C 1 0 0 は、プロセッサに供給すべき電圧レベルを電力管理に示すために、レジスタ 1 8 0 に接続されている。電力管理は、例えば、低ドロップアウト ( L D O ) 電圧調節器とすることができる。電力管理は、L D O 制御 1 8 2 を含み、レジスタ 1 8 0 によって指定される電圧レベルが、安定して、供給ライン 1 4 2 に供給されるときを示すことができる。

さらに、D P C 1 0 0 はクロック制御 1 1 0 に接続されている。プロセッサ 2 0 ' は、例えば、図 2 に示すものと、実質的に同一のシステムクロッキング方式を有する。したがって、クロック制御 1 1 0 には、クロック信号をプロセッサの様々なサブシステムに分配するためには、様々な構成要素および論理ゲートを含めることができる。例えば、クロック制御 1 1 0 には、図 2 に示すような、システム P L L 遅倍器、バイパスマルチプレクサ、分割器選択 ( divider select ) 、ディセーブル論理 ( disable logic ) 、クロックツリーなどを含めてよい。

10

20

30

40

50

#### 【 0 0 3 4 】

クロック制御 1 1 0 には、システム P L L 遅倍器に結合されて、システム P L L によって出力される周波数を記憶する、書き込み可能レジスタを含めることができる。このレジスタは、代替的に、V C O に要求される電圧値を記憶し、所望の周波数、その所望の周波数を生成するのに要する入力クロック信号の倍数比、またはシステム P L L 遅倍器によって生成される高周波出力クロック信号の所望の周波数を表すその他の値を生成してもよい。さらに、クロック制御には、様々なクロックドメインにおいて、分割器の所望の分割を制御することのできる、レジスタまたはその他の制御手段を含めてよい。例えば、分割器選択には、所望の分割器係数を記憶するレジスタのバンクを含めることができる。さらに、クロック制御 1 1 0 には、様々なクロックドメインをゲートオフできるようにする論理、独立して動作不能にされるクロックツリー、および / または動作不能にされたクロックツリーの部分を含めることができる。

#### 【 0 0 3 5 】

D P C 1 0 0 は、プロセッサ 2 0 ' を監視して、プロセッサの現在クロック周波数要求を特定するために、構成要素および / またはサブシステムの処理状態を判定する。そのクロック周波数要求に応じて、D P C 1 0 0 は、クロック周波数要求を支援するのに必要な電圧レベルを特定する。次いで、D P C 1 0 0 は、プロセッサに供給される電圧を調整するように電力管理 4 0 に指令するとともに、プロセッサのクロック周波数要求によって様々なサブシステムおよび構成要素に与えられる周波数分配を提供するようにクロック制御 1 0 に指令する。

#### 【 0 0 3 6 】

コントローラ ( 例えば、動的電力コントローラ 1 0 0 ) は、専用ハードウェア ( 例えば、様々な回路、ブレプログラム論理配列、有限状態機械 ( F S M s ) など ) を用いるか、またはソフトウェア ( 例えば、マイクロコード ) を使用して、コントローラの様々な機能を実行するようにプログラムされた 1 つまたは複数のプロセッサを使用するなどの、多くの方法で実現ができるることを理解すべきである。本発明の様々な実施態様によるコントローラの実現には、ハードウェア、ファームウェア、およびソフトウェア指向要素を含めてよいことを理解すべきである。

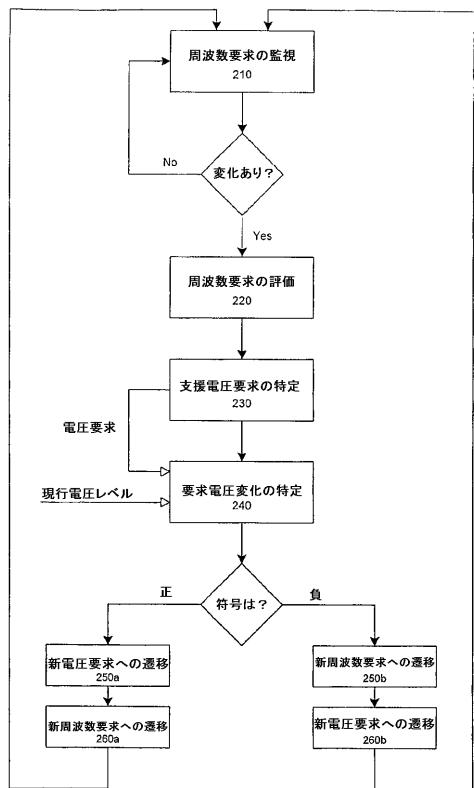

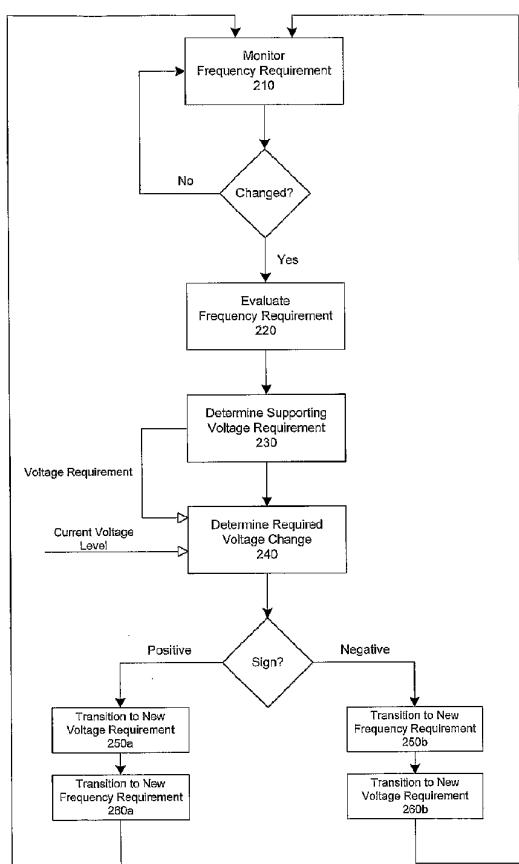

図 5 は、本発明によるプロセッサに供給される電力を動的に調整する一方法を示すフローチャートである。例えば、以下に記述する方法を、プロセッサ 2 0 ' への電圧供給を動的に制御するために、D P C 1 0 0 で使用することができる。

#### 【 0 0 3 7 】

ステップ 2 1 0 において、D P C はプロセッサのクロック周波数要求を監視する。クロック周波数要求の変化は、プロセッサに供給する電圧レベルを低減することができることを示すか、または新クロック周波数要求を支援するために、プロセッサの処理需要が追加の電圧を必要とすることを示す場合がある。したがって、ステップ 2 2 0 において、新しいクロック周波数要求を支援するのに必要な電圧要求を特定するために、クロック周波数要求が評価される。

例えば、クロック周波数要求は、そのクロックドメインで動作している構成要素の関数および／または計算タスクを実行するために各クロックドメインが必要とする、最小周波数を表すことができる。このようにして、DPCは、システムの電圧要求を特定するために、最大最小周波数値と呼ぶ、最大値を選択することができる。

#### 【0038】

プロセッサのクロック周波数要求から電圧要求を特定する他の方法は、当業者であれば思いつくであろうが、それは特定のプロセッサ実装のクロッキング方式に依存する。例えば、DPCは、電圧要求を特定するときに、新しいクロック周波数要求の下で、どのクロックツリーを動作不能にすることができるかを、考慮することができる。DPCはまた、電圧を特定するときに、クロック周波数要求の最大最小値以上のことを考慮することができる。所与のクロック周波数要求から電圧要求を特定するための様々な方法が、本発明の範囲に含まれると考えられる。10

ステップ230において、クロック周波数要求を支援するのに十分な電圧レベルが特定される。ステップ240において、プロセッサに供給されている現行電圧レベルが、ステップ240において特定される電圧レベルと比較されて、電圧要求を提供するのに必要な、要求電圧変化、またはデルタが特定される。

#### 【0039】

電圧変化の符号が正である（すなわち、電圧要求が現行電圧レベルよりも大きい）場合には、ステップ250aおよび260aで示す、高電力状態に遷移するための一連の事象が続く。すなわち、電圧要求によって示される電圧レベルが、最初に遷移させられる。例えば、DPCは、プロセッサの電圧要求に合致するように供給電圧を増加させるように電力管理に要求することができる。新電圧レベルに完全に遷移した（すなわち、新供給電圧が安定した）後に、クロック周波数要求によって示される新しい周波数分配が、プロセッサの様々なサブシステムに適用される。例えば、DPCは、クロック周波数要求に応じたクロック信号をプロセッサに分配するようにクロック制御に指令することができる。20

#### 【0040】

電圧変化の符号が負である（すなわち、電圧要求が電圧レベルよりも低い）場合には、ステップ250bおよび260bで示す、低電力状態へ遷移するための一連の事象が続く。すなわち、クロック周波数要求によって示される周波数分配は、最初に、プロセッサのサブシステムおよび構成要素に供給される。プロセッサが、新クロック周波数要求に応じて動作しているときに、プロセッサに供給される電圧は、ステップ230で特定される電圧要求によって示される電圧レベルに低減される。30

#### 【0041】

電圧遷移および周波数遷移は、プロセッサの誤動作を回避するために、上記のような順序に並べることができる。例えば、メモリにアクセスするための、クロック周波数要求を考えてみる。一定電圧に対して周波数が増大すると、メモリアクセスに障害が発生する点がある場合がある。したがって、電力状態遷移中の、そのような潜在的な問題を回避するために、高電力状態に移行するときには、クロック周波数を増加させる前に、電圧を増大させることができる。低電力状態に移行するときには、プロセッサに供給される電圧を低減する前に、周波数を最初に低下させることができる。40

#### 【0042】

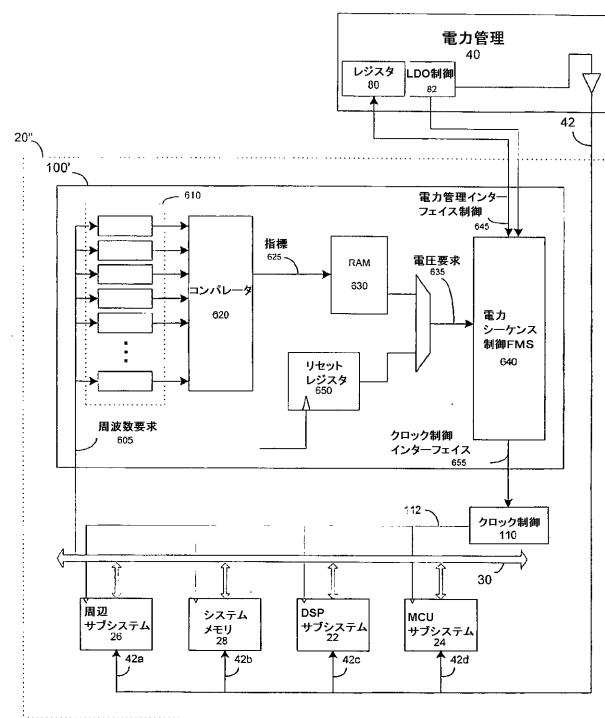

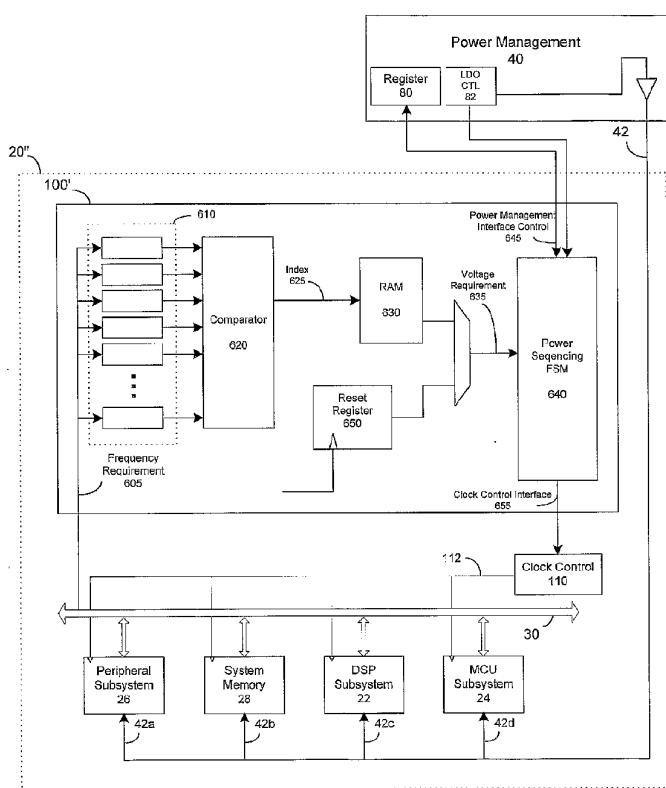

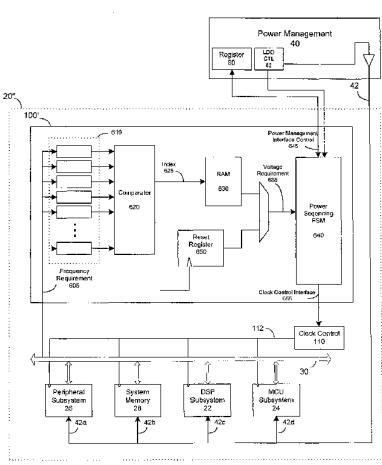

図5と関連して記述した方法は、多くの方法で、また様々な設計および実装によって実現することができる。図6は、本発明によるDPCの一実施例を示す。この略図は、動的電力制御に対する1つのハードウェア解決策を示す。DPC100'には、レジスタのバンク610、コンパレータ620、ランダムアクセスメモリ(RAM)630、電源シーケンス制御有限状態機械(FSM)640、およびリセットレジスタ650が含まれる。DSP100'は、プロセッサ20"のサブシステムを制御している状態で示してあり、このプロセッサには、わかりやすくするために、先述のサブシステム、構成要素、クロッキング方式を含めてある。電力は、電力管理40によってプロセッサに供給される。

レジスタ610は、プロセッサ20"のクロック周波数要求を示す情報を記憶する。例え50

ば、レジスタ 610 は、各クロックドメインに対して必要な周波数値を記憶してもよい。さらに、あるクロックドメイン内で動作する各サブシステムと関連するレジスタを設けて、クロックドメインのそれぞれから、各サブシステムによって要求されるクロック周波数を示してもよい。レジスタの特定の数、配設および関連は、設計選択の問題であり、プロセッサ周波数要求を適切に示す変更はすべて、本発明の範囲内であると考えられる。

#### 【 0043 】

コンパレータ 620 は、レジスタバンクに示されるクロック周波数の分配を支援するために必要な電圧を特定するために、レジスタ 610 内のレジスタに記憶された周波数値を比較する。電圧要求を特定する一方法は、レジスタバンクから最大の周波数を選択する（すなわち、コンパレータは、プロセッサのクロック周波数要求から最大最小値を選択する）ことによって、電圧要求を特定する方法である。例えば、この周波数値は、システム PLL 適倍器によって提供されるクロック信号が要求する周波数を指示してもよい。次いで、システム PLL 適倍器の信号生成器（例えば、電圧制御発振器）が指示された周波数を生成するのに必要とする電圧レベルを、少なくとも部分的に、電圧要求の基本とすることができる。

#### 【 0044 】

例えば、RAM 630 には、プロセッサの様々なクロック周波数要求を支援するのに必要な電圧値を含む、ルックアップテーブルを記憶してもよい。そうすれば、コンパレータ 620 は、RAM 630 内の場所に、選択された周波数値をマッピングするか、またはレジスタ 610 に示される周波数要求をマッピングすることができる。RAM 630 から取得される電圧レベルは、プロセッサ周波数要求に関連する電圧要求に一致する。

ここで理解すべきことは、当業者であれば、ある特定のクロック周波数要求で動作しているプロセッサを支援する、電圧レベルを特定するために、クロック周波数要求を符号化する様々な方法を思いつくことである。プロセッサの設計、クロッキング方式、およびその他のプロセッサ要件および検討によって、クロック周波数要求から電圧要求への具体的なマッピング方式を導くことができる。しかしながら、これらの変形態は、本発明の範囲から逸脱するものではない。

#### 【 0045 】

RAM 630 から得られる電圧値は、次いで、電源シーケンス制御有限状態機械（FSM）に供給される。次いで、この電源シーケンス制御 FSM は、クロック周波数および電圧要求によって示される電力状態に、プロセッサを遷移させる。例えば、電源シーケンス制御 FSM は、プロセッサの電圧要求（例えば、RAM 630 から得られる電圧レベル）に合致させるのに必要な電圧変更の符号を判定するために、レジスタ 180 内に記憶された電圧値を読み取ることによって、プロセッサに供給されている現行電圧レベルを検査することができる。

#### 【 0046 】

電圧変化の符号が正の場合には、電源シーケンス制御 FSM は、最初に電力管理 40 に指令して、所望の電圧レベルを供給させる（すなわち、DPC100' が、レジスタ 180 に所望電圧レベルを書き込ませる）ことができる。電力管理 40 が、電圧レベルが遷移して、安定であることを示した（すなわち、電力管理 40 がライン 184 を介して電圧が安定であることを示した）後に、次いで、電源シーケンス FSM は、プロセッサのクロック周波数要求に合致させるために、様々なクロックドメインの周波数を増大させるように、クロック制御 110 に指令することができる。

例えば、電源シーケンス FSM は、クロック制御 110 に指令して、システム PLL 適倍器からのクロック信号出力の周波数を増大させることができる。代替手法としては、システム PLL 適倍器に対してどのクロック周波数を出力すべきかを示すレジスタに、電源シーケンス制御 FSM をアクセスさせることができる。

#### 【 0047 】

電圧変化の符号が負の場合には、電源シーケンス制御 FSM は、最初にクロック制御 110 に指令して、様々なクロックドメインのクロック周波数を低減して、プロセッサの周波

10

20

30

40

50

数要求を反映させることができ。一旦、周波数が低減されると、電源シーケンス制御 F S M は、電力管理に指令して、R A M から得られる電圧レベルに応じてプロセッサに供給される電圧を修正させることができる。このようにして、電力シーケンス F S M は、プロセッサの潜在的な誤動作を回避する順序に電力状態遷移が並べられることを保証する。

リセットレジスタ 6 5 0 は、スタートアップ / リセット中に、電力シーケンス F S M 6 4 0 に、適正な電圧を供給する。R A M 6 3 0 内に記憶される情報は、スタートアップ / リセットの間は信頼できない場合があるので、リセットレジスタ 6 5 0 は、リセット / スタートアップ、様々なブーツ事象、その他に関係するタスクを支援するために十分な電圧が、プロセッサに供給されることを保証する。このようにして、リセットレジスタ 6 5 0 に記憶される値（単数または複数）は、スタートアップ / リセット中にのみ選択できるようになる。

#### 【 0 0 4 8 】

レジスタバンク内の値の 1 つが変化するために、新しいクロック周波数要求を収容するために、電圧レベルを変更できるか、または変更すべきかを判定するために、コンパレータは、プロセッサのクロック周波数要求を再評価してもよい（例えば、コンパレータ 6 2 0 が、プロセッサが新しい電力状態に遷移できるかどうかを判定する）。レジスタ 6 1 0 のバンクには、例えば、プロセッサ（例えば、D S P またはM C U ）上で実行されるソフトウェアによって書き込んでもよい。例として、プロセッサ 2 0 ” を参照して、D S P が、3 0 0 M H z 周波数クロックを必要とする高優先順位タスクを処理している動作モードを考える。M C U は、6 0 M H z 周波数クロックを必要とするタスクを同時に処理している。

#### 【 0 0 4 9 】

このような場合に、D S P および / またはM C U 上で実行中のソフトウェアによって、様々なクロックドメインが必要とする周波数を、レジスタバンク 6 1 0 内の関連するレジスタ中に書き込んでもよい（例えば、クロックドメイン 4 1 0 に関連するレジスタが、周波数値 3 0 0 M H z を記憶し、クロックドメイン 3 2 0 に関連するレジスタが、周波数値 6 0 M H z を記憶してもよい）。

コンパレータ 6 2 0 は、最大最小選択法を実現することができる。したがって、コンパレータは、3 0 0 M H z 周波数値を、プロセッサの電圧要求を特定するための基本として選択することになる。R A M 6 3 0 に入れる指標を、最大最小値から取り出し、例えば 3 0 0 M H z の値を 1 . 5 ボルトの電圧値を記憶するメモリの場所にマッピングすることができる。このようにして、電力管理は、プロセッサの現行クロック周波数要求を支援するために、プロセッサに 1 . 5 ボルトを供給するようにすることができる。

#### 【 0 0 5 0 】

ある時点において、プロセッサは、高優先順位のタスクを完了して、プロセッサの計算需要が低下することがある。例えば、現行計算の処理要求を満たすのに、D S P が、わずかに 1 8 0 M H z を必要とするだけになる場合がある。例えば、D S P 上で実行中のソフトウェアによって、このように低下したD S P のクロック周波数要求を特定して、適当なレジスタに新しい周波数値を書き込むことができる。次いで、D C P 1 0 0 ” が、レジスタバンクに記憶された値の 1 つにおける変化を検出する。このようにして、コンパレータ 6 2 0 が、プロセッサのクロック周波数要求を再評価して、新規の最大最小周波数値が 1 8 0 M H z であることを特定することができる。この新しい値が、例えば、R A M 6 3 0 の 1 . 2 ボルトの値にマッピングされる。

#### 【 0 0 5 1 】

電源シーケンス制御 F S M は、この新電圧値を受け取り、プロセッサの新クロック周波数要求を支援するのに必要な電圧要求を反映するには、負の電圧遷移が必要であると判定する。このようにして、電源シーケンス制御 F S M は、遙倍器に、1 8 0 M H z クロック信号を供給するために、システムP L L 遙倍器の遙倍器選択値を低減するように指令することができる。P L L によって低減された周波数が供給された後に、電源シーケンス制御 F S M は、1 . 2 ボルトの値をレジスタ 1 8 0 中に書き込むことができる。次いで、電力管

10

20

30

40

50

理 4 0 が、この値を読み取り、新規な低減された電圧レベルをプロセッサに供給する。このようにして、プロセッサは、プロセッサのクロック周波数要求を反映して低減された電力状態で、動作することになる。

#### 【 0 0 5 2 】

コンパレータは、最大最小値に基づいて、ルックアップテーブル中の指標を特定する必要はない。例えば、コンパレータは、様々な方法で、レジスタバンク内に記憶された様々なクロック周波数を考慮することができる。例えば、クロックドメイン 3 1 0 の 1 8 0 M H z クロック周波数は、低電圧、例えば 0 . 0 9 ボルトで支援することができる。しかしながら、他のクロックドメインからの要求による理由から（例えば、クロックドメイン 3 2 0 に対して 7 5 M H z 、および 2 6 M H z システムクロック分配）、0 . 9 ボルトは、プロセッサのクロック周波数要求を満たすのに十分ではない場合もある。コンパレータを、クロック周波数要求が、0 . 9 ボルトで支援できないことを認識するように構成し、そのような場合には、最大最小値自体は低電圧によって支援できるとしても、上記のクロック周波数要求を 1 . 2 ボルトの電圧要求にマッピングするようにしてもよい。

#### 【 0 0 5 3 】

将来の時点において、M C U はそのタスクを終了して、現行処理状態の計算要求に合致するために 4 5 M H z クロックを必要とするだけとなることがある。例えば、M C U 上で実行中のソフトウェアによって、新規の処理状態を特定して、新規の周波数値を適当なレジスタに書き込むことができる。

レジスタ値の変化に応答して、コンパレータは、最大最小値が同一（例えば、1 8 0 M H z ）のままではあるが、プロセッサのクロック周波数要求が修正されたことを判定することができる。例えば、新規のクロック周波数要求は、0 . 9 ボルトの電圧レベルにマッピングすることができる。次いで、電源シーケンス制御 F S M は、上記の順序に従って、低電力状態に遷移することができる。しかしながら、M C U が必要とする周波数（例えば、4 5 M H z ）の変化は、適当なクロックドメインの分割器係数を調整することによって生成することができる。その場合には、P L L の遅倍器選択値は、ある電力状態遷移においては、低減することはできない。

#### 【 0 0 5 4 】

将来のある時点において、D S P は、別の高優先順位タスクを処理する必要があるかもしれない。そのような場合には、ソフトウェアによって、D S P の新しいクロック周波数要求、例えば 2 4 0 M H z を特定し、この値を適当なレジスタに書き込むことができる。次いで、コンパレータが、プロセッサのクロック周波数要求を再評価し、プロセッサの現行クロック周波数を支援するために、新規の電圧要求が必要であると判定する。次いで、コンパレータが、メモリ中に索引をつけて、対応する電圧値、例えば 1 . 5 ボルトが、電源シーケンス制御 F S M に送出される。電源シーケンス制御 F S M は、新規の電圧要求を満足させるためには、電圧レベルの正の変化が必要なことを判定する。

#### 【 0 0 5 5 】

したがって、F S M は、プロセッサに供給される電圧を遷移させるために、最初に、レジスタ 1 8 0 に新規の電圧値を書き込むことができる。電力管理 4 0 がその値を読み取り、電圧が遷移して、安定化したことを示した後に、F S M は、高クロック周波数要求を提供するために、シーケンスロック制御を開始する（例えば、電源シーケンス制御 F S M は、システム P L L 遅倍器によって生成されるクロック信号の周波数を増大させるように、遅倍器選択値を修正するか、またはクロック制御に指令してそれを修正させることができる）。

その他の因子および／または処理条件も、特定のクロック周波数要求を支援するために必要な電圧レベルに影響を与えることがある。例えば、全体に動作不能にすることのできるクロックツリーの数は、電圧要求に影響を与える可能性がある。そのような場合には、D P C 1 0 0 ” は、周波数値以上のものを考慮することができる。例えば、D P C は、クロックドメイン内で、どのクロックドメインまたはどのクロックツリーが、所与の動作モード中に動作不能にできるかを考慮することができる。

10

20

30

40

50

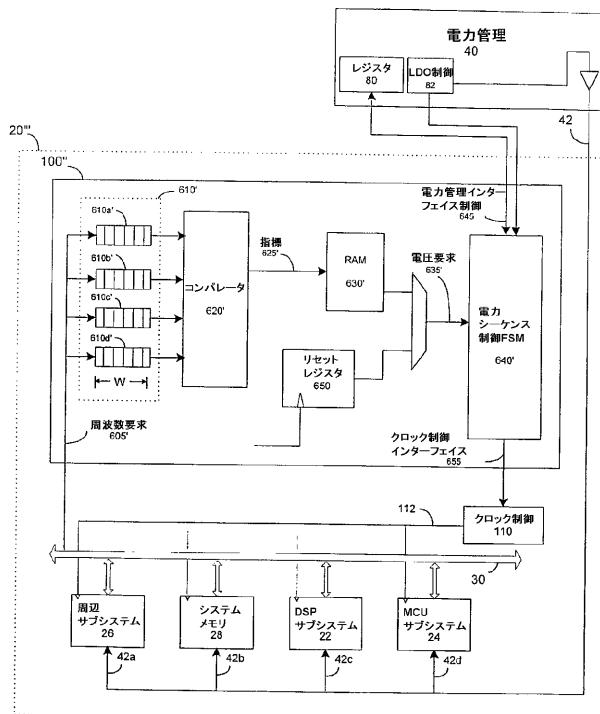

## 【 0 0 5 6 】

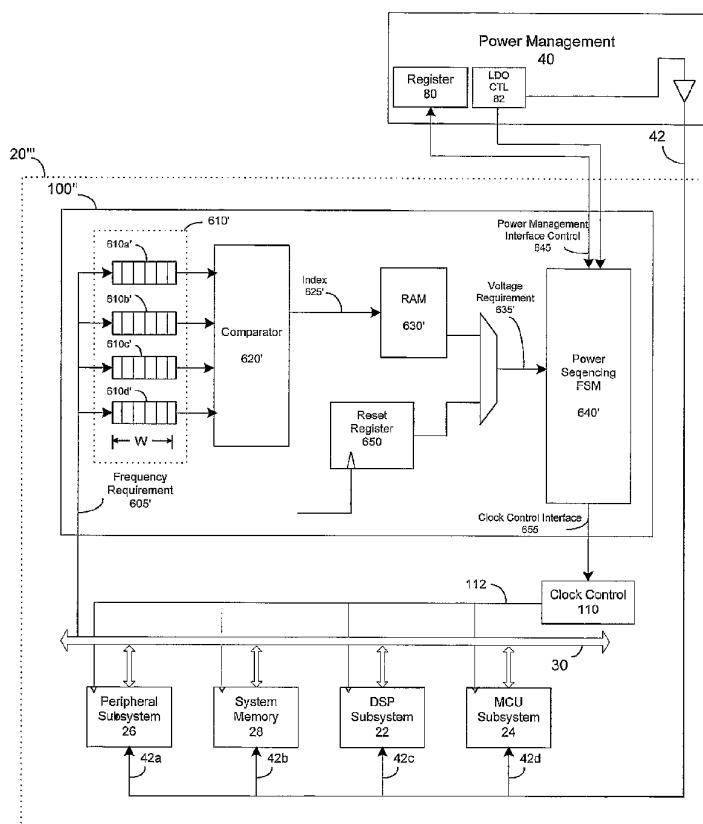

図 7 は、本発明による別の実施例を示す。レジスタ 610' は、プロセッサの周波数要求を示す情報を記憶する。レジスタ 610' には、例えば、プロセッサの主サブシステムの各々に対するレジスタを含めてもよい。各レジスタは、関連するサブシステムが、特定のクロック信号を必要とするか、または特定のクロックドメインのクロック信号を必要とするかについての、2 値表示を記憶することができる。したがって、レジスタ 610' の幅 W は、プロセッサに供給、かつ分配されるクロック信号の数に関係する。

## 【 0 0 5 7 】

例えば、レジスタ 610' は、DSP サブシステムの周波数要求に対応すると仮定する。サブシステムの計算需要に応じて、DSP は、現行処理需要に合致するためには、どのクロック信号を必要とするかを示すことができる。例えば、DSP は、アイドル状態への遷移の前に、レジスタ 610' の各ビットにゼロを書き込むことによって、そのようなクロック周波数要求を示すことができる。代替手法として、例えば、DSP がアイドル状態においても、なおシステムクロック信号を必要とする場合には、DSP は、システムクロックに対応するビットにおいて 1 を示すことができる。プロセッサの他方のサブシステムは、同様に、特定の動作モードの関数および / または計算タスクを実行するために、どのクロック信号が必要であるかを示すことになる。

## 【 0 0 5 8 】

そのような場合に、コンパレータ 620' は、レジスタ 610' 内に記憶される周波数要求によって示されるクロック信号構成を支援する電圧レベルを記憶するメモリ内の場所に、2 値クロック指示をマッピングすることができる。一実施例においては、各クロックドメインは、サブシステムが、それが必要であることを示すときに、そのクロックドメインが動作する関連する周波数を有してもよい。例えば、最大クロック速度は、DSP サブシステムが、例えば、図 3 に示すクロックドメイン 310において、クロック信号を必要とすることを示すときに、最大クロック速度を考慮することができる。

## 【 0 0 5 9 】

この実施態様の一態様においては、コンパレータ 620' は、レジスタ 610' によって示されるクロック信号構成を考慮し、必要なクロック周波数を特定する、ソフトウェアを含む。例えば、MCU サブシステムおよび DSP サブシステムの両方が、ドメイン 310 におけるクロック信号を必要とする場合に、ソフトウェアは、周波数要求は DSP によって誘導されることを認識することができる。MCU が、クロックドメイン 310 内のクロック信号が必要なことを示すが、DSP は、それが必要でないことを示す場合には、ソフトウェアは、MCU がその要求を誘導することから、クロック信号の周波数を低減することができることを判定することができる。次いで、ソフトウェアによって判定される周波数要求を、クロック周波数要求を支援することのできる電圧レベルを記憶するメモリ内の場所にマッピングすることができる。

## 【 0 0 6 0 】

代替手法として、レジスタ 610' に、各サブシステムに対して一対のレジスタを含めてもよい。第 1 のレジスタには、プロセッサ内の各クロック信号に対して、サブシステムが能動状態にあるときにクロック信号を必要とするかどうかを示す、ビットを含めてもよい。第 2 のレジスタには、プロセッサ内のクロック信号に対して、サブシステムがアイドル状態にあるときにクロック信号を必要とするかどうかを示す、ビットを含めてもよい。実施例によっては、RAM 630 は、プログラマブルロジックアレイで置き換えることができる。例えば、コンパレータは、プロセッサのクロック周波数要求に関して提供される情報を、符号化入力に（例えば、レジスタバンク、メモリなどに記憶された状態で）マッピングすることができる。プログラマブルロジックアレイを、クロック周波数要求を支援するのに必要な電圧レベルを示す、符号化入力からの出力を供給するようにプログラムすることができる。クロック周波数要求から PLA への入力への符号化は、前述のように、プロセッサの様々な設計上の考察に依存する。

## 【 0 0 6 1 】

10

20

30

40

50

電力制御における高い細分性のレベルを達成する一方法は、特定のタスク、プロセス、および／またはタスクのプロファイルにおける関係するタスクの組のクロック周波数要求を含めることに関係する。例えば、特定のタスクまたはジョブを処理しようとするとき、プロセススケジューラは、例えば、タスクプロファイルから周波数要求を抽出し、DPCのレジスタを更新してもよい。この更新によって、プロセッサの電力遷移を引き起こすことができる。そのようにして、プロセッサは、タスクまたはプロセスレベルでの、プロセッサの需要を反映する電力状態で動作することができる。

#### 【0062】

当業者であれば、プロセッサに電力制御を提供して、プロセッサが過剰な電力を用いて動作する時間を低減することにおける、他の修正形態、変更形態および改善形態を思いつくであろうが、これらは本発明の範囲に含まれると考えられる。 10

本発明のいくつかの実施態様を詳細に記述したが、当業者であれば、様々な修正形態および改善形態を思いつくであろう。このような修正形態および改善形態は、本発明の範囲に含まれることを意図するものである。したがって、以上の記述は、例示のためだけのものであり、限定することを意図するものではない。本発明は、添付の特許請求の範囲およびその等価物による定義によってのみ限定されるものである。

#### 【図面の簡単な説明】

#### 【0063】

【図1】例示的なプロセッサの、様々なサブシステムを示すブロック図である。

【図2】図1に示したプロセッサの様々な構成要素に、クロック信号を生成して分配するクロッキング方式と制御を示す図である。 20

【図3】異なる動作モードにおける、プロセッサの例示的なクロック信号の、時間の関数としての変化を示す図である。

【図4】本発明の一実施態様による、動的電力制御機能を有するプロセッサを示す図である。

【図5】本発明の一実施態様による、プロセッサに動的電力制御を提供する方法を示す。

【図6】本発明による、動的電力コントローラの一実施態様を示す図である。

【図7】本発明による、動的電力コントローラの別の実施態様を示す図である。

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

13 March 2003 (13.03.2003)

PCT

(10) International Publication Number

WO 03/021409 A2

(51) International Patent Classification: G06F 1/32 (DK). ALLEN, Michael; 7603 Jester Blvd., Austin, TX 78750 (US).

(21) International Application Number: PCT/US02/27666

(74) Agent: PRITZKER, Randy, J.; Wolf, Greenfield &amp; Sacks, P.C., 600 Atlantic Avenue, Boston, MA 02210 (US).

(22) International Filing Date: 29 August 2002 (29.08.2002)

(81) Designated States (national): AI, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, IIR, IH, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LI, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SH, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZW.

(25) Filing Language: English

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW); Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TU, TM); European patent (AL, BE, BG, CH, CY, CZ, DE, DK, EE,

(26) Publication Language: English

(85) Frequency Requirement: 29 August 2001 (29.08.2001) US

(30) Priority Data: 60/315,655 29 August 2001 (29.08.2001) US

(86) Power Management Interval: 64s

(71) Applicant: ANALOG DEVICES, INC. [US/US]; One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 (US).

(87) Inventors: BIRK, Palle; Kronen 34, DK-9260 Gistrup (DK), SOERENSEN, Joern; Blaervej 35, DK-9600 Aars

[Continued on next page]

(54) Title: DYNAMIC VOLTAGE CONTROL, METHOD AND APPARATUS

WO 03/021409 A2

**(57) Abstract:** A dynamic power controller is provided that identifies a clock frequency requirement of a processor and determines a voltage requirement to support the clock frequency requirement. The dynamic power controller transitions the processor to a power state defined by the clock frequency requirement and the voltage requirement. In particular, a voltage level indicated by the voltage requirement is supplied to the processor and the frequency distribution indicated by the frequency requirement is provided by the clock signals of the processor.

**WO 03/021409 A2**

ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR), OAPI patent (BF, BJ, CI, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

**Published:**

— *without international search report and to be republished upon receipt of that report*

-1-

**DYNAMIC VOLTAGE CONTROL METHOD AND APPARATUS**

This application claims the benefit of U.S. Provisional Application 60/315,655 under 35 U.S.C. §119(e) filed August 29, 2001, entitled "DIGITAL BASEBAND PROCESSOR," 5 by Allen, et al. The entirety of the above provisional application is hereby incorporated by reference.

**Field of the Invention**

This invention relates to reducing the power consumption in processors and, more particularly, to methods and apparatus for dynamically controlling the voltage level supplied 10 to a processor based on the processing state and/or computational demands of the processor by determining the clock frequency requirement and a corresponding voltage requirement of the processor.

**Background of the Invention**

15 Power consumption and management is a design concern for developers of processors, digital devices, computer systems etc. In battery powered devices such as cellular phones, laptop computers, person digital assistants (PDAs), and other portable and handheld devices, power consumption may be a significant contributor to the length of time during which a device may operate before the device must either be recharged and/or 20 connected to an alternate power source. As such, power consumption may significantly impact the utility of these devices.

In some computer systems and/or digital devices, power control may provide a binary power state wherein the first power state corresponds to an idle processor and the second power state corresponds to an active processor. However, the processor in a digital 25 device, for example, may have a variety of active processing states with computational demands that require varying levels of power to support the processing state.

However, conventional power control methods may not consider differing power demands of the processor. As such, depending on the computational requirements of the processor, a device may be consuming power in excess of that required to perform the 30 computational tasks and/or functions of the processor.

**Summary of the Invention**

- One embodiment according to the present invention includes a method of dynamic power control in a system having at least one processor, the at least one processor including

- 5 at least one clock signal capable of operating at a plurality of frequencies. The method comprises acts of determining a clock frequency requirement of the at least one processor, determining a voltage requirement to support the clock frequency requirement, operating the at least one clock signal according to the clock frequency requirement, and providing a voltage to supply the at least one processor according to the voltage requirement.

- 10 Another embodiment according to the present invention includes a processor including at least one clock signal operating at a plurality of frequencies. The processor comprises one or more clocked components receiving the at least one clock signal, and a controller coupled to at least one of the components to determine a clock frequency requirement of the processor, the controller adapted to determine a voltage requirement

- 15 based on the clock frequency requirement of the processor and to sequence a transition to a power state defined by the clock frequency requirement and the voltage requirement.

- Another embodiment according to the present invention includes a controller to dynamically control the power to a processor. The controller comprises a plurality of registers to store information indicating a clock frequency requirement of the processor, a

- 20 comparator coupled to the plurality of registers, the comparator configured to determine a voltage requirement based on the information stored in the plurality of registers, and a sequencer coupled to the comparator to receive the voltage level signal, the sequencer configured to transition the processor to a power state defined by the clock frequency requirement and the voltage requirement.

- 25 Another embodiment according to the present invention includes a low power device comprising at least one processor having a plurality of clocked components operating with a plurality of clock signals, a power supply adapted to provide a variable voltage to the at least one processor, a clock controller adapted to control the frequency of the plurality of clock signals, and a dynamic power controller connected to the power supply and the clock controller, the dynamic power controller adapted to monitor the at least one processor to

- 30

-3-

determine a clock frequency requirement of the at least one processor and to determine a voltage requirement based on the frequency requirement, the dynamic power controller configured to transition the power supply and the clock controller to a power state defined by the clock frequency requirement and the voltage requirement.

5

**Brief Description of the Drawings**

Fig. 1 illustrates a block diagram various subsystems of an exemplary processor;

Fig. 2 illustrates a clocking scheme and control to generate and distribute clock signals to the various components of the processor illustrated in Fig. 1;

10 Fig. 3 illustrates a diagram of how exemplary clock signals of a processor may vary as a function of time in different operating modes;

Fig. 4 illustrates a processor having dynamic power control capabilities according to one embodiment the present invention;

15 Fig. 5 illustrates a method of providing dynamic power control to a processor according to one embodiment of the present invention;

Fig. 6 illustrates one embodiment of a dynamic power controller according to the present invention; and

Fig. 7 illustrates another embodiment of a dynamic power controller according to the present invention.

20 **Detailed Description**

In many devices, particularly battery powered devices, it is advantageous to reduce the amount of time in which the device's processor is consuming excess power. A processor is considered to be consuming excess power when the computational tasks, functions, and operations of the processor may be performed, and/or the processing demands met, at a 25 lower power state. The term "processor" refers, generally, to any apparatus that performs logic operations, computational tasks, control functions, etc. A processor may include one or more subsystems, components, and/or other processors. A processor will typically include various logic components that operate using a clock signal to latch data, advance and/or sequence logic states, synchronize computations and logic operations, and/or provide 30 other timing functions.

-4-

Applicant has observed that the power consumption of a device is related to the square of the voltage supplied to the device's processor and proportional to the frequency at which the processor operates. The power consumption of a device may be expressed as:

5  $P_D = cV^2F$  (Equation 1)

where,

V = the voltage supplied to the device (i.e., the difference between Vdd and Gnd)

F = the frequency (e.g., the clock frequency of a device)

c = a constant determined by the circuits operating at V and F.

10

In addition, Applicant has recognized that the voltage needed to operate the processor may be a function of the clock frequency or frequencies being provided and distributed to the processor. Accordingly, one way to reduce the power consumption of a device is to dynamically adjust the frequency of the clock signals provided to a processor to reflect the clock frequency requirement of the processor.

15

The term "clock frequency requirement" refers generally to the clock frequency or set of clock frequencies provided to a processor that are necessary to support the tasks, functions, and/or computational requirements of a processor. Typically, a clock signal or clock signals having a frequency below the clock frequency requirement are not sufficient to operate the logic gates, flips-flops, other clocked circuitry and components to which the clock signal is provided, and are not sufficient to complete tasks in the required amount of time, and/or incapable of performing one or more operations of the processor.

20

As noted above, the voltage required by the processor may be a function of the clock frequency or set of clock frequencies (i.e., the clock frequency requirement) provided and distributed to the processor. As such, when the computational demands of a processor are low, the processor may have a reduced clock frequency requirement. Therefore, the voltage necessary to support the clock frequency requirement, that is, the voltage requirement, may be reduced accordingly.

25

The term "voltage requirement" refers, generally, to the voltage level or levels supplied to a processor to support a given clock frequency requirement. In particular, a

-5-

- voltage requirement indicates a voltage value or level sufficient to drive the various clock signals of a processor according to the clock frequency requirement without causing the clocked components to operate erroneously (e.g., memory access failures, timing violations, delays in critical speed paths, etc.). While there may be many voltage levels that will 5 support a clock frequency requirement (e.g. voltages exceeding some minimum voltage), the voltage requirement typically refers to a voltage level that more closely meets the needs of the clock frequency requirement.

As the computational demands on a processor vary with time, there may be 10 opportunities to reduce both the clock signal frequencies and the voltage level applied to the processor (i.e., the processor may be transitioned into a lower power state). Thus, the power consumption of the device can be dynamically adjusted to reflect the processing requirements of the processor. Accordingly, one embodiment according to the present invention includes identifying a clock frequency requirement of a processor and adjusting the voltage supplied to the processor to support the identified clock frequency requirement.

15 Fig. 1 illustrates a block diagram of an exemplary processor 20. Processor 20 may, for instance, be fabricated on a single semiconductor chip. Processor 20 includes a digital signal processor (DSP) subsystem 22, a microcontroller (MCU) subsystem 24, system memory 28, and peripheral subsystem 26. The various subsystems of the processor are connected to a system bus 30 in order to communicate and/or transfer data between the 20 various components, such as, operands or instructions, addresses and/or control signals, etc.

DSP subsystem 22 may include a high speed digital signal processor. Operation of a 25 digital signal processor is often characterized by real-time performance, computationally intensive and often time critical tasks, frequent memory accesses, etc. The MCU subsystem 24, for instance, may carry out various control functions, coordinate system events, execute system software, etc., and may operate at a lower clock frequency than the DSP. System memory 28 may be an on-chip memory, such as a RAM, providing a memory resource shared by the various subsystems of processor 20. Peripheral subsystem 26 may include the 30 various interfaces and logic required for the processor to communicate with off-chip devices or other processors. For example, peripheral subsystem 26 may communicate with an off-chip power management chip or access an off-chip memory. In addition, the peripheral

-6-

subsystem may include interfaces to support various communication standards such as serial, Infrared Data Association (IrDA), Universal Serial Bus (USB), SIM interfaces, etc.

The processor depicted in Fig. 1 and similar variants will be used herein to illustrate and demonstrate various aspects of the present invention, however, it should be appreciated

5 that the components and subsystems of the processor here and throughout are merely exemplary. The invention is not limited to or by the number, type, or configuration of the components in a processor implementation. Any device, processor, and/or logic circuitry having a clock frequency requirement that may vary with time is considered to be within the scope of the invention.

10 As an example, DSP subsystem 22 may also include a variety of components including a scratch memory, a coprocessor, interrupt controller, a dedicated bus, etc. The various components of the DSP subsystem itself may have independent clock frequency requirements. Likewise, the other processor components such as MCU subsystem 24 and peripheral subsystem 26 may contain a variety of clock frequency requirements. As such,

15 the clock frequency requirement of the processor may vary frequently, that is, the active state of the processor may have numerous operating modes.

As such, processor 20 may have a clock frequency requirement that varies with time. For instance, in some operating modes, the DSP may be in an idle state. As such, the high frequency clock signal required by the DSP to perform certain computational tasks may not 20 be necessary in such operating modes. The term "operating mode" characterizes a processing state or set of processing states of the various components of a processor that give rise to a particular clock frequency requirement of the processor. Typically, an operating mode characterizes a processing state of the processor in which it may be possible to transition to a different power state.

25 In order to provide a processor with the various clock signals that it requires, a single low frequency clock, referred to herein as the system clock, is often provided to the processor as a clock reference. The various clock frequencies required by the processor are then generated from the system clock and distributed appropriately to the subsystems and/or components of the processor. The various clock frequencies required by the processor are 30 often generated from the system clock by a phase locked loop (PLL) multiplier, such that the

-7-

clock signals distributed to the components of the processor are in-phase with the common reference clock. That is, the clock signals distributed throughout the processor are synchronized.

- Fig. 2 illustrates an exemplary system clocking scheme, for example, that distributes 5 the clock signals at the required frequencies to the various components of processor 20. An exemplary set of components that may be part of processor 20 are illustrated in Fig. 2, including DSP 22a, coprocessor 22b, DSP bus 22c (e.g., a dedicated bus that interconnects the DSP subsystem 22), DSP SRAM 22d (e.g., a cache, scratch memory, etc.), MCU 24a, system memory (SMEM) 28, peripheral bus 26a, and external bus (EBUS) 26b. The term 10 clock domain refers generally to a clock signal and a set of frequencies at which the clock signal normally operates. Typically, components operating in a clock domain will have one or more clocked elements (e.g., logic gates, flip-flops, etc.) that operate at the set of frequencies of the respective clock domain. A component may operate in more than one clock domain and, conversely, a clock domain may service more than one component.

- 15 The various clock signals and clock signal frequencies required by processor 20 are provided and distributed by the components of clock control 110. In particular, clock control 110 includes a system clock signal 82 and system PLL multiplier 114. System clock signal 82, or simply the system clock, is provided as a reference to synchronize the various other clock signals distributed to the processor. System PLL multiplier 114 receives the 20 system clock signal 82 and provides a high frequency clock signal 84 and locks it in-phase with the system clock signal. Typically, clock signal 84 is some multiple of the system clock.

- Fig. 2 illustrates three major clock domains generated from system clock signal 82 and the PLL clock signal 84; clock domain 90a, clock domain 90b, and clock domain 90c. 25 The components of processor 20 operate within these clock domains. For example, DSP 22a and coprocessor 22b may operate in clock domain 90a. DSP bus 22c, and DSP SRAM may operate within clock domain 90b. MCU 24a, SMEM 28, peripheral bus 26a, and external bus (EBUS) 26b, may operate within clock domain 90c.

- The clock signals in each clock domain are provided by various select, divider, and 30 gating logic and distributed to the components of the processor via a plurality of clock trees

-8-

50a-50h. For example, clock control 110 includes multiplexers in each of clock domains (e.g., multiplexers 70a, 70b, and 70c, respectively) which may independently select whether clock signal 84 is required in order to operate the components in the corresponding clock domain. Otherwise, clock signal 84 may be bypassed and the system clock signal 82 may be 5 provided to the appropriate components of the processor.

Additionally, clock control 110 may divide the frequency of clock signal 84 in order to provide the components of the processor with clock signals having reduced frequencies in order to meet the clock frequency requirement of the processor. In particular, dividers 62 and 64 allow the frequency of clock signal 84 to be reduced in frequency. For example, 10 divider 62 may provide the clocked components operating in clock domain 90b with a clock signal having half the frequency of clock signal 84 when the clock signal from the system PLL multiplier is selected. Similarly, divider 64 may provide the clocked components operating in clock domain 90c with a clock signal having a frequency reduced by factors of 2, 4, 6, 8, 10, 12, and 14. Dividers 62 and 64 may be, for instance, divide-by-n counters or 15 equivalent components for reducing the frequency of a clock signal. The various divider factors selected for each clock domain may be selected, for example, by divider select 66.

In the clocking scheme illustrated in Fig. 2, there are multiple stages where power is being consumed. System PLL multiplier 114, for example, may include a voltage controlled oscillator (VCO) in order to generate clock signal 84. As is known in the art, a voltage 20 controlled oscillator provides a voltage to an oscillator to produce a signal having a frequency proportional to the provided voltage. As such, the power consumed in generating clock signal 84 is proportional to the frequency being generated.

In addition, in order to provide clock signals to the various clocked circuits, logic 25 gates, flip-flops, etc. of the processor, clock distribution trees, or simply clock trees, are provided within the components and/or subsystems of the processor. For example, clock tree 50a drives the clock signal of clock domain 90a and distributes it to the low level components of DSP 22a. Similarly, clock tree 50e drives the clock signal of clock domain 90c and distributes it to the low level logic components of MCU 24a. Power is required to charge the various clock trees, thus, power may be conserved if the clock trees may be 30 disabled when the associated components are in an idle state. Moreover, further clock

-9-

gating logic may be included within the clock trees in order to control power consumption at a finer granularity, that is, to gate off certain portions of the clock tree distribution network.

As such, by recognizing the clock frequency requirement of the processor, clock control 100 may configure the frequency distribution to reduce the intervals when excess 5 clock frequencies are being generated. In addition, clock control 110 may control the disabling of various clock trees or portions of clock trees according to the clock frequency requirement of the processor.

It should be appreciated that the clocking scheme illustrated in Fig. 2 is merely exemplary and is meant to illustrate one scheme by which the various clock signals required 10 by a processor may be controlled and distributed to the components and/or subsystems of the processor. However, various system clocking schemes will occur to those skilled in the art to satisfy a particular set of clocking requirements. For instance, the system clock is shown as being multiplexed with the clock signal provided by the PLL multiplier. However, the system clock may be considered and distributed as a separate clock domain independent 15 of the PLL clock signal. The particular design choice for a system clocking scheme is not limiting and the various alternatives, modifications, and improvements are considered to be within the scope of the invention.

Fig. 3 is a diagram illustrating how the various clock frequencies distributed to a processor might vary over time. Plot 300 shows exemplary frequency values of four clock 20 domains of a system clocking scheme of a baseband processor as they might vary in time. The baseband processor producing the exemplary clock frequency requirement function illustrated in Fig. 3 may be similar to processor 20 illustrated in Fig. 1. Clock domain 310, denoted by the dotted line, and clock domain 320, denoted by the regular solid line, may be similar to clock domains 90a and 90c of Fig. 2, respectively. Clock domain 330, denoted by 25 the dashed line, may be, for instance, a system clock domain. In addition, the baseband processor includes baseband clock domain 340, denoted by the bold line, to provide the baseband clock to the appropriate components of the processor. Often processors used in wireless communication will be synchronized to external and often remote devices operate via a low frequency baseband clock.

-10-

Labeled across the top of plot 300, are a series of operating modes indicated as O1-O9. It should be appreciated that the operating modes may be demarcated in any number of ways and will depend upon the design of a processor and the level of desired granularity. For instance, each change in frequency in one of the clock domains may be considered a 5 different operating mode.

In operating mode O1, the only enabled clock is the baseband clock 330. All other 10 clocks may be disabled. For instance, if the baseband processor is used in a cellular phone, for example, operation mode 1 may occur when the cellular phone is on but not being used (i.e., in a standby mode). At some time  $t_1$ , an event occurs requiring the processing power 15 of, for example, the DSP. As such, the system clock 330 is enabled, supplied to the PLL which generates the maximum clock rate. The event triggering a transition into the second operating mode may require processing from components in clock domains 310, and 320. As such, all the clock trees may be enabled. Over time, the performance demands may decrease and the clock frequencies may be stepped down (e.g., the frequency of the clock 15 signal generated from a system PLL multiplier may be reduced).

At a time  $t_2$  the task or tasks requiring clock domains 310 and 320 may be completed 20 and the computational demands of the processor reduced. As such, the system PLL multiplier may be bypassed, leaving only the system clock and the baseband clock enabled. At a time  $t_3$ , another event may occur wherein the processing requirements yield a 25 configuration of active clock domains illustrated in operating mode O4. Similarly, operating modes O5-O9 illustrate further processing states that may give rise to the corresponding clock requirements illustrated in Fig. 2.

Accordingly, as the computational demands vary with time, the reduced processing 25 requirements may provide opportunities where the clock signal frequencies may be reduced. Moreover, certain clock domains may be unnecessary during certain operating modes such that the associated clock trees may be disabled. In response to the changing clock frequency requirement, the voltage supplied to the processor may be adjusted to support the changing needs of the clock frequency requirement. As such, reduced clock frequency requirements may have reduced voltage requirements.

-11-

Applicants have identified and appreciated that by monitoring the clock frequency requirement of a processor, the voltage supplied to the processor can be dynamically controlled such that the processor spends less time supplying a voltage to the processor in excess of the requirement.

5 Fig. 4 illustrates one embodiment according to the present invention including a processor 20' having dynamic power control (DPC) capabilities. For purposes of illustration, processor 20' includes the subsystems as shown and described in connection with Fig. 1.

During operation of processor 20', the computational demands on the subsystems 10 may vary with time. As such, the clock frequency requirement of the processor may also change as the various components and subsystems transition into different processing states. Dynamic power control (DPC) 100 may be connected to system bus 30 in order to communicate with the various subsystems of processor 20'. Dynamic power controller 100 may, alternatively, communicate with the subsystems in various other ways, such as shared 15 registers having appropriate interconnections, etc.

In Fig. 4, processor 20' is supplied power by off-chip power management 40. Although, power management 40 is illustrated as residing off-chip, it may alternatively be located on the same semiconductor chip as the processor. Power management 40 may be any component capable of providing a source of power, typically, by providing a voltage 20 level that may be specified by the component receiving power. For example, power management 40 may include a read/write register that may be accessed and written to in order to request a particular voltage level.

DPC 100 is connected to register 180 in order to indicate to power management the 25 voltage level to be supplied to the processor. Power management may be, for instance, a low dropout (LDO) voltage regulator. Power management may include LDO control 182 to indicate when the voltage level specified in register 180 is stable and may be provided on supply line 142.

In addition, DPC 100 is connected to clock control 110. Processor 20' may, for 30 example, have a system clocking scheme substantially the same as that illustrated in Fig. 2. As such, clock control 110 may include various components and logic gates to distribute

-12-

clock signals to the various subsystems of the processor. For example, clock control 110 may include a system PLL multiplier, bypass multiplexers, divider selects, disable logic, clock trees, etc., as illustrated in Fig. 2.

- Clock control 110 may include a writeable register coupled to the system PLL

- 5 multiplier to store the frequency to be output by the system PLL multiplier. This register, may alternatively, store a voltage value required of the VCO to produce the desired frequency, a multiplier ratio of the input clock signal required to provide the desired frequency, or some other value indicative of the desired frequency of the high frequency output clock signal produced by the system PLL multiplier. In addition, clock control may

- 10 include registers or other control means by which the desired divider factors of the dividers in the various clock domains may be controlled. For instance, divider select may include a bank of registers with which to store the desired divider factors. In addition, clock control 110 may include logic that allows the various clock domains to be gated off, the clock trees independently disabled, and/or portions of the clock trees disabled.

- 15 DPC 100 monitors processor 20' to determine the processing states of the components and/or subsystems in order to determine a current clock frequency requirement of the processor. In response to the clock frequency requirement, DPC 100 determines a voltage level required to support the clock frequency requirement. DPC 100 then instructs power management 40 to adjust the voltage supplied to the processor and instructs clock

- 20 control 110 to provide the frequency distribution accorded by the clock frequency requirement of the processor to the various subsystems and components.

It should be appreciated that a controller (e.g., dynamic power controller 100) may be implemented in numerous ways, such as with dedicated hardware (e.g., various circuitry, preprogrammed logic arrays, finite state machines (FSMs), etc.), or using one or more

25 processors that are programmed using software (e.g., microcode) to perform the various functions of the controller. It also should be appreciated that implementations of a controller according to various embodiments of the present invention may include hardware, firmware, and software oriented elements.

Fig. 5 illustrates a flow chart depicting one method of dynamically adjusting the power supplied to a processor according to the present invention. For instance, the method

-13-

described below may be used by DPC 100 in order dynamically control the voltage supply to processor 20<sup>1</sup>.

In step 210, a DPC monitors the clock frequency requirement of the processor. A change in the clock frequency requirement may indicate that the voltage level supplied to the processor may be reduced or it may indicate that the processing demands of the processor now require additional voltage in order to support the new clock frequency requirement. As such, in step 220, the clock frequency requirement is evaluated in order to determine a voltage requirement necessary to support the new clock frequency requirement.

For example, the clock frequency requirement may represent the minimum frequency that each clock domain requires in order to perform the functions and/or computational tasks of the components operating in that clock domain. As such, the DPC may select the maximum value, referred to as the maximum-minimum frequency value, in order to determine the voltage requirement of the system.

Other methods of determining a voltage requirement from a clock frequency requirement of the processor will occur to those skilled in the art and may depend on the clocking scheme of a particular processor implementation. For instance, the DPC may consider which clock trees may be disabled under the new clock frequency requirement when determining the voltage requirement. The DPC may also consider more than the maximum minimum value of the clock frequency requirement when determining the voltage. The various methods for determining a voltage requirement from a given clock frequency requirement are considered to be within the scope of the present invention.

In step 230, a voltage level sufficient to support the clock frequency requirement is determined. In step 240, the current voltage level being supplied to the processor is compared to the voltage requirement determined in step 240 to determine the required voltage change, or delta, required to provide the voltage requirement.

If the sign of the voltage change is positive (i.e., the voltage requirement is greater than the current voltage level), then the sequence of events to transition to the higher power state follows that indicated in step 250a and 260a. As such, the voltage level indicated by the voltage requirement is first transitioned. For example, the DPC may request that power management increase the supply voltage to meet the voltage requirement of the processor.

-14-

After the new voltage level has been fully transitioned (i.e., the new supply voltage is stable), the new frequency distribution as indicated by the clock frequency requirement may be applied to the various subsystems of the processor. For example, the DPC may instruct clock control to distribute clock signals according to the clock frequency requirement to the 5 processor.

If the sign of the voltage change is negative (i.e., the voltage requirement is less than the voltage level), then the sequence of events to transition to the lower power state follows that indicated in step 250b and 260b. As such, the frequency distribution indicated by the clock frequency requirement is first provided to the subsystems and components of the 10 processor. When the processor is operating according the new clock frequency requirement, the voltage supplied to the processor is reduced to the voltage level indicated by the voltage requirement determined in step 230.

The voltage and frequency transitions may be sequenced in the order described above to avoid erroneous operation of the processor. For example, consider the clock 15 frequency requirement for accessing memory. As the frequency increases for a fixed voltage, there may be a point at which memory access fails. As such, to avoid such potential problems during power state transitions, when going to a higher power state, the voltage may be stepped up before the clock frequency is increased. When going to a lower power state, frequency may be first decreased before reducing the voltage supplied to the 20 processor.

The method described in connection with Fig. 5 may be realized in a number of ways and by various designs and implementations. Figure 6 illustrates one embodiment of a DPC according to the present invention. The schematic illustrates a hardware solution to dynamic power control. DPC 100' includes a bank of registers 610, a comparator 620, random access 25 memory (RAM) 630, and power sequencing finite state machine (FSM) 640, and reset register 650. DPC 100' is illustrated as controlling the subsystems of processor 20'', which, for clarity, include those subsystems, components, and clocking scheme previously described. Power is supplied to the processor by power management 40.

Registers 610 store information indicating the clock frequency requirement of 30 processor 20''. For instance, registers 610 may store frequency values required for each

-15-

clock domain. In addition, there may be a register associated with each subsystem operating in a clock domain to indicate the clock frequency required by each subsystem from each of the clock domains. The particular number, arrangement and association of the registers is a matter of design choice and any variation that adequately indicates the processor frequency requirement is considered to be within the scope of the invention.

5 Comparator 620 compares the frequency values stored in the registers in registers 610 in order to determine a voltage required to support the distribution of clock frequencies as indicated in the register bank. One method of determining the voltage requirement is to choose the largest frequency from the register bank (i.e., the comparator selects the 10 maximum minimum value from the clock frequency requirement of the processor) to determine the voltage requirement. This frequency value, for example, may indicate the frequency required of the clock signal provided by the system PLL multiplier. The voltage requirement may then be based, at least in part, on the voltage level that the signal generator (e.g., a voltage controlled oscillator) of the system PLL multiplier needs to generate the 15 indicated frequency.

RAM 630 may, for example, store a lookup table containing voltage values required to support various clock frequency requirements of the processor. As such, comparator 620 may map the selected frequency value or otherwise map the frequency requirement indicated in registers 610 to a location in RAM 630. The voltage level obtained from RAM 20 630 corresponds to the voltage requirement associated with the processor frequency requirement.

It should be appreciated that various methods of encoding the clock frequency requirement to determine a voltage level that will support the processor operating at a particular clock frequency requirement will occur to those skilled in the art. The design of 25 the processor, clocking scheme, and other processor requirement and considerations may guide the particular mapping scheme from clock frequency requirement to voltage requirement. However, these variations do not depart from the scope of the invention.

The voltage value obtained from RAM 630 is then provided to the power sequencing finite state machine (FSM). The power sequencing FSM then transitions the processor to 30 the power state indicated by the clock frequency and voltage requirements. For example,

-16-

the power sequencing FSM may check the current voltage level being supplied to the processor by reading the voltage value stored in register 180 in order to determine the sign of the voltage change required to meet the voltage requirement of the processor (e.g., the voltage level obtained from RAM 630).

5 If the sign of the voltage change is positive, the power sequencing FSM may first instruct power management 40 to supply the desired voltage level (i.e., DPC 100' may write the desired voltage level into register 180). After power management 40 has indicated that the voltage level has been transitioned and is stable (i.e., power management 40 may indicate that the voltage is stable via line 184), the power sequencing FSM may then instruct

10 clock control 110 to increase the frequency of the various clock domains in order to meet the clock frequency requirement of the processor.

For example, power sequencing FSM may instruct clock control 110 to increase the frequency of the clock signal output from the system PLL multiplier. Alternatively, power sequencing FSM may have access to a register that indicates to the system PLL multiplier

15 what clock frequency should be output.

If the sign of the voltage change is negative, the power sequencing FSM may first instruct clock control 110 to reduce the clock frequency of the various clock domains to reflect the clock frequency requirement of the processor. Once the frequencies have been reduced, the power sequencing FSM may instruct the power management to modify the

20 voltage supplied to the processor according to the voltage level obtained from RAM. As such, the power sequencing FSM insures that power state transitions are sequenced in an order that avoids potential operation errors of the processor.

Reset register 650 provides power sequencing FSM 640 with valid voltage levels during startup/reset. Since the information stored in RAM 630 may not be dependable

25 during startup/reset, reset register 650 insures that a voltage sufficient to support the tasks involved in reset/startup, various boot events, etc., will be provided to the processor. As such, the value or values stored in reset register 650 might only be selected during startup/reset.

Each time that one of the values in the register bank changes, the comparator may re-

30 evaluate the clock frequency requirement of the processor in order to determine whether or

-17-

not the voltage level can or should be changed in order to accommodate the new clock frequency requirement (e.g., comparator 620 decides if the processor can transition to a new power state). The bank of registers 610 may be written to, for example, by software that runs on the processor (e.g., the DSP or the MCU). As an example, referring to processor 5 20", consider an operating mode in which the DSP is processing a high priority task that requires a 300 MHz frequency clock. The MCU is concurrently processing a task requiring a 60 MHz frequency clock.

As such, software running on the DSP and/or MCU may write the frequency required by the various clocks domains into the associated register in register bank 610 (e.g., 10 the register associated with clock domain 310 may store a frequency value of 300 MHz and the register associated with clock domain 320 may store a value of 60 MHz).

The comparator 620 may implement a maximum minimum selection method. Accordingly, the comparator would select the 300 MHz frequency value as a basis for determining the voltage requirement of the processor. An index into RAM 630 may be 15 derived from the maximum minimum value, for instance, a value of 300 MHz may map to a location in memory storing a voltage value of 1.5 volts. As such, the power management may be supplying the processor with 1.5 volts in order to support the current clock frequency requirement of the processor.

At some point in time, the processor may complete its high priority task, and the 20 computational demands of the processor may be reduced. For instance, the DSP may require only a 180 MHz clock in order to meet the processing demands of the current computation. Software running on the DSP, for instance, may identify this reduced clock frequency requirement of the DSP and write the new frequency value into the appropriate register. DPC 100" then detects a change in one of the values stored in the register bank. 25 Accordingly, comparator 620 may reevaluate the processor's clock frequency requirement and determine that the new maximum-minimum frequency value is 180 MHz. This new value may map, for instance, to a value of 1.2 volts in RAM 630.

Power sequencing FSM receives this new voltage value and determines that a negative voltage transition is required to reflect the voltage requirement needed to support 30 the new clock frequency requirement of the processor. As such, the power sequencing FSM

-18-

may instruct the multiplier select value of the system PLL multiplier to be reduced in order to supply a 180 MHz clock signal. After the reduced frequency is provided by the PLL, the power sequencing FSM may write a value of 1.2 volts into register 180. Power management 40 then reads this value and supplies the new reduced voltage level to the processor. As 5 such, the processor will operate in a reduced power state reflecting clock frequency requirement of the processor.

The comparator need not determine the index into the lookup table based on the maximum-minimum value. For instance, the comparator may consider the various clock frequencies stored in the register bank in a variety of ways. For example, the 180 MHz 10 clock frequency of clock domain 310, may be able to be supported by a lower voltage, for instance, .09 volts. However, it may be the case that .9 volts isn't sufficient to support the processor clock frequency requirement because of the requirements of the other clock domains (e.g., 75 MHz for clock domain 320 and a 26 MHz system clock distribution). The comparator may be configured to recognize that the clock frequency requirement cannot be 15 supported by .9 volts, and as such, and the clock frequency requirement described above may map to a voltage requirement of 1.2 volts, even though the maximum minimum value could itself be supported by a lower voltage.

At some later instant, the MCU may finish its task and require only a 45 MHz clock in order to meet the computational demands of the current processing state. Software 20 running on the MCU, for instance, may identify the new processing state and write the new frequency value into the appropriate register.

In response to a change in a register value, the comparator may determine that the 25 clock frequency requirement of the processor has been modified, even though the maximum-minimum value remains the same (e.g., 180 MHz). For instance, the new clock frequency requirement may map to a voltage level of .9 volts. The power sequencing FSM may then transition to the reduced power state according to the sequence described above. However, the change in frequency required by the MCU (e.g., 45 MHz) may be generated by adjusting the divider factor of the appropriate clock domain. As such, the multiplier select value of the PLL may not be reduced in some power state transitions.

-19-

- At some later instant, the DSP may need to process another high priority task. As such, software may identify the new clock frequency requirement of the DSP, for instance, 240 MHz and write this value into the appropriate register. The comparator may then reevaluate the clock frequency requirement of the processor and determine that a new voltage requirement is necessary to support the current clock frequency requirement of the processor. The comparator then indexes into memory and a corresponding voltage value, for instance, 1.5 volts is issued to the power sequencing FSM. The power sequencing FSM determines that a positive change in the voltage level is required to meet the new voltage requirement.