(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5222029号

(P5222029)

(45) 発行日 平成25年6月26日(2013.6.26)

(24) 登録日 平成25年3月15日(2013.3.15)

(51) Int.Cl.

HO4N 5/335 (2011.01)

F 1

HO4N 5/335

請求項の数 8 (全 20 頁)

(21) 出願番号 特願2008-148315 (P2008-148315)

(22) 出願日 平成20年6月5日 (2008.6.5)

(65) 公開番号 特開2009-296358 (P2009-296358A)

(43) 公開日 平成21年12月17日 (2009.12.17)

審査請求日 平成23年6月6日 (2011.6.6)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像装置、撮像システム、および、撮像装置の制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素が行方向及び列方向に配列された画素配列と、

増幅率を設定するための設定部をそれぞれ含む複数の列増幅部と、

第1の参照信号と第2の参照信号とを異なるタイミングで前記画素配列の列信号線へそれぞれ出力する複数の参照信号供給部と、

を備え、

前記第1の参照信号と前記第2の参照信号とは、前記画素配列における複数の列に対して共通であり、

前記複数の列増幅部のそれぞれは、前記複数の列増幅部のそれぞれの増幅率を設定するための期間において、前記第1の参照信号と前記第2の参照信号との差分を増幅して出力し、あるいは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力するよう構成され、

前記設定部は、前記期間において前記複数の列増幅部のそれぞれから出力された信号に応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するようそれぞれ決定された増幅率を前記複数の列増幅部のそれぞれに設定し、

前記複数の列増幅部は、前記設定部による増幅率の設定後に前記画素配列における各列の画素から前記列信号線へ異なるタイミングで出力されてくる第1の信号と第2の信号との差分を増幅する、あるいは、前記第1の信号と前記第2の信号とをそれぞれ増幅することを特徴とする撮像装置。

10

20

## 【請求項 2】

前記複数の列増幅部のそれぞれは、前記第1の参照信号と前記第2の参照信号との差分を増幅することにより、第1の画像信号を生成して出力し、

前記複数の列増幅部のそれぞれの前記設定部は、前記第1の画像信号に応じて前記複数の列増幅部における増幅率のばらつきを低減するように決定された増幅率を設定し、

前記複数の列増幅部は、それぞれの前記設定部により設定された増幅率で、前記第1の信号と前記第2の信号との差分を増幅することにより、第2の画像信号を生成して出力する

ことを特徴とする請求項1に記載の撮像装置。

## 【請求項 3】

前記複数の列増幅部のそれぞれは、

入力端子と出力端子とを有する演算増幅器と、

前記画素配列における各列の画素又は前記参照信号供給部から前記列信号線を介して伝達された信号が入力される第1の電極と、前記演算増幅器の前記入力端子に接続された第2の電極とを含む入力容量と、

前記演算増幅器の前記入力端子と前記出力端子とに接続され、容量値が可変の帰還容量と、

前記演算増幅器の前記入力端子と前記出力端子とに接続され、前記演算増幅器をリセットするリセットスイッチと、

をさらに含み、

前記複数の列増幅部のそれぞれの前記設定部は、前記第1の画像信号に応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するように決定された増幅率に応じた容量値に前記帰還容量を制御する

ことを特徴とする請求項2に記載の撮像装置。

## 【請求項 4】

前記複数の列増幅部のそれぞれは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力し、

前記複数の列増幅部のそれぞれの前記設定部は、前記増幅された前記第1の参照信号と前記増幅された前記第2の参照信号とに応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するように決定された増幅率を前記列増幅部に設定し、

前記複数の列増幅部は、それぞれの前記設定部により設定された増幅率で、前記第1の信号と前記第2の信号とをそれぞれ増幅して出力する

ことを特徴とする請求項1に記載の撮像装置。

## 【請求項 5】

前記複数の列増幅部のそれぞれは、前記画素配列における各列の画素又は前記参照信号供給部から前記列信号線を介して伝達された信号が入力される増幅器をさらに含み、

前記複数の列増幅部のそれぞれの前記設定部は、前記増幅された前記第1の参照信号と前記増幅された前記第2の参照信号とに応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するように決定された増幅率を前記増幅器に設定する

ことを特徴とする請求項4に記載の撮像装置。

## 【請求項 6】

請求項1から3のいずれか1項に記載の撮像装置と、

前記撮像装置の撮像面へ像を形成する光学系と、

前記撮像装置から出力された信号を処理して画像データを生成する信号処理部と、

を備え、

前記複数の列増幅部のそれぞれは、前記第1の参照信号と前記第2の参照信号との差分を増幅することにより第1の画像信号を生成して出力し、

前記信号処理部は、前記第1の画像信号を受けて、受けた前記第1の画像信号に応じて、前記複数の列増幅部における増幅率のばらつきを低減するように、前記複数の列増幅部のそれぞれの増幅率を決定し、決定した増幅率を設定するように前記複数の列増幅部のそ

10

20

30

40

50

それぞれの前記設定部を制御し、

前記複数の列増幅部のそれぞれは、前記信号処理部に制御されることにより、前記複数の列増幅部のそれぞれの前記設定部により設定された増幅率で、前記第1の参照信号と前記第2の参照信号との差分を増幅することにより第2の画像信号を生成して出力することを特徴とする撮像システム。

【請求項7】

請求項1、4及び5のいずれか1項に記載の撮像装置と、

前記撮像装置の撮像面へ像を形成する光学系と、

前記撮像装置から出力された信号を処理して画像データを生成する信号処理部と、

を備え、

前記複数の列増幅部のそれぞれは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力し、

前記信号処理部は、前記増幅された前記第1の参照信号と前記増幅された前記第2の参照信号とをそれぞれ受け、それぞれ受けた前記増幅された前記第1の参照信号と前記増幅された前記第2の参照信号との差分をとることにより第1の画像信号を生成し、生成された前記第1の画像信号に応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するように、前記複数の列増幅部のそれぞれの増幅率を決定し、決定した増幅率を設定するように前記設定部を制御し、

前記複数の列増幅部のそれぞれは、前記信号処理部に制御されることにより、前記複数の列増幅部のそれぞれの前記設定部により設定された増幅率で、前記第1の信号と前記第2の信号とをそれぞれ増幅して出力し、

前記信号処理部は、前記増幅された前記第1の信号と前記増幅された前記第2の信号とを受けて、前記増幅された前記第1の信号と前記増幅された前記第2の信号との差分をとることにより第2の画像信号を生成する

ことを特徴とする撮像システム。

【請求項8】

複数の画素が行方向及び列方向に配列された画素配列と、複数の列増幅部と、前記画素配列における複数の列に対して共通な第1の参照信号と第2の参照信号とを異なるタイミングで前記画素配列の列信号線へそれぞれ出力する複数の参照信号供給部と、を備える撮像装置の制御方法であって、

前記複数の列増幅部のそれぞれが、前記第1の参照信号と前記第2の参照信号との差分を増幅して出力し、あるいは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力するステップと、

前記複数の列増幅部のそれぞれから出力された信号に応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するようにそれぞれ決定された増幅率を前記複数の列増幅部のそれぞれに設定するステップと、

前記複数の列増幅部のそれぞれへの増幅率の設定後に前記画素配列における各列の画素から前記列信号線へ異なるタイミングで出力されてくる第1の信号と第2の信号との差分を増幅する、あるいは、前記第1の信号と前記第2の信号とをそれぞれ増幅するステップと、

を含むことを特徴とする撮像装置の制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像装置、撮像システム、および、撮像装置の制御方法に関する。

【背景技術】

【0002】

近年、デジタルカメラやデジタルビデオカメラなどの撮像システムには、画素内に能動素子を持ち周辺回路をオンチップ化できるCMOSセンサなどの撮像装置が用いられることがある。

## 【0003】

C MOSセンサは、画素配列を備える。画素配列では、複数の画素が行方向及び列方向に配列されている。各画素は、フォトダイオード、転送MOSトランジスタ、フローティングディフュージョン(FD)、リセットMOSトランジスタ及び増幅MOSトランジスタを含む。

## 【0004】

フォトダイオードは、光に応じた電荷を発生させて蓄積する。転送MOSトランジスタは、フォトダイオードで発生した電荷をFDへ転送する。FDは、転送された電荷を電圧に変換する。リセットMOSトランジスタは、FDをリセットする。増幅MOSトランジスタは、リセットMOSトランジスタによりFDがリセットされた状態でFDの電圧に応じたN信号を列信号線へ出力する。また、増幅MOSトランジスタは、転送MOSトランジスタによりフォトダイオードの電荷がFDへ転送された状態でFDの電圧に応じたS信号を列信号線へ出力する。

10

## 【0005】

ここで、増幅MOSトランジスタの閾値電圧が画素ごとにばらついており、また、リセットMOSトランジスタがFDをリセットする際にFDでKTCノイズ(熱雑音)が発生するので、N信号とS信号とには、それぞれ、固定パターンノイズが混入する。

## 【0006】

それに対して、特許文献1に示された技術では、各列のCDS回路が、画素配列から列信号線を介して伝達されたN信号とS信号との差分をとるCDS処理を行うことにより、固定パターンノイズが除去された画像信号を生成している。特許文献1に示された技術では、N信号とS信号とをそのまま読み出して両者の差分をとり保持させているので、その差分のレベルが小さい場合に、得られる画像信号のSN比が悪化する可能性がある。

20

## 【0007】

それに対して、特許文献2に示された技術では、各列のクランプ容量及び演算増幅器が、画素配列から列信号線を介して伝達されたN信号とS信号との差分を増幅するCDS処理を行うことが提案されている。これにより、特許文献2によれば、差分を増幅してから保持させるので、得られる画像信号のSN比を向上できるとされている。

【特許文献1】特開2005-223860号公報

30

【特許文献2】特開2005-217771号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0008】

しかし、特許文献2に示された技術では、複数の演算増幅器(列増幅部)における増幅率がばらついていた場合に、複数の演算増幅器から出力される画像信号のレベルがばらつく可能性がある。すなわち、複数の画素における特性のばらつきに起因した固定パターンノイズを低減できたとしても、複数の演算増幅器における増幅率のばらつきに起因した固定パターンノイズを低減できない可能性がある。この結果、特に高感度設定時において、画像信号により得られた画像において縦筋状のノイズが依然として目立ってしまう可能性がある。

40

## 【0009】

本発明の目的は、複数の列増幅部における増幅率のばらつきに起因した固定パターンノイズを低減することにある。

## 【課題を解決するための手段】

## 【0010】

本発明の第1の側面に係る撮像装置は、複数の画素が行方向及び列方向に配列された画素配列と、増幅率を設定するための設定部をそれぞれ含む複数の列増幅部と、第1の参照信号と第2の参照信号とを異なるタイミングで前記画素配列の列信号線へそれぞれ出力する複数の参照信号供給部と、を備え、前記第1の参照信号と前記第2の参照信号とは、前記画素配列における複数の列に対して共通であり、前記複数の列増幅部のそれぞれは、前

50

記複数の列増幅部のそれぞれの増幅率を設定するための期間において、前記第1の参照信号と前記第2の参照信号との差分を増幅して出力し、あるいは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力するように構成され、前記設定部は、前記期間において前記複数の列増幅部のそれぞれから出力された信号に応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するようにそれぞれ決定された増幅率を前記複数の列増幅部のそれぞれに設定し、前記複数の列増幅部は、前記設定部による増幅率の設定後に前記画素配列における各列の画素から前記列信号線へ異なるタイミングで出力されてくる第1の信号と第2の信号との差分を増幅する、あるいは、前記第1の信号と前記第2の信号とをそれぞれ増幅することを特徴とする。

【0011】

10

本発明の第2側面に係る撮像システムは、本発明の第1側面に係る撮像装置と、前記撮像装置の撮像面へ像を形成する光学系と、前記撮像装置から出力された信号を処理して画像データを生成する信号処理部とを備え、前記複数の列増幅部のそれぞれは、前記第1の参照信号と前記第2の参照信号との差分を増幅することにより第1の画像信号を生成して出力し、前記信号処理部は、前記第1の画像信号を受けて、受けた前記第1の画像信号に応じて、前記複数の列増幅部における増幅率のばらつきを低減するように、前記複数の列増幅部のそれぞれの増幅率を決定し、決定した増幅率を設定するように前記設定部を制御し、前記複数の列増幅部のそれぞれは、前記信号処理部に制御されることにより前記設定部により設定された増幅率で、前記第1の参照信号と前記第2の参照信号との差分を増幅することにより第2の画像信号を生成して出力することを特徴とする。

【0012】

20

本発明の第3側面に係る撮像システムは、本発明の第1側面に係る撮像装置と、前記撮像装置の撮像面へ像を形成する光学系と、前記撮像装置から出力された信号を処理して画像データを生成する信号処理部とを備え、前記複数の列増幅部のそれぞれは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力し、前記信号処理部は、前記増幅された前記第1の参照信号と前記増幅された前記第2の参照信号とをそれぞれ受けて、それぞれ受けた前記増幅された前記第1の参照信号と前記増幅された前記第2の参照信号との差分をとることにより第1の画像信号を生成し、生成された前記第1の画像信号に応じて前記複数の列増幅部における増幅率のばらつきを低減するように、前記複数の列増幅部のそれぞれの増幅率を決定し、決定した増幅率を設定するように前記設定部を制御し、前記複数の列増幅部のそれぞれは、前記信号処理部に制御されることにより前記設定部により設定された増幅率で、前記第1の信号と前記第2の信号とをそれぞれ増幅して出力し、前記信号処理部は、前記増幅された前記第1の信号と前記増幅された前記第2の信号とを受けて、前記増幅された前記第1の信号と前記増幅された前記第2の信号との差分をとることにより第2の画像信号を生成することを特徴とする。

30

本発明の第4側面に係る撮像装置の制御方法は、複数の画素が行方向及び列方向に配列された画素配列と、複数の列増幅部と、前記画素配列における複数の列に対して共通な第1の参照信号と第2の参照信号とを異なるタイミングで前記画素配列の列信号線へそれぞれ出力する複数の参照信号供給部と、を備える撮像装置の制御方法であって、前記複数の列増幅部のそれぞれが、前記第1の参照信号と前記第2の参照信号との差分を増幅して出力し、あるいは、前記第1の参照信号と前記第2の参照信号とをそれぞれ増幅して出力するステップと、前記複数の列増幅部のそれぞれから出力された信号に応じて前記複数の列増幅部のそれぞれにおける増幅率のばらつきを低減するようにそれぞれ決定された増幅率を前記複数の列増幅部のそれぞれに設定するステップと、前記複数の列増幅部のそれぞれへの増幅率の設定後に前記画素配列における各列の画素から前記列信号線へ異なるタイミングで出力されてくる第1の信号と第2の信号との差分を増幅する、あるいは、前記第1の信号と前記第2の信号とをそれぞれ増幅するステップと、

を含むことを特徴とする。

40

【発明の効果】

【0013】

50

本発明によれば、複数の列増幅部における増幅率のばらつきに起因した固定パターンノイズを低減することができる。

【発明を実施するための最良の形態】

【0014】

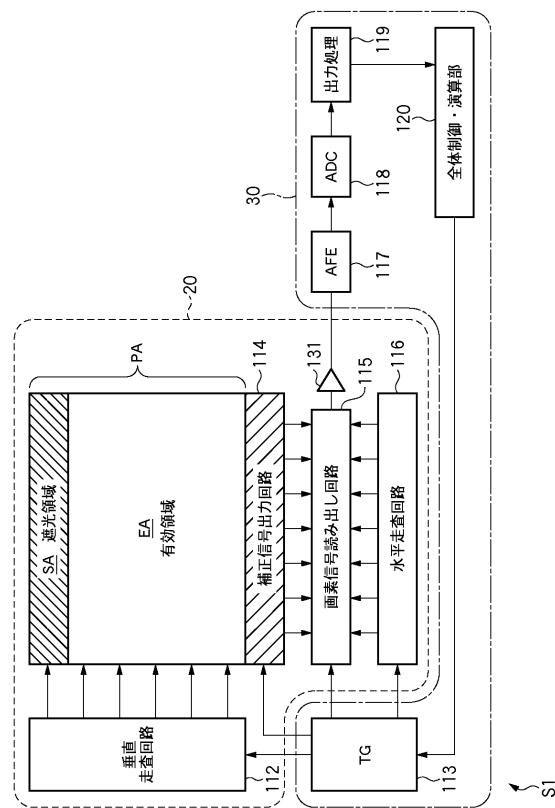

本発明の実施形態に係る撮像システムS1について、図1を用いて説明する。図1は、本発明の実施形態に係る撮像システムS1の構成の一例を示す図である。

【0015】

撮像システムS1は、例えば、デジタルカメラやデジタルビデオカメラである。撮像システムS1は、光学系(図示せず)、撮像装置20、及び信号処理部30を備える。

【0016】

光学系は、撮像装置20の撮像面(画素配列PA)へ像を形成する。

10

【0017】

撮像装置20は、画素配列PAに形成された被写体の像を画像信号に変換する。撮像装置20は、変換された画像信号を出力する。撮像装置20は、例えば、CMOSセンサである。

【0018】

信号処理部30は、撮像装置20から出力された信号を処理して画像データを生成する。また、信号処理部30は、生成した画像データに応じて、光学系や撮像装置20を制御する。

【0019】

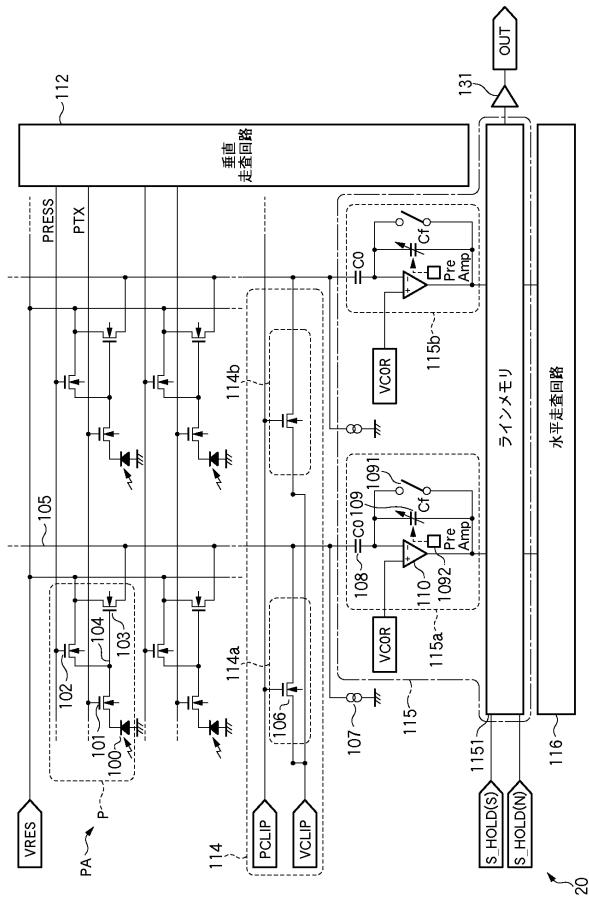

次に、撮像装置20の構成を、図1及び図2を用いて説明する。図2は、撮像装置20の回路構成を示す図である。

20

【0020】

撮像装置20は、画素配列PA、垂直走査回路112、補正信号出力回路114、画素信号読み出し回路115、水平走査回路116、及び出力回路131を備える。

【0021】

画素配列PAでは、複数の画素Pが行方向及び列方向に配列されている。画素配列PAは、遮光領域SA及び有効領域EAを含む。遮光領域SAには、遮光された画素が配されている。有効領域EAには、遮光されていない画素が配されている。遮光領域SAの画素から出力された信号は、後段の信号処理部30により、有効領域EAの画素から出力された信号の黒レベルを補正するために使用される。遮光領域SAの画素と有効領域EAの画素とは、同様の構成である。

30

【0022】

なお、図2では、有効領域EAが2行2列の画素Pで構成されている場合が例示されており、遮光領域SAの図示が省略されている。

【0023】

各画素Pは、光電変換部100、転送部101、電荷電圧変換部104、リセット部102、及び出力部103を含む。

【0024】

光電変換部100は、光に応じた電荷を発生させて蓄積する。光電変換部100は、例えば、フォトダイオードである。

40

【0025】

転送部101は、垂直走査回路112からアクティブな信号が供給された際に、光電変換部100で発生した電荷を電荷電圧変換部104へ転送する。転送部101は、例えば、転送MOSトランジスタであり、垂直走査回路112からアクティブな信号がゲートに供給された際にオンすることにより、光電変換部100の電荷を電荷電圧変換部104へ転送する。

【0026】

電荷電圧変換部104は、転送された電荷を電圧に変換する。電荷電圧変換部104は、出力部103の入力部としても機能し、その電圧に応じた信号を出力部103へ入力す

50

る。電荷電圧変換部 104 は、例えば、フローティングディフュージョンである。

【0027】

リセット部 102 は、垂直走査回路 112 からアクティブな信号が供給された際に、電荷電圧変換部 104 をリセットする。リセット部 102 は、特開平 11-112018 に記載されている回路形式と同様に、電荷電圧変換部 104 の電位を制御することにより画素を選択状態 / 非選択状態にする。

【0028】

リセット部 102 は、電荷電圧変換部 104 の電位を第 1 の電位 (VRESH) にリセットすることにより、画素 P を選択状態にする。第 1 の電位 (VRESH) は、出力部 (增幅 MOS トランジスタ) 103 がオンする電位である。このとき、電源 VRES の電位は、第 1 の電位 (VRESH) に制御されている。

10

【0029】

リセット部 102 は、電荷電圧変換部 104 の電位を第 2 の電位 (VRESL) にリセットすることにより、画素 P を非選択状態にする。第 2 の電位 (VRESL) は、出力部 (增幅 MOS トランジスタ) 103 がオフする電位である。このとき、電源 VRES の電位は、第 2 の電位 (VRESL) に制御されている。

【0030】

リセット部 102 は、例えば、リセット MOS トランジスタであり、垂直走査回路 112 からアクティブな信号がゲートに供給された際にオンすることにより、電荷電圧変換部 104 をリセットする。リセット部 102 のゲートには、第 1 の電位 (VRESH) より閾値電圧以上高い電位の信号がアクティブな信号として供給される。

20

【0031】

出力部 103 は、電荷電圧変換部 104 の電圧に応じた信号を列信号線 105 へ出力する。出力部 103 は、リセット部 102 が電荷電圧変換部 104 をリセットした状態で第 1 の信号 (ノイズ信号) を列信号線 105 へ出力する。出力部 103 は、転送部 101 が光電変換部 100 の電荷を電荷電圧変換部 104 へ転送した状態で第 2 の信号 (光信号) を列信号線 105 へ出力する。出力部 103 は、例えば、増幅 MOS トランジスタであり、列信号線 105 に接続された定電流源 107 とソースフォロワ動作を行うことにより、電荷電圧変換部 104 の電圧に応じた信号を列信号線 105 へ出力する。

【0032】

30

垂直走査回路 112 は、画素配列 PA の各行を垂直方向に走査することにより、画素配列 PA における所定の行を選択するとともに、選択された行を駆動する。

【0033】

補正信号出力回路 114 は、複数の参照信号供給部 114a, 114b を含む。複数の参照信号供給部 114a, 114b は、それぞれ、画素配列 PA における各列の画素に列信号線 105 で接続されている。各列の参照信号供給部 114a, 114b は、第 1 の参照信号 VCLIPH と第 2 の参照信号 VCLIPL とを異なるタイミングで列信号線 105 へ出力する。第 1 の参照信号 VCLIPH と第 2 の参照信号 VCLIPL とは、画素配列 PA における複数の列に対して一定である。

【0034】

40

なお、各列の参照信号供給部 114a, 114b の構成は、後述する。

【0035】

画素信号読み出し回路 115 は、複数の列増幅部 (列アンプ) 115a, 115b、及びラインメモリ 1151 を含む。複数の列増幅部 115a, 115b は、それぞれ、画素配列 PA における各列の画素と各列の参照信号供給部 114a, 114b とに列信号線 105 で接続されている。

【0036】

各列の列増幅部 115a, 115b は、そのオフセットを第 1 の N 信号としてラインメモリ 1151 へ出力する。各列の列増幅部 115a, 115b は、各列の参照信号供給部 114a, 114b から異なるタイミングで列信号線 105 へ出力された第 1 の参照信号

50

V C L I P H と第 2 の参照信号 V C L I P L とをそれぞれ受ける。各列の列増幅部 115 a, 115 b は、第 1 の参照信号 V C L I P H と第 2 の参照信号 V C L I P L との差分を増幅する C D S 処理を行う。これにより、各列の列増幅部 115 a, 115 b は、第 1 の画像信号を生成して、そのオフセットが第 1 の画像信号に重畠された信号を第 1 の S 信号としてラインメモリ 115 1 へ出力する。ラインメモリ 115 1 は、各列の画素の第 1 の N 信号と第 1 の S 信号とをそれぞれ保持する。

【 0 0 3 7 】

また、各列の列増幅部 115 a, 115 b は、そのオフセットを第 2 の N 信号としてラインメモリ 115 1 へ出力する。各列の列増幅部 115 a, 115 b は、選択された行の画素から列信号線 105 へ異なるタイミングで出力された第 1 の信号と第 2 の信号とをそれぞれ受ける。各列の列増幅部 115 a, 115 b は、第 1 の信号と第 2 の信号との差分を増幅する C D S 処理を行う。これにより、各列の列増幅部 115 a, 115 b は、第 2 の画像信号を生成して、そのオフセットが第 2 の画像信号に重畠された信号を第 2 の S 信号としてラインメモリ 115 1 へ出力する。ラインメモリ 115 1 は、各列の画素の第 2 の N 信号と第 2 の S 信号とをそれぞれ保持する。

【 0 0 3 8 】

なお、各列の列増幅部 115 a, 115 b 内の構成は、後述する。

【 0 0 3 9 】

水平走査回路 116 は、画素信号読み出し回路 115 を水平方向に走査することにより、画素信号読み出し回路 115 におけるラインメモリ 115 1 により保持された各列の画素の第 1 の S 信号及び第 1 の N 信号を順次に出力回路 131 へ転送させる。

【 0 0 4 0 】

また、水平走査回路 116 は、画素信号読み出し回路 115 を水平方向に走査することにより、画素信号読み出し回路 115 におけるラインメモリ 115 1 により保持された各列の画素の第 2 の S 信号及び第 2 の N 信号を順次に出力回路 131 へ転送させる。

【 0 0 4 1 】

出力回路 131 は、転送された第 1 の S 信号と第 1 の N 信号との差分を演算することにより、列増幅部（後述の演算増幅器）のオフセットが除去された第 1 の画像信号を得る。出力回路 131 は、第 1 の画像信号を後述の A F E 117 へ出力する。

【 0 0 4 2 】

また、出力回路 131 は、転送された第 2 の S 信号と第 2 の N 信号との差分を演算することにより、列増幅部（後述の演算増幅器）のオフセットが除去された第 2 の画像信号を得る。出力回路 131 は、第 2 の画像信号を後述の A F E 117 へ出力する。

【 0 0 4 3 】

次に、信号処理部 30 の構成を、図 1 を用いて説明する。

【 0 0 4 4 】

信号処理部 30 は、アナログフロントエンド（A F E）117、A / D コンバータ（A D C）118、出力処理回路 119、全体制御・演算部 120、及びタイミング制御回路（T G）113 を含む。

【 0 0 4 5 】

A F E 117 は、第 1 の画像信号を撮像装置 20 から受ける。A F E 117 は、第 1 の画像信号に増幅処理等の所定の処理を行い、処理後の第 1 の画像信号を A D C 118 へ出力する。

【 0 0 4 6 】

また、A F E 117 は、第 2 の画像信号を撮像装置 20 から受ける。A F E 117 は、第 2 の画像信号に増幅処理及び O B クランプ処理等の所定の処理を行う。O B クランプ処理において、A F E 117 は、遮光領域 S A の画素から出力された信号を用いて、有効領域 E A の画素から出力された信号（第 2 の画像信号）の黒レベルを補正する。A F E 117 は、処理後の第 2 の画像信号を A D C 118 へ出力する。

【 0 0 4 7 】

10

20

30

40

50

A D C 1 1 8 は、第1の画像信号を A F E 1 1 7 から受ける。A D C 1 1 8 は、受けた第1の画像信号（アナログ信号）を A / D 変換して第1の画像信号（デジタル信号）を生成する。A D C 1 1 8 は、生成した第1の画像信号（デジタル信号）を出力処理回路 1 1 9 へ出力する。

【 0 0 4 8 】

また、A D C 1 1 8 は、第2の画像信号を A F E 1 1 7 から受ける。A D C 1 1 8 は、受けた第2の画像信号（アナログ信号）を A / D 変換して第2の画像信号（デジタル信号）を生成する。A D C 1 1 8 は、生成した第2の画像信号（デジタル信号）を出力処理回路 1 1 9 へ出力する。

【 0 0 4 9 】

出力処理回路 1 1 9 は、第1の画像信号（デジタル信号）を A D C 1 1 8 から受ける。出力処理回路 1 1 9 は、第1の画像信号（デジタル信号）に各種の補正等の演算処理を行い、参照画像データを生成する。出力処理回路 1 1 9 は、参照画像データに応じて、複数の列増幅部 1 1 5 a , 1 1 5 b における増幅率のばらつきを低減するように、複数の列増幅部 1 1 5 a , 1 1 5 b のそれぞれの増幅率を決定する。出力処理回路 1 1 9 は、決定した増幅率に関する情報を全体制御・演算部 1 2 0 へ供給する。

【 0 0 5 0 】

また、出力処理回路 1 1 9 は、第2の画像信号（デジタル信号）を A D C 1 1 8 から受ける。出力処理回路 1 1 9 は、第2の画像信号（デジタル信号）に各種の補正等の演算処理を行い、表示用又は記録用の画像データを生成する。出力処理回路 1 1 9 は、表示用又は記録用の画像データを全体制御・演算部 1 2 0 へ供給する。

【 0 0 5 1 】

全体制御・演算部 1 2 0 は、決定した増幅率に関する情報を出力処理回路 1 1 9 から受ける。全体制御・演算部 1 2 0 は、決定した増幅率に応じて、T G 1 1 3 を制御する。

【 0 0 5 2 】

また、全体制御・演算部 1 2 0 は、表示用又は記録用の画像データを出力処理回路 1 1 9 から受ける。全体制御・演算部 1 2 0 は、表示用の画像データに応じた画像が表示部（図示せず）に表示されるように、各部を制御する。全体制御・演算部 1 2 0 は、記録用の画像データが記録媒体（図示せず）に記録されるように、各部を制御する。

【 0 0 5 3 】

T G 1 1 3 は、全体制御・演算部 1 2 0 に制御されて、撮像装置 2 0 における垂直走査回路 1 1 2 、補正信号出力回路 1 1 4 、画素信号読み出し回路 1 1 5 、及び水平走査回路 1 1 6 のそれぞれに駆動信号を供給する。

【 0 0 5 4 】

例えば、T G 1 1 3 は、決定された増幅率に応じた駆動信号を画素信号読み出し回路 1 1 5 へ供給することにより、決定された増幅率で第1の信号と第2の信号との差分を増幅するように複数の列増幅部 1 1 5 a , 1 1 5 b のそれぞれを制御する。この結果、各列の列増幅部 1 1 5 a , 1 1 5 b は、第1の画像信号に応じて複数の列増幅部における増幅率のばらつきを低減するように決定された増幅率で第1の信号と第2の信号との差分を増幅することにより第2の画像信号を生成する。

【 0 0 5 5 】

次に、列増幅部の構成を、図 2 を用いて説明する。列増幅部 1 1 5 a の構成を例示的に説明するが、他の列増幅部 1 1 5 b の構成も列増幅部 1 1 5 a の構成と同様である。

【 0 0 5 6 】

列増幅部 1 1 5 a は、入力容量 1 0 8 、帰還容量 1 0 9 、演算増幅器 1 1 0 、リセットスイッチ 1 0 9 1 、及び設定部 1 0 9 2 を含む。

【 0 0 5 7 】

入力容量 1 0 8 は、第1の電極と第2の電極とを含む。第1の電極には、画素配列 P A における各列の画素 P 又は参照信号供給部 1 1 4 a から列信号線 1 0 5 を介して伝達された信号が入力される。第2の電極は、第1の電極に対向している。第2の電極は、演算増

10

20

30

40

50

幅器 110 の反転入力端子に接続されている。

【0058】

帰還容量 109 は、演算増幅器 110 の反転入力端子と出力端子とに接続されている。帰還容量 109 は、演算増幅器 110 の出力端子から反転入力端子へ帰還をかけるように構成されている。帰還容量 109 は、その容量値が可変である。

【0059】

演算増幅器 110 は、参照信号供給部 114a から列信号線 105 を介して第 1 の参照信号と第 2 の参照信号とをそれぞれ異なるタイミングで受ける。入力容量 108 と演算増幅器 110 とは、クランプ回路として動作し、第 1 の参照信号と第 2 の参照信号との差分をとることにより第 1 の差分信号を生成する。演算増幅器 110 は、第 1 の差分信号を入力容量 108 と帰還容量 109 との容量比に応じた所定の増幅率（反転ゲイン）で増幅することにより、第 1 の画像信号を生成する。すなわち、演算増幅器 110 は、第 1 の参照信号と第 2 の参照信号との差分を増幅する CDS 处理を行うことにより、第 1 の画像信号を生成する。

【0060】

リセットスイッチ 1091 は、演算増幅器 110 の反転入力端子と出力端子とに接続されている。リセットスイッチ 1091 は、オンすることにより、演算増幅器 110 の出力端子と反転入力端子とを短絡して演算増幅器 110 をリセットする。これにより、演算増幅器 110 の出力端子から演算増幅器 110 のオフセットが出力されるようになる。

【0061】

設定部 1092 は、入力容量 108 と帰還容量 109 との容量比に応じた増幅率が、第 1 の画像信号に応じて複数の列増幅部における増幅率のばらつきを低減するように決定された増幅率になるように、帰還容量の容量値を制御する。すなわち、設定部 1092 は、第 1 の画像信号に応じて複数の列増幅部における増幅率のばらつきを低減するように決定された増幅率に応じた容量値に帰還容量を制御する。これにより、演算増幅器 110 は、入力された信号を、入力容量 108 の容量値と帰還容量 109 の制御後の容量値との比に応じた所定の増幅率（反転ゲイン）で増幅するようになる。

【0062】

すなわち、演算増幅器 110 は、画素配列 PA における各列の画素 P から列信号線 105 を介して第 1 の信号と第 2 の信号とをそれぞれ異なるタイミングで受ける。演算増幅器 110 は、設定部 1092 により設定された増幅率で、第 1 の信号と第 2 の信号との差分を増幅する CDS 处理を行うことにより、第 2 の画像信号を生成する。

【0063】

次に、参照信号供給部の構成を、図 2 を用いて説明する。参照信号供給部 114a の構成を例示的に説明するが、他の参照信号供給部 114b の構成も参照信号供給部 114a の構成と同様である。

【0064】

参照信号供給部 114a は、クリップ MOS トランジスタ 106 を有する。クリップ MOS トランジスタ 106 は、そのゲートに TG113 からアクティブな信号が供給された際に、オンして、そのドレインに供給された所定の参照信号 VCLIP をそのソースへ出力する。

【0065】

クリップ MOS トランジスタ 106 は、そのゲートに TG113 からアクティブな信号が供給された際に、そのドレインに第 1 の参照信号 VCLIPH が供給されているタイミングで、ソースを介して列信号線 105 へ第 1 の参照信号 VCLIPH を出力する。

【0066】

クリップ MOS トランジスタ 106 は、そのゲートに TG113 からアクティブな信号が供給された際に、そのドレインに第 2 の参照信号 VCLIPL が供給されているタイミングで、ソースを介して列信号線 105 へ第 2 の参照信号 VCLIPL を出力する。

【0067】

10

20

30

40

50

このようにして、各列の参照信号供給部 114a, 114b は、列信号線へ異なるタイミングで第1の信号と第2の信号とが output される前に、第1の参照信号 VCLIPH と第2の参照信号 VCLIPL とを異なるタイミングで列信号線 105 へ output する。

【0068】

次に、撮像装置 20 の動作を、図 3 を用いて説明する。図 3 は、撮像装置 20 の動作を示すタイミングチャートである。

【0069】

タイミング T1 では、垂直走査回路 112 が、パルス PRESA をアクティブにし、パルス PRESA とパルス PRESS との論理和のパルス PRES をリセット制御線経由で全行の画素 P へ供給する。これにより、全行の画素 P においてリセット部 102 が電荷電圧変換部 104 を第2の電位 (VRESL) にリセットするので、全行の画素 P が一括して非選択状態になる。 10

【0070】

タイミング T2 では、TG113 が、パルス PCLIP をアクティブにする。これにより、各列のクリップ MOS トランジスタ 106 は、オンして、第1の参照信号 VCLIPH を列信号線 105 へ output する。これにより、各列の列増幅部 115a, 115b は、第1の参照信号 VCLIPH を受ける。

【0071】

タイミング T3 では、TG113 が、パルス S\_HOLD(N) をアクティブにする。これにより、各列の列増幅部 115a, 115b のオフセットが、各列の画素の第1の N 信号として各列の列増幅部 115a, 115b からラインメモリ 1151 へ転送される。 20

【0072】

タイミング T4 では、TG113 が、パルス S\_HOLD(N) をノンアクティブにする。これにより、ラインメモリ 1151 は、転送された各列の画素の第1の N 信号を保持する。

【0073】

タイミング T5 では、TG113 が、パルス PCLIP をアクティブにする。これにより、各列のクリップ MOS トランジスタ 106 は、オンして、第2の参照信号 VCLIPL を列信号線 105 へ output する。これにより、各列の列増幅部 115a, 115b は、第2の参照信号 VCLIPL を受けるとともに、第1の参照信号 VCLIPH と第2の参照信号 VCLIP との差分を増幅することにより第1の画像信号を生成する。 30

【0074】

タイミング T6 では、TG113 が、パルス S\_HOLD(S) をアクティブにする。これにより、各列の列増幅部 115a, 115b は、そのオフセットが第1の画像信号に重畳された信号が、各列の画素の第1の S 信号として各列の列増幅部 115a, 115b からラインメモリ 1151 へ転送される。

【0075】

タイミング T7 では、TG113 が、パルス S\_HOLD(S) をノンアクティブにする。これにより、ラインメモリ 1151 は、転送された各列の画素の第1の S 信号を保持する。 40

【0076】

タイミング T8 ~ T9 の期間では、水平走査回路 116 が、各列の水平転送信号 HT を順次にアクティブにする。これにより、水平走査回路 116 は、画素信号読み出し回路 115 におけるラインメモリ 1151 により保持された各列の画素の第1の S 信号及び第1の N 信号を順次に出力回路 131 へ転送させる。出力回路 131 は、転送された第1の S 信号と第1の N 信号との差分を演算することにより、列増幅部のオフセットが除去された第1の画像信号を得る。出力回路 131 は、第1の画像信号を AFE117 へ output する。

【0077】

これにより、AFE117 は、第1の画像信号を撮像装置 20 から受ける。AFE117 は、第1の画像信号に増幅処理等の所定の処理を行い、処理後の第1の画像信号を AD 50

C 118 へ出力する。

【0078】

ADC118 は、第1の画像信号を AFE117 から受ける。ADC118 は、受けた第1の画像信号（アナログ信号）を A/D 変換して第1の画像信号（デジタル信号）を生成する。ADC118 は、生成した第1の画像信号（デジタル信号）を出力処理回路119 へ出力する。

【0079】

出力処理回路119 は、第1の画像信号（デジタル信号）を ADC118 から受ける。出力処理回路119 は、第1の画像信号（デジタル信号）に各種の補正等の演算処理を行い、参照画像データを生成する。出力処理回路119 は、参照画像データに応じて、複数の列増幅部115a, 115b における増幅率のばらつきを低減するように、複数の列増幅部115a, 115b のそれぞれの増幅率を決定する。

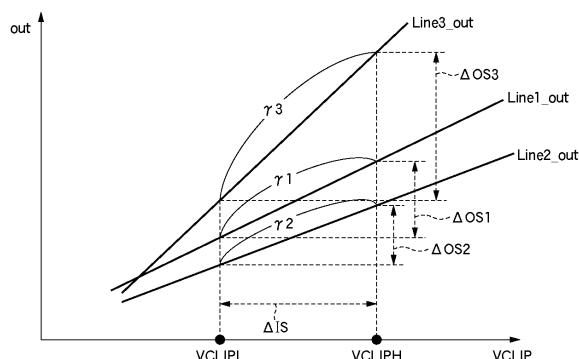

【0080】

例えば、画素配列が2行3列の画素で構成されている場合を考える。この場合、図4に示すように、第1の参照信号 VCLIPH のレベルと第2の参照信号 VCLIPL のレベルとは、いずれも、複数の列（Line 1 ~ 3）に対して共通である。すなわち、列増幅部への入力信号は、複数の列に対して共通の IS である。そこで、各列（Line 1 ~ 3）の列増幅部からの出力信号 OS1 ~ OS3 をモニターすることにより、複数の列増幅部における増幅率のばらつきを知ることができる。すなわち、第1の列 Line 1 の列増幅部における増幅率は、

$$1 = OS1 / (IS) \cdots \text{数式 1}$$

と求まる。第2の列 Line 2 の列増幅部における増幅率は、

$$2 = OS2 / (IS) \cdots \text{数式 2}$$

と求まる。第3の列 Line 3 の列増幅部における増幅率は、

$$3 = OS3 / (IS) \cdots \text{数式 3}$$

と求まる。そして、複数の列増幅部における増幅率のばらつきを低減するように、各列（Line 1 ~ 3）の列増幅部における増幅率を設定するための係数を、例えば、次のように決定する。すなわち、第1の列 Line 1 の列増幅部に対する係数を、

$$K1 = 1 / 1 = 1 \cdots \text{数式 4}$$

に決定し、第2の列 Line 2 の列増幅部に対する係数を、

$$K2 = 1 / 2 \cdots \text{数式 5}$$

に決定し、第1の列 Line 1 の列増幅部に対する係数を、

$$K3 = 1 / 3 \cdots \text{数式 6}$$

に決定する。出力処理回路119 は、例えば、増幅率を設定するための係数を、上述の決定した増幅率に関する情報として全体制御・演算部120 へ供給する。

【0081】

全体制御・演算部120 は、決定した増幅率に関する情報を出力処理回路119 から受ける。全体制御・演算部120 は、決定した増幅率に応じて、T G113 を制御する。

【0082】

T G113 は、全体制御・演算部120 に制御されて、撮像装置20 における垂直走査回路112、補正信号出力回路114、画素信号読み出し回路115、及び水平走査回路116 のそれぞれに駆動信号を供給する。

【0083】

例えば、T G113 は、決定された増幅率に関する駆動信号を各列の列増幅部115a, 115b へ供給する。決定された増幅率に関する駆動信号は、例えば、増幅率を設定するための係数を示す駆動信号である。これにより、例えば、列増幅部115a の設定部1092 は、その駆動信号に応じて、決定された増幅率に列増幅部115a における増幅率を設定する。

【0084】

タイミングT10 では、垂直走査回路112 が、パルスPRESA をアクティブにし、

10

20

30

40

50

パルス P R E S A とパルス P R E S S との論理和のパルス P R E S をリセット制御線経由で全行の画素 P へ供給する。これにより、全行の画素 P においてリセット部 102 が電荷電圧変換部 104 を第 2 の電位 (V R E S L ) にリセットするので、全行の画素 P が一括して非選択状態になる。

【 0085 】

タイミング T 11 では、垂直走査回路 112 が、パルス P R E S A をノンアクティブにし、選択行のパルス P R E S S をアクティブにすることにより、アクティブなパルス P R E S を選択行の画素のみに供給する。これにより、選択行の画素 P のみにおいてリセット部 102 が電荷電圧変換部 104 を第 1 の電位 (V R E S H ) にリセットするので、選択行の画素 P のみが選択状態になる。選択状態の画素 P では、出力部 103 が第 1 の信号 (ノイズ信号) を列信号線 105 へ出力する。これにより、各列の列増幅部 115a, 115b は、第 1 の信号を受ける。

【 0086 】

タイミング T 12 では、T G 113 が、パルス P C L I P を所定のクリップレベル (第 1 の参照信号 V C L I P H + 閾値電圧) にする。

【 0087 】

列信号線 105 のレベルがクリップレベルよりも低くなることがある。

【 0088 】

例えば、被写界に太陽などの非常に明るい被写体が含まれる場合、その被写体の像が形成された画素における電荷電圧変換部 104 上にも強い光があたることがある。電荷電圧変換部 104 は、通常遮光されてはいるものの、光の漏れこみや光電変換部 100 からの電荷の溢れこみを考えると、リセット後の電位変動を完全にゼロにすることはできない。そのため、非常に強い光が照射された場合、第 1 の信号 (ノイズ信号) のレベルが黒レベルから白レベルへ近づくように変動し、信号のダイナミックレンジを圧迫してしまう。結果として、強い光があたった画素から画像信号のレベルが黒階調へ沈むという高輝度黒沈み現象が発生する。

【 0089 】

例えば太陽を撮影した場合には太陽の中心部分が黒い点となり不自然な画像になる。この問題は、被写体と光電変換部との間にメカニカルシャッターを設ければ、静止画に対して解決できる。静止画撮影時においても安価なカメラではメカニカルシャッターを省略する場合が多いので、静止画に対して高輝度黒沈み現象を抑制できないことがある。

【 0090 】

また、動画撮影時にメカニカルシャッターを併用することは、露光時間、コマ速を確保する上で大きなデメリットとなるため、実現性が低い。これにより、動画に対して高輝度黒沈み現象を抑制できないことがある。

【 0091 】

それに対して、本実施形態では、列信号線 105 のレベルがクリップレベルよりも低い場合、各列のクリップMOSトランジスタ 106 はオンする。一方、列信号線 105 のレベルがクリップレベルよりも高い場合、各列のクリップMOSトランジスタ 106 はオフしたままである。

【 0092 】

すなわち、クリップMOSトランジスタ 106 は、第 1 の信号と第 1 の参照信号 V C L I P H とを比較する。各列のクリップMOSトランジスタ 106 は、比較した結果に応じて、列信号線 105 に出力されている第 1 の信号を第 1 の参照信号 V C L I P H で置き換えるように、第 1 の参照信号 V C L I P H を列信号線 105 へ出力する。第 1 の参照信号 V C L I P H が列信号線 105 へ出力された場合、各列の列増幅部 115a, 115b は、第 1 の信号に代えて、第 1 の参照信号 V C L I P H を受ける。

【 0093 】

タイミング T 13 では、T G 113 が、パルス S\_HOLD (N) をアクティブにする。これにより、各列の列増幅部 115a, 115b のオフセットが、各列の画素の第 2 の

N信号として各列の列増幅部 115a, 115b からラインメモリ 1151 へ転送される。

。

【0094】

タイミング T14 では、TG113 が、パルス S\_HOLD(N) をノンアクティブにする。これにより、ラインメモリ 1151 は、転送された各列の画素の第 2 の N 信号を保持する。

【0095】

タイミング T15 では、垂直走査回路 112 が、選択行の転送信号 P\_TX をアクティブにする。これにより、選択状態の画素 P では、転送部 101 が光電変換部 100 の電荷を電荷電圧変換部 104 へ転送し、出力部 103 が第 2 の信号(光信号)を列信号線 105 へ出力する。これにより、各列の列増幅部 115a, 115b は、第 2 の信号を受ける。

10

【0096】

ここで、タイミング T12 において列信号線 105 のレベルがクリップレベルよりも高い場合、各列の列増幅部 115a, 115b は、第 1 の信号と第 2 の信号との差分を増幅することにより第 2 の画像信号を生成する。

【0097】

一方、タイミング T12 において列信号線 105 のレベルがクリップレベルよりも低い場合、各列の列増幅部 115a, 115b は、第 1 の参照信号 VCLIPH と第 2 の信号との差分を増幅することにより第 2 の画像信号を生成する。この場合、第 1 の参照信号 VCLIPH をノイズ信号として CDS 处理を行うので、第 2 の画像信号のレベルが黒階調へ沈むことを抑制できる。すなわち、高輝度黒沈み現象を抑制できる。

20

【0098】

いずれの場合も、各列の列増幅部 115a, 115b は、第 1 の画像信号に応じて複数の列増幅部における増幅率のばらつきを低減するように決定された増幅率で 2 つの信号の差分を増幅することにより第 2 の画像信号を生成する。

【0099】

タイミング T16 では、TG113 が、パルス S\_HOLD(S) をアクティブにする。これにより、各列の列増幅部 115a, 115b は、そのオフセットが第 2 の画像信号に重畠された信号が、各列の画素の第 2 の S 信号として各列の列増幅部 115a, 115b からラインメモリ 1151 へ転送される。

30

【0100】

タイミング T17 では、TG113 が、パルス S\_HOLD(S) をノンアクティブにする。これにより、ラインメモリ 1151 は、転送された各列の画素の第 2 の S 信号を保持する。

【0101】

タイミング T18 ~ T19 の期間では、水平走査回路 116 が、各列の水平転送信号 HT を順次にアクティブにする。これにより、水平走査回路 116 は、画素信号読み出し回路 115 におけるラインメモリ 1151 により保持された各列の画素の第 2 の S 信号及び第 2 の N 信号を順次に出力回路 131 へ転送させる。出力回路 131 は、転送された第 2 の S 信号と第 2 の N 信号との差分を演算することにより、列増幅部(演算増幅器)のオフセットが除去された第 2 の画像信号を得る。出力回路 131 は、第 2 の画像信号を AFE 117 へ出力する。

40

【0102】

これにより、AFE 117 は、第 2 の画像信号を撮像装置 20 から受ける。AFE 117 は、第 2 の画像信号に増幅処理及び OB クランプ処理等の所定の処理を行う。OB クランプ処理において、AFE 117 は、遮光領域 SA の画素から出力された信号を用いて、有効領域 EA の画素から出力された信号の黒レベルを補正する。AFE 117 は、処理後の第 2 の画像信号を ADC 118 へ出力する。

【0103】

ADC 118 は、第 2 の画像信号を AFE 117 から受ける。ADC 118 は、受けた

50

第2の画像信号(アナログ信号)をA/D変換して第2の画像信号(デジタル信号)を生成する。ADC118は、生成した第2の画像信号(デジタル信号)を出力処理回路119へ出力する。

【0104】

出力処理回路119は、第2の画像信号(デジタル信号)をADC118から受ける。出力処理回路119は、第2の画像信号(デジタル信号)に各種の補正等の演算処理を行い、表示用又は記録用の画像データを生成する。出力処理回路119は、表示用又は記録用の画像データを全体制御・演算部120へ供給する。

【0105】

全体制御・演算部120は、表示用又は記録用の画像データを出力処理回路119から受ける。全体制御・演算部120は、表示用の画像データに応じた画像が表示部(図示せず)に表示されるように、各部を制御する。全体制御・演算部120は、記録用の画像データが記録媒体(図示せず)に記録されるように、各部を制御する。

10

【0106】

以上のように、本実施形態によれば、第1の画像信号に応じて複数の列増幅部における増幅率のばらつきを低減するように決定された値の増幅率で第1の信号と第2の信号との差分を増幅することにより画像信号(第2の画像信号)を生成することができる。この結果、列増幅部115a, 115bから出力される画像信号のレベルが列ごとにばらつかないようになることができる。複数の列増幅部における増幅率のばらつきに起因した固定パターンノイズを低減できる。この結果、画像信号(第2の画像信号)により得られた画像における縦筋状のノイズを抑制することができる。

20

【0107】

なお、撮像システムは、N信号とS信号との差分をとるCDS処理を、撮像装置20以外で、例えば、AFE117で行うように構成されていても良い。

【0108】

この場合、複数の列増幅部のそれぞれは、第1の参照信号と第2の参照信号とをそれぞれ増幅してラインメモリ及び出力回路経由でAFE117へ出力する。AFE117は、その出力された増幅後の第1の参照信号と増幅後の第2の参照信号との差分をとることにより第1の画像信号を生成する。また、複数の列増幅部のそれぞれは、決定された増幅率で第1の信号と第2の信号とをそれぞれ増幅してラインメモリ及び出力回路経由でAFE117へ出力する。AFE117は、複数の列増幅部のそれぞれから出力された増幅後の第1の信号と増幅後の第2の信号との差分をとることにより第2の画像信号を生成する。

30

【0109】

この場合でも、各列の第1の画像信号のレベルに応じて、各列の列増幅部における増幅率のばらつきを把握することができるので、各列の列増幅部における増幅率のばらつきを低減するように増幅率を決定できる。

【0110】

なお、画素配列に遮光領域SAを設ける代わりに、本撮影の前に、画素配列の各画素を絞りで遮光状態にして撮像することにより取得された遮光画像信号を読み出し、その読み出した遮光画像信号を黒レベルの基準信号として使用しても良い。この場合、遮光領域SAを設けなくて良い分だけ画素配列の面積を低減できるので、撮像装置20のチップサイズを低減できる。

40

【0111】

一方で、読み出し速度を優先させる場合には、上記の実施形態のように、画素配列に遮光領域SAを設けることが好ましい。

【0112】

また、撮像装置20、TG113、AFE117、ADC118、及び出力処理回路119は、同一チップ上に配されていても良い。

【0113】

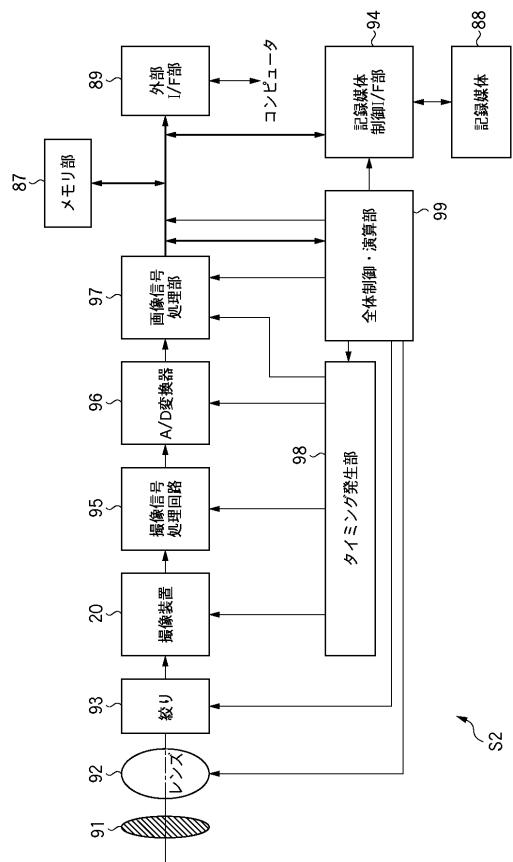

次に、上記の撮像装置20を適用した撮像システムの別の一例を、図5に示す。図5は

50

、本発明の実施形態に係る撮像システム S 2 の構成の別の一例を示す図である。

【 0 1 1 4 】

撮像システム S 2 は、図 5 に示すように、主として、光学系、撮像装置 2 0 及び信号処理部を備える。光学系は、主として、シャッター 9 1、撮影レンズ 9 2 及び絞り 9 3 を備える。信号処理部は、主として、撮像信号処理回路 9 5、A / D 変換器 9 6、画像信号処理部 9 7、メモリ部 8 7、外部 I / F 部 8 9、タイミング発生部 9 8、全体制御・演算部 9 9、記録媒体 8 8 及び記録媒体制御 I / F 部 9 4 を備える。なお、信号処理部は、記録媒体 8 8 を備えなくても良い。

【 0 1 1 5 】

シャッター 9 1 は、光路上において撮影レンズ 9 2 の手前に設けられ、露出を制御する。シャッター 9 1 は、撮影レンズ 9 2 をプロテクトする機能とメインスイッチとしての機能とを兼ねる。

【 0 1 1 6 】

撮影レンズ 9 2 は、入射した光を屈折させて、撮像装置 2 0 の画素配列（撮像面）に被写体の像を形成する。

【 0 1 1 7 】

絞り 9 3 は、光路上において撮影レンズ 9 2 と撮像装置 2 0 との間に設けられ、撮影レンズ 9 2 を通過後に撮像装置 2 0 へ導かれる光の量を調節する。

【 0 1 1 8 】

撮像装置 2 0 は、画素配列に形成された被写体の像を画像信号に変換する。撮像装置 2 0 は、その画像信号を画素配列から読み出して出力する。

【 0 1 1 9 】

撮像信号処理回路（A F E）9 5 は、撮像装置 2 0 に接続されており、撮像装置 2 0 から出力された画像信号に対して増幅処理や O B クランプ処理などの処理を行う。

【 0 1 2 0 】

A / D 変換器（A D C）9 6 は、撮像信号処理回路 9 5 に接続されており、撮像信号処理回路 9 5 から出力された処理後の画像信号（アナログ信号）をデジタル信号へ変換する。

【 0 1 2 1 】

画像信号処理部（出力処理回路）9 7 は、A / D 変換器 9 6 に接続されており、A / D 変換器 9 6 から出力された画像信号（デジタル信号）に各種の補正等の演算処理を行い、画像データを生成する。この画像データは、メモリ部 8 7、外部 I / F 部 8 9、全体制御・演算部 9 9 及び記録媒体制御 I / F 部 9 4 などへ供給される。

【 0 1 2 2 】

メモリ部 8 7 は、画像信号処理部 9 7 に接続されており、画像信号処理部 9 7 から出力された画像データを一時的に記憶する。

【 0 1 2 3 】

外部 I / F 部 8 9 は、画像信号処理部 9 7 に接続されている。これにより、画像信号処理部 9 7 から出力された画像データを、外部 I / F 部 8 9 を介して外部の機器（パソコン等）へ転送する。これにより、ユーザは、外部の機器（パソコン等）を介して画像の加工を行ってもよい。

【 0 1 2 4 】

タイミング発生部（T G）9 8 は、撮像装置 2 0 、撮像信号処理回路 9 5 、A / D 変換器 9 6 及び画像信号処理部 9 7 に接続されている。これにより、撮像装置 2 0 、撮像信号処理回路 9 5 、A / D 変換器 9 6 及び画像信号処理部 9 7 へタイミング信号を供給する。そして、撮像装置 2 0 、撮像信号処理回路 9 5 、A / D 変換器 9 6 及び画像信号処理部 9 7 がタイミング信号に同期して動作する。

【 0 1 2 5 】

なお、撮像信号処理回路 9 5 、A / D 変換器 9 6 、画像信号処理部 9 7 、及びタイミング発生部 9 8 は、撮像装置 2 0 と同一チップ上に形成しても良い。

10

20

30

40

50

## 【0126】

全体制御・演算部99は、タイミング発生部98、画像信号処理部97及び記録媒体制御I/F部94に接続されており、タイミング発生部98、画像信号処理部97及び記録媒体制御I/F部94を全体的に制御する。

## 【0127】

例えば、全体制御・演算部99は、画像信号処理部97から受けた画像データに基づいて、測光を行う。全体制御・演算部99は、測光を行った結果に応じて、適正な露出値が得られるように、絞り93の開度や撮像装置20における各画素の電荷蓄積時間を調節する。

## 【0128】

10

あるいは、例えば、全体制御・演算部99は、画像信号処理部97から受けた画像データに基づいて、測距を行う。全体制御・演算部99は、測距を行った結果に応じて、合焦状態になるように、撮影レンズ92を駆動制御する。

## 【0129】

記録媒体88は、記録媒体制御I/F部94に取り外し可能に接続されている。これにより、画像信号処理部97から出力された画像データを、記録媒体制御I/F部94を介して記録媒体88へ記録する。記録媒体88は、例えば、半導体メモリ等を用いて構成されている。

## 【0130】

20

以上の構成により、撮像装置20において良好な画像信号が得られれば、良好な画像(画像データ)を得ることができる。

## 【図面の簡単な説明】

## 【0131】

【図1】本発明の実施形態に係る撮像システムS1の構成の一例を示す図。

【図2】撮像装置20の回路構成を示す図。

【図3】撮像装置20の動作を示すタイミングチャート。

【図4】各列の列増幅部のばらつきを低減する方法を説明するための図。

【図5】本発明の実施形態に係る撮像システムS2の構成の別の一例を示す図。

## 【符号の説明】

## 【0132】

30

20 撮像装置

S1、S2 撮像システム

【 図 1 】

【 図 2 】

【 図 3 】

【 図 4 】

【図5】

---

フロントページの続き

(72)発明者 松田 崇

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 木方 庸輔

(56)参考文献 特開平08-289204 (JP, A)

特開2002-044370 (JP, A)

特開2008-034974 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/335