## (10) **DE 103 44 039 A1** 2005.04.14

(12)

# Offenlegungsschrift

(21) Aktenzeichen: 103 44 039.9(22) Anmeldetag: 23.09.2003(43) Offenlegungstag: 14.04.2005

(51) Int Cl.7: **H01L 27/115**

(71) Anmelder:

Infineon Technologies AG, 81669 München, DE

(74) Vertreter:

Müller - Hoffmann & Partner Patentanwälte, 81667 München

(72) Erfinder:

Reisinger, Hans, 82031 Grünwald, DE; Gutsche, Martin, 84405 Dorfen, DE; Seidl, Harald, 85622 Feldkirchen, DE; Gordon, Roy, Cambridge, Mass., (56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

US2003/01 55 229 A1 US2003/01 24 783 A1 US2002/01 15 252 A1 US2002/00 24 092 A1 US2002/00 14 647 A1

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

Prüfungsantrag gemäß § 44 PatG ist gestellt.

(54) Bezeichnung: Nichtflüchtige Speicherzellen auf Basis von SONOS-Technologie

(57) Zusammenfassung: Die Erfindung beschreibt elektrisch programmierbare nicht-flüchtige Speicher und ein Verfahren zur Herstellung dieser Speicher, wobei die Speicher auf Basis von Treshold veränderbaren MOSFETs gebildet sind und sich durch eine Ladung speichernde Schicht kennzeichnen, die eine Verbindung der allgemeinen Formel  $HfO_xN_v$  aufweist.

## **Beschreibung**

**[0001]** Die Erfindung betrifft elektrisch programmierbare nichtflüchtige Speicher auf der Basis von SO-NOS-Technologie.

[0002] Für eine dauerhafte Speicherung von Daten auf Basis von nichtflüchtigen Halbleiterspeichern werden in der Regel Feldeffekt-Transistor-Strukturen benutzt, bei denen der durch die Spannung an der Steuerelektrode (Gate-Elektrode) regelbare Stromfluss durch den Transistorkanal den Zustand eines Bits charakterisiert. Ein solcher Transistor besteht aus einer Gate-Elektrode, die zwischen eine Quelle (Source) und Senke (Drain) einen leitfähigen Kanal oder eine isolierende Raumladungszone aufweisen. Den Übergang vom leitfähigen zum isolierenden Zustand im Transistorkanal charakterisiert die sogenannte Schwellspannung (Tresholdspannung), wobei die Zustände "1" bzw. "0" einen der beiden Zustände (leitender/nichtleitender Kanal) entsprechen.

[0003] Bisher sind drei Typen von Speichern auf Basis von Halbleiterfeldeffekttransistoren (Metal-Oxid Semiconductor Field Effect Transistor (MOSFET)) gebräuchlich. Der erste Typ sind sogenannte FLO-TOX (Floating Gate Tunneling Oxide) Speicher, die unter dem Gate ein vollständig zwischen Siliciumdio-xid(SiO<sub>2</sub>)Schichten isoliertes floating gate aufweisen, auf dem die Ladungsdichte verändert werden kann. Durch die Veränderung der Ladungsdichte auf dem floating gate kann auch der Treshold des MOSFETS verändert werden. Das sogenannte Tunneloxid, das zwischen Substrat und floating gate angeordnet ist, weist eine Dicke von mindestens 10 nm auf, so dass dadurch die zum Programmieren benötigten Spannungen nicht unter 10 V gesenkt werden können.

[0004] Der zweite gebräuchliche Typ der nichtflüchtigen Speicher ist MNOS- bzw. SONOS-Speicher. Dieser Typ hat statt des oben beschriebenen floating gates eine Schicht aus Siliciumnitrid (Si<sub>3</sub>N<sub>4</sub>). Die Aufgabe dieser Schicht ist die homogen verteilte Ladung zu speichern. Das Tunneloxid bei den MNOS- bzw. SONOS-Speichern beträgt circa 2 nm, die der Si<sub>3</sub>N<sub>4</sub> circa 10 nm und die des Topoxids 4 bis 5 nm. Die Programmierspannungen bei diesem Typ von nichtflüchtigen Speichern liegt knapp unterhalb von 10 V. Das Problem bei diesem Typ von Speichern ist die ungenügende charge retention bei erhöhten Temperaturen, so dass der Datenerhalt bei diesen Temperaturen nicht in genügendem Maße gewährleistet werden kann

**[0005]** Der dritte Typ der nichtflüchtigen Speicher ist NROM-Speicher (nitrated-read-only-memory-Speicher), die ähnlich wie SONOS-Speicher aufgebaut sind, wobei die Ladung auf der Si<sub>3</sub>N<sub>4</sub> Schicht nicht homogen verteilt ist, sondern die Ladung wird über hot carrier injection nur lokal bei Source oder Drain-Elek-

trode gespeichert. Wenn die Ladung lateral entlang der  $\mathrm{Si_3N_4}$  Schicht wandert, geht die gespeicherte Information verloren. Dieser Effekt begrenzt die Skalierbarkeit der NROM-Speicher, so dass die Gesamtdicke des NROM-Dielektrikums relativ hoch ist (höher als bei SONOS-Speichern) und ebenfalls nicht skalierbar ist.

#### Aufgabenstellung

[0006] Es besteht daher Bedarf an die weiteren nichtflüchtigen Speicher auf Basis der MOS-FET-Technologie, die die Treibfähigheit der MOSFET erhöht und gleichzeitig die Spannungen beim Schreiben und Löschen als auch beim Lesen verringert.

**[0007]** Der vorliegenden Erfindung liegt die Aufgabe zu Grunde, die SONOS- bzw. NROM-Speicher so zu gestalten, dass eine Skalierbarkeit dieser Speicher möglich ist und gleichzeitig die Spannungen beim Schreiben und Löschen als auch beim Lesen verringert werden.

[0008] Die Lösung der Aufgabe ist, dass gemäß der vorliegenden Erfindung die Ladung speichernde Schicht ein Dielektrikum mit der allgemeinen Formel HfO,N, aufweist. Die Top- und die Bottom-Schicht des Dielektrikums bestehen weiterhin aus Siliciumdioxid. Die Aufgabe dieser Schichten ist es, die Speicherschicht vollkommen zu isolieren, so dass die Leckströme weniger als 10<sup>-15</sup> A/cm<sup>2</sup> betragen. Das ist notwendig, da wenn die Leckstromdichten höher als circa 10<sup>-15</sup> A/cm<sup>2</sup> betragen, vollständiger Ladungsund damit Datenverlust zu beobachten ist. Die Feldstärken des erfindungsgemäßen nichtflüchtigen Speichers liegen bei 1 bis 2 MV/cm am Bottomoxid bei V<sub>gate</sub> = 0. Die erfindungsgemäße Ladung speichernde Schicht weist eine spezifische Kapazität des gesamten Dielektrikums, die der bisherigen Si<sub>3</sub>N<sub>4</sub>-Schicht sehr ähnlich ist und circa 300 nF/cm<sup>2</sup> entspricht, auf. Bei dieser spezifischen Kapazität wird eine in Si<sub>3</sub>N<sub>4</sub> getrappte Ladung von 600 nC/cm<sup>2</sup> benötigt, falls sich die Ladung etwa in der Mitte der Si<sub>3</sub>N<sub>4</sub>-Schicht befindet. Die Ladungsträgerdichte der erfindungsgemäßen Schicht ist mit Si<sub>3</sub>N<sub>4</sub>-Schicht bei einer Dicke von 10 nm vergleichbar und beträgt 4·10<sup>12</sup>/cm<sup>2</sup> bzw. 4·10<sup>18</sup>/cm<sup>2</sup>. Das durch diese Ladung bei Gatespannung von 0 im Bottomoxid erzeugte Feld beträgt 1 bis 2 MV/cm.

[0009] Ein wesentlicher Vorteil der erfindungsgemäßen Schicht ist, dass der Abstand zwischen dem Leitungsband und dem Trapzustand, im Nachfolgenden auch als Bindungsenergie bezeichnet, größer ist, als 1 eV, wie in der herkömmlichen Si₃N₄-Schicht. Der Vorteil einer höheren Bindungsenergie ist, dass der Trapping bzw. die Anregung der Elektronen ins Leitungsband, insbesondere bei erhöhten Temperaturen unwahrscheinlicher wird. Bei SONOS-Speichern wird damit Ladungsverlust von der trappenden Schicht in

das Substrat verhindert bzw. bei NROM-Speichern, wird der laterale Strom verhindert, der auch zu Datenverlusten führt.

[0010] Die elektrischen Felder in der trappenden Schicht sind proportional zur Ladungsdichte in der trappenden Schicht, die normalerweise unabhängig von sonstigen Eigenschaften immer bei ca. 4·10<sup>12</sup>/cm<sup>2</sup> liegt, um die gewünschte Tresholdverschiebung von 2 v zu erhalten. Die elektrischen Felder in der trappenden Schicht sind aber umgekehrt proportional zur Dielektrizitätskonstante ε der trappenden Schicht. Wenn also ε erhöht wird, so sinkt die Feldstärke und somit sämtliche Ströme. Wenn also wie im vorliegenden Fall ε der erfindungsgemäßen Schicht um einen Faktor 3 erhöht wird, so sinken bei gleicher Tresholdverschiebung die Feldstärke der trappenden Schicht um einen Faktor 3. Das bedeutet, dass sämtliche Ströme in der trappenden Schicht um viele Größenordnungen sinken.

[0011] Ein weiterer Vorteil von erhöhtem  $\epsilon$  ist, dass bei der angenommenen konstant gehaltenen Schichtdichte der trappenden Schicht die Kapazität steigt und damit der Spannungsabfall über der Schicht beim Programmieren sinkt.

[0012] Die erfindungsgemäße Schicht ist insbesondere der bisher benutzten Si<sub>3</sub>N<sub>4</sub>-Schicht überlegen, da die Elektronen bei erhöhten Temperaturen in der Schicht nicht wandern, so dass ein Ladungsverlust nicht stattfindet. Die Ladung speichernde Schicht gemäß der Erfindung weist eine Trapdichte auf, die der Trapdichte einer Si<sub>3</sub>N<sub>4</sub>-Schicht ähnlich ist, die Ladungsträger sind aber auf einem Energie-Niveau gebunden, das tiefer liegt als in der Si₃N₄-Schicht, da die Dielektrizitätskonstante der erfindungsgemäßen Schicht höher ist als bei einer Si<sub>3</sub>N<sub>4</sub>-Schicht (ungefähr 7). Die dadurch erzielten Vorteile sind, dass die Detrap-Wahrscheinlichkeit in der Speicherschicht als auch die Tunnelwahrscheinlichkeit von der Speicherschicht über das Tunneloxid ins Substrat verringert wird. Der weitere Vorteil ist, dass bei der gleichen Tresholdverschiebung und bei der gleichen Gesamtkapazität das elektrische Feld in der Speicherschicht um den Faktor der Erhöhung der Dielektrizitätskonstante niedriger als bei der Si<sub>3</sub>N<sub>4</sub>-Schicht liegt und dadurch die Ladung weniger beweglich ist. Die Höhe der Dielektrizitätskonstante macht ebenfalls eine Verringerung der Dicke und damit eine erhöhte spezifische Kapazität des Dielektrikums möglich, so dass eine Verringerung der Programmier- und Lesespannung erreicht werden kann.

**[0013]** In einer besonderen Ausführungsform hat sich gezeigt, dass die besten Ergebnisse mit einem Hafniumoxidnitrid der allgemeinen Formel  $HfO_xN_y$  erreichet werden, wenn das Verhältnis von x:y zwischen 1 und 1:0,6 beträgt. In diesem Fall beträgt die Dielektrizitätskonstante von Hafniumoxidnitrid circa

20 und ist circa dreimal so hoch wie die Dielektrizitätskonstante von  $Si_3N_4$ . Dadurch ist die Trapdichte wesentlich größer und die Tiefe des Traps höher als in  $Si_3N_4$ .

**[0014]** Insbesondere für die Ladung speichernde Schicht mit dieser Struktur kann eine erhebliche Verringerung der Programmier- und Lesespannung erzielt werden, da das elektrische Feld in der Speicherschicht kleiner ist. Da die Traptiefe in dieser Schicht höher liegt als bei  $\mathrm{Si}_3\mathrm{N}_4$  ist eine geringere Detrapund Tunnelwahrscheinlichkeit zu beobachten.

#### Ausführungsbeispiel

**[0015]** Die vorliegende Erfindung wird nun anhand der nachstehenden Figuren erläutert.

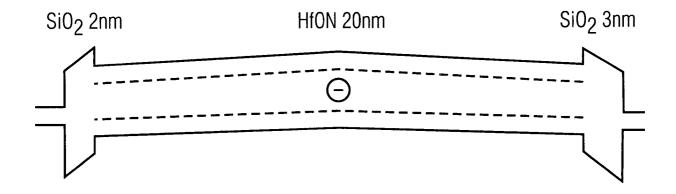

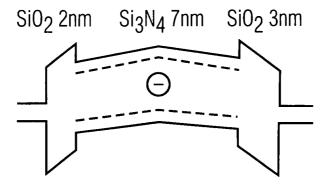

**[0016] Fig.** 1 zeigt die Ladung speichernde Schicht eines herkömmlichen SONOS-Speichers;

**[0017]** Fig. 2 zeigt die Ladung speichernde Schicht gemäß der vorliegenden Erfindung.

[0018] Der Fig. 2 ist zu entnehmen, dass die Ladung speichernde Schicht gemäß der Erfindung dieselbe (negative) Ladung aufweist wie eine  $\mathrm{Si}_3\mathrm{N}_4$ -Schicht, und dass sich die Ladung in der Mitte der Ladung speichernden Schicht befindet. Beide Schichten, die in den Fig. 1 und 2 dargestellt wurden, weisen die selbe spezifische Kapazität von circa 400 nF/cm². Die gestrichelten Linien markieren Trap-Niveaus für Elektronen und Löcher. Die rechte und die linke Elektrode sind auf gleichem Potential angelegt, so dass die angelegte Gatespannung 0 ist. In diesen Vergleichsfiguren ist eine elektrische Spannung für die HfON- Schicht um ein Faktor 3 niedriger als bei der  $\mathrm{Si}_3\mathrm{N}_4$ -Schicht.

### Patentansprüche

- 1. Elektrisch programmierbarer nichtflüchtiger Speicher auf Basis von Treshold veränderbaren MOSFETs, **dadurch gekennzeichnet**, dass die Ladung speichernde Schicht eine Verbindung der allgemeinen Formel  $HfO_xN_v$  aufweist.

- 2. Nichtflüchtiger Speicher nach Anspruch 1, dadurch gekennzeichnet, dass 1·x/y·1/0,6 beträgt.

- 3. Nichtflüchtiger Speicher nach Anspruch 1 oder 2, dadurch gekennzeichnet, dass die Dielektrizitätskonstante der Ladung speichernden Schicht circa 20 beträgt.

- 4. Nichtflüchtiger Speicher nach Anspruch 1, dadurch gekennzeichnet, dass die spezifische Kapazität circa 400 nF/cm² beträgt.

- 5. Nichtflüchtiger Speicher nach Anspruch 1 bis

- 4, dadurch gekennzeichnet, dass das Top- und Bottomoxid aus Siliciumoxid besteht.

- 6. Nichtflüchtiger Speicher nach Anspruch 1 bis 5, dadurch gekennzeichnet, dass die Feldstärke zwischen 1 und 2 MV/cm beträgt.

- 7. Verfahren zur Herstellung eines elektrisch programmierbaren nichtflüchtigen Speichers auf Basis von Treshold veränderbaren MOSFET, dadurch gekennzeichnet, dass die Ladung speichernde Schicht eine Vebindung der allgemeinen Formel  $\mathrm{HfO_xN_y}$  aufweist.

- 8. Verfahren nach Anspruch 7, dadurch gekennzeichnet, dass 1·x/y·1/0,6 beträgt.

- 9. Verfahren nach Anspruch 6 bis 8, dadurch gekennzeichnet, dass die Dielektrizitätskonstante der Ladung speichernden Schicht circa 20 beträgt.

- 10. Verfahren nach Anspruch 6 bis 9, dadurch gekennzeichnet, dass die spezifische Kapazität des Gesamtdielektrikums zwischen 300 nF/cm² und 500nF/cm² liegt.

Es folgt ein Blatt Zeichnungen

# Anhängende Zeichnungen

FIG 1

FIG 2