## (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 13 December 2007 (13.12.2007)

(10) International Publication Number WO 2007/143657 A2

(51) International Patent Classification: Not classified

(21) International Application Number:

PCT/US2007/070426

(22) International Filing Date: 5 June 2007 (05.06.2007)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

60/803.946 5 June 2006 (05.06.2006) US

(71) Applicant (for all designated States except US): IDEAL INDUSTRIES, INC. [US/US]; Backer Place, Sycamore, IL 60178 (US).

(72) Inventor (for US only): YANG, Huaibin; 12531 Heatherton Court, Apartment 151, San Diego, CA 92128 (US).

(74) Agent: PRISTELSKI, James, S.; Cook, Alex, Mcfarron, Manzo, Cummings & Mehler, ltd, 200 West Adams Street, Suite 2850, Chicago, IL 60606 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: VOLTAGE DISTURBANCE AND HARMONICS MONITOR

(57) Abstract: An electronic monitor for monitoring characteristics of an AC power line for swells, sags, RMS voltage, impulses, total harmonic distortion (THD) and frequency. The waveform is received at the monitor, scaled to a lower magnitude, rectified by an op amp with zero offset voltage, converted a digital form which is representative of the waveform and processed to determine the occurrence of any irregularity in the AC power waveform. Two DMA channels are used to store each cycle, or groups of cycles, of the waveform into two buffers for further processing. An input surge protective circuit limits impulse voltage to the power supply. Related methods are also disclosed.

#### VOLTAGE DISTURBANCE AND HARMONICS MONITOR

CROSS-REFERENCE TO RELATED PATENT APPLICATION

[0001] This PCT international patent application claims a right of priority to a prior United States of America provisional patent application Serial No. 60/803,946, filed on June 5, 2006.

#### FIELD OF THE INVENTION

[0002] The present invention relates generally to a voltage and harmonics monitor. More particularly, the present invention relates to surge protection, signal conditioning and storage of AC waveform data in a voltage and harmonics monitor.

#### BACKGROUND OF THE INVENTION

[0003] Voltage disturbances and harmonics premature equipment failures, automation failures, erratic computer operation, lost data and data errors, burned out electronic module failure, premature motors, lighting failure and the like. There is more equipment in homes, offices and industrial facilities that is sensitive to voltage disturbances and harmonics. For example, some types of equipment that are affected by poor power quality include electronic lighting ballasts, computers, copiers, laser printers, adjustable speed drives, industrial programmable logic controllers (PLCs), medical equipment and many microprocessor-controlled devices. Some equipment also contributes to poor power quality. Poor power quality may also reduce the useful life of many types of equipment. [0004] Thus, stable power is needed for the complex electrical installations typically encountered in today's buildings. Of course, voltage surges can be caused by lightning. However, the cause of poor power quality frequently resides in the building rather than in the electrical power distribution system outside of building. Thus, monitoring of the power quality inside of the building, such as on selected electrical circuits, may assist in diagnosing where any problems occur. studies indicate that about one-half of the cost associated

with electrical failures could be prevented by regular maintenance.

[0005] A voltage disturbance and harmonics monitor can verify and diagnose voltage sags, swells, impulses and total harmonic distortion (THD) to assist in the monitoring of power quality. Sags and swells are temporary increases or decreases in voltage that can affect the performance of equipment. Sources of such voltage events include motors, photocopiers, arcing switches, water coolers, air conditioners and some routine utility operations.

Harmonic distortion is an increasing problem due to the increase of electronic loads. A harmonic is an integer multiple of the fundamental 60Hz waveform. Electronic loads typically convert AC voltage to DC voltage for supplying power to lower voltage electronic circuitry. process distorts the AC voltage waveform contributes to the "flat-topping" of the AC supply voltage, which starves other power supplies of the optimal peak voltage needed to power their loads. The more devices that are present, the greater the likelihood of this type of voltage distortion and the greater the likelihood of adverse effects on other equipment. Harmonics can also be caused by loads switching on and off, electronic ballasts in fluorescent lighting, variable speed motor drives, soft start motors, welding equipment and the like. Harmonics also affect traditional loads and wiring as well, in the form of added heat, nuisance tripping of peak detecting circuit breakers and noise on communication equipment. THD above about five percent should general, a investigated and mitigated where feasible.

[0007] There has therefore a need for an improved voltage disturbance and harmonic monitor for monitoring the quality of the electrical power.

[0008] A general object of the present invention is to therefore provide an improved voltage disturbance and harmonic monitor for monitoring the quality of the electrical power.

[0009] Another object of the present invention is to provide an improved voltage disturbance and harmonic monitor which is capable of monitoring power quality for all power systems throughout the world.

[0010] A further object of the present invention is to provide a voltage disturbance and harmonic monitor which includes improved surge protection for high voltage surges in the power system.

[0011] Yet another object of the present invention is to provide a voltage disturbance and harmonic monitor with low-distortion signal conditioning.

[0012] A still further object of the present invention is to provide a voltage disturbance and harmonic monitor with improved storage of sample data collected during the monitoring of power quality.

[0013] Another object of the present invention is to provide a voltage disturbance and harmonic monitor with double buffering of sample data acquired during the monitoring of power quality.

[0014] Yet another object of the present invention is to provide a voltage disturbance and harmonic monitor which utilizes direct memory access (DMA) techniques to alternately store sample data acquired during the monitoring of power quality in dual buffers.

#### SUMMARY OF THE INVENTION

The present invention is directed to a method of [0015] processing information about the waveform in an electronic monitor for monitoring an AC power waveform to detect any impulses on the waveform. The method includes the steps of receiving the waveform at the monitor, scaling the waveform including any impulses to a lower magnitude, rectifying any positive impulses on the waveform with a first operational amplifier having a diode in a feedback loop of the first operational amplifier, and rectifying any negative impulses on the waveform with a second operational amplifier having a diode in a feedback loop of the second operational amplifier. The first and second operational amplifiers rectify the positive and negative impulses approximately zero offset voltage.

[0016] Additional steps of the method include converting the rectified positive and negative impulses to a digital form which is representative of the positive and negative impulses, processing the digital representations of the positive and negative impulses to determine the occurrence of an impulse on the AC power waveform, and displaying the occurrence of an impulse on the AC power waveform on a display of the monitor. The step of scaling the waveform including any impulses may be accomplished with a resistor divider.

[0017] The present invention is further directed to an electronic monitor for monitoring an AC power waveform to detect any impulses on the waveform. The monitor preferably includes an input line for receiving waveform at the monitor, means for scaling the waveform including any impulses to a lower magnitude, a first operational amplifier having a diode in a feedback loop of

the first operational amplifier to rectify any positive impulses on the waveform, and a second operational amplifier having a diode in a feedback loop of the second operational amplifier to rectify any negative impulses on the waveform. The first and second operational amplifiers rectify the positive and negative impulses with approximately zero offset voltage.

[0018] The electronic monitor preferably includes an analog to digital converter to convert the rectified positive and negative impulses to a digital form is representative of the positive and negative impulses, digital processor to process a the digital representations of the positive and negative impulses to determine the occurrence of an impulse on the AC power waveform, and a display for displaying the occurrence of an impulse on the AC power waveform on a display of the monitor. The means for scaling the waveform including any impulses may be a resistor divider.

[0019] The present invention is also directed to methods of monitoring an AC power waveform, including the steps of receiving the waveform at the monitor, converting the waveform into digital data representative of the waveform; determining the zero crossing of successive cycles of the AC waveform, grouping a predetermined number of cycles of the AC waveform into a first group and a second group, using a first direct memory access channel of a digital processor to store the digital representation of a first group of cycles in a first buffer, and using a second direct memory access channel of the digital processor to store the digital representation of a second group of cycles in a second buffer.

[0020] The methods may further include processing the first group of cycles with the digital processor while the second group of cycles is being stored in the second buffer to determine the frequency of the AC waveform, the root mean square of the voltage of the AC waveform and/or the total harmonic distortion of the AC waveform. The first and second groups of cycles may each constitute four cycles.

The present invention is further directed to [0021] electronic monitor for monitoring an AC power waveform, including an input line for receiving the waveform at the monitor, an analog to digital converter for converting the waveform into digital data representative of the waveform, a zero crossing detector for determining the zero crossing of successive cycles of the AC waveform, a digital processor for grouping a predetermined number of cycles of the AC waveform into a first group and a second group, a first direct memory access channel of the digital processor for storing the digital representation of a first group of cycles in a first buffer, and a second direct memory access channel of the digital processor for storing the digital representation of a second group of cycles in a second buffer.

[0022] Preferably, the digital processor processes the first group of cycles with the digital processor while the second group of cycles is being stored in the second buffer. The processing of the first group of cycles may determine the frequency of the AC waveform, the root mean square of the voltage of the AC waveform, and/or the total harmonic distortion of the AC waveform. The first and second groups each constitute four cycles.

Further methods in accordance with the present [0023] invention for monitoring an AC power waveform include the steps of receiving the waveform at the monitor, converting the waveform into digital data representative of waveform, determining the zero crossing of successive cycles of the AC waveform, grouping a predetermined number of cycles of the AC waveform into a first group and a second group, using a first direct memory access channel of a digital processor to store the digital representation of a first cycle of the first group of cycles in a first memory location in a first buffer, and using a second direct memory access channel of the digital processor to store the digital representation of a second cycle of the first group of cycles in a second memory location of the first buffer.

Additional method steps include continuing to alternate use the first and second direct memory access channels to store successive cycles of the first group of cycles in successive memory locations of the first buffer until all cycles of the first group of cycles are stored in the first buffer, using a first direct memory access channel of a digital processor to store the digital representation of a first cycle of the second group of cycles in a first memory location in a second buffer, using a second direct memory access channel of the digital processor to store the digital representation of a second cycle of the second group of cycles in a second memory location of the second buffer, continuing to alternate use the first and second direct memory access channels to store successive cycles of the second group of cycles successive memory locations of the second buffer until all cycles of the second group of cycles are stored in the

second buffer. The first and second groups may each constitute four cycles.

The present invention further contemplates a [0025] surge current limiting input circuit for a power supply includes at least one surge current limiting resistor in series between a source of AC power and an impulse protective device, the impulse protective device coupled to ground to attenuate some impulse energy from the source of surge current limiting resistor power, a second connected in series with a rectifying diode between the impulse protective device and an input to the power supply, and a capacitor coupled from the input of the power supply to ground. The at least one surge current limiting resistor may include a plurality of surge current limiting resistors. The capacitor may be selected with a lower voltage rating. The at least one surge current limiting resistor and the second surge current limiting resistor limit the surge currents associated with any impulses from the source of AC power.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0026] The invention, together with its objects and the advantages thereof, may best be understood by reference to the following description taken in conjunction with the accompanying drawings, in which like reference numerals identify like elements in the figures, and in which:

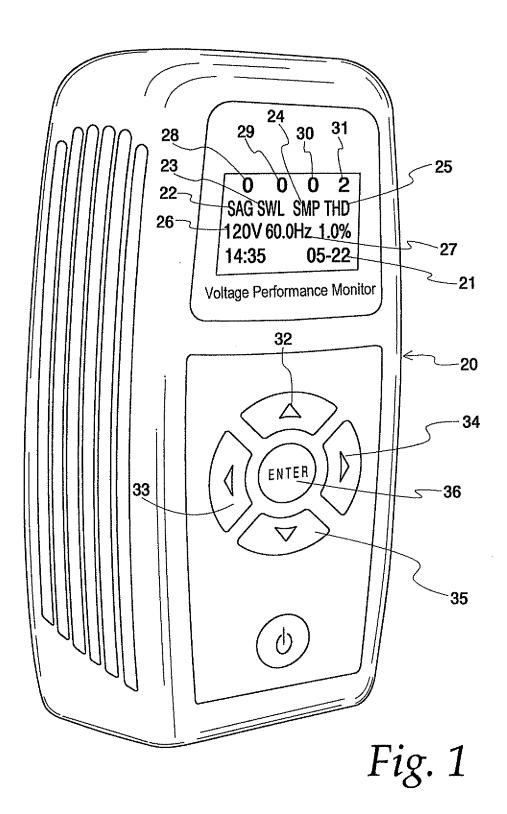

[0027] FIG. 1 is a perspective view of a voltage disturbance and harmonic monitor which incorporates the improvements of the present invention;

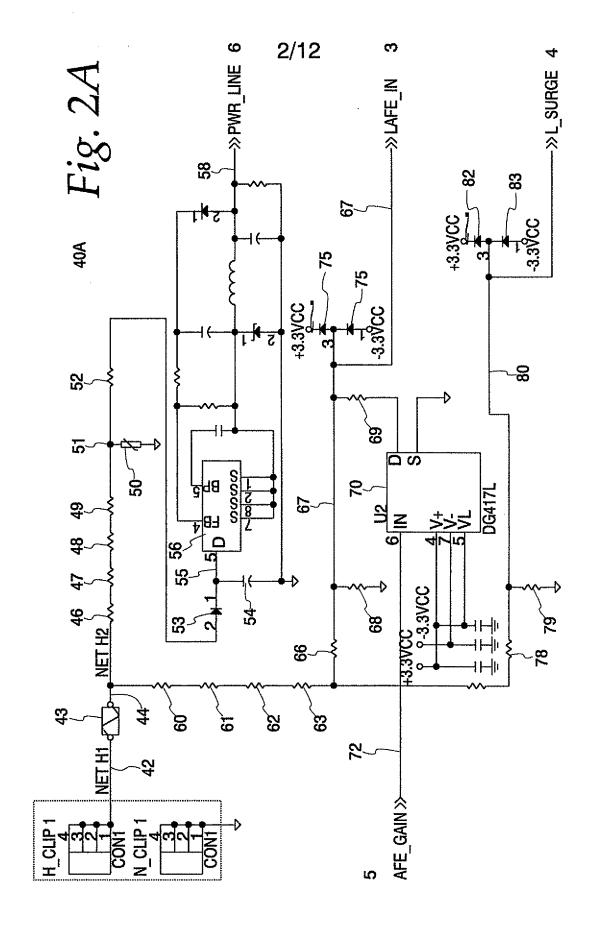

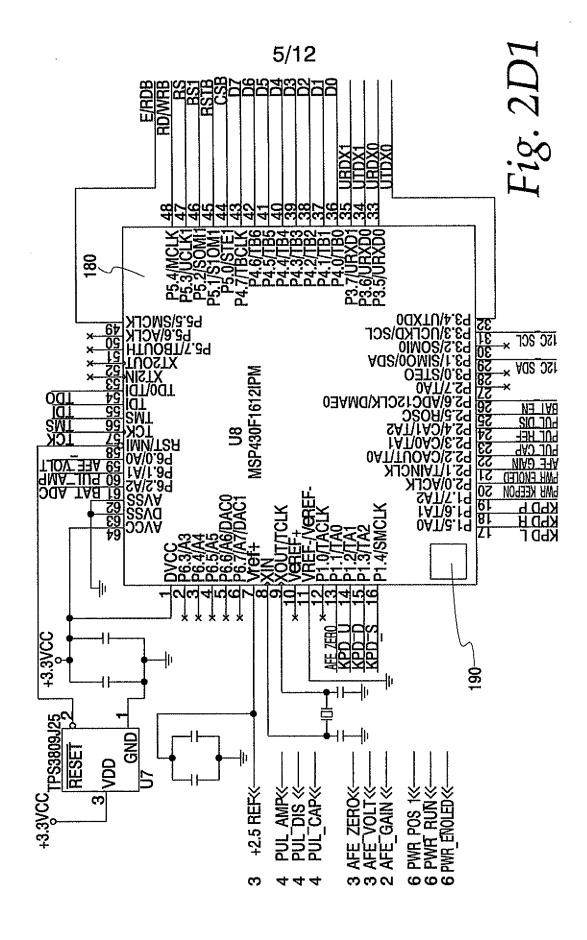

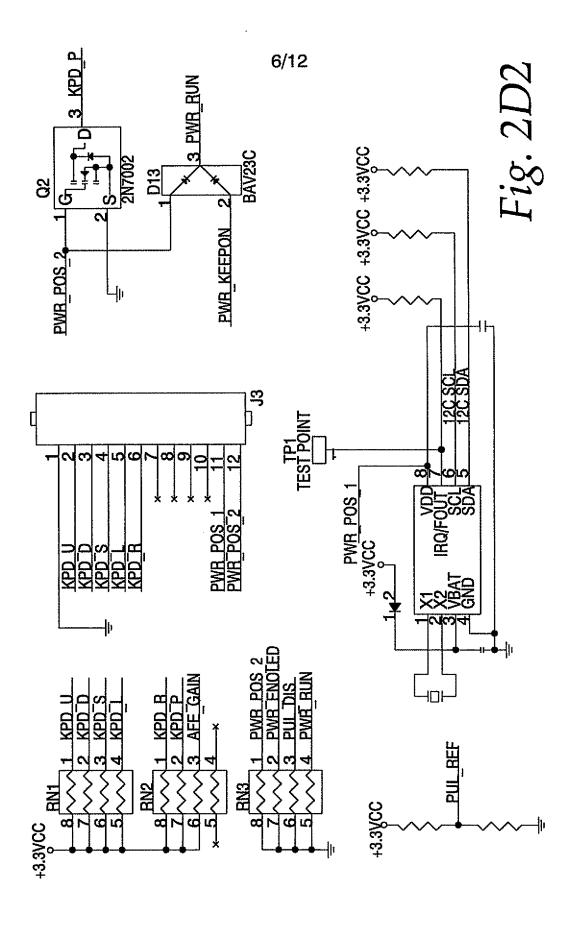

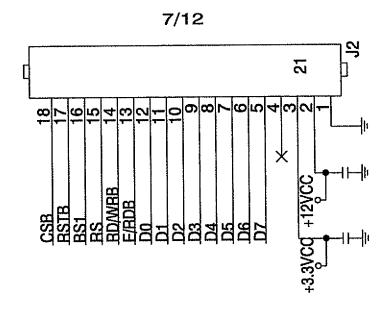

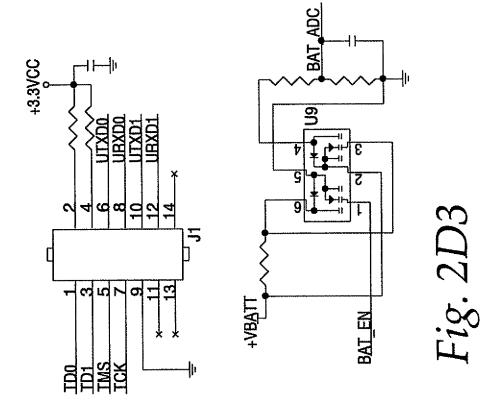

[0028] FIGS. 2A-2C and 2D1-2D3 collectively constitute a schematic diagram of electronic circuitry utilized in the

voltage disturbance and harmonic monitor of FIG. 1 in accordance with the present invention;

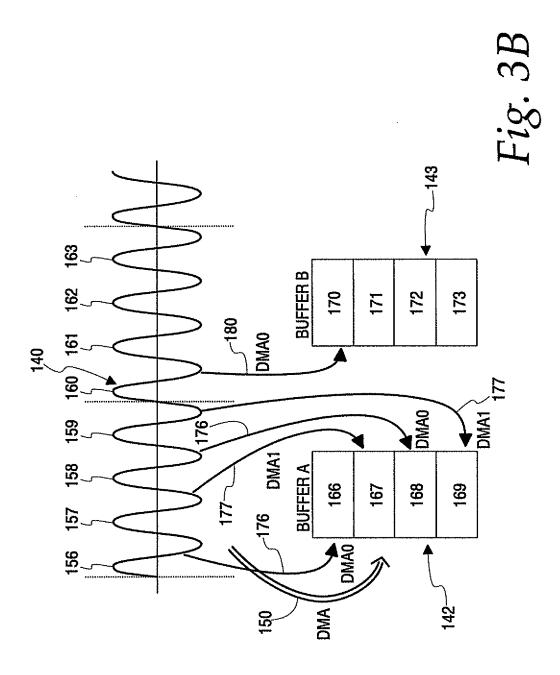

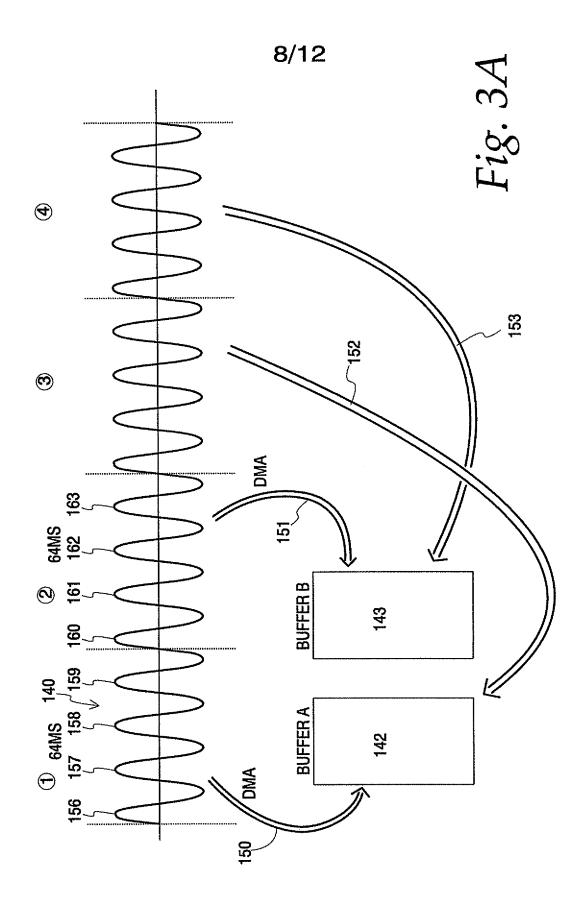

[0029] FIGS. 3A-3B are diagrams illustrating the use of dual buffers for storing sample AC waveform data acquired by the voltage disturbance and harmonic monitor of FIG. 1

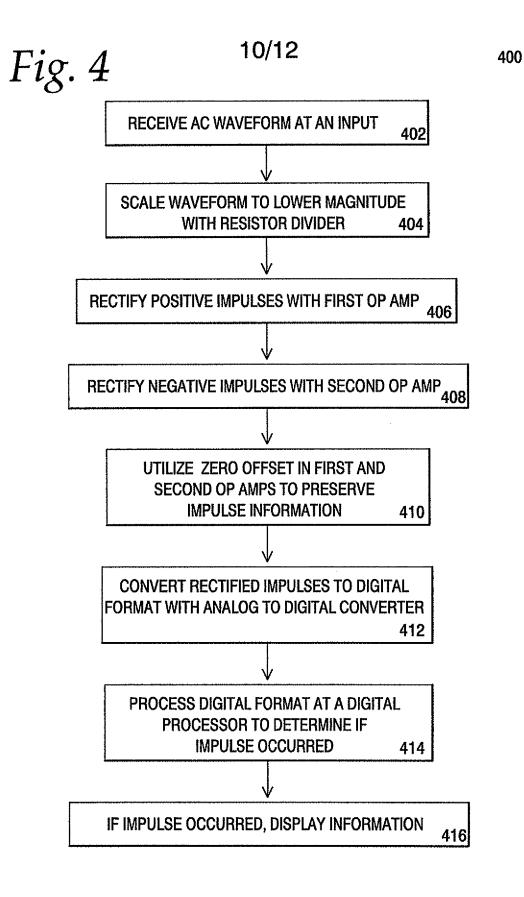

[0030] FIG. 4 is a flow chart illustrating representative steps of methods utilized by the present invention for determining if an impulse occurred on the AC waveform; and

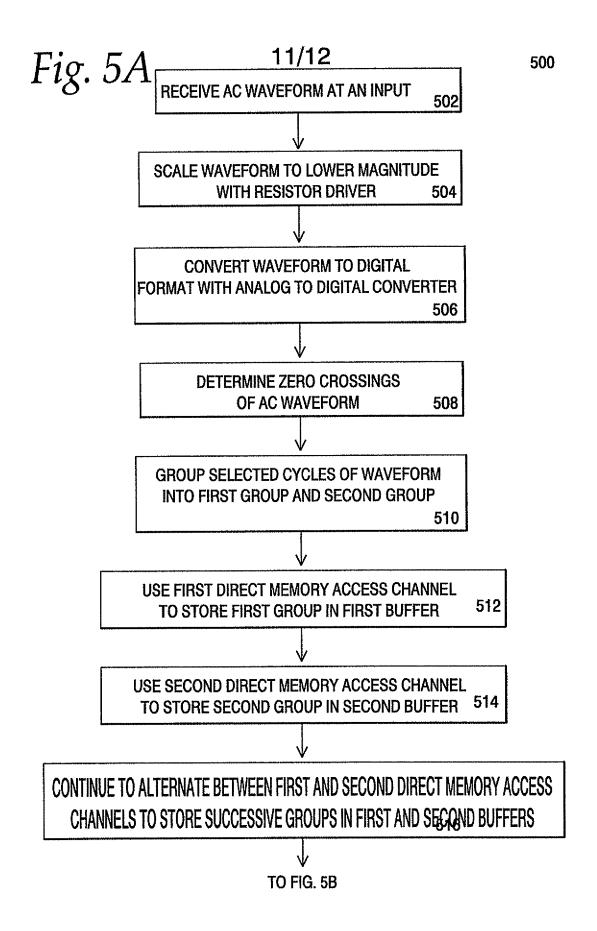

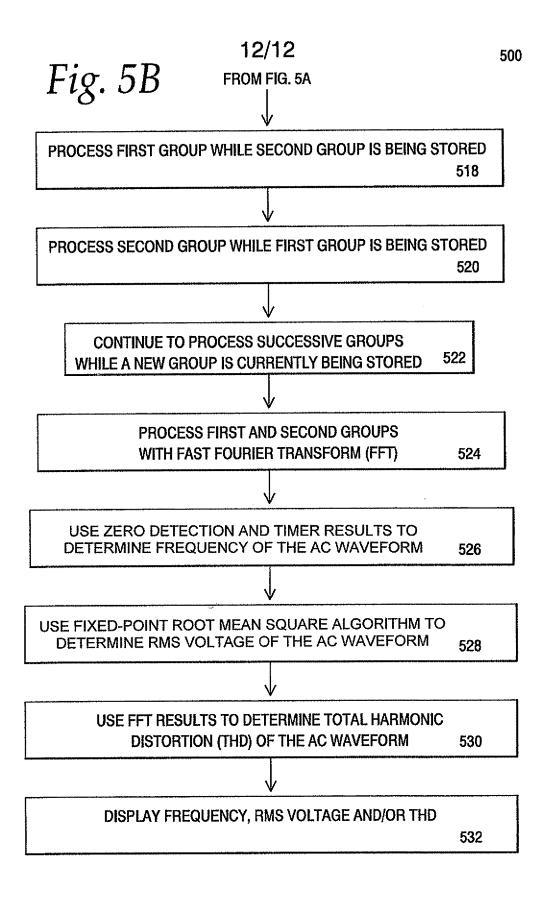

[0031] FIGS. 5A-5B together constitute a flow chart illustrating representative steps of methods utilized by the present invention for determining the frequency, RMS voltage and total harmonic distortion of the AC waveform.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0032] It will be understood that the present invention may be embodied in other specific forms without departing from the spirit thereof. The present examples and embodiments, therefore, are to be considered in all respects as illustrative and not restrictive, and the invention is not to be limited to the details presented herein.

A voltage disturbance and harmonic monitor, [0033] is designed and generally designated 20, and which constructed in accordance with the present invention, is shown in FIG. 1. The monitor 20 has a display 21 for displaying conditions or events relating to its monitoring of an electrical circuit. For example, in FIG. 1, display 21 may display conditions or events relating to sag 22, 24, total (SWL) 23, impulses (IMP) harmonic swell distortion (THD) 25, line voltage 26 and/or line frequency In addition, display 21 may indicate the number of 27.

times that certain characteristics, such as sag 23, swell 24 and THD 26 are out of specification, or if an impulse 25 event has occurred. The occurrence of any of these events is indicated at fields 28, 29, 31 and 30, respectively, in the display 21. In the example shown in FIG. 1, THD 25 has been out of specification two times during the last monitoring interval as shown at field 31. On the other hand, sag 23 and swell 24 have not been out of specification, and no impulses 25 have occurred as indicated by the zeros in fields 28, 29 and 30.

[0034] Navigation keys 32, 33, 34 and 35 permit a user to access and scroll through the various screens besides the screen displayed in FIG. 1. For example, a user may scroll one of the characteristics displayed in FIG. 1 and press the enter button 36 for more information on the selected characteristic.

[0035] FIGS. 2A-2C and 2D1-2D3 collectively constitute a schematic diagram 40 for monitor 20. That portion of schematic diagram 40 shown in FIG. 2A is designated 40A, that portion of schematic diagram 40 shown in FIG. 2B is designated 40B, that portion of schematic diagram 40 shown in FIG. 2C is designated 40D, and that portion of schematic diagram 40 shown in FIGS. 2D1-2D3 is designated 40D. reference to FIG. 2A, an input AC voltage line 42 that is being monitored by monitor 20 is protected by a fuse 43. An input line 44 on the other side of fuse 43 provides current to a power supply, including a linear voltage regulator 56 for supplying DC operating power to various electronic components in the schematic diagram 40 from power output line 58, which may be about 3.3 VDC. Before the input 55 of voltage regulator 56 are a plurality of surge current limiting resistors 46-49 connected in

series between the input AC line 44 and node 51. Connected at node 51 to ground is a varistor 50 to clip input transient voltages. For example, varistor 50 may be selected to clip AC voltages that exceed 275 VAC. surge current limiting resistor 52 is in series with a diode 53 between node 50 and input terminal 55 of the Resistors voltage regulator 56. 46-49 and 51 are preferably surge current limiting resistors which assist in absorbing the energy of any voltage transients or impulses on input AC line 44. Diode 53 half-wave rectifies the input AC voltage to provide an unregulated DC voltage at input terminal 55. A capacitor 54 is connected at input terminal 55 to ground and it stores energy for those portions of the AC cycle when diode 53 is reverse biased and non-conducting.

While varistor 50 clips most of the energy of voltage transients or impulses, some of the peak magnitudes of fast rising impulses is not clipped due to the response time and other characteristics of varistors. For example, if a lightning strike occurs near a line that monitor 40 is monitoring, a spike on the order of 700 volts may appear on input line. Such a spike will not be entirely attenuated by varistor 50, such as impulses that have fast rise times, and some of the spike energy will therefore be present at node 51. Energy absorbing resistor 52 thus assists in reducing the transient voltage fed through diode 53 to capacitor 54 and to the input terminal 55 of the voltage regulator 56. At the same time, energy absorbing resistors 46-49 also assist in reducing the transient voltage at input terminal 55. Since resistors 46-49 and 52 reduce the impulse or transient voltage that appears at terminal 55 and across capacitor 54, the maximum operating

voltage of capacitor 54 may be lower. For example, electrolytic capacitors suitable for power supply use with a maximum voltage rating above 500 volts are fairly expensive. With energy absorbing resistors 46-49 and 52, the voltage rating of capacitor 54 may be selected below 500 volts, such as about 400 volts. Resistors 46-49 and 52 may each be about 100 ohms.

[0037] A portion 40A of the circuitry 40 illustrated in FIG. 2A is used to provide a reduced AC voltage suitable for monitoring by lower voltage electronics, such as for sag, swell and harmonic content. To this end, a resistor divider formed by the series connected resistors 60-63 and 66 and resistor 68 provide a reduced AC voltage signal on line 67 that is representative of the AC voltage on input AC line 44. For example, if resistors 60-63 and 66 are each selected to be about 68K ohms and resistor 68 is selected to be about 4.3K ohms, line 67 will have a voltage of about 1.5 VAC when input AC line 44 is 120 VAC.

[0038] However, it is desirable that monitor 20 be capable of monitoring line voltages throughout the world, which entails a voltage range of about 85 VAC to about 220 VAC. To accommodate the higher end of this range, an analog switch 70, which is normally open, can be closed by a signal on line 72 to place resistor 69 in parallel with resistor 68. For example, if resistors 68 and 69 are both about 4.3K ohms, the signal on line 67 can be reduced by about one-half when switch 70 closes and places resistor 69 in conduction. Thus, if the AC input line is about 220 VAC, the signal on line 67 will be about 1.4 VAC. Analog switch 70 is commercially available as part number DG417 from Dallas Semiconductor. Input line 72 of switch 70 may be controlled by a microprocessor 180 shown in FIG. 2D1,

and which is further described below. A pair of diodes 74 and 75 is poled and biased to +3.3 VDC and to -3.3 VDC to limit the signal on line 67 to about  $\pm$  4 VDC to protect the electronics which monitors line 67.

[0039] Input AC line 44 is also routed through resistors 60-63 and 78 to a line 80 which is monitored by monitor 20 for any impulses or other transients. Resistors 60-63 and 78, in combination with resistor 79, form another voltage divider which represents a divided portion of any impulse that appears on the input AC line 44. For example, if resistors 60-63 and resistor 78 are about 68K ohms and resistor 79 is about 270 ohms, it can be shown that a several hundred volt impulse appearing on AC line 44 will be translated into an impulse of slightly less than a volt on line 80. Diodes 82 and 83 limit the voltage which may appear on line 80 in a similar manner as the previously described diodes 74 and 75 on line 67.

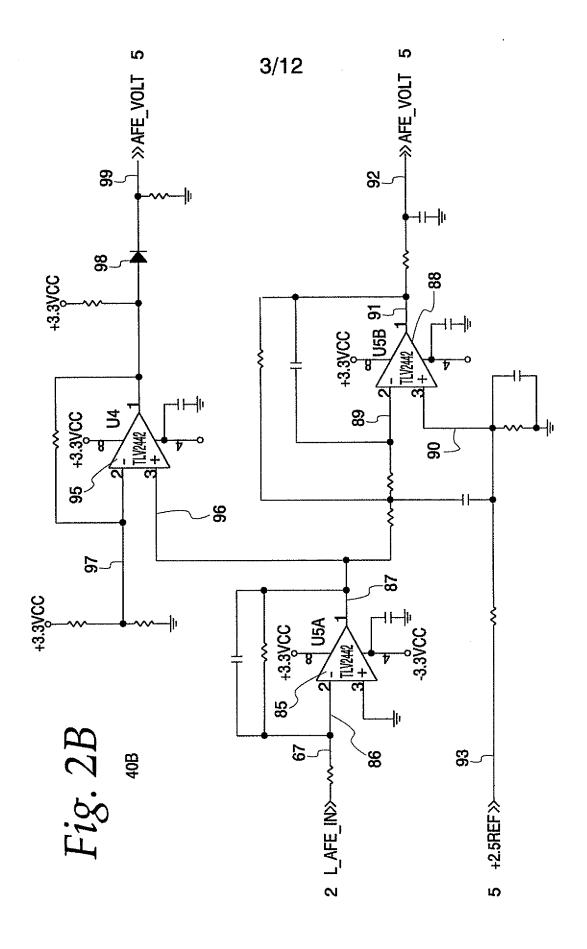

[0040] The circuitry 40B shown in FIG. 2B provides signal conditioning for the voltage signals on line 67 of FIG. 2A. A first operational amplifier 85 receives the representation of the input AC voltage on line 67 at its inverting input 86. Preferably, op amp 85 has its feedback loop set for about unity gain. The output of op amp 85 is fed to the inverting input 89 of another op amp 88, which is also preferably set for about unity gain. The non-inverting input 90 of op amp 88 is connected to a voltage reference, such as about +2.5 VDC, to level shift the output 92 of op amp 88 by the amount of the voltage reference. This assures that the negative portions of the AC voltage signal on line 67 will be shifted to a positive voltage level to be compatible with the voltage level

constraints of an input terminal of a microprocessor, such as microprocessor 180 in FIG. 2D1.

Another op amp or comparator 95 operates as a zero crossing detector to determine when the AC waveform crosses from positive to negative. Comparator 95 has its non-inverting input referenced to a very low positive bias such as about +15 mV. The inverting input 96 is connected to the output 87 of op amp 85. Thus, while representation of the AC waveform is positive, the output 94 of comparator 95 is negative, diode 98 is reverse biased and non-conducting and zero crossing output line 99 is at a logic 0. However, as the AC waveform crosses zero volts and turns negative, the output 94 of comparator 95 goes positive, diode 98 becomes forward biased and conducting, and zero crossing output line 99 rises to a logic 1. microprocessor 180 will know that a zero crossing of the AC waveform has occurred when zero crossing output line 99 becomes a logic 1.

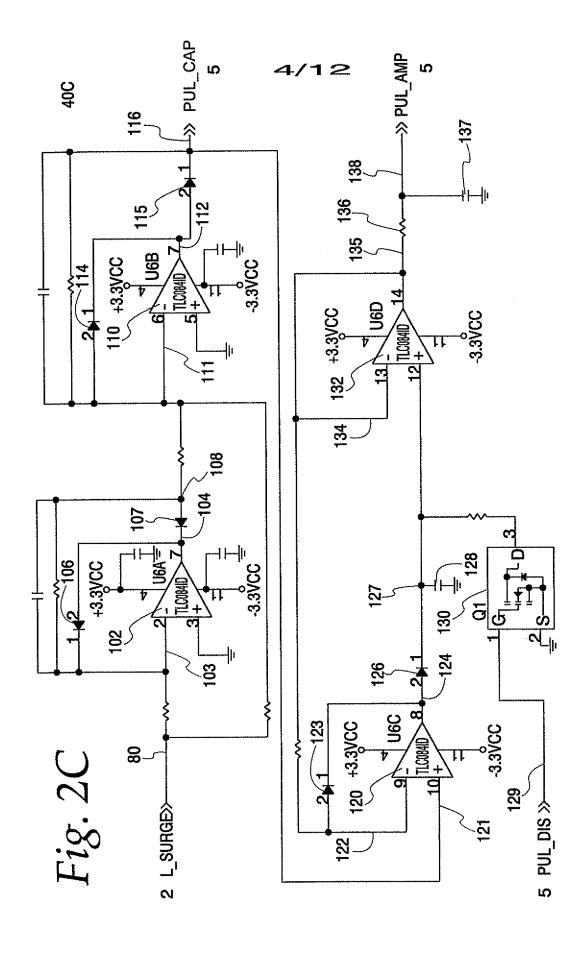

[0042] The circuitry 40C shown in FIG. 2C provides signal conditioning for the impulse and transient signals on line 80 of FIG. 2A. It will be appreciated that line 80 may have both positive and negative impulses. It is desirable to preserve and monitor both polarities of impulses. Line 80 from FIG. 2A is coupled to the inverting input 103 of a first op amp 102. Op amp 102 has a diode 106 in its feedback loop between output 104 and inverting input 103. Another diode 107 is disposed in the output line 104. The feedback loop of op amp 102 is set for about unity gain. It will be appreciated that, with diodes 106 and 107 poled as shown in FIG. 2C, that op amp 102 will rectify positive impulses on line 80, and negative impulses

on line 80 will be blocked. Thus, a positive impulse on line 80 will appear as a negative impulse at node 108.

Line 80 from FIG. 2A is also coupled to the [0043] inverting input 111 of a second op amp 110. Op amp 110 also has a diode 114 in its feedback loop between output 112 and inverting input 111. Another diode 115 is disposed in the output line 116. The feedback loop of op amp 110 is set for about unity gain. It will be appreciated that, with diodes 114 and 115 poled as shown in FIG. 2C, that op amp 110 will rectify negative impulses on line 80, and positive impulses on line 80 will be blocked. Op amp 110 will also rectify any negative impulses from op amp 102 at node 108, which is also coupled to the inverting input 111 of op amp 110. Thus, negative impulses from line 80, and negative impulses from op amp 102, will appear as positive impulses on output line 116.

It will be further appreciated that op amps 102 and 110 rectify the impulses appearing on line 80 with virtually no offset. For example, if the operational amplifier circuits, including op amps 102 and 110 were replaced by diodes, much of the impulse information on line 80 would be lost due to the typical forward bias voltage of silicon diodes of about 0.7 volts. That is, diodes would clip or lose the impulse information which is between + 0.7 Since resistors 60-65 and 78-79 divide any impulse appearing on input AC line 44 on line 80 to a small portion of the actual impulse, information concerning smaller impulses could be completely lost by using rectifying diodes only. In this sense, the operational amplifier circuits in FIG. 40C may be thought of as "super diodes" since they act as diodes without any forward bias offset.

Op amps 120 and 132 in FIG. 2C form a peak [0045] detector which will capture the peak magnitude of impulses The output of op amp 110 on line 116 on line 80. received at the non-inverting input of op amp 120. signal PUL CAP on line 116 is used by microprocessor 180 to determine the duration of any detected impulses. A diode 123 is connected in the feedback loop of op amp 120 from its output 124 to its inverting input 122. Thus, op amp 120 will effectively rectify any positive pulses appearing on line 116. Another diode 126 disposed between output 124 of op amp 120 and a capacitor 128 will then peak charge capacitor 128 with the peak magnitude of any pulses processed by op amp 120.

[0046] Another op amp 132 is configured as a voltage follower with its inverting input 134 connected to its output 135. Op amp 132 therefore provides the voltage across capacitor 128 at its output 135. Resistor 136 and capacitor 137 provide high frequency filtering of the output 135 on peak detector output line 138. Microprocessor 180 can reset the peak magnitude or disable the peak detector by controlling line 129 to an electronic switch 130. Electronic switch 130 can then discharge capacitor 128 to ground.

[0047] FIGS. 2D1-2D3 illustrate a portion 40D of the circuitry 40, including a microprocessor 180 and its associated circuitry. Preferably, microprocessor 180 has an analog to digital converter 190 for receiving analog input impulse signals from op amp 110 in FIG. 2C and for receiving the analog waveform signals from op amp 88 in FIG. 2B. Such a microprocessor is commercially available from Texas Instruments as part number MSP430F1612. This microprocessor also has direct memory access (DMA) channels

150 and 151, which will be utilized and further described below with reference to FIGS. 3A-3B. While the present invention contemplates the use of a microprocessor, any other suitable digital processor may also be utilized.

FIG. 3A illustrates methods in accordance with [0048] the present invention for storing data representative of groups of cycles of the monitored AC waveform 140 into dual buffers 142 and 143 by utilizing the DMA capabilities of microprocessor 180 of FIG. 2D1. A zero crossing detector determines the start and end of each cycle of the AC In the example of FIG. 3A, each cycle of a 60 Hz waveform. waveform represents about 16 milliseconds (ms) in time. Thus, each successive group of four cycles is about 64 ms. When the first group of four cycles 144 of waveform information is received, the first group 144 may be stored via a first DMA cycle 150 in a first buffer 142. second group of four cycles 145 of waveform information is received, the second group 145 may be stored via a second DMA cycle 151 in a second buffer 143. Likewise, when the third group of four cycles 146 of waveform information is received, the third group 146 may be stored via a third DMA cycle 152 in the first buffer 142. Lastly, when the fourth group of four cycles 147 of waveform information received, the fourth group 147 may be stored via a fourth DMA cycle 153 in the second buffer 143. Thus, the groups four cycles 144-147 of waveform information alternately stored in first buffer 142 and in second buffer Since it takes about 64 ms to accumulate the waveform information concerning each group of four cycles, microprocessor 180 can be processing the prior group of four cycles while the next group of four cycles is being accumulated for storage in one of buffers 142 or 143. For

example, microprocessor 180 may conduct fast Fourier transforms (FFTs) on matched cycles of waveform information to determine certain characteristics of the waveform, such as the total harmonic distortion present in waveform 140. Zero detection and timer results may be used to determine the frequency of waveform 140. Similarly, a fixed-point square root algorithm may be used to determine the RMS voltage of the AC waveform 140.

[0049] FIG. 3B illustrates a further refinement of the methods shown in FIG. 3A. In FIG. 3B, each successive cycle of waveform 140 is stored in a separate location in the first buffer 142 or in the second buffer 143. DMA cycle 150 consists of separate DMA cycles in which the microprocessor's DMA channels DMA0 176 and DMA1 alternate in placing each waveform cycle, such as cycles 166-169, in a separate location in the first buffer 142. Thus, each successive cycle of waveform information from waveform 140 is alternately stored in buffer 142 until four cycles 166-169 have been stored in buffer 142. The process then alternates to place the next four successive cycles, such as cycles 170-173, of waveform information in the second buffer 143. Since it takes about 16 ms accumulate the waveform information for each cycle, microprocessor 180 can be processing the prior cycle while the next cycle is being accumulated for storage in one of buffers 142 or 143. As with the example in FIG. 3A, microprocessor 180 may conduct fast Fourier transforms (FFTs) on matched cycles of waveform information in FIG. 3B to determine the characteristics of the waveform, such as the total harmonic distortion of waveform As previously mentioned, zero detection and timer results may be used to determine the frequency of waveform 140 and a

fixed-point square root algorithm may be used to determine the RMS voltage of the AC waveform 140.

[0050] FIG. 4 is a flow chart illustrating representative steps of methods utilized by the present invention for determining if an impulse occurred on the AC In view of the above description of circuitry 40 shown in FIGS. 2A-2D3 and the use of the direct memory access to process successive cycles of the AC waveform 140, it will be appreciated that the present invention is also directed to methods of processing information about the waveform in an electronic monitor for monitoring an AC power waveform. For example, an exemplary method of detecting any impulses on the waveform 140 is shown in flow chart 400 in FIG. 4. The method begins with receiving the waveform 140 at the monitor 20 in block 404, and scaling the waveform, including any impulses, to a lower magnitude such as with a resistor divider at block Any positive impulses on the waveform may then be rectified at block 406, such as with a first operational amplifier having a diode in its feedback loop at block 406. Similarly, any negative impulses on the waveform may be rectified, such as with a second operational amplifier having a diode in its feedback loop at block Preferably, the first and second operational amplifiers rectify the positive and negative impulses approximately zero offset voltage, as shown in block 410.

[0051] Additional steps of the method include converting the rectified positive and negative impulses to a digital form which is representative of the positive and negative impulses, such as with an analog to digital converter in block 412. The digital representations of the positive and negative impulses may then be processed to determine the

occurrence of an impulse on the AC power waveform at block 414. If an impulse has occurred, the occurrence of an impulse on the AC power waveform may be displayed on a display of the monitor, at block 416.

FIGS. 5A-5B together constitute a flow chart 500, which illustrates representative steps of methods utilized by the present invention for determining the frequency, RMS voltage and total harmonic distortion of the AC waveform. Exemplary steps of the methods may include receiving the waveform at the monitor in block 502, scaling the waveform to a lower magnitude such as with a resistor divider at block 504, converting the waveform into digital data representative of the waveform such as with an analog to digital converter at block 506, determining the crossing of successive cycles of the AC waveform at block 508, grouping a predetermined number of cycles of the AC waveform into a first group and into a second group at block 510, using a first direct memory access channel of a digital processor to store the digital representation of a first group of cycles in a first buffer at block 512, and using a second direct memory access channel of the digital processor to store the digital representation of a second group of cycles in a second buffer at block 514.

[0053] Further steps of the methods may include continuing to alternate use the first and second direct memory access channels to store successive cycles of the first group of cycles in successive memory locations of the first buffer until all cycles of the first group of cycles are stored in the first buffer as shown in block 516, processing the first group of cycles with the digital processor while the second group of cycles is being stored in the second buffer to determine the frequency of the AC

waveform, the root mean square of the voltage of the AC waveform and/or the total harmonic distortion of the AC waveform as shown in block 518, processing the second group of cycles with the digital processor while the first group of cycles is being stored in the first buffer to determine the frequency of the AC waveform, the root mean square of the voltage of the AC waveform and/or the total harmonic distortion of the AC waveform as shown in block 520, and continuing to alternate use the first and second direct memory access channels to store successive cycles of the second group of cycles in successive memory locations of the second buffer until all cycles of the second group of cycles are stored in the second buffer as shown in block 522.

Still further steps of the methods may include processing the first and second groups of cycles with a fast Fourier transform (FFT) as shown at block 524, using zero detection and timer results to determine the frequency of waveform 140 as shown at block 526, using a fixed-point square root algorithm to determine the RMS voltage of the AC waveform 140 as shown at block 528, using the results of FFT processing to determine the total harmonic distortion (THD) of the AC waveform as shown at block 530, and displaying the frequency, RMS voltage and/or the total harmonic distortion on display 21 οf the voltage disturbance and harmonic monitor 20 as shown in block 532.

[0055] While particular embodiments of the invention have been shown and described, it will be obvious to those skilled in the art that changes and modifications may be made therein without departing from the invention in its broader aspects.

### CLAIMS

1. In an electronic monitor for monitoring an AC power waveform, a method of processing information about the waveform to detect any impulses on the waveform, said method comprising the steps of:

receiving said waveform at the monitor;

scaling the waveform including any impulses to a lower magnitude;

rectifying any positive impulses on the waveform with a first operational amplifier having a diode in a feedback loop of the first operational amplifier; and

rectifying any negative impulses on the waveform with a second operational amplifier having a diode in a feedback loop of the second operational amplifier.

- 2. The method in accordance with Claim 1 wherein the first and second operational amplifiers rectify the positive and negative impulses with approximately zero offset voltage.

- 3. The method in accordance with Claim 1, said method further comprising the step of:

converting the rectified positive and negative impulses to a digital form which is representative of the positive and negative impulses on the waveform.

4. The method in accordance with Claim 3, said method further comprising the step of:

processing the digital representations of the positive and negative impulses to determine the occurrence of an impulse on the AC power waveform.

5. The method in accordance with Claim 4, said method further comprising the step of:

displaying the occurrence of an impulse on the AC power waveform on a display of the monitor.

- 6. The method in accordance with Claim 1, wherein the step of scaling the waveform including any impulses is accomplished with a resistor divider.

- 7. An electronic monitor for monitoring an AC power waveform to detect any impulses on the waveform, said electronic monitor comprising:

an input line for receiving said waveform at the monitor;

means for scaling the waveform including any impulses to a lower magnitude;

- a first operational amplifier having a diode in a feedback loop of the first operational amplifier to rectify any positive impulses on the waveform; and

- a second operational amplifier having a diode in a feedback loop of the second operational amplifier to rectify any negative impulses on the waveform.

- 8. The electronic monitor in accordance with Claim 7 wherein the first and second operational amplifiers rectify

the positive and negative impulses with approximately zero offset voltage.

- 9. The electronic monitor in accordance with Claim 7, said electronic monitor further comprising:

- an analog to digital converter to convert the rectified positive and negative impulses to a digital form which is representative of the positive and negative impulses on the waveform.

- 10. The electronic monitor in accordance with Claim 9, said electronic monitor further comprising:

- a digital processor to process the digital representations of the positive and negative impulses to determine the occurrence of an impulse on the AC power waveform.

- 11. The electronic monitor in accordance with Claim 10, said electronic monitor further comprising:

- a display for displaying the occurrence of an impulse on the AC power waveform on a display of the monitor.

- 12. The electronic monitor in accordance with Claim 7, wherein the means for scaling the waveform including any impulses is a resistor divider.

- 13. In an electronic monitor for monitoring an AC power waveform, said method comprising the steps of:

receiving said waveform at the monitor;

converting the waveform into digital data representative of the waveform;

determining the zero crossing of successive cycles of the AC waveform;

grouping a predetermined number of cycles of the AC waveform into a first group and a second group;

using a first direct memory access channel of a digital processor to store the digital representation of a first group of cycles in a first buffer; and

using a second direct memory access channel of the digital processor to store the digital representation of a second group of cycles in a second buffer.

14. The method in accordance with Claim 13, said method further comprising the step of:

processing the first group of cycles with the digital processor while the second group of cycles is being stored in the second buffer.

- 15. The method in accordance with Claim 14, wherein the processing of the first group of cycles determines the frequency of the AC waveform.

- 16. The method in accordance with Claim 14, wherein the processing of the first group of cycles determines the root mean square of the voltage of the AC waveform.

- 17. The method in accordance with Claim 14, wherein the processing of the first group of cycles determines the total harmonic distortion of the AC waveform.

18. The method in accordance with Claim 14, wherein the first and second groups each constitute four cycles of the AC waveform.

- 19. An electronic monitor for monitoring an AC power waveform, said electronic monitor comprising:

- an input line for receiving said waveform at the monitor;

- an analog to digital converter for converting the waveform into digital data representative of the waveform;

- a zero crossing detector for determining the zero crossing of successive cycles of the AC waveform;

- a digital processor for grouping a predetermined number of cycles of the AC waveform into a first group and a second group;

- a first direct memory access channel of the digital processor for storing the digital representation of a first group of cycles in a first buffer; and

- a second direct memory access channel of the digital processor for storing the digital representation of a second group of cycles in a second buffer.

- 20. The electronic monitor in accordance with Claim 19, wherein said digital processor processes the first group of cycles with the digital processor while the second group of cycles is being stored in the second buffer.

21. The electronic monitor in accordance with Claim 20, wherein the processing of the first group of cycles determines the frequency of the AC waveform.

- 22. The electronic monitor in accordance with Claim 20, wherein the processing of the first group of cycles determines the root mean square of the voltage of the AC waveform.

- 23. The electronic monitor in accordance with Claim 20, wherein the processing of the first group of cycles determines the total harmonic distortion of the AC waveform.

- 24. The electronic monitor in accordance with Claim 19, wherein the first and second groups each constitute four cycles.

- 25. In an electronic monitor for monitoring an AC power waveform, said method comprising the steps of:

receiving said waveform at the monitor;

converting the waveform into digital data representative of the waveform;

determining the zero crossing of successive cycles of the AC waveform;

grouping a predetermined number of cycles of the AC waveform into a first group and a second group;

using a first direct memory access channel of a digital processor to store the digital representation of a

first cycle of the first group of cycles in a first memory location in a first buffer; and

using a second direct memory access channel of the digital processor to store the digital representation of a second cycle of the first group of cycles in a second memory location of the first buffer.

26. The method in accordance with Claim 25, said method further comprising the step of:

continuing to alternate use the first and second direct memory access channels to store successive cycles of the first group of cycles in successive memory locations of the first buffer until all cycles of the first group of cycles are stored in the first buffer.

27. The method in accordance with Claim 26, said method further comprising the steps of:

using a first direct memory access channel of a digital processor to store the digital representation of a first cycle of the second group of cycles in a first memory location in a second buffer; and

using a second direct memory access channel of the digital processor to store the digital representation of a second cycle of the second group of cycles in a second memory location of the second buffer.

28. The method in accordance with Claim 27, said method further comprising the step of:

continuing to alternate use the first and second direct memory access channels to store successive cycles of the second group of cycles in successive memory locations of the second buffer until all cycles of the second group of cycles are stored in the second buffer.

- 29. The method in accordance with Claim 28, wherein the first and second groups each constitute four cycles of the AC waveform.

- 30. A surge current limiting input circuit for a power supply comprising:

at least one surge current limiting resistor in series between a source of AC power and an impulse protective device;

said impulse protective device coupled to ground to attenuate some impulse energy from the source of AC power;

a second surge current limiting resistor connected in series with a rectifying diode between said impulse protective device and an input to the power supply; and

a capacitor coupled from the input of the power supply to ground.

- 31. The surge current limiting input circuit in accordance with Claim 30 wherein said at least one surge current limiting resistor comprises a plurality of surge current limiting resistors.

- 32. The surge current limiting input circuit in accordance with Claim 30 wherein said capacitor may be selected with a lower voltage rating.

33. The surge current limiting input circuit in accordance with Claim 30 wherein said at least one surge current limiting resistor and said second surge current limiting resistor limit the surge currents associated with any impulses from the source of AC power.

1/12

9/12