## MINISTERO DELLO SVILUPPO ECONOMICO DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA NUMERO     | 102007901498252 |  |

|--------------------|-----------------|--|

| Data Deposito      | 27/02/2007      |  |

| Data Pubblicazione | 27/08/2008      |  |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| G       | 11     | С           |        |             |

Titolo

SISTEMA DI INIBIZIONE DI AUTOBOOST LOCALE CON LINEA DI PAROLE SCHERMATA.

# RM 2007 A 00010Z

SIB BI3801R 400.4641T01

Descrizione dell'invenzione industriale dal titolo: "SISTEMA DI INIBIZIONE DI AUTOBOOST LOCALE CON LINEA DI PAROLE SCHERMATA"

a nome di Micron Technology, Inc. (Società dello Stato del Delaware)

di Boise, Idaho (U.S.A)

#### DESCRIZIONE

#### Campo tecnico dell'invenzione

Le presenti forme di realizzazione fanno genericamente riferimento a dispositivi di memoria e, in particolare, a dispositivi di memoria EEPROM e Flash.

### Base tecnica dell'invenzione

I dispositivi di memoria vengono di norma forniti come aree di memorizzazione interna nel computer. Il termine memoria identifica una memorizzazione di dati che arriva nella forma di chip di circuiti integrati. Vi sono svariati tipi differenti di memorie impiegate in elettronica moderna, un tipo comune è la RAM (memoria ad accesso casuale). La RAM si trova

caratteristicamente nell'utilizzazione come memoria principale in un ambiente di computer. La RAM fa riferimento ad una memoria a lettura e scrittura; cioè, si possono scrivere dati in una RAM e leggere dati da una RAM. Questo è in contrasto con la ROM, che consente soltanto di leggere dati. La maggior parte delle RAM è volatile, il che significa che richiede un flusso continuo di elettricità il conservare suo contenuto. Non appena l'alimentazione viene disattivata, tutti nella RAM vengono persi.

I computer contengono quasi sempre una piccola quantità di memoria a sola lettura (ROM) trattiene istruzioni per avviare il computer. A differenza di una RAM, una ROM non può essere scritta. I dispositivi di memoria che non perdono il contenuto di dati delle loro celle di memoria quando l'alimentazione viene rimossa vengono genere indicati come memorie non volatili. EEPROM (memoria sola lettura programmabile cancellabile elettricamente) è un tipo speciale di ROM non volatile che può essere cancellata esponendola ad una carica elettrica. La EEPROM comprende un gran numero di celle di memoria aventi porte isolate elettricamente (porte flottanti). I

dati vengono memorizzati nelle celle di memoria in forma di carica sulle porte flottanti. Una tipica cella di memoria a porta flottante viene prodotta in un substrato di circuito integrato ed include una regione sorgente ed una regione collettore che è distanziata dalla regione sorgente per formare intermedia di canale. Una regione una conduttiva, realizzata di norma flottante silicio policristallino drogato, oppure uno strato non conduttivo ad intrappolamento di carica flottante), quale nitruro (come verrebbe nodo impiegato in cataste di isolante-porta di silicioossido-nitruro-ossido-silicio o SONOS), è disposta di canale, isolata sulla regione elettricamente dagli altri elementi della celle mediante un materiale dielettrico, di norma ossido, ad esempio, un ossido di canale che viene formato tra la porta/nodo flottante e la regione di canale. Una porta di controllo è localizzata sulla porta/nodo flottante, ed è di norma realizzata in silicio policristallino drogato oppure in metallo. La porta di controllo è separata elettricamente dalla porta/nodo flottante mediante un altro strato la porta flottante o lo di dielettrico. Così, strato/nodo flottante di intrappolamento di carica

è "flottante" nel dielettrico, in modo tale che è isolato sia dal canale sia dalla porta di controllo. La carica viene trasportata verso la oppure rimossa dalla porta flottante o strato di intrappolamento da operazioni specializzate di programmazione e cancellazione, rispettivamente, modificando la tensione di soglia del dispositivo.

Ancora un altro tipo di una memoria non volatile e una memoria Flash. Una tipica memoria Flash comprende una schiera di memoria, che include un gran numero di celle di memoria. Ciascuna delle celle di memoria include una porta flottante o uno strato di intrappolamento di carica incorporato in un transistore a transistore ad effetto di campo (FET). Le celle sono solitamente raggruppate in sezioni chiamate "blocchi dí cancellazione". Ciascuna delle celle all'interno di un blocco di cancellazione può essere programmata elettricamente canalizzando le cariche verso la sua singola porta/nodo flottante. A differenza delle operazioni programmazione, tuttavia, le operazioni cancellazione in memorie Flash di norma cancellano celle di memoria in operazioni di cancellazione di volume, in cui tutte le celle di memoria porta/nodo flottante in un blocco di cancellazione

selezionato vengono cancellate in un'unica operazione. Si osserva che in recenti dispositivi di memoria Flash, più bit sono stati memorizzati in unica cella impiegando più livelli di soglia oppure uno strato non conduttivo di intrappolamento di carica con l'immagazzinamento di dati intrappolati vicino carica ciascuna in una delle sorgenti/collettori della FET a celle di memoria.

Una architettura a schiera EEPROM o NAND Flash dispone la sua schiera di celle di memoria non volatili in una matrice di righe e colonne, come fa una schiera NOR convenzionale, in modo tale che le porte di ciascuna cella di memoria non volatile della schiera vengano accoppiate mediante righe alle linee di parole (WL). Tuttavia, a differenza di una NOR, ciascuna cella di memoria non è accoppiata direttamente ad una linea di sorgenti e ad una linea di colonne di bit. Invece, le celle di memoria della schiera sono disposte insieme in stringhe, di norma di 8, 16, 32 o più ciascuna, dove le celle di memoria nella stringa vengono insieme serie, sorgente accoppiate in da collettore, tra una linea di sorgenti comune ed una linea di colonne di bit. Ciò consente ad una architettura a schiera NAND di avere una maggiore

densità di celle di memoria di una schiera NOR comparabile, tuttavia con il costo di velocità di accesso e complessità di programmazione generalmente minori. Si osserva che sono presenti altre architetture a schiera di memoria non volatile, incluse, tuttavia non limitate a schiere AND, schiere OR, e schiere di massa virtuale.

Un problema nei moderni dispositivi di memoria Flash ad architettura NAND è che, appena vengono ulteriormente ridotte 1e dimensioni caratteristiche con un procedimento migliorato, la separazione tra linee di parole adiacenti nella schiera viene ridotta (pure noto come linea di parole aumentata o cella di memoria "a passo di schiera"). Questa ridotta separazione delle linee di parole può aumentare l'accoppiamento capacitivo tra linee di parole adiacenti, in modo particolare quando queste presentano elevate tensioni applicate ad esse e/oppure sono presenti alte differenze di tensioni tra linee di parole adiacenti, ad esempio durante operazioni di programmazione.

Per i motivi sopra asseriti, e per altri motivi asseriti appresso che diventeranno evidenti a coloro che sono esperti nel ramo dopo aver letto e compreso la presente invenzione, c'è la necessità

nel ramo di metodi di programmazione alternativi e di accesso alle schiere di memoria Flash ad architettura NAND.

#### Breve descrizione dei disegni

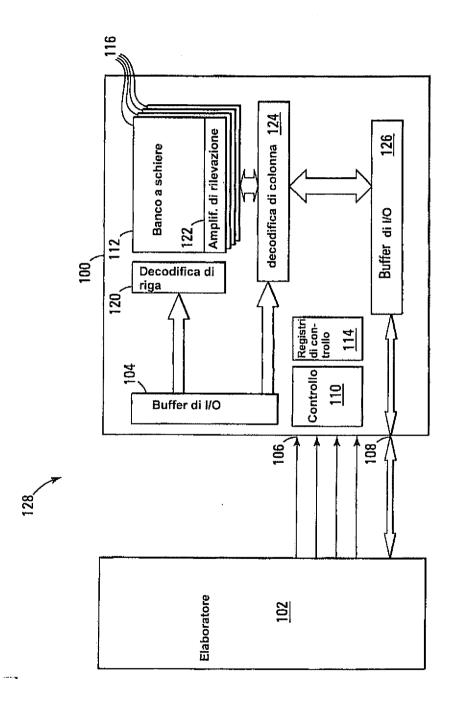

La figura 1 è uno schema a blocchi semplificato di un sistema contenente un dispositivo di memoria non volatile secondo una forma di realizzazione della presente invenzione.

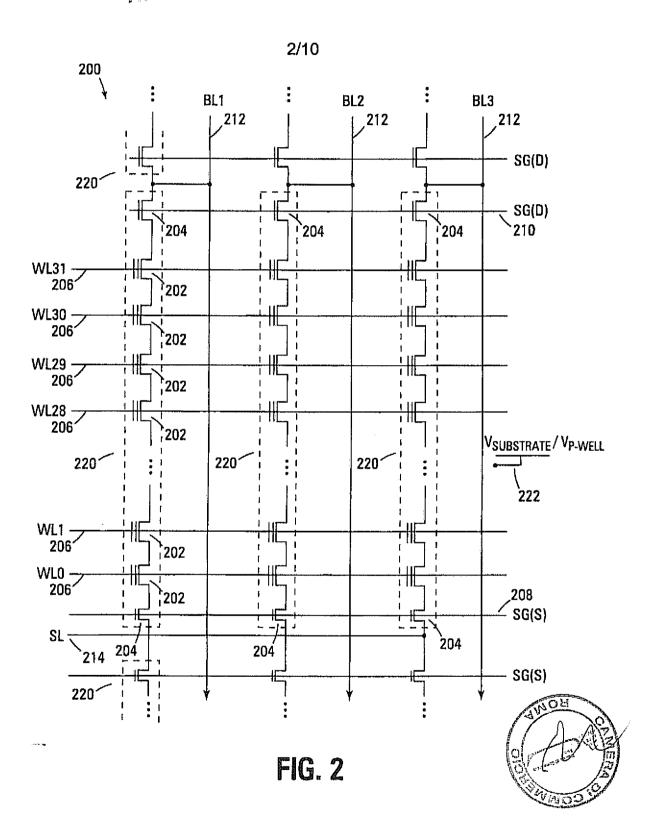

La figura 2 è uno schema a blocchi semplificato di una schiera di memoria Flash ad architettura NAND secondo una forma di realizzazione della presente invenzione.

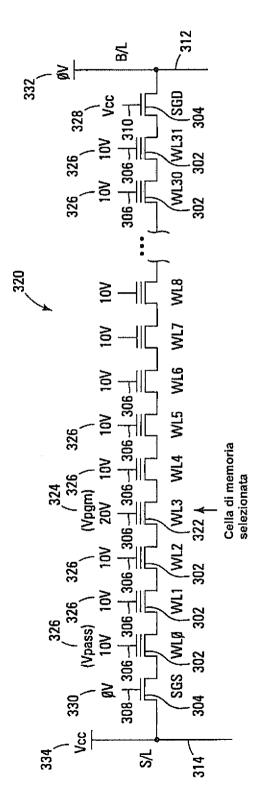

La figura 3 mostra un diagramma che dettaglia tipiche tensioni di linee di parole di programma a stringa non divisa, che mostra la selezione di Vpgm Vpass.

La figura 4 dettaglia tensioni delle linee di parole di programma, mostrante la selezione Vpgm e Vpass in una operazione di programmazione di autoboost locale di tecnica antecedente.

Le figure 5A-5C mostrano diagrammi che dettagliano tensioni delle linee di parole di programma in operazioni di programmazione autoboost e auto-bost locale modificato secondo forme di realizzazione della presente invenzione.

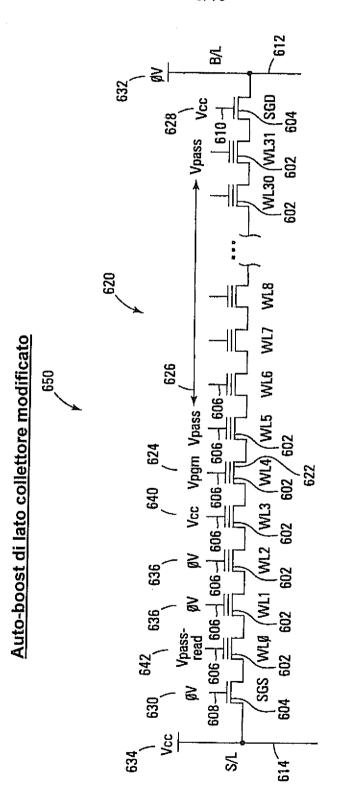

Le figure 6A-6B mostrano diagrammi che dettagliano le tensioni delle linee delle parole di programma in operazioni di programmazione autoboost di lato collettore e auto-boost modificato di lato di collettore secondo forme di realizzazione della presente invenzione.

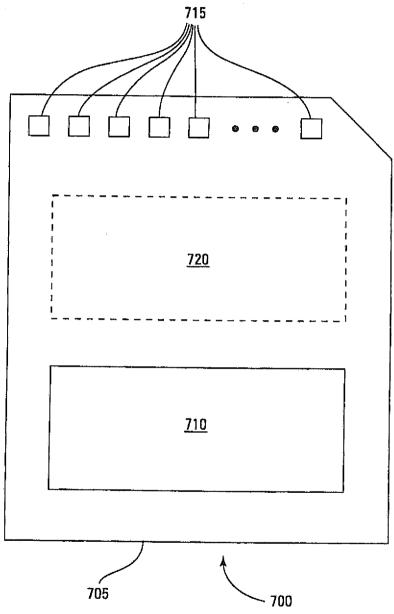

La figura 7 è uno schema a blocchi semplificato di un modulo di memoria secondo la forma di realizzazione della presente invenzione.

#### Descrizione dettagliata

Nella seguente descrizione dettagliata delle forme di realizzazione preferite, si fa riferimento ai disegni annessi che ne fanno parte, ed in cui vengono mostrate, titolo di illustrazione a specifica, forme di realizzazione preferite in cui l'invenzione può essere realizzata. Queste forme di realizzazione vengono descritte in dettaglio sufficiente per consentire а coloro che esperti nel ramo di realizzare l'invenzione, e si deve comprendere che possono essere impiegate altre forme di realizzazione che possono essere effettuate altre variazioni logiche, meccaniche ed elettriche senza allontanarsi dallo spirito dall'ambito della presente invenzione. I termini wafer o substrato impiegati nella descrizione che

seque includono una qualsiasi struttura di base a semiconduttore. Entrambi devono essere compresi come includenti la tecnologia a silicio su zaffiro (SOS), la tecnologia a silicio su isolante (SOI), la tecnologia a transistori a pellicola sottile (TFT), semiconduttori drogati e non drogati, strati epitassiali di silicio supportati da una struttura di base a semiconduttore, nonché altre strutture a semiconduttore ben note a coloro che sono esperti Inoltre, quando nella sequente nel ramo. fa riferimento ad un wafer descrizione si substrato, i precedenti passi dell'elaborazione essere impiegati per formare possono regioni/giunzioni nella struttura semiconduttore, ed i termini wafer o substrato includono gli strati soggiacenti contenenti tali regioni/giunzioni. La descrizione dettagliata che segue, perciò, non deve essere assunta in senso limitativo, e l'ambito della presente invenzione viene definito solo dalle rivendicazioni.

Forme di realizzazioni della presente invenzione includono dispositivi e schiere di memoria che riducono l'effetto dell'accoppiamento capacitivo di tensione a linea di parole rispetto al linea di parole impiegando insiemi di coppie di

linee di parole adiacenti ed applicando la stessa tensione a ciascuna nelle operazioni di accesso di schiera. Ciò consente a ciascuna linea di parole della coppia, in effetti, di schermare l'altra dall'accoppiamento capacitivo delle linee di parole verso linea di parole e di ridurre i suoi effetti sull'insieme accoppiato di linee di parole quello osservato con un'unica linea di parole. Si deve inoltre osservare che più di due linee di parole possono essere pure fatte funzionare come un insieme per una data variazione di tensione in una di memoria per ridurre ulteriormente schiera l'effetto dell'accoppiamento capacitivo di tensione sulla variazione di tensione. Le forme di realizzazione della presente invenzione sono vantaggiose particolarmente in operazioni di di programmazioni di stringhe memoria ad architettura NAND, che combinano linee di parole distanziate da vicino con grandi variazioni del tensione delle linee di parole, livello di rendendole soprattutto sensibili agli effetti dell'accoppiamento capacitivo di tensione.

Si deve osservare che, sebbene varie forme di realizzazione di programmazione operative della presente invenzione vengano descritte in dettaglio

in relazione ad elaborazioni di auto-boost locale e auto-boost sul lato di collettore, le forme di realizzazione di auto-boost di lato sorgente e di massa virtuale della presente invenzione inoltre possibili e saranno evidenti a coloro che sono esperti nel ramo con l'aiuto della presente invenzione. Si deve inoltre osservare che le forme invenzíone della presente realizzazione di includono tutti i dispositivi e memorie a cella di memoria non volatile che intrappolano cariche in una regione elettricamente isolata (ad esempio le flottante/ad nodo celle di memoria а intrappolamento di carica) e non sono limitate alle schiere di celle di memoria oppure a dispositivi di memoria a gate flottante.

La figura 1 dettaglia uno schema semplificato di un sistema 128 che incorpora un dispositivo di 100 forma di volatile di una memoria non realizzazione della presente invenzione collegato ad un host 102, che è di norma un dispositivo di unità di controllo di elaborazione oppure una memoria. La memoria non volatile 100, quale un dispositivo di memoria Flash, ha una interfaccia di controllo 106 ed una interfaccia indirizzo/dati 108, che sono ciascuna collegata al dispositivo di elaborazione 102 per consentire accessi in memoria per lettura e scrittura. Si osserva che, in forme alternative. l'interfaccia di realizzazioni indirizzo/dati 108 può essere divisa in interfacce separate. All'interno del dispositivo di memoria non volatile. una macchina а stati controllo/circuito di controllo 110 dirige il funzionamento interno, gestendo la schiera 112 di memoria non volatile ed aggiornando i registri di controllo di RAM ed ì registri di gestione 114 di cancellazione di blocchi. I registri di controllo di RAM e le tabelle 114 vengono impiegati dalla macchina a stati di controllo 110 durante il funzionamento della memoria non volatile 100. La schiera 112 di memoria non volatile contiene una sequenza di banchi o segmenti di memoria 116, ciascun banco 116 è organizzato logicamente in una serie di blocchi di cancellazione (non mostrati). Indirizzi di accesso in memoria vengono ricevuti sull'interfaccia indirizzo/dati 108 della memoria non volatile 100 e divisi in parti di indirizzo di riga colonna. Su un accesso in lettura, l'indirizzo di riga viene agganciato dal buffer di interfaccia I/O 104 e decodificato mediante un circuito 120 di decodifica di riga, che seleziona

ed attiva una pagina di riga (non mostrata) celle di memoria e le altre celle di memoria nelle loro stringhe associate attraverso un banco memoria selezionato. I valori dei bit codificati all'uscita della riga selezionata di celle memoria vengono collegati da una linea bit/stringa locale (non mostrata) ad una linea di bit globale (non mostrata) е rivelati amplificatori di rilevazione 122 associati al banco di memoria. Gli amplificatori di rivelazione 122 includono inoltre di norma una cache di dati e circuiti di aggancio di dati di scrittura (non mostrati). L'indirizzo di colonna dell'accesso viene pure agganciato dal buffer di interfaccia I/O 104 e decodificato dal circuito 124 di decodifica di colonna. L'uscita del circuito di decodifica di colonna seleziona i dati della colonna desiderata dalle uscita dell'amplificatore di rilevazione e collegate al buffer di dati 126 per trasferimento dal dispositivo di memoria attraverso l'interfaccia indirizzo/dati 108. Su un accesso in scrittura, il circuito 120 di decodifica di riga seleziona la pagina di riga, ed il circuito di decodifica di colonna seleziona gli amplificatori di rilevazione di scrittura 122. Il valore dei dati da scrivere vengono collegati dal buffer dei dati 126 alla cache dei dati, e quindi ai registri latch degli amplificatori 122 di rilevazione di scrittura selezionati dal circuito 124 di decodifica colonna e scritti nelle celle di memoria non volatile selezionata (non mostrate) della schiera di memoria 112. Le celle scritte vengono quindi riselezionate dai circuiti 120, 124 di decodifica riga e colonna e dagli amplificatori rilevazione 122, in modo tale che questi possano essere letti per verificare che i valori corretti sono stati programmati nelle celle di memoria selezionate. Si osserva che, in una forma realizzazione della presente invenzione, la decodifica di colonna 124 può essere facoltativamente posta tra la schiera di memoria 112 e gli amplificatori di rilevazione 122.

sopra asserito, due tipi comuni architetture a schiera di memoria non volatile o Flash sono le architetture "NAND" e "NOR", così chiamate per la rassomiglianza che configurazione della base di celle di memoria di ciascuna architettura ha rispettivamente rispetto circuito a porte NAND NOR. ad un Nella architettura a schiere NAND, le celle di memoria

della schiera di memoria sono disposte in una matrice simile ad una RAM o ROM convenzionale, in modo tale che le porte di ciascuna cella di memoria della schiera vengono accoppiate mediante righe a linee di parole (WL). Tuttavia, ciascuna cella di memoria non è accoppiata direttamente ad una linea di sorgenti (SL) e ad una linea di colonne (BL), come sarebbe il caso nello stile dell'architettura NOR. Invece, le celle di memoria della schiera sono disposte insieme in stringhe, di norma ciascuna di 8, 16, 32 o più, dove le celle di memoria della stringa sono accoppiate insieme in serie, sorgente a collettore, tra una linea di sorgenti comune ed una linea di colonne di bit. Ciò consente ad una architettura a schiera NAND di avere una maggiore densità di celle di memoria rispetto ad una schiera NOR confrontabile, tuttavia con il costo di una velocità di accesso ed una complessità di programmazione in genere minori.

La figura 2 mostra uno schema di una schiera di memoria 200 semplificata a strati di intrappolamento oppure nodi flottanti ad architettura NAND di un dispositivo di memoria Flash NAND, di una forma di realizzazione della presente invenzione. Si osserva che la schiera di

memoria 200 di figura 2 è per fini illustrativi, e non dovrebbe essere presa come limitativa, e che altre forme di realizzazione della schiera memoria NAND della presente invenzione possibili e saranno evidenti a coloro che sono esperti nel ramo con l'aiuto della presente descrizione. In figura 2, una serie di stringhe 220 di memoria NAND è disposta in una schiera 200 ed accoppiata a linee di bit 212 ed a linee sorgenti 214. In ciascuna stringa 220 di memoria NAND, una serie di porte flottanti o celle di memoria a nodi flottanti 202 delle forme di realizzazione della presente invenzione vengono accoppiate insieme, da sorgente a collettore, per formare la stringa NAND 220 (di norma, avente 8, 16, 32 o più celle). Come sopra descritto, ciascun FET 202 di cella di memoria a porta /nodo flottante ha una catasta di isolatori di porta formata sulla regione di canale. Per consentire ulteriormente il funzionamento, in una forma di realizzazione della presente invenzione, una o più stringhe 220 di memoria ad architettura NAND della memoria vengono mostrate formate in una trincea di isolamento, consentendo al substrato di ciascuna trincea di isolamento di essere polarizzato singolarmente per

programmazione e cancellazione. Le linee di parole 206 si accoppiano attraverso le stringhe NAND 220, accoppiando le porte di controllo di celle memoria adiacenti 202 consentendo ad un'unica cella di memoria 202 in ciascuna stringa 220 di memoria di essere selezionata. In ciascuna stringa memoria NAND 220, regioni drogate (di norma, N+) con impurezze vengono formate tra ciascuna catasta di isolante di porta per formare le regioni di sorgente e di collettore delle celle di memoria 202, operano ulteriormente adiacenti che connettori per accoppiare insieme le celle della stringa NAND 220. In una forma di realizzazione della presente invenzione, le regioni drogate N+ vengono omesse, ed un'unica regione di canale viene formata nella stringa di memoria NAND 220, accoppiando le singole celle di memoria Ciascuna stringa di memoria NAND 220 accoppiata per selezionare porte 204 che formate sia al termine di ciascuna stringa NAND 220 sia in estremità di accoppiamento contrapposte in modo selettivo di ciascuna stringa NAND 220 ad una linea di bit 212 e ad una linea di sorgenti 214. Le porte selezionate 204 sono ciascuna accoppiata a linee di selezione di porta, ad un collettore di

selezione di porta {SG(D)} 210 ed alla sorgente di selezione di porta {SG(S)} 208, che controllano l'accoppiamento delle stringhe NAND rispettivamente alle linee di bit 212 e alle linee di sorgenti 214, attraverso le porte di selezione 204. In figura 2, il collegamento di substrato 222 viene mostrato accoppiato a ciascuna stringa NAND 220, consentendo alle celle di memoria 202 di ciascuna stringa NAND 220 di essere polarizzate dal substrato.

Ad una schiera di memoria a nodo flottante o porta flottante ad architettura NAND si accede mediante un decodificatore di riga, attivando una riga di celle di memoria selezionando la linea di selezione di parola accoppiata alle loro porte. Inoltre, vengono pure pilotate le linee di parole accoppiate alle porte delle celle di memoria non selezionate di ciascuna stringa. Tuttavia, le celle di memoria non selezionate di ciascuna stringa vengono di norma pilotate da una tensione di porta maggiore, in modo da farle funzionare transistori di passaggio e consentire loro di far passare corrente in modo che sia illimitata dai loro valori di dati memorizzati. Lа corrente fluisce quindi dalla linea di sorgenti alla linea delle colonne di bit attraverso ciascuna cella di

porta/nodo flottante memoria di della stringa accoppiata in serie, limitata soltanto dalle celle memoria di ciascuna stringa che sono state selezionate da leggere. Questo pone i valori correnti dei dati codificati memorizzati della riga delle celle di memoria selezionate sulle linee di colonna di bit. Una pagina di colonne delle linee di bit viene selezionata e rilevata, e quindi singole parole di dati vengono selezionate dalle parole rilevate di dati dalla pagina di colonna e comunicate dal dispositivo di memoria.

Una tecnica comune di programmazione memorie Flash/EEPROM programma un bit oppure una riga (usualmente indicata come pagina) della memoria applicando una tensione di programmazione oppure una serie di impulsi di tensione programmazione alle porte di controllo delle celle di memoria selezionate, e quindi programmando oppure inibendo le celle di memoria selezionate rispetto ad un livello di soglia programmato (di norma da impostare al valore logico "0" mediante l'iniezione di carica alla porta flottante oppure al nodo flottante di una celle di memoria) oppure ad livello un inibito (la cella non viene programmata e lasciata nel suo stato originario, di

solito inteso per lasciare la cella cancellata ed impostata al valore logico "1") accoppiando canali delle celle di memoria ad un programma oppure ad una tensione di inibizione. Si osserva che talune operazioni di cancellazione includono inoltre cicli di programma. Questi cicli del programma di cancellazione vengono dí norma impiegati per preprogrammare le celle ad tensione di soglia programmata uniforme prima di una cancellatura e, in seguito, "cicatrizzare" le celle di memoria sopra cancellate rispetto ad una tensione uniforme di soglia di stato cancellato.

Come dettagliato in figura 3, in un metodo di programmazione in schiere di memoria Flash/EEPROM ad architettura NAND, la tensione di programmazione 324 viene accoppiata ad una linea di parole 306 accoppiata alla porta della cella di memoria selezionata 322 di una stringa di memoria 320. Inoltre, le linee di parole 206 che sono accoppiate alle porte delle celle di memoria non selezionate 302 della stringa 320 vengono inoltre pilotate da una tensione di passaggio (Vpass) 326 in modo da farle funzionare come transistori di passaggio, generando un canale di portatori mediante accoppiamento capacitivo nelle celle di memoria non

selezionate 302, e consentendo a queste di passare corrente in modo che sia relativamente non vincolata dai loro valori di dati memorizzati. La stringa di memoria 320 viene quindi accoppiata ad linea di bit 312 oppure ad una linea sorgenti 314 che ha posta su di essa una tensione di programma, attraverso il canale generato della stringa 320 ed una od entrambe delle porte di selezione 304. Ciò applica un campo che, attraverso la cella di memoria selezionata 322, fa sì che portatori formino canali dal canale verso la porta flottante oppure uno strato di intrappolamento di carica, modificando il livello della tensione di soglia (Bt) della cella di memoria selezionata 322 e memorizzando il valore di dati. Se una tensione di inibizione di programma viene posta sulla linea di bit accoppiata 312 oppure sulla linea sorgenti 314, il campo applicato non è sufficiente canalizzare i portatori nella porta/nodo flottante, non viene programmato il valore dei dati, e la cella di memoria selezionata 322 rimane nello stato cancellato.

Nella operazione di programmazione esemplificativa dettagliata in figura 3, una tensione di programma (Vpgrm = 20V) 324 viene posta

sulla linea di parole 306 accoppiata alla porta di controllo della cella di memoria selezionata 322. Nella stringa 320 viene generato un canale, mediante l'applicazione di tensione di passaggio (Vpass = 10 V) 326 alle linee di parole accoppiate alle porte di controllo delle celle di memoria non selezionate 302 della stringa 320. La porta di selezione 304 che accoppia la stringa di memoria 320 alla linea di 314 sorgenti disattivata per isolare la stringa 320 dalla linea di sorgenti 314 mediante l'applicazione OV 330 alla linea di controllo 308 della porta di selezione di sorgenti e Vcc 334 alla linea di sorgenti 314. La stringa di memoria 320 è accoppiata alla linea di bit 312 attraverso la porta 304 di selezione di collettore mediante l'applicazione di Vcc 328 alla porta di selezione della linea di controllo di collettore 310 e la cella di memoria selezionata 322 viene quindi programmata ad uno stato logico "0" mediante l'applicazione alla linea di bit 312 di 0V 332. Si osserva che l'operazione programmazione di figura 3 è per fini illustrativi e non dovrebbe essere assunta come limitativa.

Dopo aver programmato la/le cella/e di memoria selezionata/e 322, viene quindi eseguita una

operazione di verifica per confermare che i dati sono stati programmati con successo. Se la/le cella/e di memoria programmata/e 322 falliscono la verifica, il ciclo di programma e di verifica viene ripetuto finchè i dati non vengono programmati con successo oppure non è trascorso un numero di iterazioni selezionato, e si ritiene che l'operazione di programmazione sia fallita.

In altri metodi alternativi di programmazione per stringe di celle di memoria ad architettura NAND, viene impiegata una elaborazione a canale diviso. In una elaborazione di programmazione a canale diviso, una cella di memoria "a blocchi" viene impiegata dividere il canale per della stringa in due o più sezioni per isolare celle di memoria e/oppure le sezioni di stringa durante la programmazione con l'aiuto di velocità o rendimento di programmazione migliorati, del rendimento del boost canale e/oppure rendendo minimo il disturbo di programma delle celle di memoria non volatili della stringa. Questi metodi di programmazione includono, tuttavia non sono limitati a elaborazioni di programmazione di autoboost locale, auto-boost locale modificato, autoboost di lato di collettore, auto-boost di lato di

collettore modificato, auto-boost di lato dí sorgente. di е massa virtuale. In queste elaborazioni di programmazione a canale suddiviso, le celle a blocchi sono di norma poste adiacenti alla cella di memoria che è stata selezionata per la programmazione, e presentano una potenziale di massa, o Vss, posto sulle loro linee di parole per porle in interdizione. Nella operazione programmazione, la tensione di programmazione è quindi accoppiata alla linea di parole della cella selezionata, e Vpass viene posto sulle linee di parole non selezionate tra la cella di memoria selezionata e la linea di bit per effettuare il boost del canale sotto le celle. La cella di memoria selezionata viene quindi variamente accoppiata alla linea di bit oppure alla linea di sorgenti per applicare una tensione di programma o di inibizione di programma per completare l'operazione di programmazione.

Ad esempio, l'auto-boost di lato collettore (pure noto come auto-boost di area cancellata) aiuta ad impedire la possibilità di disturbo in celle di memoria adiacenti e stringhe adiacenti isolando il canale della cella di memoria che sta venendo programmata oppure inibita dalle rimanenti

celle di memoria non programmate della stringa. In una operazione di programmazione auto-boost di lato collettore, una cella di memoria/linea di parole sul lato della linea di sorgenti della cella di memoria selezionata per programmazione fissata a OV oppure a massa come una cella del blocco per isolare le celle a valle della stringa di memoria. Una tensione di programmazione viene quindi accoppiata alla linea di parole della cella selezionata per accoppiare oppure "eseguire un boost" del canale sotto la cella selezionata, e Vpass viene posto nelle linee di parole non selezionate tra la cella di memoria selezionata e la linea di bit per eseguire un boost del canale sotto le celle non selezionate. Questo accoppia la cella di memoria selezionata alla linea di bit che ha applicata ad essa una tensione di programma o di inibizione di programma. Qualsiasi altra linea di parole sul lato di sorgente isolato dal canale principale mediante la cella del blocco ha Vpass applicato a questa per generare un canale locale ed inoltre aiutare nella prevenzione di un disturbo di programma. L'auto-boost di lato sorgente è una tecnica correlata all'auto-boost di collettore. L'auto-boost di lato sorgente esegue un

boost di un canale sotto la cella di memoria selezionata e tutte le celle di memoria sul lato sorgente della cella di memoria selezionata applicando il programma oppure l'inibizione di programma alla linea di sorgenti della stringa di celle di memoria. L'auto-boost locale inoltre isola la cella programmata della stringa ponendo a massa linee di memoria adiacenti direttamente entrambi i lati della linea di parole selezionata, e fissa a Vpass le rimanenti delle linee di parole selezionate. Esistono inoltre elaborazioni auto-boost locale modificato, auto-boost di lato collettore ed auto-boost di lato sorgente che impiegano una tensione secondaria, ad esempio Vcc, su una linea di parole intercorrente per diminuire la tensione dalla tensione di programmazione della linea di parole e gli OV o Vss della cella del blocco, riducendo la differenza complessiva tensione osservata tra una qualsiasi delle linee di parole adiacenti.

Come sopra asserito, un problema nei moderni dispositivi di memoria è che l'accoppiamento capacitivo di tensione può influenzare i livelli di tensione delle linee di parole e introdurre rumore di tensione non voluto appena questi vengono

impiegati in operazioni di accesso di schiera. Gli effetti dell'accoppiamento capacitivo aumentano quando la distanza tra conduttori viene diminuita e/oppure quando le tensioni pilotate sui conduttori vengono aumentate. Appena la distanza conduttori diminuisce, il rapporto di accoppiamento tra i conduttori viene aumentato, mentre aumenta pure in genere la resistenza dei conduttori, dal momento che diminuisce in genere la sezione trasversale dei conduttori, influenzando negativamente la costante di tempo RC del conduttore е la capacità del dispositivo di pilotaggio a superare qualsiasi di rumore tensione). Perciò, dal momento che le dimensioni e le caratteristiche del dispositivo ulteriormente ridotte (pure noto come aumentare il "passo di schiera" delle linee di parole o delle celle di memoria), viene diminuita la separazione linee di parole adiacenti, e gli effetti dell'accoppiamento capacitivo di tensione in moderno dispositivo di memoria diventano così più di un problema. Questo effetto dell'accoppiamento capacitivo è particolarmente un problema dispositivi a memoria non volatile che possono pure porre elevate tensioni sulle linee di

adiacenti, ad esempio durante una operazione di programmazione e cancellazione.

L'accoppiamento capacitivo ha l'effetto di. indurre rumore di tensione nei livelli di tensione pilotati delle linee di parole, opponendosi a variazioni di tensione della linea di parole e/oppure allo sfalsamento della linea di tensione (per effetto di una variazione di parole tensione su una o più linee di parole adiacenti). L'accoppiamento capacitivo, in particolare, influenzare singole linee di parole che vengono pilotate ad un tensione differente di quella di linee di parole adiacenti (oppure singole linee di livello parole che vengono conservate al di tensione originario mentre le linee di parole adiacenti vengono variate) a causa degli effetti di accoppiamento da più lati della quantità е relativamente piccola di carica presente singola linea di parole stessa. Ciò può consentire disturbo o corruzione di dati, un rendimento di programmazione abbassato, oppure guasto, un rendimento abbassato di cancellazione di blocchi, sovracancellazione, lavoro di scrittura aumentato, velocità di accesso più bassa, oppure altri problemi determinati dall'eccessivo

accoppiamento capacitivo indotto attraverso la distanza ravvicinata di schiere e grandi differenze di tensioni.

Dal momento che questi di norma non presentano di molte linee intercorrenti bit. linee sorgenti, linee di controllo o altri dispositivi mezzo di ciascuna stringa di memoria per aumentare la separazione delle linee di parole come altri tipi di architettura di schiere di memoria, dispositivi di memoria non volatile ad architettura NAND ad alta densità possono soprattutto essere influenzati da problemi di accoppiamento di tensione capacitiva.

Ad esempio, in elaborazioni di programmazione di canale suddiviso ad architettura NAND, il canale munito di boost può non effettuare un boost in modo efficiente oppure perfino perdere la carica di boost se le celle a blocchi non sono fermamente in interdizione, e possono fuoriuscire cariche del canale di stringa di memoria. Ciò può verificarsi in modo massimamente prevalente in due situazioni. In primo luogo, quando le celle adiacenti/a blocchi si trovano in uno stato cancellato in modo profondo (cioè, sovracancellate e da funzionare così come dispositivi a modo di svuotamento, aventi una

tensione di soglia negativa o vicina a zero volt). Oppure, in secondo luogo, quando rumore di tensione indotto dalle alte tensioni di programmazione delle linee di parole e gli effetti capacitivi accoppiamento impediscono fermo in modo il posizionamento in interdizione delle celle blocchi (lasciandole leggermente "ON" o facendole condurre ed operando in modo non lineare oppure anche in modo lineare) durante un boost.

Come sopra asserito, le forme di realizzazione dei dispositivi di memoria della presente invenzione riducono gli effetti dell'accoppiamento di tensione da linea di parole a linea di parole impiegando insiemi di coppie di linee di parole adiacenti ed applicando a ciascuna la tensione nell'operazione di accesso di schiera. Ciò consente a ciascuna linea di parole della coppia, in realtà, di schermare l'altra dall'accoppiamento capacito di tensione, riducendo l'effetto sull'insieme accoppiato di linee di parole quello osservato con un'unica linea di parole. Si osserva inoltre che più di due linee di parole possono essere fatte funzionare come un insieme per ridurre ulteriormente l'effetto dell'accoppiamento capacitivo di tensione su una data variazione di

tensione. Le forme di realizzazione della presente invenzione sono particolarmente vantaggiose operazioni di programmazione di stringhe di memoria ad architettura NAND per aumentare il rendimento di boost di canali, dal momento che le linee di parole distanziate da vicino e le grandi variazioni del tensione della linea di parole di livello di dispositivi ad architettura NAND ٦6 rendono soprattutto suscettibili agli effetti dell'accoppiamento capacitivo di tensione.

In forme di realizzazione di un dispositivo di memoria non volatile ad architettura NAND e di elaborazione di programmazione della presente invenzione, le varie celle di stringhe di celle di memoria non volatili vengono programmate impiegando una elaborazione a canale suddiviso, ad esempio una elaborazione di programmazione auto-boost locale, auto-boost locale modificato, auto-boost di lato collettore, auto-boost di lato collettore modificato, auto-boost di lato sorgente e di masse virtuale, che impiegano due o più celle di memoria "a blocchi" per dividere il canale della stringa ed isolare le varie celle di memoria o le sezioni di stringhe durante una programmazione. Le coppie di celle a blocchi sono di norma poste adiacenti alla

cella di memoria selezionata per una programmazione, e presentano un potenziale di massa, o Vss, posto sulle loro linee di parole per interdizione. porle in un Nell'operazione di programmazione, la tensione di programmazione viene quindi accoppiata alla linea di parole della cella selezionata, e Vpass viene posto sulle linee di parole non selezionate tra la cella di memoria selezionata e la linea di bit per eseguire il boost del canale sotto le celle selezionate selezionate. La cella di memoria selezionata viene quindi accoppiata in modo vario alla linea di bit per programma oppure inibizione di programma. Le celle accoppiate di memoria а blocchi non selezionate si schermano l'una con l'altra durante l'operazione di programmazione e l'applicazione della programmazione e delle tensioni Vpass per ridurre il rumore delle linee di parole, impedendo a queste di attivarsi e di far fuoriuscire carica al di fuori del canale munito boost. Ciò diminuisce la fuoriuscita di canale e aumenta il rendimento di boost durante una programmazione.

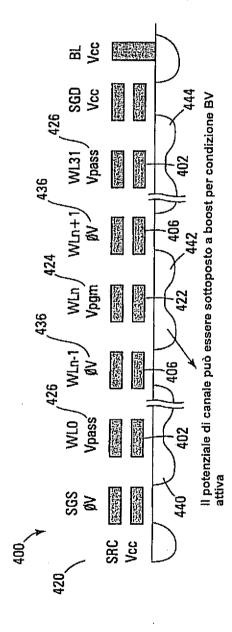

La figura 4 illustra una memoria ad architettura NAND di tecnica antecedente 400 in una operazione di programmazione di auto-boost locale

con uniche celle a blocchi, che mostra le sezioni di canale generate. In figura 4, una cella di memoria 422 accoppiata ad un WLn della stringa di memoria 420 è stata selezionata per programmazione, ed a questa è stata applicata una elevata tensione celle di programmazione 424. Le memoria direttamente adiacenti accoppiate a WLn+1 e WLn-1 singole celle а blocchi per da agiscono l'operazione di auto-boost locale e presentano una tensione di interdizione (ad esempio, massa o OV) 436 applicata alle loro porte. Una tensione di passaggio (Vpass) 426 è accoppiata alle porte delle rimanenti celle di memoria non selezionate della stringa 420 che si trovano all'esterno delle celle a blocchi. Questo eseque un boost di canale di portatori mediante accoppiamento capacitivo al disotto delle celle di memoria 402, 422, che viene suddiviso in tre sezioni (una sezione 440 di canale munito di boost di lato sorgente, una sezione 444 di canale munito di boost di lato collettore, ed il della munito di boost 442 cella canale programmata), ciascuna con differenti tensioni di isolato dalle celle a canale munito di boost, blocchi di interdizione 406. Come sopra asserito, se le celle a blocchi sono state cancellate in profondità (sovracancellate) oppure presentano una tensione di linee di parole indotta sulle loro porte di controllo mediante accoppiamento capacitivo a Vpass 426 oppure Vpgm 424 delle linee di parole adiacenti, il canale munito di boost può non effettuare un boost in modo efficiente o perfino perdere la carica di boost dal momento che le celle a blocchi non saranno fermamente in interdizione e fuoriusciranno cariche da sezione in sezione del canale di stringa di memoria.

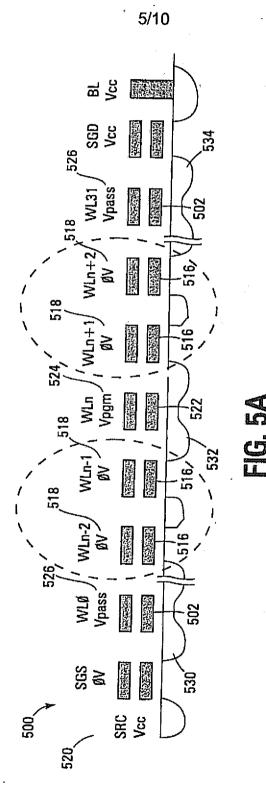

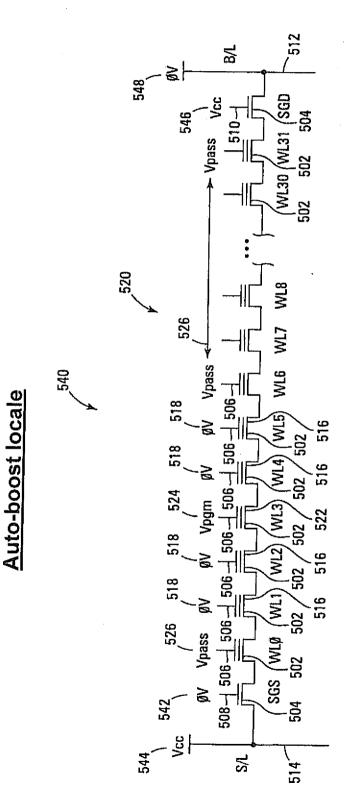

Le figure 5A-5C e 6A-6B illustrano una tipica schiera di memoria ad architettura NAND operazioni di programmazione di stringa di forme di realizzazione della presente invenzione impiegano linee di parole accoppiate per schermarle dagli effetti dell'accoppiamento capacitivo. riducendo la fuoriuscita di carica ed aumentando il rendimento del boost di canale. Si osserva che, mentre le forme di realizzazione delle operazioni di programmazione NAND della presente invenzione vengono descritte in relazione ad elaborazioni di auto-boost locale e diauto-boost di collettore, forme di realizzazione di auto-boost di lato sorgente e di massa virtuale della presente invenzione sono pure possibili, e saranno evidenti

a coloro che sono esperti nel ramo con l'aiuto della presente invenzione. Si deve perciò pure osservare che le operazioni di programmazione NAND descritte nelle figure 5A-5C e 6A-6B sono per finalità illustrative e non dovrebbero essere assunte come limitative.

Le figure 5A e 5B illustrano una memoria ad architettura NAND 500, 540 di una forma di realizzazione della presente invenzione che impiega coppie di celle a blocchi 516 per schermare gli effetti dell'accoppiamento capacitivo durante una operazione di programmazione di auto-boost locale e che mostra le sezioni di canale generate 530, 532, 534. 5, una celle di memoria Ιn figura accoppiata a WLn della stringa di memoria 520 è stata selezionata per una programmazione, ed è stata applicata a questa una elevata tensione di programmazione 524. Le coppie di celle di memoria direttamente adiacenti accoppiate a WLn+1, WLn+2 e WLn-1, WLn-2 sono state selezionate in modo da agire come celle a blocchi accoppiate 516 l'operazione di auto-boost locale, e presentano una tensione di interdizione (ad esempio massa o 0V) 518 applicata alle porte di controllo di ciascuna coppia. Una tensione di passaggio (Vpass) 526 è

accoppiata alle porte delle rimanenti celle di memoria non selezionate 502 della stringa 520 che sono al di fuori delle celle a blocchi 516. Questo esegue un boost di canale di portatori mediante accoppiamento capacitivo sotto le celle di memoria 502, 522 nella stringa 520, che è divisa in tre sezioni (una sezione 530 di canale munito di boost di lato sorgente, una sezione 534 di canale munito di boost di lato collettore ed il canale 532 munito di boost di cella programmata), ciascuna con differenti tensioni di canale di boost isolate dalle celle a blocchi di interdizione 516.

osservato, le forme di Come sopra realizzazione delle celle a blocchi accoppiate 516 della presente invenzione consentono alle loro linee di parole di aiutare la schermatura l'una con l'altra dagli effetti negativi dell'accoppiamento capacitivo, riducendo qualsiasi tensione di linea di parole indotta sulle loro porte di controllo da un accoppiamento capacitivo rispetto Vpass 526 o Vpqm 524 delle linee di parole adiacenti. Ciò consente al canale di esequire efficacemente un boost ed impedisce la perdita della carica di boost dal momento che le celle a blocchi 516 saranno saldamente in interdizione, е la carica

fuoriuscirà da sezione a sezione del canale 530, 532, 534 della stringa di memoria. Inoltre, il problema con celle profondamente cancellate (sovracancellate) viene allentato dal momento che la probabilità di avere entrambe le celle a blocchi 516 instato cancellato profondamente o uno sovracancellato è piccola. Così, perfino se una cella della coppia a blocchi 516 si trova in uno stato profondamente cancellato, è alta la probabilità che un'altra cella non lo sarà e, così, almeno una cella della coppia sarà "OFF" e posta in interdizione. Ciò consente, in varie forme realizzazione della presente invenzione. verifica di cancellazione meno rigorosa e/oppure un procedimento di cicatrizzazione e l'accettazione di una più ampia finestra di intervallo/logica per lo stato cancellato.

In figura 5B, una cella di memoria 522 accoppiata a WL3 506 della stringa di memoria 420 che è stata selezionata per programmazione, ed è stata applicata a questa una elevata tensione di programmazione 524. Le celle di memoria accoppiate a linee di parole adiacenti, WL1/WL2 e WL4/WL5 agiscono come coppie di celle a blocchi per l'autoboost locale, e presentano una tensione di

interdizione (massa o OV) 518 applicata alle loro porte. Inoltre, una tensione di passaggio (Vpass) 526 viene applicata a WLO durante l'operazione di programmazione per effettuare un boost di tensione nel canale osservato alla sorgente della cella del blocco di WLO e migliorare l'interdizione in questo nella porta 504 di sorgente selezionata accoppiata alla linea di sorgenti 514. Le linee di parole 506 che sono accoppiate alle porte delle celle di memoria non selezionate 502 della stringa 520 verso la linea di bit 512 vengono pure pilotate dalla tensione di passaggio (Vpass) 526 in modo da farle funzionare come transistori di passaggio, generando un canale di portatori mediante l'accoppiamento capacitivo nelle celle di memoria non selezionate 502, e consentendo a questi di far passare corrente in un modo che sia relativamente illimitata dai loro valori della tensione soglia. Una volta che i canali di portatori vengono muniti di boost nella stringa di memoria 520, celle a blocchi 516 sul lato di collettore della cella di memoria selezionata 522 vengono attivate pilotando le loro porte con Vpass per accoppiare la cella di memoria selezionata 522 ad una linea di bit 512 che ha posta su di essa una tensione di

programma, attraverso il canale generato di lato collettore della stringa 520 e la porta 504 di selezione di collettore. Ciò applica un campo attraverso la cella di memoria selezionata 522 che fa sì che i portatori si canalizzino dal canale la porta flottante oppure lo strato di verso intrappolamento di carica, modificando il livello di tensione (Vt) della cella di memoria selezionata 522 e memorizzando il valore di dati. Se tensione di inibizione di programma è posta sulla linea di bit accoppiata 512, il campo applicato non è sufficiente a canalizzare i portatori verso la porta/nodo flottante, non viene programmato alcun valore di dati, e la cella di memoria selezionata 522 rimane nello stato cancellato.

Ad esempio, nell'operazione di programmazione dettagliata in figura 5B, una tensione di programma (Vpgm = 20V) 524 è posta sulla linea di parole 506 accoppiata alla porta di controllo della cella di memoria selezionata di WL3, 522. Una tensione di passaggio (Vpass = 9V) 526 è applicata alle linee di parole 506 accoppiate alle porte di controllo delle celle di memoria non selezionate di lato collettore 502 della stringa 520. Le celle di memoria 502 accoppiate a WL1/WL2 e WL4/WL5 agiscono

dal momento che le coppie 516 delle celle a blocchi hanno una tensione di interdizione (ad esempio OV, VSS o massa) 518 applicata alla loro porta per interdizione, e viene in applicata tensione di passaggio (Vpass = 9 V) 526 a WLO per eseguire il boost della tensione alla sorgente della cella del blocco 516 di WL1, e migliorano l'interdizione in questa e nella porta di selezione 504 accoppiata alla linea di sorgenti 514. La porta di selezione 504 che accoppia la stringa di memoria 520 alla linea di sorgenti 514 viene disattivata per isolare la stringa 520 della linea di sorgenti 514 mediante l'applicazione di OV 542 alla linea di controllo 508 della porta di selezione di sorgente e Vcc 544 alla linea di sorgenti 514. La stringa di memoria 520 viene quindi accoppiata alla linea di bit 512 attraverso la porta 504 di selezione di collettore mediante l'applicazione di Vcc 546 alla linea di controllo 510 di collettore della porta di selezione, e la cella di memoria selezionata 522 viene quindi programmata al valore logico "0" dallo stato cancellato oppure al valore logico mediante l'applicazione di OV 548 alla linea di bit 512.

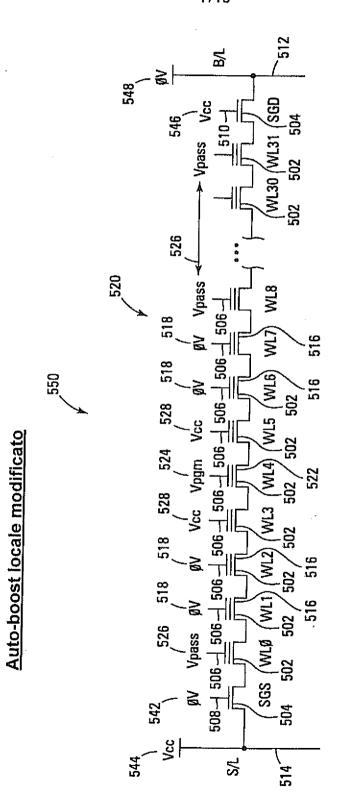

La figura 5C illustra una forma di

realizzazione di una memoria 550 ad architettura NAND della presente invenzione, che impiega coppie di celle a blocchi 516 per schermare gli effetti dell'accoppiamento capacitivo durante operazione di programmazione di auto-boost locale modificato. In figura 5C, la cella di memoria 522, accoppiata al WL4 506 della stringa di memoria 520, è stata selezionata per programmazione, ed è stata applicata а questa una elevata tensione programmazione 524. Celle di linee di 502 parole/memoria accoppiate а MT3 WL5. adiacenti direttamente alla cella di memoria/WL4 selezionata per la programmazione 522, vengono accoppiate ad una tensione intermedia 528, ad esempio Vcc oppure Vdd, per far diminuire la differenza di tensione massima di linea di parole rispetto alla linea di parole dell'operazione di programmazione. Le celle di memoria 502 accoppiate WL1/WL2 e WL4/WL5 agiscono dal momento che coppie delle celle a blocchi per l'auto-boost locale modificato hanno un potenziale di massa o OV 518 applicato alle loro porte. Inoltre, tensione di passaggio (Vpass) 526 viene applicata a durante l'operazione di programmazione per eseguire il boost della tensione alla sorgente

della cella del blocco di WL1 е migliorare l'interdizione della cella del blocco e della porta di selezione 504 accoppiata alla linea di sorgenti 514. Le linee di parole 506 che sono accoppiate alle porte delle celle di memoria non selezionate 502 della stringa 520 verso la linea di bit 512 vengono pilotate da una tensione di passaggio farle funzionare come 526 in modo da (Vpass) transistori di passaggio, generando un canale di portatori nelle celle di memoria non selezionate 502. Una volta che sono stati generati i canali dei portatori, le celle a blocchi 516 sul lato di collettore della cella di memoria selezionata 522 vengono accoppiate a Vpass, accoppiando la stringa di memoria 520 ad una linea di bit 502 la stringa di memoria 520 ad una linea di bit 512 che ha posta su di essa una tensione di programma o inibizione di programma, attraverso il canale di lato collettore generato della stringa 520 e la porta di selezione 504.

Si osservi che le linee di parole selezionate, i livelli di programmazione operativi e di tensione delle figure 5A-5C sono per fini illustrativi e non dovrebbero essere assunti come limitazione.

La figura 6A illustra una forma di

realizzazione di una memoria ad architettura NAND della presente invenzione che impiega coppia di celle a blocchi 616 per schermare gli effetti dell'accoppiamento capacitivo durante una operazione di programmazione auto-boost di lato collettore. In figura 6A, una cella di memoria 622 accoppiata a WL4 606 della stringa di memoria 620 è stata selezionata per programmazione, ed è stata applicata questa una elevata tensione di programmazione 624. Le celle di memoria accoppiate WL2 WL3, sul lato sorgente della cella selezionata, agiscono come la coppia 616 di celle a blocchi per l'auto-boost di lato collettore, hanno una tensione di interdizione (ad esempio massa o OV) 636 applicata alle loro porte. Inoltre, una tensione di passaggio di lettura (Vpass-read, la tipica tensione di passaggio di lettura per il dispositivo di memoria) 642 è applicata a WLO e WL1 durante l'operazione di programmazione per esequire il boost di tensione alla sorgente della cella del blocco di WL2 e migliorare l'interdizione in questa nella porta 604 di selezione di accoppiata alla linea di sorgenti 614. Si osservi in un'altra forma di realizzazione, viene impiegata una tensione di passaggio di programma

(Vpass) invece della tensione di passaggio lettura (Vpass - read) su WLO e WL1 (le celle di memoria non selezionate 602 di lato sorgente). Le linee di parole 606 che sono accoppiate alle porte delle celle di memoria non selezionate 602 della stringa 620 verso la linea di bit 612 (il lato di collettore della cella di memoria selezionata 622) vengono pilotate mediante una tensione di passaggio di programma (Vpass) 626 in modo da farle funzionare come transistori di passaggio, generando un canale di portatori mediante accoppiamento capacitivo nelle celle di memoria non selezionate 602, e consentendo loro di far passare corrente in modo tale che venga relativamente illimitata dai loro valori di tensione di soglia. La stringa di memoria 620 è quindi accoppiata ad una linea di bit 612 che ha una tensione di programma posta su di attraverso il canale di essa, lato collettore generato della stringa 620 e la porta di selezione di collettore 604. Ciò applica un campo attraverso la cella di memoria selezionata 622 che fa sì che i portatori si canalizzino tra il canale verso la porta flottante o lo strato di intrappolamento di carica, modificando il livello della tensione di soglia (Vt) della cella di memoria selezionata 622

e memorizzando il valore di dati. Se una tensione di inibizione di programma viene posta sulla linea di bit accoppiata 612, il campo applicato non è sufficiente a canalizzare i portatori verso la porta/nodo flottante, non viene programmato alcun valore di dati, e la cella di memoria selezionata 622 rimane nello stato cancellato.

Ad esempio, nell'operazione di programmazione dettagliata in figura 6A, la tensione di programma  $(Vpgm = 20 \ V)$  624 è posta sulla linea di parola 606 accoppiata alla porta di controllo della cella di memoria selezionata di WL4 = 622. Viene generato un canale nella stringa 620, mediante l'applicazione di una tensione di passaggio (Vpass = 9V) 626 alle linee di parole 606 accoppiate alle porta controllo delle celle di memoria non selezionate di lato collettore 602 della stringa 620. Le celle di memoria a blocchi accoppiate a WL2 e WL3 hanno una tensione di interdizione, ad esempio OV, Vss o massa) 636 applicata alle loro porte per porle in interdizione, ed una tensione di passaggio lettura (Vpass - read = 6V-8V) 638 viene applicata a WLO e WL1 (le celle non selezionate di lato sorgente) per eseguire il boost di tensione alla sorgente delle celle a blocchi WL2

migliorare l'interdizione in queste e nella porta di selezione 604 accoppiata alla linea di sorgenti 614. La porta di selezione 604 che accoppia la stringa di memoria 620 alla linea di sorgenti 614 viene disattivata per isolare la stringa 620 dalla linea di sorgenti 614 mediante l'applicazione di 0V 360 alla linea di controllo della porta di sorgente 608 e Vcc 634 alla linea di sorgenti 614. stringa di memoria 620 è accoppiata alla linea di bit 612 attraverso la porta di selezione collettore 604 mediante l'applicazione di Vcc 628 alla linea di controllo del collettore della porta selezionata 610, e la cella di memoria selezionata 622 viene quindi programmata allo stato logico "0" mediante l'applicazione di OV 632 alla linea di bit 612.

illustra La figura 6B una forma di realizzazione di una memoria ad architettura NAND 650 della presente invenzione che impiega coppia di celle a blocchi 616 per schermare gli effetti dell'accoppiamento capacitivo durante una operazione di programmazione di auto-boost di lato collettore. In figura 6B, la cella di memoria 622 accoppiata al WL4 606 della stringa di memoria 620 è stata selezionata per la programmazione, ed è

stata applicata a questa una elevata tensione di programmazione 624. La cella 602 di memoria/linea di parole accoppiata a WL3, direttamente adiacente cella di memoria/WL4 selezionata alla per programmazione 622, è accoppiata ad una tensione intermedia 640, ad esempio Vcc oppure Vdd, per diminuire la massima differenza di tensione della linea di parole rispetto а linea dì parole dell'operazione di programmazione. Le celle di memoria accoppiate a WL1 e WL2 fanno agire la coppia di celle a blocchi per l'auto-bost di lato collettore modificato, ed hanno potenziale di massa o OV 636 applicato alle loro porte. Inoltre, a WLO, viene applicata una tensione di passaggio di lettura (Vpass-read) 642 durante l'operazione di programmazione per eseguire il bost di tensione alla sorgente della cella del blocco di WL1 e migliorare l'interdizione nella cella del blocco e nella porta di selezione 604 accoppiata alla linea di sorgenti 614.

Le linee di parole 606 che sono accoppiate alle porte delle celle di memoria non selezionate 602 della stringa 620 verso la linea di bit 612 vengono pilotate da una tensione di passaggio (Vpass) 626, in modo da farle funzionare come

transistori di passaggio, generando un canale di portatori nelle celle di memoria non selezionate 602. La stringa di memoria 620 viene quindi accoppiata ad una linea di bit 612 che ha una tensione di programma oppure in inibizione di programma posta su di essa, attraverso il canale di lato connettore generato della stringa 620 e della porta di selezione 604.

Viene di nuovo osservato che l'operazione di programmazione dei livelli di tensione delle figure 6A-6B sono per fini illustrativi, e non dovrebbe essere assunta come limitativa. Si deve inoltre osservare che nelle forme di realizzazione di autoboost di lato sorgente e di auto-boost di lato sorgente modificato della presente invenzione, tensioni applicate alla stringa di memoria 620 sono opposte speculari dell'auto-boost di collettore, con la coppia di celle a blocchi 616 sul lato collettore della cella di selezionata, e la cella di memoria selezionata essendo accoppiata alla linea di sorgenti 614 per tensione di programma o di inibizione programma attraverso un canale di portatori generati nelle celle di memoria non selezionate 602 di lato sorgente. Si deve inoltre osservare che le

realizzazione di massa virtuale della di presente invenzione consentono ai ruoli della linea di sorgenti 624 e della linea di bit 612 di essere intercambiati, invertendo il flusso dei portatori nella stringa, invertendo l'applicazione forma selezionata dell'operazione di programmazione di auto-boost di lato collettore, di auto-boost di lato sorgente oppure di auto-boost locale che viene impieqata stringa. Ciò, sulla in particolare, consente a porte/nodi flottanti non conduttivi di essere impiegati per memorizzare più bit di dati in ciascuna cella di memoria della stringa attraverso l'immagazzinamento di cariche su ciascuna regione sorgente/collettore della cella.

Si osservi che possono essere impiegate altre tensioni e numero di celle blocchi operazioni di programmazione di massa virtuale, di auto-boost locale, di auto-boost di lato sorgente, auto-boost di lato connettore non modificato e modificato, come sarà evidente a coloro che sono esperti nel ramo l'aiuto con della presente descrizione.

La figura 7 è una illustrazione di un modulo di memoria 700 secondo una forma di realizzazione della presente invenzione. Il modulo di memoria 700

viene illustrato come scheda di memoria, sebbene i concetti discussi con riferimento ad un modulo di memoria 700 siano applicabili ad altri tipi di memorie portatili o amovibili, ad esempio unità Flash USB, che sono intese essere nell'ambito di "modulo di memoria" come impiegato in questa sede. Inoltre, sebbene in figura 7 venga descritto un fattore di forma esemplificativo, questi concetti sono applicabili pure ad altri fattori di forma.

In talune forme di realizzazione, il modulo di memoria 700 includerà un alloggiamento 705 (come illustrato) per custodire uno o più dispositivi di memoria 710, sebbene un alloggiamento non essenziale per tutti i dispositivi o applicazioni di dispositivo. Almeno un dispositivo di memoria 710 è una memoria non volatile che include circuiti per oppure adatti ad eseguire elementi di metodi della presente invenzione. Dove presente, l'alloggiamento 705 include uno o più contatti 715 per comunicazione con un dispositivo host. Esempi di dispositivi host includono videocamere digitali, dispositivi di registrazione e di riproduzione digitale, PDA, personal computer, lettori di schede di memoria, hub di interfaccia e simili. Per talune forme di realizzazione, i contatti 715 sono nella

forma di una interfaccia standardizzata. Ad esempio, con una unità Flash USB, i contatti 715 potrebbero essere nella forma di un connettore maschio USB del tipo A. In genere, tuttavia, i contatti 715 uniscono una interfaccia per far passare segnali di controllo, di indirizzo e/oppure di dati tra il modulo di memoria 700 ed un host avente recettori compatibili per i contatti 715.

Il modulo di memoria 700 può facoltativamente includere una ulteriore circuiteria 720, che può essere uno o più circuiti integrati e/oppure componenti discreti. Per talune forme di realizzazione, la circuiteria ulteriore 720 può includere una unità di controllo di memoria 710 per controllare l'accesso attraverso più dispositivi di memoria 710 e/oppure per fornire uno strato di traslazione tra un host esterno ed un dispositivo di memoria 710. Ad esempio, può non esservi una corrispondenza da uno ad uno tra il numero contatti 715 ed il numero di collegamenti all'uno o più dispositivi di memoria 710. Così, una unità di controllo di memoria potrebbe accoppiare selettivamente un collegamento I/O (non mostrato in figura 7) di un dispositivo di memoria 710 per ricevere 1'opportuno segnale all'opportuno

collegamento all'istante I/O opportuno oppure fornire l'opportuno segnale all'opportuno contatto 715 nell'opportuno istante. In modo simile, il protocollo di comunicazione tra un host e il modulo di memoria 700 può essere differente da ciò che viene richiesto per l'accesso di un dispositivo di memoria 710. Una unità di controllo di memoria potrebbe quindi traslare le sequenze di comando ricevute da una host nelle opportune sequenze di comando per ottenere l'accesso desiderato al dispositivo di memoria 710. Tale traslazione può includere inoltre variazioni nel livello di tensione dei segnali oltre alle sequenze di comando.

La ulteriore circuiteria 720 può ulteriormente funzionalità includere la non correlata al controllo di un dispositivo di memoria 710, quali funzioni logiche come potrebbero essere eseguite da una ASIC (circuito integrato di applicazione specifica). Inoltre, la circuiteria ulteriore 720 includere óuq circuiteria una per limitare l'accesso in lettura o scrittura al modulo di memoria 700, ad esempio una password, protezione, biometriche o simili. La circuiteria ulteriore 720 può includere una circuiteria per indicare lo stato

del modulo di memoria 700. Ad esempio, la circuiteria ulteriore 720 può includere la funzionalità per determinare se stia venendo alimentata energia elettrica al modulo di memoria 700 e se si stia attualmente accedendo al modulo di memoria 700, e visualizzare una indicazione del suo stato. ad esempio una luce compatta, mentre alimentato ed una luce lampeggiante durante l'accesso. La circuiteria ulteriore 720 óuq includere ulteriormente dispositivi passivi, esempio capacitori di disaccoppiamento, per aiutare i requisiti di alimentazione all'interno del modulo di memoria 700.

Si osservi che sono possibili altre forme di realizzazione di operazioni di programmazione e livelli di tensione per un dispositivo ed una schiera di memoria non volatile della presente invenzione, e sarà evidente per coloro che sono esperti nel ramo con l'aiuto di questa descrizione.

### CONCLUSIONE

Sono stati descritti un dispositivo a memoria non volatile ad architettura NAND ed una elaborazione di programmazione che riducono gli effetti dell'accoppiamento di tensione da una linea di parole ad una linea di parole impiegando insiemi

dí più linee di parole adiacenti ed applicando la stessa tensione a ciascuna in operazioni di accesso di schiera. Ciò consente a ciascuna linea dell'insieme o coppia di schermare l'accoppiamento capacitivo di tensione da una linea di parole rispetto ad una linea di parole. In particolare, le forme di realizzazione di programmazione di stringhe di memoria ad architettura NAND della presente invenzione programmano le varie celle di stringhe di celle di memoria non volatili impiegando elaborazioni programmazione di massa virtuale, di auto-boost locale, di auto-boost di lato sorgente, di autoboost di lato connettore modificato modificato che impiega due o più celle di memoria "a blocchi" su entrambi il lato di sorgenti ed il lato di linea di collettore di una cella di memoria selezionata per programmazione. Le celle accoppiate di memoria blocchi selezionate adiacenti alla cella di memoria selezionata si schermano l'una con l'altra durante l'operazione di programmazione per ridurre rumore della linea di parole e impedire a queste di attivarsi e di far fuoriuscire cariche dal canale munito di boost della cella di memoria selezionata,

diminuendo la fuoriuscita di canale ed aumentando il rendimento di boost durante una programmazione.

Sebbene in questa sede siano state illustrate e descritte specifiche forme di realizzazione, verrà compreso da coloro di capacità ordinaria nel ramo che una qualsiasi disposizione che viene calcolata per ottenere lo stesso fine può essere sostituita per le specifiche forme di realizzazione mostrate. Molti adattamenti dell'invenzione saranno evidenti a coloro di capacità ordinaria nel ramo. Di conseguenza, questa domanda intende coprire tutti gli adattamenti o varianti dell'invenzione. E' manifestamente inteso che questa invenzione è limitata soltanto dalle seguenti rivendicazioni e dai relativi equivalenti.

Alberto Tonon (leer. Albo n. 83 666)

### RIVENDICAZIONI

1. Metodo per schermare l'accoppiamento capacitivo di linee di parole in dispositivi di memoria, comprendente:

applicare una prima tensione ad una prima linea di parole in una schiera di memoria di un dispositivo di memoria;

applicare la prima tensione ad una o più seconde linee di parole per schermare in modo capacitivo la prima linea di parole, in cui l'una o più seconde linee di parole sono direttamente adiacenti alla prima linea di parole; e

applicare almeno una terza tensione ad almeno una o più terze linee di parole, in cui l'almeno una o più seconde linee di parole sono adiacenti alla prima linea di parole adiacente direttamente ed una o più seconde linee di parole nella schiera di memoria.

- 2. Metodo della rivendicazione 1, in cui il dispositivo di memoria è un dispositivo di memoria non volatile.

- 3. Metodo della rivendicazione 2, in cui il dispositivo di memoria non volatile è uno tra un dispositivo di memoria ad architettura NOR, un dispositivo di memoria ad architettura NAND, ed un

dispositivo di memoria di massa virtuale.

- 4. Metodo della rivendicazione 2, in cui la terza tensione è una tensione di programmazione elevata oppure una tensione di cancellazione elevata.

- 5. Metodo per programmare una stringa di memoria non volatile ad architettura NAND, comprendente:

applicare una tensione programmazione ad una linea di parole selezionate accoppiata ad una cella di memoria non volatile della stringa di memoria ad architettura NAND che è stata selezionata per programmazione;

applicare una tensione intermedia ad almeno un insieme di due o più linee di parole, in cui l'insieme di due o più linee di parole sono direttamente adiacenti l'una con l'altra; e

applicare una tensione di passaggio ad una o più linee di parole rimanenti tra l'insieme dell'una o più linee di parole adiacenti di lato sorgente e la linea di sorgenti.

- 6. Metodo della rivendicazione 5, in cui la tensione intermedia è la tensione di interdizione.

- 7. Metodo della rivendicazione 5, in cui la tensione intermedia è una tra Vcc, Vss e massa.

- 8. Metodo della rivendicazione 5, in cui l'almeno un insieme di due o più linee di parole sono

fisicamente adiacenti alla linea di parole selezionata.

- 9. Metodo della rivendicazione 5, in cui l'almeno un insieme di due o più linee di parole sono tra la linea di parola selezionata e la linea di sorgenti.

10. Metodo della rivendicazione 5, in cui l'almeno un insieme di due o più linee di parole sono tra la linea di parole selezionata ed una linea di bit oppure la linea di collettore.

- 11. Metodo della rivendicazione 5. in cui il. metodo di programmazione è uno tra un'operazione di programmazione di auto-boost locale, una operazione di programmazione di auto-boost locale modificato, una operazione di programmazione di auto-boost di lato collettore, un'operazione di programmazione di auto-boost di lato collettore modificata, un'operazione di programmazione di auto-boost di lato sorgente, una operazione di programmazione di auto-boost di lato sorgente modificata, ed una operazione di programmazione di massa virtuale.

- 12. Metodo della rivendicazione 5, in cui la cella di memoria non volatile è una tra una cella di memoria a porta flottante, una cella di livello multiplo (MLC) ed una cella di memoria non conduttiva a nodo flottante.

- 13. Metodo della rivendicazione 5, in cui il metodo è parte di un'operazione di cancellazione.

- 14. Metodo di programmazione di auto-boost di lato connettore in un dispositivo di memoria ad architettura NAND, comprendente:

applicare una tensione di programmazione ad una linea di parole selezionata accoppiata ad una cella di memoria non volatile della stringa di memoria ad architettura NAND che è stata selezionata per programmazione;

applicare una tensione di interdizione ad un primo insieme di due o più linee di parole non selezionate in cui il primo insieme di due o più linee di parole sono direttamente adiacenti l'una con l'altra, ed in cui il primo insieme di due o più linee di parole non selezionate sono tra la linea di parola selezionata e la linea di sorgenti: e

applicare una tensione di passaggio ad una o più rimanenti linee di parole della stringa di memoria.

15. Metodo della rivendicazione 14, comprendente inoltre:

applicare una seconda tensione di passaggio ad un secondo insieme di una o più linee di parole non selezionate, in cui il secondo insieme di una o più linee di parole non selezionate si trovano tra il primo insieme di due o più linee di parole non selezionate e la linea di parole selezionata, ed in cui la seconda tensione di passaggio si trova tra la tensione di passaggio ed un potenziale di massa.

16. Metodo della rivendicazione 14, in cui la

- tensione di interdizione è una tra Vss e massa. 17. Metodo della rivendicazione 14, in cui la

- cella di memoria non volatile è una tra una cella di memoria a porta flottante, una cella a livello multiplo (MLC) ed una cella di memoria non conduttiva a nodo flottante.

- 18. Metodo della rivendicazione 14, in cui il primo insieme di due o più linee di parole non selezionate sono fisicamente adiacenti alla linea di parole selezionata.

- 19. Metodo di programmazione ad auto-boost locale in un dispositivo di memoria ad architettura NAND, comprendente:

applicare una tensione di programmazione ad una linea di parole selezionata accoppiata ad una cella di memorie non volatile della stringa di memoria ad architettura NAND che viene selezionata per programmazione;

applicare una tensione di interdizione ad un primo insieme di due o più linee di parole non selezionate, in cui il primo insieme di due o più linee di parole non selezionate sono direttamente adiacente l'uno con l'altro, ed in cui il primo insieme di due o più linee di parole non selezionate si trovano tra la linea di parole selezionata ed una linea di sorgenti;

applicare una tensione di interdizione ad un secondo insieme di due o più linee di parole non selezionate, in cui il secondo insieme di due o più linee di parole sono direttamente adiacenti l'uno con l'altro ed in cui il secondo insieme di due o più linee di parole non selezionate si trovano tra la linea di parole selezionata e una linea di bit; e

applicare una tensione di passaggio ad una o più linee di parole non selezionate rimanenti della stringa di memoria.

20. Metodo della rivendicazione 19, comprendente inoltre:

applicare una seconda tensione di passaggio ad un terzo insieme di una o più linee di parole non selezionate, in cui il terzo insieme di una o più linee di parole non selezionate si trovano tra gli insiemi primo e secondo di due linee di parole non selezionate e la linea di parole selezionata, ed in cui la seconda tensione di passaggio si trova tra la tensione di passaggio ed il potenziale di massa.

- 21. Metodo della rivendicazione 19, in cui la tensione di interdizione si trova tra Vcc e massa.

- 22. Metodo della rivendicazione 19, in cui la cella di memoria non volatile è una tra una cella di memoria a porta flottante, una cella a livello multiplo (MLC), ed una cella di memoria non conduttiva a nodo flottante.

- 23. Metodo della rivendicazione 19, in cui gli insiemi primo e secondo di due o più linee di parole non selezionate sono fisicamente adiacenti alla linea di parole selezionata.

- 24. Dispositivo di memoria non volatile ad architettura NAND, comprendente:

una schiera di memoria non volatile di architettura NAND avente una molteplicità di blocchi di memoria; e

un circuito di controllo, in cui il circuito di controllo è atto a programmare celle di memoria in un blocco di memoria selezionato della schiera di memoria non volatile,

applicando una tensione di programmazione ad

una linea di parole selezionata accoppiata ad una cella di memoria non volatile di una stringa di memoria ad architettura NAND che viene selezionata per programmazione;

applicare una tensione di interdizione ad almeno un insieme di due o più linee di parole, in cui l'insieme di due o più linee di parole sono direttamente adiacenti l'uno con l'altro; e

applicare una prima tensione di passaggio ad una o più linee di parole rimanenti tra gli insiemi di una o più linee di parole adiacenti di lato sorgente e la linea di sorgenti.

- 25. Dispositivo di memoria non volatile ad architettura NAND della rivendicazione 4, in cui il circuito di controllo è atto ad applicare seconda tensione di passaggio ad un secondo insieme di una o più linee di parole non selezionate, in cui il secondo insieme di una o più linee di parole non selezionate si trova tra l'almeno un insieme di una o più linee di parole non selezionate e la linea di parole selezionata, ed in cui la seconda tensione di passaggio si trova tra la prima tensione di passaggio ed il potenziale di massa.

- 16. Dispositivo di memoria non volatile ad architettura NAND della rivendicazione 25, in cui

la seconda tensione di passaggio è una tra la tensione di passaggio di lettura (Vpass\_read) e la tensione di selezione di lettura (Vselect read).

- 27. Dispositivo dí memoria non volatile ad architettura NAND della rivendicazione 24, in cui il circuito di controllo è atto a programmare celle di memoria mediante una tra un'operazione programmazione di auto-boost di lato collettore, una operazione di programmazione di auto-boost a modificata, lato collettore un'operazione programmazione di auto-boost locale, un'operazione modificata di programmazione di auto-boost locale, una operazione di programmazione di auto-boost di lato sorgente, una operazione di programmazione modificata di auto-boost di lato sorgente, ed una operazione di programmazione di massa virtuale.

- 28. Dispositivo di memoria non volatile ad architettura NAND della rivendicazione 24, in cui le celle di memoria sono una tra celle di memoria a porta flottante, celle a livello multiplo (MLC) e celle di memoria non conduttive a nodo flottante.

#### 29. Sistema comprendente:

un host accoppiato ad un dispositivo di memoria non volatile, in cui il dispositivo di memoria non volatile comprende:

una schiera di memoria non volatile ad architettura NAND avente una molteplicità di blocchi;

in cui il sistema è atto a programmare celle di memoria in un blocco selezionato della schiera di memoria non volatile,

applicare una tensione di programmazione ad una linea di parole scelta accoppiata ad una cella di memoria non volatile di una stringa di memoria ad architettura NAND della schiera che viene selezionata per programmazione;

applicare una tensione di interdizione ad almeno un primo insieme di due o più linee di parole, in cui l'insieme di due o più linee di parole sono direttamente adiacenti l'uno con l'altro; e

applicare una prima tensione di passaggio ad una o più linee di parole rimanenti tra l'insieme di una o più linee di parole adiacenti di lato sorgente e la linea di sorgenti.

- 30. Sistema della rivendicazione 29, in cui l'host è uno tra un elaboratore ed una unità di controllo di memoria.

- 31. Sistema della rivendicazione 29, in cui il sistema è atto ad applicare una seconda tensione di

passaggio ad un secondo insieme di una o più linee parole non selezionate, in cui il secondo insieme di una 0 più linee di parole selezionate si trova tra l'almeno un primo insieme di una o più linee di parole non selezionate e la seconda linea di parole, ed in cui la seconda tensione di passaggio si trova tra la prima tensione di passaggio ed il potenziale di massa.

- 32. Sistema della rivendicazione 29, in cui il sistema è atto a programmare celle di memoria mediante una tra una operazione di programmazione di auto-boost di lato collettore, una operazione di programmazione di auto-boost di lato collettore modificata, una operazione di programmazione di auto-boost locale, una operazione di programmazione di auto-boost locale modificata, una operazione di programmazione di auto-boost di lato sorgente, una operazione di programmazione di auto-boost di lato sorgente modificata, ed una operazione di programmazione di massa virtuale.

- 33. Sistema della rivendicazione 29, in cui le celle di memoria sono una tra celle di memoria a porta flottante, celle a livello multiplo (MLC), e celle di memoria non conduttive a nodo flottante.

- 34. Modulo di memoria comprendente:

una molteplicità di contatti; e

due o più dispositivi di memoria, ciascuna avendo linee di accesso accoppiate selettivamente alla molteplicità di contatti;

in cui almeno uno dei dispositivi di memoria comprende:

una schiera di memoria non volatile ad architettura NAND avente una molteplicità di blocchi di memoria, e

in cui il modulo di memoria è atto a programmare celle di memoria in un blocco selezionato della schiera di memoria non volatile,

applicando una tensione di programmazione ad una linea di parole selezionata accoppiata ad una cella di memoria di una stringa di memoria ad architettura NAND che viene selezionata per programmazione in una schiera di memoria non volatile ad architettura NAND del dispositivo di memoria,

applicando una tensione di interdizione ad almeno un insieme di due o più linee di parole, in cui l'insieme di due o più linee di parole sono adiacenti direttamente l'una con l'altra, e

applicando una prima tensione di passaggio ad una o più linee di parole rimanenti tra l'insieme

di una o più linee di parole adiacenti di lato sorgente e la linea di sorgenti.

35. Modulo di memoria della rivendicazione 34, comprendente inoltre una unità di controllo di memoria accoppiata all'uno o più dispositivi di memoria per controllare l'operazione di ciascun dispositivo di memoria in risposta al sistema host.

36. Modulo di memoria, comprendente:

un alloggiamento avente una molteplicità di contatti; e

uno o più dispositivo di memoria racchiusi nell'alloggiamento ed accoppiati selettivamente alla molteplicità di contatti;

in cui il modulo di memoria atto programmare celle di memoria in un blocco selezionato di almeno uno dei dispositivi memoria,