(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5232018号

(P5232018)

(45) 発行日 平成25年7月10日(2013.7.10)

(24) 登録日 平成25年3月29日(2013.3.29)

(51) Int.Cl.

G06F 12/16 (2006.01)

F 1

G06F 12/16 320F

請求項の数 4 (全 14 頁)

(21) 出願番号 特願2008-555429 (P2008-555429)

(86) (22) 出願日 平成19年1月18日 (2007.1.18)

(65) 公表番号 特表2009-527820 (P2009-527820A)

(43) 公表日 平成21年7月30日 (2009.7.30)

(86) 國際出願番号 PCT/US2007/060659

(87) 國際公開番号 WO2007/103590

(87) 國際公開日 平成19年9月13日 (2007.9.13)

審査請求日 平成21年12月22日 (2009.12.22)

(31) 優先権主張番号 11/359,329

(32) 優先日 平成18年2月21日 (2006.2.21)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100142907

弁理士 本田 淳

(72) 発明者 モイヤー、ウィリアム シー。

アメリカ合衆国 78620 テキサス州

ドリッピング スプリングス メドー<sup>10</sup>

リッジ ドライブ 1111

審査官 野田 佳邦

最終頁に続く

(54) 【発明の名称】エラー処理方法およびエラー処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1記憶領域に関連する第1エラー訂正状態指標の状態を判定することであって、前記第1記憶領域には第1アクセス要求が行われることと；

前記第1エラー訂正状態指標が第1状態であるとの判定に応答して、前記第1アクセス要求に対するエラー処理を実行しないことと

を含むエラー処理方法であって、

前記エラー処理は、エラー検出とエラー訂正のうち少なくともエラー検出を含み、

前記第1アクセス要求が部分書き要求である場合、

前記第1エラー訂正状態指標が第1状態であるとの判定に応答して、前記第1アクセス要求に対するエラー処理を実行せずに、前記部分書き要求を全体書き要求に昇格させることと；

前記第1エラー訂正状態指標が第1状態でないとの判定に応答して、前記第1アクセス要求に対するエラー処理を実行し、前記部分書き要求を前記全体書き要求に昇格させないことを含むことを特徴とする、エラー処理方法。

## 【請求項 2】

前記エラー処理方法は更に、前記全体書き要求に対するエラー訂正情報を算出することを含む、請求項1記載のエラー処理方法。

## 【請求項 3】

前記全体書き要求に基づく全体書き動作は、前記第1記憶領域に関連するエラー訂正デー<sup>20</sup>

タ単位の幅全体に亘って行なわれる、請求項1記載のエラー処理方法。

**【請求項 4】**

データ領域とエラー訂正領域を含む記憶領域を備えるメモリと；

前記記憶領域に関連する状態指標と；

前記メモリに接続されるエラー処理モジュールであって、前記エラー処理モジュールは前記記憶領域に関連するエラー処理を行なうことと；

アクセス制御モジュールと

を備えるエラー処理装置であって、

前記アクセス制御モジュールは、前記状態指標に接続される第1入力と、前記エラー処理モジュールに接続される出力とを有し、

10

前記記憶領域に対して部分書き込み要求が行われた場合、前記アクセス制御モジュールは、

前記状態指標が所定状態であるとの判定に応答して、前記記憶領域に対するエラー処理を前記エラー処理モジュールに実行させないようにし、前記部分書き込み要求を全体書き込み要求に昇格させ、

前記状態指標が前記所定状態でないとの判定に応答して、前記記憶領域に対するエラー処理を前記エラー処理モジュールに実行させ、前記部分書き込み要求を全体書き込み要求に昇格させ、

前記エラー処理は、エラー検出とエラー訂正のうち少なくともエラー検出を含むことを特徴とする、エラー処理装置。

**【発明の詳細な説明】**

20

**【技術分野】**

**【0001】**

本開示はエラー制御手法に関し、特にメモリ用のエラー制御手法に関する。

**【背景技術】**

**【0002】**

R A M、フラッシュメモリ、およびハードディスクドライブのような記憶装置は、記憶エラーを含むことがある。これらのエラーは、記憶装置の物理的原因または他の要因に起因する場合がある。メモリエラーは、記憶装置から読み取られる誤ったデータをもたらすことがある、頻繁なエラーまたは繰り返されるエラーは、貧弱な装置動作をもたらすことがある。

30

**【0003】**

記憶装置エラーの影響を低減するために、装置はエラー訂正技術を利用できる。たとえば記憶装置は、記憶装置の記憶領域に対するエラー訂正符号（E C C）データを格納できる。エラー訂正符号データは、装置がエラーを検出可能にするパリティまたは他のデータを含む。更にエラー訂正符号データは、装置が、検出したエラーを訂正可能にするエラー訂正データを含むことができる。

**【0004】**

メモリエラー訂正技術は、メモリの信頼度を向上できるが、装置電力や応答時間のような装置資源も消費する。資源消費は、可搬型装置や他の低電力装置のような幾つかの用途では望ましくない場合がある。

40

**【0005】**

幾つかの装置は、メモリ信頼度を向上させるために、リセットイベント後、メモリが所定のデータシーケンスで満たされる手法を利用する。リセットイベントはリセット、電源投入、または他のイベントである。エラー訂正符号データは、所定シーケンスに基づきメモリに対して算出される。

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0006】**

しかし、この手法は、リセットイベント後の望ましくない遅延や、リセットイベント後の望ましくない電力消費をもたらすことがある。電力消費は、特に可搬型装置や、頻繁に

50

リセットイベントする装置には望ましくないことがある。

【0007】

従って、望ましくない量の装置資源を消費せずにエラー訂正できる装置が望ましい。

【課題を解決するための手段】

【0008】

上記課題を解決するエラー訂正方法とエラー訂正装置が開示される。本装置は、状態指標の状態に依存して、記憶領域に対するエラー処理を無効にするメモリ制御モジュールを備える。状態指標は、記憶領域に対する有効なエラー訂正およびエラー検出情報が利用可能ではない場合（リセットまたは電源投入イベント後）、エラー処理が無効になるように設定できる。更に、メモリ制御モジュールは、エラー処理が無効な場合、部分的な書き要求である部分書き動作を、全体的な書き要求である全体書き動作に昇格できる。その結果、有効なエラー検出とエラー訂正データが記憶領域に対して算出されることを保証する。有効なエラー検出とエラー訂正情報が利用可能になるまでエラー処理を無効にすることによって、不要または無効なエラー処理動作の数が低減される。よって、装置資源が節約される。

10

【0009】

エラー訂正のための装置と方法が開示される。その方法の1つは、第1記憶領域に関連する第1エラー訂正状態指標の状態を判定することと、および第1エラー訂正状態指標が第1状態であるとの判定に応答して、第1記憶領域へのアクセス要求に対するエラー訂正、エラー検出、または任意のその組合せのうちの1つを無効にすることとを含む。

20

【0010】

特定態様では、本方法は、エラー訂正状態指標が第2状態であるとの判定に応答して、第1記憶領域へのアクセス要求に対するエラー検出またはエラー訂正のうちの少なくとも1つを無効にすることとを含む。

【0011】

別の特定態様では、アクセス要求は部分書き動作であり、本方法は、部分書き動作を全体書き動作に昇格することを更に含む。更に別の特定態様では、本方法は、第1全体書き動作に対するエラー訂正情報を算出することを含む。別の特定態様では、本方法は、第1部分書き動作を第1全体書き動作に昇格後、第1エラー訂正状態指標を第2状態に変更することを含む。

30

【0012】

特定態様では、第1アクセス要求は部分書き動作であり、本方法は、エラー訂正状態指標が第2状態であるとの判定に応答して、第1記憶領域に対するエラー訂正またはエラー検出を行なうことと、第1記憶領域の一部にデータを書込むことによって第1部分書き動作を行なうこととを含む。

【0013】

別の特定態様では、本方法は、リセット指示（リセット指標、reset indication）を受信することと、リセット指示の受信に応答してエラー訂正状態指標を第1状態にすることとを含む。更に別の特定態様では、第1記憶領域は第1装置に組込まれ、リセット指示は、第1装置が低電力モードからアクティブモードに移行するのに応答して受信される。

40

【0014】

特定態様では、本方法は、第2記憶領域に関連する第2アクセス要求を受信することと、第2記憶領域に関連する第2エラー訂正状態指標の状態を判定することと、第2エラー訂正状態指標が第1状態であるとの判定に応答して、第2記憶領域へのアクセス要求に対するエラー訂正、エラー検出、または任意のそれらの組合せを無効にすることとを含む。

【0015】

別の特定態様では、第1全体書き動作は、第1記憶領域に関連するエラー訂正データ単位の幅全体に亘って行なわれる。

開示された装置は、第1記憶領域を有するメモリを備える。第1記憶領域は、データ領域とエラー訂正領域を備える。本装置は、第1記憶領域に関連する第1状態指標と、メモ

50

リに接続されるエラー訂正モジュールとを更に備える。エラー訂正を行なうエラー訂正モジュールは、第1記憶領域に関連する。本装置はアクセス制御モジュールを更に備える。アクセス制御モジュールは、第1状態指標に接続される第1入力と、エラー訂正モジュールに接続される出力とを有する。アクセス制御モジュールは、第1状態指標が第1状態になるのに応答して、第1記憶領域に対するエラー訂正、エラー検出、または任意のそれらの組合せのうちの1つを無効にする。

#### 【0016】

特定態様では、第1状態指標が第1状態になるのに応答して、アクセス制御モジュールは、第1記憶領域に関連する第1部分書込動作を全体書込動作に昇格させる。

別の特定態様では、アクセス制御モジュールは、リセット信号を受信する第2入力を更に備える。アクセス制御モジュールは、第1状態指標を、リセット信号の受信に応答して第1状態にする。

#### 【0017】

更に別の特定態様では、エラー訂正モジュールは、全体書込動作に関連するエラー訂正データを算出する。

特定態様では、第1状態指標は、第1記憶領域に関連する状態フラグビットである。

#### 【0018】

別の開示された方法は、第1記憶領域に関連する第1エラー訂正状態指標の状態を判定することと、エラー訂正状態指標が第1状態であるとの判定に応答して、第1記憶領域に関連する第1部分書込動作を第1全体書込動作に昇格させることとを含む。

#### 【0019】

特定態様では、本方法は、第1部分書込動作の処理中に、エラー検出またはエラー訂正のうちの少なくとも1つを無効にすることを含む。

別の特定態様では、本方法は、リセット指示を受信することと、リセット指示の受信に応答して、エラー訂正状態指標を第1状態にすることとを含む。

#### 【0020】

更に別の特定態様では、本方法は、第1全体書込動作に対するエラー訂正情報を算出することを含む。

特定態様では、本方法は、第1部分書込動作を第1全体書込動作に昇格後に、第1エラー訂正状態指標を第2状態に変更することを含む。

#### 【0021】

本開示の多数の特徴と利点は、添付の図面に参照を付すことによって一層よく理解可能であり、当業者に明白となる。

異なる図面中の同一の参照符号の使用は、同様または同一の要素を示す。

#### 【発明を実施するための最良の形態】

#### 【0022】

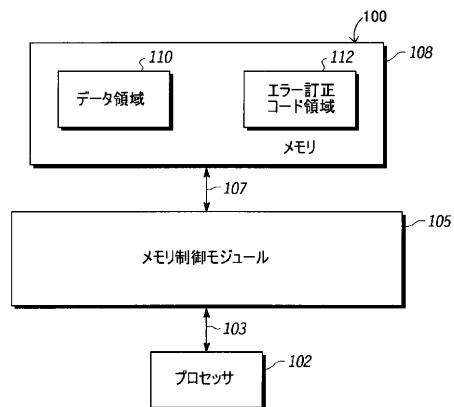

図1は、処理装置100を示す。処理装置100はプロセッサ102、メモリ制御モジュール105、およびメモリ108を備える。プロセッサ102は、第1インタフェース103を介してメモリ制御モジュール105に接続される。揮発性のメモリ108は、第2インタフェース107を介してメモリ制御モジュール105に接続される。メモリ108は、データ領域110とエラー訂正符号領域（エラー訂正コード領域、ECC領域）1112を備える。処理装置100は、ASIC、システムオンチップ（SOC）、集積回路、または他の装置ができる。更に、処理装置100は、モバイルまたは可搬型装置、自動車の装置、または他の適切な装置のような様々な用途で使用できる。メモリ108は、RAMメモリ（DRAMまたはSRAMまたは他のRAMメモリを含む）または他の種類の揮発性メモリができる。

#### 【0023】

動作中にプロセッサ102は、読み要求と書き要求のようなメモリアクセス要求を、メモリ制御モジュール105に送信する。メモリ制御モジュール105は、メモリアクセス要求に関連する記憶領域に対してエラー処理が有効で適切なアクションを行なうか否か判

10

20

30

40

50

定する。エラー処理が有効な場合、メモリ制御モジュール105は、読み取り要求に対するエラー検出とエラー訂正のような適切なエラー処理や、書き込み要求に対するパリティデータとシンクロームデータの生成を行なう。エラー処理が無効な場合、メモリ制御モジュール105はこれらの機能を行なわない。そのような処理が有効な場合に限ってエラー処理を行なうことによって、処理装置100は、不必要的エラー処理を低減できる。よって電力、時間、または他の装置資源を節約する。

#### 【0024】

たとえば処理装置100がリセットされたか、または電源が入れられた後では、メモリ108のデータ領域110におけるデータは正確ではない。従って、エラー訂正符号領域112に格納されたパリティデータやシンクロームデータのように、メモリ108に関連する任意のエラー訂正符号データは、典型的にはランダムなデータであり、従って恐らく無効である。従って、メモリ108上のエラー訂正または検出動作は、有効なデータがメモリ108に書き込まれるまでは、恐らく誤った結果を返すであろう。メモリ制御モジュール105は、有効なデータがメモリ108に書き込まれるまで、エラー訂正またはエラー検出のうちの少なくとも1つを無効にすることによって、不要または無効なエラー処理動作の数を低減できる。

#### 【0025】

図示の実施形態では、メモリ制御モジュール105は、読み取り要求と書き込み要求を含む様々な種類のメモリアクセス要求に応じて、エラー処理を行なうことができる。たとえば読み取り要求の場合、メモリ制御モジュール105は、エラー検出を行ない、そして必要ならば、エラー処理が読み取り要求に関連するメモリ108の部分が有効な場合にはエラー訂正を行なう。

#### 【0026】

書き込み要求は、全体書き込み要求または部分書き込み要求であることが可能である。全体書き込み要求は、エラー訂正符号データ単位の幅全体にデータを書込む全体的な書き込み要求である。エラー訂正符号データ単位の幅は、単一のエラー訂正符号シンクローム値に関連するメモリ量である。一方、部分書き込み要求は、エラー訂正符号データ単位の幅全体よりも少なくデータを書込む部分的な書き込み要求である。たとえばメモリ制御モジュール105とメモリ108は、64ビットのエラー訂正符号データ単位に基づきエラー検出とエラー訂正を行なうように構成可能である。この例では、全体書き込み動作は64ビットの書き込み動作である。一方、部分書き込み動作は32ビット(ワード)、16ビット(ハーフワード)、または8ビット(バイト)の書き込み動作である。

#### 【0027】

全体書き込み要求の場合、メモリ制御モジュール105は、書き込み動作に関連するデータに対して、パリティデータのようなエラー検出情報と、シンクロームデータのようなエラー訂正情報を算出する。書き込みモジュール206は、エラー検出情報とエラー訂正情報を、書き込み要求に関連するデータと同様にメモリ108に書き込む。

#### 【0028】

部分書き込み要求の場合、書き込みモジュール206またはプロセッサ102は、エラー処理が有効な場合に部分書き込み動作用のエラー訂正符号データを算出するために、部分書き込み要求を「読み取り修正書き込み動作」に変形できる。読み取り修正書き込み動作は、エラー処理が有効な場合、部分書き込み要求に関連するメモリアドレスにおけるデータ単位全体を読み取り、メモリ制御モジュール105はエラー検出とエラー訂正をデータ単位全体に亘って行なう。たとえば64ビットのエラー訂正符号データ単位用に構成されたメモリ108の場合、64ビットの記憶領域のすべてが、エラー訂正符号データを算出するために使用される。その後、データ単位全体の適切な部分が、部分書き込み動作に関連するデータに置換され、データ単位全体(置換されたデータを有する)がメモリ108に書き込まれる。更新されたエラー検出とエラー訂正值は、新しい部分的な書き込みデータ値を含む更新されたデータ単位全体に基づき算出される。

#### 【0029】

10

20

30

40

50

代わりに、エラー処理が無効な場合、メモリ制御モジュール105は、部分書き込み要求を全体書き込み要求に昇格できる。書き込み要求の昇格は、ここで使用されるように、部分書き込み要求を全体書き込み要求に変形するものとして定義される。一実施形態では、8ビット、16ビット、または32ビットの部分的なデータ書き込み要求は、64ビットの全体的なデータ書き込み要求に昇格される。これは、様々な方法で行なわれることができる。たとえばメモリ制御モジュール105は、所定のデータシーケンスを、部分書き込み要求に関連するデータに添付または挿入でき、その結果、変形されたデータは、エラー訂正符号データ単位全体と同じ大きさである。その後、変形されたデータは、メモリ108に書き込まれることができる。更新されたエラー検出とエラー訂正值は、変形された書き込みデータ値を含む更新されたデータ単位全体に基づき算出される。

10

### 【0030】

部分書き込み要求を全体書き込み要求に昇格させることによって、データに対する有効なエラー訂正および検出値は、将来のエラー処理動作にメモリ108に格納される。従って、部分書き込み要求を全体書き込み要求に昇格し、全体書き込み要求に対するエラー訂正および検出情報を算出および格納後、書き込み要求に関連する記憶領域に対するエラー訂正が有効になることができる。そしてエラー処理は、記憶領域に関連する後続のメモリアクセス要求に対して行なわれることができる。

### 【0031】

更に、エラー処理動作を選択的に有効にすることと共に、部分書き込み要求を全体書き込み要求に昇格させることによって、メモリ制御モジュール105は、システム資源を節約できる。たとえば説明したように、装置リセットまたは電源投入イベント後ではメモリ108内のデータは正確ではなく、メモリ108上のエラー処理は、読み取りアクセスと書き込みアクセスに対して恐らくエラーをもたらすであろう。特に部分書き込み動作の場合に該当する。部分書き込み動作は、読み取り機能と書き込み機能の両方を含むからである。更に、全体書き込みまたは昇格された部分書き込み動作のいずれかが記憶領域上で行なわれる場合、各記憶領域は既知のデータで満たされる。よってメモリ108は、リセットまたは電源投入イベントの直後では、既知のデータシーケンスで予め満たされたり、または初期化されたりする必要は無く、よって時間と電力を節約できる。

20

### 【0032】

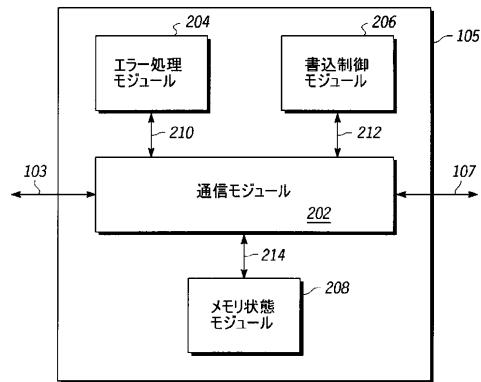

図2は、図1のメモリ制御モジュール105の一実施形態を示す。図示のように、メモリ制御モジュール105は通信モジュール202、エラー処理モジュール204、書き込み制御モジュール206、およびメモリ状態モジュール208を備える。通信モジュール202は、第1インターフェース103と第2インターフェース107に接続される。通信モジュール202は、第3インターフェース210を介してエラー処理モジュール204に接続され、第4インターフェース212を介して書き込み制御モジュール206に接続され、そして第5インターフェース214を介してメモリ状態モジュール208に接続される。通信モジュール202、エラー処理モジュール204、書き込み制御モジュール206、およびメモリ状態モジュール208はハードウェア、ソフトウェア、ファームウェア、または任意のそれらの組合せとしてインストール可能である。例示のために、通信モジュール202、エラー処理モジュール204、および書き込み制御モジュール206のうちの幾つかまたはすべては、それらの対応する機能を行なうロジックとしてインストール可能である。

30

### 【0033】

動作中に、メモリ制御モジュール105は、エラー処理とメモリアクセス要求処理を行なう。エラー処理を行なうために通信モジュール202は、プロセッサ102から第1インターフェース103を介してメモリアクセス要求を受信する。メモリアクセス要求は、典型的には関連する記憶領域のメモリアドレスを含む。メモリアクセス要求は書き込み要求の場合、メモリ108に書き込まれるペイロードデータを含む。通信モジュール202は、メモリ状態モジュール208にメモリアドレスを提供する。メモリ状態モジュール208は、メモリアドレスに関連する特定の記憶領域に対してエラー処理が有効であるか否か判定する。

40

50

**【0034】**

メモリアクセス要求に関する特定の記憶領域に対してエラー処理が無効な場合、メモリ状態モジュール208は、エラー処理がメモリアクセス要求に対して行なわれるべきではないことを、通信モジュール202を介してエラー処理モジュール204に通信する。その後、通信モジュール202はメモリアクセス要求を、第2インターフェース107を介してメモリ108(図1)に通信する。

**【0035】**

エラー処理が、メモリアクセス要求に関する特定の記憶領域に対して有効な場合、メモリ状態モジュール208は、エラー処理が進められるべきであることをエラー処理モジュール204に通信する。よって、エラー処理モジュール204は、データ領域110からのデータと、エラー訂正符号領域112からのエラー訂正符号情報とを利用して、適切なエラー処理を行なう。たとえば読み取り要求の場合、エラー処理モジュール204は、メモリ108から読み取られたデータにおけるエラーを検出し、必要な場合にエラー訂正し、エラー訂正された読み取りデータを生成する。書き要求の場合、エラー処理モジュール204は、書き要求に関するペイロードデータに基づき、パリティデータとシンドロームデータのようなエラー訂正符号データを算出する。

10

**【0036】**

エラー処理が完了後、通信モジュール202は、メモリアクセス要求を完了すべく、プロセッサ102(図1)とメモリ108に通信する。たとえば読み取り要求の場合、通信モジュール202は、プロセッサ102にエラー訂正された読み取りデータを通信する。書き要求の場合、通信モジュール202は、エラー処理モジュール204によって算出されたペイロードデータとエラー訂正符号データを、メモリ108に通信する。

20

**【0037】**

エラー処理を選択的に有効にすることによって、メモリ制御モジュール105は、不要または望ましくないエラー処理量を低減できる。たとえばエラー処理は、メモリアクセス要求に対する応答時間を改善するためにプロセッサ102によって無効にされる場合がある。よって、高速メモリ応答を必要とする重大な装置動作にとって望ましい。別の実施形態では、エラー処理は、電力消費を低減するために無効にされる場合がある。たとえばメモリ制御モジュール105を組込んだ装置は、低電力状態を含むことがあり、頻繁なエラー制御動作は、付随する電力消費のためには望ましくないからである。

30

**【0038】**

更に、一実施形態では、メモリ制御モジュール105はエラー処理を制御できる。その結果、エラー処理はメモリ108の或る部分に対して有効になり、他の部分に対して無効になる。この制御は、様々な場面で役立つことがある。たとえばメモリ制御モジュール105は、エラー処理が、重大な装置データを含むメモリ108の一部分に対して有効になるが、それほど重大でないデータを格納するメモリ108の他の部分に対しては無効になるように構成できる。別の実施形態では、エラー訂正是、頻繁なエラーを被ったか、または好ましくない動作条件下で動作するメモリ108の部分に対して有効である一方で、エラー処理は、より少数の動作エラーを被るメモリ108の他の部分に対しては無効であることが可能である。別の実施形態では、エラー訂正是、初期化されたメモリ108の部分に対して有効であることが可能である。なぜならば、電源投入イベントが生じている一方、エラー処理は、まだ初期化されていないメモリ108の他の部分に対しては無効であるからである。

40

**【0039】**

更に、メモリ状態モジュール208は、時間経過と共に、記憶領域に対するエラー処理状態を変更可能である。たとえばエラー処理は、書き要求が記憶領域に対して満たされるまで、特定の記憶領域に対して無効であることが可能であり、有効なエラー訂正符号データは、当該記憶領域に対して算出される。このようにメモリ制御モジュール105は、適切な状況に依存して、メモリ108に対するエラー処理構成を動的に変更できる。

**【0040】**

50

別の一実施形態では、メモリ状態モジュール208は、通信モジュール202を介して、プロセッサ102からリセット指示（リセット指標）を受信できる。リセット指示に応答して、メモリ状態モジュール208は、記憶領域のすべてまたは一部に対するエラー処理を無効にできる。よってシステムリセット後、電源投入後、または他のリセットイベント後、無効または不必要的エラー処理量を低減できる。

#### 【0041】

メモリ制御モジュール105は、エラー処理後に更に、書き要求処理を行なう。通信モジュール202は、第1インターフェース103を介してプロセッサ102から書き要求を受信する。通信モジュール202は、書き制御モジュール206に、書き要求に関連するアドレスデータまたはペイロードデータを提供する。書き制御モジュール206は、書き要求が全体書き要求であるかまたは部分書き要求か判定する。書き要求の判定は、様々な方法で行なわれることができる。たとえば書き制御モジュール206は、メモリ108のエラー訂正符号データ単位のサイズに対して、ペイロードデータのサイズを比較することに基づき、全体書き要求か部分書き要求か判定できる。別の実施形態では、全体書き要求か部分書き要求かの判定は、メモリアクセス要求に関連するアドレスに基づくことができる。代替の実施形態は、任意の他の適切な方法で判定可能である。

10

#### 【0042】

書き要求が全体書き要求である場合、書き制御モジュール206は、全体書き要求が処理されることがあることを通信モジュール202に示す。ペイロードデータは、算出された場合にはエラー訂正符号データと共にメモリ108に書き可能である。

20

#### 【0043】

書き要求が部分書き要求である場合、書き制御モジュール206は、エラー処理が要求に関連する記憶領域に対して有効であるか否か判定するためにメモリ状態モジュール208を調べる。エラー処理が有効な場合、書き制御モジュール206は、部分書き要求を全体書き要求に昇格せずに、部分書き要求を満足させるために読み修正書き動作を行なうことができる。部分的な書きデータ値は、「修正」動作の間、読み修正書き動作の読み動作から得られたエラーを、訂正された読みデータに吸収する。記憶領域は、読み修正書き動作の書き部分の間、修正された値で繰り返して更新される。修正されたデータ値から算出された更新されたエラー訂正符号データもまた、格納される。エラー処理が無効な場合、書き制御モジュール206は、部分書き要求を全体書き要求に昇格させる。その後、書き制御モジュール206は、エラー訂正符号データ算出用のエラー処理モジュール204に、結果として生じる全体書き要求を提供する。更に書き制御モジュール206は、メモリ108への通信用の通信モジュール202に、結果として生じる全体書き要求に関連するデータを提供できる。

30

#### 【0044】

部分書き要求を全体書き要求に選択的に昇格させることによって、書き制御モジュール206は、有効なまたは既知のデータがすべての種類の書き要求に対する特定の記憶領域に書き込まれることを保証できる。その後、メモリ状態モジュール208は、記憶領域に対するエラー訂正を有効にする。

#### 【0045】

40

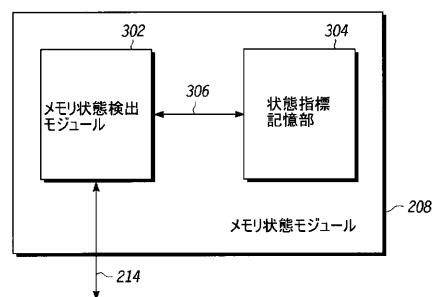

図3は、図2のメモリ状態モジュール208の一実施形態を示す。メモリ状態モジュール208は、メモリ状態検出モジュール302と状態指標記憶部304を備える。メモリ状態検出モジュール302は、第5インターフェース214に接続される。メモリ状態検出モジュール302は、インターフェース306を介して状態指標記憶部304に接続される。状態指標記憶部304は、対応する記憶領域に関連する一または複数の状態指標を含む。状態指標記憶部304は、データファイル、状態レジスタ、一連の状態フラグビット、または他の適切な状態指標であることが可能である。メモリ状態検出モジュール302と状態指標記憶部304は、ハードウェア、ソフトウェア、ファームウェア、または任意のそれらの組合せとしてインストール可能である。例示のために、メモリ状態検出モジュール302と状態指標記憶部304のうちの一方または両方は、それらの対応する機能を行

50

なうためのロジックとしてインストール可能である。

#### 【0046】

動作中に、メモリ状態検出モジュール302は、第5インターフェース214を介してメモリ状態の問合せを受信する。メモリ状態の問合せは、メモリアドレスまたはメモリアドレスに基づく指標のような問合せに関連する記憶領域の指標を含む。問合せに応答して、メモリ状態検出モジュール302は、エラー処理が記憶領域に対して有効であるか否か判定するために状態指標記憶部304にアクセスする。その後、メモリ状態検出モジュール302は、エラー処理が有効か無効かを示すべく、問合せに対する反応を返す。

#### 【0047】

更に、メモリ状態検出モジュール302は、第5インターフェース214を介してメモリ状態変更要求を受信できる。メモリ状態の問合せと同様に、メモリ状態変更要求は、記憶領域指標を含むことができる。メモリ状態変更要求に応答して、メモリ状態検出モジュール302は、一または複数の記憶領域のエラー処理状態を変更するために状態指標記憶部304にアクセスできる。たとえば状態指標記憶部304が記憶領域に関連する状態フラグビットを含む場合、メモリ状態検出モジュール302は、記憶領域に対するエラー処理を有効にするか無効にするか必要に応じて、ビットを設定またはクリアできる。

#### 【0048】

更に、メモリ状態変更要求は、複数の記憶領域に関連することが可能である。従って、メモリ状態変更要求に応答して、メモリ状態検出モジュール302は、メモリ108の領域またはメモリ装置全体に対するエラー処理を有効または無効にできる。

#### 【0049】

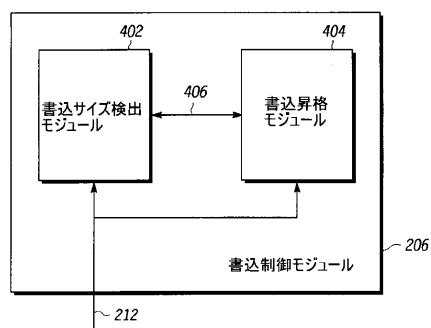

図4は、図2の書き制御モジュール206の一実施形態を示す。書き制御モジュール206は、書きサイズ検出モジュール402と書き昇格モジュール404を備える。書きサイズ検出モジュール402は、インターフェース406を介して書き昇格モジュール404に接続される。書きサイズ検出モジュール402と書き昇格モジュール404は、それぞれ第4インターフェース212に接続される。書きサイズ検出モジュール402と書き昇格モジュール404は、ハードウェア、ソフトウェア、ファームウェア、または任意のそれらの組合せとしてインストール可能である。例示のために、書きサイズ検出モジュール402と書き昇格モジュール404のうちの幾つかまたはすべては、それらの対応する機能を行なうためのロジックとしてインストール可能である。

#### 【0050】

動作中に、書きサイズ検出モジュール402は、第4インターフェース212を介して書き要求を受信する。書きサイズ検出モジュール402は、受信した書き要求が全体書き要求であるか部分書き要求か判定する。書き要求が部分書き要求である場合、書きサイズ検出モジュール402は、書き要求を全体書き動作に昇格させるように書き昇格モジュール404に指示する。これに応答して、書き昇格モジュール404は、第4インターフェース212を介して、部分書き動作に関連するペイロードデータを受信する。その後、書き昇格モジュール404は、部分書き動作を全体書き動作に昇格し、第4インターフェース212を介して、生成結果のペイロードデータを返す。

#### 【0051】

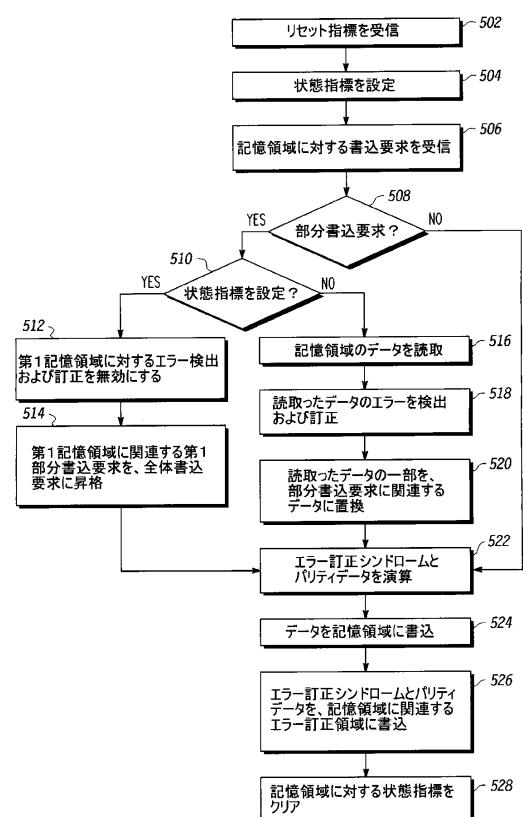

図5は、メモリ108に対する書き要求の処理方法の一実施形態のフローチャートを示す。ステップ502では、メモリ制御モジュール105またはプロセッサ102は、リセット指示(リセット指標)を受信する。リセット指示は、電源投入イベント、低電力状態からアクティブ状態への装置の移行、リセットイベント、または他の適切なイベントのような様々なイベント後に受信可能である。

#### 【0052】

ステップ504に進んで、メモリ制御モジュール105またはプロセッサ102は、複数の状態指標を設定する。これらの状態指標は、複数の記憶領域に関連し、記憶領域に対するエラー処理が無効になるべきであることを示すことができる。リセット指示の後に記憶領域に対するエラー処理を無効にすることによって、不必要または望ましくないエラー

10

20

30

40

50

処理を低減可能である。

**【0053】**

ステップ506に移動して、メモリ制御モジュール105またはプロセッサ102は、特定の記憶領域に対する書込要求を受信する。書込要求は、記憶領域に対するアドレスと、記憶領域に書込まれるデータとを含むことが可能である。

**【0054】**

判定ステップ508では、プロセッサ102またはメモリ制御モジュール105は、受信した書込要求が部分書込要求であるかまたは全体書込要求であるか判定する。要求が全体書込要求である場合、本方法はステップ522に移動し、プロセッサ102またはメモリ制御モジュール105は、書込要求に対するエラー訂正シンドロームとパリティデータを算出する。典型的には、エラー訂正シンドロームとパリティデータは、書込要求に関連するデータに基づく。その後、本方法はステップ524に進み、書込要求に関連するデータが、適切な記憶領域に書込まれる。更に、ステップ526では、算出されたエラー訂正シンドロームとパリティデータが、記憶領域に関連するエラー訂正領域に書込まれる。エラー訂正データは、書込要求データと同一の記憶装置、または異なる装置に書込可能である。その後、本方法はステップ528に進み、記憶領域に関連する状態指標がクリアされる。よって、記憶領域への後続の書込動作に対するエラー訂正が有効になる。

**【0055】**

判定ステップ508に戻って、書込要求が部分書込要求である場合、本方法は判定ステップ510に進み、プロセッサ102またはメモリ制御モジュール105は、書込要求に関連する記憶領域に対する状態指標が設定されているか否か判定する。状態指標が設定されている場合は、エラー処理が無効にされるべきであることを意味するため、本方法はステップ512に移動する。プロセッサ102またはメモリ制御モジュール105は、記憶領域に対するエラー検出とエラー訂正を無効にする。本方法はステップ514に移動し、プロセッサ102またはメモリ制御モジュール105は、部分書込要求を全体書込要求に昇格させる。部分書込要求を全体書込要求に昇格させることによって、有効なエラー処理データは、関連する記憶領域に対して算出可能であり、将来のメモリアクセス要求に対する有効なエラー処理を許容する。本方法はステップ522に進み、エラー訂正データは、部分書込要求の昇格に起因する全体書込要求に対して算出される。

**【0056】**

判定ステップ510に戻って、状態指標が設定されていないと判定した場合は、エラー処理が有効であることを意味する。よって本方法はステップ516に移動し、読み修正書込動作を開始する。書込要求に関連する記憶領域のデータは、ステップ516において読み取られる。ステップ518では、読み取ったデータにおけるエラーが検出され、必要ならば訂正される。ステップ520では、読み取ったデータの適切な部分は、部分書込要求に関連するデータに置換される。本方法はステップ522に移動し、読み修正書込動作に起因するデータに対するエラー訂正シンドロームとパリティデータを算出する。ステップ522から、本方法はステップ524に進み、先に記述した動作を行なう。

**【0057】**

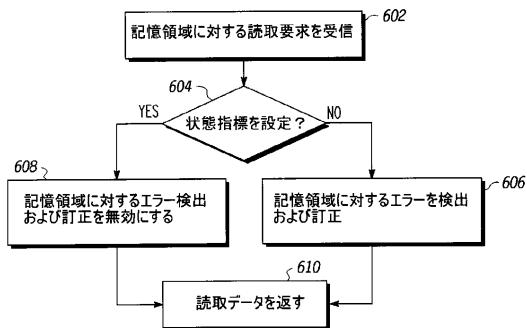

図6は、読み要求の処理方法の一実施形態のフローチャートを示す。ステップ602では、プロセッサ102またはメモリ制御モジュール105は、記憶領域に対する読み要求を受信する。読み要求は、記憶領域に関連するアドレスと、読み要求が部分読み要求であるか全体読み要求であるかの指標とを含むことが可能である。その後、記憶領域データが得られる。

**【0058】**

判定ステップ604に移動して、プロセッサ102またはメモリ制御モジュール105は、記憶領域に関連する状態指標が設定されているか否か判定する。状態指標は、記憶領域に対するエラー処理が有効であるか否か判定するために使用される。

**【0059】**

状態指標が設定されていないと判定した場合、本方法はステップ606に移動し、エラ

10

20

30

40

50

一検出とエラー訂正が行なわれる。エラー検出は、記憶領域に関連するパリティデータに基づくことが可能である。エラー訂正是、記憶領域に関連するエラーシンドロームデータを使用して行なわれることが可能である。またはエラー検出とエラー訂正是、任意の他の代替の方法で行なわれることが可能である。本方法はステップ 610 に進み、エラー訂正されたデータは、読み取り要求を発した装置に返される。

#### 【0060】

判定ステップ 604 に戻って、状態指標が記憶領域に対して設定されていないと判定した場合、本方法はステップ 608 に移動し、記憶領域に対するエラー検出とエラー訂正が無効にされる。本方法はステップ 610 に移動し、読み取ったデータは、読み取り要求を発した装置に返される。

10

#### 【0061】

当業者は、図 5 と図 6 で議論した状態指標の設定状態が、如何なる特定の格納値にも限定されないことを認識するであろう。たとえばロジック「1」または「0」を含む任意の値が、本開示の範囲を逸脱せずに設定状態を示すために使用可能である。

#### 【0062】

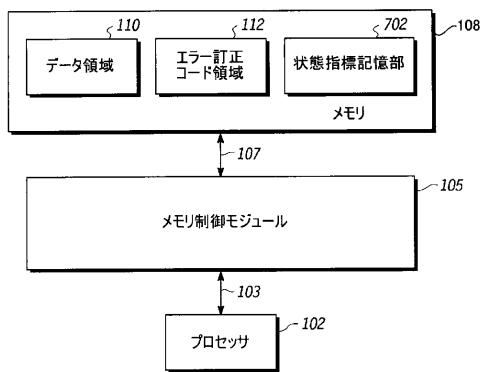

図 7 は、図 1 の処理装置 100 の他の実施形態を示す。図 7 に示すメモリ 108 は、状態指標記憶部 702 を備える。状態指標記憶部 702 は、エラー処理がデータ領域 110 における対応する記憶領域に対して有効または無効であるべきであるかを示すために複数の状態指標を備える。メモリ制御モジュール 105 は、プロセッサ 102 から受信したメモリアクセス要求に対するエラー処理を有効にすべきか無効にすべきか判定するために、状態指標記憶部 702 にアクセスできる。

20

#### 【0063】

この場合、メモリ 108 に対するエラー処理を有効または無効にするために使用される状態指標は、メモリ制御モジュール 105 にではなく、メモリ 108 自体に格納できる。

本発明の原理は、特定の装置に関して上述されるが、この記述が例示としてのみなされ、本発明の範囲に対する限定としてなされていないことが明白に理解されるべきである。

#### 【図面の簡単な説明】

#### 【0064】

【図 1】エラー訂正手法を利用する処理装置のブロック図。

30

【図 2】図 1 に示すメモリ制御モジュールのブロック図。

【図 3】図 2 に示すメモリ状態モジュールのブロック図。

【図 4】図 2 に示す書き込み制御モジュールのブロック図。

【図 5】メモリ書き込みアクセス要求の処理方法のフローチャート。

【図 6】メモリ読み取りアクセス要求の処理方法のフローチャート。

【図 7】図 1 とは別例の処理装置のブロック図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開平10-289164(JP,A)

特開平04-364552(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 16