(12)

# Österreichische Patentanmeldung

(21) Anmeldenummer: A 391/2005

(22) Anmeldetag: 08.03.2005

(43) Veröffentlicht am: 15.09.2006

(51) Int. Cl.<sup>8</sup>: H04B 1/16 (2006.01),

H04L 7/04 (2006.01),

H04B 7/26 (2006.01)

(73) Patentanmelder:

TECHNISCHE UNIVERSITÄT GRAZ

A-8010 GRAZ (AT)

(72) Erfinder:

GAPPMAIR WILFRIED DIPLO.ING. DR.

GRAZ (AT)

KOGLER WOLFGANG DIPLO.ING.

KLAGENFURT (AT)

## (54) AKQUISITIONSEINHEIT

(57) Bei einer Akquisitionseinheit für ein digitales TDMA-Modem, umfassend eine Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts (1) eines digitalen Datenstroms, welcher durch Überabtastung mit einer vorgebbaren Anzahl Samples pro Symbol aus einem Basisbandsignal generiert ist, einer Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens (2) und einer Schaltungsanordnung zum Bestimmen der Trägerfrequenz (3) eines digitalen Datenstroms, wird zur effizienteren Nutzung der Systembandbreite vor allem bei kleineren Paketlängen vorgeschlagen, dass eine kombinierte Schaltungsanordnung (4) mit einem gemeinsamen Dateneingang (30) ausgebildet ist, welche die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens (2) und die Schaltungsanordnung zum Bestimmen des optimalen Abtastzeitpunkts (1) umfasst.

**Z U S A M M E N F A S S U N G**

Bei einer Akquisitionseinheit für ein digitales TDMA-Modem, umfassend eine Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts (1) eines digitalen Datenstroms, welcher durch Überabtastung mit einer vorgebbaren Anzahl Samples pro Symbol aus einem Basisbandsignal generiert ist, einer Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens (2) und einer Schaltungsanordnung zum Bestimmen der Trägerfrequenz (3) eines digitalen Datenstroms, wird zur effizienteren Nutzung der Systembandbreite vor allem bei kleineren Paketlängen vorgeschlagen, dass eine kombinierte Schaltungsanordnung (4) mit einem gemeinsamen Dateneingang (30) ausgebildet ist, welche die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens (2) und die Schaltungsanordnung zum Bestimmen des optimalen Abtastzeitpunkts (1) umfasst.

⟨(Fig. 2)⟩

002408

28253/1h

Die Erfindung betrifft eine Akquisitionseinheit für ein digitales TDMA-Modem, umfassend eine Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts eines digitalen Datenstroms, welcher durch Überabtastung mit einer vorgebbaren Anzahl Samples pro Symbol aus einem Basisbandsignal generiert ist, einer Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens und einer Schaltungsanordnung zum Bestimmen der Trägerfrequenz eines digitalen Datenstroms.

In einem Kommunikationsnetzwerk, wo mehrere Sender aktiv sind, muss dafür gesorgt werden, dass im jeweiligen Empfänger die eintreffenden Informationen auch wieder entsprechend getrennt werden können. Eine weit verbreitete Technik ist die zyklische Partitionierung der Zeitachse, auch als TDMA (time-division multiple access) bezeichnet, wo die Sendestationen nicht kontinuierlich arbeiten, sondern periodisch Zeitschlüsse zugeteilt bekommen, in die sie ihre Daten (frames, bursts) packen können. Selbstverständlich hat jede dieser Stationen im allgemeinen Fall unterschiedliche Sende- und Ausbreitungsbedingungen, die sich im Lauf der Zeit auch ändern können. Ein brauchbarer Empfang der einzelnen Datenpakete ist nur dann gewährleistet, wenn der Demodulator die relevanten Übertragungsparameter kennt bzw. zuverlässig ermitteln und nachführen kann (Synchronisation). Zu den Größen, die in diesem Zusammenhang üblicherweise als bekannt vorausgesetzt werden dürfen, zählen das Modulationsverfahren und die Form des Basisband-Pulses. In vielen Fällen, etwa bei satellitengestützten Datenstrecken, ist letzterer meist bandbegrenzt im engeren Sinne sowie interferenzfrei, d. h. dass das erste Nyquist-Kriterium erfüllt ist.

Wenn in weiterer Folge von Übertragungsparametern die Rede ist, dann sind die Trägerfrequenz, die Trägerphase, die Symbolrate sowie der optimale Abtastzeitpunkt gemeint. Bei vielen Nachrichtensystemen darf man davon ausgehen, dass die Nominalwerte von Trägerfrequenz und Symbolrate empfängerseitig bekannt sind; bei TDMA ist das auch für den Beginn eines Übertragungsrahmens der Fall (Präambel, Synchronisationswort), was den Synchronisationsprozess gerade in diesem Fall ganz wesentlich unterstützt.

In der ersten Synchronisationsphase, der sogenannten Akquisition, muss eine Parameterkombination gefunden werden, welche in der Nähe des globalen Optimums liegt. Der Prozess muss gerade in TDMA-Systemen sehr effizient vonstatten gehen, was durch das im Voraus bekannte Synchronisationswort gewährleistet wird. Mit den derart ermittelten

Werten für die Übertragungsparameter lassen sich die nachfolgenden Verarbeitungsstufen initialisieren, etwa das Nachregeln (Tracking) für Trägerphase und Abtastzeitpunkt. Letzteres ist insofern notwendig, da sich im Allgemeinen die Übertragungsbedingungen ständig ändern, z. B. durch die Drift lokaler Oszillatoren, Doppler-Effekte, Änderung der Ausbreitungsbedingungen etc..

Heute übliche TDMA-Modems arbeiten mit einer separaten Anordnung zur Bestimmung des optimalen Abtastzeitpunktes. Dieser Einheit nachgeschaltet findet in einer weiteren Einheit die Bestimmung von Rahmenbeginn, Trägerfrequenz und Trägerphase statt. Für die separate Bestimmung des optimalen Abtastzeitpunktes muss der gesendeten Nachricht eine Präambel vorangestellt werden, gefolgt von einem Synchronisationswort zur Bestimmung der Trägerfrequenz, des Rahmenbeginns und der Trägerphase.

Nachteilig an derartigen Lösungen ist, dass gerade bei sehr kurzen Datenpaketen der notwendige Overhead zur Synchronisation des Empfängers sehr groß ist im Vergleich zur Länge der Nachricht. Vor allem bei Übertragungsstrecken mit begrenzter Systembandbreite führt dies zu einer ineffizienten Nutzung der Systembandbreite besonders bei kleineren Paketlängen.

Aufgabe der Erfindung ist es, ein TDMA- Modem der eingangs erwähnten Art anzugeben, welches die bekannten Nachteile vermeidet und das eine effizientere Nutzung der Systembandbreite vor allem bei kleineren Paketlängen ermöglicht.

Erfindungsgemäß wird dies dadurch erreicht, dass eine kombinierte Schaltungsanordnung mit einem gemeinsamen Dateneingang ausgebildet ist, welche die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens und die Schaltungsanordnung zum Bestimmen des optimalen Abtastzeitpunkts umfasst.

Dadurch wird die vorhandene Systembandbreite speziell bei kleineren Paketlängen wesentlich besser genutzt, da die Präambel ersatzlos weggelassen werden kann. Wenn statt der Präambel das Synchronisationswort und ein Teil der Nutzdaten zur Ermittlung des Abtastzeitpunktes verwendet wird, lässt sich mit der erfindungsgemäßen Schaltungsanordnung die dadurch vergrößerte Lücke (guard time) zwischen den Datenpaketen im Ausmaß der Länge der Präambel verkleinern.

In diesem Zusammenhang kann in Weiterführung der Erfindung vorgesehen sein, dass die kombinierte Schaltungsanordnung mit einem gemeinsamen Dateneingang die Schaltungsanordnung zum Bestimmen der Trägerfrequenz eines digitalen Datenstroms umfasst. Dadurch kann auch die Frequenzschätzung in der kombinierten

Schaltungsanordnung vorgenommen werden, wodurch der Aufbau noch weiter vereinfacht wird.

In Weiterführung der Erfindung kann vorgesehen sein, dass die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens und die Schaltungsanordnung zum Bestimmen der Trägerfrequenz eines digitalen Datenstroms der Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts vorgeschaltet sind. Dadurch arbeitet die Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts bereits mit den frequenzkorrigierten Abtastwerten.

In diesem Zusammenhang kann vorgesehen sein, dass der kombinierten Schaltungsanordnung ein signalangepasstes Filter vorgeschaltet ist. Dadurch gelangt nur das gewünschte Empfangssignal an den Eingang der kombinierten Schaltungsanordnung.

In Weiterführung der Erfindung kann vorgesehen sein, dass die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens ein erstes Schieberegister umfasst, dessen Registerlänge dem Produkt aus der Anzahl der Samples pro Symbol und der Länge eines Synchronisationswortes in Symbolen eines vorgebbaren Modulationsverfahrens, entspricht. Dadurch können hintereinander die Abtastwerte im Abstand der Überabtastung aus dem Register ausgelesen werden und mit dem gespeicherten Synchronisationswort verglichen werden bis eine optimale Übereinstimmung gefunden ist.

In diesem Zusammenhang kann in Weiterführung der Erfindung vorgesehen sein, dass dem Ausgang der Schaltungsanordnung zum Bestimmen der Trägerfrequenz eines digitalen Datenstroms eine Frequenzkorrekturteinheit nachgeschaltet ist. Dadurch werden die Sampels für die weitere Verarbeitung frequenzkorrigiert.

Gemäß einer weiteren Ausführungsform der Erfindung kann vorgesehen sein, dass dem Ausgang der Frequenzkorrekturteinheit wenigstens eine Einheit zur Bildung des Absolutbetrags der aufaddierten und frequenzkorrigierten Produkte aus dem konjugiert-komplexen Synchronisationswort und den eingehenden Sampels nachgeschaltet ist. Dadurch steht der Absolutbetrag des komplexen Empfangssignal zur Weiterverarbeitung zur Verfügung.

In Weiterführung der Erfindung kann vorgesehen sein, dass die Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts wenigstens ein zweites Schieberegister umfasst, wobei das zweite Schieberegister vorzugsweise eine ungerade Anzahl Schieberegisterzellen aufweist, wobei insbesondere bei einer ungeraden Anzahl Samples pro Symbol die Anzahl der Schieberegisterzellen der Anzahl Samples pro

Symbol entspricht, bzw. dass bei einer geraden Anzahl Samples pro Symbol die Anzahl der Schieberegisterzellen der Anzahl Samples pro Symbol minus eins entspricht. Dadurch kann die Weiterverarbeitung entsprechend der Auflösung durch die Überabtastung vonstatten gehen, wobei die nachfolgende Verarbeitung schrittweise für jeden Neueintrag in das Schieberegister durchgeführt werden kann.

In diesem Zusammenhang kann in Weiterführung der Erfindung vorgesehen sein, dass das zweite Schieberegister einen ersten Zellenblock, eine mittlere Zelle und einen zweiten Zellenblock aufweist, wobei der erste Zellenblock und der zweite Zellenblock die gleiche Anzahl Zellen umfassen, und die mittlere Zelle an einen Eingang einer Entscheidungslogik angeschlossen ist, oder dass das zweite Schieberegister einen ersten Zellenblock, zwei mittlere Zellen und einen zweiten Zellenblock aufweist, wobei der erste Zellenblock und der zweite Zellenblock die gleiche Anzahl Zellen umfassen, und die beiden mittleren Zellen an einen Eingang einer Mittelwerteinheit angeschlossen sind, deren Ausgang an den Eingang der Entscheidungslogik angeschlossen ist. Dadurch stehen die Einträge des ersten Zellenblocks und die Einträge des zweiten Zellenblocks zur weiteren Verarbeitung, etwa zu einem Vergleich, zur Verfügung, wobei die mittlere Zelle bzw. der Mittelwert der beiden mittleren Zellen als Entscheidungskriterium fungieren kann.

Gemäß einer weiteren Ausführungsform der Erfindung kann vorgesehen sein, dass der erste Zellenblock und der zweite Zellenblock an Eingängen jeweils wenigstens einer Summiereinheit angeschlossen sind, und dass jeweils wenigstens ein Ausgang der Summiereinheiten an einer Subtraktionseinheit angeschlossen ist. Dadurch kann der Gesamtbetrag des ersten Zellenblocks mit dem Gesamtbetrag des zweiten Zellenblocks verglichen werden.

Gemäß wieder einer anderen Ausführungsform der Erfindung kann vorgesehen sein, dass wenigstens ein Ausgang der Subtraktionseinheit sowohl mittels wenigstens eines Verzögerungsglieds als auch direkt an Eingängen der Entscheidungslogik angeschlossen ist. Dadurch können die Werte der Subtraktionseinheit für zwei aneinanderfolgende Verarbeitungsschritte miteinander verglichen werden.

Eine Variante der Erfindung kann darin bestehen, dass wenigstens ein Ausgang der Entscheidungslogik mit wenigstens einem Eingang einer Schaltungsanordnung zum Bestimmen einer Phasenlage des digitale Datenstroms in Relation zu Referenzdaten, vorzugsweise dem Synchronisationswort, und/oder wenigstens einem Eingang einer Schaltungsanordnung zum Bestimmen des Beginns eines Datenrahmens verbunden ist, wobei

vorzugsweise die Schaltungsanordnung zum Bestimmen der Phasenlage des digitalen Datenstroms in Relation zu Referenzdaten und/oder die Schaltungsanordnung zum Bestimmen des Beginns eines Datenrahmens Teil der kombinierten Schaltungsanordnung mit gemeinsamen Dateneingang sind. Dadurch kann auf einfacherem Weg die Phasenlage des digitalen Datenstroms in Relation zu Referenzdaten und/oder der Beginn eines Datenrahmens festgestellt werden.

In weiterer Ausgestaltung der Erfindung kann vorgesehen sein, dass die Ausgänge der kombinierten Schaltungsanordnung mit wenigstens einem komplexen Phasenschieber zur Korrektur des digitalen Datenstroms mit wenigstens einem Korrekturfaktor, vorzugsweise einem Frequenzkorrekturfaktor und/oder einer Trackingeinheit, leitend verbunden sind. Dadurch kann der Datenstrom vor der Ausgabe an eine weitere Verarbeitungsstufe mit den ermittelten Korrekturwerten korrigiert werden.

Die Erfindung betrifft weiters ein Verfahren zur Synchronisation eines digitalen TDMA-Modems auf einen entsprechenden aus Samples bestehenden digitalen Datenstrom, welcher aus einem mit einer vorgebbaren Anzahl Samples pro Symbol überabgetasteten Basisbandsignal generiert ist, wobei aus dem digitalen Datenstrom eine Trägerfrequenz des digitalen Datenstroms, der Beginn eines Übertragungsrahmens, ein optimaler Abtastzeitpunkt sowie eine Phasenlage des digitalen Datenstroms in Relation zu Referenzdaten ermittelt werden, und der digitale Datenstrom vor der Ausgabe mit wenigstens einem Korrekturwert korrigiert wird.

Aufgabe der Erfindung ist es, ein Verfahren zur Synchronisation eines digitalen TDMA-Modems der eingangs erwähnten Art anzugeben, das eine effizientere Nutzung der Systembandbreite vor allem bei kleineren Paketlängen ermöglicht.

Erfindungsgemäß wird dies dadurch erreicht, dass der Beginn des Übertragungsrahmens und der optimale Abtastzeitpunkt in einer kombinierten Schaltungsanordnung mit einem gemeinsamen Dateneingang ermittelt werden.

Dadurch lässt sich die Lücke (guard time) zwischen den aufeinanderfolgenden Datenpaketen im Ausmaß der Präambel reduzieren bzw. diese selbst einsparen, wodurch die vorhandene Systembandbreite vor allem bei kleineren Paketlängen wesentlich besser genutzt wird.

In diesem Zusammenhang kann in Weiterführung der Erfindung vorgesehen sein, dass die Trägerfrequenz des digitalen Datenstroms in der kombinierten

Schaltungsanordnung mit einem gemeinsamen Dateneingang ermittelt wird. Dadurch wird das Verfahren noch weiter vereinfacht.

In Weiterbildung der Erfindung kann vorgesehen sein, dass vor Ermittlung des Beginns eines Übertragungsrahmens, der Trägerfrequenz des digitalen Datenstroms und des optimalem Abtastzeitpunkts der eingehende digitale Datenstrom in einem signalangepassten Filter gefiltert wird. Dadurch kann sichergestellt werden, dass lediglich die gewollten Empfangsdaten weiterverarbeitet werden.

Eine andere mögliche Ausführungsform kann darin bestehen, dass die Trägerfrequenz des digitalen Datenstroms in an sich bekannter Weise detektiert wird, ein Frequenzkorrekturfaktor gebildet und der digitale Datenstrom frequenzkorrigiert wird. Dadurch steht für die Weiterverarbeitung ein frequenzkorrigierter Datenstrom zur Verfügung.

Gemäß einer weiteren Ausbildung der Erfindung kann vorgesehen sein, dass aus den frequenzkorrigierten Samples des digitalen Datenstroms die Betragssumme gebildet wird. Dadurch ist es möglich, nach dem Betragssmaximum als Indikator für den optimalen Abtastzeitpunkt zu suchen.

Eine Variante der Erfindung kann darin bestehen, dass die Betragssummen sukzessive in ein zweites Schieberegister mit ungeradzahliger Registerlänge geladen werden, wobei die Registerlänge vorzugsweise der Anzahl Samples pro Symbol oder der Anzahl Samples pro Symbol minus eins entspricht. Dadurch können die weiteren Verarbeitungsschritte entsprechend für jeden Schritt der Überabtastung durchgeführt werden.

In weiterer Ausgestaltung der Erfindung kann vorgesehen sein, dass das zweite Schieberegister erste Registereinträge, einen mittleren Registereintrag und zweite Registereinträge aufweist, wobei die Anzahl der ersten Registereinträge gleich der Anzahl der zweiten Registereinträge ist und der mittlere Registereintrag an einen Eingang einer Entscheidungslogik geliefert wird. Dadurch steht der Inhalt zweier gleich großer Blöcke zur Weiterverarbeitung bereit.

In Weiterbildung der Erfindung kann vorgesehen sein, dass die ersten Registereinträge sowie die zweiten Registereinträge, jeweils aufsummiert werden, und die derart gebildete erste und zweite Registereintragssumme voneinander subtrahiert werden. Dadurch besteht die Möglichkeit, ein Korrelationsmaximum im Verlauf des überabgetasteten Signals zu detektieren.

Eine weitere mögliche Ausführungsform kann darin bestehen, dass jeweils zwei aufeinanderfolgende Ergebnisse der Subtraktion der Registereintragssummen als

Eingänge an die Entscheidungslogik geliefert werden, und die Entscheidungslogik an einem Ausgang einen Synchronisationspuls als Kennzeichen des optimalen Abtastzeitpunkts liefert, wenn die zwei aufeinanderfolgenden Ergebnisse der Subtraktion verschiedene Vorzeichen aufweisen, und der mittlere Registereintrag oberhalb einer vorgebbaren Korrelationsschwelle liegt. Dadurch wird ein Maximum detektiert und einer nachfolgenden Verarbeitungsstufe der optimale Abtastzeitpunkt mitgeteilt.

Gemäß einer weiteren Ausbildung der Erfindung kann vorgesehen sein, dass mit dem Synchronisationspuls ein Trägerphasenwert und/oder ein Rahmenbeginnsignal in an sich bekannter Weise in der kombinierten Schaltungsanordnung mit gemeinsamen Dateneingang ermittelt werden. Mittels bekannter Trägerphase und/oder dem Beginn des Übertragungsrahmens besteht die Möglichkeit, den Datenstrom in einer nachfolgenden Verarbeitungsstufe korrekt nachzuführen (Tracking).

In diesem Zusammenhang kann in Weiterführung der Erfindung vorgesehen sein, dass der digitale Datenstrom mit dem Frequenzkorrekturfaktor und/oder dem Trägerphasenwert und/oder dem Rahmenbeginnsignal, vorzugsweise in wenigstens einer Trackingeinheit und/oder wenigstens einem komplexen Phasenschieber, korrigiert wird und/oder an weitere Verarbeitungsstufen weitergegeben wird. Dadurch steht ein korrigiertes sowie rahmensynchronisiertes Ausgangssignal zur Weiterverarbeitung zur Verfügung.

Die Erfindung betrifft weiters ein Computerprogrammprodukt, das direkt in den internen Speicher eines Computers geladen werden kann und Softwarecodeabschnitte umfasst, mit denen die Schritte des Verfahrens gemäß einem der Ansprüche 14 bis 24 ausgeführt werden, wenn das Computerprogrammprodukt auf einem Computer läuft. Dadurch kann das erfindungsgemäße Verfahren auf flexible Weise in eine Anwendung integriert werden.

Die Erfindung betrifft weiters einen Datenträger mit einem Computerprogrammprodukt nach Anspruch 25. Dadurch ist ein derartiges Computerprogrammprodukt transportabel und aufbewahrbar.

Die Erfindung betrifft weiters ein digitales TDMA-Modem mit einer Akquisitionseinheit nach einem der Ansprüche 1 bis 13. Dadurch kann die vorhandene Systembandbreite vor allem bei kleineren Paketlängen wesentlich besser genutzt werden, da auf die Präambel bzw. die verlängerte „guard time“ verzichtet werden kann.

Die Erfindung betrifft weiters ein digitales TDMA-Modem, wobei ein Verfahren nach einem der Ansprüche 14 bis 24, insbesondere mittels eines

Computerprogrammprodukts nach Anspruch 25, implementiert ist. Dadurch ist ein derartiges Modem flexibel einsetzbar und nachrüstbar.

Die Erfindung wird unter Bezugnahme auf die beigeschlossenen Zeichnungen, in welchen besonders bevorzugte Ausführungsformen dargestellt sind, näher beschrieben. Dabei zeigt:

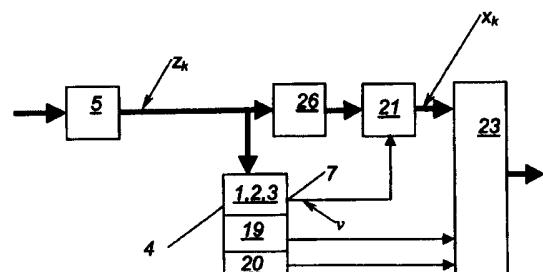

Fig. 1 ein Blockschaltbild einer herkömmlichen Akquisitionseinheit eines digitalen TDMA-Modems;

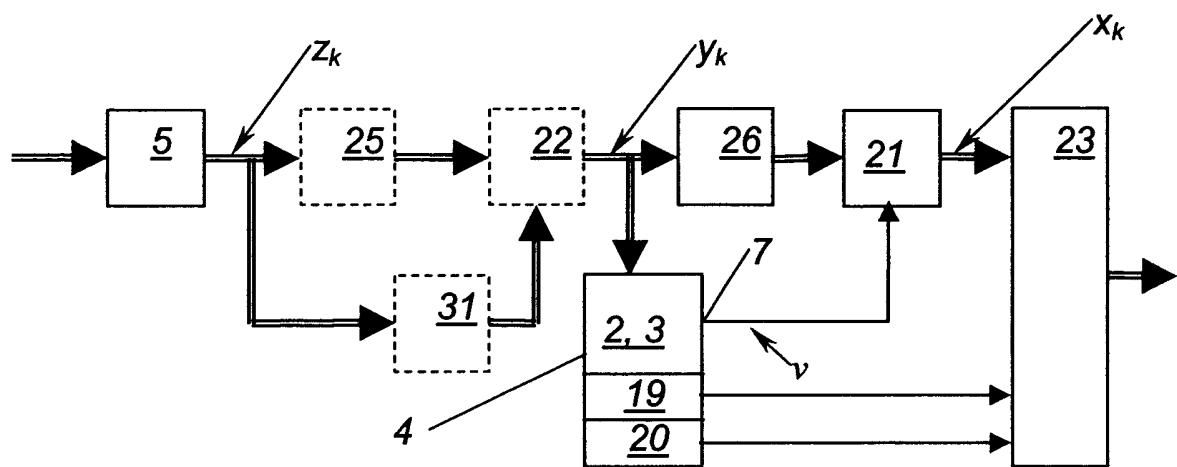

Fig. 2 ein Blockschaltbild einer erfindungsgemäßen Akquisitionseinheit für ein digitales TDMA-Modem mit einer kombinierten Schaltungsanordnung;

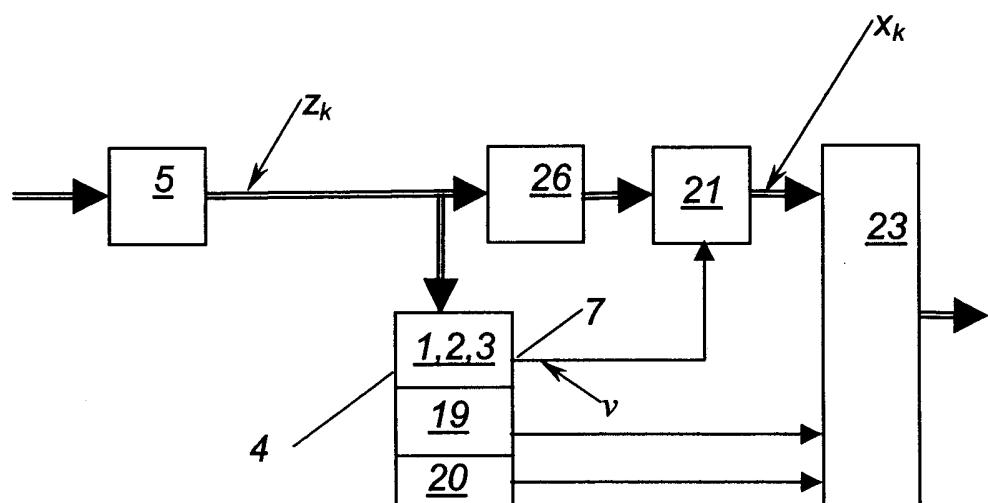

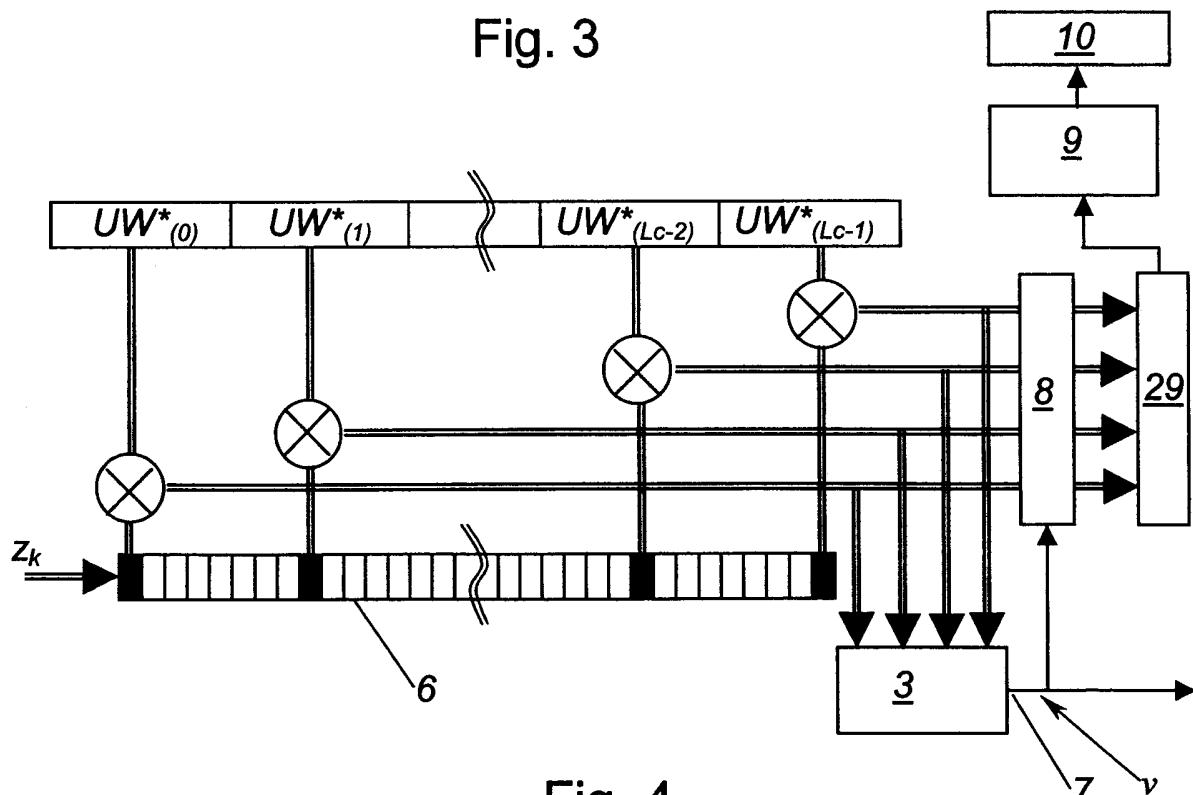

Fig. 3 eine weitere Ausführung einer Akquisitionseinheit gemäß Fig. 2;

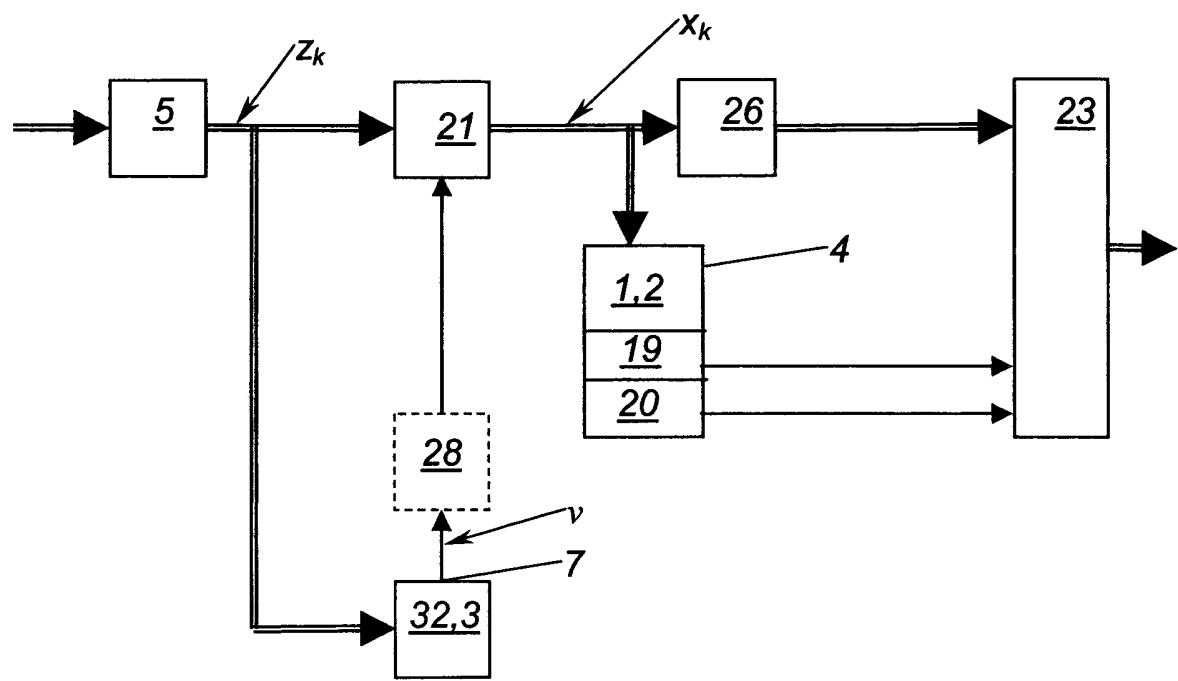

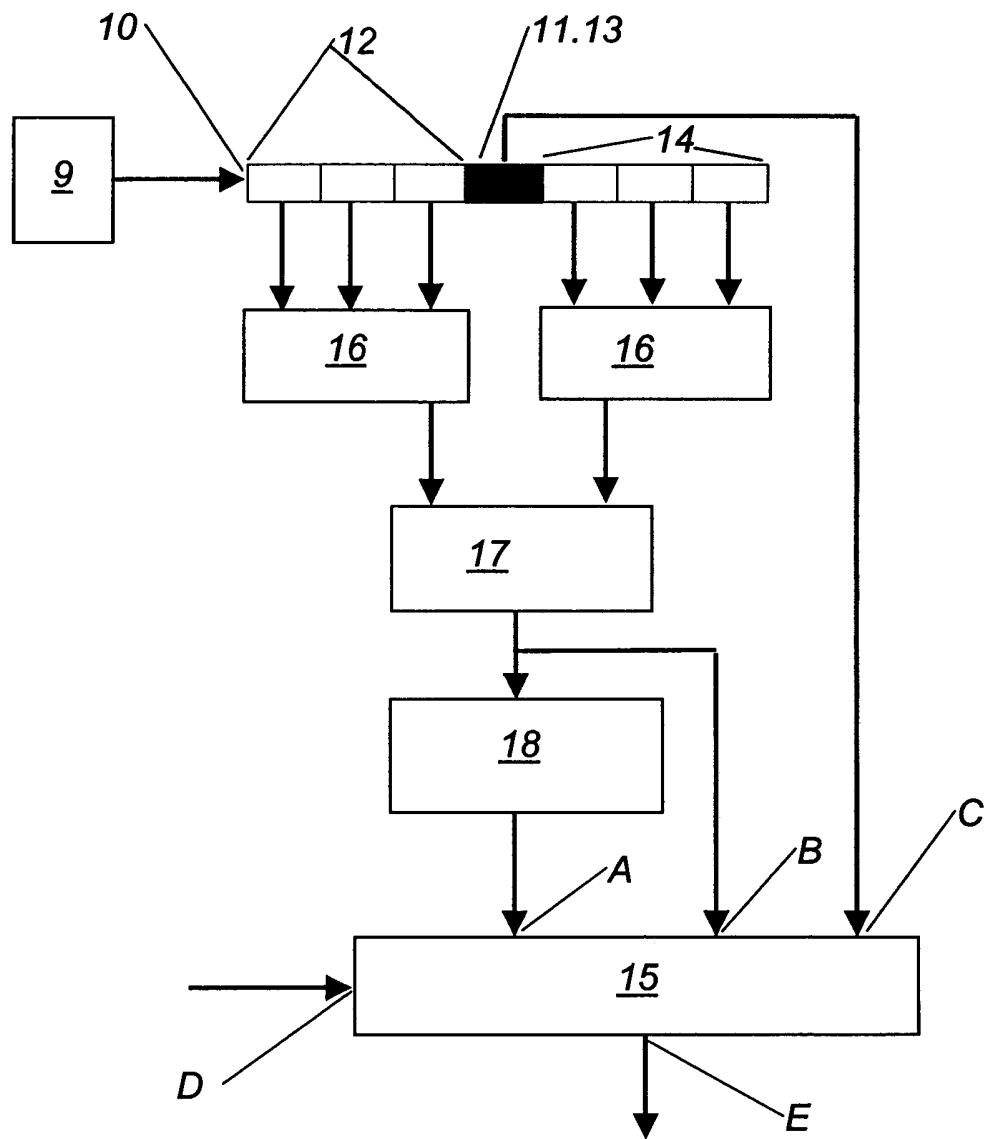

Fig. 4 ein Blockschaltbild der Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens (Korrelationseinheit) und der Schaltungsanordnung zum Bestimmen der Trägerfrequenz; und

Fig. 5 ein Blockschaltbild der Schaltungsanordnung zum Bestimmen des optimalen Abtastzeitpunkts.

Die Fig. 2 und 3 zeigen eine Akquisitionseinheit für ein digitales TDMA-Modem, umfassend eine Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts 1 eines digitalen Datenstroms, welcher durch Überabtastung mit einer vorgebbaren Anzahl Samples pro Symbol des Datenstroms aus einem Basisbandsignal generiert ist, einer Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens 2 und einer Schaltungsanordnung zum Bestimmen der Trägerfrequenz 3 eines digitalen Datenstroms, wobei eine kombinierte Schaltungsanordnung 4 mit einem gemeinsamen Dateneingang 30 ausgebildet ist, welche die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens 2 und die Schaltungsanordnung zum Bestimmen des optimalen Abtastzeitpunkts 1 umfasst.

Fig. 1 zeigt ein Blockschaltbild einer herkömmlichen Akquisitionseinheit für ein digitales TDMA-Modem, wie es zur Zeit üblich ist (in diesem Zusammenhang bezeichnen Doppellinien komplexe Signale, während einfache Linien reelle Signale charakterisieren). Gespeist wird der Prozess von den Abtastwerten (Samples)  $Z_k$  am Ausgang eines signalangepassten (matched) Filters 5. Die vorwärtsgekoppelte Einheit zur Ermittlung des Abtastzeitpunktes 31 arbeitet ohne Datenunterstützung (non-data-aided) mit einer Beobachtungslänge  $L_t$  (in Symbolen des gewählten Modulationsverfahrens). Das Verzögerungsglied 25 verzögert den eingehenden Datenstrom entsprechend um  $L_t$  Symbole.

Um den optimalen Abtastzeitpunkt zu berechnen, ist eine moderate Überabtastung  $N_{OS} = 4$  ausreichend. Wenn diese groß genug ist, etwa  $N_{OS} = 6$ , nimmt man das Sample, welches dem errechneten Abtastwert am nächsten liegt, ansonsten ist wie in Fig. 1 dargestellt ein Interpolator 22 vorgesehen. In der Folge dienen die Abtastwerte  $Y_k$  der Ermittlung des Frequenzfehlers zwischen Sender und Empfänger. Die jeweiligen Verzögerungsglieder 25, 26 dienen allein dazu, die betreffenden Symbolströme zu verzögern, und zwar jeweils um die für die Berechnungen benötigten Beobachtungslängen  $L_t$  bzw.  $L_c$ , sodass parallel die betreffende Schaltungsanordnung beladen und der jeweilige Wert berechnet werden kann.

Falls für die bekannte Bestimmung des optimalen Abtastzeitpunkts keine Präambel, sondern das Synchronisationswort und ein Teil der anschließenden Nutzdaten verwendet wird, dann ist für eine derartige Anordnung eine entsprechend große Lücke (guard time) zwischen den Datenpaketen notwendig, wodurch ebenfalls die vorhandene Bandbreite nur ungenügend genutzt wird (analog zur Verwendung einer Präambel).

Um die Bestimmung des Frequenzfehlers effizient durchführen zu können, werden in der Praxis meist datengestützte (data-aided) Algorithmen verwendet, d. h. den eigentlichen Nutzdaten stellt man eine Sequenz definierter Symbole (Synchronisationswort) mit einer Länge  $L_c$  voran, welche über einen Korrelationsprozess zur vorwärtsgekoppelten Ermittlung der Trägerfrequenz verwendet wird. In diesem Zusammenhang markiert der Betrag des frequenzkorrigierten Korrelationsmaximums den Beginn eines Datenrahmens; der zugeordnete Wert  $v$  für den Frequenzversatz zwischen Sender und Empfänger speist den komplexen Phasenschieber 21, um den in  $Y_k$  enthaltenen Frequenzfehler zu berichtigen. Schlussendlich erhält man einen Wert für die Trägerphase, indem das Argument der komplexen Zahl, welche mit dem Korrelationsmaximum korrespondiert, auswertet. Frequenzkorrigierte Samples  $X_k$ , detekter Rahmenbeginn sowie geschätzte Trägerphase werden an die Tracking-Einheit 23 weitergegeben.

Eine erfindungsgemäße Akquisitionseinheit weist keine separate Einheit 31 zur Ermittlung eines optimalen Abtastzeitpunkts eines digitalen überabgetasteten Datenstroms auf, welche nach einem signalangepassten Filter 5 im Signalweg angeordnet ist und zur Bestimmung des optimalen Abtastzeitpunkts eine Präambel im Signal benötigt. Erfindungsgemäß erfolgt die Bestimmung des optimalen Abtastzeitpunkts in einer kombinierten Schaltungsanordnung 4 mit einem gemeinsamen Dateneingang, wobei in der kombinierten Schaltungsanordnung 4 auch die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens 2 (Korrelationseinheit) und vorzugsweise die

Schaltungsanordnung zum Bestimmen der Trägerfrequenz 3 eines digitalen Datenstroms zusammengefasst sind.

Es kann vorgesehen sein, dass die gemeinsame Akquisition vorwärtsgekoppelte (feedforward) Bestimmungsmethoden für Trägerfrequenz und -phase benutzt, wie sie aus der technischen Literatur bekannt sind, und dass diese Philosophie durch die Bestimmung des optimalen Abtastzeitpunktes auch nicht beeinträchtigt wird (keine Einschwing- oder Stabilitätsprobleme, wie das bei rückwärtsgekoppelten Lösungen der Fall ist). Weiters kann vorgesehen sein, dass die Erfindung auf alle linearen Modulationsverfahren und alle Basisband-Pulse, sofern sie bandbreitenbegrenzt sind und dem ersten Nyquist-Kriterium gehorchen, anwendbar ist. Weiters kann vorgesehen sein, dass die Erfindung transparent gegenüber der gewählten Länge  $Lc$  arbeitet.

Wenn nun die separate Einheit 31 zur Bestimmung des Abtastzeitpunkts und der Interpolator 22 (falls implementiert) ersatzlos gestrichen werden, um einer erweiterten Form einer kombinierten Schaltungsanordnung 4 Platz zu machen, in die auch die Bestimmung des optimalen Abtastzeitpunkts integriert ist, dann ergibt sich dadurch ein bedeutender Vorteil: Die Lücke (guard time) zwischen zwei Datenpaketen, die ohne Verwendung einer Präambel mindestens  $Lt + Lc$  Symbole (oder einem proportionalen Faktor dazu) lang ist, kann um wenigstens  $Lt$  Symbole (oder einem proportionalen Faktor dazu) verkürzt werden. Damit ist eine Steigerung der Effizienz des TDMA-Systems sichergestellt, die umso bedeutender ausfällt, je kleiner die Paketlängen sind. Der Effekt ist derselbe, wenn dem Synchronisationswort  $Lt$  Symbole oder ein Teil davon als Präambel vorangestellt sind, die durch die erfindungsgemäße Schaltungsanordnung ersatzlos gestrichen werden können.

Eine derartige Lösung macht eine entsprechend feine Auflösung der Zeitachse durch Überabtastung notwendig, was gegenüber der herkömmlichen Lösung eine höhere Systemleistung in der Akquisitionseinheit nach sich zieht, um eine entsprechend schnelle Kalkulation von Korrelation und Frequenzversatz sicherzustellen. Dies stellt nach dem heutigen Stand der Technik und der Verfügbarkeit schneller Hardwarekomponenten, wie etwa FPGAs, keinen Nachteil dar.

Im Grunde kann die erfindungsgemäße kombinierte Schaltungsanordnung für jede Art der Abtastung angewendet werden. Bei höherer Überabtastung des Basisbandsignals, vorzugsweise ab  $N_{os} > 4$ , kann in weiterer Folge der ermittelte optimale Abtastzeitpunkt durch den nächstgelegenen Abtastwert charakterisiert werden. Bei größerer Auflösung der Zeitachse, z. B. mit  $N_{os} = 4$ , können interpolative Methoden vorgesehen sein, um das

Korrelationsmaximum zu errechnen, welches mit dem optimalen Abtastzeitpunkt korrespondiert.

Bevorzugt kann vorgesehen sein, dass, wie in Fig. 2 dargestellt, der kombinierten Schaltungsanordnung 4 ein signalangepasstes Filter 5 vorgeschalten ist. Weiters kann vorgesehen sein, dass in der kombinierten Schaltungsanordnung 4 die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens 2 (Korrelationseinheit) und die Schaltungsanordnung zum Bestimmen der Trägerfrequenz 3 eines digitalen Datenstroms der Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts 1 vorgeschaltet sind. Die kombinierte Schaltungsanordnung 4 gemäß der bevorzugten Anordnung nach Fig. 2 umfasst die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens 2, die Schaltungsanordnung zum Bestimmen des optimalen Abtastzeitpunkts 1 und die Schaltungsanordnung zum Bestimmen der Trägerfrequenz eines digitalen Datenstroms 3. Diesen Schaltungsanordnungen 1, 2, 3 nachgeschaltet, baulich aber vorzugsweise in die kombinierte Schaltungsanordnung 4 integriert, sind die Schaltungsanordnung zum Bestimmen einer Phasenlage 19 des digitalen Datenstroms in Relation zu Referenzdaten, vorzugsweise das Synchronisationswort, und/oder die Schaltungsanordnung 20 zum Bestimmen des Beginns eines Datenrahmens.

Fig. 4 zeigt eine schematische Darstellung der Schaltungsanordnung 2 zur Bestimmung des Beginns eines Übertragungsrahmens, realisiert als Korrelation des eingehenden Datenstroms  $Z_k$  mit einem gespeicherten Synchronisationswort  $UW$ , wobei die Schaltungsanordnung zum Bestimmen der Trägerfrequenz 3 lediglich als Block dargestellt ist. Diesbezügliche technische Lösungen sind aus der einschlägigen Fachliteratur bekannt. Bevorzugt umfasst die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens 2 ein erstes Schieberegister 6 mit einer Registerlänge  $L_C N_{os}$ , wobei  $L_C$  die Länge des Synchronisationswortes  $UW$  und  $N_{os}$  der Grad der Überabtastung (Anzahl der Samples pro Symbol) ist.

Die Samples  $Z_k$ , wie sie am Ausgang des signalangepassten (matched) Filters 5 zur Verfügung stehen, werden in das erste Schieberegister 6 geladen. Dessen Inhalt wird im Abstand  $N_{os}$  abgegriffen, die betreffenden Samples (schwarz markiert) mit dem konjugiert-komplexen Synchronisationswort  $UW^*$  multipliziert (um die Datenmodulation zu eliminieren) und der Schaltungsanordnung zum Bestimmen der Trägerfrequenz 3 eines digitalen Datenstroms zugeführt. In der Folge werden die Samples, welche zuvor in einer Frequenzkorrekturseinheit 8 frequenzkorrigiert wurden, in einer Addiereinheit 29 aufaddiert

und in einer Betragsbildungseinheit 9 wird die Betragssumme für die weiterfolgende Bestimmung des optimalen Abtastzeitpunktes gebildet. Es kann vorgesehen sein, dass die Schaltungsanordnung zum Bestimmen der Trägerfrequenz 3 eines digitalen Datenstroms weiters einen Frequenzkorrekturwert  $v$  an einen komplexen Phasenschieber 21 zur Frequenzkorrektur des digitalen Datenstroms liefert.

Die aufaddierten Betragssummen werden an die Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts 1 weitergegeben.

Sowohl bei mäßig überabgetastet – interpolierten wie auch bei stärker überabgetasteten Signalen ohne Interpolation kann bei der bekannten Lösung das Korrelationsmaximum nicht berechnet bzw. gesucht werden, bevor nicht alle Samples, die über einer vorgebbaren Schwelle liegen, empfangen worden sind. Diese Tatsache wirkt sich insofern negativ aus, als bei derartigen Lösungen ein Register implementiert werden muss, welches die Samples für die Ermittlung des Betragssmaximums zwischenspeichert; deren Anzahl ist im Allgemeinen nicht konstant, was eine variable Registerlänge bedingt, die gerade für Hardware-Lösungen wenig elegant ist.

Bevorzugt ist vorgesehen, dass die Schaltungsanordnung zur Bestimmung des optimalen Abtastzeitpunkts eine Einheit zur Bestimmung der Änderung zweier aufeinanderfolgender Beträge des frequenzkorrigierten Korrelationsergebnisses umfasst. Eine derartige Einheit könnte als Differenziereinheit bezeichnet werden. Da es sich jedoch um einen digitalen Datenstrom handelt, ist bevorzugt eine Schaltungsanordnung vorgesehen, welche diese Bestimmung der Änderung zweier aufeinanderfolgender Samples auf diskrete Weise durchführt.

Es kann vorgesehen sein, dass die Schaltungsanordnung zur Bestimmung des optimalen Abtastzeitpunkts 1 wenigstens ein zweites Schieberegister 10 umfasst, wobei das zweite Schieberegister 10 vorzugsweise eine ungerade Anzahl Schieberegisterzellen 11 aufweist, wobei insbesondere bei einer ungeraden Überabtastung  $N_{OS}$  die Anzahl der Schieberegisterzellen 11 dem Wert von  $N_{OS}$  entspricht, bzw. dass bei einer geraden Überabtastung  $N_{OS}$  die Anzahl der Schieberegisterzellen 11 dem Wert von  $N_{OS}$  minus eins entspricht.

Eine bevorzugte Ausführung einer derartigen Schaltungsanordnung 1 ist in Fig. 5 dargestellt. Das zweite Schieberegister 10 wird schrittweise mit den Betragssummen aus der Betragsbildungseinheit 9 beschickt. Es kann vorgesehen sein, dass das zweite Schieberegister 10 einen ersten Zellenblock 12, eine mittlere Zelle 13 (schwarz markiert) und einen zweiten

Zellenblock 14 aufweist, wobei der erste Zellenblock 12 und der zweite Zellenblock 14 die gleiche Anzahl Zellen 11 umfassen, und die mittlere Zelle 13 an den dritten Eingang C einer Entscheidungslogik 15 angeschlossen ist. In dem Fall, wo bei einer geraden Anzahl Samples pro Symbol die Anzahl der Schiebregisterzellen der Anzahl der Samples pro Symbol entspricht, weist das zweite Schieberegister 10 einen ersten Zellenblock 12, zwei mittlere Zellen und einen zweiten Zellenblock 14 aufweist, wobei der erste Zellenblock 12 und der zweite Zellenblock 14 die gleiche Anzahl Zellen 11 umfassen, und die beiden mittleren Zellen an einen Eingang einer Mittelwerteinheit angeschlossen sind, deren Ausgang an den dritten Eingang C der Entscheidungslogik 15 angeschlossen ist. Der erste Zellenblock 12 und der zweite Zellenblock 14 sind bevorzugt an Eingängen jeweils wenigstens einer Summiereinheit 16 angeschlossen, wobei jeweils wenigstens ein Ausgang der Summiereinheiten 16 an einer Subtraktionseinheit 17 angeschlossen ist. Der Ausgang der Subtraktionseinheit 17 ist sowohl an einen Eingang eines Verzögerungsglieds 18 als auch direkt an einen zweiten Eingang B einer Entscheidungslogik 15 angeschlossen. Der Ausgang des Verzögerungsglieds 18 ist an einen ersten Eingang A der Entscheidungslogik 15 angeschlossen. An einen dritten Eingang C der Entscheidungslogik 15 ist die mittlere Zelle 13 bzw. bei zwei mittleren Zellen der Ausgang einer Mittelwerteinheit angeschlossen. An einen vierten Eingang D der Entscheidungslogik 15 liegt eine vorgebbare Korrelationsschwelle an.

Die Entscheidungslogik 15 liefert einen Synchronisationsimpuls an einen Ausgang E für den Beginn des Übertragungsrahmens und/oder des Datenrahmens, für die Berechnung der Trägerphase sowie für den Index jenes Samples, das dem optimalen Abtastzeitpunkt am nächsten liegt, genau dann, wenn der erste und der zweite Eingang A, B der Entscheidungslogik 15 das erste mal verschiedenes Vorzeichen besitzen und der dritte Eingang C über der am vierten Eingang D anliegenden Korrelationsschwelle liegt.

Der Synchronisationspuls wird an eine nachgeschaltete Schaltungsanordnung zum Bestimmen einer Phasenlage 19 des digitalen Datenstroms in Relation zu Referenzdaten und/oder an einen Eingang einer Schaltungsanordnung zum Bestimmen des Beginns eines Datenrahmens 20 geliefert, wobei vorzugsweise die Schaltungsanordnung zum Bestimmen der Phasenlage 19 des digitalen Datenstroms in Relation zu Referenzdaten und/oder die Schaltungsanordnung zum Bestimmen des Beginns eines Datenrahmens 20 Teil der kombinierten Schaltungsanordnung 4 mit gemeinsamen Dateneingang sind.

Die Ausgänge der kombinierten Schaltungsanordnung 4 sind, wie teilweise bereits dargelegt, mit einem komplexen Phasenschieber 21 und/oder mit einer Trackingeinheit

23 verbunden, wobei an den komplexen Phasenschieber 21 bevorzugt ein Frequenzkorrektursignal  $v$  geliefert wird und an die Trackingeinheit 23 bevorzugt wenigstens ein Wert für die Phasenlage des digitalen Datenstroms in Relation zu Referenzdaten und/oder ein Signal für den Beginn eines Datenrahmes geschickt wird.

Wenn das Sampling gegenüber dem empfangenen Signal keine bzw. eine unerhebliche Drift aufweist (hochgenaue lokale Oszillatoren in Sender und Empfänger, vernachlässigbarer Doppler-Effekt, stabile Ausbreitungsbedingungen etc.), was bei vielen Systemen in der Praxis der Fall ist, dann kann eventuell auf ein Nachführen des optimalen Abtastzeitpunktes verzichtet werden. Bei stärkerer Überabtastung ist in der Folge nur mehr ein Tracking der Trägerphase zu implementieren. Insofern unterstützt die gemeinsame Akquisition mit  $N_{OS} > 4$  nicht zuletzt moderne Konzepte für die Fehlerkorrektur, wo Trägersynchronisation und Datendetektion gemeinsam gelöst werden, was eine Tracking-Einheit 23 hinfällig macht.

Fig. 3 zeigt eine Anordnung, bei der die Schaltungsanordnung zum Bestimmen der Trägerfrequenz 3 eines digitalen Datenstroms nicht in die gemeinsame Schaltungsanordnung 4 integriert ist. Vielmehr ist diese zusammen mit einer speziellen Korrelationseinheit 32 in einer separaten Schaltungsanordnung untergebracht. Der eingehende Datenstrom wird dabei vor der gemeinsamen Schaltungsanordnung 4 frequenzkorrigiert, wodurch der Aufbau der gemeinsamen Schaltungsanordnung 4 vereinfacht werden kann.

Zu diesem Zweck wird ein Burst-Konzept implementiert, wo zwischen Referenz-Bursts auf der einen und Daten-Bursts auf der anderen Seite mit Hilfe des Synchronisationswortes  $UW$  unterschieden wird. So können etwa in einem digitalen TDMA-System die Referenz-Bursts von der Master-Station in regelmäßigen Abstand, welcher von der maximalen Frequenzdrift zwischen Sender und Empfänger bestimmt ist, ausgesendet werden.

Da viele Einheiten zur Frequenzermittlung auch dann noch brauchbare Resultate liefern, wenn nicht exakt in der Symbolmitte abgetastet wird, ist es kein Problem, diese unabhängig von der Schaltungsanordnung zum Bestimmen des optimalen Abtastzeitpunkts 1 zu betreiben.

Mit dem Wert von  $v$  wird in weiterer Folge der komplexe Phasenschieber 21 angesteuert. Ein Mittelwertbildner 28 ist nur notwendig, wenn ein einziger Wert zu ungenau ist, um eine zuverlässige Frequenzkorrektur zu gewährleisten. Die frequenzkorrigierten Samples der Daten-Bursts werden anschließend der kombinierten Schaltungsanordnung 4

übergeben. Im Detail bedeutet das, dass Sequenzen von  $L_c$  Samples, jeweils in einem Abstand von  $N_{os}$  Samples zu ihren Nachbarn, mit dem Synchronisationswort  $UW$  korreliert werden. Die Schaltungsanordnung zum Bestimmen des optimalen Abtastzeitpunkts 1 wird aktiv, sobald der Betrag eines Korrelationsergebnisses über der vorgegebenen Schwelle liegt. Erst dann werden die folgenden Betragssummen geprüft und diejenige, welcher der Nulllinie am nächsten liegt, als Referenz für die Bestimmung von Rahmenbeginn und Phasenlage des digitalen Datenstroms in Relation zu Referenzdaten herangezogen.

Bevorzugt kann vorgesehen sein, eine erfindungsgemäße Akquisitionseinheit mittels Hardwarekomponenten (etwa digitale Gatter, PGAs oder FPGAs) aufzubauen.

Die Erfindung umfasst weiters ein digitales TDMA-Modem mit einer beschriebenen Akquisitionseinheit und/oder ein digitales TDMA-Modem welches mit einer Software betrieben wird, welche ein erfindungsgemäßes Verfahren durchführt.

Es kann vorgesehen sein, eine ein erfindungsgemäßes Verfahren umsetzende Software auf einem Datenträger zu speichern.

Weitere erfindungsgemäße Ausführungsformen weisen lediglich einen Teil der beschriebenen Merkmale auf, wobei jede Merkmalskombination, insbesondere auch von verschiedenen beschriebenen Ausführungsformen, als weitere Ausführungsformen vorgesehen sein können.

Patentansprüche:

ÖOJ2406

16

PATENTANWALT DIPLO-ING. DR. TECHN.

**FERDINAND GIBLER**

Vertreter vor dem Europäischen Patentamt

A-1010 WIEN Dorotheergasse 7

Telefon: (-43-1-) 512 10 98

Fax: (-43-1-) 513 47 76

28253/II

## P A T E N T A N S P R Ü C H E

1. Akquisitionseinheit für ein digitales TDMA-Modem, umfassend eine Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts (1) eines digitalen Datenstroms, welcher durch Überabtastung mit einer vorgebbaren Anzahl Samples pro Symbol aus einem Basisbandsignal generiert ist, einer Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens (2) und einer Schaltungsanordnung zum Bestimmen der Trägerfrequenz (3) eines digitalen Datenstroms, **dadurch gekennzeichnet**, dass eine kombinierte Schaltungsanordnung (4) mit einem gemeinsamen Dateneingang (30) ausgebildet ist, welche die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens (2) und die Schaltungsanordnung zum Bestimmen des optimalen Abtastzeitpunkts (1) umfasst.

2. Akquisitionseinheit nach Anspruch 1, **dadurch gekennzeichnet**, dass die kombinierte Schaltungsanordnung (4) mit einem gemeinsamen Dateneingang (30) die Schaltungsanordnung zum Bestimmen der Trägerfrequenz (3) eines digitalen Datenstroms umfasst.

3. Akquisitionseinheit nach Anspruch 1 oder 2, **dadurch gekennzeichnet**, dass die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens (2) und die Schaltungsanordnung zum Bestimmen der Trägerfrequenz (3) eines digitalen Datenstroms der Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts (1) vorgeschaltet sind.

4. Akquisitionseinheit nach einem der Ansprüche 1 bis 3, **dadurch gekennzeichnet**, dass der kombinierten Schaltungsanordnung (4) ein signalangepasstes Filter (5) vorgeschaltet ist.

5. Akquisitionseinheit nach einem der Ansprüche 1 bis 4, **dadurch gekennzeichnet**, dass die Schaltungsanordnung zum Bestimmen des Beginns eines Übertragungsrahmens (2) ein erstes Schieberegister (6) umfasst, dessen Registerlänge dem Produkt aus der Anzahl der Samples pro Symbol und der Länge eines Synchronisationswortes in Symbolen eines vorgebbaren Modulationsverfahrens entspricht.

6. Akquisitionseinheit nach einem der Ansprüche 1 bis 5, **dadurch gekennzeichnet**, dass dem Ausgang (7) der Schaltungsanordnung zum Bestimmen der Trägerfrequenz (3) eines digitalen Datenstroms eine Frequenzkorrekturereinheit (8) nachgeschaltet ist.

7. Akquisitionseinheit nach Anspruch 6, **dadurch gekennzeichnet**, dass dem Ausgang der Frequenzkorrekturereinheit (8) wenigstens eine Einheit zur Bildung des Absolutbetrags (9) der aufaddierten und frequenzkorrigierten Produkte aus dem konjugiert-komplexen Synchronisationswort und den eingehenden Sampels nachgeschaltet ist.

8. Akquisitionseinheit nach einem der Ansprüche 1 bis 7, **dadurch gekennzeichnet**, dass die Schaltungsanordnung zur Bestimmung eines optimalen Abtastzeitpunkts (1) wenigstens ein zweites Schieberegister (10) umfasst, wobei das zweite Schieberegister (10) vorzugsweise eine ungerade Anzahl Schieberegisterzellen (11) aufweist, wobei insbesondere bei einer ungeraden Anzahl Samples pro Symbol die Anzahl der Schieberegisterzellen (11) der Anzahl Samples pro Symbol entspricht, bzw. dass bei einer geraden Anzahl Samples pro Symbol die Anzahl der Schieberegisterzellen (11) der Anzahl Samples pro Symbol minus eins entspricht.

9. Akquisitionseinheit nach Anspruch 8, **dadurch gekennzeichnet**, dass das zweite Schieberegister (10) einen ersten Zellenblock (12), eine mittlere Zelle (13) und einen zweiten Zellenblock (14) aufweist, wobei der erste Zellenblock (12) und der zweite Zellenblock (14) die gleiche Anzahl Zellen (11) umfassen, und die mittlere Zelle (13) an einen Eingang (C) einer Entscheidungslogik (15) angeschlossen ist, oder dass das zweite Schieberegister (10) einen ersten Zellenblock (12), zwei mittlere Zellen und einen zweiten Zellenblock (14) aufweist, wobei der erste Zellenblock (12) und der zweite Zellenblock (14) die gleiche Anzahl Zellen (11) umfassen, und die beiden mittleren Zellen an einen Eingang einer

Mittelwerteinheit angeschlossen sind, deren Ausgang an den Eingang (C) der Entscheidungslogik (15) angeschlossen ist.

10. Akquisitionseinheit nach Anspruch 9, **dadurch gekennzeichnet**, dass der erste Zellenblock (12) und der zweite Zellenblock (14) an Eingängen jeweils wenigstens einer Summiereinheit (16) angeschlossen sind, und dass jeweils wenigstens ein Ausgang der Summriereinheiten (16) an einer Subtraktionseinheit (17) angeschlossen ist.

11. Akquisitionseinheit nach Anspruch 10, **dadurch gekennzeichnet**, dass wenigstens ein Ausgang der Subtraktionseinheit (17) sowohl mittels wenigstens eines Verzögerungsglieds (18), als auch direkt an Eingängen (A, B) der Entscheidungslogik (15) angeschlossen ist.

12. Akquisitionseinheit nach einem der Ansprüche 9 bis 11, **dadurch gekennzeichnet**, dass wenigstens ein Ausgang (E) der Entscheidungslogik (15) mit wenigstens einem Eingang einer Schaltungsanordnung zum Bestimmen einer Phasenlage (19) des digitale Datenstroms in Relation zu Referenzdaten, vorzugsweise dem Synchronisationswort, und/oder wenigstens einem Eingang einer Schaltungsanordnung zum Bestimmen des Beginns eines Datenrahmens (20) verbunden ist, wobei vorzugsweise die Schaltungsanordnung zum Bestimmen der Phasenlage (19) des digitalen Datenstroms in Relation zu Referenzdaten und/oder die Schaltungsanordnung zum Bestimmen des Beginns eines Datenrahmens (20) Teil der kombinierten Schaltungsanordnung (4) mit gemeinsamen Dateneingang sind.

13. Akquisitionseinheit nach einem der Ansprüche 1 bis 12, **dadurch gekennzeichnet**, dass die Ausgänge der kombinierten Schaltungsanordnung (4) mit wenigstens einem komplexen Phasenschieber (21) zur Korrektur des digitalen Datenstroms mit wenigstens einem Korrekturfaktor, vorzugsweise einem Frequenzkorrekturfaktor und/oder einer Trackingeinheit (23) leitend verbunden sind.

14. Verfahren zur Synchronisation eines digitalen TDMA-Modems auf einen entsprechenden aus Samples bestehenden digitalen Datenstrom, welcher aus einem mit einer vorgebbaren Anzahl Samples pro Symbol überabgetasteten Basisbandsignal generiert ist, wobei aus dem digitalen Datenstrom eine Trägerfrequenz des digitalen Datenstroms, der Beginn eines Übertragungsrahmens, ein optimaler Abtastzeitpunkt sowie eine Phasenlage des

digitalen Datenstroms in Relation zu Referenzdaten ermittelt werden, und der digitale Datenstrom vor der Ausgabe mit wenigstens einem Korrekturwert korrigiert wird, **dadurch gekennzeichnet**, dass der Beginn des Übertragungsrahmens und der optimale Abtastzeitpunkt in einer kombinierten Schaltungsanordnung (4) mit einem gemeinsamen Dateneingang ermittelt werden.

15. Verfahren nach Anspruch 14, **dadurch gekennzeichnet**, dass die Trägerfrequenz des digitalen Datenstroms in der kombinierten Schaltungsanordnung (4) mit einem gemeinsamen Dateneingang ermittelt wird.

16. Verfahren nach Anspruch 14 oder 15, **dadurch gekennzeichnet**, dass vor Ermittlung des Beginns eines Übertragungsrahmens, der Trägerfrequenz des digitalen Datenstroms und des optimalem Abtastzeitpunkts der eingehende digitale Datenstrom in einem signalangepassten Filter (5) gefiltert wird.

17. Verfahren nach Anspruch 14, 15 oder 16, **dadurch gekennzeichnet**, dass die Trägerfrequenz des digitalen Datenstroms in an sich bekannter Weise detektiert wird, ein Frequenzkorrekturfaktor gebildet und der digitale Datenstrom frequenzkorrigiert wird.

18. Verfahren nach Anspruch 17, **dadurch gekennzeichnet**, dass aus den frequenzkorrigierten Sampels des digitalen Datenstroms die Betragssumme gebildet wird.

19. Verfahren nach Anspruch 18, **dadurch gekennzeichnet**, dass die Betragssummen sukzessive in ein zweites Schieberegister (10) mit ungeradzahliger Registerlänge geladen werden, wobei die Registerlänge vorzugsweise der Anzahl Samples pro Symbol oder der Anzahl Samples pro Symbol minus eins entspricht.

20. Verfahren nach Anspruch 19, **dadurch gekennzeichnet**, dass das zweite Schieberegister (10) erste Registereinträge, einen mittleren Registereintrag und zweite Registereinträge aufweist, wobei die Anzahl der ersten Registereinträge gleich der Anzahl der zweiten Registereinträge ist und der mittlere Registereintrag an einen Eingang einer Entscheidungslogik geliefert wird.

21. Verfahren nach Anspruch 20, **dadurch gekennzeichnet**, dass die ersten Registereinträge sowie die zweiten Registereinträge jeweils aufsummiert werden, und die derart gebildete erste und zweite Registereintragssumme voneinander subtrahiert werden.

22. Verfahren nach Anspruch 21, **dadurch gekennzeichnet**, dass jeweils zwei aufeinanderfolgende Ergebnisse der Subtraktion der Registereintragssummen als Eingänge an die Entscheidungslogik (15) geliefert werden, und die Entscheidungslogik an einem Ausgang (E) einen Synchronisationspuls als Kennzeichen des optimalen Abtastzeitpunkts liefert, wenn die zwei aufeinanderfolgenden Ergebnisse der Subtraktion verschiedene Vorzeichen aufweisen und der mittlere Registereintrag oberhalb einer vorgebbaren Korrelationsschwelle liegt.

23. Verfahren nach Anspruch 22, **dadurch gekennzeichnet**, dass mit dem Synchronisationspuls ein Trägerphasenwert und/oder ein Rahmenbeginnsignal in an sich bekannter Weise in der kombinierten Schaltungsanordnung (4) mit gemeinsamen Dateneingang ermittelt werden.

24. Verfahren nach Anspruch 23, **dadurch gekennzeichnet**, dass der digitale Datenstrom mit dem Frequenzkorrekturfaktor und/oder dem Trägerphasenwert und/oder dem Rahmenbeginnsignal, vorzugsweise in wenigstens einer Trackingeinheit (23) und/oder wenigstens einem komplexen Phasenschieber (21), korrigiert wird und/oder an weitere Verarbeitungsstufen weitergegeben wird.

25. Computerprogrammprodukt, das direkt in den internen Speicher eines Computers geladen werden kann und Softwarecodeabschnitte umfasst, mit denen die Schritte des Verfahrens gemäß einem der Ansprüche 14 bis 24 ausgeführt werden, wenn das Computerprogrammprodukt auf einem Computer läuft.

26. Datenträger mit einem Computerprogrammprodukt nach Anspruch 25.

27. Digitales TDMA-Modem, **gekennzeichnet durch** eine Akquisitionseinheit nach einem der Ansprüche 1 bis 13.

00124-06:

21

28. Digitales TDMA-Modem, **dadurch gekennzeichnet**, dass ein Verfahren nach einem der Ansprüche 14 bis 24, insbesondere mittels eines Computerprogrammprodukts nach Anspruch 25, implementiert ist.

Der Patentanwalt:

~~PATENTANWALT DIPL.-ING. DR. TECHN.

F E R D I N A N D G A B L E R~~

Vertreter vor dem Europäischen Patentamt

A-1010 WIEN Dorotheergasse 7

Telefon: (-43-1-) 512 10 98

Fax: (-43-1-) 513 47 76

002406

1 / 3

Fig. 1

Fig. 2

0002406

2 / 3

Fig. 3

Fig. 4

Fig. 5