(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5912841号

(P5912841)

(45) 発行日 平成28年4月27日(2016.4.27)

(24) 登録日 平成28年4月8日(2016.4.8)

(51) Int.Cl.

F 1

|             |                |                  |             |              |             |

|-------------|----------------|------------------|-------------|--------------|-------------|

| <b>H03K</b> | <b>3/356</b>   | <b>(2006.01)</b> | <b>HO3K</b> | <b>3/356</b> | <b>B</b>    |

| <b>HO1L</b> | <b>27/10</b>   | <b>(2006.01)</b> | <b>HO1L</b> | <b>27/10</b> | <b>495</b>  |

| <b>HO1L</b> | <b>21/8242</b> | <b>(2006.01)</b> | <b>HO1L</b> | <b>27/10</b> | <b>621Z</b> |

| <b>HO1L</b> | <b>27/108</b>  | <b>(2006.01)</b> | <b>HO1L</b> | <b>27/10</b> | <b>671C</b> |

| <b>HO1L</b> | <b>29/786</b>  | <b>(2006.01)</b> | <b>HO1L</b> | <b>27/10</b> | <b>671Z</b> |

請求項の数 5 (全 47 頁) 最終頁に続く

(21) 出願番号

特願2012-113045 (P2012-113045)

(22) 出願日

平成24年5月17日(2012.5.17)

(65) 公開番号

特開2013-9323 (P2013-9323A)

(43) 公開日

平成25年1月10日(2013.1.10)

審査請求日

平成27年3月13日(2015.3.13)

(31) 優先権主張番号

特願2011-114084 (P2011-114084)

(32) 優先日

平成23年5月20日(2011.5.20)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 大嶋 和晃

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 小林 英智

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 角田 慎治

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

フリップフロップ回路と、選択回路と、前記選択回路を介して前記フリップフロップ回路と電気的に接続された記憶回路と、を含むレジスタ回路と、

ビット線と、

データ線と、を有し、

前記データ線は前記フリップフロップ回路と電気的に接続され、

前記ビット線は、前記選択回路を介して前記記憶回路と電気的に接続され、

前記選択回路は、前記フリップフロップ回路の出力の電位または前記ビット線の電位に応じたデータを選択的に前記記憶回路に格納し、

前記記憶回路はチャネル形成領域に、酸化物半導体を含むトランジスタと、前記トランジスタの第1の電極と一方の電極が電気的に接続され、他方の電極が接地されている容量素子と、を有し、

前記データ線または前記ビット線の電位は、前記トランジスタの第1の電極と、前記容量素子の一方の電極と、が接続されたノードに格納されることを特徴とする半導体装置。

## 【請求項 2】

フリップフロップ回路と、選択回路と、前記選択回路を介して前記フリップフロップ回路と電気的に接続する記憶回路と、を含むレジスタ回路と、

ビット線と、

データ線と、

10

20

ワード線と、

メモリライトイネーブル線と、を有し、

前記ワード線及び前記メモリライトイネーブル線は前記選択回路と電気的に接続され、

前記データ線は前記フリップフロップ回路と電気的に接続され、

前記ピット線は、前記選択回路を介して前記記憶回路と電気的に接続され、

前記選択回路は、

前記記憶回路と、前記ワード線または前記メモリライトイネーブル線との電気的接続を選択する第1のスイッチと、

前記記憶回路と、前記フリップフロップ回路の出力または前記ピット線との電気的接続を選択する第2のスイッチと、を有し、

前記記憶回路はチャネル形成領域に、酸化物半導体を含むトランジスタと、前記トランジスタの第1の電極と一方の電極が電気的に接続され、他方の電極が接地されている容量素子と、を有し、

前記データ線または前記ピット線の電位は、前記トランジスタの第1の電極と、前記容量素子の一方の電極と、が接続されたノードに格納されることを特徴とする半導体装置。

### 【請求項3】

マトリクス状に設けられた複数のレジスタ回路と、

ピット線と、

データ線と、を有し、

前記レジスタ回路の一は、

フリップフロップ回路と、選択回路と、前記選択回路を介して前記フリップフロップ回路と電気的に接続された記憶回路と、を含み、

前記データ線は前記フリップフロップ回路と電気的に接続され、

前記ピット線は、前記選択回路を介して前記記憶回路と電気的に接続され、

前記選択回路は、前記フリップフロップ回路の出力の電位または前記ピット線の電位に応じたデータを選択的に前記記憶回路に格納し、

前記記憶回路はチャネル形成領域に、酸化物半導体を含むトランジスタと、前記トランジスタの第1の電極と一方の電極が電気的に接続され、他方の電極が接地されている容量素子と、を有し、

前記データ線または前記ピット線の電位は、前記トランジスタの第1の電極と、前記容量素子の一方の電極と、が接続されたノードに格納されることを特徴とする半導体装置。

### 【請求項4】

マトリクス状に設けられた複数のレジスタ回路と、

ピット線と、

データ線と、

ワード線と、

メモリライトイネーブル線と、を有し、

前記レジスタ回路の一は、

フリップフロップ回路と、選択回路と、前記選択回路を介して前記フリップフロップ回路と電気的に接続された記憶回路と、を含み、

前記ワード線及び前記メモリライトイネーブル線は前記選択回路と電気的に接続され、

前記データ線は前記フリップフロップ回路と電気的に接続され、

前記ピット線は、前記選択回路を介して前記記憶回路と電気的に接続され、

前記選択回路は、

前記記憶回路と、前記ワード線または前記メモリライトイネーブル線との電気的接続を選択する第1のスイッチと、

前記記憶回路と、前記フリップフロップ回路の出力または前記ピット線との電気的接続を選択する第2のスイッチと、を有し、

前記記憶回路はチャネル形成領域に、酸化物半導体を含むトランジスタと、前記トランジスタの第1の電極と一方の電極が電気的に接続され、他方の電極が接地されている容量

10

20

30

40

50

素子と、を有し、

前記データ線または前記ビット線の電位は、前記トランジスタの第1の電極と、前記容量素子の一方の電極と、が接続されたノードに格納されることを特徴とする半導体装置。

#### 【請求項 5】

請求項1乃至請求項4のいずれか一項において、

前記選択回路は、

前記記憶回路に前記フリップフロップ回路を介してデータ線の電位に応じたデータを格納する第1の動作モードと、

前記フリップフロップ回路に、前記記憶回路に格納されたデータを入力する第2の動作モードと、

10

前記記憶回路に前記ビット線の電位に応じたデータを格納する第3の動作モードと、

前記ビット線に前記記憶回路に格納されたデータを入力する第4の動作モードと、のいずれかを選択することを特徴とする半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体装置及び該半導体装置の駆動方法に関するものである。

##### 【背景技術】

##### 【0002】

中央演算処理装置(CPU: Central Processing Unit)などの信号処理回路は、その用途によって多種多様な構成を有しているが、一般的に、データやプログラムを記憶するためのメインメモリの他にレジスタ、キャッシュメモリなど、各種の記憶装置が設けられている。レジスタは、演算処理やプログラムの実行状態の保持などのために一時的にデータを保持する役割を担っている。また、キャッシュメモリは、演算回路とメインメモリの間に介在し、メインメモリへのアクセスを減らして演算処理を高速化させることを目的として設けられている。

20

##### 【0003】

レジスタやキャッシュメモリ等の記憶装置は、メインメモリよりも高速でデータの書き込みを行う必要がある。よって、通常は、レジスタとしてフリップフロップ回路が、キャッシュメモリとしてSRAM(Static Random Access Memory)等が用いられる。つまり、これらのレジスタ、キャッシュメモリ等には、電源電圧の供給が途絶えるとデータを消失してしまう揮発性記憶回路が用いられている。

30

##### 【0004】

消費電力を抑えるため、データの入出力が行われない期間において、信号処理回路への電源電圧の供給を一時的に停止するという方法が提案されている。この方法では、レジスタ、キャッシュメモリ等の揮発性の記憶装置の周辺に不揮発性記憶装置を配置し、上記データをその不揮発性記憶装置に一時的に記憶させる。こうして、信号処理回路において電源電圧の供給を停止する間も、レジスタ、キャッシュメモリに記憶されていたデータを保持することができる(例えば、特許文献1参照)。

40

##### 【0005】

また、信号処理回路において、長時間の電源電圧の供給停止を行う際には、電源電圧の供給停止の前に、揮発性の記憶装置内のデータをハードディスク、フラッシュメモリ等の外部記憶装置に移すことによって、データの消失を防ぐこともできる。

##### 【先行技術文献】

##### 【特許文献】

##### 【0006】

【特許文献1】特開平10-078836号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0007】

50

上記のように、電源電圧の供給停止期間中にデータを記憶するための外部記憶装置を設ける構成とした場合、信号処理回路から外部記憶装置へのデータの書き込みに時間がかかるため、短時間の電源停止には適さないといった問題がある。

#### 【0008】

また、信号処理回路内のデータに不具合が生じた場合、不具合が生じたデータの評価及び不具合が生じたデータの書き換えを行うには時間がかかり、速やかに電源電圧の供給停止状態から復帰できなくなるといった問題がある。

#### 【0009】

したがって、信号処理回路のデータを高速で不揮発性記憶装置へ移行して、高頻度で電力の供給を停止することが可能なため、消費電力を低減することができる半導体装置を提供することを課題の一とする。また、所望のタイミングでデータの評価、書き換えを行うことができる半導体装置を提供することを課題の一とする。10

#### 【課題を解決するための手段】

#### 【0010】

半導体装置が有するフリップフロップ回路毎に不揮発性記憶回路を設ける。該フリップフロップ回路と不揮発性記憶回路間ににおいてデータのやりとりを行うことで、高速にデータを移動することができる。さらに、該不揮発性記憶回路に直接、データの書き込み及び読み出しを行う配線を設ける構成として、該配線を通して所望のタイミングで半導体装置が保持しているデータの評価、書き換えを行うことができる。

#### 【0011】

したがって、本発明の一態様は、フリップフロップ回路と、選択回路と、選択回路を介してフリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含むレジスタ回路と、ビット線と、データ線と、を有し、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、データ線の電位またはビット線の電位に応じたデータを選択的に不揮発性記憶回路に格納する半導体装置である。20

#### 【0012】

また、本発明の別の一態様は、フリップフロップ回路と、選択回路と、選択回路を介してフリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含むレジスタ回路と、ビット線と、データ線と、ワード線と、メモリライトイネーブル線と、を有し、ワード線及びメモリライトイネーブル線は選択回路と電気的に接続し、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、不揮発性記憶回路と、ワード線またはメモリライトイネーブル線との電気的接続を選択する第1のスイッチと、不揮発性記憶回路と、データ線またはビット線との電気的接続を選択する第2のスイッチと、を有する半導体装置である。30

#### 【0013】

また、本発明の一態様は、マトリクス状に設けられた複数のレジスタ回路と、ビット線と、データ線と、を有し、レジスタ回路の一は、フリップフロップ回路と、選択回路と、選択回路を介してフリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含み、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、データ線の電位またはビット線の電位に応じたデータを選択的に不揮発性記憶回路に格納する半導体装置である。40

#### 【0014】

また、本発明の別の一態様は、マトリクス状に設けられた複数のレジスタ回路と、ビット線と、データ線と、ワード線と、メモリライトイネーブル線と、を有し、レジスタ回路の一は、フリップフロップ回路と、選択回路と、選択回路を介してフリップフロップ回路と電気的に接続する不揮発性記憶回路と、を含み、ワード線及びメモリライトイネーブル線は選択回路と電気的に接続し、データ線はフリップフロップ回路と電気的に接続し、ビット線は、選択回路を介して不揮発性記憶回路と電気的に接続し、選択回路は、不揮発性記憶回路と、ワード線またはメモリライトイネーブル線との電気的接続を選択する第1のス50

イッチと、不揮発性記憶回路と、データ線またはビット線との電気的接続を選択する第2のスイッチと、を有する半導体装置である。

**【0015】**

また、本発明の一態様の半導体装置に用いる選択回路は、不揮発性記憶回路にフリップフロップ回路を介してデータ線の電位に応じたデータを格納する第1の動作モードと、フリップフロップ回路に、不揮発性記憶回路に格納されたデータを入力する第2の動作モードと、不揮発性記憶回路にビット線の電位に応じたデータを格納する第3の動作モードと、ビット線に不揮発性記憶回路に格納されたデータを入力する第4の動作モードと、のいずれかを選択する。

**【0016】**

10

また、本発明の一態様の半導体装置に用いる不揮発性記憶回路は、チャネル形成領域に、酸化物半導体を含むトランジスタと、トランジスタの第1の電極と一方の電極が電気的に接続し、他方の電極が接地されている容量素子と、を有し、データ線またはビット線の電位は、トランジスタの第1の電極と、容量素子の一方の電極と、が接続されたノードに格納される半導体装置である。

**【発明の効果】**

**【0017】**

レジスタ回路に含まれるフリップフロップ回路毎に不揮発性記憶回路が設けられ、電力の供給を停止してもデータを保持できるため、消費電力の低減された半導体装置を提供することができる。また、該不揮発性記憶回路がレジスタ回路の外部と直接データのやり取りを行う配線を設けることで、所望のタイミングでデータの評価、書き換えを行うことができる半導体装置を提供することができる。

20

**【図面の簡単な説明】**

**【0018】**

【図1】本発明の一態様の半導体装置を示す図。

【図2】本発明の一態様の半導体装置が有するフリップフロップ回路について示す図。

【図3】本発明の一態様の半導体装置の動作を示すタイミングチャート。

【図4】本発明の一態様の半導体装置の動作を示すタイミングチャート。

【図5】本発明の一態様の半導体装置の動作を示すタイミングチャート。

【図6】本発明の一態様の半導体装置を示す図。

30

【図7】トランジスタに適用できる酸化物材料の結晶構造を説明する図。

【図8】トランジスタに適用できる酸化物材料の結晶構造を説明する図。

【図9】トランジスタに適用できる酸化物材料の結晶構造を説明する図。

【図10】トランジスタに適用できる酸化物材料の結晶構造を説明する図。

【図11】計算によって得られた移動度のゲート電圧依存性を説明する図。

【図12】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図。

。

【図13】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図

。

【図14】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図

40

【図15】計算に用いたトランジスタの断面構造を説明する図。

【図16】酸化物半導体膜を用いたトランジスタ特性を説明する図。

【図17】試料1のトランジスタのBT試験後のドレイン電流のゲート電圧依存性を説明する図。

【図18】試料2であるトランジスタのBT試験後のドレイン電流のゲート電圧依存性を説明する図。

【図19】ドレイン電流のゲート電圧依存性を説明する図。

【図20】基板温度としきい値電圧の関係及び基板温度と電界効果移動度の関係を説明する図。

50

【図21】試料Aおよび試料BのXRDスペクトルを説明する図。

【図22】トランジスタのオフ電流と測定時基板温度との関係を説明する図。

【図23】トランジスタの断面図。

【図24】本発明の一態様に係る信号処理回路を示す図。

【発明を実施するための形態】

【0019】

以下に本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の主旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更しうることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。10

【0020】

また、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0021】

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、コイル、容量素子、その他の各種機能を有する素子などが含まれる。20

【0022】

なお、一般的に電圧とは、ある二点間における電位の差（電位差ともいう）のことをいう。しかし、電圧及び電位の値は、回路図などにおいていずれもボルト（V）で表されることがあるため、区別が困難である。そこで、本明細書では、特に指定する場合を除き、ある一点の電位と基準となる電位（基準電位ともいう）との電位差を、該一点の電圧として用いる場合がある。

【0023】

また、ソースやドレインの機能は異なる極性のトランジスタを採用する場合や、回路動作において、電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、ソースやドレインの用語は入れ替えて用いることが出来るものとする。さらに、本明細書ではトランジスタのソース、またはドレインのどちらか一方のことを第1の電極と呼び、ソース、またはドレインの他方を第2の電極と呼ぶことがある。30

【0024】

（実施の形態1）

本実施の形態では、本発明の一態様の半導体装置について説明する。

【0025】

<基本回路>

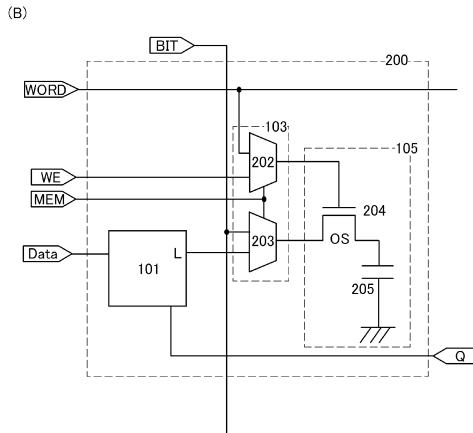

はじめに、本実施の形態の半導体装置の一態様のレジスタ回路及びその動作について説明する。図1（A）にレジスタ回路のブロック図を示す。図1（A）に示すレジスタ回路100は、フリップフロップ回路101と、選択回路103と、不揮発性記憶回路105と、を有している。また、図1（A）において、データ線（Data）はフリップフロップ回路101と電気的に接続し、ビット線（BIT）は、選択回路103を介して不揮発性記憶回路105と電気的に接続する。また、フリップフロップ回路101と出力信号線（Q）とは、電気的に接続されている。40

【0026】

フリップフロップ回路101は、データ線（Data）の電位が入力され、入力された電位に応じたデータをフリップフロップ回路101の内部状態として格納するとともに、出力信号線（Q）から外部へと出力する。50

**【0027】**

なお、電位に応じたデータとは、例えば二つの異なる電位のいずれかが選択的に供給され、一方の電位（例えば、高電位、ハイレベル）をデータ”1”に対応させ、他方の電位（例えば、低電位、ロウレベル）をデータ”0”に対応させることによって、1ビットのデータとしたものである。また、異なる三つまたはそれ以上の電位のうちから選択することによって、多値（複数ビット）の情報を書き込み、半導体装置の記憶容量を向上させてもよい。

**【0028】**

一般的に、フリップフロップ回路は少なくとも2つの演算回路を有し、一方の演算回路の出力が他方の演算回路に入力され、他方の演算回路の出力が一方の演算回路に入力されるような帰還ループを有する構成とすることができます。したがって、フリップフロップ回路はデータ線（Data）から入力された電位に応じたデータを格納し出力する揮発性記憶回路である。レジスタ回路100において、フリップフロップ回路101の出力は選択回路103へ入力される。10

**【0029】**

選択回路103には、フリップフロップ回路101の出力とビット線（BIT）の電位が入力される。選択回路103の出力端子は不揮発性記憶回路105の入力端子と電気的に接続している。不揮発性記憶回路105は、選択回路103が選択する動作モードに応じて、フリップフロップ回路101またはビット線（BIT）とデータのやり取りを行う。

**【0030】**

ここで、選択回路103が選択する半導体装置の動作モードについて説明する。20

**【0031】**

選択回路103は半導体装置の4つの動作モードのいずれか一を選択する。4つの動作モードとは、不揮発性記憶回路105にフリップフロップ回路101を介してデータ線（Data）の電位に応じたデータを格納する第1の動作モードと、フリップフロップ回路101に、不揮発性記憶回路105に格納されたデータを入力する第2の動作モードと、不揮発性記憶回路105にビット線（BIT）の電位に応じたデータを格納する第3の動作モードと、ビット線（BIT）に不揮発性記憶回路105に格納されたデータを入力する第4の動作モードと、である。

**【0032】**

上記の4つの動作モードを組み合わせることで、半導体装置の消費電力を低減することができる。その動作方法について説明する。

**【0033】**

本実施の形態の半導体装置においては、データ線（Data）の電位がフリップフロップ回路101に入力され、当該電位に応じたデータがフリップフロップ回路101に格納される。上記したとおり、フリップフロップ回路101は揮発性記憶回路であるため、フリップフロップ回路101に格納されたデータを保持するためには電力の供給が必要である。したがってフリップフロップ回路101の内部状態を書き換えない期間においても、フリップフロップ回路101に格納されたデータを保持するためには電力を供給し続ける必要がある。40

**【0034】**

しかしながら、本実施の形態の半導体装置は、レジスタ回路100毎に、フリップフロップ回路101と電気的に接続された不揮発性記憶回路105を有するため、フリップフロップ回路101の内部状態が変化しない期間に際し、不揮発性記憶回路105にデータを格納することで、電力の供給を停止しても、フリップフロップ回路101の内部状態を保持することができる。フリップフロップ回路101の内部状態の不揮発性記憶回路105への格納は、選択回路103による第1の動作モードの選択によって可能となる。

**【0035】**

続いて、選択回路103が第2の動作モードを選択し、フリップフロップ回路101に不揮発性記憶回路105に格納されているデータを格納することで、フリップフロップ回路50

101を電力の供給を停止する以前の状態へ復帰することができる。

**【0036】**

また、選択回路による4つの動作モードを組み合わせることで、半導体装置は所望のタイミングでフリップフロップ回路101の内部状態を評価することができる。その動作方法について説明する。

**【0037】**

選択回路103が第1の動作モードを選択することで、フリップフロップ回路101の内部状態が不揮発性記憶回路105に格納される。この状態で、選択回路103が第4の動作モードを選択し、不揮発性記憶回路105に格納されているデータをビット線(BIT)に入力することで、ビット線(BIT)にフリップフロップ回路101の内部状態に応じた電位が入力される。したがって、ビット線(BIT)に入力された電位を読み出すことで、フリップフロップ回路101の内部状態を評価することができる。10

**【0038】**

また、フリップフロップ回路101の内部状態を評価し、不具合を見つかった場合において、本実施の形態の半導体装置は容易にフリップフロップ回路101の内部状態を書き換えることができる。その動作方法について説明する。

**【0039】**

フリップフロップ回路101の内部状態を書き換えるためには、まず、選択回路103に第3の動作モードを選択させる。第3の動作モードにおいて、ビット線(BIT)に書き換えデータに応じた電位を入力し、不揮発性記憶回路105にビット線(BIT)の電位に応じたデータを格納する。20

**【0040】**

次に、選択回路103に第2の動作モードを選択することで、不揮発性記憶回路105に格納されたデータに応じた電位がフリップフロップ回路101へ入力される。したがって、ビット線(BIT)から入力された書き換えデータがフリップフロップ回路101へ入力される。

**【0041】**

本実施の形態の半導体装置は、ビット線(BIT)から不揮発性記憶回路105を介して直接、フリップフロップ回路101のデータの読み出し及び書き込みができるため、所望のタイミングでフリップフロップ回路101の内部状態を評価し、書き換えることができる。30

**【0042】**

続いて、選択回路103及び不揮発性記憶回路105のより具体的な回路について示したレジスタ回路200について説明する。レジスタ回路200について図1(B)に示す。

**【0043】**

図1(B)に示すように、選択回路103は第1のスイッチ202と第2のスイッチ203とを有する回路によって構成することができる。

**【0044】**

第1のスイッチ202はワード線(WORLD)及びライトイネーブル線(WE)と電気的に接続する。第1のスイッチ202の出力は不揮発性記憶回路105に入力される。第1のスイッチ202はワード線(WORLD)及びライトイネーブル線(WE)のどちらか一方の電位を不揮発性記憶回路105へ出力する切り替えスイッチである。40

**【0045】**

第2のスイッチ203はフリップフロップ回路101の出力端子及びビット線(BIT)と電気的に接続されている。第2のスイッチ203の出力は不揮発性記憶回路105に入力される。第2のスイッチ203はフリップフロップ回路101の内部状態に応じた電位及びビット線(BIT)の電位のどちらか一方を不揮発性記憶回路105へ出力する切り替えスイッチである。第2のスイッチ203は不揮発性記憶回路105と、フリップフロップ回路101またはビット線(BIT)との電気的接続を選択する。

**【0046】**

図1(B)に示す不揮発性記憶回路105は、トランジスタ204と容量素子205とを有している。トランジスタ204の第1の電極は容量素子205の一方の電極と電気的に接続し、容量素子205の他方の電極は接地されている。ここで、トランジスタ204の第1の電極と容量素子205の一方の電極とが接続されたノード(以下、単にノードとも表記する)にはデータが格納される。

#### 【0047】

トランジスタ204のゲート電極は選択回路103が備える第1のスイッチ202と電気的に接続し、ワード線(WORLD)またはライトイネーブル線(WE)の電位が入力される。つまり、ワード線(WORLD)またはライトイネーブル線(WE)の電位によってトランジスタ204のオン状態とオフ状態が切り替わる。

10

#### 【0048】

トランジスタ204の第2の電極は選択回路103が備える第2のスイッチ203と電気的に接続する。トランジスタ204がオン状態のとき、第2のスイッチ203からフリップフロップ回路101の内部状態に応じた電位またはビット線(BIT)の電位が入力され、トランジスタ204の第1の電極と、容量素子205の一方の電極と、が接続されるノードに格納される。

#### 【0049】

ここで、トランジスタ204はオフ電流が低減されたトランジスタを適用する。トランジスタ204にオフ電流が低減されたトランジスタを適用すると、トランジスタ204をオフ状態にすることによって、電力の供給が停止されてもノードに格納された電位を長時間にわたって保持させることができる。

20

#### 【0050】

不揮発性記憶回路105へのデータの書き込みは、例えば、容量素子205に異なる二つの電位に対応する電荷(以下、低電位を与える電荷を電荷 $Q_L$ 、高電位を与える電荷を電荷 $Q_H$ という)のいずれかを選択的に与えればよい。ここで、 $Q_L$ と $Q_H$ の一方をデータ“1”に対応させ、他方をデータ“0”に対応させることによって、不揮発性記憶回路105に1ビットの情報を書き込むことができる。なお、電荷を異なる三つまたはそれ以上の電位に対応する電荷のうちから選択することによって、不揮発性記憶回路105の記憶容量を向上させても良い。

#### 【0051】

30

なお、トランジスタ204に用いる、オフ電流が低減されたトランジスタとしては、例えば、酸化物半導体材料を用いたトランジスタ(酸化物半導体層にチャネルが形成されるトランジスタ)等を適用することができる。酸化物半導体材料を用いたトランジスタのオフ電流は、シリコンにチャネルが形成されるトランジスタの10万分の1以下であるため、トランジスタ204をオフ状態としたときに、トランジスタ204からのリークによって生じる、容量素子205に蓄積された電荷の消失を無視することが可能である。したがって、ノードに格納された電位を長時間にわたって保持することができる。なお、図面ではトランジスタ204が酸化物半導体を用いたトランジスタであることを示すために、OSの符号を付す。

#### 【0052】

40

不揮発性記憶回路105を上記の構成とすることで、新たなデータを書き込む場合に、書き込まれたデータを一度消去する必要がなく、再度のデータの書き込みによって直接データを書き換えることが可能である。このため消去動作に起因する動作速度の低下を抑制することができる。つまり半導体装置の高速動作が実現される。

#### 【0053】

また、開示する発明の半導体装置においては、従来のフローティングゲート型トランジスタにおいて指摘されているゲート絶縁層(トンネル絶縁層)の劣化という問題が存在しない。つまり、従来問題とされていた、電子をフローティングゲートに注入する際のゲート絶縁層の劣化という問題を解消できる。これは、原理的な書き込み回数の制限が存在しないことを意味するものである。また、従来のフローティングゲート型トランジスタにおい

50

て書き込みや消去の際に必要であった高電圧も不要である。

#### 【0054】

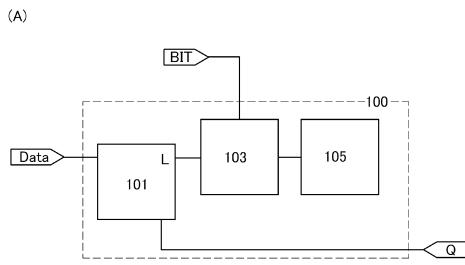

続いて、図1(B)に示すレジスタ回路200の動作について、タイミングチャートを用いて詳細に説明する。まず、図1(B)で示すレジスタ回路200の動作を説明するためには用いるフリップフロップ回路の具体的な回路構成について説明する。図2に、レジスタ回路200に用いるフリップフロップ回路101について示す。なお、本実施の形態の半導体装置に用いることのできるフリップフロップ回路は図2に示す構成に限らない。

#### 【0055】

図2に示すフリップフロップ回路101は、インバータ回路251、スイッチ回路252、インバータ回路253、クロックドインバータ回路254、クロックドインバータ回路255、スイッチ回路256、クロックドインバータ回路257、及びクロックドインバータ回路258を有する。10

#### 【0056】

フリップフロップ回路101にはデータ線(Data)の電位が入力される。データ線(Data)の電位は、スイッチ回路252を介して、クロックドインバータ回路254へ入力される。クロックドインバータ回路254によってデータ線(Data)の電位は反転され、信号線(L)及びスイッチ回路256へ入力される。なお、ここで信号線(L)に入力される電位をフリップフロップ回路101の内部状態として読み出す。スイッチ回路256に入力された電位は、クロックドインバータ回路257によって再び反転され、データ線(Data)の電位と等しい電位となって出力信号線(Q)から出力される。出力信号線(Q)の電位は、フリップフロップ回路101の出力電位であり、フリップフロップ回路101の内部状態の電位を反転した電位である。20

#### 【0057】

スイッチ回路252及びスイッチ回路256の導通状態を制御しているのはクロック信号(CLK)である。スイッチ回路252にはインバータ回路251によって反転されたクロック信号が入力され、スイッチ回路256にはクロック信号が直接入力されているため、スイッチ回路252及びスイッチ回路256は、どちらか一方のスイッチ回路が開いているとき、他方のスイッチ回路は閉じている。ここでは、クロック信号線(CLK)にロウレベルの電位が入力されたときに、スイッチ回路252が閉じ、反対にスイッチ回路256が開き、クロック信号線(CLK)にハイレベルの電位が入力されたとき、スイッチ回路252が開き、スイッチ回路256が閉じる構成とする。30

#### 【0058】

クロックドインバータ回路254の出力がクロックドインバータ回路255へ入力され、クロックドインバータ回路255の出力がクロックドインバータ回路254へ入力される帰還ループを有するラッチ回路を構成する。互いの出力が入力されることで、ラッチ回路によるデータの保持が行える。

#### 【0059】

なお、クロックドインバータ回路255にはクロック信号(CLK)が入力され、クロック信号(CLK)がハイレベルのときのみ動作を行う。したがって、クロック信号(CLK)としてハイレベルの電位が入力され、スイッチ回路252が開き、スイッチ回路256が閉じているとき、クロックドインバータ回路255が動作し、クロックドインバータ回路254及びクロックドインバータ回路255によるラッチ回路が電位を保持する。40

#### 【0060】

クロックドインバータ回路257の出力がクロックドインバータ回路258へ入力され、クロックドインバータ回路258の出力がクロックドインバータ回路257へ入力される帰還ループを有するラッチ回路を構成する。互いの出力が入力されることで、ラッチ回路はデータの保持を行っている。

#### 【0061】

なお、クロックドインバータ回路258にはインバータ回路251によって反転されたクロック信号が入力され、クロック信号がロウレベルのときのみ動作を行う。したがって、50

クロック信号（ C L K ）としてロウレベルの電位が入力され、スイッチ回路 2 5 2 が閉じ、スイッチ回路 2 5 6 が開いているときに、クロックドインバータ回路 2 5 8 が動作し、クロックドインバータ回路 2 5 7 及びクロックドインバータ回路 2 5 8 によるラッチ回路が動作して電位を保持する。

#### 【 0 0 6 2 】

また、クロックドインバータ回路 2 5 4 には、インバータ回路 2 5 3 を介してリードイネーブル線（ R E ）の電位が入力される。リードイネーブル線（ R E ）にハイレベルの電位が入力されると、クロックドインバータ回路 2 5 4 にはインバータ回路 2 5 3 によって反転されたロウレベルの電位が入力され、クロックドインバータ回路 2 5 4 は動作を停止する。したがって、リードイネーブル線（ R E ）にハイレベルの電位が入力されている間は、クロックドインバータ回路 2 5 4 及びクロックドインバータ回路 2 5 5 によるラッチ回路がデータを保持することはない。10

#### 【 0 0 6 3 】

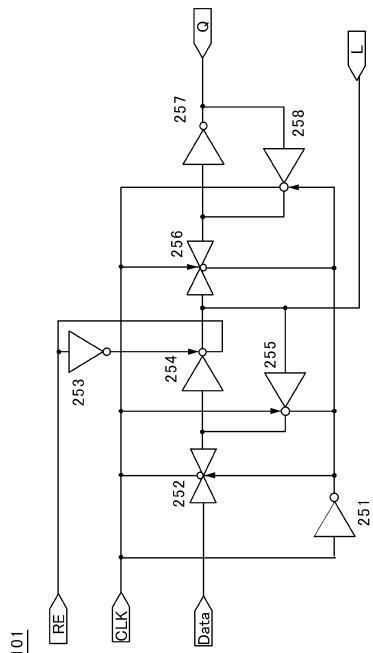

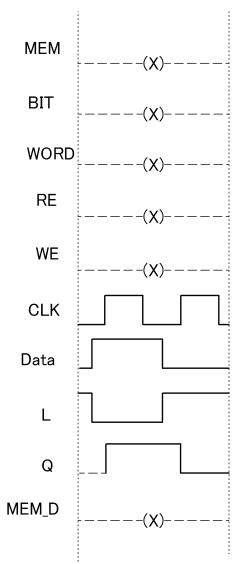

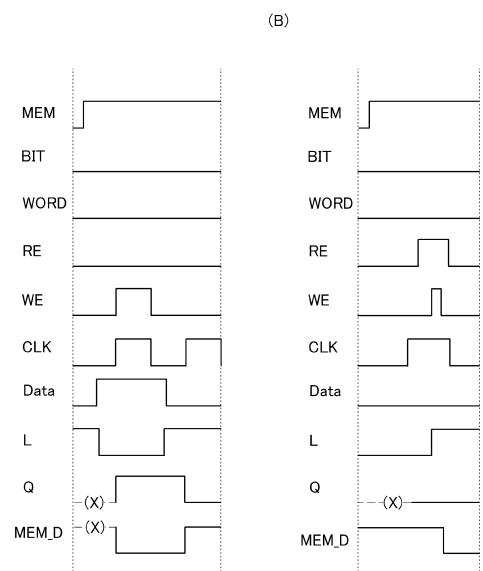

以上が図 2 に示すフリップフロップ回路 1 0 1 の構成及び動作である。続いて、図 1 ( B ) のレジスタ回路 2 0 0 の動作について示す。なお、ここでは、フリップフロップ回路 1 0 1 として、図 2 に示すフリップフロップ回路 1 0 1 が適用された場合を示す。図 3 乃至図 5 にレジスタ回路 2 0 0 のタイミングチャートを示す。

#### 【 0 0 6 4 】

なお、図 3 乃至図 5 に示すタイミングチャートにおいて、 M E M は選択信号線を、 B I T はビット線を、 W O R D はワード線を、 R E はリードイネーブル線を、 W E はライトイネーブル線を、 C L K はクロック信号を、 D a t a はデータ線を、 L は信号線を、 Q はフリップフロップ回路の出力信号線を、 M E M \_ D は不揮発性記憶回路 1 0 5 に格納されているデータ（不揮発性記憶回路 1 0 5 のノードに保持されているデータ）の電位をそれぞれ示している。20

#### 【 0 0 6 5 】

はじめに、レジスタ回路がフリップフロップ回路の通常動作を行う時のタイミングチャートについて説明する。図 3 に示すタイミングチャートは、フリップフロップ回路の通常動作を示している。フリップフロップ回路の通常動作時において、選択回路 1 0 3 はいずれの動作モードを選択していてもよい。したがって、選択信号線（ M E M ）、ビット線（ B I T ）、ワード線（ W O R D ）、リードイネーブル線（ R E ）、ライトイネーブル線（ W E ）の電位は任意の電位とすることができます。タイミングチャートでは、任意の電位を波線で示し、（ X ）の記号を付す。30

#### 【 0 0 6 6 】

フリップフロップ回路 1 0 1 はクロック信号（ C L K ）がロウレベルのとき、スイッチ回路 2 5 2 が閉じ、データ線（ D a t a ）の電位に応じたデータがクロックドインバータ回路 2 5 4 に入力される。クロックドインバータ回路 2 5 4 によってデータ線（ D a t a ）の電位に応じたデータは反転し、信号線（ L ）に送られる。続いて、クロック信号（ C L K ）がハイレベルとなると、スイッチ回路 2 5 2 は開かれ、クロックドインバータ回路 2 5 5 が動作を行い、クロックドインバータ回路 2 5 4 とクロックドインバータ回路 2 5 5 によるラッチ回路によって、信号線（ L ）の電位が保持される。40

#### 【 0 0 6 7 】

また、クロック信号（ C L K ）がハイレベルになるとスイッチ回路 2 5 6 が閉じ、クロックドインバータ回路 2 5 4 によって反転されたデータがクロックドインバータ回路 2 5 7 に入力される。クロックドインバータ回路 2 5 7 に反転されたデータが入力されると、クロックドインバータ回路 2 5 7 によって再び反転され、フリップフロップ回路 1 0 1 の出力信号線（ Q ）から出力する。

#### 【 0 0 6 8 】

続いて、クロック信号（ C L K ）がロウレベルになると、スイッチ回路 2 5 6 は開かれ、クロックドインバータ回路 2 5 8 が動作し、クロックドインバータ回路 2 5 7 とクロックドインバータ回路 2 5 8 によって構成されるラッチ回路によって、フリップフロップ回路50

の出力信号線( Q )の電位は保持される。

**【 0 0 6 9 】**

次に、選択回路 103 が第 1 の動作モードにおいて、不揮発性記憶回路 105 にフリップフロップ回路 101 を介してデータ線( Data )の電位に応じたデータを格納する動作について説明する。

**【 0 0 7 0 】**

図 4 ( A ) に、第 1 の動作モードのタイミングチャートを示した。選択回路 103 が第 1 の動作モードを選択するには、選択信号線( MEM )の電位をハイレベルとする。選択信号線( MEM )をハイレベルとしたことで、第 1 のスイッチ 202 を介してトランジスタ 204 のゲート電極とライトイネーブル線( WE )が電気的に接続する。また、第 2 のスイッチ 203 を介して、フリップフロップ回路 101 の出力端子とトランジスタ 204 の第 2 の電極が電気的に接続する。

10

**【 0 0 7 1 】**

選択回路 103 が第 1 の動作モードを選択した状態で、クロック信号( CLK )にロウレベルが入力されると、データ線( Data )の電位がクロックドインバータ回路 254 によって反転し、信号線( L )に入力される。続いて、クロック信号( CLK )がハイレベルとなると、スイッチ回路 252 は開かれ、クロックドインバータ回路 254 とクロックドインバータ回路 255 によって、信号線( L )の電位が保持される。さらに、スイッチ回路 256 が閉じられ、クロックドインバータ回路 257 によって信号線( L )の電位が反転した電位( Data 線の電位)が出力信号線( Q )に出力される。

20

**【 0 0 7 2 】**

ここで、ライトイネーブル線( WE )をハイレベルにすることで、トランジスタ 204 のゲート電極にハイレベルの電位が入力され、トランジスタ 204 がオン状態となる。これにより、フリップフロップ回路 101 の内部状態が不揮発性記憶回路 105 のノードに格納される。その後、ライトイネーブル線( WE )をロウレベルとすることで、トランジスタ 204 がオフ状態となる。トランジスタ 204 はオフ電流が極めて小さいため、トランジスタ 204 をオフ状態とすることで、ノードに格納された電位を極めて長時間にわたって保持することが可能となる。

**【 0 0 7 3 】**

上記の動作によって、フリップフロップ回路 101 の内部状態を不揮発性記憶回路 105 に格納させることができるため、半導体装置は電力の供給が停止されても、フリップフロップ回路 101 の内部状態を保持することが可能となる。

30

**【 0 0 7 4 】**

本実施の形態の半導体装置は、フリップフロップ回路毎に、電力の供給を停止してもデータを保持できる不揮発性記憶回路が設けられているため、フリップフロップ回路の内部状態が変化しないときには電力の供給を停止し、消費電力を低減することができる。

**【 0 0 7 5 】**

次に、選択回路 103 が第 2 の動作モードにおいて、不揮発性記憶回路 105 に格納されているデータをフリップフロップ回路 101 へ入力する動作について説明する。図 4 ( B ) に第 2 の動作モードのタイミングチャートについて示す。

40

**【 0 0 7 6 】**

選択回路 103 が第 2 の動作モードを選択するには、選択信号線( MEM )の電位をハイレベルとする。選択信号線( MEM )をハイレベルとしたことで、第 1 のスイッチ 202 を介してトランジスタ 204 のゲート電極とライトイネーブル線( WE )が電気的に接続する。また、第 2 のスイッチ 203 を介してフリップフロップ回路 101 の出力端子とトランジスタ 204 の第 2 の電極が電気的に接続する。

**【 0 0 7 7 】**

第 2 の動作モードにおいて、クロック信号( CLK )がロウレベルのとき、データ線( Data )の電位がクロックドインバータ回路 254 に入力され、信号線( L )にデータ線( Data )の電位を反転した電位が入力されている。

50

## 【0078】

ここでクロック信号（C L K）がハイレベルとなると、クロックドインバータ回路254及びクロックドインバータ回路255によるラッチ回路が動作し、信号線（L）の電位が保持される。また、スイッチ回路256が閉じ、クロックドインバータ回路254によって反転されたデータがクロックドインバータ回路257に入力される。クロックドインバータ回路257に入力されたデータは、クロックドインバータ回路257によって反転され、フリップフロップ回路101の出力端子から出力される。

## 【0079】

このとき、リードイネーブル線（R E）をハイレベルとすると、クロックドインバータ回路254の動作が停止し、クロックドインバータ回路254とクロックドインバータ回路255によるラッチ回路は動作を停止する。10

## 【0080】

クロックドインバータ回路254及びクロックドインバータ回路255によるラッチ回路が動作を停止している間に、ライトイネーブル線（W E）をハイレベルとしてトランジスタ204をオン状態とすると、トランジスタ204と容量素子205によるノードに格納されていた電位（M E M \_ D）が信号線（L）を通じてクロックドインバータ回路255に入力される。

## 【0081】

この後、ライトイネーブル線（W E）をロウレベルに戻しても、信号線（L）にはノードに格納されていた電位が保持される。したがって、リードイネーブル線（R E）をロウレベルとし、クロックドインバータ回路254が動作を再開して、クロックドインバータ回路254及びクロックドインバータ回路255により構成されるラッチ回路が動作を再開すると、該ラッチ回路によって、ノードに格納されていた電位が保持される。20

## 【0082】

その後、クロック信号（C L K）がロウレベルとなると、スイッチ回路252が閉じ、データ線（D a t a）の電位がクロックドインバータ回路254に入力され、フリップフロップ回路101が再び、通常動作を再開する。

## 【0083】

なお、本実施の形態で示す半導体装置では、トランジスタ204に酸化物半導体材料を用いたトランジスタ（酸化物半導体層にチャネルが形成されるトランジスタ）が適用されている。酸化物半導体材料を用いたトランジスタはオフ電流が極めて小さいという特徴を有している。このため、トランジスタ204をオフ状態とすることで、容量素子205の電位を極めて長時間にわたって保持することが可能となる。30

## 【0084】

続いて、選択回路103が第3の動作モードにおいて、不揮発性記憶回路105にピット線（B I T）の電位に応じたデータを格納する動作について説明する。

## 【0085】

図5（A）に第3の動作モードについて示す。選択回路103が第3の動作モードを選択するためには、選択信号線（M E M）をロウレベルとする。選択信号線（M E M）をロウレベルとしたことで、第1のスイッチ202を介してトランジスタ204のゲート電極とワード線（W O R D）が電気的に接続する。また、第2のスイッチ203を介してピット線（B I T）とトランジスタ204の第2の電極が電気的に接続する。40

## 【0086】

なお、第3の動作モードにおいて、リードイネーブル線（R E）、クロック信号（C L K）、データ線（D a t a）、信号線（L）、フリップフロップ回路の出力は、任意の電位とすることができます。

## 【0087】

第3の動作モードにおいて、ワード線（W O R D）をハイレベルにすることで、トランジスタ204がオン状態となり、ピット線（B I T）の電位に応じた電位がトランジスタ204の第1の電極と、容量素子205の一方の電極と、が接続されたノードに格納される50

。ビット線（BIT）に不揮発性記憶回路105へ格納する電位を入力するタイミングは、ワード線（WORD）がハイレベルとなり、ビット線（BIT）の電位がノードに入力されるよりも前である。

#### 【0088】

続いて、選択回路103が第4の動作モードにおいて、ビット線（BIT）に不揮発性記憶回路105に格納された電位を入力する動作について説明する。図5（B）に第4の動作モードについて示す。選択回路103が第4のモードを選択するためには、選択信号線（MEM）をロウレベルとする。選択信号線（MEM）がロウレベルとなつたことで、第1のスイッチ202を介してトランジスタ204のゲート電極とワード線が電気的に接続する。また、第2のスイッチ203を介してビット線（BIT）とトランジスタ204の第2の電極が電気的に接続する。10

#### 【0089】

第4の動作モードにおいて、ビット線（BIT）にミドルレベルの電位を入力する。続いて、ワード線（WORD）をハイレベルとすることで、トランジスタ204がオン状態となり、トランジスタ204及び容量素子205によって形成されるノードに格納されている電位がビット線（BIT）に入力される。このとき、トランジスタ204及び容量素子205に格納されている電位がハイレベルの場合、ミドルレベルであったビット線（BIT）の電位がハイレベルへ上昇する。また、トランジスタ204及び容量素子205に格納されている電位がロウレベルの場合、ビット線（BIT）の電位は上昇しない。20

#### 【0090】

したがって、ビット線（BIT）の電位を判別することで、不揮発性記憶回路105に格納されていた電位を読み出すことができる。電位の読み出しとしては、例えば、ビット線（BIT）の先にレベルシフタを接続しておくと、ハイレベルの電位と近くなつたビット線（BIT）の状態をハイレベルへ確定することができ、完全な読み出しが可能となる。20

#### 【0091】

これら、4つの動作モードを任意に組み合わせることで、フリップフロップ回路の内部状態が変化しないときには電力の供給を停止し、消費電力を低減することができる。また、不揮発性記憶回路の電位をレジスタ回路外部から直接読み出すことでフリップフロップ回路の内部状態を所望のタイミングで評価することができる。また、フリップフロップ回路の内部状態を容易に書き換えることができる。30

#### 【0092】

##### <応用例>

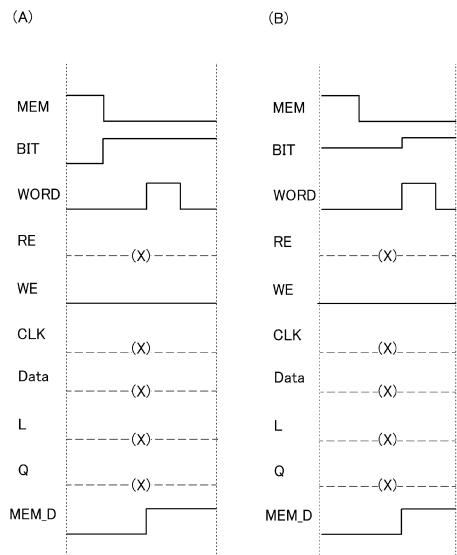

続いて、上記のレジスタ回路を複数有する半導体装置及びその動作について説明する。図6に示す本発明の一態様の半導体装置は、上記のレジスタ回路を複数有し、該レジスタ回路がマトリクス状に設けられている。

#### 【0093】

図6の半導体装置は、縦m個（行）×横n個（列）のマトリクス状に配置されたレジスタ回路と、n本のビット線と、m本のワード線と、メモリコントローラ（MEMORY CONTROLLER）と、ビット列デコーダ（BIT COLUMN DECODER）と、ワード行デコーダ（WORD ROW DECODER）と、コア（CORE IO）を有する。40

#### 【0094】

図6中のレジスタ回路は、図1（B）に示すレジスタ回路100と同様の構成である。つまり、個々のレジスタ回路に注目すると、フリップフロップ回路と、選択回路と、不揮発性記憶回路と、を有している。さらに、各選択回路は第1のスイッチ及び第2のスイッチを有し、各不揮発性記憶回路は、オフ電流の低いトランジスタ（例えば、酸化物半導体を含んで構成されるトランジスタ）及び容量素子を有する。また、各レジスタ回路は、選択回路と電気的に接続するビット線を各列に共通して用い、ワード線を各行で共通して用いている。

#### 【0095】

10

20

30

40

50

本実施の形態では、複数のレジスタ回路が有する不揮発性記憶回路同士が直列には接続されず、それぞれビット線及びワード線と接続されている構成としたが、レジスタ回路をマトリクス状に配置する方法はこれに限らない。

#### 【 0 0 9 6 】

なお、ライトイネーブル線（WE）、選択信号線（MEM）、データ線（Data）、クロック信号線（CLK）等については、図1（B）と同様の構成とすることができますため、図6においては省略する。

#### 【 0 0 9 7 】

$n$ 本のビット線は、ビット列デコーダと電気的に接続し、第 $k$ 列目のビット線（ $k$ は1以上 $n$ 以下の整数）は第 $k$ 列目のレジスタ回路が有する選択回路の第2のスイッチと電気的に接続している。

10

#### 【 0 0 9 8 】

また、 $m$ 本のワード線はワード行デコーダと電気的に接続し、第 $q$ 行目のワード線（ $q$ は1以上 $m$ 以下の整数）は第 $q$ 行目のレジスタ回路が有する選択回路の第1のスイッチと電気的に接続している。

#### 【 0 0 9 9 】

コアの内部状態や演算結果に応じてメモリコントローラがどのレジスタ回路に対して、データの読み出し及び書き込みを行うかを決定する。例えば、メモリコントローラが書き込みを行うレジスタ回路を決定すると、選択回路が第3の動作モードを選択し、メモリコントローラからビット列デコーダ及びワード行デコーダに所定の電位が入力される。

20

#### 【 0 1 0 0 】

例えば、ワード行デコーダに対しては、読み出しまだ書き込みを行うレジスタ回路のアドレス情報が送られる。すると、ワード行デコーダがアドレス情報に応じて、各ワード線に所定の電位を入力し、読み出しまだ書き込みを行うレジスタ回路をアクティブ状態とする。

#### 【 0 1 0 1 】

また、ビット列デコーダに対しては、レジスタ回路に書き込むデータが送られる。すると、ビット列デコーダから、各ビット線に書き込むデータに応じた電位が入力される。ワード行デコーダによって、アクティブになったレジスタ回路には、ビット列デコーダからの電位が格納される。

30

#### 【 0 1 0 2 】

レジスタ回路が有する、フリップフロップ回路の入力端子及び出力端子には、論理演算回路、またはメインメモリ等が接続されており、マトリクス状に配置されたフリップフロップ回路全体で信号処理回路を構成している。信号処理回路において、フリップフロップ回路は演算処理や、プログラムの実行状態を一時的に保持する役割を担っている。

#### 【 0 1 0 3 】

本発明の半導体装置は、フリップフロップ回路毎に、不揮発性記憶回路が設けられているため、レジスタ回路を複数有する構成としても、高速にデータを読み出すことができる。また、不揮発性記憶回路と直接データの読み出しまだ書き込みができるため、信号処理回路の内部状態を容易に評価、書き換えることができる。

40

#### 【 0 1 0 4 】

本実施の形態は、他の実施の形態と適宜組み合わせることができる。

#### 【 0 1 0 5 】

##### (実施の形態2)

実施の形態1に示した、不揮発性記憶回路が含む、オフ電流の低減されたトランジスタについて説明する。オフ電流の小さいトランジスタとしては、酸化物半導体材料を用いたトランジスタがあげられる。

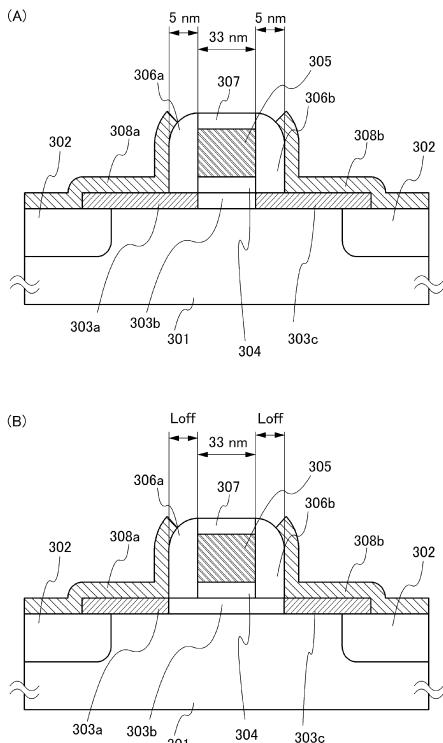

#### 【 0 1 0 6 】

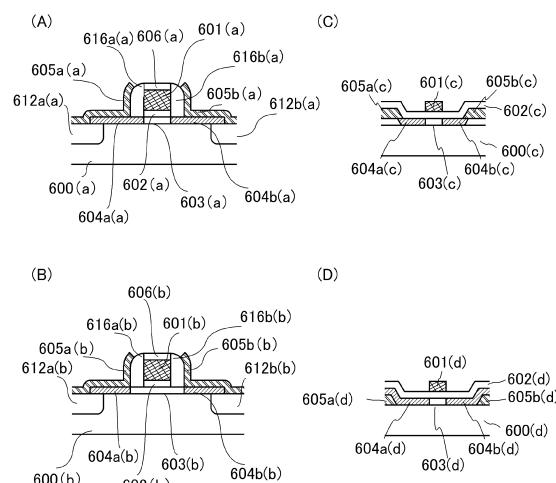

本実施の形態で示すトランジスタの構造について、図23（A）～（D）を参照して説明する。なお、図23（A）～（D）は、トランジスタの構造例を示す断面模式図である。

50

**【0107】**

図23(A)に示すトランジスタは絶縁層600(a)と、絶縁層600(a)に埋め込まれるように形成された埋め込み絶縁物612a(a)及び埋め込み絶縁物612b(a)との上に形成される。

**【0108】**

図23(A)に示すトランジスタは、ゲート電極601(a)と、ゲート絶縁層602(a)と、酸化物半導体層603(a)と、ソース電極605a(a)と、ドレイン電極605b(a)と、を含んでいる。

**【0109】**

酸化物半導体層603(a)は、不純物領域604a(a)及び不純物領域604b(a)を含んでいる。不純物領域604a(a)及び不純物領域604b(a)は、互いに離間し、それぞれドーパント(不純物)が添加された領域である。なお、不純物領域604a(a)及び不純物領域604b(a)の間の領域がチャネル形成領域になる。酸化物半導体層603(a)は、絶縁層600(a)の上に設けられる。なお、必ずしも不純物領域604a(a)及び不純物領域604b(a)を設けなくてもよい。なお、図23(A)に示すトランジスタにおいて、不純物領域604a(a)及び不純物領域604b(a)はn<sup>+</sup>の導電型を呈する半導体領域である。

**【0110】**

また、ゲート電極601(a)の両側面には側壁絶縁物616a(a)および側壁絶縁物616b(a)、ゲート電極601(a)の上部には、ゲート電極601(a)と他の配線との短絡を防止するための絶縁層606(a)を有する。

**【0111】**

ソース電極605a(a)及びドレイン電極605b(a)は、酸化物半導体層603(a)の上に設けられ、酸化物半導体層603(a)に電気的に接続されている。

**【0112】**

また、ソース電極605a(a)は、不純物領域604a(a)の一部に重畠する。ソース電極605a(a)を不純物領域604a(a)の一部に重畠させることにより、ソース電極605a(a)及び不純物領域604a(a)の間の抵抗値を小さくすることができる。

**【0113】**

また、ドレイン電極605b(a)は、不純物領域604b(a)の一部に重畠する。ドレイン電極605b(a)を不純物領域604b(a)の一部に重畠させることにより、ドレイン電極605b(a)及び不純物領域604b(a)の間の抵抗を小さくすることができる。

**【0114】**

ゲート絶縁層602(a)は、酸化物半導体層603(a)の上に設けられている。

**【0115】**

ゲート電極601(a)は、ゲート絶縁層602(a)を介して酸化物半導体層603(a)に重畠する。ゲート絶縁層602(a)を介してゲート電極601(a)と重畠する酸化物半導体層603(a)の領域がチャネル形成領域になる。

**【0116】**

図23(B)に示すトランジスタは絶縁層600(b)と、絶縁層600(b)に埋め込まれるように形成された埋め込み絶縁物612a(b)及び埋め込み絶縁物612b(b)との上に形成される。

**【0117】**

図23(B)に示すトランジスタは、ゲート電極601(b)と、ゲート絶縁層602(b)と、酸化物半導体層603(b)と、ソース電極605a(b)と、ドレイン電極605b(b)と、を含んでいる。

**【0118】**

酸化物半導体層603(b)は、不純物領域604a(b)及び不純物領域604b(b)

10

20

30

40

50

)を含んでいる。不純物領域 604a(b) 及び不純物領域 604b(b) は、互いに離間し、それぞれドーパント(不純物)が添加された領域である。なお、不純物領域 604a(b) 及び不純物領域 604b(b) の間の領域がチャネル形成領域になる。酸化物半導体層 603(b) は、絶縁層 600(b) の上に設けられる。なお、必ずしも不純物領域 604a(b) 及び不純物領域 604b(b) を設けなくてもよい。なお、図 23(B) に示すトランジスタにおいて、不純物領域 604a(b) 及び不純物領域 604b(b) は  $n^+$  の導電型を呈する半導体領域である。

#### 【0119】

また、ゲート電極 601(b) の両側面には側壁絶縁物 616a(b) および側壁絶縁物 616b(b)、ゲート電極 601(b) の上部には、ゲート電極 601(b) と他の配線との短絡を防止するための絶縁層 606(b) を有する。

10

#### 【0120】

ソース電極 605a(b) 及びドレイン電極 605b(b) は、酸化物半導体層 603(b) の上に設けられ、酸化物半導体層 603(b) に電気的に接続されている。

#### 【0121】

また、ソース電極 605a(b) は、不純物領域 604a(b) に重畠する。ソース電極 605a(b) を不純物領域 604a(b) に重畠させることにより、ソース電極 605a(b) 及び不純物領域 604a(b) の間の抵抗値を小さくすることができる。

#### 【0122】

また、ドレイン電極 605b(b) は、不純物領域 604b(b) に重畠する。ドレイン電極 605b(b) を不純物領域 604b(b) に重畠させることにより、ドレイン電極 605b(b) 及び不純物領域 604b(b) の間の抵抗を小さくすることができる。

20

#### 【0123】

ゲート絶縁層 602(b) は、酸化物半導体層 603(b) の上に設けられている。

#### 【0124】

ゲート電極 601(b) は、ゲート絶縁層 602(b) を介して酸化物半導体層 603(b) に重畠する。ゲート絶縁層 602(b) を介してゲート電極 601(b) と重畠する酸化物半導体層 603(b) の領域がチャネル形成領域になる。

#### 【0125】

図 23(A) に示すトランジスタでは、不純物領域 604a(a) 及び不純物領域 604b(a) は側壁絶縁物 616a(a) および側壁絶縁物 616b(a) と重畠して設けられている。一方、図 23(B) に示すトランジスタでは、不純物領域 604a(b) 及び不純物領域 604b(b) は側壁絶縁物 616a(b) および側壁絶縁物 616b(b) と重畠して設けられていない。

30

#### 【0126】

図 23(C) に示すトランジスタは、ゲート電極 601(c) と、ゲート絶縁層 602(c) と、酸化物半導体層 603(c) と、ソース電極 605a(c) と、ドレイン電極 605b(c) と、を含んでいる。

#### 【0127】

酸化物半導体層 603(c) は、不純物領域 604a(c) 及び不純物領域 604b(c) を含んでいる。不純物領域 604a(c) 及び不純物領域 604b(c) は、互いに離間し、それぞれドーパント(不純物)が添加された領域である。なお、不純物領域 604a(c) 及び不純物領域 604b(c) の間の領域がチャネル形成領域になる。酸化物半導体層 603(c) は、絶縁層 600(c) の上に設けられる。なお、必ずしも不純物領域 604a(c) 及び不純物領域 604b(c) を設けなくてもよい。

40

#### 【0128】

ソース電極 605a(c) 及びドレイン電極 605b(c) は、酸化物半導体層 603(c) の上に設けられ、酸化物半導体層 603(c) に電気的に接続されている。また、ソース電極 605a(c) 及びドレイン電極 605b(c) の側面は、テーパ状である。

#### 【0129】

50

また、ソース電極 605a(c) は、不純物領域 604a(c) の一部に重畠するが、必ずしもこれに限定されない。ソース電極 605a(c) を不純物領域 604a(c) の一部に重畠させることにより、ソース電極 605a(c) 及び不純物領域 604a(c) の間の抵抗値を小さくすることができる。また、ソース電極 605a(c) に重畠する酸化物半導体層 603(c) の領域の全てが不純物領域 604a(c) でもよい。

#### 【0130】

また、ドレイン電極 605b(c) は、不純物領域 604b(c) の一部に重畠するが、必ずしもこれに限定されない。ドレイン電極 605b(c) を不純物領域 604b(c) の一部に重畠させることにより、ドレイン電極 605b(c) 及び不純物領域 604b(c) の間の抵抗を小さくすることができる。また、ドレイン電極 605b(c) に重畠する酸化物半導体層 603(c) の領域の全てが不純物領域 604b(c) でもよい。10

#### 【0131】

ゲート絶縁層 602(c) は、酸化物半導体層 603(c)、ソース電極 605a(c) 及びドレイン電極 605b(c) の上に設けられている。

#### 【0132】

ゲート電極 601(c) は、ゲート絶縁層 602(c) を介して酸化物半導体層 603(c) に重畠する。ゲート絶縁層 602(c) を介してゲート電極 601(c) と重畠する酸化物半導体層 603(c) の領域がチャネルになる。

#### 【0133】

また、図 23(D) に示すトランジスタは、ゲート電極 601(d) と、ゲート絶縁層 602(d) と、酸化物半導体層 603(d) と、ソース電極 605a(d) と、ドレイン電極 605b(d) と、を含んでいる。20

#### 【0134】

ソース電極 605a(d) 及びドレイン電極 605b(d) は、絶縁層 600(d) の上に設けられる。また、ソース電極 605a(d) 及びドレイン電極 605b(d) の側面は、テーパ状である。

#### 【0135】

酸化物半導体層 603(d) は、不純物領域 604a(d) 及び不純物領域 604b(d) と、を含んでいる。不純物領域 604a(d) 及び不純物領域 604b(d) は、互いに離間し、それぞれドーパントが添加された領域である。また、不純物領域 604a(d) 及び不純物領域 604b(d) の間の領域がチャネル形成領域になる。酸化物半導体層 603(d) は、例えばソース電極 605a(d)、ドレイン電極 605b(d)、及び絶縁層 600(d) の上に設けられ、ソース電極 605a(d) 及びドレイン電極 605b(d) に電気的に接続される。なお、必ずしも不純物領域 604a(d) 及び不純物領域 604b(d) を設けなくてもよい。30

#### 【0136】

不純物領域 604a(d) は、ソース電極 605a(d) に電気的に接続されている。

#### 【0137】

不純物領域 604b(d) は、ドレイン電極 605b(d) に電気的に接続されている。

#### 【0138】

ゲート絶縁層 602(d) は、酸化物半導体層 603(d) の上に設けられている。40

#### 【0139】

ゲート電極 601(d) は、ゲート絶縁層 602(d) を介して酸化物半導体層 603(d) に重畠する。ゲート絶縁層 602(d) を介してゲート電極 601(d) と重畠する酸化物半導体層 603(d) の領域がチャネル形成領域になる。

#### 【0140】

さらに、図 23(A) 乃至図 23(D) に示す各構成要素について説明する。

#### 【0141】

絶縁層 600(a) 乃至絶縁層 600(d) としては、例えば、絶縁性酸化物、または絶縁表面を有する基板などを用いることができる。また、予め素子が形成された層を絶縁層50

600 (a) 乃至絶縁層600 (d) として用いることもできる。

**【0142】**

ゲート電極601 (a) 乃至ゲート電極601 (d) のそれぞれは、トランジスタのゲートとしての機能を有する。なお、トランジスタのゲートとしての機能を有する層をゲート配線ともいう。

**【0143】**

ゲート電極601 (a) 乃至ゲート電極601 (d) としては、例えばモリブデン、マグネシウム、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、若しくはスカンジウムなどの金属材料、又はこれらを主成分とする合金材料の層を用いることができる。また、ゲート電極601 (a) 乃至ゲート電極601 (d) の形成に適用可能な材料の層の積層により、ゲート電極601 (a) 乃至ゲート電極601 (d) を構成することもできる。10

**【0144】**

ゲート絶縁層602 (a) 乃至ゲート絶縁層602 (d) としては、例えば酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、酸化ハフニウム層、又は酸化ランタン層を用いることができる。また、ゲート絶縁層602 (a) 乃至ゲート絶縁層602 (d) に適用可能な材料の層の積層によりゲート絶縁層602 (a) 乃至ゲート絶縁層602 (d) を構成することもできる。20

**【0145】**

また、ゲート絶縁層602 (a) 乃至ゲート絶縁層602 (d) としては、例えば元素周期表における第13族元素及び酸素元素を含む材料の絶縁層を用いることができる。例えば、酸化物半導体層603 (a) 乃至酸化物半導体層603 (d) が第13族元素を含む場合に、酸化物半導体層603 (a) 乃至酸化物半導体層603 (d) に接する絶縁層として第13族元素を含む絶縁層を用いることにより、該絶縁層と酸化物半導体層との界面の状態を良好にすることもできる。20

**【0146】**

第13族元素及び酸素元素を含む材料としては、例えば酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、酸化ガリウムアルミニウムなどが挙げられる。なお、酸化アルミニウムガリウムとは、ガリウムの含有量(原子%)よりアルミニウムの含有量(原子%)が多い物質のことをいい、酸化ガリウムアルミニウムとは、ガリウムの含有量(原子%)がアルミニウムの含有量(原子%)以上の物質のことをいう。例えば、 $A_{1-x}O_x$  ( $x = 3+$ 、 $x$ は0以上1未満)、 $Ga_2O_x$  ( $x = 3+$ 、 $x$ は0以上1未満)、又は $Ga_xA_{1-x}O_{3+x}$  ( $x$ は0より大きく2より小さい値、 $x$ は0より大きく1より小さい値)で表記される材料を用いることもできる。30

**【0147】**

また、ゲート絶縁層602 (a) 乃至ゲート絶縁層602 (d) に適用可能な材料の層の積層によりゲート絶縁層602 (a) 乃至ゲート絶縁層602 (d) を構成することもできる。例えば、複数の $Ga_2O_x$ で表記される酸化ガリウムを含む層の積層によりゲート絶縁層602 (a) 乃至ゲート絶縁層602 (d) を構成してもよい。また、 $Ga_2O_x$ で表記される酸化ガリウムを含む絶縁層及び $A_{1-x}O_x$ で表記される酸化アルミニウムを含む絶縁層の積層によりゲート絶縁層602 (a) 乃至ゲート絶縁層602 (d) を構成してもよい。40

**【0148】**

ゲート絶縁層602 (a) 乃至ゲート絶縁層602 (d) は、少なくとも酸化物半導体層に接する部分に酸素を含み、酸素の一部が加熱により脱離する絶縁性酸化物により形成することが好ましい。ゲート絶縁層602 (a) 乃至ゲート絶縁層602 (d) の酸化物半導体層と接する部分を酸化シリコンにより形成すると、酸化物半導体層に酸素を拡散させることができ、トランジスタの低抵抗化を防止することができる。

**【0149】**

10

20

30

40

50

なお、ゲート絶縁層 602 (a) 乃至ゲート絶縁層 602 (d) として、ハフニウムシリケート ( $HfSiO_x$ )、窒素が添加されたハフニウムシリケート ( $HfSi_xOyNz$ )、窒素が添加されたハフニウムアルミネート ( $HfAl_xOyNz$ )、酸化ハフニウム、酸化イットリウムまたは酸化ランタンなどの  $h_ig_{h-k}$  材料を用いると、ゲートトリーク電流を低減することができる。ここで、ゲートトリーク電流とは、ゲート電極とソース電極またはドレイン電極の間に流れるリーク電流をいう。さらには、前記  $h_ig_{h-k}$  材料により形成される層と、酸化シリコン、酸化窒化シリコン、窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化窒化アルミニウム及び酸化ガリウムにより形成される層が積層されていてもよい。ただし、ゲート絶縁層 602 (a) 乃至ゲート絶縁層 602 (d) を積層構造とする場合であっても、酸化物半導体層に接する部分は、絶縁性酸化物であることが好ましい。

#### 【0150】

また、トランジスタのチャネル長を 30 nm としたとき、酸化物半導体層 603 (a) 乃至酸化物半導体層 603 (d) の厚さを例えば 5 nm 程度にしてもよい。このとき、酸化物半導体層 603 (a) 乃至酸化物半導体層 603 (d) が CAC-O<sub>5</sub> 膜（後述）の酸化物半導体層であれば、トランジスタにおける短チャネル効果を抑制することができる。

#### 【0151】

不純物領域 604a (a) 乃至不純物領域 604a (d) 及び不純物領域 604b (a) 乃至不純物領域 604b (d) は、N 型又は P 型の導電型を付与するドーパント（不純物）が添加され、トランジスタのソース領域又はドレイン領域としての機能を有する。

#### 【0152】

ドーパントとしては、例えば元素周期表における 13 族の元素（例えば硼素など）、元素周期表における 15 族の元素（例えば窒素、リン、及び砒素の一つ又は複数）、及び希ガス元素（例えばヘリウム、アルゴン、及びキセノンの一つ又は複数）の一つ又は複数を用いることができる。

#### 【0153】

ここで、ドーパントの添加は、イオンインプランテーション法またはイオンドーピング法により行えばよい。または、ドーパントを含むガス雰囲気中でプラズマ処理を行うことでドーパントの添加を行ってもよい。

#### 【0154】

不純物領域 604a (a) 乃至不純物領域 604a (d) 及び不純物領域 604b (a) 乃至不純物領域 604b (d) にドーパントを添加することによりソース電極またはドレイン電極との接続抵抗を小さくすることができるため、トランジスタを微細化することができる。

#### 【0155】

ソース電極 605a (a) 乃至ソース電極 605a (d)、及びドレイン電極 605b (a) 乃至ドレイン電極 605b (d) のそれぞれは、トランジスタのソース又はドレインとしての機能を有する。なお、トランジスタのソースとしての機能を有する層をソース電極又はソース配線ともいい、トランジスタのドレインとしての機能を有する層をドレイン電極又はドレイン配線ともいう。

#### 【0156】

ソース電極 605a (a) 乃至ソース電極 605a (d)、及びドレイン電極 605b (a) 乃至ドレイン電極 605b (d) としては、例えばアルミニウム、マグネシウム、クロム、銅、タンタル、チタン、モリブデン、若しくはタングステンなどの金属材料、又はこれらの金属材料を主成分とする合金を用いることができる。例えば、銅、マグネシウム、及びアルミニウムを含む合金材料の層により、ソース電極 605a (a) 乃至ソース電極 605a (d)、及びドレイン電極 605b (a) 乃至ドレイン電極 605b (d) を構成することができる。また、ソース電極 605a (a) 乃至ソース電極 605a (d)、及びドレイン電極 605b (a) 乃至ドレイン電極 605b (d) に適用可能な材料の

10

20

30

40

50

層の積層により、ソース電極 605a(a)乃至ソース電極 605a(d)、及びドレイン電極 605b(a)乃至ドレイン電極 605b(d)を構成することもできる。例えば、銅、マグネシウム、及びアルミニウムを含む合金材料の層と銅を含む層の積層により、ソース電極 605a(a)乃至ソース電極 605a(d)、及びドレイン電極 605b(a)乃至ドレイン電極 605b(d)を構成することができる。

#### 【0157】

また、ソース電極 605a(a)乃至ソース電極 605a(d)、及びドレイン電極 605b(a)乃至ドレイン電極 605b(d)としては、導電性の金属酸化物を含む層を用いることもできる。導電性の金属酸化物としては、例えば酸化インジウム、酸化スズ、酸化亜鉛、インジウムスズ酸化物、又はインジウム亜鉛酸化物を用いることができる。なお、ソース電極 605a(a)乃至ソース電極 605a(d)、及びドレイン電極 605b(a)乃至ドレイン電極 605b(d)に適用可能な導電性の金属酸化物は、酸化シリコンを含んでいてもよい。

10

#### 【0158】

ソース電極 605a(a)乃至ソース電極 605a(d)、及びドレイン電極 605b(a)乃至ドレイン電極 605b(d)は、例えば、スパッタリング法を用いて導電膜（例えば金属膜、または一導電型の不純物元素が添加されたシリコン膜など）を形成し、該導電膜上にエッチングマスクを形成してエッチングを行うことで選択的に形成すればよい。または、インクジェット法などを用いてもよい。なお、ソース電極 605a(a)乃至ソース電極 605a(d)、及びドレイン電極 605b(a)乃至ドレイン電極 605b(d)となる導電膜は、単層で形成してもよいし、複数の層を積層して形成してもよい。例えば、T<sub>i</sub>層によりA<sub>1</sub>層を挟持した3層の積層構造とすればよい。

20

#### 【0159】

絶縁層 600(a)乃至絶縁層 600(d)としては、例えばゲート絶縁層 602(a)乃至ゲート絶縁層 602(d)に適用可能な材料の層を用いることができる。また、ゲート絶縁層 602(a)乃至ゲート絶縁層 602(d)に適用可能な材料の積層により絶縁層 600(a)乃至絶縁層 600(d)を構成してもよい。例えば、酸化アルミニウム層及び酸化シリコン層の積層により絶縁層 600(a)乃至絶縁層 600(d)を構成することにより、絶縁層 600(a)乃至絶縁層 600(d)に含まれる酸素が酸化物半導体層 603(a)乃至酸化物半導体層 603(d)を介して脱離するのを抑制することができる。

30

#### 【0160】

絶縁層 606(a)及び絶縁層 606(b)、埋め込み絶縁物 612a(a)及び埋め込み絶縁物 612b(a)、埋め込み絶縁物 612a(b)及び埋め込み絶縁物 612b(b)、側壁絶縁物 616a(a)及び側壁絶縁物 616b(a)、並びに側壁絶縁物 616a(b)及び側壁絶縁物 616b(b)としては、ゲート絶縁層 602(a)乃至ゲート絶縁層 602(d)に適用可能な材料の単層または積層を用いることができる。

#### 【0161】

また、酸化物半導体層 603(a)乃至酸化物半導体層 603(d)に接する絶縁層中の酸素を過剰にすることにより、酸化物半導体層 603(a)乃至酸化物半導体層 603(d)に酸素が供給されやすくなる。よって、酸化物半導体層 603(a)乃至酸化物半導体層 603(d)中、又は当該絶縁層と酸化物半導体層 603(a)乃至酸化物半導体層 603(d)の界面における酸素欠陥を低減することができるため、酸化物半導体層 603(a)乃至酸化物半導体層 603(d)のキャリア濃度をより低減することができる。また、これに限定されず、製造過程により酸化物半導体層 603(a)に含まれる酸素を過剰にした場合であっても、酸化物半導体層 603(a)に接する上記絶縁層により、酸化物半導体層 603(a)からの酸素の脱離を抑制することができる。

40

#### 【0162】

酸化物半導体層 603(a)乃至酸化物半導体層 603(d)と絶縁層 600(a)乃至絶縁層 600(d)の間に、下地絶縁層を設けてもよい。下地絶縁層は、少なくとも表面

50

に酸素を含み、酸素の一部が加熱処理により脱離する絶縁性酸化物により形成するとよい。酸素の一部が加熱処理により脱離する絶縁性酸化物としては、化学量論比よりも多くの酸素を含むものを用いることが好ましい。これは、該加熱処理により、下地絶縁層に接する酸化物半導体層に酸素を供給することができるためである。

#### 【0163】

化学量論比よりも多くの酸素を含む絶縁性酸化物として、例えば、 $\text{SiO}_x$ において $x > 2$ である酸化シリコンが挙げられる。ただし、これに限定されず、下地絶縁層は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化窒化アルミニウム、酸化ガリウム、酸化ハフニウムまたは酸化イットリウムなどで形成してもよい。

#### 【0164】

なお、下地絶縁層は、複数の膜が積層されて形成されていてもよい。下地絶縁層は、例えば、窒化シリコン膜上に酸化シリコン膜が設けられた積層構造であってもよい。

#### 【0165】

ところで、化学量論比よりも多くの酸素を含む絶縁性酸化物では、酸素の一部が加熱処理により脱離しやすい。酸素の一部が加熱処理により脱離しやすいときのTDS分析による酸素の脱離量（酸素原子に換算した値）は、 $1.0 \times 10^{18}$  atoms/cm<sup>3</sup>以上、好ましくは $1.0 \times 10^{20}$  atoms/cm<sup>3</sup>以上、より好ましくは $3.0 \times 10^{20}$  atoms/cm<sup>3</sup>以上であるとよい。

#### 【0166】

下地絶縁層は、スパッタリング法またはCVD法などにより形成すればよいが、好ましくはスパッタリング法を用いて形成する。下地絶縁層として、酸化シリコン膜を形成する場合には、ターゲットとして石英（好ましくは合成石英）ターゲット、スパッタリングガスとしてアルゴンガスを用いればよい。または、ターゲットとしてシリコンターゲット、スパッタリングガスとして酸素を含むガスを用いてもよい。なお、酸素を含むガスとしては、アルゴンガスと酸素ガスの混合ガスでもよいし、酸素ガスのみであってもよい。

#### 【0167】

下地絶縁層を形成した後、酸化物半導体層603(a)乃至酸化物半導体層603(d)となる酸化物半導体層を形成する前に、第1の加熱処理を行う。第1の加熱処理は、下地絶縁層中に含まれる水及び水素を除去するための工程である。第1の加熱処理の温度は、下地絶縁層中に含まれる水及び水素が脱離する温度（脱離量がピークになる温度）以上基板の変質する温度未満とするとよく、好ましくは400以上750以下とし、後に行う第2の加熱処理よりも低い温度とすればよい。

#### 【0168】

そして、酸化物半導体層を形成した後、第2の加熱処理を行う。第2の加熱処理は、下地絶縁層を酸素の供給源として酸化物半導体層に酸素を供給する工程である。ただし、第2の加熱処理を行うタイミングはこれに限定されず、酸化物半導体層を加工した後に行ってもよい。

#### 【0169】

なお、第2の加熱処理は、窒素ガス、またはヘリウム、ネオン若しくはアルゴンなどの希ガス雰囲気中で行い、該雰囲気中に、水素、水、水酸基または水素化物などが含まれていないことが好ましい。または、加熱処理装置に導入する窒素ガス、またはヘリウム、ネオン、アルゴンなどの希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、（即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。

#### 【0170】

また、第2の加熱処理の条件、または酸化物半導体層の材料によっては、酸化物半導体層が結晶化され、微結晶層または多結晶層となる場合もある。例えば、結晶化率が90%以上または80%以上の微結晶層となる場合もある。また、第2の加熱処理の条件、または酸化物半導体層の材料によっては、結晶成分を含まない非晶質となる場合もある。また、非晶質層中に微結晶（結晶粒径1nm以上20nm以下）が混在することもある。

10

20

30

40

50

## 【0171】

なお、酸化物半導体層が結晶性である場合に、酸化物半導体膜の被形成面の平均面荒さ( $R_a$ )は0.1nm以上0.5nm未満であることが好ましい。平均面荒さ( $R_a$ )は1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

## 【0172】

なお、ここで、平均面粗さ( $R_a$ )とは、JIS B 0601：2001(ISO 4287：1997)で定義されている算術平均粗さ( $R_a$ )を、曲面に対して適用できるよう三次元に拡張したものをいう。平均面粗さ( $R_a$ )は、基準面から指定面までの偏差の絶対値を平均した値で表される。

10

## 【0173】

ここで、算術平均粗さ( $R_a$ )は、粗さ曲線を評価長さ $L_0$ に対応した分抜き取り、この抜き取り部の平均線の方向をX軸、縦倍率の方向(X軸に垂直な方向)をY軸とし、粗さ曲線を $y = f(x)$ で表すとき、下記の式(1)で与えられる。

## 【0174】

## 【数1】

$$R_a = \frac{1}{L} \int_0^L |F(X)| dx$$

## 【0175】

20

そして、平均面粗さ( $R_a$ )は、測定面から長波長成分を遮断して得た曲面を $Z_0 = f(x, y)$ で表すとき、基準面から指定面までの偏差の絶対値を平均した値で表現され、次の式(2)で与えられる。

## 【0176】

## 【数2】

$$R_a = \frac{1}{S_0} \iint_{y_1}^{y_2} \int_{x_1}^{x_2} |F(x, y) - Z_0| dx dy$$

## 【0177】

30

ここで、指定面は、粗さ計測の対象となる面であり、座標( $x_1, y_1, f(x_1, y_1)$ ) ( $x_1, y_2, f(x_1, y_2)$ ) ( $x_2, y_1, f(x_2, y_1)$ ) ( $x_2, y_2, f(x_2, y_2)$ )で表される4点で表される四角形の領域とし、指定面が理想的にフラットであるとしたときの面積を $S_0$ とする。

## 【0178】

また、基準面は、指定面の平均の高さにおける、xy平面と平行な面である。つまり、指定面の高さの平均値を $Z_0$ とするとき、基準面の高さも $Z_0$ で表される。

## 【0179】

このように、被形成面の平均面粗さを0.1nm以上0.5nm未満とするためには、化学的機械的研磨(Chemical Mechanical Polishing: CMP)処理を行えばよい。CMP処理は、酸化物半導体層の形成前に行えばよいが、第1の加熱処理の前に行うことが好ましい。

40

## 【0180】

ここで、CMP処理は、一回以上行えばよい。複数回に分けてCMP処理を行う場合には、高い研磨レートで一次研磨を行った後、低い研磨レートで仕上げ研磨を行うことが好ましい。

## 【0181】

また、被形成面を平坦化させるためには、CMP処理に代えてドライエッティングなどを行ってもよい。ここで、エッティングガスとしては、塩素、塩化ボロン、塩化シリコンまたは四塩化炭素などの塩素系ガス、四フッ化炭素、フッ化硫黄またはフッ化窒素などのフッ素

50

系ガスなどを用いればよい。

**【0182】**

また、被形成面を平坦化させるためには、C M P処理に代えてプラズマ処理などを行ってもよい。ここで、プラズマ処理には希ガスを用いればよい。このプラズマ処理により、被処理面に不活性ガスのイオンが照射され、スパッタリング効果により被処理面の微細な凹凸が平坦化される。このようなプラズマ処理は逆スパッタとも呼ばれる。

**【0183】**

なお、被形成面を平坦化するためには、前記処理のいずれを用いてもよい。例えば、逆スパッタのみを行ってもよいし、C M P処理を行った後にドライエッチングを行ってもよい。ただし、酸化物半導体膜の被形成面である被形成面に水などを混入させないためには、ドライエッチングまたは逆スパッタを用いることが好ましい。特に、第1の加熱処理を行った後に平坦化処理を行う場合には、ドライエッチングまたは逆スパッタを用いることが好ましい。

10

**【0184】**

酸化物半導体層は、少なくともインジウム(I n)または亜鉛(Z n)を含むことが好ましい。特に、I nとZ nの双方を含むことが好ましい。さらには、ガリウム(G a)を有することが好ましい。ガリウム(G a)を有すると、トランジスタ特性のばらつきを低減することができる。このようなトランジスタ特性のばらつきを低減することができる元素をスタビライザーと呼ぶ。スタビライザーとしては、スズ(S n)、ハフニウム(H f)またはアルミニウム(A l)が挙げられる。

20

**【0185】**

また、この他のスタビライザーとしては、ランタン(L a)、セリウム(C e)、プラセオジム(P r)、ネオジム(N d)、サマリウム(S m)、ユウロピウム(E u)、ガドリニウム(G d)、テルビウム(T b)、ジスプロシウム(D y)、ホルミウム(H o)、エルビウム(E r)、ツリウム(T m)、イッテルビウム(Y b)、ルテチウム(L u)が挙げられる。これらのいずれか一種または複数種を有してもよい。

**【0186】**

また、酸化物半導体としては、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるI n-Z n系酸化物、S n-Z n系酸化物、A l-Z n系酸化物、Z n-M g系酸化物、S n-M g系酸化物、I n-M g系酸化物、I n-G a系酸化物、三元系金属の酸化物であるI n-G a-Z n系酸化物(IG Z Oとも表記する)、I n-A l-Z n系酸化物、I n-S n-Z n系酸化物、S n-G a-Z n系酸化物、A l-G a-Z n系酸化物、S n-A l-Z n系酸化物、I n-H f-Z n系酸化物、I n-L a-Z n系酸化物、I n-C e-Z n系酸化物、I n-P r-Z n系酸化物、I n-N d-Z n系酸化物、I n-S m-Z n系酸化物、I n-E u-Z n系酸化物、I n-G d-Z n系酸化物、I n-T b-Z n系酸化物、I n-D y-Z n系酸化物、I n-H o-Z n系酸化物、I n-E r-Z n系酸化物、I n-T m-Z n系酸化物、I n-Y b-Z n系酸化物、I n-L u-Z n系酸化物、四元系金属の酸化物であるI n-S n-G a-Z n系酸化物、I n-H f-G a-Z n系酸化物、I n-A l-G a-Z n系酸化物、I n-S n-A l-Z n系酸化物、I n-S n-H f-Z n系酸化物、I n-H f-A l-Z n系酸化物を例示することができる。

30

**【0187】**

なお、ここで、例えば、I n-G a-Z n系酸化物とは、I nとG aとZ nを主成分として有する酸化物という意味であり、I nとG aとZ nの比率は問わない。また、I nとG aとZ n以外の金属元素が入っていてもよい。

**【0188】**

例えば、原子数比I n:G a:Z n=1:1:1(=1/3:1/3:1/3)またはI n:G a:Z n=2:2:1(=2/5:2/5:1/5)のI n-G a-Z n系酸化物やその組成の近傍の酸化物を用いることができる。または、原子数比I n:S n:Z n=

40

50

1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3)、In : Sn : Zn = 2 : 1 : 3 (= 1 / 3 : 1 / 6 : 1 / 2)若しくはIn : Sn : Zn = 2 : 1 : 5 (= 1 / 4 : 1 / 8 : 5 / 8)のIn - Sn - Zn系酸化物やその近傍の組成の酸化物を用いるとよい。

#### 【0189】

しかし、本発明の一態様において用いることができる酸化物半導体層は、これらに限定されるものではなく、必要とする半導体特性(移動度、しきい値、ばらつきなど)に応じて適切な組成のものを用いればよい。必要とするトランジスタ特性(半導体特性)に応じて、キャリア濃度、不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離及び密度などを適宜調整すればよい。

#### 【0190】

例えば、In - Sn - Zn系酸化物では比較的高い移動度が得られる。しかしながら、In - Ga - Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

#### 【0191】

なお、例えば、In、Ga、Znの原子数比がIn : Ga : Zn = a : b : c (a + b + c = 1)である酸化物の組成が、原子数比がIn : Ga : Zn = A : B : C (A + B + C = 1)の酸化物の組成の近傍であるとは、a、b、cが、(a - A)<sup>2</sup> + (b - B)<sup>2</sup> + (c - C)<sup>2</sup> / r<sup>2</sup>を満たすことをいうものとし、rは、例えば、0.05とすればよい。

#### 【0192】

酸化物半導体は、単結晶でもよいし、非単結晶でもよい。非単結晶である場合には、非晶質でもよいし、多結晶でもよい。また、非晶質中に結晶性を有する部分を含む構造であってもよい。または、非アモルファスであってもよい。

#### 【0193】

なお、前記金属酸化物には、これらの化学量論比に対し、酸素を過剰に含ませることが好ましい。酸素を過剰に含ませると、形成される酸化物半導体層の酸素欠損によるキャリアの生成を抑制することができる。

#### 【0194】

なお、一例として、酸化物半導体層をIn - Zn系金属酸化物により形成する場合には、Znに対するInの原子数比が、In / Zn = 1 ~ 100、好ましくはIn / Zn = 1 ~ 20、さらに好ましくはIn / Zn = 1 ~ 10とする。Znの原子数比を好ましい前記範囲とすることで、電界効果移動度を向上させることができる。ここで、酸素を過剰に含ませるために、金属酸化物の原子数比In : Zn : O = X : Y : Zを、Z > 1.5X + Yとすることが好ましい。

#### 【0195】

なお、ここで、ターゲットとして用いる焼結体の充填率は90%以上100%以下、好ましくは95%以上100%以下であるとよい。ターゲットの充填率を高くすることで、形成される酸化物半導体層を緻密なものとすることができる。

#### 【0196】

なお、酸化物半導体層に適用することができる金属酸化物は、エネルギーギャップが2eV以上、好ましくは2.5eV以上、更に好ましくは3eV以上であるとよい。このように、バンドギャップの広い金属酸化物を用いると、トランジスタのオフ電流を低減することができる。

#### 【0197】

なお、酸化物半導体層には、水素が含まれる。この水素は、水素原子の他、水素分子、水、水酸基、またはその他の水素化物として含まれる場合もある。酸化物半導体膜に含まれる水素は、極力少ないことが好ましい。

#### 【0198】

なお、酸化物半導体層のアルカリ金属及びアルカリ土類金属は少なくすることが好ましく、これらの濃度は、好ましくは $1 \times 10^{-8}$ atoms/cm<sup>3</sup>以下、更に好ましくは2

10

20

30

40

50

$\times 10^{16}$  atoms/cm<sup>3</sup> 以下とする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアが生成されることがあり、トランジスタのオフ電流を増大させる原因となるからである。

#### 【0199】

なお、酸化物半導体層の形成方法及び厚さは特に限定されず、作製するトランジスタのサイズなどに応じて決めればよい。酸化物半導体層の形成方法としては、例えば、スパッタリング法、分子線エピタキシー法、塗布法、印刷法またはパルスレーザー蒸着法などが挙げられる。酸化物半導体層の厚さは、3 nm 以上 50 nm 以下とすればよい。50 nm 以上に厚くするとノーマリーオンとなるおそれがあるためである。また、トランジスタのチャネル長を 30 nm としたときには、酸化物半導体膜の厚さは 5 nm 以下とすると、短チャネル効果を抑制することができる。10

#### 【0200】

ここでは、好ましい一例として、In - Ga - Zn 系金属酸化物ターゲットを用いてスパッタリング法により酸化物半導体層を形成する方法について説明する。ここで、スパッタリングガスとしては、希ガス（例えばアルゴンガス）、酸素ガス、または希ガスと酸素ガスの混合ガスを用いればよい。

#### 【0201】

なお、酸化物半導体層を形成する際に用いるスパッタリングガスとしては、水素、水、水酸基または水素化物などが除去された高純度ガスを用いることが好ましい。スパッタリングガスを高純度ガスとするためには、処理室の内壁などに付着したガスを除去し、酸化物半導体層を形成する前に被形成面を加熱処理すればよい。また、処理室に導入するスパッタリングガスを高純度ガスとしてもよく、このとき、アルゴンガスにおいて、純度は 9N (99.999999%) 以上、露点は -121 以下、水は 0.1 ppb 以下、水素は 0.5 ppb 以下とすればよい。酸素ガスにおいて、純度は 8N (99.99999%) 以上、露点は -112 以下、水は 1 ppb 以下、水素は 1 ppb 以下とすればよい。被形成面を加熱しつつ高温に保持した状態で酸化物半導体層を形成すると、酸化物半導体層に含まれる水などの不純物の濃度を低減することができる。さらには、スパッタリング法を適用したことにより酸化物半導体層に混入する損傷を少なくすることができる。20

#### 【0202】

また、酸化物半導体層に酸素を過剰に含ませるために、イオン注入により酸素を供給してもよい。30

#### 【0203】

ここで、酸化物半導体の構造の一態様である、CAAC - OS (C Axis Aligned Crystalline Oxide Semiconductor) 膜について説明する。

#### 【0204】

CAAC - OS 膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC - OS 膜は、結晶部及び非晶質部を有する結晶 - 非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一边が 100 nm 未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡 (TEM : Transmission Electron Microscope) による観察像では、CAAC - OS 膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEM によって CAAC - OS 膜には粒界（グレインバウンダリーともいう）は確認できない。そのため、CAAC - OS 膜は、粒界に起因する電子移動度の低下が抑制される。40

#### 【0205】

CAAC - OS 膜に含まれる結晶部は、c 軸が CAAC - OS 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつ ab 面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸及び b 軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、50 85

°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上5°以下の範囲も含まれることとする。

#### 【0206】

なお、CAC-O<sub>x</sub>膜において、結晶部の分布が一様でなくてもよい。例えば、CAC-C-O<sub>x</sub>膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部のしめる割合が高くなることがある。また、CAC-O<sub>x</sub>膜へ不純物等を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

#### 【0207】

CAC-O<sub>x</sub>膜に含まれる結晶部のc軸は、CAC-O<sub>x</sub>膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAC-O<sub>x</sub>膜の形状（被形成面の断面形状または表面の断面形状）によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向はCAC-O<sub>x</sub>膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

10

#### 【0208】

CAC-O<sub>x</sub>膜を用いることで、可視光や紫外光の照射によるトランジスタの電気特性の変動を低減することが可能である。よって、信頼性の高いトランジスタを得ることができる。

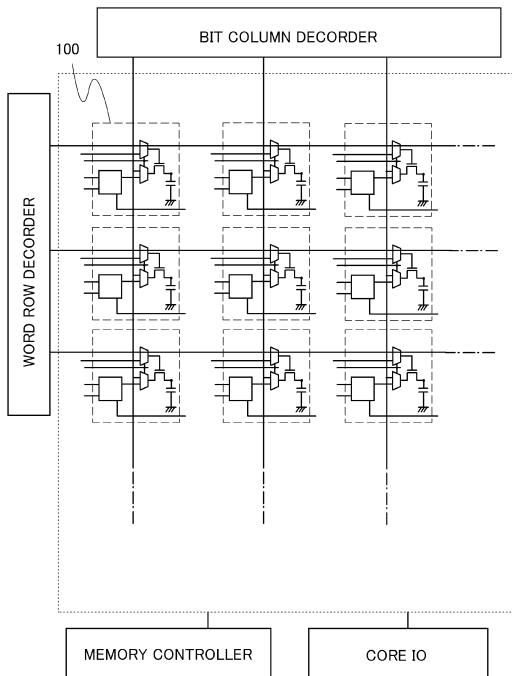

#### 【0209】

20

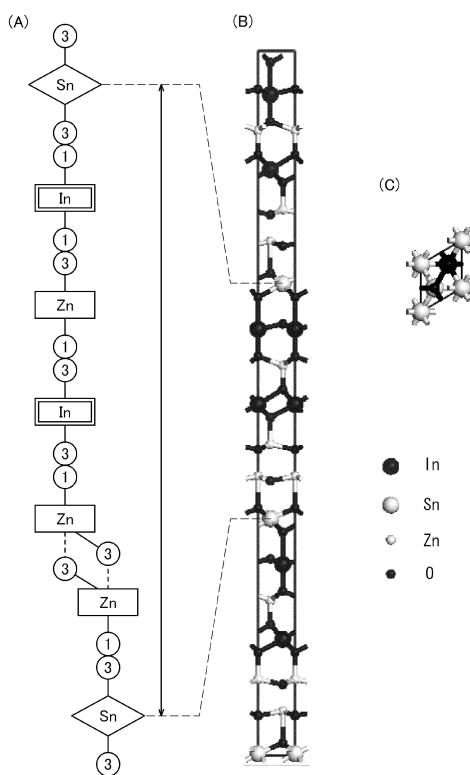

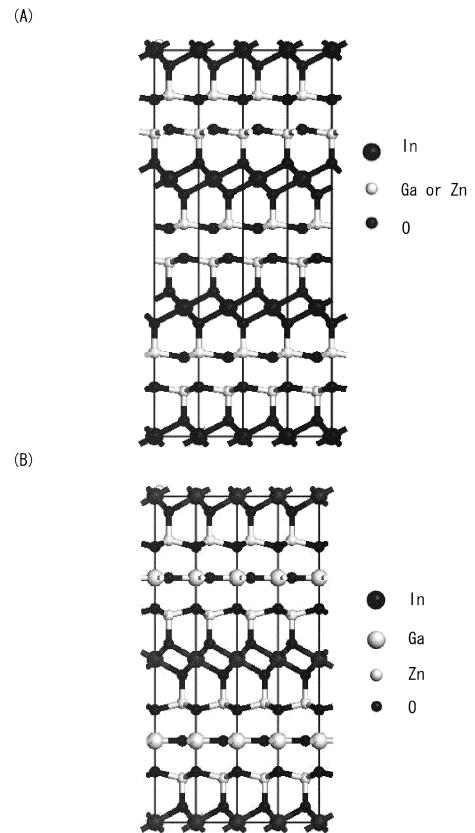

CAC-O<sub>x</sub>膜に含まれる結晶構造の一例について図7乃至図10を用いて詳細に説明する。なお、特に断りがない限り、図7乃至図10は上方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。また、図7において、丸で囲まれたOは4配位のOを示し、二重丸のOは3配位のOを示す。

#### 【0210】

図7(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子（以下4配位のO）と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図7(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図7(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図7(A)に示す小グループは総電荷が0である。

30

#### 【0211】

図7(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子（以下3配位のO）と、Gaに近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもab面に存在する。図7(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図7(B)に示す構造をとりうる。図7(B)に示す小グループは総電荷が0である。

#### 【0212】

図7(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図7(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図7(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあつてもよい。図7(C)に示す小グループは総電荷が0である。

40

#### 【0213】

図7(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図7(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図7(D)に示す小グループは総電荷が+1となる。

#### 【0214】

図7(E)に、2個のZnを含む小グループを示す。図7(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図7(E)に示す小グループは総電荷が-1となる。

50

**【 0 2 1 5 】**

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループと呼ぶ。

**【 0 2 1 6 】**

ここで、これらの小グループ同士が結合する規則について説明する。図7 ( A ) に示す 6 配位の I n の上半分の 3 個の O は下方向にそれぞれ 3 個の近接 I n を有し、下半分の 3 個の O は上方向にそれぞれ 3 個の近接 I n を有する。図7 ( B ) に示す 5 配位の G a の上半分の 1 個の O は下方向に 1 個の近接 G a を有し、下半分の 1 個の O は上方向に 1 個の近接 G a を有する。図7 ( C ) に示す 4 配位の Z n の上半分の 1 個の O は下方向に 1 個の近接 Z n を有し、下半分の 3 個の O は上方向にそれぞれ 3 個の近接 Z n を有する。この様に、金属原子の上方向の 4 配位の O の数と、その O の下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の 4 配位の O の数と、その O の上方向にある近接金属原子の数は等しい。O は 4 配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は 4 になる。従って、金属原子の上方向にある 4 配位の O の数と、別の金属原子の下方向にある 4 配位の O の数との和が 4 個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6 配位の金属原子 ( I n または S n ) が下半分の 4 配位の O を介して結合する場合、4 配位の O が 3 個であるため、5 配位の金属原子 ( G a または I n ) または 4 配位の金属原子 ( Z n ) のいずれかと結合することになる。

10

**【 0 2 1 7 】**

これらの配位数を有する金属原子は、c 軸方向において、4 配位の O を介して結合する。また、このほかにも、層構造の合計の電荷が 0 となるように複数の小グループが結合して中グループを構成する。

20

**【 0 2 1 8 】**

図8 ( A ) に、I n - S n - Z n - O 系酸化物の層構造を構成する中グループのモデル図を示す。図8 ( B ) に、3 つの中グループで構成される大グループを示す。なお、図8 ( C ) は、図8 ( B ) の層構造を c 軸方向から観察した場合の原子配列を示す。

**【 0 2 1 9 】**

図8 ( A ) においては、簡単のため、3 配位の O は省略し、4 配位の O は個数のみ示し、例えば、S n の上半分および下半分にはそれぞれ 3 個ずつ 4 配位の O があることを丸枠の 3 として示している。同様に、図8 ( A ) において、I n の上半分および下半分にはそれぞれ 1 個ずつ 4 配位の O があり、丸枠の 1 として示している。また、同様に、図8 ( A ) において、下半分には 1 個の 4 配位の O があり、上半分には 3 個の 4 配位の O がある Z n と、上半分には 1 個の 4 配位の O があり、下半分には 3 個の 4 配位の O がある Z n とを示している。

30

**【 0 2 2 0 】**

図8 ( A ) において、I n - S n - Z n - O 系酸化物の層構造を構成する中グループは、上から順に 4 配位の O が 3 個ずつ上半分および下半分にある S n が、4 配位の O が 1 個ずつ上半分および下半分にある I n と結合し、その I n が、上半分に 3 個の 4 配位の O がある Z n と結合し、その Z n の下半分の 1 個の 4 配位の O を介して 4 配位の O が 3 個ずつ上半分および下半分にある I n と結合し、その I n が、上半分に 1 個の 4 配位の O がある Z n 2 個からなる小グループと結合し、この小グループの下半分の 1 個の 4 配位の O を介して 4 配位の O が 3 個ずつ上半分および下半分にある S n と結合している構成である。この中グループが複数結合して大グループを構成する。

40

**【 0 2 2 1 】**

ここで、3 配位の O および 4 配位の O の場合、結合 1 本当たりの電荷はそれぞれ - 0 . 6 6 7 、 - 0 . 5 と考えることができる。例えば、I n ( 6 配位または 5 配位 ) 、Z n ( 4 配位 ) 、S n ( 5 配位または 6 配位 ) の電荷は、それぞれ + 3 、 + 2 、 + 4 である。従って、S n を含む小グループは総電荷が + 1 となる。そのため、S n を含む層構造を形成するためには、電荷 + 1 を打ち消す電荷 - 1 が必要となる。電荷 - 1 をとる構造として、図7 ( E ) に示すように、2 個の Z n を含む小グループが挙げられる。例えば、S n を含む

50

小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の総電荷を0とすることができる。

#### 【0222】

具体的には、図8(B)に示した大グループが繰り返されることで、In-Sn-Zn-O系の結晶( $In_2SnZn_3O_8$ )を得ることができる。なお、得られるIn-Sn-Zn-O系の層構造は、 $In_2SnZn_2O_7 (ZnO)_m$ (mは0または自然数。)とする組成式で表すことができる。

#### 【0223】

また、このほかにも、四元系金属の酸化物であるIn-Sn-Ga-Zn-O系酸化物や、三元系金属の酸化物であるIn-Ga-Zn-O系酸化物(IGZOとも表記する。)、In-Al-Zn-O系酸化物、Sn-Ga-Zn-O系酸化物、Al-Ga-Zn-O系酸化物、Sn-Al-Zn-O系酸化物や、In-Hf-Zn-O系酸化物、In-La-Zn-O系酸化物、In-Ce-Zn-O系酸化物、In-Pr-Zn-O系酸化物、In-Nd-Zn-O系酸化物、In-Sm-Zn-O系酸化物、In-Eu-Zn-O系酸化物、In-Gd-Zn-O系酸化物、In-Tb-Zn-O系酸化物、In-Dy-Zn-O系酸化物、In-Ho-Zn-O系酸化物、In-Er-Zn-O系酸化物、In-Tm-Zn-O系酸化物、In-Yb-Zn-O系酸化物、In-Lu-Zn-O系酸化物や、二元系金属の酸化物であるIn-Zn-O系酸化物、Sn-Zn-O系酸化物、Al-Zn-O系酸化物、Zn-Mg-O系酸化物、Sn-Mg-O系酸化物、In-Mg-O系酸化物や、In-Ga-O系酸化物などを用いた場合も同様である。

10

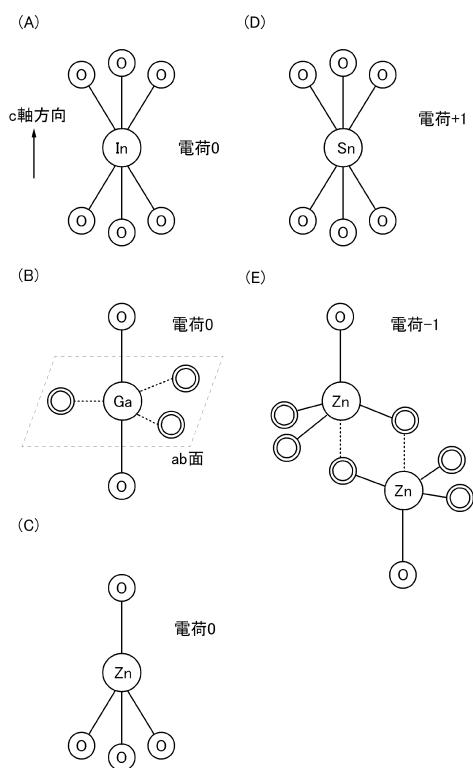

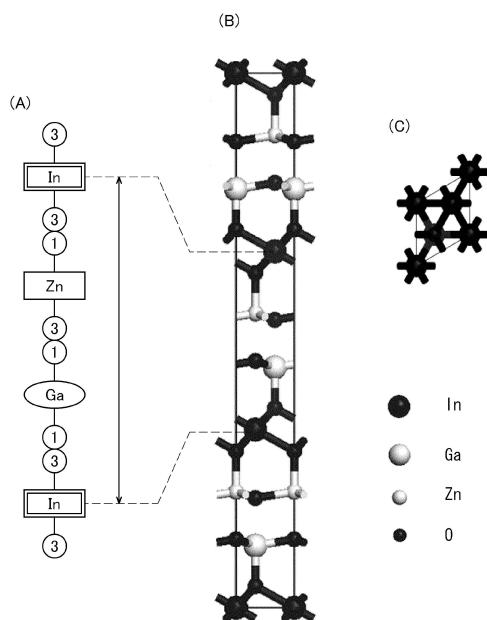

#### 【0224】

例えば、図9(A)に、In-Ga-Zn-O系酸化物の層構造を構成する中グループのモデル図を示す。

#### 【0225】

図9(A)において、In-Ga-Zn-O系酸化物の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合し、そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合し、そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合している構成である。この中グループが複数結合して大グループを構成する。

30

#### 【0226】

図9(B)に3つの中グループで構成される大グループを示す。なお、図9(C)は、図9(B)の層構造をc軸方向から観察した場合の原子配列を示している。

#### 【0227】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

#### 【0228】

また、In-Ga-Zn-O系酸化物の層構造を構成する中グループは、図9(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

40

#### 【0229】

具体的には、図9(B)に示した大グループが繰り返されることで、In-Ga-Zn-O系酸化物の結晶を得ることができる。なお、得られるIn-Ga-Zn-O系酸化物の層構造は、 $InGaO_3 (ZnO)_n$ (nは自然数。)とする組成式で表すことができる。

#### 【0230】

$n = 1$ ( $InGaZnO_4$ )の場合は、例えば、図10(A)に示す結晶構造を取りうる。なお、図10(A)に示す結晶構造において、図7(B)で説明したように、Ga及び

50

$I_n$  は 5 配位をとるため、 $Ga$  が  $I_n$  に置き換わった構造も取りうる。

【0231】

また、 $n = 2$  ( $I_n Ga Zn_2 O_5$ ) の場合は、例えば、図 10 (B) に示す結晶構造を取りうる。なお、図 10 (B) に示す結晶構造において、図 7 (B) で説明したように、 $Ga$  及び  $I_n$  は 5 配位をとるため、 $Ga$  が  $I_n$  に置き換わった構造も取りうる。

【0232】

ここで、CACAC-O<sub>5</sub> 膜の形成方法について説明する。

【0233】

まず、酸化物半導体層をスパッタリング法などによって形成する。なお、被形成面を高温に保持しつつ酸化物半導体層の形成を行うことで、非晶質部分よりも結晶部分の占める割合を大きくすることができる。このとき、被形成面の温度は、例えば、150 以上 450 以下とすればよく、好ましくは 200 以上 350 以下とする。

10

【0234】

ここで、形成された酸化物半導体層に対して加熱処理を行ってもよい。この加熱処理によって、非晶質部分よりも結晶部分の占める割合を大きくすることができる。この加熱処理時の温度は、例えば、200 以上、被形成面自体が変質または変形しない程度の温度未満とすればよく、好ましくは 250 以上 450 以下とすればよい。この加熱処理の時間は 3 分以上とすればよく、24 時間以下とすることが好ましい。この加熱処理の時間を長くすると非晶質部分よりも結晶部分の占める割合を大きくすることができるが、生産性の低下を招くことになるからである。なお、この加熱処理は、酸化性雰囲気または不活性雰囲気で行えばよいが、これらに限定されるものではない。また、この加熱処理は減圧下で行われてもよい。

20

【0235】

酸化性雰囲気は、酸化性ガスを含む雰囲気である。酸化性ガスとしては、例えば、酸素、オゾンまたは亜酸化窒素などを例示することができる。酸化性雰囲気からは、酸化物半導体層に含まれないことが好ましい成分（例えば、水及び水素）が極力除去されていることが好ましい。例えば、酸素、オゾン、亜酸化窒素の純度を、8N (99.99999%) 以上、好ましくは 9N (99.999999%) 以上とすればよい。

【0236】

また、酸化性雰囲気は、酸化性ガスを含む希ガスなどの不活性ガスでもよい。ただし、酸化性雰囲気には、10 ppm 以上の酸化性ガスが含まれているものとする。不活性雰囲気には、不活性ガス（窒素ガスまたは希ガスなど）が含まれ、酸化性ガスなどの反応性ガスが 10 ppm 未満で含まれているものとする。

30

【0237】

なお、すべての加熱処理は、RTA (Rapid Thermal Anneal) 装置を用いて行えばよい。RTA 装置を用いることで、短時間であれば、高い温度で熱処理を行うこともできる。そのため、非晶質部分よりも結晶部分の占める割合の大きい酸化物半導体層を形成することができ、生産性の低下を抑制することができる。

【0238】

ただし、すべての加熱処理に用いられる装置は RTA 装置に限定されず、例えば、抵抗発熱体などからの熱伝導または熱輻射によって、被処理物を加熱する機構が備えられた装置を用いればよい。すべての加熱処理に用いられる加熱処理装置として、例えば、電気炉や、GRTA (Gas Rapid Thermal Anneal) 装置、LRTA (Lamp Rapid Thermal Anneal) 装置などの RTA 装置などを挙げることができる。なお、LRTA 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプまたは高圧水銀ランプなどのランプから発せられる光（電磁波）の輻射により、被処理物を加熱する装置である。また、GRTA 装置は、高温のガスを熱媒体として用いて被処理物を加熱する装置である。

40

【0239】

50

なお、窒素の濃度が  $1 \times 10^{17}$  atoms/cm<sup>3</sup> 以上  $5 \times 10^{19}$  atoms/cm<sup>3</sup> 以下である In - Ga - Zn 系金属酸化物を用いると、c 軸配向した六方晶の結晶構造を含む金属酸化物膜が形成され、一または複数の Ga 及び Zn を有する層が、二層の In - O の結晶面（インジウムと酸素を含む結晶面）の間に配される。

#### 【0240】

また、In - Sn - Zn 系金属酸化物の形成には、例えば、In : Sn : Zn が原子数比で、1 : 2 : 2、2 : 1 : 3、1 : 1 : 1、または 20 : 45 : 35 のターゲットを用いればよい。

#### 【0241】

以上説明したように CAAC - OS 膜を形成することができる。CAAC - OS 膜は、非晶質の酸化物半導体層と比較して、金属と酸素の結合の秩序性が高い。すなわち、酸化物半導体層が非晶質構造の場合には、金属原子によって配位している酸素原子の数が異なるが、CAAC - OS 膜では金属原子に配位している酸素原子の数はほぼ一定となる。そのため、酸素欠損がほぼ見られず、水素原子（水素イオンを含む）やアルカリ金属原子などによる電荷の移動や電気伝導性の不安定さを抑制することができる。10

#### 【0242】

従って、CAAC - OS 膜を用いたチャネル形成領域によってトランジスタを作製する、トランジスタへの光照射またはバイアス - 熱ストレス (BT) の付加を行った後に生じる、トランジスタのしきい値電圧の変化を抑制することができ、安定した電気的特性を有するトランジスタを作製することができる。20

#### 【0243】

ゲート絶縁層 602 (a) 乃至ゲート絶縁層 602 (d) は、例えば、スパッタリング法を用いて絶縁性材料（例えば、窒化シリコン、窒化酸化シリコン、酸化窒化シリコンまたは酸化シリコンなど）膜を形成すればよい。なお、ゲート絶縁層 602 (a) 乃至ゲート絶縁層 602 (d) は単層で形成してもよいし、複数の層を積層して形成してもよい。ここでは、例えば、窒化シリコン層上に酸化窒化シリコン層が積層された 2 層の積層構造とする。

#### 【0244】

酸化物半導体を用いたトランジスタでは、電界効果移動度も高くすることができる。

#### 【0245】

ただし、実際の酸化物半導体を用いたトランジスタの電界効果移動度は、バルクの移動度よりも低くなる。移動度を低下させる要因としては半導体内部の欠陥や半導体と絶縁層との界面の欠陥がある。Levinson モデルを用いると、半導体内部に欠陥がないと仮定した場合の電界効果移動度を理論的に導き出せる。30

#### 【0246】

半導体本来の移動度を  $\mu_0$ 、測定される電界効果移動度を  $\mu$  とし、半導体中に何らかのポテンシャル障壁（粒界など）が存在すると仮定すると、下記の式で表現できる。

#### 【0247】

#### 【数3】

$$\mu = \mu_0 \exp\left(-\frac{E}{kT}\right)$$

ここで、E はポテンシャル障壁の高さ、k はボルツマン定数、T は絶対温度である。また、ポテンシャル障壁が欠陥に由来すると仮定すると、Levinson モデルでは、ポテンシャル障壁は下記の式で表される。40

#### 【0248】

【数4】

$$E = \frac{e^2 N^2}{8\epsilon n} = \frac{e^3 N^2 t}{8\epsilon C_{ox} V_g}$$

【0249】

ここで、 $e$  は電気素量、 $N$  はチャネル内の単位面積当たりの平均欠陥密度、 $\epsilon$  は半導体の誘電率、 $n$  は単位面積当たりのチャネルに含まれるキャリア数、 $C_{ox}$  は単位面積当たりの容量、 $V_g$  はゲート電圧、 $t$  はチャネルの厚さである。なお、厚さ 30 nm 以下の半導体層であれば、チャネルの厚さは半導体層の厚さと同一として差し支えない。

10

【0250】

また、線形領域におけるドレイン電流  $I_d$  は、下記の式で表される。

【0251】

【数5】

$$I_d = \frac{W\mu}{L} V_g V_d C_{ox} \exp(-\frac{E}{kT})$$

【0252】

ここで、 $L$  はチャネル長、 $W$  はチャネル幅であり、 $L = W = 10 \mu m$  としている。また、 $V_d$  はドレイン電圧である。上式の両辺を  $V_g$  で割り、更に両辺の対数をとると、下記の式が得られる。

20

【0253】

【数6】

$$\ln\left(\frac{I_d}{V_g}\right) = \ln\left(\frac{W\mu}{L} V_d C_{ox}\right) - \frac{E}{kT} = \ln\left(\frac{W\mu}{L} V_d C_{ox}\right) - \frac{e^3 N^2 t}{8kT \epsilon C_{ox} V_g}$$

【0254】

式(6)の右辺は  $V_g$  の関数である。式(6)からわかるように、縦軸を  $1n(I_d/V_g)$  、横軸を  $1/V_g$  とする直線の傾きから欠陥密度  $N$  が求められる。すなわち、トランジスタの  $I_d - V_g$  特性から、欠陥密度を評価できる。酸化物半導体としては、インジウム( $In$ )、スズ( $Sn$ )、亜鉛( $Zn$ )の比率が、 $In : Sn : Zn = 1 : 1 : 1$  のものでは欠陥密度  $N$  は  $1 \times 10^{12} / cm^2$  程度である。

30

【0255】

このようにして求めた欠陥密度などをもとに式(3)及び式(4)より  $\mu_0 = 120 cm^2/Vs$  が導出される。欠陥のある  $In-Sn-Zn$  酸化物で測定される移動度は  $40 cm^2/Vs$  程度である。しかし、上記導出された結果より、半導体内部及び半導体と絶縁層の界面に欠陥がない場合の酸化物半導体の移動度  $\mu_0$  は  $120 cm^2/Vs$  となる。

40

【0256】

ただし、半導体内部に欠陥がなくても、トランジスタの輸送特性はチャネルとゲート絶縁層との界面での散乱による影響を受ける。すなわち、ゲート絶縁層界面から  $x$  だけ離れた場所における移動度  $\mu_1$  は、下記の式(7)で表される。

【0257】

【数7】

$$\frac{1}{\mu_1} = \frac{1}{\mu_0} + \frac{D}{B} \exp(-\frac{x}{l})$$

【0258】

50

ここで、Dはゲート方向の電界、B、lは定数である。B及びlは、実際の測定結果より求めることができ、上記の測定結果からは、 $B = 4.75 \times 10^7 \text{ cm/s}$ 、 $l = 10 \text{ nm}$ （界面散乱が及ぶ深さ）である。Dが増加する（すなわち、ゲート電圧が高くなる）と数7の第2項が増加するため、移動度 $\mu_1$ は低下することがわかる。

#### 【0259】

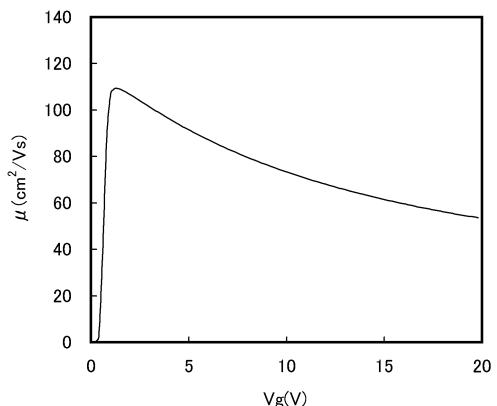

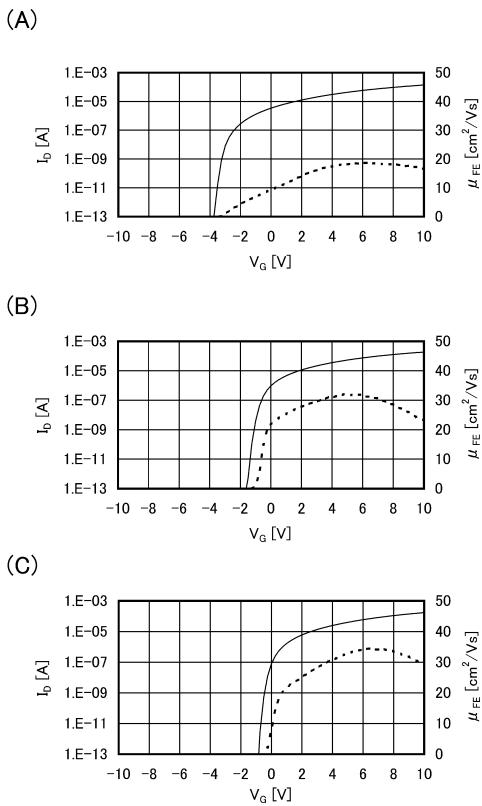

半導体内部の欠陥が無い理想的な酸化物半導体をチャネルに用いたトランジスタの移動度を計算した結果を図11に示す。なお、計算にはデバイスシミュレーションソフトSentaurus Device（シノプシス社製）を使用し、酸化物半導体のバンドギャップを2.8eV、電子親和力を4.7eV、比誘電率を1.5、厚さを15nmとした。さらに、ゲートの仕事関数を5.5eV、ソースの仕事関数を4.6eV、ドレインの仕事関数を4.6eVとした。また、ゲート絶縁層の厚さは100nm、比誘電率は4.1とした。チャネル長及びチャネル幅はともに10μm、ドレイン電圧 $V_d$ は0.1Vとした。

10

#### 【0260】

図11で示されるように、ゲート電圧1V強で移動度 $100 \text{ cm}^2/\text{Vs}$ 以上のピークをつけるが、ゲート電圧がさらに高くなると、界面散乱が大きくなり、移動度が低下する。なお、界面散乱を低減するためには、上記式(1)などを示して説明したように、半導体層表面を原子レベルで平坦にすること（Atomic Layer Flatness）が好ましい。

20

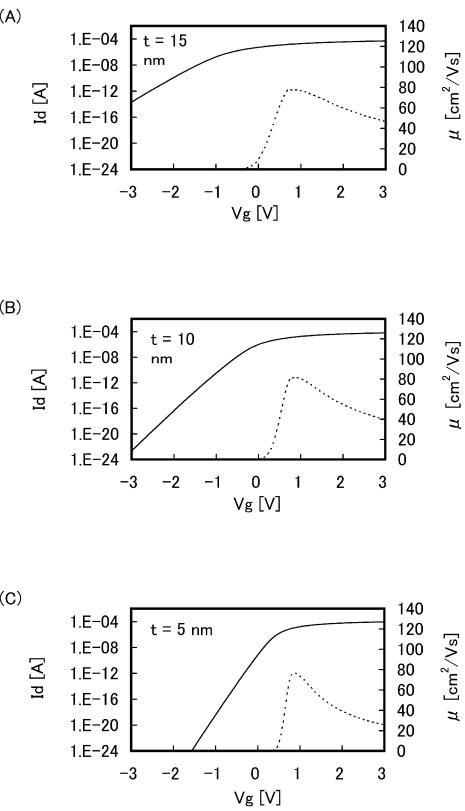

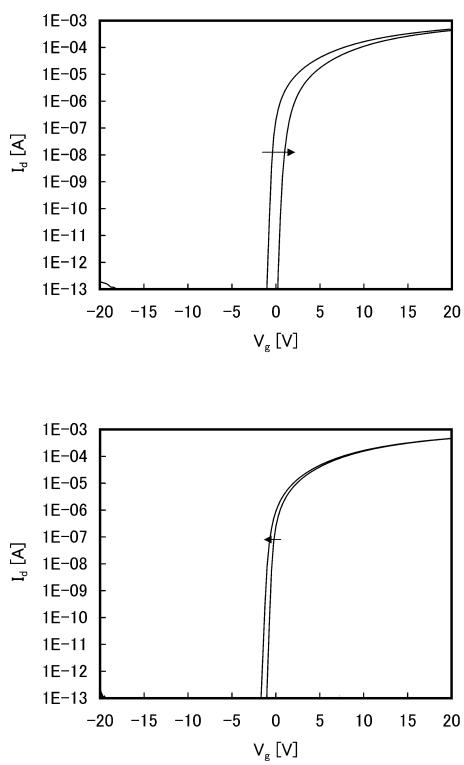

#### 【0261】

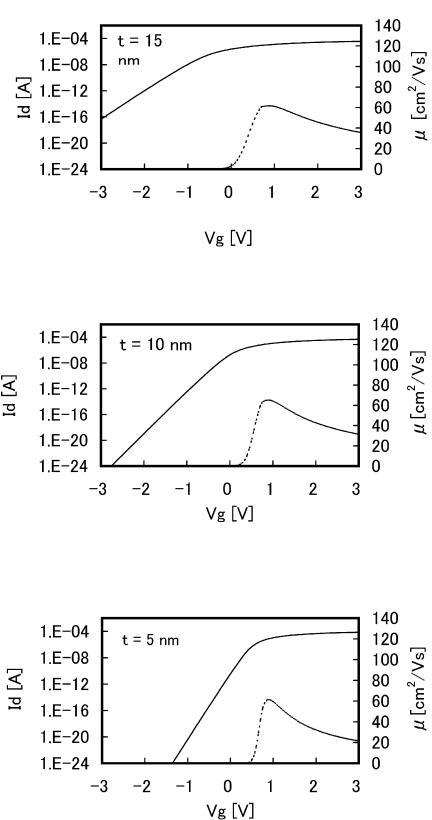

このような移動度を有する酸化物半導体を用いて微細なトランジスタを作製した場合の特性の計算結果を図12乃至図14に示す。ここで、計算に用いたトランジスタの断面構造を図15に示す。図15に示すトランジスタは、酸化物半導体層に $n^+$ の導電型を呈する半導体領域303a及び半導体領域303cを有する。計算において、半導体領域303a及び半導体領域303cの抵抗率は $2 \times 10^{-3} \text{ cm}$ とした。

20

#### 【0262】

図15(A)に示すトランジスタは、上記実施の形態に示した図16(A)と対応しており、図15(B)に示すトランジスタは、上記実施の形態に示した図16(B)と対応している。

30

#### 【0263】

図15(A)に示すトランジスタは、絶縁層301と、絶縁層301に埋め込まれるように形成された酸化アルミニウムよりなる埋め込み絶縁物302の上に形成される。トランジスタは半導体領域303a、半導体領域303cと、それらに挟まれ、チャネル形成領域となる真性の半導体領域303bと、ゲート電極305を有する。ゲート電極305の幅を33nmとする。

30

#### 【0264】

ゲート電極305と半導体領域303bの間には、ゲート絶縁層304を有し、また、ゲート電極305の両側面には側壁絶縁物306aおよび側壁絶縁物306b、ゲート電極305の上部には、ゲート電極305と他の配線との短絡を防止するための絶縁層307を有する。側壁絶縁物の幅は5nmとする。また、半導体領域303aおよび半導体領域303cに接して、ソース電極308aおよびドレイン電極308bを有する。

40

#### 【0265】

図15(B)に示すトランジスタは、絶縁層301と、酸化アルミニウムよりなる埋め込み絶縁物302の上に形成され、半導体領域303a、半導体領域303cと、それらに挟まれた真性の半導体領域303bと、幅33nmのゲート電極305とゲート絶縁層304と側壁絶縁物306aおよび側壁絶縁物306bと絶縁層307とソース電極308aおよびドレイン電極308bを有する点で図15(A)に示すトランジスタと同じである。

50

#### 【0266】

図15(A)に示すトランジスタと図15(B)に示すトランジスタは、側壁絶縁物30

6 a 及び側壁絶縁物 3 0 6 b 直下の半導体領域の導電型が異なる。側壁絶縁物 3 0 6 a 及び側壁絶縁物 3 0 6 b 直下の半導体領域は、図 15 ( A ) に示すトランジスタでは  $n^+$  の導電型を呈する領域であるが、図 15 ( B ) に示すトランジスタでは真性の半導体領域である。すなわち、半導体領域 3 0 3 a ( 半導体領域 3 0 3 c ) とゲート電極 3 0 5 が  $L_{off}$  だけ重ならない領域ができている。この領域をオフセット領域といい、その幅  $L_{off}$  をオフセット長という。オフセット長は、側壁絶縁物 3 0 6 a ( 側壁絶縁物 3 0 6 b ) の幅と同じである。

#### 【 0 2 6 7 】

その他の計算に使用するパラメータは上述の通りである。計算にはシノプシス社製デバイスシミュレーションソフト、Sentaurus Device を使用した。図 12 は、

10 図 15 ( A ) に示される構造のトランジスタのドレン電流 ( $I_d$ 、実線) 及び移動度 ( $\mu$ 、点線) のゲート電圧 ( $V_g$  : ソースを基準としたゲートとの電位差) 依存性を示す。ドレン電流  $I_d$  は、ドレン電圧 ( $V_d$  : ソースを基準としたドレンとの電位差) を +1 V とし、移動度  $\mu$  はドレン電圧を +0 . 1 V として計算したものである。

#### 【 0 2 6 8 】

ゲート絶縁層の厚さは、図 12 ( A ) では 15 nm としており、図 12 ( B ) では 10 nm としており、図 12 ( C ) は 5 nm としている。ゲート絶縁層が薄くなるほど、特にオフ状態でのドレン電流  $I_d$  ( オフ電流 ) が顕著に低下する。一方、移動度  $\mu$  のピーク値やオン状態でのドレン電流  $I_d$  ( オン電流 ) には目立った変化が無い。

#### 【 0 2 6 9 】

図 13 は、図 15 ( B ) に示すトランジスタで、オフセット長  $L_{off}$  を 5 nm としたときのドレン電流  $I_d$  ( 実線 ) 及び移動度  $\mu$  ( 点線 ) のゲート電圧  $V_g$  依存性を示す。ドレン電流  $I_d$  は、ドレン電圧を +1 V とし、移動度  $\mu$  はドレン電圧を +0 . 1 V として計算したものである。ゲート絶縁層の厚さは、図 13 ( A ) では 15 nm としており、図 13 ( B ) では 10 nm としており、図 13 ( C ) は 5 nm としている。

20

#### 【 0 2 7 0 】

図 14 は、図 15 ( B ) に示すトランジスタで、オフセット長  $L_{off}$  を 15 nm としたもののドレン電流  $I_d$  ( 実線 ) および移動度  $\mu$  ( 点線 ) のゲート電圧依存性を示す。ドレン電流  $I_d$  は、ドレン電圧を +1 V とし、移動度  $\mu$  はドレン電圧を +0 . 1 V として計算したものである。ゲート絶縁層の厚さは、図 14 ( A ) では 15 nm としており、図 14 ( B ) では 10 nm としており、図 14 ( C ) は 5 nm としている。

30

#### 【 0 2 7 1 】

いずれもゲート絶縁層が薄くなるほど、オフ電流が顕著に低下する一方、移動度  $\mu$  のピーク値やオン電流には目立った変化が無い。

#### 【 0 2 7 2 】

なお、移動度  $\mu$  のピークは、図 12 では  $80 \text{ cm}^2 / \text{Vs}$  程度であるが、図 13 では  $60 \text{ cm}^2 / \text{Vs}$  程度、図 14 では  $40 \text{ cm}^2 / \text{Vs}$  と、オフセット長  $L_{off}$  が増加するほど低下する。また、オフ電流も同様な傾向がある。一方、オン電流にはオフセット長  $L_{off}$  の増加にともなって減少するが、オフ電流の低下に比べるとはるかに緩やかである。

#### 【 0 2 7 3 】

以上説明したように、酸化物半導体をチャネルに用いるトランジスタは非常に高い移動度とすることができる。

#### 【 0 2 7 4 】

なお、ここで、酸化物半導体をチャネルに用いるトランジスタとして説明したトランジスタは一例であり、酸化物半導体をチャネルに用いるトランジスタはこれに限定されず、様々な形態とすることができる。

#### 【 0 2 7 5 】

$In$ 、 $Sn$ 、 $Zn$  を主成分とする酸化物半導体をチャネル形成領域とするトランジスタは、該酸化物半導体を形成する際に基板を加熱して成膜すること、或いは酸化物半導体膜を形成した後に熱処理を行うことで良好な特性を得ることができる。なお、主成分とは組成

40

50

比で 5 atomic % 以上含まれる元素をいう。

#### 【0276】

In、Sn、Zn を主成分とする酸化物半導体膜の成膜後に基板を意図的に加熱することで、トランジスタの電界効果移動度を向上させることができるとなる。また、トランジスタのしきい値電圧をプラスシフトさせ、ノーマリ・オフ化させることができるとなる。

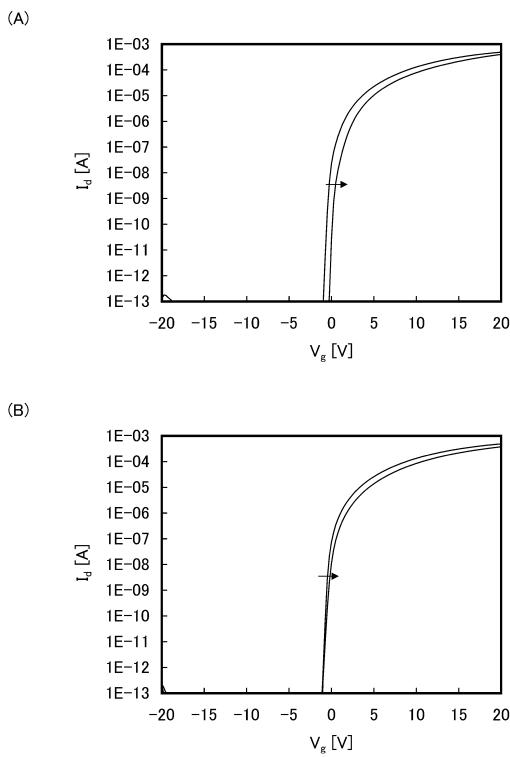

#### 【0277】

例えば、図 16 (A) 乃至図 16 (C) は、In、Sn、Zn を主成分とし、チャネル長 L が 3 μm、チャネル幅 W が 10 μm である酸化物半導体膜と、厚さ 100 nm のゲート絶縁層を用いたトランジスタの特性である。なお、V<sub>d</sub> は 10 V とした。

#### 【0278】

図 16 (A) は基板を意図的に加熱せずにスパッタリング法で In、Sn、Zn を主成分とする酸化物半導体膜を形成したときのトランジスタ特性である。このとき電界効果移動度は 18.8 cm<sup>2</sup> / V sec が得られている。一方、基板を意図的に加熱して In、Sn、Zn を主成分とする酸化物半導体膜を形成すると電界効果移動度を向上させることができるとなる。図 16 (B) は基板を 200 °C に加熱して In、Sn、Zn を主成分とする酸化物半導体膜を形成したときのトランジスタ特性を示すが、電界効果移動度は 32.2 cm<sup>2</sup> / V sec が得られている。

#### 【0279】

電界効果移動度は、In、Sn、Zn を主成分とする酸化物半導体膜を形成した後に熱処理をすることによって、さらに高めることができる。図 16 (C) は、In、Sn、Zn を主成分とする酸化物半導体膜を 200 °C でスパッタリング成膜した後、650 °C で熱処理をしたときのトランジスタ特性を示す。このとき電界効果移動度は 34.5 cm<sup>2</sup> / V sec が得られている。

#### 【0280】

基板を意図的に加熱することでスパッタリング成膜中の水分が酸化物半導体膜中に取り込まれるのを低減する効果が期待できる。また、成膜後に熱処理をすることによっても、酸化物半導体膜から水素や水酸基若しくは水分を放出させ除去することができ、上記のように電界効果移動度を向上させることができる。このような電界効果移動度の向上は、脱水化・脱水素化による不純物の除去のみならず、高密度化により原子間距離が短くなるためとも推定される。また、酸化物半導体から不純物を除去して高純度化することで結晶化を図ることができる。このように高純度化された非単結晶酸化物半導体は、理想的には 100 cm<sup>2</sup> / V sec を超える電界効果移動度を実現することも可能になると推定される。

#### 【0281】

In、Sn、Zn を主成分とする酸化物半導体に酸素イオンを注入し、熱処理により該酸化物半導体に含まれる水素や水酸基若しくは水分を放出させ、その熱処理と同時に又はその後の熱処理により酸化物半導体を結晶化させても良い。このような結晶化若しくは再結晶化の処理により結晶性の良い非単結晶酸化物半導体を得ることができる。

#### 【0282】

基板を意図的に加熱して成膜すること及び / 又は成膜後に熱処理することの効果は、電界効果移動度の向上のみならず、トランジスタのノーマリ・オフ化を図ることにも寄与している。基板を意図的に加熱しないで形成された In、Sn、Zn を主成分とする酸化物半導体膜をチャネル形成領域としたトランジスタは、しきい値電圧がマイナスとなってしまう傾向がある。しかし、基板を意図的に加熱して形成された酸化物半導体膜を用いた場合、このしきい値電圧がマイナスとなってしまう傾向は解消される。つまり、加熱しない場合と比べてしきい値電圧が高くなり、このような傾向は図 16 (A) と図 16 (B) の対比からも確認することができる。

#### 【0283】

なお、しきい値電圧は In、Sn 及び Zn の比率を変えることによっても制御することができるであり、組成比として In : Sn : Zn = 2 : 1 : 3 とすることでトランジスタのノーマリ・オフ化を期待することができる。また、ターゲットの組成比を In : Sn : Zn

10

20

30

40

50

= 2 : 1 : 3 とすることで結晶性の高い酸化物半導体膜を得ることができる。

#### 【0284】

意図的な基板加熱温度若しくは熱処理温度は、150以上、好ましくは200以上、より好ましくは400以上であり、より高温で成膜し或いは熱処理することでトランジスタのノーマリ・オフ化を図ることが可能となる。

#### 【0285】

また、意図的に基板を加熱した成膜及び/又は成膜後に熱処理をすることで、ゲートバイアス・ストレスに対する安定性を高めることができる。例えば、2MV/cm、150、1時間印加の条件において、ドリフトがそれぞれ±1.5V未満、好ましくは1.0V未満を得ることができる。

10

#### 【0286】

実際に、酸化物半導体膜成膜後に加熱処理を行っていない試料1と、650の加熱処理を行った試料2のトランジスタに対してBT試験を行った。

#### 【0287】

まず基板温度を25とし、 $V_d$ を10Vとし、トランジスタの $V_g - I_d$ 特性の測定を行った。なお、 $V_d$ はドレン電圧(ドレンとソースの電位差)を示す。次に、基板温度を150とし、 $V_d$ を0.1Vとした。次に、ゲート絶縁層に印加される電界強度が2MV/cmとなるような電圧をゲート電極に印加し、そのまま1時間保持した。次に、 $V_g$ を0Vとした。次に、基板温度25とし、 $V_d$ を10Vとし、トランジスタの $V_g - I_d$ 測定を行った。これをプラスBT試験と呼ぶ。

20

#### 【0288】

同様に、まず基板温度を25とし、 $V_d$ を10Vとし、トランジスタの $V_g - I_d$ 特性の測定を行った。次に、基板温度を150とし、 $V_d$ を0.1Vとした。次に、ゲート絶縁層に印加される電界強度が-2MV/cmとなるように $V_g$ に-20Vを印加し、そのまま1時間保持した。次に、 $V_g$ を0Vとした。次に、基板温度25とし、 $V_d$ を10Vとし、トランジスタの $V_g - I_d$ 測定を行った。これをマイナスBT試験と呼ぶ。

#### 【0289】

試料1のプラスBT試験の結果を図17(A)に、マイナスBT試験の結果を図17(B)に示す。また、試料2のプラスBT試験の結果を図18(A)に、マイナスBT試験の結果を図18(B)に示す。

30

#### 【0290】

試料1のプラスBT試験およびマイナスBT試験によるしきい値電圧の変動は、それぞれ1.80Vおよび-0.42Vであった。また、試料2のプラスBT試験およびマイナスBT試験によるしきい値電圧の変動は、それぞれ0.79Vおよび0.76Vであった。試料1および試料2のいずれも、BT試験前後におけるしきい値電圧の変動が小さく、信頼性が高いことがわかる。

#### 【0291】

熱処理は酸素雰囲気中で行うことができるが、まず窒素若しくは不活性ガス、または減圧下で熱処理を行ってから酸素を含む雰囲気中で熱処理を行っても良い。最初に脱水化・脱水素化を行ってから酸素を酸化物半導体に加えることで、熱処理の効果をより高めることができる。また、後から酸素を加えるには、酸素イオンを電界で加速して酸化物半導体膜に注入する方法を適用しても良い。

40

#### 【0292】

酸化物半導体中及び該酸化物半導体と接する膜との界面には、酸素欠損による欠陥が生成されやすいが、かかる熱処理により酸化物半導体中に酸素を過剰に含ませることにより、定常的に生成される酸素欠損を過剰な酸素によって補償することが可能となる。過剰酸素は主に格子間に存在する酸素であり、その酸素濃度は $1 \times 10^{16} / \text{cm}^3$ 以上 $2 \times 10^{20} / \text{cm}^3$ 以下とすれば、結晶に歪み等を与えることなく酸化物半導体中に含ませることができる。

#### 【0293】

50

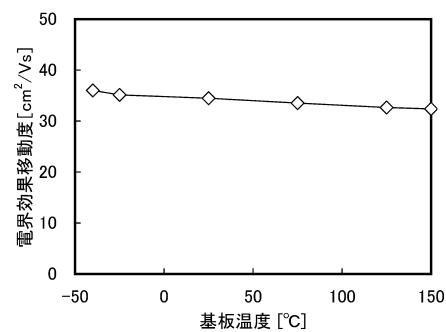

また、熱処理によって酸化物半導体に結晶が少なくとも一部に含まれるようにすることでき、より安定な酸化物半導体膜を得ることができる。例えば、組成比  $In : Sn : Zn = 1 : 1 : 1$  のターゲットを用いて、基板を意図的に加熱せずにスパッタリング成膜した酸化物半導体膜は、X線回折(XRD: X-Ray Diffraction)でハローパターンが観測される。この成膜された酸化物半導体膜を熱処理することによって結晶化させることができる。熱処理温度は任意であるが、例えば650の熱処理を行うことで、X線回折において明確な回折ピークを観測することができる。

#### 【0294】

実際に、 $In - Sn - Zn - O$  膜のXRD測定を行った。XRD測定には、Bruker AXS社製X線回折装置 D8 ADVANCE を用い、Out-of-Plane法で測定した。10

#### 【0295】

XRD分析を行った試料として、試料Aおよび試料Bを用意した。以下に試料Aおよび試料Bの作製方法を説明する。

#### 【0296】

脱水素化処理済みの石英基板上に $In - Sn - Zn - O$  膜を100nmの厚さで成膜した。10

#### 【0297】

$In - Sn - Zn - O$  膜は、スパッタリング装置を用い、酸素雰囲気で電力を100W(DC)として成膜した。ターゲットは、原子数比で、 $In : Sn : Zn = 1 : 1 : 1$  の $In - Sn - Zn - O$  ターゲットを用いた。なお、成膜時の基板加熱温度は200とした。このようにして作製した試料を試料Aとした。20

#### 【0298】

次に、試料Aと同様の方法で作製した試料に対し加熱処理を650の温度で行った。加熱処理は、はじめに窒素雰囲気で1時間の加熱処理を行い、温度を下げずに酸素雰囲気でさらに1時間の加熱処理を行っている。このようにして作製した試料を試料Bとした。

#### 【0299】

図21に試料Aおよび試料BのXRDスペクトルを示す。試料Aでは、結晶由来のピークが観測されなかったが、試料Bでは、2が35deg近傍および37deg～38degに結晶由来のピークが観測された。30

#### 【0300】

このように、In、Sn、Znを主成分とする酸化物半導体は成膜時に意図的に加熱すること及び/又は成膜後に熱処理することによりトランジスタの特性を向上させることができる。

#### 【0301】

この基板加熱や熱処理は、酸化物半導体にとって悪性の不純物である水素や水酸基を膜中に含ませないようにすること、或いは膜中から除去する作用がある。すなわち、酸化物半導体中でドナー不純物となる水素を除去することで高純度化を図ることができ、それによってトランジスタのノーマリ・オフ化を図ることができ、酸化物半導体が高純度化されることによりオフ電流を1aA/ $\mu m$ 以下にすることができる。ここで、上記オフ電流値の単位は、チャネル幅1 $\mu m$ あたりの電流値を示す。40

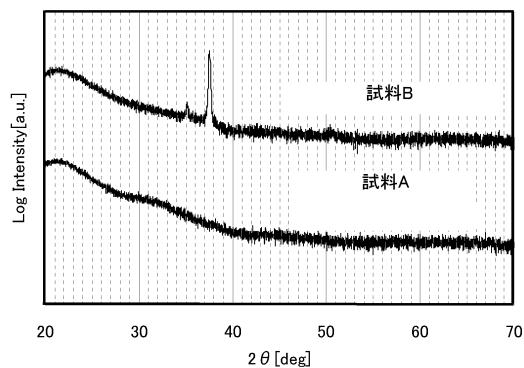

#### 【0302】

図22に、トランジスタのオフ電流と測定時の基板温度(絶対温度)の逆数との関係を示す。ここでは、簡単のため測定時の基板温度の逆数に1000を掛けた数値(1000/T)を横軸としている。

#### 【0303】

具体的には、図22に示すように、基板温度が125の場合には1aA/ $\mu m$ ( $1 \times 10^{-18} A / \mu m$ )以下、85の場合には100zA/ $\mu m$ ( $1 \times 10^{-19} A / \mu m$ )以下、室温(27)の場合には1zA/ $\mu m$ ( $1 \times 10^{-21} A / \mu m$ )以下にすることができる。好ましくは、125において0.1aA/ $\mu m$ ( $1 \times 10^{-19} A / \mu m$ )50

m) 以下に、85において  $10 \text{ zA} / \mu\text{m}$  ( $1 \times 10^{-20} \text{ A} / \mu\text{m}$ ) 以下に、室温において  $0.1 \text{ zA} / \mu\text{m}$  ( $1 \times 10^{-22} \text{ A} / \mu\text{m}$ ) 以下にすることができる。

#### 【0304】

もっとも、酸化物半導体膜の成膜時に水素や水分が膜中に混入しないように、成膜室外部からのリークや成膜室内の内壁からの脱ガスを十分抑え、スパッタガスの高純度化を図ることが好ましい。例えば、スパッタガスは水分が膜中に含まれないように露点 -70 以下であるガスを用いることが好ましい。また、ターゲットそのものに水素や水分などの不純物が含まれていないように、高純度化されたターゲットを用いることが好ましい。

In、Sn、Znを主成分とする酸化物半導体は熱処理によって膜中の水分を除去することができるが、In、Ga、Znを主成分とする酸化物半導体と比べて水分の放出温度が高いため、好ましくは最初から水分の含まれない膜を形成しておくことが好ましい。

10

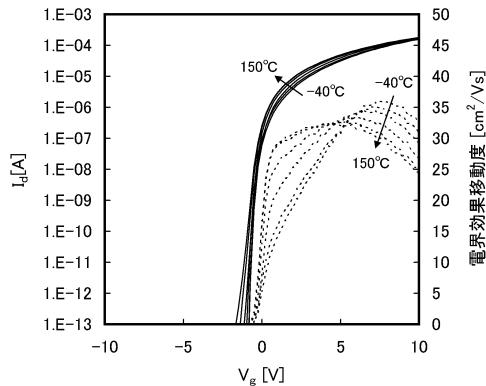

#### 【0305】

また、酸化物半導体膜成膜後に 650 の加熱処理を行った試料を用いたトランジスタにおいて、基板温度と電気的特性の関係について評価した。

#### 【0306】

測定に用いたトランジスタは、チャネル長 L が  $3 \mu\text{m}$ 、チャネル幅 W が  $10 \mu\text{m}$ 、L o v が  $0 \mu\text{m}$  である。なお、 $V_d$  は  $10 \text{ V}$  とした。なお、基板温度は -40、-25、25、75、125 および 150 で行った。ここで、トランジスタにおいて、ゲート電極とソース電極及びドレイン電極とチャネル長方向に重畠する幅を L o v と呼ぶ。

20

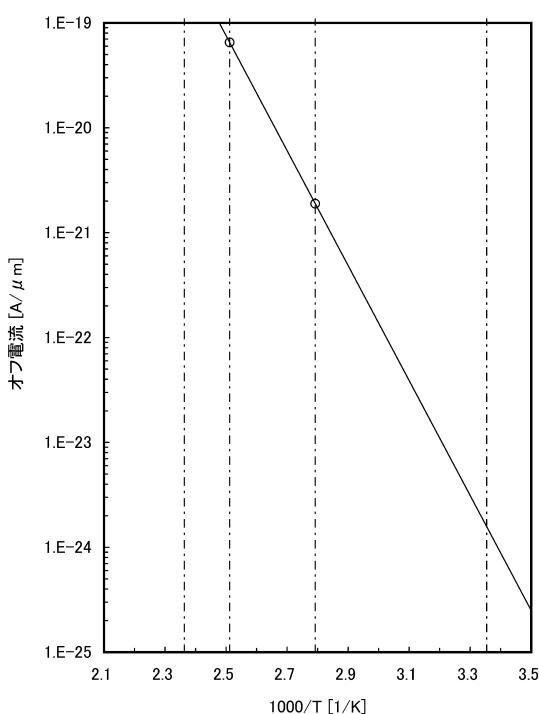

#### 【0307】

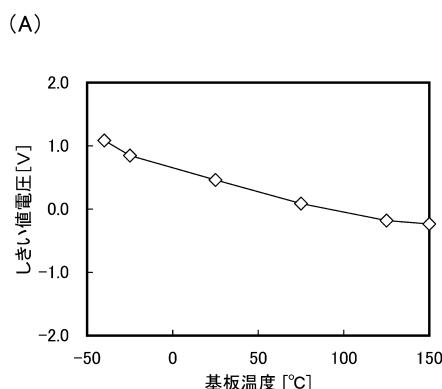

図 19 に、 $I_d$  (実線) および電界効果移動度 (点線) の  $V_g$  依存性を示す。また、図 20 (A) に基板温度としきい値電圧の関係を、図 20 (B) に基板温度と電界効果移動度の関係を示す。

#### 【0308】

図 20 (A) より、基板温度が高いほどしきい値電圧は低くなることがわかる。なお、その範囲は -40 ~ 150 で  $1.09 \text{ V} \sim -0.23 \text{ V}$  であった。

#### 【0309】

また、図 20 (B) より、基板温度が高いほど電界効果移動度が低くなることがわかる。なお、その範囲は -40 ~ 150 で  $36 \text{ cm}^2 / \text{Vs} \sim 32 \text{ cm}^2 / \text{Vs}$  であった。従って、上述の温度範囲において電気的特性の変動が小さいことがわかる。

30

#### 【0310】

上記のような In、Sn、Zn を主成分とする酸化物半導体をチャネル形成領域とするトランジスタによれば、オフ電流を  $1 \text{ aA} / \mu\text{m}$  以下に保ちつつ、電界効果移動度を  $30 \text{ cm}^2 / \text{Vsec}$  以上、好ましくは  $40 \text{ cm}^2 / \text{Vsec}$  以上、より好ましくは  $60 \text{ cm}^2 / \text{Vsec}$  以上とし、LSIで要求されるオン電流の値を満たすことができる。例えば、 $L/W = 33 \text{ nm} / 40 \text{ nm}$  の FET で、ゲート電圧  $2.7 \text{ V}$ 、ドレイン電圧  $1.0 \text{ V}$  のとき  $12 \mu\text{A}$  以上のオン電流を流すことができる。またトランジスタの動作に求められる温度範囲においても、十分な電気的特性を確保することができる。

#### 【0311】

本実施の形態は他の実施の形態と適宜組み合わせることができる。

40

#### 【0312】

##### (実施の形態 3)

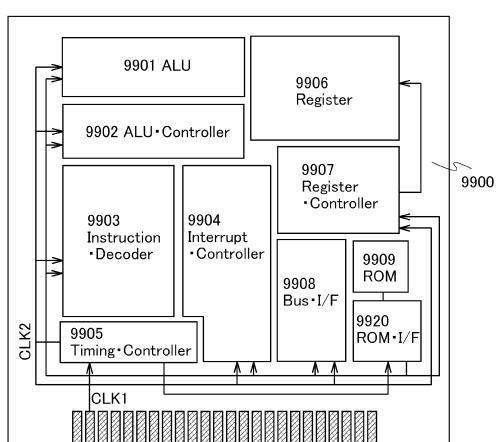

本実施の形態では、本発明の一態様に係る信号処理回路の一つである、CPUの構成について説明する。

#### 【0313】

図 24 に、本実施の形態の CPU の構成を示す。図 24 に示す CPU は、基板 9900 上に、ALU9901、ALU・Controller9902、Instruction・Decoder9903、Interrupt・Controller9904、Timing・Controller9905、Register9906、Register・Controller9907、Bus・I/F9908、書き換え可能な ROM9

50

909、ROM・I/F 9920と、を主に有している。なお、ALUはArithmetic logic unitであり、Bus・I/Fはバスインターフェースであり、ROM・I/FはROMインターフェースである。ROM9909及びROM・I/F 9920は、別チップに設けても良い。勿論、図24に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

#### 【0314】

Bus・I/F 9908を介してCPUに入力された命令は、Instruction・Decoder 9903に入力され、デコードされた後、ALU・Controller 9902、Interrupt・Controller 9904、Register・Controller 9907、Timing・Controller 9905に入力される。

10

#### 【0315】

ALU・Controller 9902、Interrupt・Controller 9904、Register・Controller 9907、Timing・Controller 9905は、デコードされた命令に基づき、各種制御を行なう。具体的にALU・Controller 9902は、ALU 9901の動作を制御するための信号を生成する。また、Interrupt・Controller 9904は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。Register・Controller 9907は、Register 9906のアドレスを生成し、CPUの状態に応じてRegister 9906の読み出しや書き込みを行なう。

20

#### 【0316】

またTiming・Controller 9905は、ALU 9901、ALU・Controller 9902、Instruction・Decoder 9903、Interrupt・Controller 9904、Register・Controller 9907の動作のタイミングを制御する信号を生成する。例えばTiming・Controller 9905は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に入力する。

#### 【0317】

本実施の形態のCPUでは、Register 9906に、上記実施の形態で示した構成を有する半導体記憶装置が設けられている。Register・Controller 9907は、ALU 9901からの指示に従い、Register 9906が有する半導体記憶装置において、データの退避及び復帰の必要がなく、電源電圧の供給を停止することができる。

30

#### 【0318】

この様にして、一時的にCPUの動作を停止し、電源電圧の供給を停止した場合においてもデータ信号を保持することが可能であり、消費電力の低減を行うことができる。具体的には、例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、CPUを停止することができ、それにより消費電力を低減することができる。

40

#### 【0319】

本実施の形態では、CPUを例に挙げて説明したが、本発明の信号処理回路はCPUに限定されず、マイクロプロセッサ、画像処理回路、DSP、FPGA等のLSIにも応用可能である。

#### 【符号の説明】

#### 【0320】

100 レジスタ回路

101 フリップフロップ回路

103 選択回路

|         |                                       |    |

|---------|---------------------------------------|----|

| 1 0 5   | 不揮発性記憶回路                              |    |

| 2 0 0   | レジスタ回路                                |    |

| 2 0 2   | スイッチ                                  |    |

| 2 0 3   | スイッチ                                  |    |

| 2 0 4   | トランジスタ                                |    |

| 2 0 5   | 容量素子                                  |    |

| 2 5 1   | インバータ回路                               |    |

| 2 5 2   | スイッチ回路                                |    |

| 2 5 3   | インバータ回路                               |    |

| 2 5 4   | クロックドインバータ回路                          | 10 |

| 2 5 5   | クロックドインバータ回路                          |    |

| 2 5 6   | スイッチ回路                                |    |

| 2 5 7   | クロックドインバータ回路                          |    |

| 2 5 8   | クロックドインバータ回路                          |    |

| 3 0 1   | 絶縁層                                   |    |

| 3 0 2   | 絶縁物                                   |    |

| 3 0 3 a | 半導体領域                                 |    |

| 3 0 3 b | 半導体領域                                 |    |

| 3 0 3 c | 半導体領域                                 |    |

| 3 0 4   | ゲート絶縁層                                | 20 |

| 3 0 5   | ゲート電極                                 |    |

| 3 0 6 a | 側壁絶縁物                                 |    |

| 3 0 6 b | 側壁絶縁物                                 |    |

| 3 0 7   | 絶縁層                                   |    |

| 3 0 8 a | ソース電極                                 |    |

| 3 0 8 b | ドレイン電極                                |    |

| 6 0 0   | 絶縁層                                   |    |

| 6 0 1   | ゲート電極                                 |    |

| 6 0 2   | ゲート絶縁層                                |    |

| 6 0 3   | 酸化物半導体層                               | 30 |

| 6 0 6   | 絶縁層                                   |    |

| 6 0 4 a | 不純物領域                                 |    |

| 6 0 4 b | 不純物領域                                 |    |

| 6 0 5 a | ソース電極                                 |    |

| 6 0 5 b | ドレイン電極                                |    |

| 6 1 2 a | 絶縁物                                   |    |

| 6 1 2 b | 絶縁物                                   |    |

| 6 1 6 a | 側壁絶縁物                                 |    |

| 6 1 6 b | 側壁絶縁物                                 |    |

| 9 9 0 0 | 基板                                    | 40 |

| 9 9 0 1 | A L U                                 |    |

| 9 9 0 2 | A L U C o n t r o l l e r             |    |

| 9 9 0 3 | I n s t r u c t i o n D e c o d e r   |    |

| 9 9 0 4 | I n t e r r u p t C o n t r o l l e r |    |

| 9 9 0 5 | T i m i n g C o n t r o l l e r       |    |

| 9 9 0 6 | R e g i s t e r                       |    |

| 9 9 0 7 | R e g i s t e r C o n t r o l l e r   |    |

| 9 9 0 8 | B u s I / F                           |    |

| 9 9 0 9 | R O M                                 |    |

| 9 9 2 0 | R O M I / F                           | 50 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

(B)

【図21】

【図22】

【図23】

【図24】

【図8】

【図9】

【図10】

---

フロントページの続き

|               |           |         |       |         |

|---------------|-----------|---------|-------|---------|

| (51)Int.Cl.   | F I       |         |       |         |

| G 1 1 C 14/00 | (2006.01) | H 0 1 L | 29/78 | 6 1 3 B |

|               |           | H 0 1 L | 29/78 | 6 1 8 B |

|               |           | G 1 1 C | 11/34 | 3 5 2 A |

(56)参考文献 特開平08-180672(JP, A)

米国特許第04328551(US, A)

特開2007-305027(JP, A)

国際公開第2003/044953(WO, A1)

特開平07-154228(JP, A)

米国特許出願公開第2011/0148463(US, A1)

特開2000-077982(JP, A)

特開2012-257200(JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |                   |

|---------|-------------------|

| H 0 3 K | 3 / 2 6 - 3 / 3 6 |

| G 1 1 C | 1 4 / 0 0         |

| H 0 1 L | 2 1 / 8 2 4 2     |

| H 0 1 L | 2 7 / 1 0         |

| H 0 1 L | 2 7 / 1 0 8       |

| H 0 1 L | 2 9 / 7 8 6       |