(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6265415号

(P6265415)

(45) 発行日 平成30年1月24日(2018.1.24)

(24) 登録日 平成30年1月5日(2018.1.5)

(51) Int.Cl.

F 1

H03F 3/195 (2006.01)

H03F 3/195

H03F 3/68 (2006.01)

H03F 3/68

H03F 3/213 (2006.01)

H03F 3/213

Z

請求項の数 8 (全 13 頁)

(21) 出願番号 特願2014-11764 (P2014-11764)

(22) 出願日 平成26年1月24日 (2014.1.24)

(65) 公開番号 特開2015-139207 (P2015-139207A)

(43) 公開日 平成27年7月30日 (2015.7.30)

審査請求日 平成29年1月17日 (2017.1.17)

(73) 特許権者 000154325

住友電工デバイス・イノベーション株式会

社

神奈川県横浜市栄区金井町1番地

(74) 代理人 100088155

弁理士 長谷川 芳樹

(74) 代理人 100113435

弁理士 黒木 義樹

(74) 代理人 100136722

弁理士 ▲高▼木 邦夫

(74) 代理人 100174399

弁理士 寺澤 正太郎

(72) 発明者 宮澤 直行

神奈川県横浜市栄区金井町1番地 住友電

工デバイス・イノベーション株式会社内

最終頁に続く

(54) 【発明の名称】增幅装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第一方向に並ぶ一対の縁部を有するパッケージと、

一方の前記縁部に設けられた入力端子と、

他方の前記縁部に設けられた出力端子と、

前記パッケージに内蔵され、第一ボンディングワイヤによって前記入力端子と直接的に接続された入力端子を有する第一段 FET チップと、

前記一方の縁部に設けられ、第二ボンディングワイヤによって前記第一段 FET チップの出力端と直接的に接続された第一段間端子と、

前記一方の縁部に設けられた第二段間端子と、

前記パッケージに内蔵され、第三ボンディングワイヤによって前記出力端子と接続された出力端を有し、前記第一段 FET チップよりも出力が大きい第二段 FET チップと、

前記パッケージに内蔵され、一方の電極が、第四ボンディングワイヤを介して前記第二段間端子と接続され、第五ボンディングワイヤを介して前記第二段 FET チップの入力端と接続されたインピーダンス整合用のキャパシタ素子と、

を備え、

前記一方の縁部と前記第一段 FET チップとの距離が、前記他方の縁部と前記第一段 FET チップとの距離よりも短く、

前記他方の縁部と前記第二段 FET チップとの距離が、前記一方の縁部と前記第二段 FET チップとの距離よりも短い、増幅装置。

10

20

**【請求項 2】**

前記第四ポンディングワイヤの一つの長さと前記第五ポンディングワイヤの一つの長さとの合計は、前記第三ポンディングワイヤの一つの長さよりも長い、請求項 1 に記載の増幅装置。

**【請求項 3】**

前記第一段 FET チップの前記入力端のインピーダンスは、前記第二段 FET チップの前記入力端のインピーダンスよりも高く、前記第一段 FET チップの前記出力端のインピーダンスは、前記第二段 FET チップの前記出力端のインピーダンスよりも高い、請求項 1 又は 2 に記載の増幅装置。

**【請求項 4】**

前記一対の縁部に沿った方向における前記出力端子の幅が、該方向における前記入力端子、前記第一段間端子、及び前記第二段間端子の幅よりも大きい、請求項 1 ~ 3 のいずれか一項に記載の増幅装置。

**【請求項 5】**

前記一方の縁部に設けられ、前記入力端子と前記第一段間端子との間に配置された第三端子を更に備え、

前記第三端子は、グランド電位を有する端子である、請求項 1 ~ 4 のいずれか一項に記載の増幅装置。

**【請求項 6】**

前記第一段間端子と前記第二段間端子とが前記パッケージの外部において互いに接続される、請求項 1 ~ 5 のいずれか一項に記載の増幅装置。

**【請求項 7】**

前記第二段 FET チップのチップサイズが前記第一段 FET チップのチップサイズよりも大きい、請求項 1 ~ 6 のいずれか一項に記載の増幅装置。

**【請求項 8】**

前記第二段 FET チップの前記出力端と前記出力端子とは、前記第三ポンディングワイヤによって直接的に接続されている、請求項 1 ~ 7 のいずれか一項に記載の増幅装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、増幅装置に関するものである。

**【背景技術】****【0002】**

高利得の高出力電力増幅を行うため、直列に接続された複数の増幅用アンプデバイスを備える増幅装置が知られている。特許文献 1 には、そのような増幅装置が開示されている。この増幅装置では、直列に接続される複数の増幅用アンプデバイスが 1 つの半導体チップに集積されている。また、この増幅装置は、3 つの整合回路を更に備える。第 1 の整合回路は、入力端子と初段の増幅用アンプデバイスの入力端との間に接続されている。第 2 の整合回路は、初段の増幅用アンプデバイスの出力端と第 2 段の増幅用アンプデバイスの入力端との間に接続されている。第 3 の整合回路は、出力端子と第 2 段の増幅用アンプデバイスの出力端との間に接続されている。これら 3 つの整合回路と 1 つの半導体チップとは、共通の誘電体基板上に実装されている。

**【先行技術文献】****【特許文献】****【0003】**

【特許文献 1】特開 2000-77954 号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

特許文献 1 に記載された増幅装置では、上述のように 3 つの整合回路が設けられている

10

20

30

40

50

。しかしながら、このように多数の整合回路を設けることは、部品コストや実装工数が増加する原因となる。本発明は、このような問題点に鑑みてなされたものであり、整合回路の数を削減して部品コストや実装工数を抑えることができる増幅装置を提供することを目的とする。

【課題を解決するための手段】

【0005】

上述した課題を解決するために、本願発明による増幅装置は、第一方向に並ぶ一対の縁部を有するパッケージと、一方の縁部に設けられた入力端子と、他方の縁部に設けられた出力端子と、パッケージに内蔵され、第一ポンディングワイヤによって入力端子と直接的に接続された入力端子を有する第一段FETチップと、一方の縁部に設けられ、第二ポンディングワイヤによって第一段FETチップの出力端と直接的に接続された第一段間端子と、一方の縁部に設けられた第二段間端子と、パッケージに内蔵され、第三ポンディングワイヤによって出力端子と直接的に接続された出力端を有し、第一段FETチップよりも出力が大きい第二段FETチップと、パッケージに内蔵され、一方の電極が、第四ポンディングワイヤを介して第二段間端子と接続され、第五ポンディングワイヤを介して第二段FETチップの入力端と接続されたインピーダンス整合用のキャパシタ素子と、を備え、一方の縁部と第一段FETチップとの距離が、他方の縁部と第一段FETチップとの距離よりも短く、他方の縁部と第二段FETチップとの距離が、一方の縁部と第二段FETチップとの距離よりも短い。

10

【発明の効果】

20

【0006】

本発明に係る増幅装置によれば、整合回路の数を削減して部品コストや実装工数を抑えることができる。

【図面の簡単な説明】

【0007】

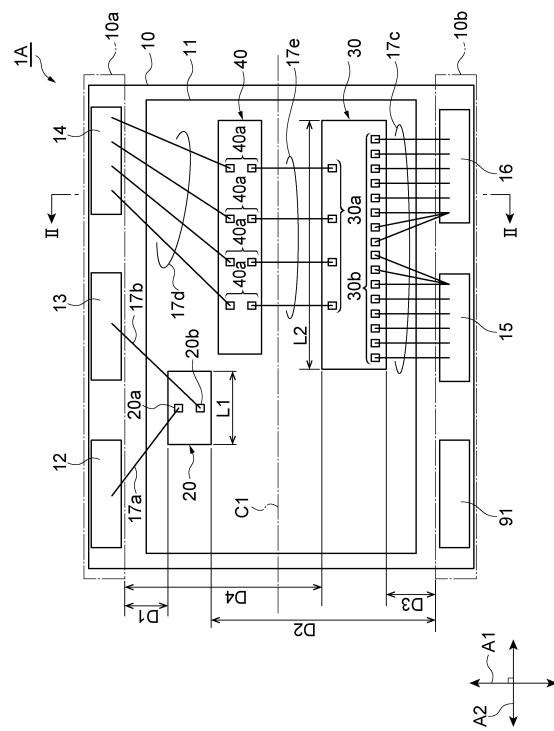

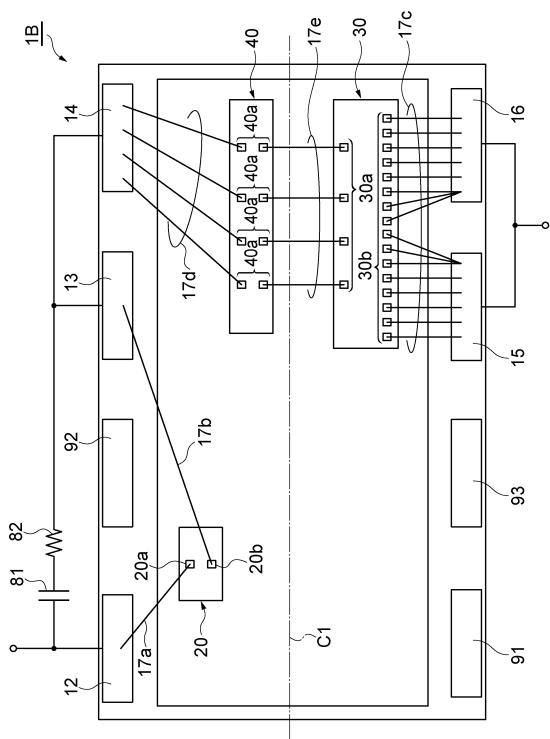

【図1】図1は、一実施形態に係る増幅装置の構成を示す平面図である。

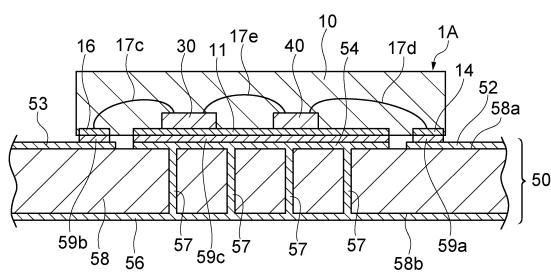

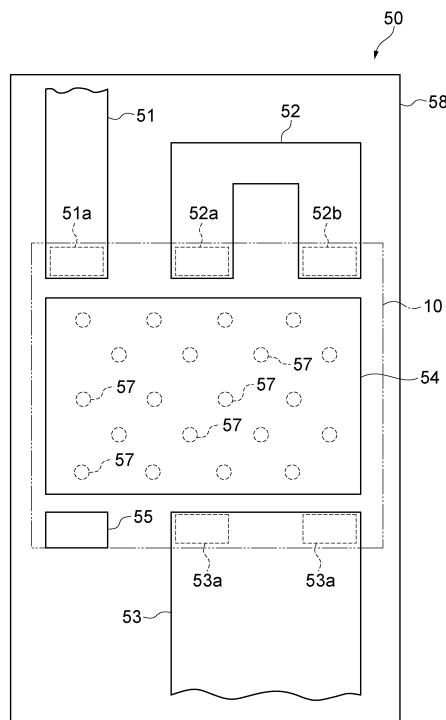

【図2】図2は、配線基板上に増幅装置が実装された様子を示す側断面図である。

【図3】図3は、配線基板の配線パターンを示す平面図である。

【図4】図4(a)は、第一段FETチップの拡大断面図である。図4(b)は、第二段FETチップの拡大断面図である。

30

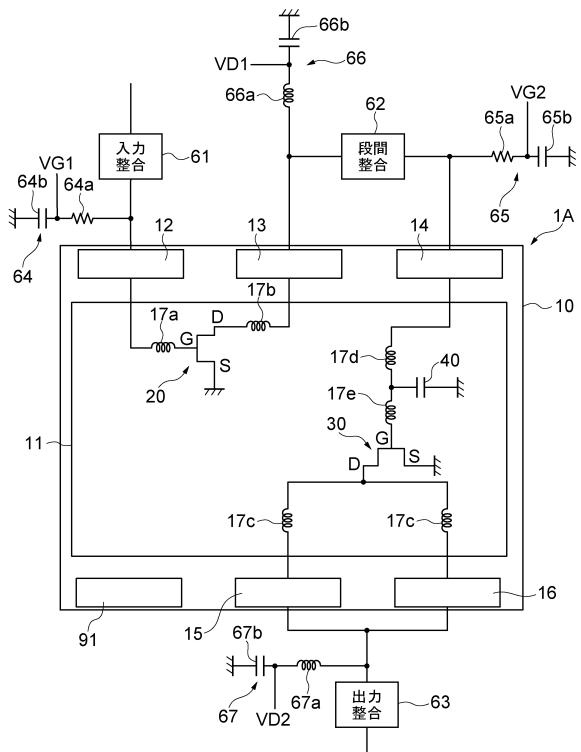

【図5】図5は、増幅装置の使用例を示す回路図である。

【図6】図6は、第1変形例に係る増幅装置の構成を示す平面図である。

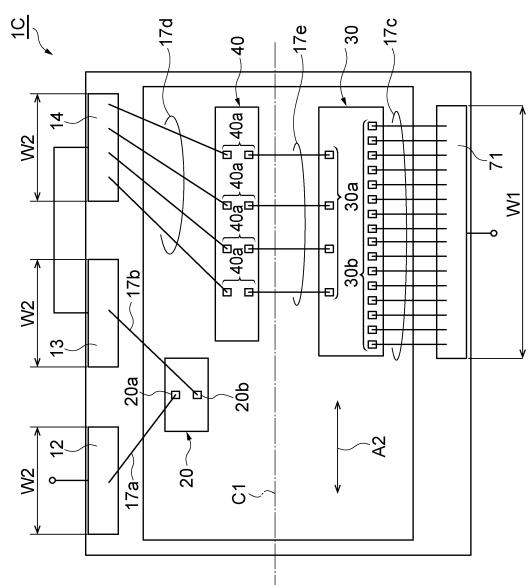

【図7】図7は、第2変形例に係る増幅装置の構成を示す平面図である。

【発明を実施するための形態】

【0008】

[本願発明の実施形態の説明]

最初に、本願発明の実施形態の内容を列記して説明する。(1)本願発明による増幅装置は、第一方向に並ぶ一対の縁部を有するパッケージと、一方の縁部に設けられた入力端子と、他方の縁部に設けられた出力端子と、パッケージに内蔵され、第一ポンディングワイヤによって入力端子と直接的に接続された入力端子を有する第一段FETチップと、一方の縁部に設けられ、第二ポンディングワイヤによって第一段FETチップの出力端と直接的に接続された第一段間端子と、一方の縁部に設けられた第二段間端子と、パッケージに内蔵され、第三ポンディングワイヤによって出力端子と直接的に接続された出力端を有し、第一段FETチップよりも出力が大きい第二段FETチップと、パッケージに内蔵され、一方の電極が、第四ポンディングワイヤを介して第二段間端子と接続され、第五ポンディングワイヤを介して第二段FETチップの入力端と接続されたインピーダンス整合用のキャパシタ素子と、を備え、一方の縁部と第一段FETチップとの距離が、他方の縁部と第一段FETチップとの距離よりも短く、他方の縁部と第二段FETチップとの距離が、一方の縁部と第二段FETチップとの距離よりも短い。

40

【0009】

50

この増幅装置では、第一段 FET チップが一方の縁部寄りに配置されており、第二段 FET チップが他方の縁部寄りに配置されている。これにより、入力端子と第一段 FET チップとを接続する第一ボンディングワイヤ、及び出力端子と第二段 FET チップとを接続する第三ボンディングワイヤを従来よりも短くすることができるので、第一ボンディングワイヤ及び第三ボンディングワイヤのインダクタンスを低くすることができる。また、通常、第一段 FET チップの入力端子及び出力端子の各インピーダンスは、外部インピーダンスに近く十分な大きさを有する。また、第二段 FET チップの出力端子のインピーダンスは、入力端子のインピーダンスと比較して十分に高い。従って、上記の増幅装置によれば、入力端子と第一段 FET チップとの間の整合回路、及び出力端子と第二段 FET チップとの間の整合回路を削減することができ、部品コストや実装工数を抑えることができる。

10

## 【 0 0 1 0 】

( 2 ) また、上記増幅装置において、第四ボンディングワイヤの一つの長さと第五ボンディングワイヤの一つの長さの合計は、第三ボンディングワイヤの一つの長さよりも長くてもよい。

## 【 0 0 1 1 】

( 3 ) また、上記増幅装置において、第一段 FET チップの入力端子のインピーダンスは、第二段 FET チップの入力端子のインピーダンスよりも高く、第一段 FET チップの出力端子のインピーダンスは、第二段 FET チップの出力端子のインピーダンスよりも高くてよい。

20

## 【 0 0 1 2 】

( 4 ) また、上記増幅装置において、一対の縁部に沿った方向における出力端子の幅は、該方向における入力端子、第一段間端子、及び第二段間端子の幅よりも大きくてよい。通常、第二段 FET チップからの出力電力は、第一段 FET チップの入力電力及び出力電力よりも格段に大きい。従って、出力端子の幅が他の端子の幅よりも大きいことにより、出力端子の抵抗値を低減して大きな電力を効率良く出力することができる。

## 【 0 0 1 3 】

( 5 ) また、上記増幅装置は、一方の縁部に設けられ、第一段間端子と第二段間端子との間に配置された第三端子を更に備え、第三端子はグランド電位を有する端子であってもよい。これにより、一方の縁部の端子間のアイソレーションを高めることができる。

30

## 【 0 0 1 4 】

( 6 ) また、上記増幅装置において、第一段間端子と第二段間端子とはパッケージの外部において互いに接続されてもよい。

## 【 0 0 1 5 】

( 7 ) また、上記増幅装置において、第二段 FET チップのチップサイズは第一段 FET チップのチップサイズよりも大きくてよい。これにより、第一段 FET チップからの出力電力よりも大きい出力電力を第二段 FET チップが好適に生成することができる。

## 【 0 0 1 6 】

[ 本願発明の実施形態の詳細 ]

本発明の実施形態にかかる増幅装置の具体例を、以下に図面を参照しつつ説明する。なお、本発明はこれらの例示に限定されるものではなく、特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内でのすべての変更が含まれることが意図される。以下の説明では、図面の説明において同一の要素には同一の符号を付し、重複する説明を省略する。

40

## 【 0 0 1 7 】

( 第 1 の実施の形態 )

図 1 は、本実施形態に係る増幅装置 1A の構成を模式的に示す平面図である。図 1 に示されるように、増幅装置 1A は、パッケージ 10 と、リードフレームのダイスステージ 11 と、入力端子 12 と、第一段間端子 13 と、第二段間端子 14 と、出力端子 15, 16 と、第一段 FET チップ 20 と、第二段 FET チップ 30 と、キャパシタ素子 40 とを備え

50

ている。

【0018】

パッケージ10は、例えばモールド成形されたエポキシ樹脂等の樹脂材料によって構成され、第一段FETチップ20、第二段FETチップ30、及びキャパシタ素子40を内蔵する。パッケージ10は、例えば長方形形状といった平面形状を有しており、第一方向A1に並んだ一対の縁部10a, 10bを有する。縁部10a, 10bは、第一方向A1と交差する第二方向A2に沿って延びている。ダイスステージ11は、金属製の板状部材である。ダイスステージ11は、パッケージ10の下面（配線基板に実装される際に該配線基板と対向する側の面）に設けられており、パッケージ10から露出している。ダイスステージ11上には、第一段FETチップ20、第二段FETチップ30、及びキャパシタ素子40が実装されている。10

【0019】

入力端子12、第一段間端子13、第二段間端子14、及び出力端子15, 16は、金属製の端子であって、パッケージ10の下面に設けられており、パッケージ10から露出している。これらのうち、入力端子12、第一段間端子13、及び第二段間端子14は、パッケージの一方の縁部10aにおいてこの順に並んで設けられている。また、出力端子15, 16は、パッケージの他方の縁部10bにおいて並んで設けられている。入力端子12には、パッケージ10の外部から電気的な入力信号が与えられる。第一段間端子13は、後述する第一段FETチップ20からの電気的な出力信号をパッケージ10の外部へ出力する。第二段間端子14は、例えばパッケージ10の外部において第一段間端子13と電気的に接続され、第一段間端子13から出力された電気信号を入力する。出力端子15, 16は、後述する第二段FETチップ30からの電気的な出力信号をパッケージ10の外部へ出力する。なお、他方の縁部10bには更に一つの端子91が設けられているが、この端子91は未使用端子である。未使用端子とは、パッケージ10内において、他の端子とボンディングワイヤで接続されていない端子である。20

【0020】

第一段FETチップ20は、例えば高移動度トランジスタ（HEMT）といったFETを内蔵するチップであって、入力端20a及び出力端20bを有する。第一段FETチップ20は、入力端20aに入力された電気信号を増幅し、増幅後の電気信号を出力端20bから出力する。入力端20aは例えばゲートであり、出力端20bは例えばドレインである。その場合、ソースはダイスステージ11に接続される。ダイスステージ11は、例えば基準電位（接地電位）とされる。30

【0021】

第一段FETチップ20は、パッケージ10の内部において、一方の縁部10a寄りの領域に配置されている。すなわち、一方の縁部10aと第一段FETチップ20との距離D1は、他方の縁部10bと第一段FETチップ20との距離D2よりも短い。より好ましくは、第一段FETチップ20は、パッケージ10の中心線C1に対して縁部10a側の領域内に配置される。入力端20aは、ボンディングワイヤ17a（第一ボンディングワイヤ）によって入力端子12と直接的に接続されている。また、出力端20bは、ボンディングワイヤ17b（第二ボンディングワイヤ）によって第一段間端子13と直接的に接続されている。ここで、直接的とは、能動的又は受動的な回路要素を含む他のチップを一切介しておらず互いに短絡されているという意味である。なお、入力端20aのインピーダンスは、入力端子12のインピーダンスと等しいことが好ましい。40

【0022】

第二段FETチップ30は、例えばHEMTといったFETを内蔵するチップであって、入力端30a及び出力端30bを有する。第二段FETチップ30は、入力端30aに入力された電気信号を増幅し、増幅後の電気信号を出力端30bから出力する。入力端30aは例えばFETのゲートであり、出力端30bは例えばFETのドレインである。その場合、FETのソースはダイスステージ11に接続される。

【0023】

50

第二段FETチップ30は、パッケージ10の内部において、他方の縁部10b寄りの領域に配置されている。すなわち、他方の縁部10bと第二段FETチップ30との距離D3は、一方の縁部10aと第二段FETチップ30との距離D4よりも短い。より好ましくは、第二段FETチップ30は、パッケージ10の中心線C1に対して縁部10b側の領域内に配置される。出力端30bは、ボンディングワイヤ17c（第三ボンディングワイヤ）によって出力端子15, 16と直接的に接続されている。この第二段FETチップ30は、第一段FETチップ20によって増幅された電気信号を更に増幅する。そのため、第二段FETチップ30のチップサイズL2は、第一段FETチップ20のチップサイズL1よりも大きい。なお、第一段FETチップ20の入力端20aのインピーダンスは、第二段FETチップ30の入力端30aのインピーダンスよりも高いことが好ましい。また、第一段FETチップ20の出力端20bのインピーダンスは、第二段FETチップ30の出力端30bのインピーダンスよりも高いことが好ましい。10

#### 【0024】

キャパシタ素子40は、インピーダンス整合用のキャパシタを内蔵する素子であって、一対の電極を有する。キャパシタ素子40の一方の電極40aは、ボンディングワイヤ17d（第四ボンディングワイヤ）を介して第二段間端子14と直接的に接続されている。また、この一方の電極40aは、ボンディングワイヤ17e（第五ボンディングワイヤ）を介して第二段FETチップ30の入力端30aと直接的に接続されている。キャパシタ素子40の他方の電極は、ダイスステージ11に接続されている。ボンディングワイヤ17dの一つの長さとボンディングワイヤ17eの一つの長さとの合計は、ボンディングワイヤ17cの一つの長さよりも長い。20

#### 【0025】

図2は、配線基板50上に増幅装置1Aが実装された様子を示す側断面図である。また、図3は、配線基板50の配線パターンを示す平面図である。図2及び図3に示されるように、配線基板50は、誘電体基板58と、配線パターン51～55と、基準電位用の配線パターン56とを備える。誘電体基板58は、正面58a及び裏面58bを有する。配線パターン51～55は正面58a上に設けられ、基準電位用の配線パターン56は裏面58b上の全面に設けられる。配線パターン51の一端部51aには、入力端子12が導電性接着剤（例えば銀ペースト）を介して接合される。配線パターン52の一端部52a及び他端部52bそれぞれには、第一段間端子13及び第二段間端子14それぞれが導電性接着剤59aを介して接合される。これにより、第一段間端子13と第二段間端子14とは、パッケージ10の外部において互いに接続される。配線パターン53の一端部53aには、出力端子15, 16が導電性接着剤59bを介して接合される。配線パターン54は、ダイスステージ11と対向する位置に設けられており、導電性接着剤59cを介してダイスステージ11と接合される。この配線パターン54は、正面58aと裏面58bとの間を貫通する複数のスルービア57を介して、基準電位用の配線パターン56と電気的に接続されている。なお、配線パターン55には未使用端子91が接合される。30

#### 【0026】

図4(a)及び図4(b)は、第一段FETチップ20及び第二段FETチップ30の拡大断面図である。図4(a)に示されるように、第一段FETチップ20は、半導体基板（例えばGaN基板若しくはGaN基板）21と、半導体基板21の正面21a上に設けられた、入力端20aとしてのゲートパッド22、ソースパッド23、及び出力端20bとしてのドレインパッド24とを有する。半導体基板21の裏面21bは、導電性接着剤（例えば銀ペースト）18を介してダイスステージ11に接合されている。ゲートパッド22及びドレインパッド24には、ボンディングワイヤ17a及び17bの各一端がそれぞれ接合されている。ソースパッド23は、半導体基板21を正面21aから裏面21bに貫通するソースビア25を介して導電性接着剤18と電気的に接続されている。また、図4(b)に示されるように、第二段FETチップ30は、半導体基板（例えばGaN基板若しくはGaN基板）31と、半導体基板31の正面31a上に設けられた、入力端30aとしてのゲートパッド32、ソースパッド33、及び出力端30bとしてのド40

レインパッド34とを有する。半導体基板31の裏面31bは、導電性接着剤（例えば銀ペースト）19を介してダイスステージ11に接合されている。ゲートパッド32及びドレインパッド34には、ボンディングワイヤ17e及び17cの各一端がそれぞれ接合されている。ソースパッド33は、半導体基板31を正面31aから裏面31bに貫通するソースピア35を介して導電性接着剤19と電気的に接続されている。

【0027】

図5は、本実施形態の増幅装置1Aの使用例を示す回路図である。図5に示されるように、入力端子12には入力側整合回路61が接続され、入力信号は入力側整合回路61を介して入力端子12に入力される。また、第一段間端子13と第二段間端子14との間には段間整合回路62が接続され、第一段間端子13から出力された信号は段間整合回路62を介して第二段間端子14に入力される。また、出力端子15, 16には出力側整合回路63が接続され、出力信号は出力側整合回路63を介してパッケージ10の外部へ出力される。

10

【0028】

図5に示されるように、入力端子12にはゲートバイアス回路64が接続されてもよい。ゲートバイアス回路64は、例えば入力端子12と接地電位線との間に直列に接続された抵抗64a及びキャパシタ64bを有し、抵抗64aとキャパシタ64bとの間のノードにゲートバイアス電圧VG1が入力される。同様に、第二段間端子14にはゲートバイアス回路65が接続されてもよい。ゲートバイアス回路65は、例えば第二段間端子14と接地電位線との間に直列に接続された抵抗65a及びキャパシタ65bを有し、抵抗65aとキャパシタ65bとの間のノードにゲートバイアス電圧VG2が入力される。

20

【0029】

図5に示されるように、第一段間端子13にはドレインバイアス回路66が接続されてもよい。ドレインバイアス回路66は、例えば第一段間端子13と接地電位線との間に直列に接続されたインダクタ66a及びキャパシタ66bを有し、インダクタ66aとキャパシタ66bとの間のノードにドレインバイアス電圧VD1が入力される。同様に、出力端子15, 16にはドレインバイアス回路67が接続されてもよい。ドレインバイアス回路67は、例えば出力端子15, 16と接地電位線との間に直列に接続されたインダクタ67a及びキャパシタ67bを有し、インダクタ67aとキャパシタ67bとの間のノードにドレインバイアス電圧VD2が入力される。

30

【0030】

以上の構成を備える増幅装置1Aによって得られる作用効果について説明する。この増幅装置1Aでは、前段の増幅回路である第一段FETチップ20と、後段の増幅回路である第二段FETチップ30とが別のチップで構成されている。また、第一段FETチップ20の入力端20aに接続される入力端子12と、第一段FETチップ20の出力端20bに接続される第一段間端子13とが、パッケージ10の同じ側（縁部10a）に配置されている。そして、第一段FETチップ20がパッケージ10の一方の縁部10a寄りに配置されている。このような構成により、入力端子12と第一段FETチップ20とを接続するボンディングワイヤ17a、及び第一段間端子13と第一段FETチップ20とを接続するボンディングワイヤ17bを従来よりも短くし、これらのインダクタンスを小さくすることができる。ここで、第一段FETチップ20に求められる最大出力は第二段FETチップ30よりも小さい（第一段FETチップ20のフィンガの数は、少なくて良い）ので、第一段FETチップ20のゲート電極（すなわち入力端20a）及びドレン電極（すなわち出力端20b）のサイズを小さくすることができる。従って、第一段FETチップ20の入力端20a及び出力端20bのインピーダンスを比較的高くすることが可能である。すなわち、ボンディングワイヤ17a, 17bのインダクタンスが小さいこと、並びに、入力端20a及び出力端20bのインピーダンスを比較的高くすることが可能であることに鑑みれば、第一段FETチップ20に関して整合回路を不要とすることができる。

40

【0031】

50

また、第二段 F E T チップ 3 0 に関しては、第一段 F E T チップ 2 0 よりも大きな最大出力が要求される。従って、ゲート電極（すなわち入力端 3 0 a）のサイズは、第一段 F E T チップ 2 0 の当該サイズよりも大きくなる。ゆえに、入力端 3 0 a のインピーダンスは極めて低くなる（典型的には 1 以下）。このため、第二段間端子 1 4 に第二段 F E T チップ 3 0 を近づけたとしても、ボンディングワイヤのインダクタンスの影響は大きくなる。このことから、入力端 3 0 a と第二段間端子 1 4 との間には、インピーダンス整合のためのキャパシタ素子 4 0 が配置されることが望ましい。

#### 【 0 0 3 2 】

一方、第二段 F E T チップ 3 0 のドレイン電極（すなわち出力端 3 0 b）のインピーダンスは、ゲート電極（入力端 3 0 a）と比較して十分に高い。その理由は次の通りである。通常、ゲート電極のインピーダンス（入力インピーダンス）の主な要因は、ゲート - ソース間のショットキー接合容量である。従って、入力信号の周波数が例えばマイクロ波帯といった高い周波数になると、入力インピーダンスは例えば 1 以下といった低い値となる。しかし、ドレイン電極のインピーダンス（出力インピーダンス）の主な要因はチャネルの抵抗成分であるので、その出力インピーダンスは例えば数 程度となり、入力インピーダンスよりも高くなる。このことから、本実施形態では、第二段 F E T チップ 3 0 を他方の縁部 1 0 b 寄りに配置している。これにより、出力端子 1 5, 1 6 と第二段 F E T チップ 3 0 とを接続するボンディングワイヤ 1 7 c を従来よりも短くし、ボンディングワイヤ 1 7 c のインダクタンスを小さくできる。ボンディングワイヤ 1 7 c の長さは、ボンディングワイヤ 1 7 e の長さよりも短い。なお、ボンディングワイヤ 1 7 c およびボンディングワイヤ 1 7 e のそれぞれの長さは、キャパシタ素子 4 0 の容量により適宜選択されるため、必ずしも、ボンディングワイヤ 1 7 c の長さがボンディングワイヤ 1 7 e の長さよりも短い関係にはならない。すなわち、ボンディングワイヤ 1 7 c のインダクタンスが小さいこと、並びに、出力端 3 0 b のインピーダンスを比較的高くすることが可能であることに鑑みれば、第二段 F E T チップ 3 0 の出力端 3 0 b に関して整合回路を不要とすることはできる。

#### 【 0 0 3 3 】

上述したように、本実施形態の增幅装置 1 A によれば、入力端子 1 2 と第一段 F E T チップ 2 0 との間の整合回路、及び出力端子 1 5, 1 6 と第二段 F E T チップ 3 0 との間の整合回路を不要とすることができます。従って、整合回路の数を削減して部品コストや実装工数を抑えることができる。

#### 【 0 0 3 4 】

また、本実施形態のように、入力端子 1 2 のインピーダンスと、第一段 F E T チップ 2 0 の入力端 2 0 a のインピーダンスとは互いに等しくてもよい。これにより、入力端子 1 2 と入力端 2 0 a との間の整合回路を更に不要とすることができます。

#### 【 0 0 3 5 】

また、本実施形態のように、第一段 F E T チップの出力端はドレインであり、第二段 F E T チップの入力端はゲートであってもよい。これにより、上記の効果を奏する増幅装置 1 A を好適に構成することができる。

#### 【 0 0 3 6 】

また、本実施形態のように、第二段 F E T チップ 3 0 のチップサイズ L 2 は、第一段 F E T チップ 2 0 のチップサイズ L 1 よりも大きくてよい。これにより、第一段 F E T チップ 2 0 からの出力電力よりも大きい出力電力を第二段 F E T チップ 3 0 が好適に生成することができる。

#### 【 0 0 3 7 】

また、本実施形態のように、複数の出力端子 1 5, 1 6 が第二段 F E T チップ 3 0 の出力端 3 0 b に接続されてもよい。これにより、第二段 F E T チップ 3 0 のチップサイズ L 2 が大きく出力端 3 0 b が多数配列されている場合であっても、これらの出力端 3 0 b にそれぞれ接続される多数のボンディングワイヤ 1 7 c の長さのばらつきを抑えることができる。

10

20

30

40

50

## 【0038】

なお、本実施形態において、第一FETチップ20の出力端20bとキャパシタ素子40の電極40aとを、第一段間端子13及び第二段間端子14を介さずに、パッケージ10内部において接続することも考えられる。しかし、そのような態様では、段間整合回路62(図5を参照)、第一段FETチップ20のドレインバイアス回路66、第二段FETチップ30のゲートバイアス回路65、及びDCブロック等がパッケージ10の内部に集積される必要が生じる。また、第一段FETチップ20のドレインバイアス回路66及び第二段FETチップ30のゲートバイアス回路65のために少なくとも2つの電圧入力端子が追加される必要が生じる。従って、そのような態様では、上記実施形態と比較して部品コストや実装工数が増加してしまう。具体的には、パッケージ10の内部の実装には微細実装技術が必要となるが、これは製造コストの増加要因となる。高周波の信号を扱う際に大きな影響がなければ、增幅装置1Aを使用する者が、段間整合回路62、ドレインバイアス回路66、ゲートバイアス回路65、及びDCブロック等を外付けした方が、製造コストを低減できる場合が多い。增幅装置1Aを使用する際には配線基板50上に他の部品を必ず実装するので、これらの外付け部品が追加されても実装工数はあまり変わらないからである。また、段間整合回路62、ドレインバイアス回路66、ゲートバイアス回路65、及びDCブロック等を外付けすることにより、部品交換による特性調整なども容易に行うことができる。本実施形態によれば、第一FETチップ20の出力端20bとキャパシタ素子40の電極40aとを、第一段間端子13及び第二段間端子14を介してパッケージ10の外部で接続することによって、部品コストや実装工数をより効果的に抑えることができる。

## 【0039】

## (第1の変形例)

図6は、上記実施形態の第1変形例に係る増幅装置1Bの構成を示す平面図である。本変形例の増幅装置1Bと上記実施形態の増幅装置1Aとの相違点は、端子の数及び配置である。すなわち、本変形例では、8つの端子を有するパッケージが用いられており、上記実施形態の構成に加えて、2つの端子92, 93が更に設けられている。端子92, 93は、共に未使用端子である。端子92(第三端子)は、一方の縁部10aに設けられており、端子93は、他方の縁部10bに設けられている。端子92は、入力端子12と第一段間端子13との間に配置されている。端子93は、端子91と出力端子15, 16との間に配置されている。

## 【0040】

上記実施形態では、第一段FETチップ20の入力端20aに接続された入力端子12と、第一段FETチップ20の出力端20aに接続された第一段間端子13とが共に縁部10aに隣接されて配置されている。従って、第一段FETチップ20の入力と出力とのアイソレーションが低下する場合がある。これに対し、本変形例のように、未使用端子である端子92が入力端子12と第一段間端子13との間に配置され、且つグランドに接地されることにより、アイソレーションを高めることができる。なお、未使用端子は、グランドに接地されていなくても良い。

## 【0041】

なお、図6に示されるように、入力端子12と第一段間端子13とは、直列に接続されたキャパシタ81及び抵抗82を介して相互に接続されてもよい。

## 【0042】

## (第2の変形例)

図7は、上記実施形態の第2変形例に係る増幅装置1Cの構成を示す平面図である。本変形例の増幅装置1Cと上記実施形態の増幅装置1Aとの相違点は、端子の数及び形状である。すなわち、本変形例では、上記実施形態の出力端子15, 16に代えて、一つの出力端子71が設けられている。また、未使用端子であった端子91(図1を参照)が省かれている。

## 【0043】

10

20

30

40

50

本変形例では、一対の縁部 10a, 10b に沿った方向（第二方向 A2）における出力端子 71 の幅 W1 が、同方向における他の端子（入力端子 12、第一段間端子 13、及び第二段間端子 14）の各幅 W2 よりも大きい。汎用パッケージではなく専用パッケージを設計することにより、このような端子の態様が可能となる。

#### 【0044】

通常、第二段 FET チップ 30 からの出力電力は、第一段 FET チップ 20 の入力電力及び出力電力よりも格段に大きい。従って、本変形例のように、出力端子 71 の幅が他の端子 12 ~ 14 の幅よりも大きいことにより、出力端子 71 の抵抗値を低減して大きな電力を効率良く出力することができる。

#### 【0045】

本発明による増幅装置は、上述した実施形態に限られるものではなく、他に様々な変形が可能である。例えば、上述した実施形態では、樹脂材料がモールド成形されてなるパッケージが例示されているが、パッケージの種類はこれに限られず、例えばハーメチックシールタイプでもよい。また、上述した実施形態では、第一段 FET チップ及び第二段 FET チップの半導体材料として GaN 及び GaAs が例示されているが、本発明はこれらの半導体材料に限られない。

#### 【符号の説明】

#### 【0046】

1A, 1B, 1C … 増幅装置、10 … パッケージ、10a, 10b … 縁部、11 … ダイスステージ、12 … 入力端子、13 … 第一段間端子、14 … 第二段間端子、15, 16 … 出力端子、17a ~ 17e … ボンディングワイヤ、18, 19 … 導電性接着剤、20 … 第一段 FET チップ、21, 31 … 半導体基板、22, 32 … ゲートパッド、23, 33 … ソースパッド、24, 34 … ドレインパッド、25, 35 … ソースビア、30 … 第二段 FET チップ、40 … キャパシタ素子、50 … 配線基板、51 ~ 56 … 配線パターン、57 … スルービア、58 … 誘電体基板、61 … 入力側整合回路、62 … 段間整合回路、63 … 出力側整合回路、71 … 出力端子、A1 … 第一方向、A2 … 第二方向、C1 … 中心線。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

審査官 石川 雄太郎

(56)参考文献 特開2002-111415(JP, A)

米国特許出願公開第2004/0174219(US, A1)

特開平06-326530(JP, A)

特開昭60-086904(JP, A)

特開2008-228347(JP, A)

特開平09-223773(JP, A)

米国特許第6162697(US, A)

特開2008-118624(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03F 1/00 - 3/72