(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5145988号

(P5145988)

(45) 発行日 平成25年2月20日(2013.2.20)

(24) 登録日 平成24年12月7日(2012.12.7)

(51) Int.Cl.

H03B 5/36 (2006.01)

H03B 5/30 (2006.01)

F 1

H03B 5/36

H03B 5/30

H03B 5/30A

E

請求項の数 7 (全 16 頁)

(21) 出願番号 特願2008-26011 (P2008-26011)

(22) 出願日 平成20年2月6日 (2008.2.6)

(65) 公開番号 特開2008-245255 (P2008-245255A)

(43) 公開日 平成20年10月9日 (2008.10.9)

審査請求日 平成22年12月27日 (2010.12.27)

(31) 優先権主張番号 特願2007-46601 (P2007-46601)

(32) 優先日 平成19年2月27日 (2007.2.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107261

弁理士 須澤 修

(74) 代理人 100127661

弁理士 宮坂 一彦

(72) 発明者 矢島 有継

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72) 発明者 足立 武彦

神奈川県横浜市南区通町4-113

最終頁に続く

(54) 【発明の名称】発振回路、発振器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1能動素子と、第2能動素子と、が備えられ、

前記第1能動素子と前記第2能動素子とが差動接続されるクロスカップル型回路を含み、前記第1能動素子と前記第2能動素子との間に接続される振動子の共振点帯域で発振し

前記第1能動素子のソース端子は第1ソース負荷回路を介してGNDに接続され、

前記第2能動素子のソース端子は第2ソース負荷回路を介してGNDに接続され、

前記第1能動素子のドレイン端子は第1ドレイン負荷回路を介して電源電圧に接続され

前記第2能動素子のドレイン端子は第2ドレイン負荷回路を介して電源電圧に接続されており、

前記第1ソース負荷回路のインピーダンスの大きさが前記第1ドレイン負荷回路のインピーダンスの大きさ以上であり、かつ、

前記第2ソース負荷回路のインピーダンスの大きさが前記第2ドレイン負荷回路のインピーダンスの大きさ以上であり、

前記第1能動素子のドレイン端子と前記第1ドレイン負荷回路の間から、前記第2能動素子のドレイン端子と前記第2ドレイン負荷回路の間を接続するコンデンサを備えることを特徴とする発振回路。

## 【請求項 2】

請求項 1に記載の発振回路において、

前記コンデンサの容量が、前記振動子の並列容量の半分であることを特徴とする発振回路。

【請求項 3】

請求項 1に記載の発振回路において、

前記第1ソース負荷回路と、前記第2ソース負荷回路と、前記第1ドレイン負荷回路と、前記第2ドレイン負荷回路のそれぞれが、定電流回路から構成されていることを特徴とする発振回路。

【請求項 4】

請求項 3に記載の発振回路において、

前記第1能動素子のソース端子とドレイン端子との間、前記第2能動素子のソース端子とドレイン端子との間それぞれに、振幅一定化回路が備えられていることを特徴とする発振回路。

【請求項 5】

請求項 4に記載の発振回路において、

前記第1能動素子のゲート端子と前記第2能動素子のドレイン端子との間、前記第2能動素子のゲート端子と前記第1能動素子のドレイン端子との間それぞれにコンデンサが備えられていることを特徴とする発振回路。

【請求項 6】

請求項 4に記載の発振回路において、

前記第1能動素子のゲート端子とドレイン端子との間、前記第2能動素子のゲート端子とドレイン端子の間それぞれに増幅器が備えられていることを特徴とする発振回路。

【請求項 7】

請求項 1～6のいずれか一項に記載の発振回路が備えられていることを特徴とする発振器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、クロスカップル型回路を備える発振回路、及びこの発振回路と振動子とを備える発振器に関する。

【背景技術】

【0002】

従来、振動子を用いた発振回路として、コルピツツ発振回路が一般的に用いられている。従来のコルピツツ回路において発振するためには、利得が4以上必要であることが知られている（例えば、非特許文献1を参照）。利得と負性抵抗は比例するので、発振するためには、4以上の利得に比例した負性抵抗以上とせざるを得ない。

【0003】

一方、移動通信機をはじめ、センサネットワークなどにおいてその多くは電池により駆動されている。したがって、回路の消費電力は所望の動作を満たしながら極力低いことが望ましい。発振回路の消費電力を下げるためには、印加する電流を少なくせざるを得ない。しかしながら電流を少なくすると利得も小さくなる。利得と負性抵抗は比例するので、利得が低下すると負性抵抗も低下する。そのため発振条件を満たすことが困難になる。

【0004】

このような課題を解決するために、負性抵抗を低下させる要因である振動子の端子間容量を減らしたり、回路のレイアウトにおいて寄生成分を最小にする工夫が取られているが、負性抵抗の増加には至っていない。

【0005】

この問題を解決するために、例えば特許文献1では、負性抵抗増加回路を設け、所望の周波数において負性抵抗を増加させている。この回路は発振回路の出力から容量を介して帰還回路を構成し、負性抵抗を増加させている。

10

20

30

40

50

**【0006】**

また、クロスカッフル型回路を用いた発振回路も知られている（例えば、特許文献2参照）。特許文献2では、1対の能動素子（MOSトランジスタ）のドレイン端子に振動子（共振子）を接続する構成であり、振動子の反共振点帯域で発振させている。

**【0007】**

【特許文献1】特開2006-60687号公報

【特許文献2】米国特許第6696899号明細書

【非特許文献1】村田誠四郎著『アナログCMOS集積回路の設計応用編』平成17年7月30日発行611頁

**【発明の開示】**

10

**【発明が解決しようとする課題】****【0008】**

しかしながら特許文献1では、負性抵抗増加のために新たな回路を必要とするため、附加した回路の消費電力分の電力は増加する。また帰還容量の精度に負性抵抗値が影響を受けるため、負性抵抗がばらつき、所望の負性抵抗を満足しない可能性がある。

**【0009】**

また、一般に振動子反共振点帯域を使用する発振回路では、共振点帯域を使用する場合よりも振動子のQ特性が劣ることが知られている。従って、上述の特許文献2の構成では振動子のQ特性がよい発振回路の実現は困難であると予測される。

**【課題を解決するための手段】**

20

**【0010】**

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の実施の形態として実現することが可能である。

**【0011】**

上記課題を解決するために、本発明の発振回路は、第1能動素子と、第2能動素子と、が備えられ、前記第1能動素子と前記第2能動素子とが差動接続されるクロスカッフル型回路を含み、前記第1能動素子と前記第2能動素子との間に接続される振動子の共振点帯域で発振することを特徴とする。

なお、ここで第1能動素子及び第2能動素子としては、例えば、MOSトランジスタを採用することができる。

30

**【0012】**

このような構成によれば、クロスカッフル型回路の利得は、2倍以上の利得があれば良い。発振に必要な利得が小さいことは、電流を少なくすることができる。よって、回路の消費電力を下げることができる。

**【0013】**

さらに、第1能動素子と第2能動素子が交互に動作するため、クロスカッフル型回路における消費電流を半分にすることができる。よって、回路の消費電力を下げることができる。

**【0014】**

また、この発振回路は振動子の共振点帯域を使用するため、Q特性の優れた発振回路を実現できるという効果を有する。

40

**【0015】**

また、上述した発振回路の構成は、前記第1能動素子のソース端子は第1ソース負荷回路を介してGNDに接続され、前記第2能動素子のソース端子は第2ソース負荷回路を介してGNDに接続され前記第1能動素子のドレイン端子は第1ドレイン負荷回路を介して電源電圧に接続され、前記第2能動素子のドレイン端子は第2ドレイン負荷回路を介して電源電圧に接続されており、前記第1ソース負荷回路のインピーダンスの大きさが前記第1ドレイン負荷回路のインピーダンスの大きさ以上であり、かつ、前記第2ソース負荷回路のインピーダンスの大きさが前記第2ドレイン負荷回路のインピーダンスの大きさ以上であることが好ましい。

50

## 【0016】

この発振器によれば、周波数が振動子の共振周波数よりも小さい場合に、発振回路が発振することを抑制することができる。なぜなら、周波数が振動子の共振周波数よりも小さい場合、振動子のインピーダンスは大きい。ここで、第1ソース負荷回路のインピーダンスが周波数に依存しない値であれば、第1能動素子のソース端子とGNDの間のインピーダンスは、第1ソース負荷回路のインピーダンスが支配的となる。ここで、この発振器の利得は、第1能動素子のソース端子とGNDの間のインピーダンスに対する第1ドレイン負荷回路のインピーダンスである。よって、この発振器の利得は、第1ソース負荷回路のインピーダンスに対する第1ドレイン負荷回路のインピーダンスで決定されることになる。そこで、第1ソース負荷回路のインピーダンスの大きさが第1ドレイン負荷回路のインピーダンスの大きさ以上であれば、利得が1以下となり、発振することはない。第2ソース負荷回路のインピーダンスと第1ドレイン負荷回路のインピーダンスの関係も同様である。10

## 【0017】

また、上記構成による発振回路は、前記第1能動素子のドレイン端子と前記第2能動素子のドレイン端子との間に接続されたコンデンサを備えることが好ましい。

## 【0018】

このような構成によれば、発振回路の周波数が振動子の共振周波数よりも大きい場合に、発振回路が発振することを抑制することができる。なぜなら、発振回路の周波数が振動子の共振周波数よりも大きい場合、第1能動素子のソース端子とGNDの間のインピーダンスは、振動子の等価回路の並列容量によるインピーダンスが支配的となる。また、第1能動素子のドレイン端子と第2能動素子のドレイン端子との間に接続されたコンデンサを備えることにより、第1能動素子のドレイン端子と電源電圧の間のインピーダンスは、コンデンサによるインピーダンスが支配的となる。利得は、並列容量によるインピーダンスに対するコンデンサによるインピーダンスの比で表すことができる。従って、コンデンサを設けることにより利得が増加することなく、共振点帯域外の発振を抑制することができる。なお、第2能動素子のソース端子とGNDの間のインピーダンスと第2能動素子のドレイン端子と電源電圧の間のインピーダンスとの関係についても、同様である。20

## 【0019】

また、上記構成に係る発振回路は、前記コンデンサの容量が、前記振動子の並列容量の半分であることが好ましい。30

## 【0020】

このような構成によれば、第1能動素子のソース端子とGNDの間のインピーダンスが大きくなつても、第1能動素子のドレイン端子と電源電圧の間のインピーダンスも大きくなるので、利得を抑制することができる。したがつて、振動子の共振周波数より大きい周波数での発振を抑制することができる。なお、第2能動素子においても同様である。

## 【0021】

また、上記構成に係る発振回路は、前記第1ドレイン負荷回路と並列接続されるコンデンサと、前記第2ドレイン負荷回路と並列接続されるコンデンサと、が備えられていることが好ましい。40

## 【0022】

このような構成によれば、第1ドレイン負荷回路と第2ドレイン負荷回路それぞれに並列接続されるコンデンサを設けることにより、振動子の並列容量よりも各ドレイン端子と電源電圧との間の容量が小さくなり、そのことにより、振動子の並列容量によるインピーダンス（ソース端子側のインピーダンス）よりも各ドレイン端子側のインピーダンスが小さくなることにより、共振点帯域外における利得を低下させて共振点帯域外の共振を抑制することができる。

## 【0023】

また、上記構成の発振回路は、前記コンデンサの容量が、前記振動子の並列容量の半分であることが好ましい。50

**【 0 0 2 4 】**

このようにすれば、各ドレイン端子側のインピーダンスの総和が、各ソース端子側のインピーダンスよりも極めて小さくなることから、共振点帯域外における利得を低下させて共振点帯域外の共振をより一層抑制することができる。

**【 0 0 2 5 】**

また、上記構成の発振回路において、前記第1ソース負荷回路と、前記第2ソース負荷回路と、前記第1ドレイン負荷回路と、前記第2ドレイン負荷回路のそれぞれが、定電流回路から構成されていることが好ましい。

**【 0 0 2 6 】**

また、第1ドレイン負荷回路および第2ドレイン負荷回路を定電流回路とし、第1ソース負荷回路および第2ソース負荷回路を定電流回路とすることにより、各ドレイン端子側のインピーダンスを各ソース端子側のインピーダンスよりも小さく設定することで振動子の直列共振周波数よりも小さい周波数における発振を抑制することができる。 10

**【 0 0 2 7 】**

また、上記構成に係る発振回路は、並列接続されたコンデンサとインダクタとから構成される前記第1ソース負荷回路及び前記第2ソース負荷回路と、並列接続されたコンデンサとインダクタとから構成される前記第1ドレイン負荷回路及び前記第2ドレイン負荷回路と、が備えられていることが好ましい。

**【 0 0 2 8 】**

このように並列接続されたコンデンサとインダクタによって構成された回路はLC並列共振回路と呼ばれる。クロスカップル型回路で利得を最大（つまり、発振しやすくする）にするためには、ドレイン端子側のインピーダンスが最大になるようにLCの定数を設定すればよい。このようにすれば、LC並列共振回路は周波数選択性を有するため、共振周波数（共振点帯域）において最も発振しやすくなる。 20

**【 0 0 2 9 】**

また、ソース端子側に接続するLC並列共振回路の周波数を異常発振の周波数帯域に合わせることにより、ソース端子側のインピーダンスを意図的に増大させて異常発振を抑制する。つまり、LCの定数を異常発振の周波数帯域に合わせることで、異常発振を抑制することができる。

**【 0 0 3 0 】**

また、上記構成による発振回路は、前記第1ソース負荷回路と、前記第2ソース負荷回路と、前記第1ドレイン負荷回路と、前記第2ドレイン負荷回路のそれぞれが、定電流回路から構成されると共に、前記第1能動素子のソース端子とドレイン端子との間、前記第2能動素子のソース端子とドレイン端子との間それぞれに、振幅一定化回路が備えられていることが望ましい。 30

**【 0 0 3 1 】**

このような構成によれば、振幅一定化回路を設けることにより、発振回路からの出力振幅が一定となる。出力振幅が一定になれば発振の起動時間を短縮することができる。

また、能動素子のコモンモードに依存しない回路ができるので、第1能動素子と第2能動素子のミスマッチやオフセットによる影響がなく、このことからも起動時間の短縮化ができると共に、低電圧駆動やノイズ耐性がある回路を実現できる。 40

**【 0 0 3 2 】**

また、上記構成による発振回路は、前記第1能動素子のゲート端子と前記第2能動素子のドレイン端子との間、前記第2能動素子のゲート端子と前記第1能動素子のドレイン端子との間それぞれにコンデンサが備えられていることが望ましい。

**【 0 0 3 3 】**

このような構成によれば、上記のようにコンデンサを配設することにより、MOSトランジスタのゲートとドレインを疎結合（インピーダンス的に極力分離）することで、回路の線形性が向上（回路の歪の減少）し、高調波発振を抑制しノイズ耐性が向上するという効果がある。 50

**【 0 0 3 4 】**

また、上記構成による発振回路は、前記第1能動素子のゲート端子とドレイン端子との間、前記第2能動素子のゲート端子とドレイン端子の間それぞれに増幅器が備えられていることが望ましい。

**【 0 0 3 5 】**

このような構成によれば、増幅器を用いることにより、回路の線形性を向上しながら任意の利得を得ることができるために、発振回路の設計が容易になるという利点を有する。

**【 0 0 3 6 】**

また、本発明の発振器は、第1能動素子と、第2能動素子と、が備えられ、前記第1能動素子と前記第2能動素子とが差動接続されるクロスカッフル型回路を含む発振回路と、前記第1能動素子のソース端子と前記第2能動素子のソース端子との間に接続され、共振点帯域で振動する振動子と、が備えられていることを特徴とする。10

**【 0 0 3 7 】**

このような構成によれば、上述した発振回路を備えていることから低電圧、低電流駆動が可能で、ノイズ耐性が高く、発振の起動性がよい発振器を実現することができる。

**【発明を実施するための最良の形態】****【 0 0 3 8 】**

続いて、発明を実施するための最良の形態を実施例に基づき図面を参照して説明する。

(第1実施例)

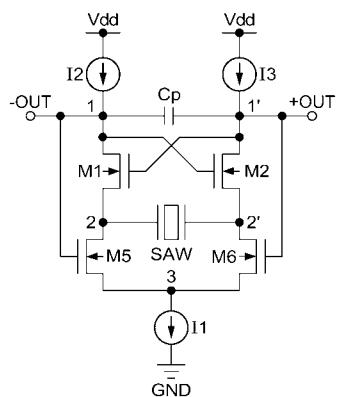

**【 0 0 3 9 】**

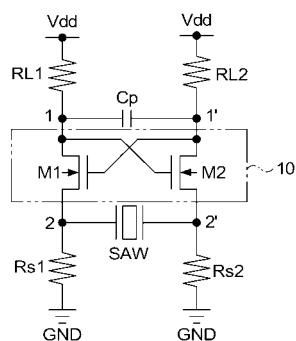

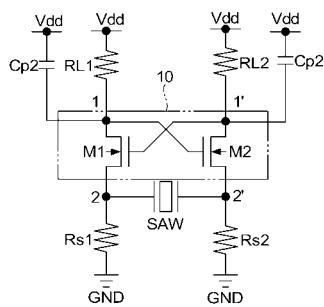

図1は第1実施例に係る発振回路の1例を示す回路図である。図1において、クロスカッフル型回路10は、差動接続された第1能動素子であるNch型トランジスタM1(以降、単にトランジスタM1と表す)と第2能動素子であるNch型トランジスタM2(以降、単にトランジスタM2と表す)で構成されている。つまり、トランジスタM1のドレイン端子はトランジスタM2のゲート端子に接続され、トランジスタM2のドレイン端子はトランジスタM1のゲート端子に接続されている。20

**【 0 0 4 0 】**

トランジスタM1のソース端子2は、第1ソース負荷回路である抵抗器Rs1に接続され、抵抗器Rs1はGNDに接続されている。同様に、トランジスタM2のソース端子2'は、第2ソース負荷回路である抵抗器Rs2に接続され、抵抗器Rs2はGNDに接続されている。30

**【 0 0 4 1 】**

トランジスタM1のドレイン端子は、第1ドレイン負荷回路である抵抗器RL1に接続され、抵抗器RL1は電源電圧Vddに接続されている。同様に、トランジスタM2のドレイン端子は、第2ドレイン負荷回路である抵抗器RL2に接続され、抵抗器RL2は電源電圧Vddに接続されている。

**【 0 0 4 2 】**

トランジスタM1のソース端子2とトランジスタM2のソース端子2'との間には、振動子が接続されている。本実施例では振動子としてSAW(弹性表面波素子)を例示している。振動子SAWの直列共振周波数で、本発明の発振回路は発振する。40

**【 0 0 4 3 】**

なお、以降の実施例を含めて、振動子SAWが含まれない状態を発振回路、振動子SAWを含む状態を発振器と呼ぶ。

**【 0 0 4 4 】**

また、第1トランジスタM1のドレイン端子1と第2トランジスタM2のドレイン端子1'の間には、コンデンサCpが接続されている。

**【 0 0 4 5 】**

続いて、差動接続の動作と消費電力との関係、発振するために必要な利得と消費電力との関係を説明する。

**【 0 0 4 6 】**

10

20

30

40

50

### 差動接続の動作

まず、差動接続の動作について説明する。トランジスタM1がON時はトランジスタM2がOFFになり、トランジスタM1がOFFの時はトランジスタM2がONになる。このように、クロスカップル型回路10では、トランジスタM1とトランジスタM2が交互にONまたはOFFになる。つまり、トランジスタM1とトランジスタM2が交互に動作する。よって、クロスカップル型回路全体で考えると、ドレイン端子に流れる電流は1/2になる。

#### 【0047】

##### 発振するために必要な利得

続いて、クロスカップル型回路10が発振するために必要な利得について説明する。

10

クロスカップル型回路10が発振するためには、利得が1より大きいことが必要である。利得は、相互コンダクタンスと負荷抵抗の積であり、相互コンダクタンスを $g_m 1$ 、負荷抵抗を $R_p 1$ とすると、発振するための条件は次式で表される。

#### 【0048】

$$(数1) g_m 1 \times R_p 1 > 1$$

また、前述した「差動接続の動作」で説明したように、クロスカップル型回路全体で考えると、ドレイン端子に流れる電流は1/2になる。つまり、1つの回路として考えるとトランジスタに流れる電流は1/2とみなすことができる。相互コンダクタンスは電流の平方根に比例するので、1つの回路としての相互コンダクタンスは、1/2となる。つまり、1つの回路としての相互コンダクタンスを $g_m 2$ とすると、相互コンダクタンス $g_m 2$ は次式で表すことができる。

20

#### 【0049】

$$(数2) g_m 2 = (1/2) \times g_m 1$$

従って、上述した(1)式、(2)式より次式が得られる。

#### 【0050】

$$(数3) g_m 2 \times R_p 1 = (1/2)$$

となる。つまり、1つの回路として発振するために必要な利得は、1/2倍以上の利得があれば良い。発振に必要な利得が小さいことは、電流を少なくすることができます。

このように、電流を少なくすることができます、回路の消費電力を下げることができる。

#### 【0051】

30

##### ソース負荷回路のインピーダンスとドレイン負荷回路のインピーダンスの関係

次に、抵抗器 $R_s 1$ のインピーダンスの大きさ（以下、抵抗値と表すことがある）と抵抗器 $R_L 1$ の抵抗値との関係、および、抵抗器 $R_s 2$ の抵抗値と抵抗器 $R_L 2$ の抵抗値との関係を説明する。本実施例では、抵抗器 $R_s 1$ の抵抗値は、抵抗器 $R_L 1$ の抵抗値以上とし、抵抗器 $R_s 2$ の抵抗値は、抵抗器 $R_L 2$ の抵抗値以上とした。

#### 【0052】

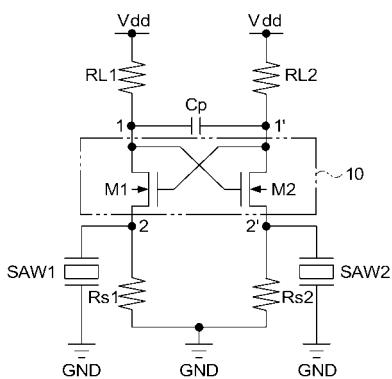

図2は、振動子SAWを分割して考えた場合の図1で表した発振回路と等価な発振回路を示す回路図である。図2に示すように、概念的には、振動子SAWは、振動子SAW1と振動子SAW2に分割することができる。このとき、振動子SAW1のインピーダンスおよび振動子SAW2のインピーダンスはそれぞれ、振動子SAWのインピーダンスの1/2となる。

40

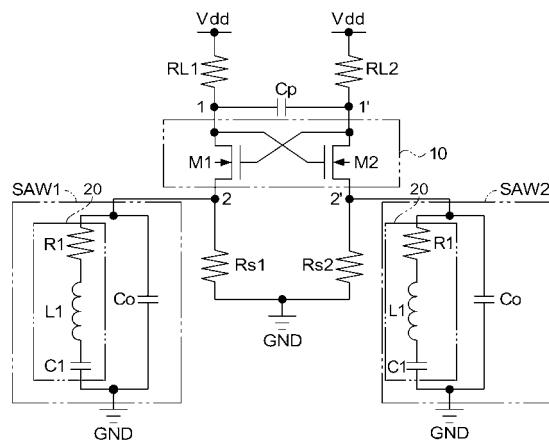

#### 【0053】

さらに、振動子SAW1および振動子SAW2を等価回路で表現すると、図2に表した発振回路は、図3のように表現できる。本実施例の発振回路における利得は、トランジスタM1のドレイン端子とGNDとの間のインピーダンスに対する抵抗器 $R_L 1$ の抵抗値との比、および、トランジスタM2のドレイン端子とGNDとの間のインピーダンスに対する抵抗器 $R_L 2$ の抵抗値との比で決定される。

#### 【0054】

##### 共振周波数より小さい場合における発振

ここで、周波数が振動子SAWの直列共振周波数よりも小さい場合について説明する。

50

この場合、直列共振アーム 20 のインピーダンスの大きさは、容量値 C1 により大きくなる。また、並列容量 C0 によるインピーダンスの大きさも大きくなる。一方、抵抗器 R<sub>S1</sub> の抵抗値は一定である。従って、トランジスタ M1 のソース端子と GND との間のインピーダンスの大きさは、抵抗器 R<sub>S1</sub> の抵抗値となる。よって、本実施例の発振回路における利得は、抵抗器 R<sub>S1</sub> の抵抗値に対する抵抗器 R<sub>L1</sub> の抵抗値との比となる。その比を 1 以下に設定すれば、利得が 1 以下となり発振しない。つまり、抵抗器 R<sub>S1</sub> の抵抗値を抵抗器 R<sub>L1</sub> の抵抗値以上にすれば発振しない。同様に、抵抗器 R<sub>S2</sub> の抵抗値を抵抗器 R<sub>L2</sub> の抵抗値以上にすれば発振しない。このようにして、周波数が振動子 SAW の直列共振周波数よりも小さい場合、発振回路が発振することを抑制することができる。

## 【0055】

10

## 共振周波数における発振

次に、周波数が振動子 SAW の直列共振周波数である場合を考える。この場合、直列共振アーム 20 におけるインピーダンスの大きさは、抵抗 R<sub>1</sub> の抵抗値のみとなる。振動子 SAW における抵抗 R<sub>1</sub> の抵抗値は極端に小さな値であり、並列容量 C0 によるインピーダンスの大きさよりも極端に小さく、抵抗器 R<sub>S1</sub> の抵抗値よりも極端に小さな値となる。したって、トランジスタ M1 のソース端子 2 と GND との間のインピーダンスは抵抗 R<sub>1</sub> の抵抗値となる。トランジスタ M2 のソース端子 2' と GND との間のインピーダンスも同様である。その結果、本実施例の発振回路における利得は、極めて大きな値となる。このようにして、本実施例の発振回路は、振動子 SAW の直列共振周波数で発振する。

## 【0056】

20

## 共振周波数より大きい場合における発振

次に、周波数が振動子 SAW の直列共振周波数よりも大きい場合を考える。この場合、直列共振アーム 20 におけるインピーダンス大きさは、インダクタ L1 により、大きくなる。一方、並列容量 C0 によるインピーダンスは、周波数が大きくなるにしたがって小さくなる。抵抗器 R<sub>S1</sub> の大きさは一定であるので、トランジスタ M1 のソース端子 2 と GND との間のインピーダンスは、並列容量 C0 によるインピーダンスが支配的となる。トランジスタ M2 のソース端子 2' と GND との間のインピーダンスも、並列容量 C0 によるインピーダンスが最も小さな値となる。仮に、並列容量 C0 によるインピーダンスよりも抵抗器 R<sub>L1</sub> の抵抗値または抵抗器 R<sub>L2</sub> の抵抗値が大きい場合、利得が 1 より大きくなり、発振する可能性がある。

30

## 【0057】

そこで、トランジスタ M1 のドレイン端子とトランジスタ M2 のドレイン端子の間にコンデンサ C<sub>p</sub> を接続している。コンデンサ C<sub>p</sub> によるインピーダンスによって、トランジスタ M1 のドレイン端子と電源電圧 V<sub>dd</sub> の間のインピーダンスおよびトランジスタ M2 のドレイン端子と電源電圧 V<sub>dd</sub> の間のインピーダンスも低下する。

## 【0058】

40

本実施例の発振回路における利得は、並列容量 C0 によるインピーダンスに対するコンデンサ C<sub>p</sub> によるインピーダンスの比が支配的となる。周波数が大きくなり、並列容量 C0 によるインピーダンスが小さくなつても、並列容量 C0 によるインピーダンスも小さくなるので、利得を抑制することができる。このようにして、周波数が振動子 SAW の直列共振周波数よりも大きい場合、発振回路が発振することを抑制することができる。

## 【0059】

ここで、コンデンサ C<sub>p</sub> の容量値は、並列容量 C0 の容量値の 1/2 に設定することが望ましい。このように設定すれば、並列容量 C0 によるインピーダンスとコンデンサ C<sub>p</sub> によるインピーダンスが同じ値となり、より効果的に直列共振周波数帯以外の帯域で発振することを抑制することができる。

## 【0060】

50

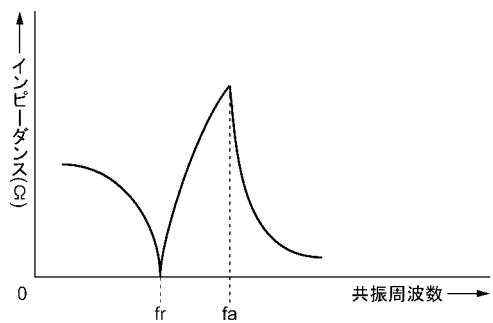

なお、本実施例では、発振周波数を振動子 SAW の共振点帯域を採用している。

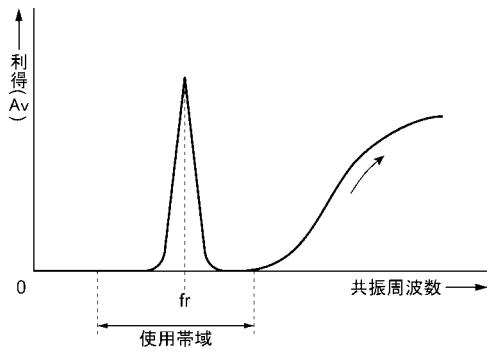

図 4 は、共振周波数とインピーダンスの関係を模式的に表す説明図である。図 4 に示すように、一般的な発振で使用する振動モードには共振点 f<sub>r</sub> と反共振点 f<sub>a</sub> との 2 点が存

在する。共振点  $f_r$  での使用は振動子のインピーダンスが最も小さくなる帯域であり、反共振点  $f_a$  は逆に振動子のインピーダンスが最も大きくなる帯域である。そして、前述した特許文献 2 では反共振点  $f_a$  の帯域を採用し、本実施例では共振点  $f_r$  の帯域を採用している。

#### 【0061】

共振特性からみた場合、共振点  $f_r$  の Q 特性は、反共振点  $f_a$  の Q 特性よりも優れている。つまり、共振点  $f_r$  を使用する本実施例の方が、前述した従来技術のように反共振点  $f_a$  を使用する場合よりも安定した振動特性が得られることになる。

#### 【0062】

続いて、共振周波数と利得の関係について説明する。

10

図 5 は、共振周波数と利得 ( $A_v$ ) との関係を模式的に表す説明図である。図 5 において、共振点  $f_r$  では利得 ( $A_v$ ) が最大値を示し、使用帯域よりも共振周波数が高い領域において利得 ( $A_v$ ) が上昇していくことを表している。これは、使用帯域よりも高い周波数でも発振しまう領域があることを示している。

#### 【0063】

そこで、コンデンサ  $C_p$  を備え、振動子 SAW の並列容量  $C_0$  によるインピーダンスを等しくする。こうすることにより、共振点帯域より高い共振周波数帯域における利得の上昇を抑制して、この帯域外における発振を抑制することができる。

#### (第 2 実施例)

#### 【0064】

20

続いて、第 2 実施例について図面を参照して説明する。第 2 実施例は、第 1 ドレイン負荷回路と並列接続されるコンデンサと、第 2 ドレイン負荷回路として抵抗器と並列接続されるコンデンサと、が備えられていることに特徴を有する。

図 6 は、第 2 実施例に係る発振回路を示す回路図である。図 6 において、トランジスタ M1 のドレイン端子 1 と電源電圧  $V_{dd}$  との間に、抵抗器  $R_L 1$  と並列接続されるコンデンサ  $C_p 2$  と、トランジスタ M2 のドレイン端子 1' と電源電圧  $V_{dd}$  との間に抵抗器  $R_L 2$  と並列接続されるコンデンサ  $C_p 2$  とから構成されている。他の構成は第 1 実施例(図 1、参照)と同じ構成であるので説明を省略する。

#### 【0065】

このような構成とすれば、前述した第 1 実施例の 差動接続の動作 において説明したように、クロスカップル型回路全体で考えると、ドレイン端子に流れる電流は 1 / 2 になり、また、1 つの回路として発振するために必要な利得を小さくすることができ、発振に必要な利得が小さいことは、電流を少なくすることができる。その結果、回路の消費電力を下げることができる。

30

#### 【0066】

さらに、第 1 実施例の 共振周波数より大きい場合における発振 の説明と同様に、周波数が振動子 SAW の直列共振周波数よりも大きい場合、発振回路が発振することを抑制することができる。

#### 【0067】

なお、この際、コンデンサ  $C_p 2$  の容量値は並列容量  $C_0$  の容量値とほぼ同じ値に設定することができる。並列容量  $C_0$  によるインピーダンスとコンデンサ  $C_p 2$  によるインピーダンスが同じ値となり、より効率的に発振することができる。

40

#### 【0068】

また、前述した 共振周波数より小さい場合における発振 での説明と同様に、周波数が振動子 SAW の直列共振周波数よりも小さい場合には、トランジスタ M1 のソース端子と GND 間のインピーダンスの大きさは抵抗器  $R_s 1$  の抵抗値となり、抵抗器  $R_s 1$  の抵抗値を抵抗器  $R_L 1$  の抵抗値以上にすれば発振しない。同様に、抵抗器  $R_s 2$  の抵抗値を抵抗器  $R_L 2$  の抵抗値以上にすれば発振しない。このようにして、周波数が振動子 SAW の直列共振周波数よりも小さい場合において、発振回路が発振することを抑制することができる。

50

## (第3実施例)

## 【0069】

続いて、第3実施例に係る発振回路について図面を参照して説明する。第3実施例は、第1ドレン負荷回路および第2ドレン負荷回路を定電流回路とし、第1ソース負荷回路および第2ソース負荷回路を定電流回路とした例である。

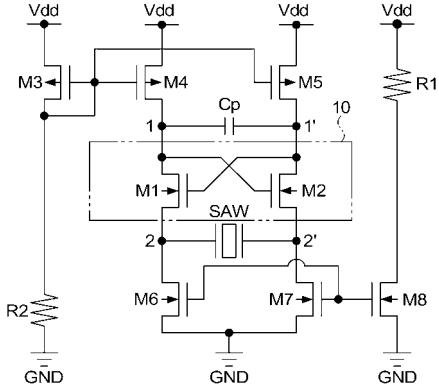

図7は、第3実施例に係る発振回路を示す回路図である。図7において、トランジスタM1のドレン端子1と電源電圧Vddとの間にはトランジスタM3, M4からなる第1ドレン負荷回路としての定電流回路が備えられている。また、トランジスタM2と電源電圧Vddとの間にはトランジスタM3, M5からなる第2ドレン負荷回路としての定電流回路が備えられている。

10

## 【0070】

トランジスタM4は、ソース端子がトランジスタM1のドレン端子1に、ドレン端子が電源電圧Vddに接続される。そして、ゲート端子がトランジスタM3のゲート端子及びソース端子に、トランジスタM5のゲート端子に接続される。トランジスタM3のソース端子が抵抗器R2を介してGNDに接続されて定電流回路を構成する。

## 【0071】

また、トランジスタM5は、ソース端子がトランジスタM2のドレン端子1'に、ドレン端子が電源電圧Vddに接続される。そして、ゲート端子がトランジスタM3, M4それぞれのゲート端子に接続されて定電流回路を構成する。

## 【0072】

一方、トランジスタM6は、ドレン端子がトランジスタM1のソース端子2に、ソース端子がGNDに接続され、ゲート端子がトランジスタM8のゲート端子に接続される。そして、トランジスタM8はソース端子がGNDに、ドレン端子が抵抗器R1を介して電源電圧Vddに接続されて定電流回路を構成する。

20

## 【0073】

このような構成であっても、前述した第1実施例の 差動接続の動作 において説明したように、クロスカップル型回路全体で考えると、ドレン端子に流れる電流は1/2になり、また、1つの回路として発振するために必要な利得を小さくすることができ、電流を少なくすることができる。その結果、回路の消費電力を下げることができる。

## 【0074】

30

また、第1実施例に記載の 共振周波数より小さい場合における発振 の説明と同様に、トランジスタM1のソース端子とGNDとの間のインピーダンスの大きさが、トランジスタM1のドレン端子と電源電圧Vddとの間のインピーダンスの大きさ以上であり、かつ、トランジスタM2のソース端子とGNDとの間のインピーダンスの大きさが、トランジスタM2のドレン端子と電源電圧Vddとの間のインピーダンスの大きさ以上であれば、振動子SAWの直列共振周波数よりも小さい周波数における発振を抑制することができる。

## 【0075】

また、 共振周波数よ大きい場合における発振 の説明と同様に、コンデンサCpを設けているので振動子SAWの直列共振周波数よりも大きい周波数における発振を抑制することができる。

40

## (第4実施例)

## 【0076】

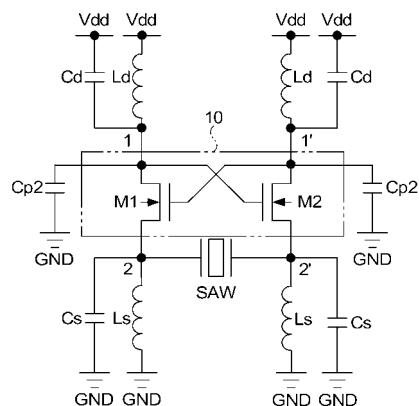

続いて、第4実施例に係る発振回路について図面を参照して説明する。第4実施例は、並列接続されたコンデンサとインダクタとから構成される第1ソース負荷回路及び第2ソース負荷回路と、並列接続されたコンデンサとインダクタとから構成される第1ドレン負荷回路及び第2ドレン負荷回路とを備えていることを特徴としている。

図8は、第4実施例に係る発振回路を示す回路図である。図8において、トランジスタM1のドレン端子1と電源電圧Vddとの間には、コンデンサCdとインダクタLdとが並列接続され、同様に、トランジスタM2のドレン端子1'과電源電圧Vddとの間には

50

、コンデンサ C d とインダクタ L d とが並列接続されている。

【0077】

一方、トランジスタ M 1 のソース端子 2 と GND の間には、コンデンサ C s とインダクタ L s とが並列接続され、同様に、トランジスタ M 2 のソース端子 2' と GND の間には、同様に、コンデンサ C s とインダクタ L s とが並列接続されている。

【0078】

なお、トランジスタ M 1 のソース端子にはコンデンサ C p 2 が設けられ、コンデンサ C p 2 は GND に接続されている。また、同様に、トランジスタ M 2 のソース端子にはコンデンサ C p 2 が設けられ、コンデンサ C p 2 は GND に接続されている。

つまり、ソース負荷回路及びドレイン負荷回路として LC 並列共振回路を構成する。

10

【0079】

クロスカッブル型回路で利得を最大（つまり、発振しやすくする）にするためには、ドレイン端子側のインピーダンスが最大になるように LC の定数を設定すればよい。このようにすれば、LC 並列共振回路は周波数選択性を有するため、共振周波数（共振点帯域）において最も発振しやすくなる。

【0080】

一方、ソース端子側のインピーダンスを最小になるように LC の定数を設定すれば、利得を最大にすることができるが、LC 並列共振回路では、共振周波数でインピーダンスが最大になるため、発振させたい周波数と LC 並列共振回路の周波数を一致させると発振を止める働きがある。

20

【0081】

そこで、ソース端子側に接続する LC 並列共振回路の周波数を異常発振の周波数帯域に合わせることにより、ソース端子側のインピーダンスを意図的に増大させて異常発振を抑制する。つまり、LC の定数を異常発振の周波数帯域に合わせることで、異常発振を抑制することができる。

（第 5 実施例）

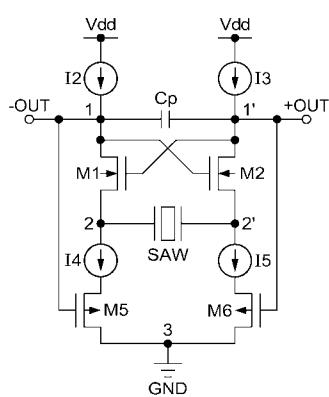

【0082】

続いて、第 5 実施例に係る発振回路について図面を参照して説明する。第 5 実施例は、第 1 ソース負荷回路と、第 2 ソース負荷回路と、第 1 ドレイン負荷回路と、第 2 ドレイン負荷回路のそれぞれが、定電流回路から構成されると共に、第 1 能動素子のソース端子とドレイン端子との間、第 2 能動素子のソース端子とドレイン端子との間それぞれに、振幅一定化回路が備えられていることを特徴とする。

30

図 9 は、第 5 実施例に係る発振器の 1 例を示す回路図である。図 9 において、トランジスタ M 1 のドレイン端子 1 と電源電圧 Vdd との間に第 1 ドレイン負荷回路としての定電流回路 I2 と、トランジスタ M 2 のドレイン端子 1' と電源電圧 Vdd との間に第 2 ドレイン負荷回路としての定電流回路 I3 とが、備えられている。

【0083】

そして、トランジスタ M 5 のドレイン端子がトランジスタ M 1 のソース端子と接続され、ゲート端子はトランジスタ M 1 のドレイン端子と接続されている。

【0084】

一方、トランジスタ M 1 のソース端子 2 にはトランジスタ M 5 が接続され、トランジスタ M 2 のソース端子 2' にはトランジスタ M 6 が接続されている。そして、トランジスタ M 5 及びトランジスタ M 6 それぞれ共通のソース端子 3 と GND との間にソース負荷回路としての定電流回路 I1 が備えられている。

40

【0085】

そして、トランジスタ M 6 のドレイン端子をトランジスタ M 2 のソース端子と接続し、ゲート端子はトランジスタ M 2 のドレイン端子と接続されている。

【0086】

この発振回路の作用について説明する。まず、振動子 SAW の振幅が所定の振幅より大きい場合について説明する。振動子 SAW の振幅が大きい場合には、トランジスタ M 5 の

50

ゲート電圧が高くなり、電流が増加する。これに伴いドレインのインピーダンスが低下し、トランジスタM1のソース電圧及びゲート電圧が低下する。すると、トランジスタM2のドレイン電圧、ソース電圧も低下することから電流が減少する。そして、トランジスタM1のゲート電圧、ドレイン電圧が低下する。従って、発振振幅が小さくなる。このようにして発振振幅が一定になるように自己調整される。従って、本実施例では、トランジスタM5, M6から構成される回路を振幅一定化回路と呼ぶ。

#### 【0087】

このような構成によれば、振幅一定化回路を設けることにより、発振回路からの出力振幅が一定となる。出力振幅が一定になれば発振の起動時間を短縮することができる。

また、能動素子のコモンモードに依存しない回路ができるので、第1能動素子と第2能動素子のミスマッチやオフセットによる影響がなく、このことからも起動時間の短縮化ができると共に、低電圧駆動やノイズ耐性がある発振回路及び発振器を実現できる。10

(第5実施例の変形例)

#### 【0088】

次に、第5実施例の変形例に係る発振回路について図面を参照して説明する。この変形例は、上述した第5実施例(図9、参照)に対して、トランジスタM1, M2のソース端子側に設けられる定電流回路の配設位置が異なることに特徴を有する。

図10は、第5実施例の変形例に係る発振回路を示す回路図である。図10において、トランジスタM1とトランジスタM5の間に定電流回路I4、トランジスタM2とトランジスタM6の間に定電流回路I5が接続されている。そして、トランジスタM5, M6の共通のソース端子3がGNDに接続されて構成されている。20

#### 【0089】

このような構成にしても、前述した第5実施例(図9、参照)と同様な作用効果がある。

(第6実施例)

#### 【0090】

続いて、第6実施例に係る発振回路について図面を参照して説明する。第6実施例は、前述した第5実施例(図10、参照)に記載の差動接続部の構成が異なることを特徴としている。従って、差動接続部以外の構成については、第1実施例～第5実施例に記載の構成を採用できるが、ここでは、第5実施例(図10、参照)を基礎構造として例示し説明する。30

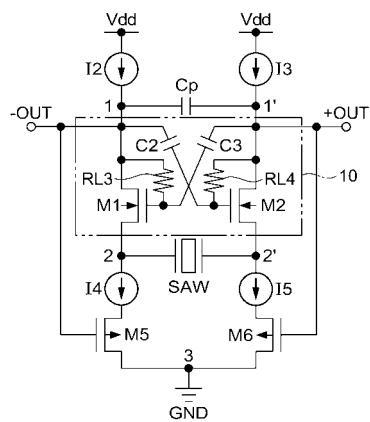

図11は、第6実施例に係る発振回路の1例を示す回路図である。図11において、クロスカップル型回路10は、トランジスタM1のゲート端子とトランジスタM2のドレイン端子との間にコンデンサC3が接続され、トランジスタM2のゲート端子とトランジスタM1のドレイン端子との間にコンデンサC2が接続されて構成されている。

#### 【0091】

また、トランジスタM1のゲート端子とドレイン端子との間に抵抗器RL3、トランジスタM2のゲート端子とドレイン端子との間に抵抗器RL4が接続されている。

#### 【0092】

このような構成によれば、トランジスタM1とトランジスタM2とが差動接続される間に、コンデンサC2, C3及び抵抗器RL3, RL4を配設することにより、MOSトランジスタのゲートとドレインを疎結合(インピーダンス的に極力分離)するので、回路の線形性が向上(回路の歪が減少)し、高調波発振を抑制しノイズ耐性が向上するという効果がある。40

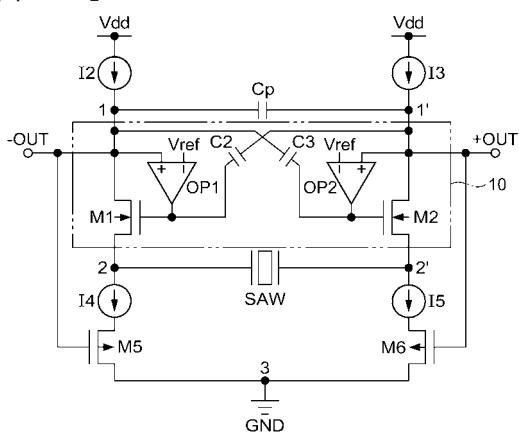

(第7実施例)

#### 【0093】

続いて、第7実施例に係る発振回路について図面を参照して説明する。第7実施例は、トランジスタM1のゲート端子とドレイン端子との間、トランジスタM2のゲート端子とドレイン端子の間それぞれに增幅器が備えられていることを特徴としている。従って、差動接続部以外の構成については、第5実施例及び第6実施例に記載の構成を採用できるが50

、ここでは、第6実施例(図11、参照)を基礎構造として例示し説明する。

図12は、第7実施例に係る発振回路の1例を示す回路図である。図12において、トランジスタM1のゲート端子とドレイン端子の間に増幅器OP1が接続され、トランジスタM2のゲート端子とドレイン端子の間に増幅器OP2が接続され構成されている。

#### 【0094】

さらに、トランジスタM1のゲート端子とトランジスタM2のドレイン端子との間にコンデンサC2が接続され、トランジスタM2のゲート端子とトランジスタM1のドレイン端子との間にコンデンサC3が接続されている。

#### 【0095】

このように構成される発振回路では、トランジスタM1とトランジスタM2とが差動接続される間に、コンデンサC2,C3及び増幅器OP1,OP2を配設することにより、MOSトランジスタのゲートとドレインを疎結合するので、回路の線形性が向上(回路の歪が減少)し、高調波発振を抑制しノイズ耐性が向上するという効果がある。10

#### 【0096】

また、増幅器OP1,OP2の増幅率を適宜設定することにより、トランジスタM1,M2それぞれのゲート電圧を任意の値に調整できるため、発振器の設計が容易になるという効果もある。

#### 【0097】

本発明は上記の実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々の態様において実施することが可能である。例えば、次のような変形が可能である。20

例えば、前述した各実施例においては、第1能動素子および第2能動素子をNch型トランジスタである例を説明した。第1能動素子または第2能動素子は、Pch型トランジスタ、Si-BiCMOS、Siバイポーラトランジスタ、SiGeバイポーラトランジスタ、GaAs-MESFET、GaAs-HEMT、InP-HEMT、P-HEMT、HBTのいずれかあっても良い。

#### 【0098】

また、各実施例においては、振動子として弹性表面波素子(SAW)である例を説明した。振動子は、AT振動子等の厚み滑り振動子、MEMS振動子、SMRやFBAR等のBAR振動子のいずれかであっても良い。

#### 【0099】

さらに、以上の説明では、第1ソース負荷回路と第2ソース負荷回路が同じ構成で、かつ、第1ドレイン負荷回路と第2ドレイン負荷回路が同じ構成である場合を示した。しかし、第1ソース負荷回路と第2ソース負荷回路は、同じ構成である必要はなく、前述の各実施例で説明した構成を適宜組み合わせても良い。例えば、第1ソース負荷回路を抵抗器で構成し、第2ソース負荷回路を定電流回路としても良い。第1ドレイン負荷回路をフィルタ回路とし、第2ドレイン負荷回路を抵抗器で構成しても良い。

#### 【0100】

以上説明した第1実施例～第7実施例による構成とすれば、消費電流を低減する、Q特性が優れる、共振周波数帯域外の発振を抑制する、発振の起動時間短縮、ノイズ耐性が優れる発振回路及び発振器を実現することができる。40

#### 【図面の簡単な説明】

#### 【0101】

【図1】第1実施例に係る発振回路の1例を示す回路図。

【図2】図1で表した発振回路と等価な発振回路を示す回路図。

【図3】振動子を等価回路で表現した場合の図1と等価な発振回路を示す回路図。

【図4】共振周波数とインピーダンスの関係を模式的に表す説明図。

【図5】共振周波数と利得との関係を模式的に表す説明図。

【図6】第2実施例に係る発振回路を示す回路図。

【図7】第3実施例に係る発振回路を示す回路図。

【図8】第4実施例に係る発振回路を示す回路図。

10

20

30

40

50

【図9】第5実施例に係る発振器の1例を示す回路図。

【図10】第5実施例の変形例に係る発振回路を示す回路図。

【図11】第6実施例に係る発振回路の1例を示す回路図。

【図12】第7実施例に係る発振回路の1例を示す回路図。

【符号の説明】

【0102】

1 ...トランジスタM1のドレイン端子、1' ...トランジスタM2のドレイン端子、2 ...トランジスタM1のソース端子、2' ...トランジスタM2のソース端子、10 ...クロスカップル型回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図11】

【図10】

【図12】

---

フロントページの続き

審査官 徳 田 賢二

- (56)参考文献 米国特許第03754152(US, A)

米国特許第04353039(US, A)

特開平03-192905(JP, A)

獨国特許出願公開第04232378(DE, A1)

米国特許出願公開第2002/0190802(US, A1)

欧州特許出願公開第00400425(EP, A1)

米国特許第03684981(US, A)

特開昭62-086908(JP, A)

特開平09-205328(JP, A)

米国特許第05422605(US, A)

特開2002-084136(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03B 5/36

H03B 5/30