(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년07월29일

(11) 등록번호 10-1643800

(24) 등록일자 2016년07월22일

(51) 국제특허분류(Int. Cl.)

*H01L 21/683* (2006.01) *H05B 3/20* (2006.01)

(21) 출원번호 10-2012-7012975

(22) 출원일자(국제) 2010년10월20일

심사청구일자 2015년09월18일

(85) 번역문제출일자 2012년05월18일

(65) 공개번호 10-2012-0103596

(43) 공개일자 2012년09월19일

(86) 국제출원번호 PCT/US2010/002794

(87) 국제공개번호 WO 2011/049620

국제공개일자 2011년04월28일

(30) 우선권주장

12/582,991 2009년10월21일 미국(US)

(56) 선행기술조사문현

JP2003524885 A

JP평성11126743 A

KR1020050040729 A

WO2008112673 A1

(73) 특허권자

램 리씨치 코포레이션

미국 94538 캘리포니아주 프레몬트 쿠싱 파크웨이

4650

(72) 발명자

싱 하르미트

미국 94539 캘리포니아주 프레몬트 프라테리아 씨

클 759

가프 키스

미국 94536 캘리포니아주 프레몬트 그랜빌 코트

5363

(뒷면에 계속)

(74) 대리인

특허법인인벤투스

전체 청구항 수 : 총 35 항

심사관 : 김대웅

(54) 발명의 명칭 반도체 프로세싱을 위한 평탄한 히터존들을 가진 가열판

### (57) 요 약

반도체 플라즈마 프로세싱 장치 내의 기판 지지 어셈블리용 가열판은, 스케일 가능한 멀리플렉싱 레이아웃으로 배열된 다중의 독립적으로 제어 가능한 평탄한 히터존들, 및 그 평탄한 히터존들을 독립적으로 제어하고 전력공급하기 위한 전자장치를 포함한다. 가열판이 통합되는 기판 지지 어셈블리는 정전 클램핑 전극 및 온도 제어된 베이스 플레이트를 포함한다. 가열판을 제작하는 방법은 평탄한 히터존들, 전력 공급 라인들, 전력 복귀 라인들 및 비아들을 갖는 세라믹 또는 폴리머 시트들을 함께 본딩하는 단계를 포함한다.

대 표 도 - 도 1

(72) 발명자

벤자민 네일

미국 94303 캘리포니아주 이스트 팔로 알토 그린

스트리트 216

코멘던트 키스

미국 94536 캘리포니아주 프레몬트 글리든 웨이

4350

## 명세서

### 청구범위

#### 청구항 1

반도체 프로세싱 장치에서 반도체 기판을 지지하는데 이용되는 기판 지지 어셈블리로서,

반도체 기판을 상기 기판 지지 어셈블리 상에 정전기적으로 클램핑하도록 구성된 적어도 하나의 클램핑 전극을 갖는 정전 클램핑층을 포함하는 정전체 (ESC);

상기 정전 클램핑층 아래에 배열된 가열판;

상기 가열판의 하부측에 열장벽층 (thermal barrier layer)에 의해 부착된 냉각판을 포함하고,

상기 가열판은,

제 1 전기 절연층;

각각 하나 이상의 히터 엘리먼트들을 포함하는, 제 1 평탄한 히터존, 제 2 평탄한 히터존, 제 3 평탄한 히터존 및 제 4 평탄한 히터존을 적어도 포함하는 평탄한 히터존들로서, 상기 평탄한 히터존들은 상기 제 1 전기 절연층에 걸쳐 측방향으로 분포되고 상기 반도체 기판 상의 공간 온도 프로파일을 튜닝하도록 동작가능한, 상기 평탄한 히터존들;

상기 제 1 평탄한 히터존 및 상기 제 2 평탄한 히터존에 전기적으로 접속된 제 1 전기적 도전성 전력 공급 라인 및 상기 제 3 평탄한 히터존 및 상기 제 4 평탄한 히터존에 전기적으로 접속된 제 2 전기적 도전성 전력 공급 라인을 적어도 포함하는 전력 공급 라인들; 및

상기 제 1 평탄한 히터존 및 상기 제 3 평탄한 히터존에 전기적으로 접속된 제 1 전기적 도전성 전력 복귀 (return) 라인 및 상기 제 2 평탄한 히터존 및 상기 제 4 평탄한 히터존에 전기적으로 접속된 제 2 전기적 도전성 전력 복귀 라인을 적어도 포함하는 전력 복귀 라인들을 포함하고, 그리고

(a) 상기 전력 공급 라인들은 서로로부터 전기적으로 절연되고 상기 냉각판 내의 적어도 하나의 전력 공급 도관을 통해 연장된 리드들에 접속되고, 상기 전력 복귀 라인들은 서로로부터 전기적으로 절연되고 상기 냉각판 내의 적어도 하나의 전력 복귀 도관을 통해 연장된 리드들에 접속되고; 또는

(b) 상기 전력 공급 라인들 및 상기 전력 복귀 라인들은 상기 냉각판 내에 임베딩된 터미널 커넥터들에 접속되는, 기판 지지 어셈블리.

#### 청구항 2

제 1 항에 있어서,

(a) 상기 평탄한 히터존들 및 상기 전력 공급 라인들은 제 1 평면에 있고; 상기 전력 복귀 라인들은 상기 제 1 평면에 평행한 제 2 평면에 있으며; 상기 제 1 평면 및 상기 제 2 평면은 서로 상기 제 1 전기 절연층에 의해 분리되고; 상기 전력 복귀 라인들은 상기 제 1 전기 절연층에서 수직으로 연장된 비아들에 의해 상기 평탄한 히터존들에 전기적으로 접속되고; 또는

(b) 상기 평탄한 히터존들 및 상기 전력 복귀 라인들은 제 1 평면에 있고; 상기 전력 공급 라인들은 상기 제 1 평면에 평행한 제 2 평면에 있으며; 상기 제 1 평면 및 상기 제 2 평면은 서로 상기 제 1 전기 절연층에 의해 분리되고; 상기 전력 공급 라인들은 상기 제 1 전기 절연층에서 수직으로 연장된 비아들에 의해 상기 평탄한 히터존들에 전기적으로 접속되며; 또는

(c) 상기 평탄한 히터존들은 제 1 평면에 있고; 상기 전력 공급 라인들은 상기 제 1 평면에 평행한 제 2 평면에 있으며; 상기 전력 복귀 라인들은 상기 제 1 평면에 평행한 제 3 평면에 있고; 상기 제 1 평면 및 상기 제 2 평면은 상기 제 1 전기 절연층에 의해 분리되며; 상기 제 2 평면 및 상기 제 3 평면은 제 2 전기 절연층에 의해 분리되고; 상기 전력 공급 라인들 및 상기 전력 복귀 라인들은 상기 전기 절연층들을 통해 연장된 비아들에 의해 상기 평탄한 히터존들에 전기적으로 접속되는, 기판 지지 어셈블리.

### 청구항 3

제 1 항에 있어서,

상기 평탄한 히터존들은 :

- (a) 평탄한 히터존 각각이 상기 반도체 기판 상에 제작되는 4 개의 디바이스 다이들보다 크지 않도록, 또는

- (b) 평탄한 히터존 각각이 상기 반도체 기판 상에 제작되는 2 개의 디바이스 다이들보다 크지 않도록, 또는

- (c) 평탄한 히터존 각각이 상기 반도체 기판 상에 제작되는 하나의 디바이스 다이보다 크지 않도록, 또는

- (d) 평탄한 히터존 각각의 면적이  $2\text{cm}^2$  와  $3\text{cm}^2$  사이가 되도록, 또는

- (e) 상기 가열판이 100 내지 400 개의 평탄한 히터존들을 포함하도록, 또는

- (f) 평탄한 히터존 각각이  $1\text{cm}^2$  내지  $15\text{cm}^2$  가 되도록, 또는

- (g) 평탄한 히터존 각각이  $16\text{cm}^2$  내지  $100\text{cm}^2$  가 되도록, 또는

- (h) 평탄한 히터존 각각이 상기 반도체 기판 상의 디바이스 다이들의 사이즈들 및 상기 반도체 기판의 전체 사이즈에 따라 스케일링되도록, 사이징되는, 기판 지지 어셈블리.

### 청구항 4

제 1 항에 있어서,

상기 제 1 전기 절연층은 폴리머 재료, 세라믹 재료 또는 이들의 조합을 포함하는, 기판 지지 어셈블리.

### 청구항 5

제 1 항에 있어서,

상기 전력 공급 라인들 및 상기 전력 복귀 라인들의 총 개수는 상기 평탄한 히터존들의 총 개수 이하인, 기판 지지 어셈블리.

### 청구항 6

제 1 항에 있어서,

상기 평탄한 히터존들의 총 면적은 상기 가열판의 상부면의 50% 내지 90% 인, 기판 지지 어셈블리.

### 청구항 7

제 1 항에 있어서,

상기 평탄한 히터존들은 직사각형 그리드, 6 각형 그리드 또는 동심원상 링들로 배열되고; 그리고

상기 평탄한 히터존들은, 폭이 최소한 1 밀리미터이고 폭이 최대한 10 밀리미터인 캡들에 의해 서로 분리되는, 기판 지지 어셈블리.

### 청구항 8

제 1 항에 있어서,

정류기가 상기 히터존 각각과, 그 히터존에 접속된 상기 전력 공급 라인 사이에 직렬 접속되며, 또는 정류기가 상기 히터존 각각과 그 히터존에 접속된 상기 전력 복귀 라인 사이에 직렬 접속되는, 기판 지지 어셈블리.

### 청구항 9

제 8 항에 있어서,

상기 정류기는 반도체 다이오드인, 기판 지지 어셈블리.

### 청구항 10

제 1 항에 있어서,

임의의 주어진 시간에, (a) 단지 상기 제 1 평탄한 히터존에만, (b) 단지 상기 제 2 평탄한 히터존에만, (c) 단지 상기 제 3 평탄한 히터존에만, (d) 단지 상기 제 4 평탄한 히터존에만, (e) 단지 상기 제 1 평탄한 히터존과 상기 제 2 평탄한 히터존에만, (f) 단지 상기 제 1 평탄한 히터존과 상기 제 3 평탄한 히터존에만, (g) 단지 상기 제 2 평탄한 히터존과 상기 제 4 평탄한 히터존에만, 그리고 (i) 상기 평탄한 히터존들 전부에, 전력을 선택적으로 공급하도록 동작가능한 제어 및 전력 회로를 더 포함하는, 기판 지지 어셈블리.

#### 청구항 11

제 10 항에 있어서,

상기 제어 및 전력 회로와 전기적 그라운드 사이에 직렬 접속된 적어도 하나의 필터 또는 아이솔레이터를 더 포함하는, 기판 지지 어셈블리.

#### 청구항 12

제 11 항에 있어서,

상기 적어도 하나의 필터 또는 아이솔레이터는 변압기인, 기판 지지 어셈블리.

#### 청구항 13

제 1 항에 있어서,

상기 가열판의 상기 제 1 전기 절연층의 상방 또는 하방에 배열된 적어도 하나의 프라이머리 히터층 (primary heater layer) 을 더 포함하며,

상기 프라이머리 히터층은, 상기 가열판의 상기 평탄한 히터존들, 상기 전력 공급 라인들, 및 상기 전력 복귀 라인들로부터 전기 절연되고; 상기 프라이머리 히터층은, 상기 반도체 기판의 평균 온도 제어를 제공하는 적어도 하나의 히터를 포함하며; 상기 평탄한 히터존들은, 상기 반도체 기판을 프로세싱하는 동안, 상기 반도체 기판의 방사상 및 방위각 온도 프로파일 제어를 제공하는, 기판 지지 어셈블리.

#### 청구항 14

제 1 항에 있어서,

상기 터미널 커넥터들은 스프링 텁抨된 패스스루 (spring tipped passthrough) 들인, 기판 지지 어셈블리.

#### 청구항 15

제 13 항에 있어서,

상기 프라이머리 히터층은 2 개 이상의 히터들을 포함하는, 기판 지지 어셈블리.

#### 청구항 16

프로세싱 챔버 내의 반도체 기판 지지 어셈블리 상에 지지된 반도체 기판의 방사상 및 방위각 온도 제어를 제공하도록 구성된 가열판으로서,

상기 반도체 기판 상에서 공간적 온도 프로파일을 튜닝하도록 동작가능한 히터존들의 어레이를 갖는 제 1 층으로서, 상기 히터존들은 2 개 이상의 전력 공급 라인들 및 2 개 이상의 전력 복귀 라인들에 의해 전력 공급되고, 전력 공급 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고 전력 복귀 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고, 상기 히터존 각각은 상기 반도체 기판 상에 제작되는 4 개의 디바이스 다이들보다 크지 않은, 상기 제 1 층; 및

상기 프로세싱 챔버 내에서의 프로세싱 동안 상기 반도체 기판의 평균 온도 제어를 제공하도록 동작가능한 하나 이상의 프라이머리 히터들을 갖는 제 2 층을 포함하는, 가열판.

#### 청구항 17

기판 지지 어셈블리로서,

프로세싱 챔버 내의 반도체 기판 지지 어셈블리 상에 지지된 반도체 기판의 방사상 및 방위각 온도 제어를 제공하도록 구성된 가열판으로서,

상기 반도체 기판 상에서 공간적 온도 프로파일을 튜닝하도록 동작가능한 히터존들의 어레이를 갖는 제 1 층으로서, 상기 히터존들은 2 개 이상의 전력 공급 라인들 및 2 개 이상의 전력 복귀 라인들에 의해 전력 공급되고, 전력 공급 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고 전력 복귀 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고, 상기 히터존 각각은 상기 반도체 기판 상에서 제작되는 4 개의 디바이스 다이들보다 크지 않은, 상기 제 1 층; 및

상기 프로세싱 챔버 내에서의 프로세싱 동안 상기 반도체 기판의 평균 온도 제어를 제공하도록 동작가능한 하나 이상의 프라이머리 히터들을 갖는 제 2 층을 포함하는, 상기 가열판;

스위치들의 시분할 멀티플렉싱에 의해 상기 히터존들 각각에 시간 평균된 전력을 제공하도록, 상기 전력 공급 라인들 중 하나 및 상기 전력 복귀 라인들 중 하나를 통해 상기 히터존들 중 각각의 하나에 전력을 독립적으로 공급하는 스위칭 디바이스; 및

상기 가열판 아래의 온도 제어되고 무선 주파수 (RF) 전력 공급된 기판 지지 어셈블리 베이스 구조물 및 상기 기판 지지 어셈블리 베이스 구조물 아래의 로컬 패러데이 상자 (faraday cage) 내에 하우징된 상측 회로를 포함하는, 기판 지지 어셈블리.

## 청구항 18

프로세싱 챔버 내의 반도체 기판 지지 어셈블리 상에 지지된 반도체 기판의 방사상 및 방위각 온도 제어를 제공하도록 구성된 가열판으로서,

상기 반도체 기판 상에서 공간적 온도 프로파일을 튜닝하도록 동작가능한 히터존들의 어레이를 갖는 제 1 층으로서, 상기 히터존들은 2 개 이상의 전력 공급 라인들 및 2 개 이상의 전력 복귀 라인들에 의해 전력 공급되고, 전력 공급 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고 전력 복귀 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고, 상기 히터존 각각은 상기 반도체 기판 상에서 제작되는 4 개의 디바이스 다이들보다 크지 않은, 상기 제 1 층;

상기 프로세싱 챔버 내에서의 프로세싱 동안 상기 반도체 기판의 평균 온도 제어를 제공하도록 동작가능한 하나 이상의 프라이머리 히터들을 갖는 제 2 층; 및

제 1 전기 절연층과 함께, 상기 제 1 전기 절연층에 걸쳐 측방향으로 분포되고 제 1 평탄한 히터존, 제 2 평탄한 히터존, 제 3 평탄한 히터존 및 제 4 평탄한 히터존을 적어도 포함하는 평탄한 히터존들로서, 상기 평탄한 히터존들은 각각 하나 이상의 히터 엘리먼트들을 포함하는, 상기 평탄한 히터존들을 포함하고,

상기 전력 공급 라인들은, 상기 제 1 평탄한 히터존 및 상기 제 2 평탄한 히터존에 전기적으로 접속된 제 1 전기적 도전성 전력 공급 라인 및 상기 제 3 평탄한 히터존 및 상기 제 4 평탄한 히터존에 전기적으로 접속된 제 2 전기적 도전성 전력 공급 라인을 적어도 포함하고, 그리고

상기 전력 복귀 라인들은, 상기 제 1 평탄한 히터존 및 상기 제 3 평탄한 히터존에 전기적으로 접속된 제 1 전기적 도전성 전력 복귀 라인 및 상기 제 2 평탄한 히터존 및 상기 제 4 평탄한 히터존에 전기적으로 접속된 제 2 전기적 도전성 전력 복귀 라인을 적어도 포함하는, 가열판.

## 청구항 19

제 16 항에 있어서,

상기 가열판은,

상기 반도체 기판 상의 위치들에서 온도를 측정하도록 구성된 온도 센서들; 및

상기 히터존들의 어레이에 접속되고 상기 온도 센서들로부터 측정된 파라미터들을 수신하고 상기 측정된 파라미터들과 설정된 목표들 간의 차이들을 최소화하도록 상기 히터존들에 전달된 전력을 조정하도록 구성된 제어 및 전력 회로를 포함하는, 상기 반도체 기판 지지 어셈블리 내에 통합되는, 가열판.

**청구항 20**

제 17 항에 있어서,

전기적 그라운드 사이에 접속된 아이솔레이터를 더 포함하고,

상기 스위칭 디바이스는 상기 아이솔레이터에 접속되는, 기판 지지 어셈블리.

**청구항 21**

제 20 항에 있어서,

상기 스위칭 디바이스는 플라즈마 에칭 챔버 내에 위치되는, 기판 지지 어셈블리.

**청구항 22**

제 20 항에 있어서,

상기 아이솔레이터는 상기 스위칭 디바이스를 RF로부터 격리시키는 절연 변압기 (isolation transformer) 인, 기판 지지 어셈블리.

**청구항 23**

프로세싱 챔버 내의 반도체 기판 지지 어셈블리 상에 지지된 반도체 기판의 방사상 및 방위각 온도 제어를 제공하도록 구성된 가열판으로서,

상기 반도체 기판 상에서 공간적 온도 튜닝하도록 동작가능한 히터존들의 어레이를 갖는 제 1 층으로서, 상기 히터존들은 2 개 이상의 전력 공급 라인들 및 2 개 이상의 전력 복귀 라인들에 의해 전력 공급되고, 전력 공급 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고 전력 복귀 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고, 상기 히터존 각각은 상기 반도체 기판 상에 제작되는 4 개의 디바이스 다이들보다 크지 않은, 상기 제 1 층; 및

상기 프로세싱 챔버 내에서의 프로세싱 동안 상기 반도체 기판의 평균 온도 제어를 제공하도록 동작가능한 하나 이상의 프라이머리 히터들을 갖는 제 2 층을 포함하고,

상기 히터존들은 제 1 전기 절연층 상에 지지되고;

상기 제 2 층은 상기 제 1 전기 절연층 위 또는 아래에 배열되고; 그리고

상기 하나 이상의 프라이머리 히터들은 상기 히터존들의 어레이, 상기 전력 공급 라인들, 및 상기 전력 복귀 라인들로부터 전기적으로 절연되는, 가열판.

**청구항 24**

제 17 항에 있어서,

상기 스위칭 디바이스는 RF 전위에서 플로팅하는 상측 제어기이고,

상기 기판 지지 어셈블리는,

하측 제어기와의 디지털 통신을 위해 상기 상측 제어기에 접속된 광 커플러를 더 포함하는, 기판 지지 어셈블리.

**청구항 25**

제 17 항에 있어서,

상기 스위칭 디바이스는 적어도 하나의 전력 복귀 라인을 플로팅 레퍼런스에 접속하는, 기판 지지 어셈블리.

**청구항 26**

제 17 항에 있어서,

상기 스위칭 디바이스는 상기 히터존에 접속된 적어도 하나의 전력 공급 라인이 전력 공급장치에 접속되고, 그

리고 상기 히터존에 접속된 적어도 하나의 전력 복귀 라인이 플로팅 레퍼런스에 접속될 때 상기 히터존들 중 하나를 턴 온하도록 구성되는, 기판 지지 어셈블리.

### 청구항 27

제 17 항에 있어서,

상기 스위칭 디바이스는 모든 상기 전력 복귀 라인들을 플로팅 레퍼런스에 접속하는, 기판 지지 어셈블리.

### 청구항 28

제 17 항에 있어서,

상기 스위칭 디바이스는 적어도 1Hz의 주파수에서 상기 히터존들의 어레이의 히터존 각각을 어드레싱하도록 구성되는, 기판 지지 어셈블리.

### 청구항 29

제 16 항에 기재된 상기 가열판을 포함하는 기판 지지 어셈블리로서,

상기 기판 지지 어셈블리는 상기 기판 지지 어셈블리 상의 상이한 위치들 및 상기 히터존들의 전력에 대한 파라미터들을 측정하도록 구성된 센서들을 포함하는, 기판 지지 어셈블리.

### 청구항 30

제 29 항에 있어서,

상기 센서들은 전압 센서 및 전류 센서 중 적어도 하나를 포함하는, 기판 지지 어셈블리.

### 청구항 31

제 29 항에 있어서,

상기 측정된 파라미터들은 적어도 온도 측정치들을 포함하는, 기판 지지 어셈블리.

### 청구항 32

제 17 항에 있어서,

상기 스위칭 디바이스는, 일 전력 공급 라인에 전력 공급되는 시간 동안 모든 상기 전력 복귀 라인들과 플로팅 레퍼런스 사이의 접속을 유지하고 턴 온된 히터존을 가열하기 위해 전송된 전력을 조절하도록 구성되는, 기판 지지 어셈블리.

### 청구항 33

기판 지지 어셈블리로서,

프로세싱 챔버 내의 반도체 기판 지지 어셈블리 상에 지지된 반도체 기판의 방사상 및 방위각 온도 제어를 제공하도록 구성된 가열판으로서,

상기 반도체 기판 상에서 공간적 온도 프로파일을 튜닝하도록 동작가능한 히터존들의 어레이를 갖는 제 1 층으로서, 상기 히터존들은 2 개 이상의 전력 공급 라인들 및 2 개 이상의 전력 복귀 라인들에 의해 전력 공급되고, 전력 공급 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고 전력 복귀 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고, 상기 히터존 각각은 상기 반도체 기판 상에서 제작되는 4 개의 디바이스 다이들 보다 크지 않은, 상기 제 1 층; 및

상기 프로세싱 챔버 내에서의 프로세싱 동안 상기 반도체 기판의 평균 온도 제어를 제공하도록 동작가능한 하나 이상의 프라이머리 히터들을 갖는 제 2 층을 포함하는, 상기 가열판; 및

상기 가열판 위의 정전 클램핑층을 포함하는, 기판 지지 어셈블리.

### 청구항 34

제 33 항에 있어서,

상기 가열판 아래의 무선 주파수 (RF) 전력 공급된 기판 지지 어셈블리 베이스 구조물을 더 포함하는, 기판 지지 어셈블리.

### 청구항 35

제 16 항에 있어서,

상기 히터존들은 세라믹 재료 내에 임베딩된 적어도 100 개의 독립적으로 제어가능한 히터존들을 포함하는, 가열판.

### 청구항 36

삭제

### 청구항 37

삭제

### 청구항 38

삭제

### 청구항 39

삭제

### 청구항 40

삭제

### 청구항 41

삭제

### 청구항 42

삭제

### 청구항 43

삭제

### 청구항 44

삭제

### 청구항 45

삭제

### 청구항 46

삭제

### 청구항 47

삭제

### 청구항 48

삭제

청구항 49

삭제

청구항 50

삭제

청구항 51

삭제

청구항 52

삭제

청구항 53

삭제

청구항 54

삭제

청구항 55

삭제

청구항 56

삭제

청구항 57

삭제

## 발명의 설명

### 기술 분야

[0001] 본 발명은 반도체 프로세싱을 위한 평탄한 히터존들을 가진 가열판에 관한 것이다.

### 배경 기술

[0002] 각각의 연속하는 반도체 기술 발생으로 인해, 기판 직경은 증가하려는 경향이 있고 트랜지스터 사이즈는 감소하여, 기판 프로세싱 시에 훨씬 더 높은 정도의 정확성 및 반복성의 필요성을 야기하였다. 실리콘 기판과 같은 반도체 기판 재료는 전공 챔버의 이용을 포함한 기법들에 의해 프로세싱된다. 이들 기법들은 전자빔 증착과 같은 낸 플라즈마 애플리케이션들은 물론, 스퍼터 증착, 플라즈마-강화 화학 기상 증착 (PECVD), 레지스트 박리, 및 플라즈마 에칭과 같은 플라즈마 애플리케이션들을 포함한다.

[0003] 오늘날 이용 가능한 플라즈마 프로세싱 시스템들은 개선된 정확성 및 반복성의 필요성이 증가되기 쉬운 반도체 제조 툴들에 속한다. 플라즈마 프로세싱 시스템들에 대한 한가지 메트릭은 증가된 균일성이며, 이는 반도체 기판 표면 상의 프로세스 결과들의 균일성은 물론 명목상 동일한 입력 파라미터들로 프로세싱된 연속적인 기판들의 프로세스 결과들의 균일성을 포함한다. 기판 상의 균일성의 끊임없는 개선이 바람직하다. 그 중에서도, 이것은 개선된 균일성, 일관성 및 자체 진단을 가진 플라즈마 챔버들을 필요로 한다.

### 발명의 내용

### 과제의 해결 수단

[0004]

일 실시형태에 따르면, 반도체 플라즈마 프로세싱 장치에서 반도체 기판을 지지하는데 이용되는 기판 지지 어셈블리용 가열판은, 적어도, 제 1 전기 절연층, 제 1 전기 절연층에 걸쳐 측방향으로 분포된 제 1 평탄한 히터존, 제 2 평탄한 히터존, 제 3 평탄한 히터존 및 제 4 평탄한 히터존을 적어도 포함하는 평탄한 히터존들, 제 1 평탄한 히터존 및 제 2 평탄한 히터존에 전기적으로 접속된 제 1 전력 공급 라인 및 제 3 평탄한 히터존 및 제 4 평탄한 히터존에 전기적으로 접속된 제 2 전력 공급 라인을 적어도 포함하는 전기적 도전성 전력 공급 라인들, 및 제 1 평탄한 히터존 및 제 3 평탄한 히터존에 전기적으로 접속된 제 1 전력 복귀 (return) 라인 및 제 2 평탄한 히터존 및 제 4 평탄한 히터존에 전기적으로 접속된 제 2 전력 복귀 라인을 적어도 포함하는 전기적 도전성 전력 복귀 라인들을 포함한다.

반도체 프로세싱 장치에서 반도체 기판을 지지하는데 이용되는 기판 지지 어셈블리가 제공된다. 기판 지지 어셈블리는, 반도체 기판을 상기 기판 지지 어셈블리 상에 정전기적으로 클램핑하도록 구성된 적어도 하나의 클램핑 전극을 갖는 정전 클램핑층을 포함하는 정전체 (ESC); 상기 정전 클램핑층 아래에 배열된 가열판; 상기 가열판의 하부측에 열장벽층 (thermal barrier layer)에 의해 부착된 냉각판을 포함하고, 상기 가열판은, 제 1 전기 절연층; 각각 하나 이상의 히터 엘리먼트들을 포함하는, 제 1 평탄한 히터존, 제 2 평탄한 히터존, 제 3 평탄한 히터존 및 제 4 평탄한 히터존을 적어도 포함하는 평탄한 히터존들로서, 상기 평탄한 히터존들은 상기 제 1 전기 절연층에 걸쳐 측방향으로 분포되고 상기 반도체 기판 상의 공간 온도 프로파일을 튜닝하도록 동작가능한, 상기 평탄한 히터존들; 상기 제 1 평탄한 히터존 및 상기 제 2 평탄한 히터존에 전기적으로 접속된 제 1 전기적 도전성 전력 공급 라인 및 상기 제 3 평탄한 히터존 및 상기 제 4 평탄한 히터존에 전기적으로 접속된 제 2 전기적 도전성 전력 공급 라인을 적어도 포함하는 전력 공급 라인들; 및 상기 제 1 평탄한 히터존 및 상기 제 3 평탄한 히터존에 전기적으로 접속된 제 1 전기적 도전성 전력 복귀 (return) 라인 및 상기 제 2 평탄한 히터존 및 상기 제 4 평탄한 히터존에 전기적으로 접속된 제 2 전기적 도전성 전력 복귀 라인을 적어도 포함하는 전력 복귀 라인들을 포함하고, 그리고 (a) 상기 전력 공급 라인들은 서로로부터 전기적으로 절연되고 상기 냉각판 내의 적어도 하나의 전력 공급 도관을 통해 연장된 리드들에 접속되고, 상기 전력 복귀 라인들은 서로로부터 전기적으로 절연되고 상기 냉각판 내의 적어도 하나의 전력 복귀 도관을 통해 연장된 리드들에 접속되고; 또는 (b) 상기 전력 공급 라인들 및 상기 전력 복귀 라인들은 상기 냉각판 내에 임베딩된 터미널 커넥터들에 접속된다.

(a) 상기 평탄한 히터존들 및 상기 전력 공급 라인들은 제 1 평면에 있고; 상기 전력 복귀 라인들은 상기 제 1 평면에 평행한 제 2 평면에 있으며; 상기 제 1 평면 및 상기 제 2 평면은 서로 상기 제 1 전기 절연층에 의해 분리되고; 상기 전력 복귀 라인들은 상기 제 1 전기 절연층에서 수직으로 연장된 비아들에 의해 상기 평탄한 히터존들에 전기적으로 접속되고; 또는 (b) 상기 평탄한 히터존들 및 상기 전력 복귀 라인들은 제 1 평면에 있고; 상기 전력 공급 라인들은 상기 제 1 평면에 평행한 제 2 평면에 있으며; 상기 제 1 평면 및 상기 제 2 평면은 서로 상기 제 1 전기 절연층에 의해 분리되고; 상기 전력 공급 라인들은 상기 제 1 전기 절연층에서 수직으로 연장된 비아들에 의해 상기 평탄한 히터존들에 전기적으로 접속되며; 또는 (c) 상기 평탄한 히터존들은 제 1 평면에 있고; 상기 전력 공급 라인들은 상기 제 1 평면에 평행한 제 2 평면에 있으며; 상기 전력 복귀 라인들은 상기 제 1 평면에 평행한 제 3 평면에 있고; 상기 제 1 평면 및 상기 제 2 평면은 상기 제 1 전기 절연층에 의해 분리되며; 상기 제 2 평면 및 상기 제 3 평면은 제 2 전기 절연층에 의해 분리되고; 상기 전력 공급 라인들 및 상기 전력 복귀 라인들은 상기 전기 절연층들을 통해 연장된 비아들에 의해 상기 평탄한 히터존들에 전기적으로 접속된다.

상기 평탄한 히터존들은 : (a) 평탄한 히터존 각각이 상기 반도체 기판 상에 제작되는 4 개의 디바이스 다이들 보다 크지 않도록, 또는 (b) 평탄한 히터존 각각이 상기 반도체 기판 상에 제작되는 2 개의 디바이스 다이들 보다 크지 않도록, 또는 (c) 평탄한 히터존 각각이 상기 반도체 기판 상에 제작되는 하나의 디바이스 다이보다 크지 않도록, 또는 (d) 평탄한 히터존 각각의 면적은  $2\text{cm}^2$  와  $3\text{cm}^2$  사이가 되도록, 또는 (e) 상기 가열판이 100 내지 400 개의 평탄한 히터존들을 포함하도록, 또는 (f) 평탄한 히터존 각각이  $1\text{cm}^2$  내지  $15\text{cm}^2$  가 되도록, 또는 (g) 평탄한 히터존 각각이  $16\text{cm}^2$  내지  $100\text{cm}^2$  가 되도록, 또는 (h) 평탄한 히터존 각각이 상기 반도체 기판 상의 디바이스 다이들의 사이즈들 및 상기 반도체 기판의 전체 사이즈에 따라 스케일링되도록, 사이징된다.

상기 제 1 전기 절연층은 폴리머 재료, 세라믹 재료 또는 이들의 조합을 포함한다.

상기 전력 공급 라인들 및 상기 전력 복귀 라인들의 총 개수는 상기 평탄한 히터존들의 총 개수 이하이다.

상기 평탄한 히터존들의 총 면적은 상기 가열판의 상부면의 50% 내지 90% 이다.

상기 평탄한 히터존들은 직사각형 그리드, 6 각형 그리드 또는 동심원상 링들로 배열되고; 그리고 상기 평탄한

히터존들은, 폭이 최소한 1 밀리미터이고 폭이 최대한 10 밀리미터인 갭들에 의해 서로 분리된다.

정류기가 상기 히터존 각각과, 그 히터존에 접속된 상기 전력 공급 라인 사이에 직렬 접속되며, 또는 정류기가 상기 히터존 각각과 그 히터존에 접속된 상기 전력 복귀 라인 사이에 직렬 접속된다.

상기 정류기는 반도체 다이오드이다.

기판 지지 어셈블리는 임의의 주어진 시간에, (a) 단지 상기 제 1 평탄한 히터존에만, (b) 단지 상기 제 2 평탄한 히터존에만, (c) 단지 상기 제 3 평탄한 히터존에만, (d) 단지 상기 제 4 평탄한 히터존에만, (e) 단지 상기 제 1 평탄한 히터존과 상기 제 2 평탄한 히터존에만, (f) 단지 상기 제 1 평탄한 히터존과 상기 제 3 평탄한 히터존에만, (g) 단지 상기 제 2 평탄한 히터존과 상기 제 4 평탄한 히터존에만, (h) 단지 상기 제 3 평탄한 히터존과 상기 제 4 평탄한 히터존에만, 그리고 (i) 상기 평탄한 히터존들 전부에, 전력을 선택적으로 공급하도록 동작가능한 제어 및 전력 회로를 더 포함한다.

기판 지지 어셈블리는 상기 제어 및 전력 회로와 전기적 그라운드 사이에 직렬 접속된 적어도 하나의 필터 또는 아이솔레이터를 더 포함한다.

상기 적어도 하나의 필터 또는 아이솔레이터는 변압기이다.

기판 지지 어셈블리는 상기 가열판의 상기 제 1 전기 절연층의 상방 또는 하방에 배열된 적어도 하나의 프라이머리 히터층 (primary heater layer) 을 더 포함하며, 상기 프라이머리 히터층은, 상기 가열판의 상기 평탄한 히터존들, 상기 전력 공급 라인들, 및 상기 전력 복귀 라인들로부터 전기 절연되고; 상기 프라이머리 히터층은, 상기 반도체 기판의 평균 온도 제어를 제공하는 적어도 하나의 히터를 포함하며; 상기 평탄한 히터존들은, 상기 반도체 기판을 프로세싱하는 동안, 상기 반도체 기판의 방사상 및 방위각 온도 프로파일 제어를 제공한다.

상기 터미널 커넥터들은 스프링 텁핑된 패스스루 (spring tipped passthrough) 들이다.

상기 프라이머리 히터층은 2 개 이상의 히터들을 포함한다.

프로세싱 챔버 내의 반도체 기판 지지 어셈블리 상에 지지된 반도체 기판의 방사상 및 방위각 온도 제어를 제공하도록 구성된 가열판이 제공된다. 가열판은, 상기 반도체 기판 상에서 공간적 온도 프로파일을 튜닝하도록 동작가능한 히터존들의 어레이를 갖는 제 1 층으로서, 상기 히터존들은 2 개 이상의 전력 공급 라인들 및 2 개 이상의 전력 복귀 라인들에 의해 전력 공급되고, 전력 공급 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고 전력 복귀 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고, 상기 히터존 각각은 상기 반도체 기판 상에 제작되는 4 개의 디바이스 다이들보다 크지 않은, 상기 제 1 층; 및 상기 프로세싱 챔버 내에서의 프로세싱 동안 상기 반도체 기판의 평균 온도 제어를 제공하도록 동작가능한 하나 이상의 프라이머리 히터들을 갖는 제 2 층을 포함하는, 상기 가열판; 스위치들의 시분할 멀티플렉싱에 의해 상기 히터존들 각각에 시간 평균된 전력을 제공하도록, 상기 전력 공급 라인들 중 하나 및 상기 전력 복귀 라인들 중 하나를 통해 상기 히터존들 중 각각의 하나에 전력을 독립적으로 공급하는 스위칭 디바이스; 및 상기 가열판 아래의 온도 제어되고 무선 주파수 (RF) 전력 공급된 기판 지지 어셈블리 베이스 구조물 및 상기 기판 지지 어셈블리 베이스 구조물 아래의 로컬 패러데이 상자 (faraday cage) 내에 하우징된 상측 회로를 포함한다.

프로세싱 챔버 내의 반도체 기판 지지 어셈블리 상에 지지된 반도체 기판의 방사상 및 방위각 온도 제어를 제공하도록 구성된 가열판이 제공된다. 가열판은, 상기 반도체 기판 상에서 공간적 온도 프로파일을 튜닝하도록 동작가능한 히터존들의 어레이를 갖는 제 1 층으로서, 상기 히터존들은 2 개 이상의 전력 공급 라인들 및 2 개 이상의 전력 복귀 라인들에 의해 전력 공급되고, 전력 공급 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고 전력 복귀 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고, 상기 히터존 각각은 상기 반도체 기판 상에서 제작되는 4 개의 디바이스 다이들보다 크지 않은, 상기 제 1 층; 상기 프로세싱 챔버 내에서의 프로세싱 동안 상기 반도체 기판의 평균 온도 제어를 제공하도록 동작가능한 하나 이상의 프라이머리 히터들을 갖는 제 2 층을 포함하는, 상기 가열판; 스위치들의 시분할 멀티플렉싱에 의해 상기 히터존들 각각에 시간 평균된 전력을 제공하도록, 상기 전력 공급 라인들 중 하나 및 상기 전력 복귀 라인들 중 하나를 통해 상기 히터존들 중 각각의 하나에 전력을 독립적으로 공급하는 스위칭 디바이스; 및 상기 가열판 아래의 온도 제어되고 무선 주파수 (RF) 전력 공급된 기판 지지 어셈블리 베이스 구조물 및 상기 기판 지지 어셈블리 베이스 구조물 아래의 로컬 패러데이 상자 (faraday cage) 내에 하우징된 상측 회로를 포함한다.

동안 상기 반도체 기판의 평균 온도 제어를 제공하도록 동작가능한 하나 이상의 프라이머리 히터들을 갖는 제 2 층; 및 제 1 전기 절연층과 함께, 상기 제 1 전기 절연층에 걸쳐 측방향으로 분포되고 제 1 평탄한 히터존, 제 2 평탄한 히터존, 제 3 평탄한 히터존 및 제 4 평탄한 히터존을 적어도 포함하는 평탄한 히터존들로서, 상기 평탄한 히터존들은 각각 하나 이상의 히터 엘리먼트들을 포함하는, 상기 평탄한 히터존들을 포함하고, 상기 전력 공급 라인들은, 상기 제 1 평탄한 히터존 및 상기 제 2 평탄한 히터존에 전기적으로 접속된 제 1 전기적 도전성 전력 공급 라인 및 상기 제 3 평탄한 히터존 및 상기 제 4 평탄한 히터존에 전기적으로 접속된 제 2 전기적 도전성 전력 공급 라인을 적어도 포함하고, 그리고 상기 전력 복귀 라인들은, 상기 제 1 평탄한 히터존 및 상기 제 3 평탄한 히터존에 전기적으로 접속된 제 1 전기적 도전성 전력 복귀 라인 및 상기 제 2 평탄한 히터존 및 상기 제 4 평탄한 히터존에 전기적으로 접속된 제 2 전기적 도전성 전력 복귀 라인을 적어도 포함한다.

상기 가열판은, 상기 반도체 기판의 위치들에서 온도를 측정하도록 구성된 온도 센서들; 및 상기 히터존들의 어레이에 접속되고 상기 온도 센서들로부터 측정된 파라미터들을 수신하고 상기 측정된 파라미터들과 설정된 목표들 간의 차이들을 최소화하도록 상기 히터존들에 전달된 전력을 조정하도록 구성된 제어 및 전력 회로를 포함하는, 상기 반도체 기판 지지 어셈블리 내에 통합된다.

전기적 그라운드 사이에 접속된 아이솔레이터를 더 포함하고, 상기 스위칭 디바이스는 상기 아이솔레이터에 접속된다.

상기 스위칭 디바이스는 플라즈마 에칭 챔버 내에 위치된다.

상기 아이솔레이터는 상기 스위칭 디바이스를 RF로부터 격리시키는 절연 변압기 (isolation transformer) 이다.

프로세싱 챔버 내의 반도체 기판 지지 어셈블리 상에 지지된 반도체 기판의 방사상 및 방위각 온도 제어를 제공하도록 구성된 가열판이 제공된다.

가열판은, 상기 반도체 기판 상에서 공간적 온도 프로파일을 튜닝하도록 동작가능한 히터존들의 어레이를 갖는 제 1 층으로서, 상기 히터존들은 2 개 이상의 전력 공급 라인들 및 2 개 이상의 전력 복귀 라인들에 의해 전력 공급되고, 전력 공급 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고 전력 복귀 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고, 상기 히터존 각각은 상기 반도체 기판 상에 제작되는 4 개의 디바이스 다이들 보다 크지 않은, 상기 제 1 층; 및 상기 프로세싱 챔버 내에서의 프로세싱 동안 상기 반도체 기판의 평균 온도 제어를 제공하도록 동작가능한 하나 이상의 프라이머리 히터들을 갖는 제 2 층을 포함하고, 상기 히터존들은 제 1 전기 절연층 상에 지지되고; 상기 제 2 층은 상기 제 1 전기 절연층 위 또는 아래에 배열되고; 그리고 상기 하나 이상의 프라이머리 히터들은 상기 히터존들의 어레이, 상기 전력 공급 라인들, 및 상기 전력 복귀 라인들로부터 전기적으로 절연된다.

상기 스위칭 디바이스는 RF 전위에서 플로팅하는 상측 제어기이고, 상기 기판 지지 어셈블리는, 하측 제어기와의 디지털 통신을 위해 상기 상측 제어기에 접속된 광 커플러를 더 포함한다.

상기 스위칭 디바이스는 적어도 하나의 전력 복귀 라인을 플로팅 레퍼런스에 접속한다.

상기 스위칭 디바이스는 상기 히터존에 접속된 적어도 하나의 전력 공급 라인이 전력 공급장치에 접속되고, 그리고 상기 히터존에 접속된 적어도 하나의 전력 복귀 라인이 플로팅 레퍼런스에 접속될 때 상기 히터존들 중 하나를 턴 온하도록 구성된다.

상기 스위칭 디바이스는 모든 상기 전력 복귀 라인들을 플로팅 레퍼런스에 접속한다.

상기 스위칭 디바이스는 적어도 1Hz의 주파수에서 상기 히터존들의 어레이의 히터존 각각을 어드레싱하도록 구성된다.

상기 가열판을 포함하는 기판 지지 어셈블리가 제공된다. 상기 기판 지지 어셈블리는 상기 기판 지지 어셈블리 상의 상이한 위치들 및 상기 히터존들의 전력에 대한 파라미터들을 측정하도록 구성된 센서들을 포함한다.

상기 센서들은 전압 센서 및 전류 센서 중 적어도 하나를 포함한다.

상기 측정된 파라미터들은 적어도 온도 측정치들을 포함한다.

상기 스위칭 디바이스는, 일 전력 공급 라인에 전력 공급되는 시간 동안 모든 상기 전력 복귀 라인들과 플로팅 레퍼런스 사이의 접속을 유지하고 턴 온된 히터존을 가열하기 위해 전송된 전력을 조절하도록 구성된다.

기판 지지 어셈블리가 제공된다. 기판 지지 어셈블리는, 프로세싱 챔버 내의 반도체 기판 지지 어셈블리 상에

지지된 반도체 기판의 방사상 및 방위각 온도 제어를 제공하도록 구성된 가열판으로서, 상기 반도체 기판 상에서 공간적 온도 프로파일을 튜닝하도록 동작가능한 히터존들의 어레이를 갖는 제 1 층으로서, 상기 히터존들은 2 개 이상의 전력 공급 라인들 및 2 개 이상의 전력 복귀 라인들에 의해 전력 공급되고, 전력 공급 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고 전력 복귀 라인 각각은 상기 히터존들 중 적어도 2 개에 접속되고, 상기 히터존 각각은 상기 반도체 기판 상에서 제작되는 4 개의 디바이스 다이들보다 크지 않은, 상기 제 1 층; 및 상기 프로세싱 챔버 내에서의 프로세싱 동안 상기 반도체 기판의 평균 온도 제어를 제공하도록 동작가능한 하나 이상의 프라이머리 히터들을 갖는 제 2 층을 포함하는, 상기 가열판; 및 상기 가열판 위의 정전 클램핑층을 포함한다.

상기 가열판 아래의 무선 주파수 (RF) 전력 공급된 기판 지지 어셈블리 베이스 구조물을 더 포함한다.

상기 히터존들은 세라믹 재료 내에 임베딩된 적어도 100 개의 독립적으로 제어가능한 히터존들을 포함한다.

### 도면의 간단한 설명

[0005]

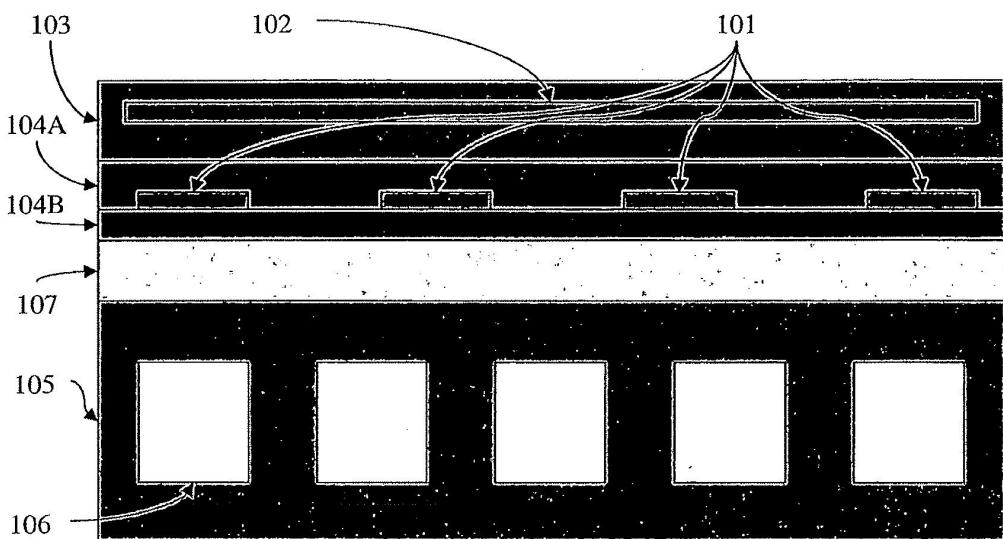

도 1 은, 히터존들의 어레이를 가진 가열판이 통합되고, 정전 척 (ESC) 을 또한 포함하는 기판 지지 어셈블리의 개략적인 단면도이다.

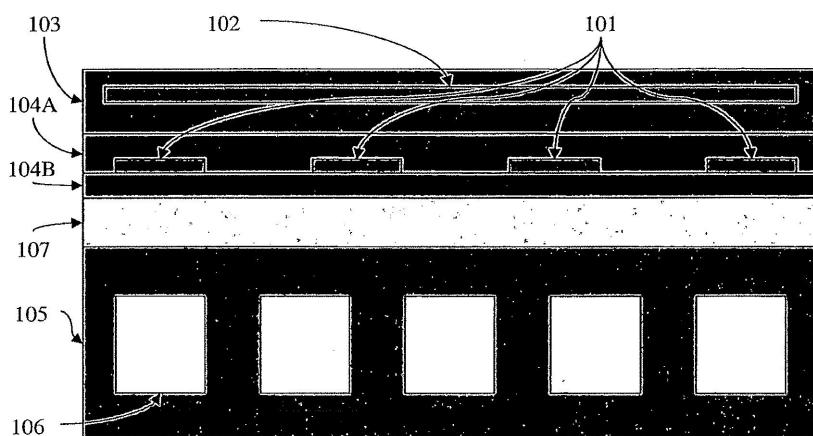

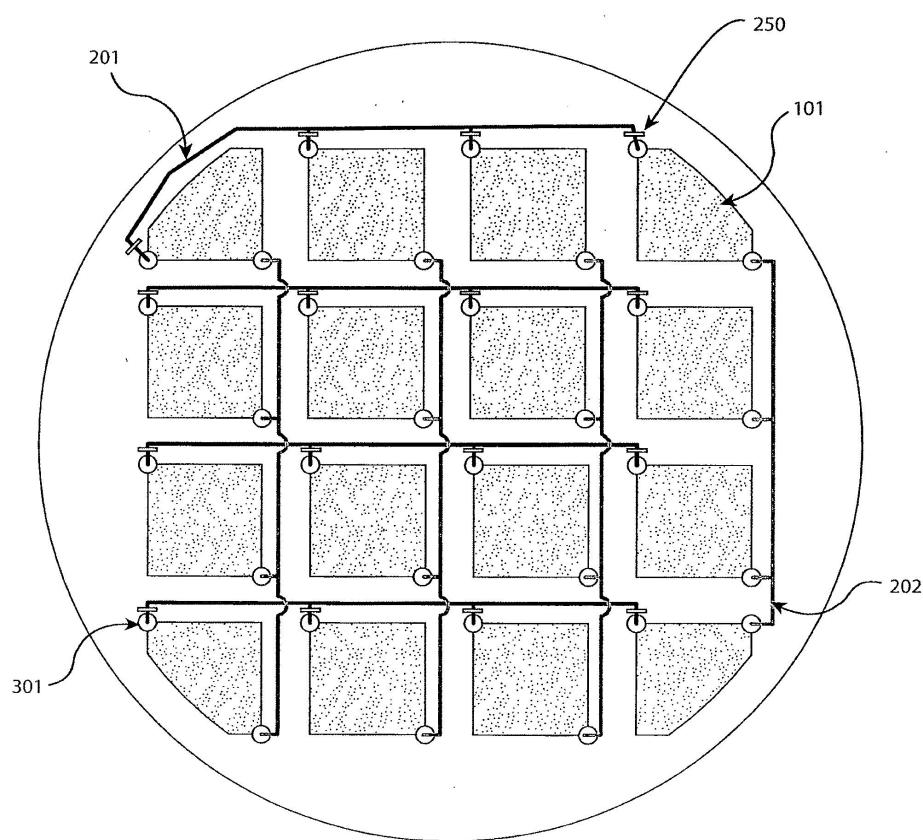

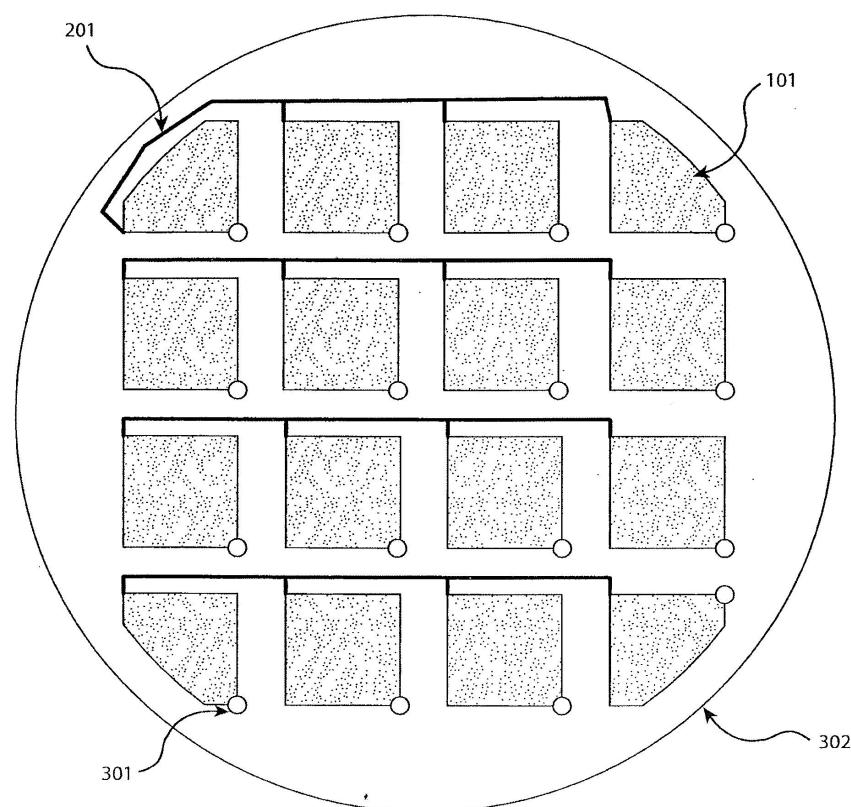

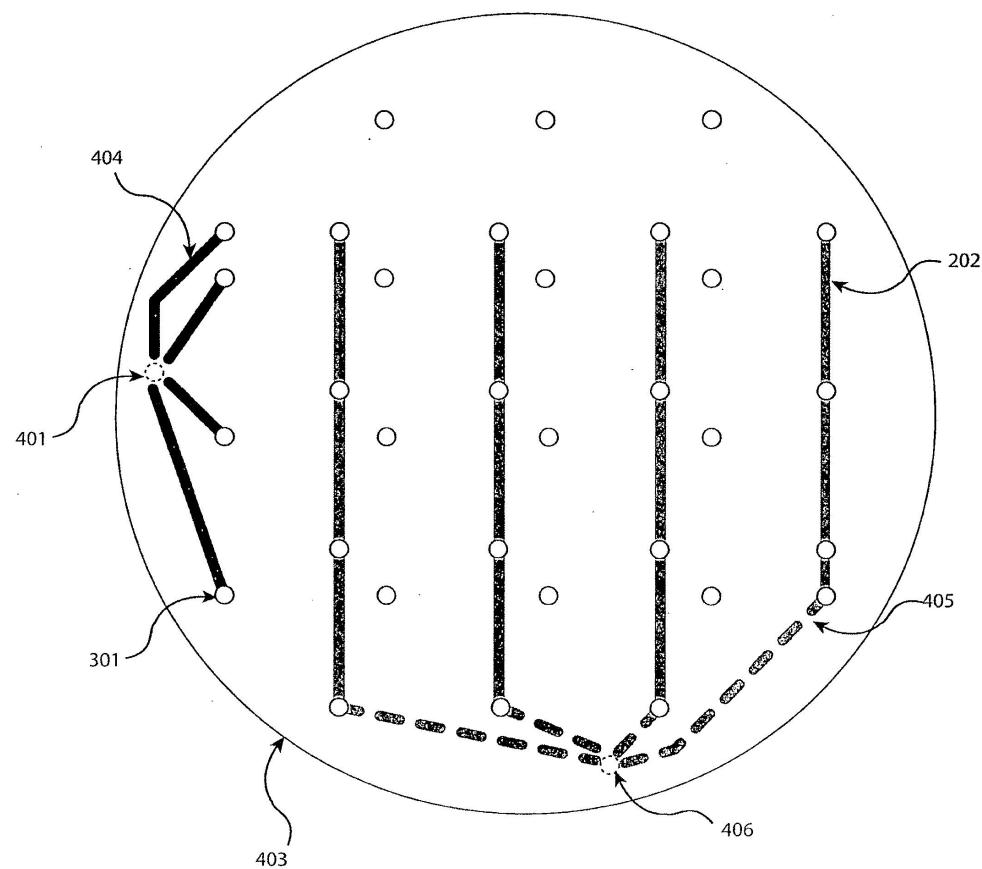

도 2 는, 기판 지지 어셈블리에 통합될 수 있는 가열판의 일 실시형태에서의 히터존들의 어레이에 대한 전력 공급 라인들과 전력 복귀 라인들 간의 토플로지 접속을 예시한 도면이다.

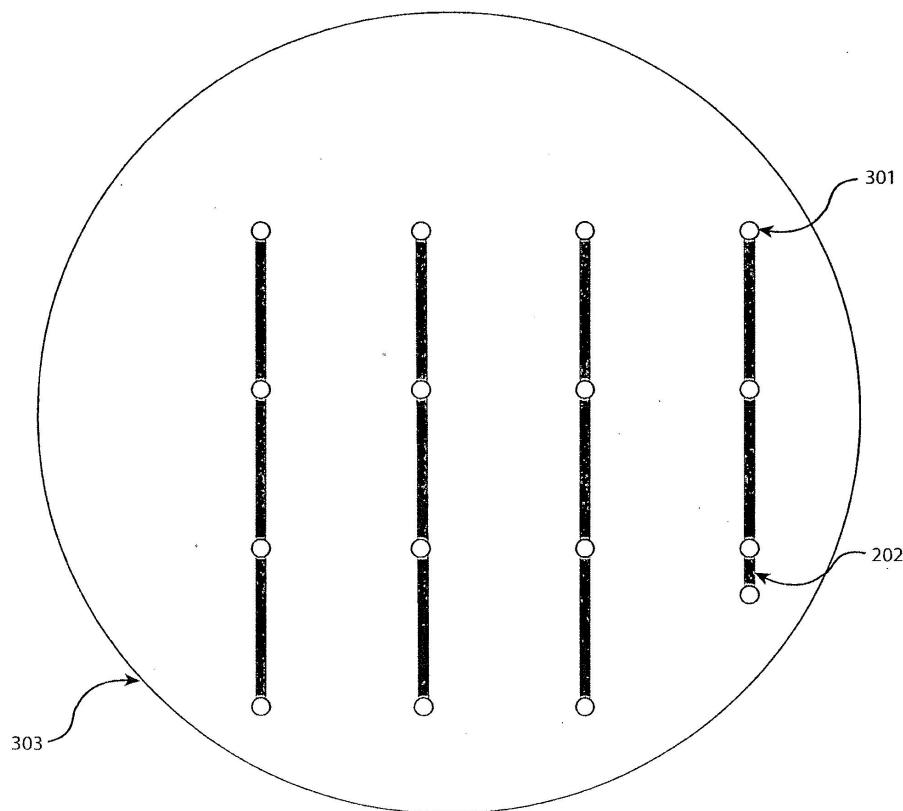

도 3a 는, 전력 공급 라인들 및 히터존들이 동일 평면 상에 있는 실시형태를 도시한 도면이다.

도 3b 는, 도 3a 의 평면과는 전기 절연층에 의해 분리된 평면 상의 전력 복귀 라인들을 도시한 도면으로, 전력 복귀 라인들은 전기 절연층을 통하여 연장된 비아들을 통해 히터존들에 접속된다.

도 3c 는, 도 3a 및 도 3b 의 가열판이 통합되는 기판 지지 어셈블리의 개략적인 단면도이다.

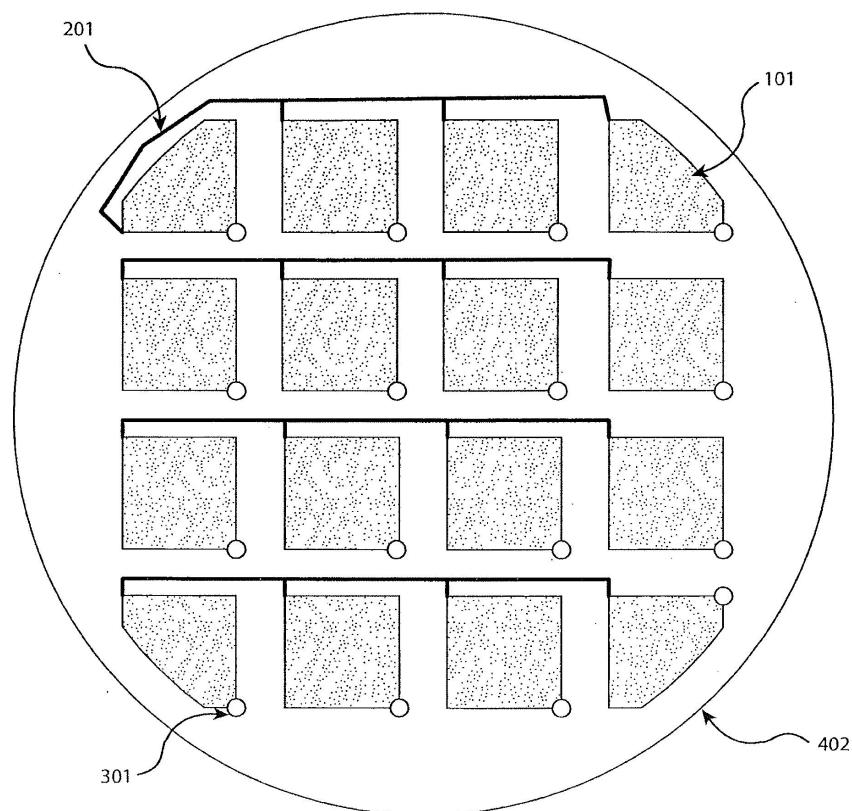

도 4a 는, 전력 공급 라인들 및 히터존들이 동일 평면 상에 있는 실시형태를 도시한 도면이다.

도 4b 는, 도 4a 의 평면과는 전기 절연층에 의해 분리된 평면을 도시한 도면으로, 전력 공급 라인들은 비아들을 통하여 이 평면 내의 리드들에 접속되고, 냉각판 (미도시) 내의 단일 홀에 이르게 된다. 이 평면 상의 전력 복귀 라인들은 이 평면과 도 4a 의 평면 사이에서 연장된 비아들을 통하여 히터존들에 접속된다. 전력 복귀 라인들은 또한 냉각판 (미도시) 내의 단일 홀에 이르게 된다.

도 5a 는, 히터존들이 일 평면 상에 있고 전력 공급 라인들 또는 전력 복귀 라인들이 그 평면 상에 없는 실시형태를 도시한 도면이다. 히터존들은 비아들을 통하여 하나 이상의 상이한 평면들 상의 전력 공급 라인들 및 전력 복귀 라인들에 접속된다.

도 5b 는, 도 5a 의 평면과는 전기 절연층에 의해 분리된 제 2 평면 상의 전력 공급 라인들을 도시한 도면이다.

전력 공급 라인들은 도 5a 및 도 5b 의 2 개의 평면들 사이에서 연장된 비아들을 통하여 히터존들에 접속된다.

도 5c 는, 도 5a 및 도 5b 의 평면들과는 다른 전기 절연층에 의해 분리된 제 3 평면 상의 전력 복귀 라인들을 도시한 도면이다. 전력 복귀 라인들은 도 5a 내지 도 5c 의 3 개의 평면들 모두 사이에서 연장된 비아들을 통하여 히터존들에 접속된다. 도 5b 의 전력 공급 라인들에 접속된 리드들은 또한 이 평면 내의 피드스루들을 통하여 라우팅된다.

도 5d 는, 도 5a 내지 도 5c 의 가열판이 통합되는 기판 지지 어셈블리의 개략적인 단면도이다.

도 5e 는, 도 5a 내지 도 5c 의 대안의 가열판이 통합되는 기판 지지 어셈블리의 개략적인 단면도이다.

도 6 은, 가열판이 통합되는 기판 지지 어셈블리의 개략적인 단면도로, 기판 지지 어셈블리는 히터존들의 어레이 상방에 프라이머리 히터 층을 더 포함하고, 프라이머리 히터는 가열판 내의 모든 평면들과는 전기 절연층에 의해 분리된 추가적인 평면 상에 위치한다.

도 7a 는, 여기에 설명된 가열판을 가진 기판 지지 어셈블리를 포함할 수 있는, 예시적인 플라즈마 프로세싱 챔버의 개략도이다.

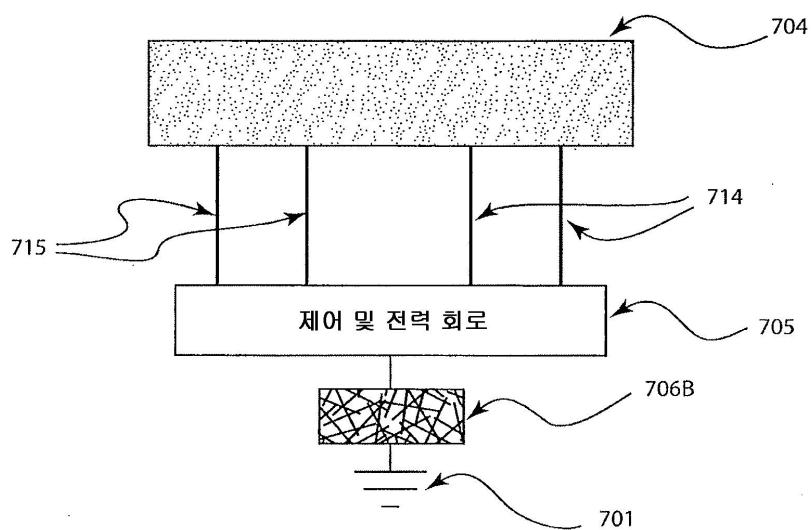

도 7b 는 RF 격리 접근법의 개략도이다.

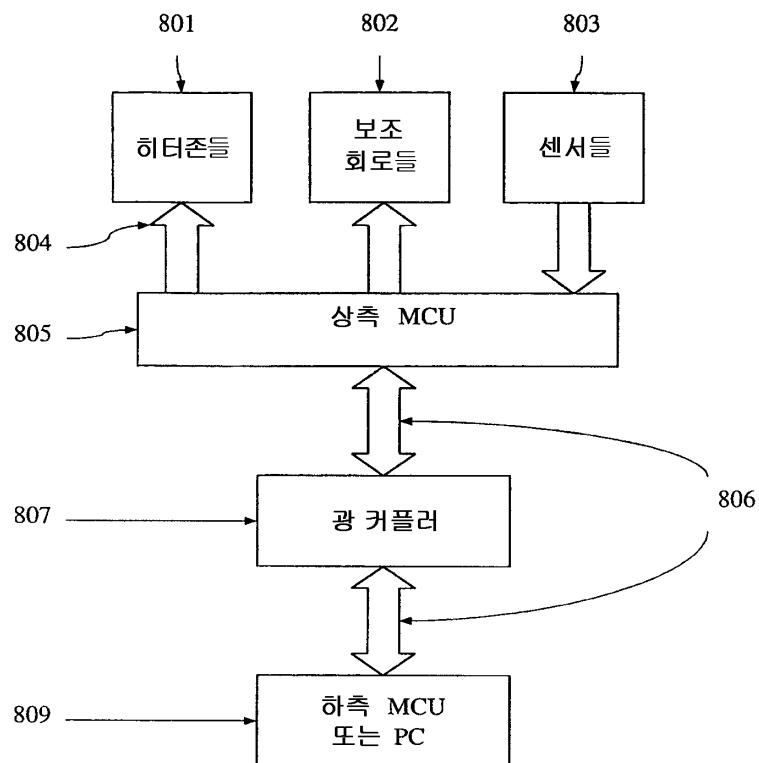

도 8 은, 기판 지지 어셈블리용 제어 전자장치의 일 실시형태에서의 신호 흐름을 도시한 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

[0006]

기판 상의 원하는 임계 치수 (CD) 균일성을 달성하기 위한 반도체 프로세싱 장치에서의 방사상 및 방위각 기판 온도 제어가 더 많이 요구되고 있다. 작은 온도 변화라도, 특히 반도체 제조 프로세스에서 CD 가 서브-100nm 에 가까워질 때, 허용불가능한 정도로 CD 에 영향을 미칠 수도 있다.

[0007]

기판 지지 어셈블리는, 기판의 지지, 기판 온도의 튜닝 및 무선 주파수 전력의 전력 공급과 같이, 프로세싱 동안 다양한 기능들을 위해 구성될 수도 있다. 기판 지지 어셈블리는, 프로세싱 동안 기판 지지 어셈블리에 기판을 정전식으로 클램핑하는데 유용한 정전 척 (ESC) 을 포함할 수 있다. ESC 는 튜닝가능한 ESC (T-ESC) 일 수도 있다. T-ESC 는 여기에 참조로 통합되는 공동 양도된 미국 특허 제6,847,014호 및 미국 특허 제6,921,724호에 기술되어 있다. 기판 지지 어셈블리는, 세라믹 기판 홀더, 유체-냉각 열 싱크 (이하 냉각판으로 지칭) 및 복수의 동심원상 히터존들을 포함하여 단계적 (step by step) 및 방사상 온도 제어를 실현할 수도 있다. 통상적으로, 냉각판은 0°C 와 30°C 사이에 유지된다. 히터들은 중간에 단열재 층을 가진 냉각판 상에 위치한다. 히터들은 기판 지지 어셈블리의 지지면을 약 0°C 내지 냉각판 온도보다 높은 80°C 의 온도로 유지할 수 있다. 복수의 히터존들 내의 히터 전력을 변화시킴으로써, 기판 지지 온도 프로파일이 센터 핫 (center hot), 센터 콜드 (center cold), 및 균일 사이에서 변화될 수 있다. 또한, 평균 기판 지지 온도는 0°C 내지 냉각판 온도보다 높은 80°C 의 동작 범위 내에서 단계적으로 변화될 수 있다. 작은 방위각 온도 변화는, 반도체 기술의 진보로 CD 가 감소함에 따라 점차 더 큰 문제를 제기한다.

[0008]

온도의 제어는 여러 이유들로 인해 쉬운 태스크가 아니다. 첫째로, 열원 및 열 싱크의 장소, 미디어의 형상, 재료 및 움직임과 같은 많은 팩터들이 열 전달에 영향을 미칠 수 있다. 둘째로, 열 전달은 동적 프로세스이다. 문제의 시스템이 열평형 상태에 있지 않다면, 열 전달이 발생할 것이고, 온도 프로파일 및 열 전달은 시간에 따라 변할 것이다. 셋째로, 플라즈마 프로세싱 시에 항상 존재하는 플라즈마와 같은 비평형 현상들은, 임의의 실제 플라즈마 프로세싱 장치의 열 전달 거동 (behavior) 의 이론적 예측을 불가능하지 않다면 매우 어렵게 만든다.

[0009]

플라즈마 프로세싱 장치의 기판 온도 프로파일은 플라즈마 밀도 프로파일, RF 전력 프로파일 및 척 내의 다양한 가열 또는 냉각 엘리먼트들의 세부 구조와 같은 많은 팩터들에 의해 영향을 받기 때문에, 기판 온도 프로파일은 종종 균일하지 않고 적은 수의 가열 또는 냉각 엘리먼트들을 사용하여 제어하기 어렵다. 이런 결점은 전체 기판에 걸친 프로세싱 레이트의 비균일성 및 기판 상의 디바이스 사이들의 임계 치수의 비균일성으로 바뀐다.

[0010]

온도 제어의 복잡한 성질을 고려하여, 장치가 원하는 공간 및 시간 온도 프로파일을 능동적으로 생성 및 유지할 수 있게 하고, CD 균일성에 영향을 미치는 다른 불리한 팩터들을 보상할 수 있게 하기 위해, 기판 지지 어셈블리에 다중의 독립적으로 제어가능한 히터존들을 통합하는 것이 바람직할 것이다.

[0011]

다중의 독립적으로 제어가능한 히터존들을 가진 반도체 프로세싱 장치 내의 기판 지지 어셈블리용 가열판이 여기에 설명되어 있다. 이 가열판은 히터존들 및 전력 공급 및 전력 복귀 (return) 라인들의 스케일가능한 멀티플렉싱 레이아웃 스킴을 포함한다. 히터존들의 전력을 튜닝함으로써, 프로세싱 중의 온도 프로파일은 방사상으로 그리고 방위각으로 형상화될 수 있다. 이 가열판은 주로 플라즈마 프로세싱 장치용으로 설명되지만, 이 가열판은 플라즈마를 이용하지 않는 다른 반도체 프로세싱 장치에도 이용될 수 있다.

[0012]

이 가열판을 제작하는 방법, 이러한 가열판을 포함하는 기판 지지 어셈블리, 및 이러한 가열판을 포함하는 기판 지지 어셈블리를 전력공급 및 제어하는 방법이 또한 설명되어 있다.

[0013]

이 가열판 내의 히터존들은 규정된 패턴, 예를 들어, 직사각형 그리드, 6 각형 그리드, 극성 어레이 (polar array), 동심원상 링 또는 임의의 원하는 패턴으로 배열되는 것이 바람직하다. 각 히터존은 임의의 적절한 사이즈로 이루어질 수도 있고, 하나 이상의 히터 엘리먼트들을 가질 수도 있다. 히터존 내의 모든 히터 엘리먼트들은 함께 턴 온되거나 또는 턴 오프된다. 전기 접속의 수를 최소화하기 위해, 전력 공급 라인들 및 전력 복귀 라인들은, 각 전력 공급 라인이 상이한 그룹의 히터존들에 접속되고, 각 전력 복귀 라인이 상이한 그룹의 히터존들에 접속되도록 배열되며, 여기서 각 히터존은 특정 전력 공급 라인에 접속된 그룹들 중 하나 및 특정 전력 복귀 라인에 접속된 그룹들 중 하나에 있다. 동일한 전력 공급 및 전력 복귀 라인들의 쌍에는 2 개의 히터존들이 접속되어 있는 것은 아니다. 따라서, 히터존은, 이 특정 히터존이 접속되는 전력 공급 및 전력 복귀 라인들의 쌍을 통하여 전류를 향하게 함으로써 활성화될 수 있다. 히터 엘리먼트들의 전력은 바람직하게는 20W 보다 작고, 보다 바람직하게는 5W 내지 10W 이다. 히터 엘리먼트들은 저항성 히터들, 이를

테면, 폴리이미드 히터들, 실리콘 고무 히터들, 운모 히터들, 금속 히터들 (예를 들어, W, Ni/Cr 합금, Mo 또는 Ta), 세라믹 히터들 (예를 들어, WC), 반도체 히터들 또는 탄소 히터들일 수도 있다. 히터 엘리먼트들은 스크린 인쇄, 권선 또는 에칭된 포일 (foil) 히터들일 수도 있다. 일 실시형태에서, 각 히터존은 반도체 기판 상에 제작되는 4 개의 디바이스 다이들보다 크지 않고, 또는 반도체 기판 상에 제작되는 2 개의 디바이스 다이들보다 크지 않고, 또는 반도체 기판 상에 제작되는 하나의 디바이스 다이보다 크지 않으며, 또는 기판 상의 디바이스 다이들에 대응하도록 면적이  $2\text{cm}^2$  와  $3\text{cm}^2$  사이다. 히터 엘리먼트들의 두께는 2 마이크로미터 내지 1 밀리미터, 바람직하게는 5 내지 80 마이크로미터의 범위일 수도 있다. 히터존들 및/또는 전력 공급 및 전력 복귀 라인들 간에 공간을 허용하기 위해, 히터존들의 총 면적은 기판 지지 어셈블리의 상부면의 면적의 90% 까지, 예를 들어, 그 면적의 50 내지 90% 일 수도 있다. 전력 공급 라인들 또는 전력 복귀 라인들 (일괄하여 전력 라인들) 은 히터존들 사이의 1mm 내지 10mm 의 범위에 이르는 캡들에, 또는 히터존들의 평면과는 전기 절연층들에 의해 분리된 별개의 평면들에 배열될 수도 있다. 전력 공급 라인들 및 전력 복귀 라인들은 큰 전류를 운반하고 줄 가열 (Joule heating) 을 감소시키기 위하여, 공간이 허용되는 만큼 넓게 만들어지는 것이 바람직하다. 전력 라인들이 히터존들과 동일한 평면에 있는 일 실시형태에서, 전력 라인들의 폭은 0.3mm 와 2mm 사이인 것이 바람직하다. 전력 라인들이 히터존들과는 상이한 평면들 상에 있는 다른 실시형태에서, 전력 라인들의 폭은 히터존들만큼 넓을 수 있고, 예를 들어, 300mm 척의 경우, 그 폭은 1 인치 내지 2 인치일 수 있다. 전력 공급 라인들 및 전력 복귀 라인들의 재료는 히터 엘리먼트들의 재료와 동일할 수도 있고, 또는 상이할 수도 있다. 바람직하게는, 전력 공급 라인들 및 전력 복귀 라인들의 재료는 Cu, Al, W, Inconel<sup>®</sup> 또는 Mo 와 같은 낮은 저항률을 가진 재료이다.

[0014]

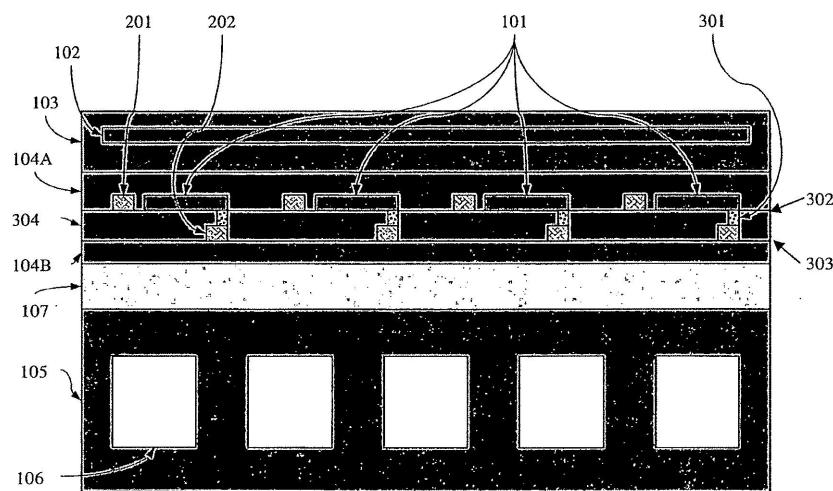

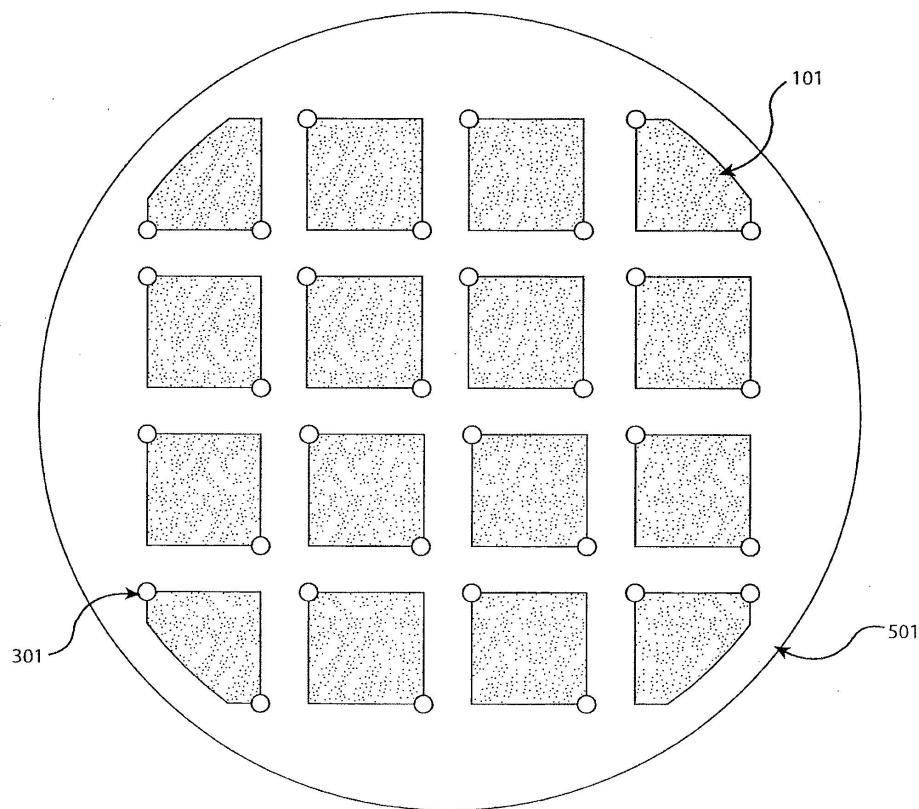

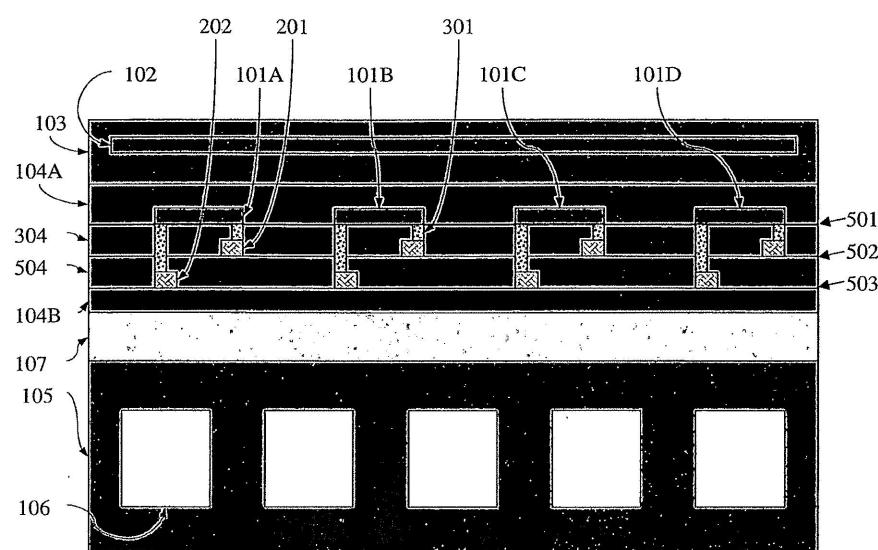

도 1 및 도 2 는 2 개의 전기 절연층들 (104A 및 104B) 에 통합된 히터존들 (101) 의 어레이를 갖는 가열판의 일 실시형태를 포함하는 기판 지지 어셈블리를 도시한다. 전기 절연층들은 폴리머 재료, 무기 재료, 세라믹, 이를 테면 실리콘 산화물, 알루미나, 이트륨, 알루미늄 질화물, 다른 적절한 재료, 또는 이들의 조합일 수도 있다. 기판 지지 어셈블리는, (a) DC 전압으로 세라믹층 (103) 의 표면에 기판을 정전식으로 클램핑하기 위해 전극 (102) (예를 들어, 단극 또는 양극) 이 임베딩되는 (embedded) 세라믹층 (103) (정전 클램핑층) 을 갖는 ESC, (b) 열장벽층 (thermal barrier layer) (107), 및 (c) 냉각제 흐름을 위한 채널들 (106) 을 포함하는 냉각판 (105) 을 더 포함한다.

[0015]

도 2 에 도시한 바와 같이, 히터존들 (101) 각각은 전력 공급 라인들 (201) 중 하나, 그리고 전력 복귀 라인들 (202) 중 하나에 접속된다. 2 개의 히터존들 (101) 이 동일한 전력 공급 (201) 및 전력 복귀 (202) 라인들의 쌍을 공유하지는 않는다. 적절한 전기 스위칭 배열에 의해, 전력 공급 (201) 및 전력 복귀 (202) 라인들의 쌍을 전력 공급장치 (미도시) 에 접속시키는 것이 가능하며, 이로써 단지 이 라인들의 쌍에 접속된 히터존만이 턴 온된다. 각 히터존의 시간-평균 가열 전력 (heating power) 은 시간-도메인 멀티플렉싱에 의해 개별적으로 튜닝될 수 있다. 상이한 히터존들 간의 크로스토크를 방지하기 위하여, 정류기 (250) (예를 들어, 디이오드) 가 각 히터존과 (도 2 에 도시한 바와 같이) 그 히터존에 접속된 전력 공급 라인들 사이에, 또는 각 히터존과 그 히터존에 접속된 전력 복귀 라인들 (미도시) 사이에 직렬 접속될 수도 있다. 정류기는 가열판 또는 임의의 적절한 장소에 물리적으로 위치할 수 있다. 대안으로는, 고체 (solid state) 스위치들과 같은 임의의 전류 차단 배열이 크로스토크를 방지하는데 이용될 수 있다.

[0016]

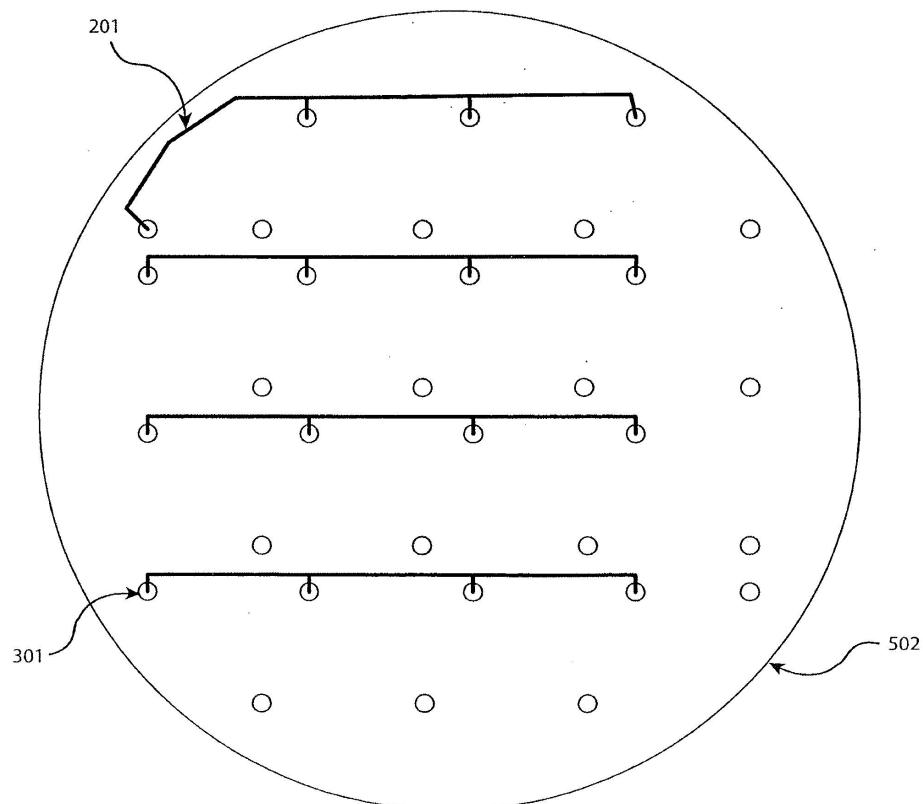

도 3a, 도 3b 및 도 3c 는, ESC, 냉각판, 및 히터존들 (101) 및 전력 공급 라인들 (201) 이 제 1 평면 (302) 에 배열되고, 전력 복귀 라인들 (202) 이 제 1 평면 (302) 과는 전기 절연층 (304) 에 의해 분리된 제 2 평면 (303) 에 배열되는 가열판의 일 실시형태를 포함하는 기판 지지 어셈블리를 도시한다. 전력 복귀 라인들 (202) 은 제 1 평면 (302) 과 제 2 평면 (303) 사이에서 연장된, 전기 절연층 (304) 내의 도전성 비아들 (301) 에 의해 히터존들 (101) 에 접속된다.

[0017]

이용 시, 전력 공급 라인들 (201) 및 전력 복귀 라인들 (202) 은 냉각판 내의 홀들 또는 도관들을 통하여 가열판 외부의 회로에 접속된다. 냉각판 내의 홀들 또는 도관들의 존재는 기판 지지 어셈블리의 온도 균일성을 악영향을 미칠 수 있으며, 따라서 냉각판 내의 홀들 또는 도관들의 개수를 감소시키면, 온도 균일성을 향상시킬 수 있다는 것을 알아야 한다. 또한, 적은 수의 홀들은 그들을 기판 지지 어셈블리의 에지 주변에 배치하는 것을 가능하게 한다. 예를 들어, 냉각판 내의 단일의 전력 공급 도관이 전력 공급 라인들 (201) 에 전기 리드들을 피딩하는데 이용될 수 있다. 일 실시형태 (도 4a 및 도 4b) 에서, 히터존들 (101) 및 전력 공급 라인들 (201) 은 제 1 평면 (402) 에 배열된다. 전력 공급 라인들 (201) 은 제 1 평면 (402) 과 제 2 평면 (403) 사이에서 연장된 도전성 비아들 (301) 을 통하여 제 2 평면 (403) 내의 리드들 (404) 에 접속된다.

제 2 평면 (403) 은 제 1 평면 (402) 과는 전기 절연층 (미도시) 에 의해 분리된다. 전력 복귀 라인들 (202) 은 제 2 평면 (403) 에 배열되고, 제 1 평면 (402) 과 제 2 평면 (403) 사이에서 연장된 도전성 비아들 (301) 을 통하여 히터존들 (101) 에 접속된다. 제 2 평면 (403) 에서, 리드들 (404) 은 그 리드들 간의 전기 절연을 유지하면서 냉각판 내의 홀 또는 도관 (401) 을 통과하게 된다. 유사하게, 전력 복귀 라인들 (202) 은 리드들 (405) 간의 전기 절연을 유지하면서 냉각판 내의 홀 또는 도관 (406) 을 통과하게 된 리드들 (405) 에 접속된다.

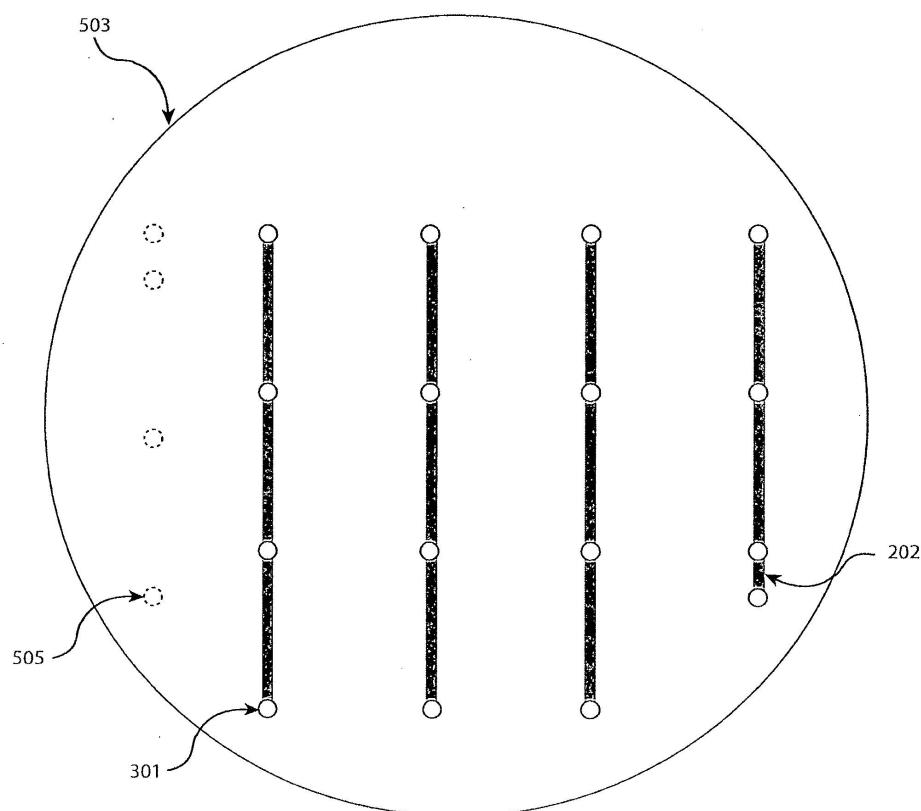

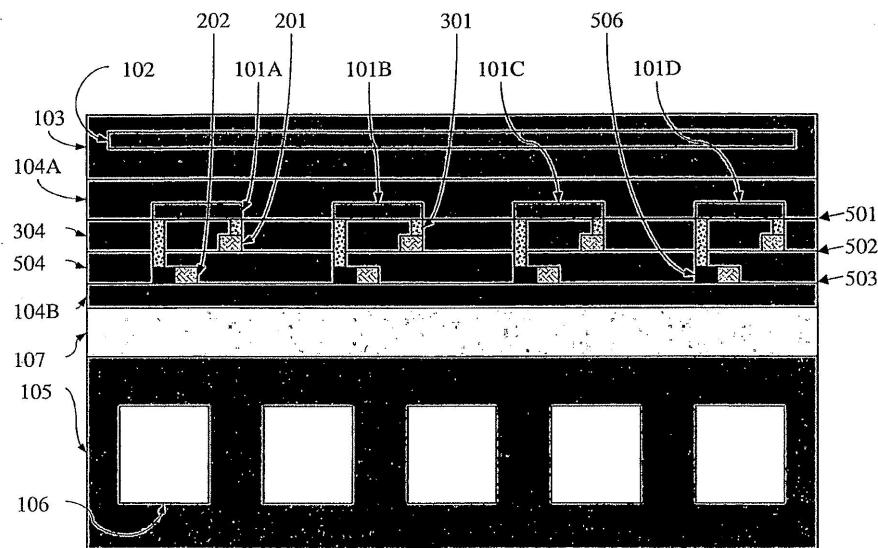

[0018] 도 5a, 도 5b, 도 5c 및 도 5d 는 가열판의 또 다른 실시형태를 포함하는 기판 지지 어셈블리를 도시하며, 히터 존들 (101) 은 제 1 평면 (501) 에 배열되고; 전력 공급 라인들 (201) 은 제 2 평면 (502) 에 배열되며; 전력 복귀 라인들 (202) 은 제 3 평면 (503) 에 배열된다. 제 1 평면 (501), 제 2 평면 (502) 및 제 3 평면 (503) 은 서로 전기 절연층들 (504 및 304) 에 의해 분리된다. 전력 공급 라인들 (201) 및 전력 복귀 라인들 (202) 은 평면들 (501, 502, 및 503) 사이에서 연장된, 전기 절연층들 (304 및 504) 내의 도전성 비아들 (301) 을 통하여 히터존들 (101) 에 접속된다. 전력 공급 라인들 (201) 에 접속된 리드들 (미도시) 은 총 (504) 내의 홀들 또는 도관들 (505) 을 통하여 라우팅된다. 평면들 (501, 502 및 503) 은, 비아들 및 도관들이 적절히 배열되는 것을 가정하여, 수직 방향으로 임의의 순서로 배열될 수도 있다는 것을 알아야 한다. 바람직하게는, 히터들은 기판 지지 어셈블리 상부면에 가장 근접하게 배열된다. 도 5e 는, 각 히터존 (101) 이 정류기 (506) (예를 들어, 다이오드) 를 통하여 전력 복귀 라인 (202) 에 접속되는 실시형태를 도시한다. 정류기 (506) 는 단지 전력 공급 라인 (201) 으로부터 히터존 (101) 을 통하여 전력 복귀 라인 (202) 으로 흐르는 전류만을 허용하기 때문에, 히터존들 간의 크로스토크를 방지한다.

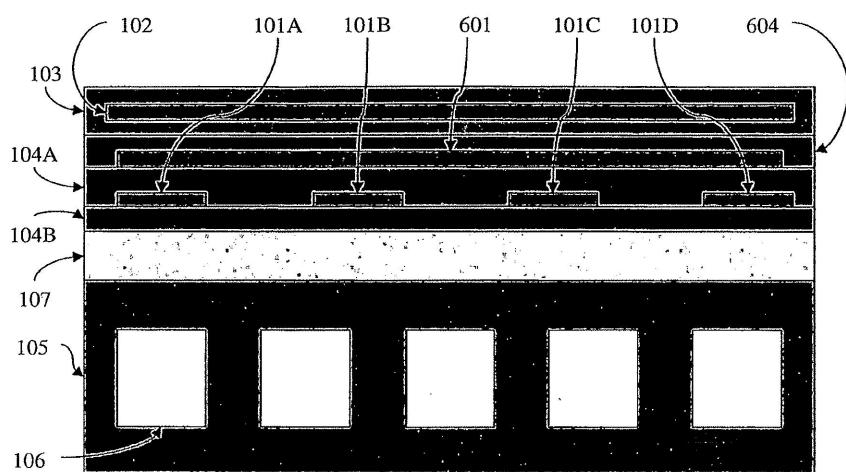

[0019] 기판 지지 어셈블리는, 하나 이상의 추가적인 히터들 (이하 프라이머리 히터들 (601) 로 지칭) 이 통합되는 추가적인 전기 절연층 (604) 을 포함할 수 있다 (도 6). 바람직하게는, 프라이머리 히터들 (601) 은 개별적으로 제어된 고전력 히터들이다. 프라이머리 히터들의 전력은 100W 와 10000W 사이이고, 바람직하게는 1000W 와 5000W 사이이다. 프라이머리 히터들은 직사각형 그리드, 동심원상의 환형 존들, 방사상 존 또는 환형 존들과 방사상 존들의 조합으로서 배열될 수도 있다. 프라이머리 히터들은 평균 온도의 변화, 방사상 온도 프로파일의 튜닝, 또는 기판 상의 단계적 온도 제어를 위해 이용될 수도 있다. 프라이머리 히터들은 가열판의 히터존들의 상방 또는 하방에 위치할 수도 있다.

[0020] 일 실시형태에서, 가열판 내의 절연층들 중 적어도 하나는 폴리머 재료의 시트이다.

[0021] 다른 실시형태에서, 가열판 내의 절연층들 중 적어도 하나는 무기 재료, 이를 테면 세라믹 또는 실리콘 산화물의 시트이다. 세라믹 척의 제조 시에 이용하기 위한 적절한 절연 및 도전성 재료의 예들은, 그 개시물이 여기에 참조로 통합되는 공동 양도된 미국 특허 제6483690호에 개시되어 있다.

[0022] 기판 지지 어셈블리는 가열판의 실시형태를 포함할 수 있으며, 여기서 가열판의 각 히터존은 기판 상의 단일의 디바이스 다이 또는 디바이스 다이들의 그룹과 유사한 사이즈이거나 또는 그보다 작아서, 기판 온도, 결과적으로는 플라즈마 애칭 프로세스가 기판으로부터의 디바이스들의 수율을 최대화하기 위해 각 디바이스 다이 위치마다 제어될 수 있다. 가열판의 스케일 가능한 아키텍처는, 냉각판 내에 최소 개수의 전력 공급 라인들, 전력 복귀 라인들, 및 퍼드스루들을 가진 다이마다의 (die-by-die) 기판 온도 제어 (통상 300mm 직경의 기판 상에는 100 개보다 많은 다이들이 존재) 를 위해 필요한 히터존들의 수를 쉽게 조정할 수 있으며, 따라서 기판 온도에 대한 외란 (disturbance), 기판 지지 어셈블리의 제작 비용 및 기판 지지 어셈블리의 복잡도를 감소시킨다. 도시하고 있지는 않지만, 기판 지지 어셈블리는, 기판을 들어올리기 위한 리프트 펀들, 헬름 백 냉각, 온도 퍼드백 신호들을 제공하기 위한 온도 센서들, 가열 전력 퍼드백 신호들을 제공하기 위한 전압 및 전류 센서들, 히터들 및/또는 클램프 전극에 대한 전력 퍼드 (power feed), 및/또는 RF 필터들과 같은 퍼처들을 포함할 수 있다.

[0023] 절연층들이 세라믹인 가열판을 제작하는 방법의 일 실시형태에서, 절연층들은 플라즈마 스프레이, 화학 기상 증착 또는 스퍼터링과 같은 기법들을 이용하여 적절한 기판 상에 세라믹을 디포짓 (deposit) 함으로써 형성될 수도 있다. 이 층은 초기 개시층일 수 있고, 또는 가열판의 절연층들 중 하나일 수 있다.

[0024] 절연층들이 세라믹인 가열판을 제작하는 방법의 일 실시형태에서, 절연층들은 시트들에 세라믹 분말, 바인더 및 액체의 혼합물을 가압하여 그 시트들 (이하 그린 시트들로 지칭) 을 건조시킴으로써 형성될 수도 있다. 그린 시트들은 두께가 약 0.3mm 일 수 있다. 비아들은 그린 시트들 내에 홀들을 편성함으로써 그린 시트들에 형성될 수도 있다. 홀들은 도전 분말의 슬러리로 채워지게 된다. 히터 엘리먼트들, 전력 공급 라인들 및 전력 복귀 라인들은, 도전 분말 (예를 들어, W, WC, 도핑된 SiC 또는 MoSi<sub>2</sub>) 의 슬러리를 스크린 인쇄함으로

써, 사전 커팅된 금속박을 가압함으로써, 도전 분말의 슬러리를 스프레이함으로써, 또는 임의의 다른 적절한 기법에 의해 형성될 수도 있다.    다이오드들과 같은 임의의 정류기들을 수용하기 위한 리세스들은 그린 시트들의 형성 프로세스 동안 가압될 수도 있고, 또는 그 형성 프로세스 후에 그린 시트들에서 커팅될 수도 있다.

별개의 컴포넌트 정류기들은 이들 리세스들에 탑재될 수도 있다.    다양한 컴포넌트들 (전력 라인들, 비아들, 정류기들 및 히터 엘리먼트들) 을 가진 다중의 그린 시트들이 그 후 전체 가열판을 형성하기 위해 얼라이닝, 가압 및 소결된다.

[0025]    절연층들이 세라믹인 가열판을 제작하는 방법의 다른 실시형태에서, 절연층들은 그린 시트들에 세라믹 분말, 바인더 및 액체의 혼합물을 가압하여 그 그린 시트들을 건조시킴으로써 형성될 수도 있다.    그린 시트들은 두께가 약 0.3mm 일 수 있다.    비아들을 수용하기 위해 그린 시트들에는 홀들이 편성된다.    다이오드들과 같은 임의의 정류기들을 수용하기 위한 리세스들은 그린 시트들의 형성 프로세스 동안 가압될 수도 있고, 또는 그 형성 프로세스 후에 그린 시트들에서 커팅될 수도 있다.    그 후, 개별 그린 시트들은 소결된다.    비아들을 수용하기 위한 소결된 시트들 내의 홀들은 도전 분말의 슬러리로 채워지게 된다.    히터 엘리먼트들, 전력 공급 라인들 및 전력 복귀 라인들은 소결된 시트들 상에, 도전 분말 (예를 들어, W, WC, 도핑된 SiC 또는 MoSi<sub>2</sub>) 의 슬러리로 스크린 인쇄될 수도 있고, 또는 임의의 다른 적절한 기법을 이용하여 형성될 수도 있다.

별개의 컴포넌트 정류기들은 소결된 시트들 내의 리세스들에 탑재될 수도 있다.    그 후, 다양한 컴포넌트들 (라인들, 비아들, 정류기들 및 히터 엘리먼트들) 을 가진 다중의 소결된 시트들이 전체 가열판을 형성하기 위해 얼라이닝되어 접착제로 본딩된다.

[0026]    절연층들이 실리콘 산화물 시트들인 일 실시형태에서, 절연층들은 증발, 스퍼터링, PVD, CVD, PECVD 등의 기법들을 이용하여 적절한 기판 상에 박막 실리콘 산화물을 디포짓시킴으로써 형성될 수도 있다.

[0027]    가열판을 제작하는 방법의 한가지 바람직한 실시형태에서, Al, Inconel<sup>®</sup> 또는 Cu 박과 같은 얇은 금속 시트 (컴포넌트층) 가 폴리이미드와 같은 제 1 폴리머 필름에 본딩 (예를 들어, 열 가압, 접착제로 접착) 된다.    패터닝된 레지스트 필름은 컴포넌트 층의 표면에 도포되며, 여기서 패턴들은 히터 엘리먼트들, 전력 공급 라인들 또는 전력 복귀 라인들과 같은 전기적 컴포넌트들의 형상 및 위치를 규정한다.    노출된 금속은 화학적으로 에칭되고, 나머지 금속 시트에는 레지스트 패턴이 유지된다.    그 후 레지스트는 적절한 용매에의 용해 또는 건식 박리에 의해 제거된다.    비아들 (비아층) 을 수용하기 위한 홀들을 가진 제 2 폴리머 필름은 제 1 폴리머 필름에 얼라이닝 및 본딩된다.    홀들의 측벽들은 금속을 그 안에 도금함으로써 코팅될 수도 있다.    임의의 적절한 수의 컴포넌트층들 및 비아층들이 직렬로 통합될 수도 있다.    마지막으로, 노출된 금속 컴포넌트들은 전기 절연을 위해 연속적인 폴리머 필름에 의해 커버된다.

[0028]    다른 실시형태에서, 히터 엘리먼트들, 전력 공급 라인들 및 전력 복귀 라인들은 절연층 또는 기판 (예를 들어, 그린 시트) 상에 디포짓 (예를 들어, 플라즈마 스프레이, 전기도금, 화학 기상 증착 또는 스퍼터링) 된 금속 필름들로 이루어진다.

[0029]    다른 실시형태에서, 히터 엘리먼트들, 전력 공급 라인들 및 전력 복귀 라인들은 절연층 또는 기판 (예를 들어, 그린 시트) 상에 디포짓 (예를 들어, 전기도금, 화학 기상 증착, 또는 스퍼터링) 된 인듐 주석 산화물과 같은 아모르페스 도전성 무기 필름의 얇은 층으로 이루어진다.

[0030]    또 다른 실시형태에서, 히터 엘리먼트들, 전력 공급 라인들 및 전력 복귀 라인들은 절연층 또는 기판 (예를 들어, 그린 시트) 상에 디포짓 (예를 들어, 화학 기상 증착, 또는 스퍼터링) 된 도전성 세라믹 필름의 얇은 층으로 이루어진다.

[0031]    일 실시형태에서, 가열판 내의 전력 공급 라인들 및 전력 복귀 라인들은 냉각판에 임베딩되지만 그 냉각판과는 전기 절연된 스프링 텁抨된 패스스루 (spring tipped passthrough) 들과 같은 터미널 커넥터들에 의해 외부 회로에 접속될 수도 있다.

[0032]    다른 실시형태에서, 가열판 내의 전력 공급 라인들 및 전력 복귀 라인들은 전력 공급 라인들 및 전력 복귀 라인들에 리드 와이어들을 부착 (납땜, 도전성 접착제로 본딩 또는 스풋 용접) 시킴으로써, 그리고 이들 리드 와이어들을 냉각판 내의 홀들 또는 도관들을 통하여 관통 (thread) 시킴으로써 외부 회로에 접속될 수도 있다.

[0033]    플라즈마 프로세싱 시스템에서, 플라즈마 프로세싱 챔버 내에 인가된 RF 전력은 보통 100W 보다 높고, 때로는 1000W 보다 높다.    RF 전압의 진폭은 킬로볼트를 초과할 수 있다.    이렇게 강한 RF 전력은 적절한 여과 또는 격리 없이 히터존들의 제어 및 전력 회로의 동작에 쉽게 영향을 미칠 수 있다.    RF 전력을 제어 및 전

력 회로로부터 멀리 이동시키기 위해 RF 필터가 이용될 수 있다. RF 필터는 플라즈마 프로세싱 시스템에 이용되는 특정 RF 주파수들을 위한 튜닝된 필터 또는 단순 광대역 필터일 수도 있다. 반면에, RF 아이솔레이터는, 임의의 RF 커플링된 컴포넌트들과 제어 및 전력 회로 사이의 직접 전기 접속을 제거한다. RF 아이솔레이터는 광 커플러 또는 변압기일 수도 있다.

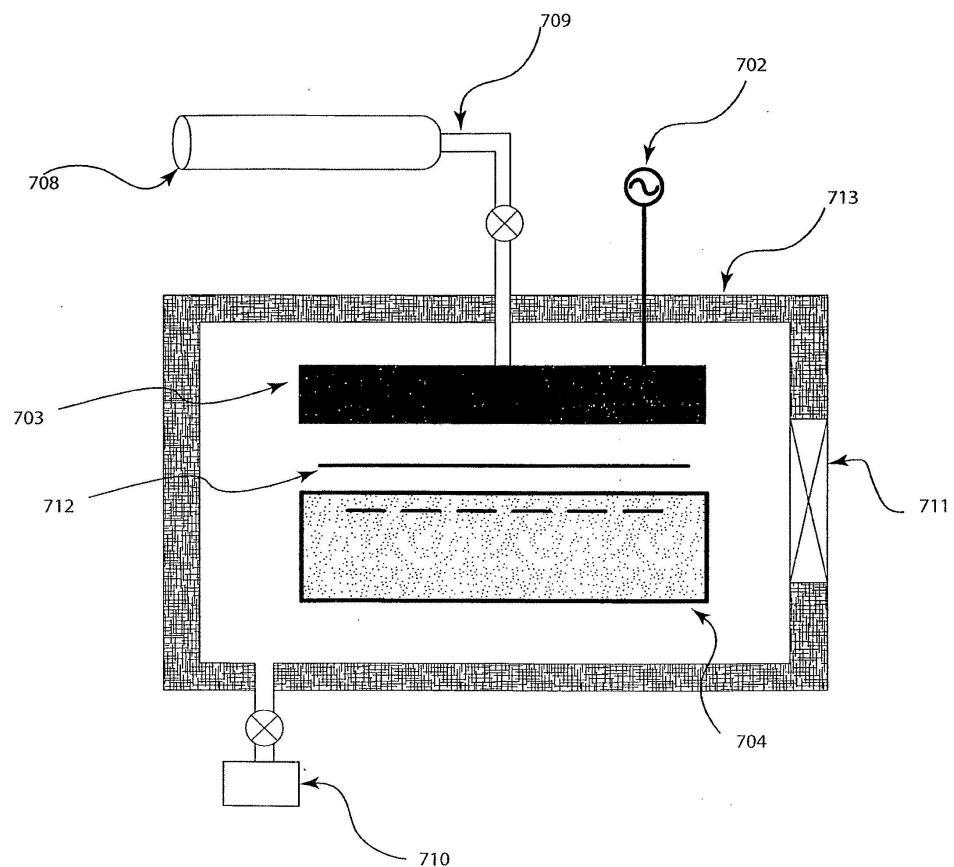

[0034] 플라즈마 프로세싱 챔버가 동작하는 방법의 개관으로서, 도 7a 는, 상부 샤큐헤드 전극 (703) 및 기판 지지 어셈블리 (704) 가 배치되는 챔버 (713) 를 포함하는 플라즈마 프로세싱 챔버의 개략도를 도시한다. 기판 지지 어셈블리 (704) 로는 로딩 포트 (711) 를 통하여 기판 (712) 이 로드된다. 챔버로 프로세스 가스를 전달하는 가스 라인 (709) 이 상부 샤큐헤드 전극 (703) 에 프로세스 가스를 공급한다. 가스 라인 (709) 에는 가스 소스 (708) (예를 들어, 적절한 가스 혼합물에 전력 공급하는 질량 유량 제어기) 가 접속된다. 상부 샤큐헤드 전극 (703) 에는 RF 전력 소스 (702) 가 접속된다. 동작 시에, 챔버는 진공 펌프 (710) 에 의해 배기되고, RF 전력은, 상부 샤큐헤드 전극 (703) 과 기판 지지 어셈블리 (704) 내의 하부 전극 사이에 용량적으로 커플링되어 기판 (712) 과 상부 샤큐헤드 전극 (703) 사이의 공간에서 프로세스 가스를 플라즈마로 에너자이징한다. 플라즈마는 기판 (712) 상의 충돌에 디바이스 다이 피처들을 에칭하는데 이용될 수 있다. 기판 지지 어셈블리 (704) 에는 히터들이 통합되어 있을 수도 있다. 플라즈마 프로세싱 챔버의 세부 설계는 변할 수도 있지만, RF 전력이 기판 지지 어셈블리 (704) 를 통하여 커플링된다는 것을 알아야 한다.

[0035] 도 7b 는 RF 여과 또는 격리의 실시형태의 개략도를 도시하며, 여기서 히터존, 전력 공급 및 전력 복귀 라인들 상에는 어떠한 필터들 또는 아이솔레이터들도 접속되지 않으며, 전기적 그라운드 (701) 에 접속되는 제어 및 전력 회로 (705) 가 필터 또는 아이솔레이터 (706B) 에 접속된다. 기판 지지 어셈블리에 존재한다면, 프라이머리 히터들 (미도시) 은, 그들의 높은 전력으로 인해 별개의 필터들 또는 아이솔레이터들을 갖는 것이 바람직하다. 이 접근법에서, 제어 및 전력 회로 (705) 는 RF 전위 또는 "상측 (high side)" 에서 플로팅한다. 이 접근법은 다중의 히터존들이 단 하나의 필터 또는 아이솔레이터를 공유하는 것을 허용한다.

[0036] 모든 상측 회로는 기판 지지 어셈블리 베이스 구조물 바로 아래에 로컬 플로팅 패러데이 상자 (Faraday cage) 내부에 하우징될 수도 있다.

[0037] 대안으로는, 절연 변압기 (isolation transformer) 가 전력 및 제어 회로 (705) 를 RF로부터 격리시키기 위해 단일의 필터 또는 아이솔레이터 (706B) 로서 이용된다. 히터존들의 제어 및 전력 회로 (705) 은, 변압기가 DC 및 저주파수 송신을 강하게 감쇠시키기 때문에 비교적 높은 주파수 (25KHz 내지 250KHz) 에서 동작하는 것이 가능해야 한다. 제어 및 전력 회로는 단일의 플로팅 전위 (플로팅 그라운드) 에 래퍼런싱된다. 이것은, 이 절연 변압기에 접속된 제어 및 전력 회로가 매우 유사한 RF 노출의 대상이 되어야 하는 것을 요구한다. RF 전위가 제어 및 전력 회로들의 2 개의 그룹들 간에 실질적으로 다르다면, 상당한 RF 전류가 이들 그룹들 사이에서 흐른다. 이 시나리오에서, 각 그룹은 그 자신의 필터 또는 아이솔레이터를 가져야 하며, 또는 이들 그룹들 사이에는 일 필터 또는 아이솔레이터가 있어야 한다.

[0038] 필터 또는 아이솔레이터 (706B) 는 플라즈마 프로세싱 챔버 또는 임의의 다른 적절한 장소에 물리적으로 위치할 수도 있다.

[0039] 히터 제어 전자장치의 일 실시형태가 도 8 에 도시된다. 하측 제어기 (809) 는 마이크로제어기 유닛 (MCU) 또는 컴퓨터 (PC) 와 같은 상위 레벨 디바이스일 수도 있다. 광 커플러 (807) 를 통하여, 하측 제어기는 히터존들 (801), 센서들 (803), 및 임의의 보조 회로들 (802) 과 상호작용하는 상측 MCU (805) 에 디지털적으로 통신한다. 상측 MCU (805) 가 충분한 용량 (capability) 및 로컬 메모리를 갖는다면, 임의의 세트-포인트 및 프로그램은 각 실행 전에 상측 MCU (805) 로 사전 로드될 수도 있으며, 따라서 하측 제어기 (809) 에 대한 실시간 링크의 필요성을 제거한다. 804 는 모듈들 간의 일방향 통신 링크들을 나타낸다. 806 은 모듈들 간의 양방향 통신 링크들을 나타낸다.

[0040] 시간-도메인 멀티플렉싱 스킴들의 일 실시형태에서, 상측 MCU 는 각 히터존 전력 공급 라인에 전력을 순차적으로 공급한다. 단 하나의 전력 공급 라인은 동시에 전력 공급장치에 접속된다. 하나의 전력 공급 라인이 전력공급되는 시간 동안, 상측 MCU 는 이 지속기간의 일부 동안 임의의 또는 모든 전력 복귀 라인들을 플로팅 래퍼런스에 계속 접속되게 할 수도 있다. 히터존은, 이 히터존에 접속된 전력 공급 라인들 중 적어도 하나가 전력 공급장치에 접속되고, 이 히터존에 접속된 전력 복귀 라인들 중 적어도 하나가 플로팅 래퍼런스에 접속될 때 턴 온된다. 히터존의 평균 전력은 그 히터존이 턴 온되는 평균 지속기간에 정비례한다. 대안으로는, 하나의 전력 공급 라인이 전력공급되는 시간 동안, 상측 MCU 는 이 전체 지속기간 동안 임의의 또는 모든 전력 복귀 라인들을 플로팅 래퍼런스에 계속 접속되게 하고, 턴 온되는 각 히터존에 송신된 전력을 조절할 수도

있다.

[0041] 예를 들어,  $10 \times 10$  그리드의 히터존들의 경우, 로우 (row) 넘버 N 의 히터존들은 전력 공급 라인 넘버 N 에 접속되고; 컬럼 (column) 넘버 M 의 히터존들은 전력 복귀 라인 넘버 M 에 접속된다. 상측 MCU 는, 전력 공급 라인들 각각이 순차적으로, 100ms 동안 전력 공급장치에 접속되도록 가열을 제어할 수도 있다. 예를 들어, 전력 공급 라인 넘버 3 이 전력 공급장치에 접속되는 100ms 시간 동안, MCU 는, 이 100ms 동안 특정 가열 요건에 의해 지시한 바와 같이, 전력 복귀 라인들 넘버 7, 8, 및 9 를 각각 10, 50 및 100ms 동안 플로팅 레퍼런스에 접속시키도록 동작가능하다. 따라서, 로우 넘버 3 및 컬럼 넘버 7 의 히터존은 1% 의 드uty 사이클을 갖고; 로우 넘버 3 및 컬럼 넘버 8 의 히터존은 5% 의 드uty 사이클을 가지며; 로우 넘버 3 및 컬럼 넘버 9 의 히터존은 10% 의 드uty 사이클을 갖는다. 이 특정 예에서, 각 히터존에 대한 최대 피크 전력은 원하는 평균 최대 전력의 10 배로 설정될 것이다.

[0042] 검출가능한 온도 변조를 방지하기 위하여, 각 히터존이 자주 (적어도 1Hz) 어드레싱되는, 스위칭 주파수들 및 전체 멀티플렉싱 스킴은 충분히 고속인 것이 바람직하다. 더 많은 온도 센서들 중 하나로부터의 피드백 데이터를 이용하여 추가적인 루프 제어가 구현될 수도 있다. 원한다면 전압 및 전류 센서들이 또한 구현될 수 있다. 이들 센서들은 기판 상의 상이한 장소의 온도 및 히터존들의 전력과 같은 파라미터들을 측정하도록 구성될 수 있다. 이들 측정된 파라미터들은 이들 파라미터들의 설정된 목표들과 비교되도록 제어 및 전력 회로로 전송되어, 제어 및 전력 회로가 측정된 파라미터들과 그들의 설정된 목표들 간의 차이를 최소화하기 위하여 히터존들에 전달되는 전력을 그에 따라 조정할 수 있다.

[0043] 가열판, 그 가열판을 제작하는 방법, 가열판을 포함하는 기판 지지 어셈블리, 및 기판 지지 어셈블리를 포함하는 플라즈마 프로세싱 챔버를 이용하는 방법이 이들의 특정 실시형태들을 참조하여 상세하게 설명되었지만, 일부된 특허청구항의 범위로부터 벗어남 없이, 다양한 변화 및 변경이 행해질 수 있으며, 등가물들이 사용될 수 있다는 것이 당업자에게 명백할 것이다. 예를 들어, 기판 지지 어셈블리는 기판 온도를 모니터링하기 위한 온도 센서들, 원하는 클램핑 전압으로 ESC 에 전력공급하기 위한 전력 피드 배열, 기판을 상승 및 하강시키기 위한 리프팅 펀 배열, 헬륨과 같은 가스를 기판의 밑면에 공급하기 위한 열 전달 가스 피드 배열, 열 전달 액체를 냉각판에 공급하기 위한 온도 제어된 액체 피드 배열, 평탄한 히터존들의 상방 또는 하방의 프라이머리 히터들에 개별적으로 전력공급하기 위한 전력 피드 배열, 기판 지지 어셈블리에 통합된 하부 전극에 하나 이상의 주파수들에서 RF 전력을 공급하기 위한 전력 피드 배열 등을 포함할 수 있다.

## 도면

### 도면1

도면2

도면3a

도면3b

도면3c

도면4a

도면4b

도면5a

도면5b

도면5c

도면5d

도면5e

도면6

도면7a

도면7b

## 도면8