(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5352912号

(P5352912)

(45) 発行日 平成25年11月27日(2013.11.27)

(24) 登録日 平成25年9月6日(2013.9.6)

|                         |                      |

|-------------------------|----------------------|

| (51) Int.Cl.            | F 1                  |

| HO 1 L 29/786 (2006.01) | HO 1 L 29/78 6 1 6 U |

| GO 2 F 1/1368 (2006.01) | GO 2 F 1/1368        |

| HO 1 L 29/417 (2006.01) | HO 1 L 29/50 M       |

| HO 1 L 21/336 (2006.01) | HO 1 L 29/78 6 1 6 V |

|                         | HO 1 L 29/78 6 2 7 B |

請求項の数 7 (全 22 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2006-294638 (P2006-294638)  |

| (22) 出願日     | 平成18年10月30日 (2006.10.30)      |

| (65) 公開番号    | 特開2007-123906 (P2007-123906A) |

| (43) 公開日     | 平成19年5月17日 (2007.5.17)        |

| 審査請求日        | 平成21年9月25日 (2009.9.25)        |

| (31) 優先権主張番号 | 10-2005-0102429               |

| (32) 優先日     | 平成17年10月28日 (2005.10.28)      |

| (33) 優先権主張国  | 韓国 (KR)                       |

|           |                                                                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 512187343<br>三星ディスプレイ株式會社<br>Samsung Display Co., Ltd.<br>大韓民国京畿道龍仁市器興区三星二路95<br>95, Samsung 2 Ro, Gih<br>eung-Gu, Yongin-City<br>, Gyeonggi-Do, Korea |

| (74) 代理人  | 110000051<br>特許業務法人共生国際特許事務所                                                                                                                           |

| (72) 発明者  | 金秉濬<br>大韓民国 京畿道 城南市 盆唐区 書ヒ<br>ヨン洞 示範団地韓新アパート 112棟<br>1503号                                                                                             |

最終頁に続く

(54) 【発明の名称】 液晶表示装置とその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ベース基板と、

前記ベース基板上に形成されたゲート電極と、

前記ゲート電極をカバーするように前記ゲート電極の上部に形成されたアクティブ層と

、

前記アクティブ層の上部に所定の間隔で離隔されて形成されたソース電極及びドレイン電極と、

前記アクティブ層と前記ソース電極との間、及び前記アクティブ層と前記ドレイン電極との間にそれぞれ形成され、前記アクティブ層に連続して形成され、前記アクティブ層の酸化を減少させるためのバッファ層とを有し、

前記バッファ層は、複数の層で構成され、前記アクティブ層を構成する第1物質と結合して化合物を形成することができる第2物質を含み、

前記第2物質は、前記バッファ層の厚さによって実質的に連続的に変動する含有量比を有し、

前記バッファ層は、第1連結層、第2連結層、及び第3連結層を含み、

前記第1連結層は前記第1物質及び前記第2物質の化合物からなり、前記第2連結層は前記第2物質からなり、前記第3連結層は前記第2物質及び第3物質の化合物からなることを特徴とする液晶表示装置。

## 【請求項 2】

10

20

前記第1連結層の厚さが増加するほど、前記第1物質の含有量は実質的に減少し、前記第2物質の含有量は実質的に連続的に増加し、

前記第3連結層の厚さが増加するほど、前記第2物質の含有量は実質的に連続的に減少し、前記第3物質の含有量は実質的に連続的に増加することを特徴とする請求項1記載の液晶表示装置。

**【請求項3】**

前記第1物質は、シリコン(Si)であることを特徴とする請求項2記載の液晶表示装置。

**【請求項4】**

前記第2物質は、チタン(Ti)、モリブデン(Mo)、及びニッケル(Ni)のうちの、いずれか一種であることを特徴とする請求項2記載の液晶表示装置。 10

**【請求項5】**

前記第3物質は、窒素(N)であることを特徴とする請求項2記載の液晶表示装置。

**【請求項6】**

前記第1連結層の厚さは50ないし150の範囲を有し、前記第2連結層の厚さは100ないし500の範囲を有し、前記第3連結層の厚さは100ないし500の範囲を有することを特徴とする請求項1記載の液晶表示装置。

**【請求項7】**

ベース基板上にゲート電極を形成する段階と、

前記ゲート電極をカバーするように前記ベース基板上にゲート絶縁層を形成する段階と、 20

前記ゲート電極をカバーするように前記ゲート絶縁層上にアクティブ層を形成する段階と、

前記アクティブ層上に前記アクティブ層の酸化を減少させるためバッファ層を前記アクティブ層に連続して形成する段階と、

前記バッファ層の第1部分及び前記アクティブ層の第1部分を第1次にエッティングする段階と、

前記第1次にエッティングされたアクティブ層上に所定の間隔で離隔されるようにソース電極及びドレイン電極を形成する段階と、

前記ソース電極及び前記ドレイン電極をマスクとして用い、前記第1次にエッティングされたバッファ層の第2部分及び前記第1次にエッティングされたアクティブ層の第2部分を第2次にエッティングする段階と、を有し、 30

前記バッファ層は、複数の層で構成され、前記アクティブ層を構成する第1物質と結合して化合物を形成することができる第2物質を含み、

前記第2物質は、前記バッファ層の厚さによって実質的に連続的に変動する含有量比を有し、

前記バッファ層は、第1連結層、第2連結層、及び第3連結層を含み、

前記第1連結層は前記第1物質及び前記第2物質の化合物からなり、前記第2連結層は前記第2物質からなり、前記第3連結層は前記第2物質及び第3物質の化合物からなることを特徴とする液晶表示装置の製造方法。 40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、液晶表示装置とその製造方法に関し、より詳細には電気的な特性を向上させた液晶表示装置とその製造方法に関する。

**【背景技術】**

**【0002】**

一般的に、平面表示装置には、液晶表示装置(Liquid Crystal Display)、プラズマ表示パネル(Plasma Display Panel)、フィ 50

ールド放射表示装置 (Field Emission Display)、及び電界発光表示装置 (Electro Luminescence Display) などがある。このような平面表示装置のうち、液晶表示装置及び電界発光表示装置は薄い薄膜で形成された複数の薄膜トランジスタを具備する。

【0003】

液晶表示装置及び電界発光表示装置に採用される薄膜トランジスタは、一般的に透明基板上に形成され、ゲート電極、ソース電極、ドレイン電極、半導体層、及び不純物層を含む。

【0004】

ゲート電極は、透明基板上に形成され、ソース電極及びドレイン電極は、ゲート電極の上部に互いに離隔されて形成される。半導体層は、ゲート電極とソース電極及びドレイン電極との間に形成され、不純物層は、半導体層とソース電極及びドレイン電極との間にそれぞれ形成される。ここで、半導体層は、アモルファスシリコンであり、不純物層は高密度イオンドーピングアモルファスシリコンである。

10

【0005】

薄膜トランジスタを製造する方法を簡単に説明すると、ゲート電極を透明基板上に形成し、半導体層及び不純物層をゲート電極の上部に形成する。その後、ソース電極及びドレイン電極を不純物層上に互いに離隔されるように形成する。ここで、不純物層が形成された後、ソース電極及びドレイン電極が形成される前に若干のブランクタイムが一般的に存在する。

20

【0006】

しかし、不純物層が形成された後、ソース電極及びドレイン電極が形成される前に若干のブランクタイムが発生する場合、不純物層の上面には自然酸化が起こる可能性がある。このような不純物層上に形成された自然酸化層は不純物層及びソース電極とドレイン電極との接触抵抗を増加させる。接触抵抗の増加は薄膜トランジスタの電気的な特性を低下させるという問題点がある。

【発明の開示】

【発明が解決しようとする課題】

【0007】

そこで、本発明は、上記従来の薄膜トランジスタとその製造における問題点に鑑みてなされたものであって、本発明の目的は、自然酸化を防止して電気的な特性を向上させた薄膜トランジスタを具備する液晶表示装置を提供することにある。

30

また、本発明の他の目的は、前記液晶表示装置を製造する方法を提供することにある。

【課題を解決するための手段】

【0008】

上記目的を達成するためになされた本発明の一特徴による薄膜トランジスタ基板は、ベース基板と、前記ベース基板上に形成されたゲート電極と、前記ゲート電極をカバーするように前記ゲート電極の上部に形成されたアクティブ層と、前記アクティブ層の上部に所定の間隔で離隔されて形成されたソース電極及びドレイン電極と、前記アクティブ層と前記ソース電極との間、及び前記アクティブ層と前記ドレイン電極との間にそれぞれ形成され、前記アクティブ層に連続して形成され、前記アクティブ層の酸化を減少させるためのバッファ層とを有し、前記バッファ層は、複数の層で構成され、前記アクティブ層を構成する第1物質と結合して化合物を形成することができる第2物質を含み、

40

前記第2物質は、前記バッファ層の厚さによって実質的に連続的に変動する含有量比を有し、

前記バッファ層は、第1連結層、第2連結層、及び第3連結層を含み、

前記第1連結層は前記第1物質及び前記第2物質の化合物からなり、前記第2連結層は前記第2物質からなり、前記第3連結層は前記第2物質及び第3物質の化合物からなる。

【0010】

50

上記他の目的を達成するためになされた本発明の一特徴による液晶表示装置の製造方法は、ベース基板上にゲート電極を形成する段階と、前記ゲート電極をカバーするように前記ベース基板上にゲート絶縁層を形成する段階と、前記ゲート電極をカバーするように前記ゲート絶縁層上にアクティブ層を形成する段階と、前記アクティブ層上に前記アクティブ層の酸化を減少させるためのバッファ層を前記アクティブ層に連続して形成する段階と、前記バッファ層の第1部分及び前記アクティブ層の第1部分を第1次にエッチングする段階と、前記第1次にエッチングされたアクティブ層上に所定の間隔で離隔されるようソース電極及びドレイン電極を形成する段階と、前記ソース電極及び前記ドレイン電極をマスクとして用い、前記第1次にエッチングされたバッファ層の第2部分及び前記第1次にエッチングされたアクティブ層の第2部分を第2次にエッチングする段階と、を有し、

前記バッファ層は、複数の層で構成され、前記アクティブ層を構成する第1物質と結合して化合物を形成することができる第2物質を含み、

前記第2物質は、前記バッファ層の厚さによって実質的に連続的に変動する含有量比を有し、

前記バッファ層は、第1連結層、第2連結層、及び第3連結層を含み、

前記第1連結層は前記第1物質及び前記第2物質の化合物からなり、前記第2連結層は前記第2物質からなり、前記第3連結層は前記第2物質及び第3物質の化合物からなる。

#### 【発明の効果】

#### 【0016】

このような本発明の液晶表示装置とその製造方法によれば、ソース電極とドレイン電極及びアクティブ層の間にバッファ層が形成されることによって、酸化による接触抵抗が増加することを防止することができる。このように、接触抵抗が増加することを防止することで、薄膜トランジスタの電気的な特性を向上させることができ、その結果、液晶表示パネルまたは電界発光表示パネルまたは電界発光表示パネルの表示品質をより向上させることができる。特に、本発明は、電流駆動方式によって画像を表示する電界発光表示パネルにおいて、より効果的である。

また、多種の反応気体の含有量の比率を連続的に変化させてチャンバの内部に流入させることによって、バッファ層は厚さが増加するほど連続的に徐々に変動する物質の含有量比を有することができ、その結果、バッファ層の含有量の比率が急激に変動することによるストレスの発生を防止することができる。

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、本発明の液晶表示装置とその製造方法を実施するための最良の形態の具体例を、添付した図面を参照しながらより詳細に説明する。

#### <液晶表示パネルの実施例>

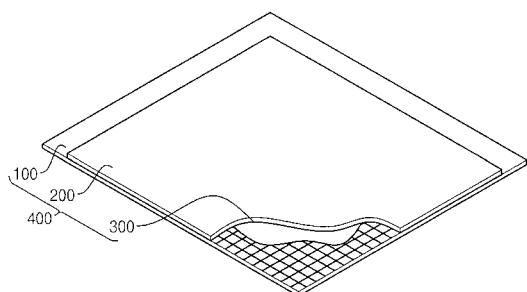

図1は、本発明の一実施例による液晶表示パネルを示す斜視図である。

図1に示すように、本発明の液晶表示パネル400は、第1基板100、第2基板200、及び液晶層300を含み、光を用いて画像を外部に表示する。

#### 【0018】

第1基板100は、マトリクス形態で形成された複数の画素電極(pixel electrode)、各画素電極に駆動電圧を印加する薄膜トランジスタ(Thin Film Transistor)、薄膜トランジスタをそれぞれ作動させるための信号線(signal line)を含む。

#### 【0019】

第2基板200は、第1基板100と向い合うように配置される。第2基板200は、第1基板100の前面に配置され、透明かつ導電性である共通電極(common electrode)、及び画素電極と向い合う位置に配置されたカラーフィルタ基板(color filter)を含む。

#### 【0020】

10

20

30

40

50

一般的に、カラーフィルタには白色光が入射され、各カラーフィルタは対応する光のみを透過させる。例えば、カラーフィルタ基板は、赤色光を選択的に通過させる赤色カラーフィルタ基板、緑色光を選択的に通過させる緑色カラーフィルタ、及び青色光を選択的に通過させる青色カラーフィルタを含む。

#### 【0021】

液晶層300は、第1基板100と第2基板200との間に介在し、画素電極と共に通電極との間に形成された電場によって再配列される。再配列された液晶層300は、外部から印加された光の光透過率を調節し、光透過率が調節された光は、カラーフィルタを通過することで画像が表示される。

#### 【0022】

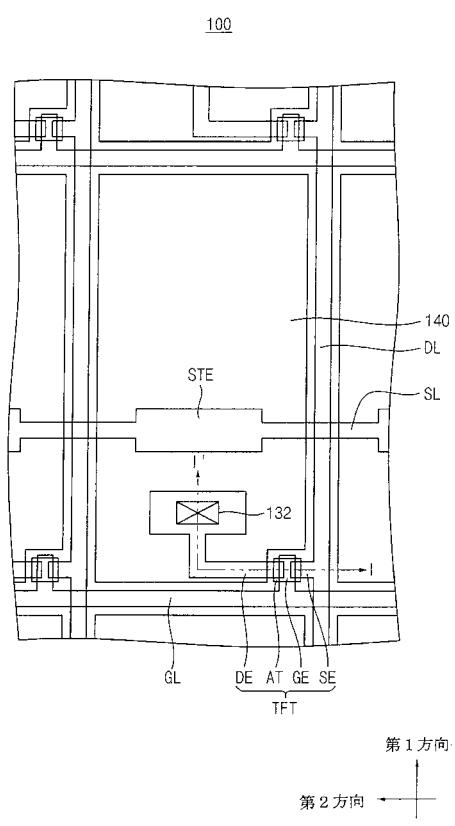

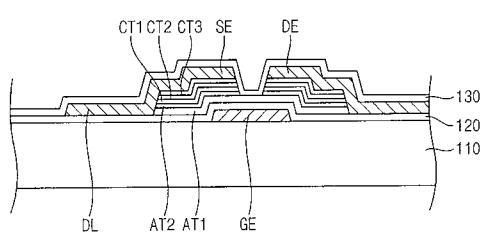

図2は、図1の表示パネルのうち、第1基板の単位画素を概念的に示した平面図であり、図3は、図2のI-I'に沿って見た断面図である。

図2及び図3に示すように、本実施例による第1基板100は、データ配線(DL)、ゲート配線(GL)、画素電極140、薄膜トランジスタ(TFT)、及びストレージ配線(SL)を含む。

#### 【0023】

データ配線(DL)は、第1方向に長く延長されて形成され、第2方向に沿って複数個が並列に形成される。データ配線(DL)は、薄膜トランジスタ(TFT)と電気的に連結されてデータ信号を印加する。

#### 【0024】

ゲート配線(GL)は、データ配線(DL)と交差するように第2方向に長く延長されて形成され、第1方向に沿って複数個が並列に形成される。ここで、第1方向は一例として、第2方向と互いに直角をなしている。ここで、データ配線(DL)及びゲート配線(GL)が互いに交差するように形成されることによって、複数の単位画素が定義される。単位画素それぞれには画素電極140及び薄膜トランジスタ(TFT)が形成される。

#### 【0025】

画素電極140は、単位画素内に形成され、透明かつ導電性物質からなる。画素電極140は、薄膜トランジスタ(TFT)とコンタクトホール132によって電気的に連結され、薄膜トランジスタ(TFT)から駆動電圧が印加されて充電される。

#### 【0026】

画素電極140は、一例としてインジウムスズ酸化薄膜(Indium Tin Oxide film、ITO)、インジウム亜鉛酸化薄膜(Indium Zinc Oxide film、IZO)、アモルファスインジウムスズ酸化薄膜(amorphous Indium Tin Oxide film、a-ITO)などをフォトリソグラフィ工程によってパターニングされて形成される。

#### 【0027】

薄膜トランジスタ(TFT)は、ゲート電極(GE)、ソース電極(SE)、ドレイン電極(DE)、アクティブ層(AT)、及びバッファ層(図示せず)を含む。

ゲート電極(GE)は、ゲート配線(GL)から第1方向に延長されて形成される。ソース電極(SE)は、データ配線(DL)から第2方向に延長されて、ゲート電極(GE)の一部と重なるように形成される。ドレイン電極(DE)は、ソース電極(SE)と向い合うようにソース電極(SE)から所定距離で離隔されて形成され、ゲート電極(GE)の一部と重なるように形成される。ドレイン電極は、一例として、第1方向及び第2方向に長く延長されて形成され、コンタクトホール132を通じて画素電極140と電気的に連結される。

#### 【0028】

アクティブ層(AT)は、ゲート電極(GE)とソース電極(SE)及びドレイン電極(DE)との間に形成され、ゲート電極(GE)をカバーするように形成される。バッファ層は、アクティブ層(AT)とソース電極(SE)との間、及びアクティブ層(AT)とドレイン電極(DE)との間に形成される。バッファ層は、アクティブ層(AT)とソ

10

20

30

40

50

ース電極( S E )との間、及びアクティブ層( A T )とドレイン電極( D E )との間の接触抵抗が増加することを防止する。

#### 【 0 0 2 9 】

ストレージ配線( S L )は、画素電極 1 4 0 の下部にゲート配線( G L )と平行に形成され、単位画素内に形成されたストレージ電極( S T E )を含む。ストレージ配線( S L )には、外部からグラウンド電圧を印加する。ストレージ電極( S T E )は、画素電極 1 4 0 と所定距離で離隔されて形成されることによって、ストレージキャパシタを形成する。ストレージキャパシタは画素電極 1 4 0 に充電された駆動電圧を維持する。

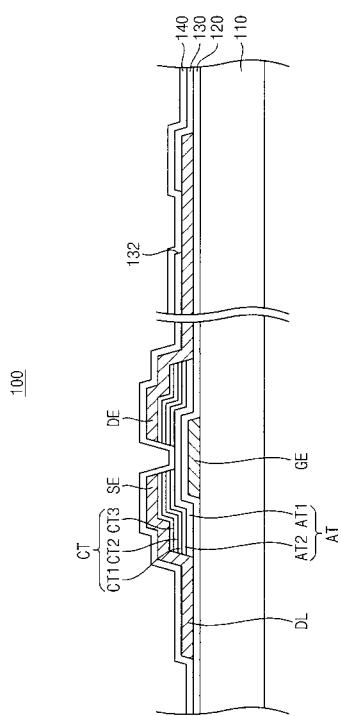

#### 【 0 0 3 0 】

図 2 及び図 3 に示すように、本実施例による第 1 基板 1 0 0 は、透明基板 1 1 0 、ゲート配線( G L )、ストレージ配線( S L )、ゲート絶縁層 1 2 0 、データ配線( D L )、薄膜トランジスタ( T F T )、パッシベーション層 1 3 0 、画素電極 1 4 0 を含む。ここで、薄膜トランジスタ( T F T )は、ゲート電極( G E )、ソース電極( S E )、ドレイン電極( D E )、アクティブ層( A T )、及びバッファ層( C T )を含む。

#### 【 0 0 3 1 】

透明基板 1 1 0 は、プレート形状を有し、透明な物質からなる。透明基板 1 1 0 は、例えば、ガラス、石英、サファイア、またはポリエスチル、ポリアクリレート、ポリカーボネート、ポリエーテルケトンなどの透明な合成樹脂からなる。

#### 【 0 0 3 2 】

ゲート配線( G L )は、第 2 方向に透明基板 1 1 0 上に形成され、ストレージ配線( S L )もゲート配線( G L )と同一の方向に透明基板 1 1 0 上に形成される。ゲート電極( G E )は、ゲート配線( G L )から第 1 方向に延長されて形成される。

#### 【 0 0 3 3 】

ゲート絶縁層 1 2 0 は、ゲート配線( G L )、ゲート電極( G E )、及びストレージ配線( S L )をカバーするように透明基板 1 1 0 上に形成される。ゲート絶縁層 1 2 0 は、一例として、酸化シリコンまたは窒化シリコンなどの透明な絶縁性物質からなる。

#### 【 0 0 3 4 】

データ配線( D L )は、第 1 方向に延長されてゲート絶縁層 1 2 0 上に形成される。ソース電極( S E )は、データ配線( D L )から第 2 方向に延長されて形成される。

アクティブ層( A T )は、ゲート電極( G E )を貫通するようゲート絶縁層 1 2 0 上に形成される。アクティブ層( A T )は、半導体層( A T 1 )及び不純物層( A T 2 )を含む。

#### 【 0 0 3 5 】

半導体層( A T 1 )は、ゲート電極( G E )を貫通するようゲート絶縁層 1 2 0 上に形成され、一例として、アモルファスシリコン( a - S i )である。不純物層( A T 2 )は半導体層( A T 1 )上に形成され、一例として、高密度イオンドーピングアモルファスシリコン( n + a - S i )である。ここで、不純物層( A T 2 )は、中間部位が除去されて 2 部分に分離される。

#### 【 0 0 3 6 】

バッファ層( C T )は、2 部分に分離された不純物層( A T 2 )上にそれぞれ一対に形成される。一対のバッファ層( C T )それぞれは、第 1 連結層( C T 1 )、第 2 連結層( C T 2 )、及び第 3 連結層( C T 3 )を含む。

#### 【 0 0 3 7 】

第 1 連結層( C T 1 )は、不純物層( A T 2 )上に形成され、一例としてシリコンチタン( T i S i )、シリコンモリブデン( M o S i <sub>2</sub> )、及びシリコンニッケル( N i S i <sub>3</sub> )で構成される。第 1 連結層( C T 1 )の厚さは、5 0 ~ 1 5 0 の範囲を有し、約 1 0 0 を有することが望ましい。

#### 【 0 0 3 8 】

第 2 連結層( C T 2 )は、第 1 連結層( C T 1 )上に形成され、一例として、チタン( T i )、モリブデン( M o )、及びニッケル( N i )からなる。第 2 連結層( C T 2 )の

厚さは 100 ~ 500 の範囲を有し、約 200 を有することが望ましい。

#### 【0039】

第 3 連結層 (C T 3) は、第 2 連結層 (C T 2) 上に形成され、一例として、窒化チタン (T i N)、窒化モリブデン (M o N)、及び窒化ニッケル (N i N) からなる。第 3 連結層 (C T 3) の厚さは 100 ~ 500 の範囲を有し、最小値である 100 を有することが望ましい。

#### 【0040】

ソース電極 (S E) はデータ配線 (D L) から延長されて第 3 連結層 (C T 3) のうち、一つの上面に形成される。ドレイン電極 (D E) は、ソース電極 (S E) から所定距離で離隔され、第 3 連結層 (C T 3) のうちの、他の上面に形成される。ドレイン電極 (D E) は、長く延長されてゲート絶縁層 120 上に形成される。ソース電極 (S E) 及びドレイン電極 (D E) は、例えば、モリブデン (M o)、銅 (C u)、銀 (A g)、アルミニウム (A l)、クロム (C r)、タンタル (T a)、及びチタン (T i) などの金属からなり、アルミニウム (A l) 及びモリブデン (M o) の二重層で構成されることが望ましい。

10

#### 【0041】

パッシベーション層 130 は、薄膜トランジスタ (T F T) をカバーするようにゲート絶縁層 120 上に形成され、薄膜トランジスタ (T F T) を外部の熱や湿気から保護する。パッシベーション層 130 は、ドレイン電極 (D E) 上に形成されたコンタクトホール 132 を含む。パッシベーション層 130 は、一例として、透明な酸化シリコン (S i O<sub>2</sub>) からなる。

20

#### 【0042】

画素電極 140 は、パッシベーション層 130 の上部に形成され、パッシベーション層 130 のコンタクトホール 132 によってドレイン電極 (D E) と電気的に連結される。

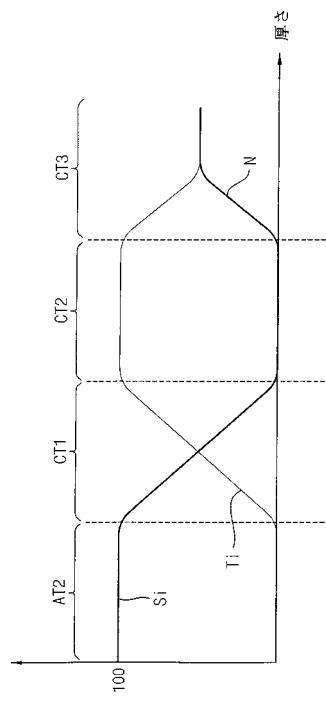

図 4 は、図 3 のバッファ層において、厚さが増加することによる物質の含有量比を示すグラフである。

#### 【0043】

図 4 を参照すると、第 1 連結層 (C T 1) から第 3 連結層 (C T 3) まで厚さが徐々に増加することにより物質の含有量比が連続的に変動する。例えば、第 1 連結層 (C T 1) はシリコンチタン (T i S i) からなり、第 2 連結層 (C T 2) はチタン (T i) からなり、第 3 連結層 (連結層 3) は窒化チタン (T i N) からなる。

30

#### 【0044】

より具体的に説明すると、第 1 連結層 (C T 1) は厚さが増加するほどチタン (T i) の含有量が連続的に増加し、それに対応してシリコン (S i) の含有量が徐々に減少する。シリコン (S i) の含有量が完全に除去されると、第 2 連結層 (C T 2) が形成される。ここで、図 4 に示した不純物層 (A T 2) は、シリコン (S i) の含有量比が 100 % であることと示したが、これと違ってリン (P)、砒素 (A s)、アンチモン (S b) などの 5 族元素が不純物として含有されることもある。

#### 【0045】

第 2 連結層 (C T 2) は、チタン (T i) のみからなり、所定の厚さを有する。第 2 連結層 (C T 2) の厚さがある程度増加した後窒素 (N) の含有量が発生すると、第 3 連結層 (C T 3) が形成される。

40

#### 【0046】

第 3 連結層 (C T 3) は、厚さが増加しつつ窒素 (N) の含有量は連続的に増加し、それに対応してチタン (T i) の含有量が徐々に減少する。ここで、チタン (T i) の含有量は窒素 (N) の含有量とほぼ同一になるまで減少し、その後は窒素 (N) の含有量と同一になるように維持されることが望ましい。これと違って、第 3 連結層 (C T 3) は、厚さが増加するほど窒素 (N) の含有量が継続増加し、それに対応してチタン (T i) の含有量が継続減少することができ、または窒素 (N) 及びチタン (T i) の含有量の比率が 1 : 1 でない異なる割合で維持することができる。

50

## 【0047】

本実施例では、第1連結層(CT1)はシリコンチタン(TiSi)からなり、第2連結層(CT2)はチタン(Ti)からなり、第3連結層(CT3)は窒化チタン(TiN)からなり、バッファ層(CT)の厚さが増加するほどその含有量の比率が連続的に変動することと説明したが、これとは違って第1連結層(CT1)は、シリコンモリブデン(MoSi<sub>2</sub>)からなり、第2連結層(CT2)はモリブデン(Mo)からなり、第3連結層(CT3)は窒化モリブデン(MoN)からなるか、または第1連結層(CT1)は、シリコンニッケル(NiSi<sub>3</sub>)からなり、第2連結層(CT2)はニッケル(Ni)からなり、第3連結層(CT3)は窒化ニッケル(NiN)からなり、その含有量の比率は上述と同様に連続的に変動することができる。

10

## 【0048】

本実施例によると、バッファ層(CT)の最外郭に窒化チタン(TiN)からなる第3連結層(CT3)が形成されることによって、バッファ層(CT)の表面が酸化することを防止してソース電極(SE)とドレイン電極(DE)及びアクティブ層(AT)の間の接触抵抗が増加することを抑制することができる。

## 【0049】

また、バッファ層(CT)の厚さが増加するほどシリコン(Si)、チタン(Ti)、及び窒素(N)の含有量比が連続的に減少するか増加することによって、バッファ層(CT)内の含有量比が急激に変動するときに発生するストレスをより減少させることができる。延いては、バッファ層(CT)のうち、第2連結層(CT2)が所定の厚さを有するように形成されることによって、バッファ層(CT)上に発生するストレスを更に減少させることができる。

20

## 【0050】

本実施例で、バッファ層(CT)が第1連結層(CT1)、第2連結層(CT2)、及び第3連結層(CT3)の3層構造で構成されることと説明したが、これとは違って第2連結層(CT2)はその厚さを最小化するか省略することもできる。

## 【0051】

## &lt;液晶表示パネルの製造方法の実施例&gt;

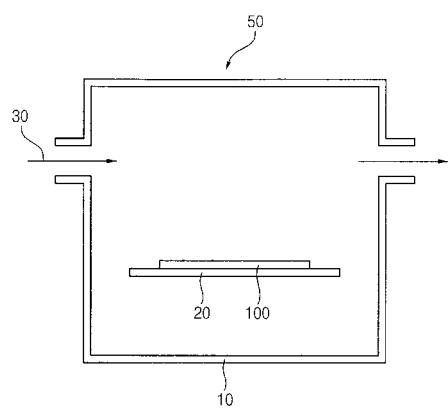

図5は、本発明の一実施例による液晶表示パネルを製造するための製造装置を概念的に示した断面図であり、図6～図17は、図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。ここで、本実施例による液晶表示パネルを製造するための製造装置をまず簡単に説明した後、液晶表示パネルの製造方法を説明する。

30

## 【0052】

図5に示すように、本実施例による液晶表示パネルを製造するためのパネル製造装置50はチャンバー10及びステージ20を含む。

チャンバー10は真空が形成されるための内部空間を有する。内部空間には第1基板100を支持するステージ20が配置される。チャンバー10には外部に気体が流入されるために開口部が形成され、望ましくは、この開口部は気体入口および気体出口で構成される。

## 【0053】

チャンバー10の内部へは、液晶表示パネルを製造するための多種の反応気体が流入されて放出される。即ち、反応気体は、気体入口よりチャンバー10の内部に流入され、第1基板と反応した後、気体出口を通じて外部に放出される。反応気体は一例として、水素ガス(H<sub>2</sub>)、水素化ケイ素ガス(SiH<sub>4</sub>)、水素化リンガス(PH<sub>3</sub>)、アンモニアガス(NH<sub>3</sub>)、塩化チタンガス(TiCl<sub>4</sub>)、塩素系ガス、及びフッ素系ガスなどを含む。

40

## 【0054】

図6及び図2に示すように、本実施例による液晶表示パネルの製造方法として、まず透明基板110上にゲート電極(GE)を形成し、その後、ゲート電極(GE)をカバーするようにゲート絶縁層120を形成する。ゲート電極(GE)は、例えば、モリブデン(Mo)、銅(Cu)、銀(Ag)、アルミニウム(Al)、クロム(Cr)、タンタル(

50

Ta)、及びチタン(Ti)などがスパッタリングによる蒸着方法または化学蒸着方法(CVD)によって透明基板110上に蒸着されて形成される。望ましくは、ゲート電極(GE)はスパッタリングによる蒸着方法によって形成される。一方、ゲート電極(GE)を形成するとき、ゲート配線(GL)、ストレージ配線(SL)、及びストレージ電極(STE)もまた同時に透明基板110上に形成される。

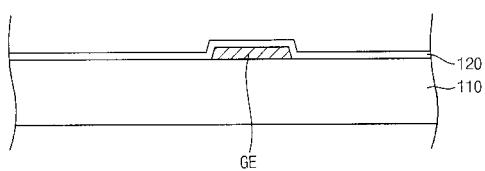

#### 【0055】

図7及び図2に示すように、ゲート絶縁層120上に半導体層(AT1)を連続的に形成する。半導体層(AT1)は、一例として、アモルファスシリコン(a-Si)からなり、プラズマによる蒸着方法(PECVD)によって形成されることが望ましい。

#### 【0056】

具体的に説明すると、ゲート絶縁層120が形成された後、チャンバ10内に反応気体30として水素ガス(H<sub>2</sub>)及び水素化ケイ素ガス(SiH<sub>4</sub>)が連続的に流入され、流入された水素ガス(H<sub>2</sub>)及び水素化ケイ素ガス(SiH<sub>4</sub>)は、プラズマによる蒸着方法(PECVD)によってゲート絶縁層120上に半導体層(AT1)を形成させる。

#### 【0057】

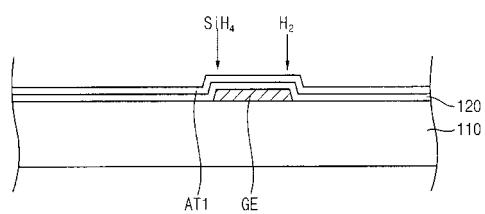

図8及び図2に示すように、半導体層(AT1)上に不純物層(AT2)を連続的に形成する。不純物層(AT2)は一例として、高密度イオンドーピングアモルファスシリコン(n+a-Si)からなり、プラズマによる蒸着方法(PECVD)によって形成されることが望ましい。

#### 【0058】

具体的に、半導体層(AT1)を形成した後、チャンバ10内に反応ガス30として水素ガス(H<sub>2</sub>)及び水素化ケイ素ガス(SiH<sub>4</sub>)のほかに水素化リンガス(PH<sub>3</sub>)が連続的に更に流入され、流入された水素ガス(H<sub>2</sub>)、水素化ケイ素ガス(SiH<sub>4</sub>)及び水素化リンガス(PH<sub>3</sub>)はプラズマによる蒸着方法(PECVD)によって半導体層(AT1)上に不純物層(AT2)を形成させる。ここで、水素化リンガス(PH<sub>3</sub>)のかわりに水素化砒素ガス(AsH<sub>3</sub>)または水素化アンチモン(SbH<sub>3</sub>)を流入してもよい。

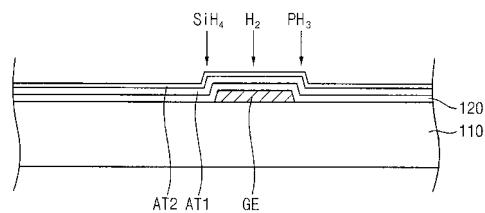

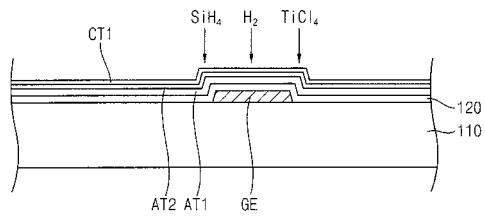

#### 【0059】

図9及び図2に示すように、不純物(AT2)上に第1連結層(CT1)を連続的に形成する。第1連結層(CT1)は、一例として、シリコンチタン(TiSi)からなり、プラズマによる蒸着方法(PECVD)によって約100の厚さに形成されることが望ましい。

#### 【0060】

具体的に、不純物層(AT2)が形成された後、チャンバ10内に水素ガス(H<sub>2</sub>)、水素化ケイ素ガス(SiH<sub>4</sub>)、及び塩化チタンガス(TiCl<sub>4</sub>)が連続的に流入され、流入された水素ガス(H<sub>2</sub>)、水素化ケイ素ガス(SiH<sub>4</sub>)、及び塩化チタンガス(TiCl<sub>4</sub>)はプラズマによる蒸着方法(PECVD)によって不純物層(AT2)上に第1連結層(CT1)を形成させる。ここで、塩化チタンガス(TiCl<sub>4</sub>)は、時間が経過するほど流入される量が徐々に増加することが望ましく、その結果、第1連結層(CT1)は厚さが増加するほどシリコン(Si)の含有量が徐々に減少しながらチタン(Ti)の含有量が徐々に増加する。

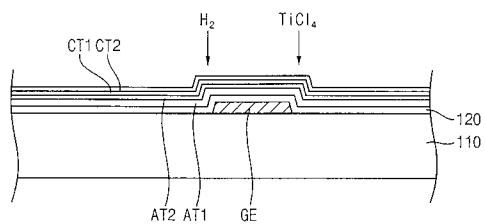

#### 【0061】

図10及び図2に示すように、第1連結層(CT1)上に第2連結層(CT2)を連続的に形成する。第2連結層(CT2)は、一例として、チタン(Ti)からなり、プラズマによる蒸着方法(PECVD)によって少なくとも約200の厚さに形成されることが望ましい。

#### 【0062】

具体的に、第1連結層(CT1)が形成された後、チャンバ10内に流入されていた水素化ケイ素ガス(SiH<sub>4</sub>)はこれ以上流入されず、水素ガス(H<sub>2</sub>)及び塩化チタンガス(TiCl<sub>4</sub>)のみが流入される。このように流入された水素ガス(H<sub>2</sub>)及び塩化チ

10

20

30

40

50

タンガス( $TiCl_4$ )は、プラズマによる蒸着方法(PECVD)によって第1連結層( $CT1$ )上に第2連結層( $CT2$ )を形成させる。ここで、場合によって第2連結層( $CT2$ )が形成される過程を省略してもよい。

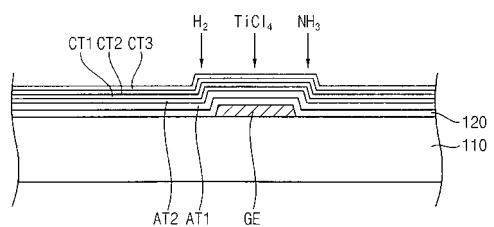

#### 【0063】

図11及び図2に示すように、第2連結層( $CT2$ )上に第3連結層( $CT3$ )を連続的に形成する。第3連結層( $CT3$ )は一例として、窒化チタン( $TiN$ )からなり、プラズマによる蒸着方法(PECVD)によって少なくとも約100の厚さに形成することが望ましい。

#### 【0064】

具体的に、第2連結層( $CT2$ )を形成した後、チャンバ10内に流入されていた水素ガス( $H_2$ )及び塩化チタンガス( $TiCl_4$ )以外にアンモニアガス( $NH_3$ )が更に連続的に流入され、流入された水素ガス( $H_2$ )、塩化チタンガス( $TiCl_4$ )及びアンモニアガス( $NH_3$ )はプラズマによる蒸着方法(PECVD)によって第2連結層( $CT2$ )上に第3連結層( $CT3$ )を形成させる。ここで、塩化チタンガス( $TiCl_4$ )の流入量は時間が経過するほど徐々に減少する反面、アンモニアガス( $NH_3$ )の流入量は時間が経過するほど徐々に増加することが望ましい。その結果、第3連結層( $CT3$ )は、厚さが増加するほどチタン( $Ti$ )の含有量が徐々に減少しながら窒素( $N$ )の含有量が徐々に増加する。

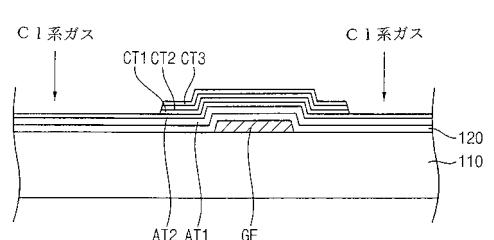

#### 【0065】

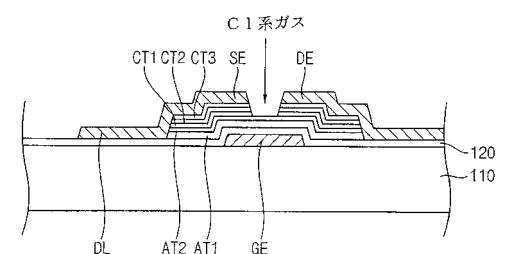

図12及び図2に示すように、第3連結層( $CT3$ )が形成された後、バッファ層( $CT$ )の一部、即ち、第3連結層( $CT3$ )、第2連結層( $CT2$ )、及び第1連結層( $CT1$ )の一部を、連続工程を通じて第1次にエッチングする。第3連結層( $CT3$ )、第2連結層( $CT2$ )、及び第1連結層( $CT1$ )の第1次エッチングは、塩素系ガスで行われることが望ましく、一例として、塩素ガス( $Cl_2$ )によって行われる。ここで、図示していないが、第3連結層( $CT3$ )の一部の上面に硬化されたフォトレジスト(図示せず)が形成された後、第3連結層( $CT3$ )、第2連結層( $CT2$ )、及び第1連結層( $CT1$ )の第1次エッチングが連続的に行われる。

#### 【0066】

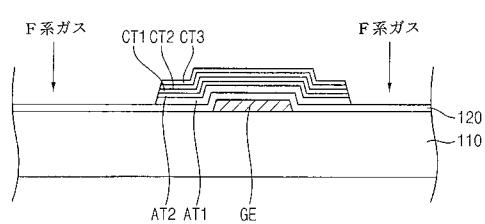

図13及び図2に示すように、バッファ層( $CT$ )の一部を第1次にエッチングした後、アクティブ層(AT)の一部、即ち、不純物層(AT2)及び半導体層(AT1)の一部を連続工程で第1次にエッチングする。不純物層(AT2)及び半導体層(AT1)の第1エッチングはフッ素系ガスからなることが望ましく、一例として、フッ化硫黄ガス( $SF_6$ )及びフッ化炭素ガス( $CF_6$ )によって行われる。

#### 【0067】

一般的に、窒化チタン( $TiN$ )からなる第3連結層( $CT3$ )は、フッ素系ガスに対するエッチング率が小さい。したがって、不純物層(AT2)及び半導体層(AT1)の第1エッチングは第1次でエッチングされたバッファ層( $CT$ )をマスクとして用いられる。これとは違って、不純物層(AT2)及び半導体層(AT1)の第1次エッチングは別途のフォトレジスト(図示せず)によって行うことができる。

#### 【0068】

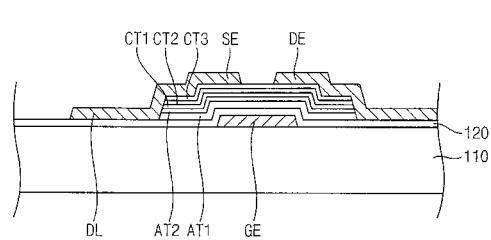

図14及び図2に示すように、アクティブ層(AT)の一部を1次にエッチングした後、ソース電極(SE)及びドレイン電極(DE)を形成する。ソース電極(SE)及びドレイン電極(DE)は、第1次にエッチングされた第3連結層( $CT3$ )の一部と重なるようにゲート絶縁層120上に形成され、所定距離で離隔されて互いに向い合うように形成される。ソース電極(SE)及びドレイン電極(DE)は一例として、アルミニウム(A1)及びモリブデン(Mo)の二重層で構成される。ここで、プラズマによる蒸着方法としてアルミニウム(A1)が蒸着された後、連続的にモリブデン(Mo)が蒸着される。その後、別途のフォトレジストを用いて連続蒸着されたアルミニウム(A1)及びモリブデン(Mo)の一部をエッチングし、その結果、ソース電極(SE)及びドレイン電極(DE)が形成される。

10

20

30

40

50

## 【0069】

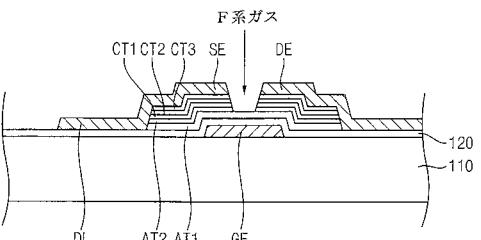

図15及び図2に示すように、ソース電極(SE)及びドレイン電極(DE)をマスクとして第1次にエッティングされたバッファ層(CT)の一部、即ち、第3連結層(CT3)、第2連結層(CT2)、及び第1連結層(CT1)の一部を、連続工程を通じて第2次にエッティングする。ここで、第3連結層(CT3)、第2連結層(CT2)、及び第1連結層(CT1)の第2次エッティングは、塩素系ガスで行われることが望ましく、一例として、塩素ガス(Cl<sub>2</sub>)によって行われる。

## 【0070】

図16及び図2に示すように、第1次にエッティングされたバッファ層(CT)の一部を第2次エッティングした後、ソース電極(SE)及びドレイン電極(DE)をマスクとして第1次にエッティングされた不純物層(AT2)の一部を第2次にエッティングする。不純物層(AT2)の第2次エッティングはフッ素系ガスで行われることが望ましく、一例として、フッ化硫黄ガス(SF<sub>6</sub>)及びフッ化炭素ガス(CF<sub>6</sub>)によって行われる。

10

## 【0071】

図17及び図2に示すように、パッシベーション層130を、薄膜トランジスタ(TFT)をカバーするように基板の全面に形成する。その後、パッシベーション層130上に画素電極140を形成する。

## 【0072】

本実施例によると、ゲート絶縁層120上に半導体層(AT1)を形成した後、不純物層(AT2)、第1連結層(CT1)、第2連結層(CT2)、及び第3連結層(CT3)を、連続工程を通じて形成させることによって、途中に酸化層が形成されることを防止することができる。即ち、多種の反応気体30を絶えず連続的にチャンバ10内に流入することで、半導体層(AT1)、不純物層(AT2)、第1連結層(CT1)、第2連結層(CT2)、及び第3連結層(CT3)を連続的に形成することができ、その結果、工程中に自然な酸化によって酸化層が形成されることを防止して接触抵抗が増加することを防止することができる。

20

## 【0073】

また、反応気体30の含有量の比率を連続的に変化させてチャンバ10の内部に流入させることによって、バッファ層(CT)の含有量比を連続して徐々に変動させて増加させることができ、その結果、バッファ層(CT)の含有量比が急激に変動することによるストレスの発生を防止することができる。

30

## 【0074】

本実施例において、チャンバ10内に、反応気体30のうち、塩化チタンガス(TiC<sub>14</sub>)が流入されることと説明したが、これと違って塩化チタンガス(TiC<sub>14</sub>)の代わりに塩化モリブデンガス(MoCl<sub>6</sub>)または塩化ニッケルガス(NiCl<sub>3</sub>)などを流入することができる。

## 【0075】

反応気体30のうち、金属成分は反応気体30によって形成された連結層の金属成分に影響を及ぼす。例えば、上述のように連結層はチタニウムを含むことができるが、ここで、塩化モリブデンガス(MoCl<sub>6</sub>)が流入される場合、第1連結層(CT1)は、シリコンモリブデン(MoS<sub>2</sub>)からなり、第2連結層(CT2)はモリブデン(Mo)からなり、第3連結層(CT3)は窒化モリブデン(MoN)からなり、塩化ニッケルガス(NiCl<sub>3</sub>)が流入される場合、第1連結層(CT1)は、シリコンニッケル(NiSi<sub>3</sub>)からなり、第2連結層(CT2)はニッケル(Ni)からなり、第3連結層(CT3)は窒化ニッケル(NiN)からなることができる。

40

## 【0076】

<電界発光表示パネルの実施例>

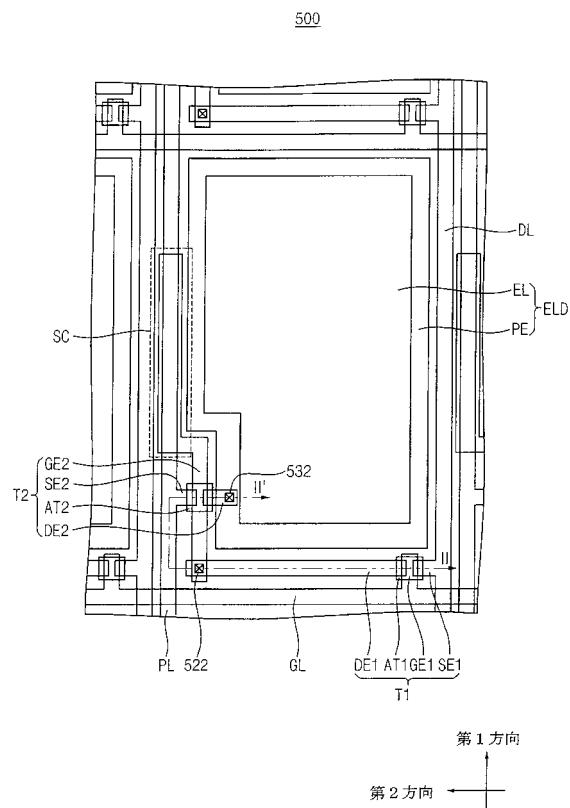

図18は、本発明の一実施例による電界発光表示パネルの一部を示した平面図であり、図19は、図18のII-I'I'に沿って見た断面図である。

図18及び図19に示すように、電界発光表示パネル500は、データ配線(DL)、

50

ゲート配線（G L）、電源配線（P L）、電界発光素子（E L D）、スイッチング薄膜トランジスタ（T 1）、駆動薄膜トランジスタ（T 2）及びストレージキャパシタ（S C）を含む。

#### 【 0 0 7 7 】

データ配線（D L）は、第1方向に長く延長されて形成され、第2方向に沿って複数個が並列に形成される。データ配線（D L）は、スイッチング薄膜トランジスタ（T 1）と電気的に連結されてデータ信号を印加する。

#### 【 0 0 7 8 】

ゲート配線（G L）は、データ配線（D L）と交差するよう第2方向に長く延長されて形成され、第1方向に沿って複数個が並列に形成される。ここで、第1方向は、一例として、第2方向と互いに直角をなしている。ここで、データ配線（D L）及びゲート配線（G L）が互いに交差するように形成することによって、複数の単位画素が定義される。単位画素それぞれには電界発光素子（E L D）、スイッチング薄膜トランジスタ（T 1）、駆動薄膜トランジスタ（T 2）、及びストレージキャパシタ（S C）が形成される。10

#### 【 0 0 7 9 】

電源配線（P L）は、データ配線（D L）と平行に形成され、例えば、データ配線（D L）と第2方向側の反対方向に所定距離で離隔されて形成される。電源配線（P L）は駆動薄膜トランジスタ（T 2）と電気的に連結されて駆動電流を印加する。

#### 【 0 0 8 0 】

電界発光素子（E L D）は電場によって自ら光を発生する。電界発光素子（E L D）は、単位画素別に互いに異なる光を発生することができ、一例として、赤色光、緑色光、及び青色光を発生する。電界発光素子（E L D）は、陽極電極（P E）、電界発光層（E L）、及び陰極電極（図示せず）を含み、陽極電極（P E）と陰極電極との間に電界発光層（E L）が形成される。20

#### 【 0 0 8 1 】

陽極電極（P E）は、単位画素内に形成され、駆動薄膜トランジスタ（T 2）と電気的に連結される。陽極電極（P E）は、駆動薄膜トランジスタ（T 2）から駆動電流の印加を受け、陽極電極（P E）と陰極電極との間に電場を発生する。

#### 【 0 0 8 2 】

電界発光層（E L）は、陽極電極（P E）の上部に形成され、陽極電極（P E）と陰極電極との間に形成された電場によって光を発生させる。電界発光層（E L）は一例として、有機電界発光物質からなり、正孔注入層、正孔輸送層、発光層、電子注入層、及び電子輸送層を含んでもよい。30

#### 【 0 0 8 3 】

陰極電極は、電界発光層（E L）の上部に形成されかつ基板の全面に形成される。陰極電極は、外部から共通電極の印加を受け、陽極電極（P E）と陰極電極との間に電場を発生させる。

#### 【 0 0 8 4 】

陽極電極（P E）及び陰極電極のうち、少なくともいずれか一つは、電界発光層（E L）から発生した光を透過させるために透明かつ導電性物質からなり、一例としてインジウムスズ酸化薄膜（I T O）、インジウム亜鉛酸化薄膜（I Z O）、アモルファスインジウムスズ酸化薄膜（a - I T O）などをフォトリソグラフィ工程によってパターニングされて形成される。40

#### 【 0 0 8 5 】

電界発光素子（E L D）から光が発生する原理を簡単に説明すると、陽極電極（P E）は駆動薄膜トランジスタ（T 2）から駆動電流の印加を受け、陰極電極は外部から共通電圧の印加を受ける。即ち、陽極電極（P E）は共通電極によって正孔の供給を受け、陰極電極は共通電圧によって電子の供給を受ける。これとは違って、陽極電極（P E）に電子が供給されてもよく、陰極電極には正孔が供給されてもよい。

#### 【 0 0 8 6 】

陽極電極(PE)に供給された正孔及び陰極電極に供給された電子は二つの電極の間で発生した電場によって電界発光層(EL)内で互いに結合する。正孔及び電子が電界発光層(EL)内で互いに結合されると、励起状態の分子である励起子が生成され、励起子は基底状態(ground state)の分子に変わりながら光を発生する。

#### 【0087】

スイッチング薄膜トランジスタ(T1)は、単位画素内に形成され、スイッチングゲート電極(GE1)、スイッチングソース電極(SE1)、スイッチングドレイン電極(DE1)、スイッチングアクティブ層(AT1)、及びスイッチングバッファ層(図示せず)を含む。

#### 【0088】

スイッチングゲート電極(GE1)は、ゲート配線(GL)から第1方向に延長されて形成される。スイッチングソース電極(SE1)は、データ配線(DL)から第2方向に延長され、スイッチングゲート電極(GE1)の一部と重なるように形成される。スイッチングドレイン電極(DE1)はスイッチングソース電極(SE1)と向い合うようにスイッチングソース電極(SE1)から所定距離で離隔されて形成され、スイッチングゲート電極(GE1)の一部と重なるように形成される。スイッチングドレイン電極(DE1)は、第2方向に長く延長されて形成され、第1コンタクトホール522を通じて駆動薄膜トランジスタ(T2)の駆動ゲート電極(GE2)と電気的に連結される。

#### 【0089】

スイッチングアクティブ層(AT1)は、スイッチングゲート電極(GE1)とスイッチングソース電極(SE1)及びスイッチングドレイン電極(DE1)との間に形成され、スイッチングゲート電極(GE1)をカバーするように形成される。スイッチングバッファ層は、スイッチングアクティブ層(AT1)とスイッチングソース電極(SE1)との間、及びスイッチングアクティブ層(AT1)とスイッチングドレイン電極(DE1)との間に形成され、接触抵抗が増加することを防止する。

#### 【0090】

駆動薄膜トランジスタ(T2)は、単位画素内に形成され、駆動ゲート電極(GE2)、駆動ソース電極(SE2)、駆動ドレイン電極(DE2)、駆動アクティブ層(AT2)、及び駆動バッファ層(図示せず)を含む。

#### 【0091】

駆動ゲート電極(GE2)は、スイッチングドレイン電極(DE1)と第2コンタクトホール522を通じて電気的に連結され、第1方向に延長されて形成される。駆動ソース電極(SE2)は、電源配線(PL)から第2方向と反対の方向に延長され、駆動ゲート電極(GE2)の一部と重なるように形成される。駆動ドレイン電極(DE2)は、駆動ソース電極(SE2)と向い合うように駆動ソース電極(SE2)から所定距離で離隔されて形成され、駆動ゲート電極(GE2)の一部と重なるように形成される。駆動ドレイン電極(DE2)は、第2方向と反対の方向に延長して形成され、第2コンタクトホール532を通じて電界発光素子(ELD)の陽極電極(PE)と電気的に連結される。

#### 【0092】

駆動アクティブ層(AT2)は、駆動ゲート電極(GE2)及び駆動ソース電極(SE2)と駆動ドレイン電極(DE2)との間に形成され、駆動ゲート電極(GE2)をカバーするように形成される。駆動バッファ層は、駆動アクティブ層(AT2)と駆動ソース電極(SE2)との間、及び駆動アクティブ層(AT2)と駆動ドレイン電極(DE2)との間に形成され、接触抵抗が増加することを防止する。

#### 【0093】

ストレージキャパシタ(SC)は、単位画素内に形成され、駆動ゲート電極(GE2)に印加された駆動電圧を維持させる。ストレージキャパシタ(SC)は、第1電極及び第2電極で構成される。ここで、第1電極は、第2方向及び第1方向に延長された駆動ゲート電極(GE2)の一部であり、第2電極は電源配線(PL)である。

#### 【0094】

10

20

30

40

50

スイッチング薄膜トランジスタ( T 1 )及び駆動薄膜トランジスタ( T 2 )の動作方法を簡単に説明すると、スイッチングゲート電極( G E 1 )にオン電圧が印加されると、データ配線( D L )を通じてスイッチングソース電極( S E 1 )に印加された駆動電圧がスイッチングアクティブ層( A T 1 )を経由してスイッチングドレイン電極( D E 1 )に伝達され第1コンタクトホール 5 2 2 を通して駆動ゲート電極( G E 2 )に印加される。

#### 【 0 0 9 5 】

駆動ゲート電極( G E 2 )に印加された駆動電圧は、ストレージキャパシタ( S C )に維持され、かつ駆動アクティブ層( A T 2 )内にチャンネル層が形成され、チャンネル層は駆動ソース電極( S E 2 )と駆動ドレイン電極( D E 2 )とを互いに電気的に連結させ、電源配線( P L )の駆動電流を駆動ドレイン電極( D E 2 )に伝達し第2コンタクトホール 5 3 2 を通して陽極電極( P E )に印加させる。 10

#### 【 0 0 9 6 】

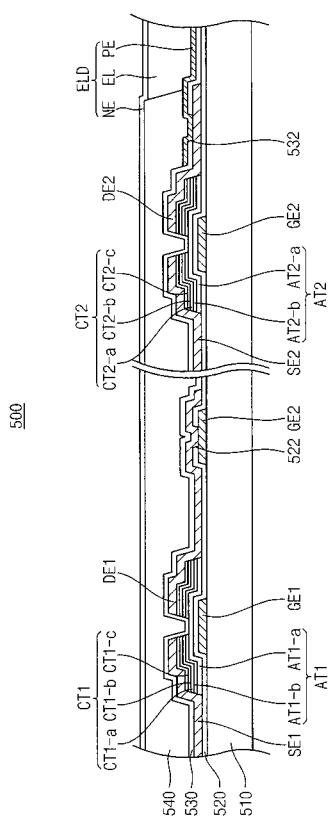

図 19 及び図 18 に示すように、本実施例による電界発光表示パネル 5 0 0 は、ベース基板 5 1 0 、ゲート配線( G L )、ゲート絶縁層 5 2 0 、データ配線( D L )、電源配線( P L )、スイッチング薄膜トランジスタ( T 1 )、駆動薄膜トランジスタ( T 2 )、パッセーション層 5 3 0 、バンク層 5 4 0 、及び電界発光素子( E L D )を含む。ここで、スイッチング薄膜トランジスタ( T 1 )は、スイッチングゲート電極( G E 1 )、スイッチングソース電極( S E 1 )、スイッチングドレイン電極( D E 1 )、スイッチングアクティブ層( A T 1 )、及びスイッチングバッファ層( C T 1 )を含み、駆動薄膜トランジスタ( T 2 )は、駆動ゲート電極( G E 2 )、駆動ソース電極( S E 2 )、駆動ドレイン電極( D E 2 )、駆動アクティブ層( A T 2 )、及び駆動バッファ層( C T 2 )を含む。 20

#### 【 0 0 9 7 】

ベース基板 5 1 0 は、プレート形状を有し、透明な物質からなる。ベース基板 5 1 0 は、例えば、ガラスまたは石英などからなる。

ゲート配線( G L )は、第2方向にベース基板 5 1 0 上に形成され、スイッチングゲート電極( G E 1 )はゲート配線( G L )から第1方向に延長されて形成される。駆動ゲート電極( G E 2 )は第1方向に所定の長さで延長されて形成される。

#### 【 0 0 9 8 】

ゲート絶縁層 5 2 0 は、ゲート配線( G L )、スイッチングゲート電極( G E 1 )、及び駆動ゲート電極( G E 2 )をカバーするようにベース基板 5 1 0 上に形成される。ゲート絶縁層 5 2 0 は、一例として、酸化シリコンまたは窒化シリコンなどの透明な絶縁性物質からなる。ゲート絶縁層 5 2 0 は、駆動ゲート電極( G E 2 )とスイッチングドレイン電極( D E 1 )とを電気的に連結させるために形成された第1コンタクトホール 5 2 2 を含む。 30

#### 【 0 0 9 9 】

データ配線( D L )は、第1方向に延長されてゲート絶縁層 5 2 0 上に形成され、スイッチングソース電極( S E 1 )は、データ配線( D L )から第2方向に延長されて形成される。

#### 【 0 1 0 0 】

電源配線( P L )は、データ配線( D L )と平行にゲート絶縁層 5 2 0 上に形成され、駆動ソース電極( S E 2 )は、電源配線( P L )から第2方向と反対の方向に延長されて形成される。 40

#### 【 0 1 0 1 】

スイッチングアクティブ層( A T 1 )は、スイッチングゲート電極( G E 1 )を貫通するようにゲート絶縁層 5 2 0 上に形成され、駆動アクティブ層( A T 2 )は駆動ゲート電極( G E 2 )を貫通するようにゲート絶縁層 5 2 0 上に形成される。ここで、スイッチングアクティブ層( A T 1 )は、第1半導体層( A T 1 - a )及び第1不純物層( A T 1 - b )を含み、駆動アクティブ層( A T 2 )は第2半導体層( A T 2 - a )及び第2不純物層( A T 2 - b )を含む。 50

## 【0102】

第1半導体層( A T 1 - a )は、スイッチングゲート電極( G E 1 )を貫通するようにゲート絶縁層 520 上に形成され、一例として、アモルファスシリコン( a - S i )である。第1不純物層( A T 1 - b )は、第1半導体層( A T 1 - a )上に形成され、一例として、高密度イオンドーピングアモルファスシリコン( n + a - S i )である。ここで、第1不純物層( A T 1 - b )は中間部位が除去されて2部分に分離される。

## 【0103】

第2半導体層( A T 2 - a )は、駆動ゲート電極( G E 2 )を貫通するようにゲート絶縁層 520 上に形成され、一例として、アモルファスシリコン( a - S i )である。第2不純物層( A T 2 - b )は、第2半導体層( A T 2 - a )上に形成され、一例として、高密度イオンドーピングアモルファスシリコン( n + a - S i )である。ここで、第2不純物層( A T 2 - b )は、中間部位が除去されて2部分に分離される。10

## 【0104】

スイッチングバッファ層( C T 1 )は、2部分に分離された第1不純物層( A T 1 - b )上にそれぞれ一対で形成される。一対のスイッチングバッファ層( C T 1 )のそれぞれは、第1スイッチング連結層( C T 1 - a )、第2スイッチング連結層( C T 1 - b )、及び第3スイッチング連結層( C T 1 - c )を含む。

## 【0105】

第1スイッチング連結層( C T 1 - a )は、第1不純物層( A T 1 - b )上に形成され、一例として、シリコンチタン( T i S i )、シリコンモリブデン( M o S i <sub>2</sub> )、及びシリコンニッケル( N i S i <sub>3</sub> )で構成される。第1スイッチング連結層( C T 1 - a )の厚さは約100 を有することが望ましい。20

## 【0106】

第2スイッチング連結層( C T 1 - b )は、第1スイッチング連結層( C T 1 - a )上に形成され、一例としてチタン( T i )、モリブデン( M o )、及びニッケル( N i )で構成される。第2スイッチング連結層( C T 1 - b )の厚さは約200 を有することが望ましい。

## 【0107】

第3スイッチング連結層( C T 1 - c )は、第2スイッチング連結層( C T 1 - b )上に形成され、一例として、窒化チタン( T i N )、窒化モリブデン( M o N )、及び窒化ニッケル( N i N )で構成される。第3スイッチング連結層( C T 1 - c )の厚さは少なくとも約100 を有することが望ましい。30

## 【0108】

第1スイッチング連結層( C T 1 - a )から第3スイッチング連結層( C T 1 - c )までの厚さが徐々に増加することにつれて物質の含有量の比率が連続的に徐々に変動する。

また、駆動バッファ層( C T 2 )は、2部分に分離された第2不純物層( A T 2 - b )上にそれぞれ一対に形成される。一対の駆動バッファ層( C T 2 )それぞれは第1駆動連結層( C T 2 - a )、第2駆動連結層( C T 2 - b )及び第3駆動連結層( C T 2 - c )を含む。

## 【0109】

第1駆動連結層( C T 2 - a )は、第2不純物層( A T 2 - b )上に形成され、一例としてシリコンチタン( T i S i )、シリコンモリブデン( M o S i <sub>2</sub> )、及びシリコンニッケル( N i S i <sub>3</sub> )で構成される。第1駆動連結層( C T 2 - a )の厚さは100 を有することが望ましい。40

## 【0110】

第2駆動連結層( C T 2 - b )は、第1駆動連結層( C T 2 - a )上に形成され、一例として、チタン( T i )、モリブデン( M o )、及びニッケル( N i )で構成される。第2駆動連結層( C T 2 - b )の厚さは約200 を有することが望ましい。

## 【0111】

第3駆動連結層( C T 2 - c )は、第2駆動連結層( C T 2 - b )上に形成され、一例

50

として窒化チタン (TiN)、窒化モリブデン (MoN)、及び窒化ニッケル (NiN) で構成される。第3駆動連結層 (CT2-c) の厚さは少なくとも約100 を有することが望ましい。

#### 【0112】

第1駆動連結層 (CT2-a) から第3駆動連結層 (CT2-c) まで厚さが徐々に増加することにつれて物質の含有量の比率が連続的に徐々に変わる。

スイッチングソース電極 (SE1) は、データ配線 (DL) から延長され、第3スイッチング連結層 (CT1-c) のうちの一上面に形成される。スイッチングドレイン電極 (DE1) は、スイッチングソース電極 (SE1) から所定距離で離隔されて第3スイッチング連結層 (CT1-c) のうちの、他の一上面に形成される。スイッチングドレイン電極 (DE1) は、長く延長されてゲート絶縁層 520 上に形成される。スイッチングソース電極 (SE1) 及びスイッチングドレイン電極 (DE1) は、例えば、アルミニウム (Al) 及びモリブデン (Mo) の二重層で構成することが望ましい。10

#### 【0113】

また、駆動ソース電極 (SE2) は、電源配線 (PL) から延長されて第3駆動連結層 (CT2-c) のうちの一上面に形成される。駆動ドレイン電極 (DE2) は、駆動ソース電極 (SE2) から所定距離で離隔されて第3駆動連結層 (CT2-c) のうちの、他の一上面に形成される。駆動ドレイン電極 (DE2) は、長く延長されてゲート絶縁層 520 上に形成される。駆動ソース電極 (SE2) 及び駆動ドレイン電極 (DE2) は、例えば、アルミニウム (Al) 及びモリブデン (Mo) の二重層で構成されることが望ましい。20

#### 【0114】

パッシベーション層 530 は、スイッチング薄膜トランジスタ (T1) 及び駆動薄膜トランジスタ (T2) をカバーするようにゲート絶縁層 520 上に形成され、スイッチング薄膜トランジスタ (T1) 及び駆動薄膜トランジスタ (T2) を外部の熱や湿気から保護する。パッシベーション層 530 は、駆動ドレイン電極 (DE2) 上に形成され、駆動ドレイン電極 (DE2) と陽極電極 (PE) とを電気的に連結させる第2コンタクトホール 532 を含む。パッシベーション層 530 は、一例として、透明な酸化シリコン (SiO<sub>2</sub>) からなる。5

#### 【0115】

陽極電極 (PE) は、第2コンタクトホール 532 を通じて駆動ドレイン電極 (DE2) と電気的に連結され、ゲート絶縁層 520 上に形成される。バンク層 540 は、パッシベーション層 530 上に形成され、陽極電極 (PE) と対応して開口部を形成する。電界発光層 (EL) は、バンク層 540 に形成された開口部に形成される。陰極電極 (NE) は、電界発光層 (EL) の上面及びバンク層 540 の上面に接するように基板の全面に形成される。30

#### 【0116】

本実施例によると、スイッチングバッファ層 (CT1) 及び駆動バッファ層 (CT2) の最外郭に酸化防止のための第3スイッチング連結層 (CT1-c) 及び第3駆動連結層 (CT2-c) が形成されることによって、酸化によって接触抵抗が増加することを防止することができる。40

#### 【0117】

ソース電極とアクティブ層との間、及びドレイン電極とアクティブ層との間にバッファ層を形成して接触抵抗の増加を防止する。駆動アクティブ層 (AT2) と駆動ソース電極 (SE2) との間、及び駆動アクティブ層 (AT2) と駆動ドレイン電極 (DE2) との間の接触抵抗が増加しないので、液晶表示装置または電界発光表示装置の画質が向上する。特に、電界発光素子 (ELD) は、電圧駆動方式でない電流駆動方式によって光を発生するので、駆動バッファ層 (CT2) を形成して接触抵抗の増加を防止する。具体的に、電界発光素子 (ELD) は、駆動アクティブ層 (AT2) と駆動ソース電極 (SE2) との間の接触抵抗、及び駆動アクティブ層 (AT2) と駆動ドレイン電極 (DE2) との間50

の接触抵抗に敏感な影響を受ける。したがって、電界発光素子（E L D）の電流駆動モードにおける効率が増加する。

#### 【0118】

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離脱することなく、本発明を修正または変更できる。

#### 【図面の簡単な説明】

#### 【0119】

【図1】本発明の一実施例による液晶表示パネルを示す斜視図である。

【図2】図1の表示パネルのうち、第1基板の単位画素を概念的に示す平面図である。 10

【図3】図2のI-I'に沿って見た断面図である。

【図4】図3のバッファ層において、厚さが増加することによる物質の含有量比を示すグラフである。

【図5】本発明の一実施例による液晶表示パネルを製造するための製造装置を概念的に示した断面図である。

【図6】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。

【図7】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。 20

【図8】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。

【図9】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。

【図10】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。

【図11】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。

【図12】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。

【図13】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。 30

【図14】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。

【図15】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。

【図16】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。

【図17】図5の製造装置によって液晶表示パネルを製造する方法を説明するための断面図である。

【図18】本発明の一実施例による電界発光表示パネルの一部を示した平面図である。 40

【図19】図18のII-II'に沿って見た断面図である。

#### 【符号の説明】

#### 【0120】

10 チャンバ

20 ステージ

30 反応気体

50 パネル製造装置

100 第1基板

110 透明基板

120、520 ゲート絶縁層

130、530 パッシベーション層

132 コンタクトホール

140 画素電極

200 第2基板

300 液晶層

400 液晶表示パネル

500 電界発光表示パネル

510 ベース基板

522 第1コンタクトホール

532 第2コンタクトホール

540 バンク層

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 11】

【図 10】

【図 12】

【図 13】

【図 15】

【図 14】

【図 16】

【図17】

【図18】

【図19】

---

フロントページの続き

(72)発明者 梁 成 勳

大韓民国 ソウル特別市 城東区 聖水1街2洞 双龍アパート 106棟 301号

(72)発明者 オ ミン 锡

大韓民国 京畿道 龍仁市 新鳳洞 韓一アパート 102棟 202号

(72)発明者 崔 在 鎬

大韓民国 ソウル特別市 鐘路区 昌信3洞 双龍アパート 207棟 1508号

(72)発明者 崔 龍 模

大韓民国 忠清北道 清州市 上黨区 龍岩洞 セウォンアパート 102棟 908号

審査官 綿引 隆

(56)参考文献 特開平03-220529(JP,A)

特開平11-354810(JP,A)

特開2000-208773(JP,A)

特開平09-092840(JP,A)

特開2001-147424(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368

H01L 21/336

H01L 29/417

H01L 29/786