(19) **日本国特許庁(JP)**

### (12) 特 許 公 報(B2)

(11)特許番号

特許第6118045号 (P6118045)

(45) 発行日 平成29年4月19日(2017.4.19)

(24) 登録日 平成29年3月31日 (2017.3.31)

(51) Int.Cl. F 1

**GO 6 F** 11/10 (2006.01) GO 6 F 11/10 6 6 8 **GO 6 F** 12/16 (2006.01) GO 6 F 12/16 3 1 O J

請求項の数 16 (全 35 頁)

(21) 出願番号 特願2012-170078 (P2012-170078)

(22) 出願日 平成24年7月31日 (2012. 7. 31) (65) 公開番号 特開2014-29616 (P2014-29616A)

(43) 公開日 平成26年2月13日 (2014.2.13) 審査請求日 平成27年6月16日 (2015.6.16) ||(73)特許権者 591128453

株式会社メガチップス

大阪府大阪市淀川区宮原一丁目1番1号

||(74)代理人 100136353

弁理士 高尾 建吾

(72) 発明者 田村 満

大阪市淀川区宮原4丁目1番6号 株式会

社メガチップス内

審査官 酒井 恭信

最終頁に続く

#### (54) 【発明の名称】半導体記憶装置

#### (57)【特許請求の範囲】

#### 【請求項1】

それぞれがデータの消去単位である複数のブロックを有する記憶部と、 前記記憶部を制御する制御部と、

#### を備え、

前記記憶部が有する全ブロックには、

前記制御部が前記記憶部を管理するために必要な管理情報を格納するためのブロックとして限定的に割り当てられた、4個以上である第1所定数個のブロックから成る第1ブロック群と、

第1ブロック群以外の第2ブロック群と、

10

#### が含まれ、

第1ブロック群の中から前記制御部によって選択された、3個以上かつ第1所定数個未満である第2所定数個のブロックの各々に、同一内容の管理情報が格納されており、

管理情報は、

第1管理情報と、

第1管理情報よりも書き換え頻度の高い第2管理情報と、

#### を含み、

第1管理情報は第1ブロック群内に格納され、

第2管理情報は第2ブロック群内に格納され、

第1管理情報には、第2ブロック群内において第2管理情報を格納しているブロックを

示す第1位置情報が含まれ、

前記制御部は、

正常な第1管理情報が格納されている正常ブロックを、第1ブロック群の中から特定し

ある1個の正常ブロックに格納されている第1管理情報と、当該第1管理情報に記述されている第<u>1</u>ブロック群内の他の2個のブロックを示す第2位置情報に基づき特定される2個の第1管理情報とを用いて多数決を行うことによって、1個の妥当な第1管理情報を特定し、

当該妥当な第1管理情報に含まれている第1位置情報に基づいて、第2ブロック群の中から第2管理情報を取得する、半導体記憶装置。

10

#### 【請求項2】

#### 【請求項3】

第1管理情報には、第1ブロック群内の不良ブロックを示す位置情報が含まれ、

第2管理情報には、第2ブロック群内の不良ブロックを示す位置情報が含まれる、請求項2に記載の半導体記憶装置。

#### 【請求項4】

第 2 ブロック群の中から選択された<u>、 2 個以上である</u>第<u>3</u>所定数個のブロックの各々に、同一内容の第 2 管理情報が格納されており、

第1管理情報には、第2管理情報を格納している第<u>3</u>所定数個のブロックを示す<u>第1</u>位 置情報が含まれており、

前記制御部は、妥当な第1管理情報に含まれている<u>第1</u>位置情報に基づいて<u>第3所定数</u>個のブロックを特定し、当該第3所定数個のブロックに格納されている第3所定数個の第2管理情報の中から、1個の第2管理情報を取得する、請求項1~3のいずれか一つに記載の半導体記憶装置。

#### 【請求項5】

第2ブロック群の中から選択された<u>2個以上である</u>第<u>3</u>所定数個のブロックに、バージョンが異なる第3所定数個の第2管理情報が格納されており、

第 1 管理情報には、第 2 管理情報を格納している第<u>3</u>所定数個のブロックを示す<u>第 1</u>位 置情報が含まれており、

前記制御部は、妥当な第1管理情報に含まれている<u>第1</u>位置情報に基づいて<u>第3所定数</u>個のブロックを特定し、当該第3所定数個のブロックに格納されている第3所定数個の第2管理情報の中から、1個の第2管理情報を取得する、請求項1~3のいずれか一つに記載の半導体記憶装置。

#### 【請求項6】

前記制御部は、第1ブロック群の中から、先天性不良ブロックを除外することにより、 正常ブロックを特定する、請求項1~5のいずれか一つに記載の半導体記憶装置。

#### 【請求項7】

前記制御部は、第1ブロック群の中から、所定の無効フラグが付加された無効ブロックを除外することにより、正常ブロックを特定する、請求項1~6のいずれか一つに記載の半導体記憶装置。

#### 【請求項8】

前記制御部は、第1ブロック群の中から、格納している第1管理情報にデータの誤りが 生じている異常ブロックを除外することにより、正常ブロックを特定する、請求項1~7 のいずれか一つに記載の半導体記憶装置。

#### 【請求項9】

それぞれがデータの消去単位である複数のブロックを有する記憶部と、

前記記憶部を制御する制御部と、

20

30

#### を備え、

前記記憶部が有する全ブロックには、

前記制御部が前記記憶部を管理するために必要な管理情報を格納するためのブロックと して限定的に割り当てられた、4個以上である第1所定数個のブロックから成る第1ブロック群と、

第1ブロック群以外の第2ブロック群と、

#### が含まれ、

第1ブロック群の中から前記制御部によって選択された、3個以上かつ第1所定数個未満である第2所定数個のブロックの各々に、同一内容の管理情報が格納されており、

管理情報は、

第1管理情報と、

第1管理情報よりも書き換え頻度の高い第2管理情報と、

#### を含み、

第1管理情報は第1ブロック群内に格納され、

第2管理情報は第2ブロック群内に格納され、

前記制御部は、

第1管理情報を更新する必要が生じた場合には、第1ブロック群の中で第2所定数個の空きブロックを確保し、当該第2所定数個の空きブロックの各々に、更新後の第1管理情報をそれぞれ書き込み、

第2所定数個の空きブロックの中の一の空きブロックに書き込む第1管理情報に、第2 所定数個の空きブロックの中の他の空きブロックを示す位置情報を含めて書き込む、半導 体記憶装置。

#### 【請求項10】

前記制御部は、第1管理情報の誤り検出符号を、第1管理情報に含めて書き込む、請求項9に記載の半導体記憶装置。

#### 【請求項11】

前記制御部は、第1ブロック群の中から、先天性不良ブロックを除外することにより、 空きブロックを確保する、請求項9又は10に記載の半導体記憶装置。

#### 【請求項12】

<u>前記制御部は、第1ブロック群の中から、後天性不良ブロックを除外することにより、</u> 空きブロックを確保する、請求項9~11のいずれか一つに記載の半導体記憶装置。

#### 【請求項13】

前記制御部は、第1プロック群の中から、更新前の第1管理情報が格納されている第2 所定数個のプロックを除外することにより、空きプロックを確保する、請求項9~12の いずれか一つに記載の半導体記憶装置。

#### 【請求項14】

前記制御部は、第2所定数個の空きブロックの中の1個の空きブロックへの第1管理情報の書き込みが完了すると、更新前の第1管理情報が格納されていた第2所定数個のブロックの中の1個のブロックに対して、所定の無効フラグを付加する、請求項9~13のいずれか一つに記載の半導体記憶装置。

#### 【請求項15】

前記制御部は、第2所定数個の空きブロックの中の1個の空きブロックへの第1管理情報の書き込みが完了すると、更新前の第1管理情報が格納されていた第2所定数個のブロックの中の1個のブロックに対して、データの消去を行う、請求項9~13のいずれか一つに記載の半導体記憶装置。

#### 【請求項16】

<u>先天性不良ブロックを除外した第1所定数個のブロックが、第1ブロック群として割り</u> 当てられる、請求項1~15のいずれか一つに記載の半導体記憶装置。

【発明の詳細な説明】

10

20

30

#### 【技術分野】

#### [0001]

本発明は、半導体記憶装置に関する。

#### 【背景技術】

#### [0002]

メモリコントローラと、フラッシュメモリ等のメモリセルアレイとを備えたメモリシステムが実用化されている。NAND型のフラッシュメモリ等においては、製造時に発生する先天性不良ブロックや、出荷後の通常使用によって発生する後天性不良ブロックが、ランダムに存在する。これらの不良ブロックを避けて使用する必要があるため、所定の管理情報によって不良ブロックの位置が管理される。

#### [0003]

制御対象メモリであるメモリセルアレイ内に管理情報を格納しようとすると、格納先のブロックが先天性不良ブロックであった場合や、格納時には先天性不良ブロックではなかったがその後に後天性不良ブロックとなった場合に、管理情報の一部又は全部のデータが破壊又は喪失されてしまう可能性がある。また、管理情報を更新するために新たな管理情報を書き込んでいる最中に、ユーザの誤操作等によって強制的に電源が遮断されてしまうと、管理情報の一部又は全部のデータが破壊又は喪失されてしまう可能性がある。管理情報が破壊又は喪失されると、その後はメモリシステムの正常動作が阻害される。

#### [0004]

そこで、背景技術に係るメモリシステムでは、制御対象メモリとは別の専用の不揮発性メモリを用意し、当該不揮発性メモリ内に管理情報を格納することによって、管理情報の破壊等が防止されている。他の方法として、メモリコントローラ内の不揮発のメモリ領域に管理情報を格納し、あるいはDIPスイッチの設定によって管理情報をメモリコントローラに与えることで、管理情報の破壊等が防止されている。

#### [0005]

なお、下記特許文献 1 には、コントローラとフラッシュメモリとを備えたメモリシステムが開示されている。不良ブロックのリスト等を含む管理情報は、複数の分割片に分割されて、各分割片がフラッシュメモリ内に個別に保存されている。また、コントローラ内には、DRAM等の揮発性メモリを用いた管理メモリが実装されている。複数の分割片がフラッシュメモリから管理メモリに読み出されることにより、管理メモリ内に管理情報が保存される。

#### 【先行技術文献】

#### 【特許文献】

#### [0006]

【特許文献1】特開2011-59866号公報

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0007]

上述したように背景技術に係るメモリシステムでは、制御対象メモリとは別の専用の不揮発性メモリ内に管理情報が格納される。従って、制御対象メモリとは別に専用の不揮発性メモリを追加する必要があるため、製造コストが増大するとともに制御が複雑化する。

#### **r** n n n s 1

本発明はかかる問題を解決するために成されたものであり、不良ブロックの存在や強制的な電源遮断等に起因して正常動作が阻害されるという事態を回避しつつ、管理情報を制御対象メモリに格納することが可能な半導体記憶装置を得ることを目的とする。

#### 【課題を解決するための手段】

#### [0009]

本発明の第1の態様に係る半導体記憶装置は、それぞれがデータの消去単位である複数のブロックを有する記憶部と、前記記憶部を制御する制御部と、を備え、前記記憶部が有する全ブロックには、前記制御部が前記記憶部を管理するために必要な管理情報を格納す

10

20

30

40

るためのブロックとして限定的に割り当てられた、4個以上である第1所定数個のブロックから成る第1プロック群と、第1プロック群以外の第2プロック群と、が含まれ、第1プロック群の中から前記制御部によって選択された、3個以上かつ第1所定数個未満である第2所定数個のブロックの各々に、同一内容の管理情報が格納されており、管理情報は、第1管理情報と、第1管理情報よりも書き換え頻度の高い第2管理情報と、を含み、第1管理情報は第1プロック群内に格納され、第2管理情報を格納しているブロック群内において第2管理情報を格納しているブロックを、第1で回ック群内において第2管理情報が格納されているでである第1位置情報が含まれ、前記制御部は、正常な第1管理情報が格納されているでででで、第1プロック群の中から特定し、ある1個の正常プロックに格納されている第1管理情報と、当該第1管理情報に記述されている第1プロック群内の他の2個のブロックを示す第2位置情報に基づき特定される2個の第1管理情報とを用いて多数決を行って、1個の妥当な第1管理情報を特定し、当該妥当な第1管理情報に含まれている第1位置情報に基づいて、第2プロック群の中から第2管理情報を取得することを特徴とするものである。

#### [0010]

第1の態様に係る半導体記憶装置によれば、4個以上である第1所定数個のブロックから成る第1ブロック群が、管理情報を格納するためのブロックとして限定的に割り当てられている。そして、第1ブロック群の中から制御部によって選択された、3個以上かつ第1所定数個未満である第2所定数個のブロックの各々に、同一内容の管理情報が格納されている。従って、第2所定数個のブロックに格納されている第2所定数個の第1管理情報のうちの一つが破壊又は喪失された場合であっても、制御部は、破壊又は喪失されていない残りの第1管理情報を、記憶部から取得することができる。その結果、不良ブロックの存在や強制的な電源遮断等に起因して正常動作が阻害されるという事態を回避しつつ、管理情報を制御対象メモリに格納することが可能となる。

また、第1の態様に係る半導体記憶装置によれば、管理情報は、第1管理情報と、第1管理情報よりも書き換え頻度の高い第2管理情報とを含む。そして、第1管理情報は第1プロック群内に格納され、第2管理情報は第2プロック群内に格納される。書き換え頻度に応じて管理情報を第1管理情報と第2管理情報とに分割し、限定的に割り当てられた第1プロック群内には、書き換え頻度の低い第1管理情報を格納することにより、第1プロック群内ではデータの書き換えが頻繁には発生しない。その結果、第1プロック群内における後天性不良プロックの発生が抑制されるため、装置の信頼性を向上することが可能となる

また、第1の態様に係る半導体記憶装置によれば、制御部は、正常な第1管理情報が格納されている正常ブロックを、第1ブロック群の中から特定する。そして、特定したある1個の正常ブロックに格納されている第1管理情報と、当該第1管理情報に記述されている第<u>1</u>ブロック群内の他の2個のブロックを示す第2位置情報に基づき特定される2個の第1管理情報とを用いて多数決を行うことによって、1個の妥当な第1管理情報を特定する。従って、更新が繰り返されることで第1ブロック群内に複数バージョンの第1管理情報が格納されている場合であっても、妥当な第1管理情報を適切に特定することが可能となる。また、多数決を行う対象を3個の第1管理情報に限定することが可能となる。また、多数決を行う対象を、更新時に併せて書き込まれた同一内容の第1管理情報に限定できるため、多数決によって妥当な第1管理情報を特定できる可能性を高めることが可能となる。

#### [0013]

本発明の第2の態様に係る半導体記憶装置は、第1の態様に係る半導体記憶装置において特に、第2管理情報には、不良プロックを示す位置情報が含まれることを特徴とするものである。

10

20

30

10

20

30

40

50

#### [0014]

第<u>2</u>の態様に係る半導体記憶装置によれば<u>、第</u>2管理情報には、不良ブロックを示す位置情報が含まれる。従って、制御部は、第1管理情報を記憶部から読み出すことによって、第2管理情報を格納しているブロックを示す位置情報を取得でき、また、当該位置情報に基づいて第2管理情報を記憶部から読み出すことによって、不良ブロックを示す位置情報を取得することが可能となる。

#### [0015]

本発明の第<u>3</u>の態様に係る半導体記憶装置は、第<u>2</u>の態様に係る半導体記憶装置において特に、第1管理情報には、第1ブロック群内の不良ブロックを示す位置情報が含まれ、第2管理情報には、第2ブロック群内の不良ブロックを示す位置情報が含まれることを特徴とするものである。

#### [0016]

第<u>3</u>の態様に係る半導体記憶装置によれば、第1管理情報には、第1ブロック群内の不良ブロックを示す位置情報が含まれ、第2管理情報には、第2ブロック群内の不良ブロックを示す位置情報が含まれる。従って、第1ブロック群内で後天性不良ブロックが発生した場合には、第1管理情報のみを更新すればよく、第2管理情報の更新を省略することができる。同様に、第2ブロック群内で後天性不良ブロックが発生した場合には、第2管理情報のみを更新すればよく、第1管理情報の更新を省略することができる。

#### [0019]

本発明の第4の態様に係る半導体記憶装置は、第1~第3のいずれか一つの態様に係る半導体記憶装置において特に、第2ブロック群の中から選択された<u>、2個以上である</u>第<u>3</u>所定数個のブロックの各々に、同一内容の第2管理情報が格納されており、第1管理情報には、第2管理情報を格納している第<u>3</u>所定数個のブロックを示す<u>第1</u>位置情報が含まれており、前記制御部は、妥当な第1管理情報に含まれている<u>第1</u>位置情報に基づい<u>て第3所定数個のブロックを特定し、当該</u>第<u>3</u>所定数個のブロックに格納されている第<u>3</u>所定数個の第2管理情報の中から、1個の第2管理情報を取得することを特徴とするものである

#### [0020]

第<u>4</u>の態様に係る半導体記憶装置によれば、第2ブロック群の中から選択された<u>、2個以上である</u>第<u>3</u>所定数個のブロックの各々に、同一内容の第2管理情報が格納されている。そして、制御部は、妥当な第1管理情報に含まれている<u>第1</u>位置情報に基づい<u>て第3所定数</u>個のブロックを特定し、当該第<u>3</u>所定数個のブロックに格納されている第<u>3</u>所定数個の第2管理情報の中から、1個の第2管理情報を取得する。従って、第<u>3</u>所定数個のブロックに格納されている第<u>3</u>所定数個の第2管理情報のうちの一つが破壊又は喪失された場合であっても、制御部は、破壊又は喪失されていない残りの第2管理情報を、記憶部から取得することができる。その結果、不良ブロックの存在や強制的な電源遮断等に起因して正常動作が阻害されるという事態を回避しつつ、管理情報を制御対象メモリに格納することが可能となる。

#### [0021]

本発明の第5の態様に係る半導体記憶装置は、第1~第3のいずれか一つの態様に係る半導体記憶装置において特に、第2ブロック群の中から選択された、2個以上である第3所定数個のブロックに、バージョンが異なる第3所定数個の第2管理情報が格納されており、第1管理情報には、第2管理情報を格納している第3所定数個のブロックを示す第1位置情報が含まれており、前記制御部は、妥当な第1管理情報に含まれている第1位置情報に基づいて第3所定数個のブロックを特定し、当該第3所定数個のブロックに格納され

ている第<u>3</u>所定数個の第2管理情報の中から、1個の第2管理情報を取得することを特徴とするものである。

#### [0022]

第5の態様に係る半導体記憶装置によれば、第2ブロック群の中から選択された、2個以上である第3所定数個のブロックに、バージョンが異なる第3所定数個の第2管理情報が格納されている。そして、制御部は、妥当な第1管理情報に含まれている第1位置情報に基づいて第3所定数個のブロックを特定し、当該第3所定数個のブロックに格納されている第3所定数個のブロックに格納されている第3所定数個のブロックに格納されている第3所定数個の第2管理情報のうちの一つが破壊又は喪失された場合であっても、制御部は、破壊又は喪失されていない残りの第2管理情報を、記憶部から取得することができる。その結果、不良ブロックの存在や強制的な電源遮断等に起因して正常動作が阻害されるという事態を回避しつつ、管理情報を制御対象メモリに格納することが可能となる。

#### [0023]

本発明の第 $\underline{6}$ の態様に係る半導体記憶装置は、第 $\underline{1}$ ~第 $\underline{5}$ のいずれか一つの態様に係る半導体記憶装置において特に、前記制御部は、第1ブロック群の中から、先天性不良ブロックを除外することにより、正常ブロックを特定することを特徴とするものである。

#### [0024]

第<u>6</u>の態様に係る半導体記憶装置によれば、制御部は、第1ブロック群の中から先天性不良ブロックを除外することにより、正常ブロックを特定する。従って、先天性不良ブロックが正常ブロックとして特定されるという事態を回避できるため、妥当な第1管理情報を適切に特定することが可能となる。

#### [0025]

本発明の第7の態様に係る半導体記憶装置は、第1~第6のいずれか一つの態様に係る半導体記憶装置において特に、前記制御部は、第1プロック群の中から、所定の無効フラグが付加された無効プロックを除外することにより、正常プロックを特定することを特徴とするものである。

#### [0026]

第<u>7</u>の態様に係る半導体記憶装置によれば、制御部は、第1ブロック群の中から無効ブロックを除外することにより、正常ブロックを特定する。従って、無効ブロックが正常ブロックとして特定されるという事態を回避できるため、妥当な第1管理情報を適切に特定することが可能となる。

#### [0027]

本発明の第8の態様に係る半導体記憶装置は、第1~第7のいずれか一つの態様に係る 40 半導体記憶装置において特に、前記制御部は、第1ブロック群の中から、格納している第 1 管理情報にデータの誤りが生じている異常ブロックを除外することにより、正常ブロックを特定することを特徴とするものである。

#### [0028]

第<u>8</u>の態様に係る半導体記憶装置によれば、制御部は、第1ブロック群の中から異常ブロックを除外することにより、正常ブロックを特定する。従って、異常ブロックが正常ブロックとして特定されるという事態を回避できるため、妥当な第1管理情報を適切に特定することが可能となる。

20

10

#### [0045]

本発明の第9の態様に係る半導体記憶装置は、それぞれがデータの消去単位である複数のブロックを有する記憶部と、前記記憶部を制御する制御部と、を備え、前記記憶部が有する全ブロックには、前記制御部が前記記憶部を管理するために必要な管理情報を格がするためのブロックとして限定的に割り当てられた、4個以上である第1所定数個のツカーので含まれた、3個以上かつ第1所定数個表別である第1ブロック群と、第1ブロック群以外の第2ブロック群と、が含まれ、第1可ック群の中から前記制御部によって選択された、3個以上かつ第1所定数個未満報息、第1管理情報と、第1管理情報よりも書き換え頻度の高い第2管理情報と、を含みいままでである。第1管理情報を更新する必要が生じた場合には、第1ブロック群内に格納され、第2管理情報は第2ブロック群内に格納でれ、前記制御部は、第1管理情報を更新する必要が生じた場合には、第1ブロック群の中の第1に書き込む、第2所定数個の空きブロックの中のの空きブロックを確保し、当該第2所定数個の空きブロックの中のの空きブロックに書き込む第1管理情報に、第2所定数個の空きブロックの中の他の空きブロックに書き込むことを特徴とするものである。

#### [0046]

第<u>9</u>の態様に係る半導体記憶装置によれば、<u>4個以上である</u>第1所定数個のブロックから成る第1ブロック群が、管理情報を格納するためのブロックとして限定的に割り当てられている。そして、第1ブロック群の中から制御部によって選択された、<u>3個以上かつ</u>第1所定数個未満<u>である</u>第2所定数個のブロックの各々に、同一内容の管理情報が格納されている。従って、第2所定数個のブロックに格納されている第2所定数個の第1管理情報のうちの一つが破壊又は喪失された場合であっても、制御部は、破壊又は喪失されていない残りの第1管理情報を、記憶部から取得することができる。その結果、不良ブロックの存在や強制的な電源遮断等に起因して正常動作が阻害されるという事態を回避しつつ、管理情報を制御対象メモリに格納することが可能となる。

また、第<u>9</u>の態様に係る半導体記憶装置によれば、管理情報は、第1管理情報と、第1管理情報よりも書き換え頻度の高い第2管理情報とを含む。そして、第1管理情報は第1プロック群内に格納され、第2管理情報は第2プロック群内に格納される。書き換え頻度に応じて管理情報を第1管理情報と第2管理情報とに分割し、限定的に割り当てられた第1プロック群内には、書き換え頻度の低い第1管理情報を格納することにより、第1プロック群内ではデータの書き換えが頻繁には発生しない。その結果、第1プロック群内における後天性不良プロックの発生が抑制されるため、装置の信頼性を向上することが可能となる。

また、第<u>9</u>の態様に係る半導体記憶装置によれば、制御部は、第1管理情報を更新する必要が生じた場合には、第1プロック群の中で第2所定数個の空きブロックを確保し、当該第2所定数個の空きブロックの各々に、更新後の第1管理情報をそれぞれ書き込む。これにより、更新後においても、同一内容の第2所定個数の第1管理情報を、第1ブロック群に格納することが可能となる。

また、第<u>9</u>の態様に係る半導体記憶装置によれば、制御部は、第2所定数個の空きブロックの中の一の空きブロックに書き込む第1管理情報に、第2所定数個の空きブロックの中の他の空きブロックを示す位置情報を含めて書き込む。従って、多数決を行う対象を、更新時に併せて書き込まれた同一内容の第1管理情報に限定できるため、多数決によって妥当な第1管理情報を特定できる可能性を高めることが可能となる。

本発明の第<u>10</u>の態様に係る半導体記憶装置は、第<u>9</u>の態様に係る半導体記憶装置において特に、前記制御部は、第1管理情報の誤り検出符号を、第1管理情報に含めて書き込むことを特徴とするものである。

第<u>10</u>の態様に係る半導体記憶装置によれば、制御部は、第1管理情報の誤り検出符号を、第1管理情報に含めて書き込む。従って、誤り検出符号を用いて多数決を行うことができ、その結果、妥当な第1管理情報を適切に特定する精度を向上することが可能となる

10

20

30

40

。また、誤り検出符号を用いてデータの誤りが生じているか否かを判定することができ、 その結果、第1ブロック群の中から正常ブロックを特定する際に、データの誤りが生じて いる異常ブロックを除外することが可能となる。

#### [0047]

本発明の第11の態様に係る半導体記憶装置は、9り以は第100の態様に係る半導体記憶装置において特に、前記制御部は、第1プロック群の中から、先天性不良プロックを除外することにより、空きプロックを確保することを特徴とするものである。

#### [0048]

第<u>11</u>の態様に係る半導体記憶装置によれば、制御部は、第1ブロック群の中から、先天性不良ブロックを除外することにより、空きブロックを確保する。従って、更新後の第1管理情報を書き込むブロックとして、先天性不良ブロックが選択されるという事態を回避することが可能となる。

#### [0049]

本発明の第12の態様に係る半導体記憶装置は、第9~第110いずれか一つの態様に係る半導体記憶装置において特に、前記制御部は、第1プロック群の中から、後天性不良プロックを除外することにより、空きプロックを確保することを特徴とするものである。

#### [0050]

第<u>12</u>の態様に係る半導体記憶装置によれば、制御部は、第1ブロック群の中から、後天性不良ブロックを除外することにより、空きブロックを確保する。従って、更新後の第1管理情報を書き込むブロックとして、後天性不良ブロックが選択されるという事態を回避することが可能となる。

#### [0051]

本発明の第 $\underline{13}$ の態様に係る半導体記憶装置は、第 $\underline{9}$ ~第 $\underline{12}$ のいずれか一つの態様に係る半導体記憶装置において特に、前記制御部は、第 $\underline{17}$ 口ック群の中から、更新前の第 $\underline{1}$ 1管理情報が格納されている第 $\underline{2}$ 1所定数個のブロックを除外することにより、空きブロックを確保することを特徴とするものである。

#### [0052]

第<u>13</u>の態様に係る半導体記憶装置によれば、制御部は、第1ブロック群の中から、更新前の第1管理情報が格納されている第2所定数個のブロックを除外することにより、空きブロックを確保する。従って、第1管理情報の更新処理中にユーザの誤操作等によって強制的に電源が遮断され、それによって更新後の第1管理情報が消去された場合等であっても、更新前の第1管理情報は記憶部内に残されているため、それを用いて再起動を行うことが可能となる。

#### [0053]

本発明の第14の態様に係る半導体記憶装置は、第9~第13のいずれか一つの態様に係る半導体記憶装置において特に、前記制御部は、第2所定数個の空きブロックの中の1個の空きブロックへの第1管理情報の書き込みが完了すると、更新前の第1管理情報が格納されていた第2所定数個のブロックの中の1個のブロックに対して、所定の無効フラグを付加することを特徴とするものである。

#### [0054]

第<u>14</u>の態様に係る半導体記憶装置によれば、制御部は、1個の空きブロックへの第1 管理情報の書き込みが完了すると、更新前の第1管理情報が格納されていた1個のブロッ 10

20

30

40

クに対して、所定の無効フラグを付加する。これにより、第1管理情報が格納されているブロックとして、少なくとも第2所定数個のブロックを常に確保することが可能となる。しかも、データを消去するのではなく無効フラグを付加するため、消去に伴うメモリセルへのストレスを回避できる。その結果、第1ブロック群内における後天性不良ブロックの発生が抑制されるため、装置の信頼性を向上することが可能となる。

#### [0055]

本発明の第15の態様に係る半導体記憶装置は、第9~第13のいずれか一つの態様に係る半導体記憶装置において特に、前記制御部は、第2所定数個の空きブロックの中の1個の空きブロックへの第1管理情報の書き込みが完了すると、更新前の第1管理情報が格納されていた第2所定数個のブロックの中の1個のブロックに対して、データの消去を行うことを特徴とするものである。

10

#### [0056]

第<u>15</u>の態様に係る半導体記憶装置によれば、制御部は、第2所定数個の空きブロックの中の1個の空きブロックへの第1管理情報の書き込みが完了すると、更新前の第1管理情報が格納されていた第2所定数個のブロックの中の1個のブロックに対して、データの消去を行う。これにより、第1管理情報が格納されているブロックとして、少なくとも第2所定数個のブロックを常に確保することが可能となる。

20

#### [0057]

本発明の第<u>16</u>の態様に係る半導体記憶装置は、第1~第<u>15</u>のいずれか一つの態様に係る半導体記憶装置において特に、先天性不良ブロックを除外した第1所定数個のブロックが、第1ブロック群として割り当てられることを特徴とするものである。

#### [0058]

第<u>16</u>の態様に係る半導体記憶装置によれば、先天性不良ブロックを除外した第1所定数個のブロックが、第1ブロック群として割り当てられる。従って、第1ブロック群を構成するブロックとして、必ず第1所定数個のブロックを確保できるため、装置の信頼性を向上することが可能となる。

30

#### 【発明の効果】

#### [0063]

本発明によれば、不良ブロックの存在や強制的な電源遮断等に起因して正常動作が阻害されるという事態を回避しつつ、管理情報を制御対象メモリに格納することが可能な半導体記憶装置を得ることができる。

#### 【図面の簡単な説明】

#### [0064]

- 【図1】本発明の実施の形態1に係る半導体記憶装置の構成を簡略化して示す図である。

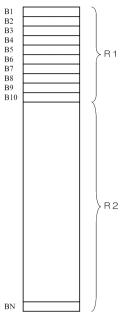

- 【図2】制御対象メモリのメモリ空間の一部を抜き出して示す図である。

40

- 【図3】使用が想定されている制御対象メモリの種類を示す図である。

- 【図4】第1ブロック群を示す図である。

- 【図5】ブロック内のページの割り当てを示す図である。

- 【図6】管理情報の取得処理を順に示す図である。

- 【図7】管理情報の取得処理を順に示す図である。

- 【図8】管理情報の取得処理を順に示す図である。

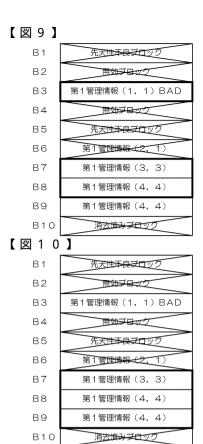

- 【図9】管理情報の取得処理を順に示す図である。

- 【図10】管理情報の取得処理を順に示す図である。

- 【図11】管理情報の取得処理を順に示す図である。

- 【図12】第1管理情報の更新処理を順に示す図である。

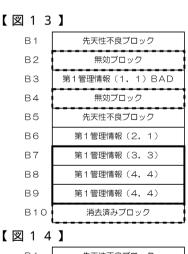

- 【図13】第1管理情報の更新処理を順に示す図である。

- 【図14】第1管理情報の更新処理を順に示す図である。

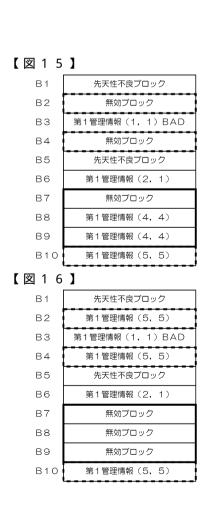

- 【図15】第1管理情報の更新処理を順に示す図である。

- 【図16】第1管理情報の更新処理を順に示す図である。

- 【図17】第1ブロック群の他の例を示す図である。

- 【図18】第1ブロック群の他の例を示す図である。

- 【図19】第1ブロック群を示す図である。

- 【図20】管理情報の取得処理を順に示す図である。

- 【図21】管理情報の取得処理を順に示す図である。

- 【図22】管理情報の取得処理を順に示す図である。

- 【図23】管理情報の取得処理を順に示す図である。

- 【図24】管理情報の取得処理を順に示す図である。

- 【図25】管理情報の取得処理を順に示す図である。

- 【図26】第1管理情報の更新処理を順に示す図である。

- 【図27】第1管理情報の更新処理を順に示す図である。

- 【図28】第1管理情報の更新処理を順に示す図である。

- 【図29】第1管理情報の更新処理を順に示す図である。

- 【図30】第1管理情報の更新処理を順に示す図である。

- 【図31】第1ブロック群の他の例を示す図である。

- 【図32】第1ブロック群の他の例を示す図である。

- 【図33】変形例1に係る半導体記憶装置の構成を簡略化して示す図である。

- 【図34】第2ブロック群の第1の例を示す図である。

- 【図35】第2ブロック群の第2の例を示す図である。

- 【発明を実施するための形態】

#### [0065]

以下、本発明の実施の形態について、図面を用いて詳細に説明する。なお、異なる図面 において同一の符号を付した要素は、同一又は相応する要素を示すものとする。

#### [0066]

#### < 実施の形態 1 >

図1は、本発明の実施の形態1に係る半導体記憶装置1の構成を簡略化して示す図であ る。半導体記憶装置1は、メモリコントローラ2(制御部)と、メモリコントローラ2に よって制御される制御対象メモリ3(記憶部)とを備えている。制御対象メモリ3は、不 揮発性のメモリであり、例えばNAND型フラッシュメモリによって構成されている。

#### [0067]

図2は、制御対象メモリ3のメモリ空間の一部を抜き出して示す図である。メモリ空間 は、複数のブロックB1~BNに分割されている。ブロックは、データの消去の単位であ る。制御対象メモリ3が有する全ブロックB1~BNは、第1ブロック群R1と第2ブロ ック群R2とに分類されている。

#### [0068]

第 1 ブロック群 R 1 は、後述する第 1 管理情報を格納するためのブロックの集合であり 全ブロックB1~BNの中から限定された特定の複数個のブロックが、第1ブロック群 R 1 として割り当てられている。本実施の形態の例では、ブロック B 1 ~ B 1 0 の合計 1 0個のブロックが、第1ブロック群R1として割り当てられている。

#### [0069]

第 2 ブロック群 R 2 は、第 1 ブロック群 R 1 以外のブロックの集合である。第 2 ブロッ ク群R2には、ユーザが使用する任意のデータが格納される。また、第2プロック群R2 には、後述する第2管理情報が格納される。

#### [0070]

管理情報は、メモリコントローラ2が制御対象メモリ3を管理するために必要な情報で あり、本実施の形態の例において、管理情報は第1管理情報と第2管理情報とに分割され 10

20

30

ている。

#### [0071]

第 1 管理情報には、第 2 管理情報を格納しているブロックの所在を示す位置情報が含まれる。位置情報としては、例えばブロックアドレスが用いられる。

#### [0072]

また、第1管理情報には、誤り検出符号が含まれる。誤り検出符号は、その第1管理情報にデータの誤りが生じているか否かの判定に使用される。また、誤り検出符号は、妥当な第1管理情報を特定するための多数決(詳細は後述する)に使用される。誤り検出符号としては、チェックサム、CRC(Cyclic Redundancy Check)、又はメッセージダイジェスト等を使用することができる。本実施の形態の例では、誤り検出符号としてCRCが使用される。

[0073]

また、第1管理情報には、固有のID情報(本明細書において「管理情報ID」と称す)が含まれる。管理情報IDは、第1管理情報のバージョンを示すものであり、第1管理情報が更新される度に管理情報IDの値も更新される。本実施の形態の例では、第1管理情報が更新される度に「1」ずつインクリメントされる整数値が、管理情報IDとして使用される。管理情報IDは、妥当な第1管理情報を特定するための多数決(詳細は後述する)に使用される。

[0074]

また、第1管理情報には、第1ブロック群R1の中に不良ブロックが存在している場合に、その不良ブロックの所在を示す位置情報が含まれる。不良ブロックには、制御対象メモリ3の製造時に発生する先天性不良ブロックと、出荷後の通常使用によって発生する後天性不良ブロックとが含まれる。

[0075]

第1管理情報を更新する場合には、第1ブロック群R1のうち、更新前の第1管理情報を格納しているブロックとは異なるブロックに、更新後の第1管理情報が書き込まれる。書き込み中に該当ブロックが後天性不良ブロックとなった場合には、第1ブロック群R1内の別のブロックに、更新後の第1管理情報が書き込まれる。

[0076]

第2管理情報には、第2ブロック群R2の中に不良ブロックが存在している場合に、その不良ブロックの所在を示す位置情報が含まれる。また、第2管理情報には、汎用領域の場所や制御対象メモリ3へのアクセス速度等の、メモリコントローラ2が制御対象メモリ3を管理するために必要な様々な情報が含まれる。

[0077]

第2管理情報を更新する場合には、第2ブロック群R2のうち、更新前の第2管理情報を格納しているブロックと同一のブロックに、更新後の第2管理情報が上書きされる。書き込み中に該当ブロックが後天性不良ブロックとなった場合には、第2ブロック群R2内の別の任意のブロック(但し不良ブロックは除く)に、更新後の第2管理情報が書き込まれる。第1管理情報には第2管理情報を格納しているブロックの位置情報が含まれているため、第2管理情報を格納するブロックが変更された場合には、第1管理情報を更新する必要がある。

[0078]

各管理情報内に含めている情報の性質上、第2管理情報は第1管理情報よりも更新頻度(書き換え頻度)が高いといえる。例えば、第2ブロック群R2の中のユーザデータ領域内で後天性不良ブロックが発生した場合には、第2管理情報は更新する必要があるが、第1管理情報の更新は不要である。第2ブロック群R2のブロック数は第1ブロック群R1のブロック数よりもはるかに大きいため、第2ブロック群R2内で後天性不良ブロックが発生する確率は、第1ブロック群R1内で後天性不良ブロックが発生する確率よりも十分に高い。従って、第1管理情報は更新せずに第2管理情報を更新するという状況は、逆の状況よりも多く発生する。

10

20

30

40

#### [0079]

図3は、使用が想定されている制御対象メモリ3の種類を示す図である。本実施の形態では、ページサイズ、ブロックサイズ、総ブロック数、読み出しサイクル、及び先天性不良フラグの位置が異なる、複数種類(この例では4種類)のメモリの使用が想定されている。なお、各メモリには、メモリの種類を識別するための固有のID情報(本明細書において「メモリID」と称す)が付与されている。メモリIDには、ページサイズ及びブロックサイズの情報が含まれている。

#### [0800]

以下、本実施の形態に係る半導体記憶装置1に関して、(1)管理情報の格納例、(2)管理情報の取得処理、(3)管理情報の更新処理を、順に説明する。

10

#### [0081]

#### (1)管理情報の格納例

本実施の形態に係る半導体記憶装置 1 では、第 1 ブロック群 R 1 に属する 1 0 個のブロック B 1 ~ B 1 0 の中から選択された 3 個のブロックに、同一内容の第 1 管理情報が格納される。但し、「 1 0 個」及び「 3 個」の値は一例であり、この値には限定されない。

#### [0082]

図4は、第1ブロック群R1を示す図である。この例において、ブロックB1,B5は 先天性不良ブロックであり、ブロックB2,B4は無効ブロック(詳細は後述する)である。

#### [0083]

20

30

ブロック B 3 , B 6 ~ B 9 には第 1 管理情報が格納されている。第 1 管理情報に付した 丸括弧内の数字は、管理情報 I D 値(左側)及び C R C 値(右側)を示している。説明の 便宜上、第 1 管理情報を書き込む際の C R C 値は、管理情報 I D 値と同一の値をとるもの とする。データの誤りが生じていない正常ブロックに関しては、 C R C 値と管理情報 I D 値とは一致し、一方、後天性不良ブロックになったこと等に起因してデータの誤りが生じている異常ブロックに関しては、 C R C 値と管理情報 I D 値とは一致 しない。この例において、ブロック B 6 に格納されている第 1 管理情報 I D 値とが一致していない。従って、ブロック B 6 は後天性不良ブロックである。

#### [0084]

また、図4に示した例では、最新の第1管理情報は第1管理情報(4,4)である。ここで、第1管理情報(4,4)はブロックB8,B9の2個のブロックにしか格納されていないが、その理由は、ブロックB10のデータを消去した後、第1管理情報(4,4)を書き込む前に、ユーザによって電源が強制的に遮断された状況を想定しているためである。従って、ブロックB10は消去済みブロックとなっている。

#### [0085]

また、ブロックB3内に表記している「BAD」は、第1管理情報をブロックB3に書き込む際に、ブロックB3が後天性不良ブロックとなったことを表している。但し、ブロックB3に格納されている第1管理情報(1,1)に関しては、管理情報ID値とCRC値とが一致している。そのため、管理情報ID値とCRC値との比較によっては、ブロックB3が後天性不良ブロックであるとは判定できない。

40

#### [0086]

なお、第1管理情報をブロックに書き込む際にそのブロックが後天性不良ブロックとなった場合には、その第1管理情報に付した管理情報ID値をメモリコントローラが保持しておき、それ以降に第1管理情報を更新する際には、その管理情報ID値を使用しないようにしても良い。これにより、サイクリックカウンタを用いて管理情報ID値を生成する場合に、後天性不良ブロックに格納されている古い第1管理情報と、それ以降に更新された新たな第1管理情報とで、管理情報ID値が偶然に一致するという事態が回避される。

#### [0087]

図 5 は、ブロック B 1 ~ B 1 0 の各ブロックに関して、ブロック内のページの割り当てを示す図である。 1 ブロックは複数のページに分割されている。ページは、データの書き

込み及び読み出しの単位である。この例では、ページ P 0 は先天性不良フラグが付加されるページであり、ページ P N は無効フラグが付加されるページであり、ページ P M は第 1 管理情報が書き込まれるページである。なお、第 1 管理情報はブロック内の複数のページに格納されていても良い。

#### [0088]

あるブロックが先天性不良ブロックである場合には、そのブロックのページ P 0 に先天性不良フラグが付加される。先天性不良フラグが付加されるページは、図 3 に示したように制御対象メモリ 3 の種類によって異なる。

#### [0089]

あるブロックのデータが無効である場合には、そのブロックのページPNに無効フラグが付加される。無効フラグが付加されるページは、制御対象メモリ3の種類によらず共通である。

#### [0090]

(2)管理情報の取得処理

図6~11は、半導体記憶装置1の起動時にメモリコントローラ2が実行する管理情報の取得処理を順に示す図である。第1ブロック群R1は、図4に示した状態になっているものとする。

#### [0091]

まず、メモリコントローラ2は、メモリIDを要求するリードコマンドを制御対象メモリ3に発行することにより、制御対象メモリ3からメモリIDを取得する。メモリIDにはページサイズ及びブロックサイズの情報が含まれているため、メモリIDを取得することにより、制御対象メモリ3内の任意のページへのアクセスが可能となる。

#### [0092]

< 先天性不良ブロックの探索ステップ >

次に図6を参照して、メモリコントローラ2は、第1ブロック群R1に属する全てのブロックB1~B10を対象として、先天性不良ブロックを探索する。具体的には、ブロックB1~B10の各ブロックに関して、先天性不良フラグの格納ページにアクセスすることにより、各ブロックが先天性不良ブロックであるか否かを判定する。

#### [0093]

この時点では制御対象メモリ3の種類が判明していないため、先天性不良フラグの格納ページを一意には特定できない。従って、メモリコントローラ2は、使用が想定されている全種類のメモリに関する先天性不良フラグの格納ページに順にアクセスする。図3に示した例では、メモリコントローラ2は、第0ページの第0バイト、第0ページの第2048バイト、第128ページの第0バイト、及び第256ページの第8192バイトに順にアクセスすることにより、いずれかの格納ページに先天性不良フラグが付加されているか否かを判定する。また、その際の制御対象メモリ3へのアクセス速度は、使用が想定されている全種類のメモリを正常に動作させることが可能な最も遅い速度とする。図3に示した例では、4種類のメモリのうち最も遅い50nsの読み出しサイクルでアクセスを行う

#### [0094]

なお、メモリIDとメモリ種類とを関連付けるテーブル情報を予め作成してメモリコントローラ 2 内に保持しておき、メモリコントローラ 2 が制御対象メモリ 3 からメモリIDを取得した後に当該テーブル情報を参照することにより、メモリ種類を特定するように構成してもよい。この場合には、特定したメモリ種類に対応したアクセス速度で、特定したメモリ種類に対応した格納ページにアクセスすることにより、先天性不良フラグが付加されているか否かを判定することができる。

#### [0095]

探索の結果、ブロックB1~B10内に先天性不良ブロックが存在している場合には、 メモリコントローラ2は、そのブロックを取得対象ブロックの候補から除外する。図6に 示した例では、先天性不良ブロックであるブロックB1,B5が候補から除外される。こ 10

20

30

40

のステップで除外されずに残ったブロック B 2 ~ B 4 , B 6 ~ B 1 0 を、本明細書において「良ブロック」と称す。

#### [0096]

< 無効ブロックの探索ステップ >

次に図 7 を参照して、メモリコントローラ 2 は、良ブロック B 2 ~ B 4 , B 6 ~ B 1 0 を対象として、無効ブロックを探索する。具体的には、各良ブロックに関して、無効フラグの格納ページ(図 5 に示したページ P N)にアクセスすることにより、各良ブロックが無効ブロックであるか否かを判定する。

#### [0097]

上記と同様に、制御対象メモリ3へのアクセス速度は、使用が想定されている全種類のメモリを正常に動作させることが可能な最も遅い速度とする。但し、メモリIDに基づいてメモリ種類を特定できる場合には、特定したメモリ種類に対応した適切なアクセス速度でアクセスすればよい。

#### [0098]

探索の結果、良ブロック内に無効ブロックが存在している場合には、メモリコントローラ2は、そのブロックを取得対象ブロックの候補から除外する。図7に示した例では、無効ブロックであるブロックB2,B4が候補から除外される。このステップで除外されずに残ったブロックB3,B6~B10を、本明細書において「有効ブロック」と称す。

#### [0099]

< 異常ブロックの探索ステップ >

次に図8を参照して、メモリコントローラ2は、有効ブロックB3,B6~B10を対象として、データの誤りが生じているブロックを探索する。具体的には、各有効ブロックに関して、第1管理情報の格納ページ(図5に示したページPM)にアクセスして第1管理情報を読み出し、読み出した第1管理情報に対してCRC演算を行う。そして、演算により求めたCRC値と、読み出した第1管理情報内に含まれているCRC値とを比較する。メモリコントローラ2は、両CRC値が一致する場合には、そのブロックはデータの誤りが生じていないブロック(本明細書において「正常ブロック」と称す)であると判定し、一方、両CRC値が一致しない場合には、そのブロックはデータの誤りが生じているブロック(本明細書において「異常ブロック」と称す)であると判定する。

- ・書き込み又は消去時に後天性不良ブロックとなった

- ・書き込み又は消去時に電源が強制遮断されたことにより正常に終了されなかった

- ・消去状態でデータが何も書き込まれていない

等の理由で両CRC値が一致しない場合には、そのブロックは異常ブロックと判定されることとなる。

#### [0100]

上記と同様に、制御対象メモリ3へのアクセス速度は、使用が想定されている全種類のメモリを正常に動作させることが可能な最も遅い速度とする。但し、メモリIDに基づいてメモリ種類を特定できる場合には、特定したメモリ種類に対応した適切なアクセス速度でアクセスすればよい。

#### [0101]

探索の結果、有効ブロック内に異常ブロックが存在している場合には、メモリコントローラ2は、そのブロックを取得対象ブロックの候補から除外する。図8に示した例では、 異常ブロックであるブロックB6,B10が候補から除外される。

#### [0102]

<妥当な第1管理情報の特定ステップ>

次に、メモリコントローラ 2 は、残った正常ブロックの中から 4 個の正常ブロックを任意に選択する。例えば、ブロックアドレスの小さい順に 4 個の正常ブロックを選択する。この例では残った正常ブロックがブロック B 3 , B 7 ~ B 9 の 4 個であるため、全ての正常ブロックが選択される。なお、この時点で残った正常ブロックが 2 個以下である場合は、後述する多数決を行えないため、その制御対象メモリ 3 は故障であると判定する。また

10

20

30

40

、この時点で残った正常ブロックが3個である場合は、後述する多数決を1回だけ行う。

#### [0103]

次に図9を参照して、メモリコントローラ2は、選択した4個の正常ブロックB3,B7~B9の中から、3個の正常ブロックを任意に選択する。この例では、ブロックアドレスの小さい順に3個の正常ブロックB3,B7,B8を選択する。そして、各正常ブロックB3,B7,B8に格納されている第1管理情報に含まれている管理情報ID値及びCRC値を相互に比較することにより、1回目の多数決を行う。メモリコントローラ2は、3個の第1管理情報のうちの2個以上で管理情報ID値及びCRC値が一致した場合には、その第1管理情報は妥当であると判定する。この例では、3個の第1管理情報の管理情報ID値及びCRC値はそれぞれ(1,1)(3,3)(4,4)であり、相互に一致しないため、妥当な第1管理情報はないと判定される。

[0104]

次に図10を参照して、メモリコントローラ2は、選択した4個の正常ブロックB3,B7~B9の中から、他の3個の正常ブロックを任意に選択する。この例では、ブロックアドレスの大きい順に3個の正常ブロックB7~B9を選択する。そして、各正常ブロックB7~B9に格納されている第1管理情報に含まれている管理情報ID値及びCRC値を相互に比較することにより、2回目の多数決を行う。この例では、3個の第1管理情報の管理情報ID値及びCRC値はそれぞれ(3,3)(4,4)(4,4)であり、(4,4)が2個以上で一致する。従って、ブロックB8,B9に格納されている第1管理情報が、妥当な第1管理情報であると判定される。

[0105]

なお、1回目の多数決によって妥当な第1管理情報を特定できた場合には、2回目の多数決は省略される。また、2回目の多数決によっても妥当な第1管理情報を特定できない場合には、その制御対象メモリ3は故障と判定される。但し、正常ブロックが5個以上残っている場合には、4個の正常ブロックの選択をやり直して、再び多数決を行っても良い

[0106]

<第2管理情報の取得ステップ>

次に図11を参照して、メモリコントローラ2は、特定した2個以上の妥当な第1管理情報の中から、任意の1個の第1管理情報を確定する。例えば、ブロックB8,B9の中でブロックアドレスの最も小さいブロックB8を選択し、ブロックB8に格納されている第1管理情報(4,4)を、妥当な第1管理情報として確定する。

[0107]

次に、メモリコントローラ 2 は、確定した妥当な第 1 管理情報に含まれている位置情報 (第 2 管理情報を格納しているブロックの所在を示す位置情報)に基づいて、第 2 ブロッ ク群 R 2 の中から第 2 管理情報を読み出すことにより、第 2 管理情報を取得する。

[0108]

(3)管理情報の更新処理

第2管理情報の格納ブロックが後天性不良ブロックとなった場合等には、第2管理情報の格納ブロックを、第2ブロック群R2内の他のブロックに変更する必要がある。ここで、第1管理情報には第2管理情報の格納ブロックの位置情報が含まれているため、第2管理情報の格納ブロックを変更する場合には、第1管理情報の内容も更新する必要がある。また、第1管理情報には第1ブロック群R1の不良ブロックの位置情報が含まれているため、第1ブロック群R1内で後天性不良ブロックが発生した場合等には、第1管理情報の内容を更新する必要がある。以下、第1管理情報を更新する手順について説明する。

[0109]

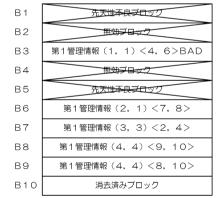

図 1 2 ~ 1 6 は、メモリコントローラ 2 が実行する第 1 管理情報の更新処理を順に示す図である。

[0110]

図12を参照して、現在有効な第1管理情報(つまり更新前の第1管理情報)は、ブロ

20

10

30

40

10

20

30

40

50

ック B 8 , B 9 に格納されている第 1 管理情報(4 , 4 ) である。また、起動時に妥当な第 1 管理情報を特定するための多数決の候補となった第 1 管理情報は、ブロック B 7 ~ B 9 に格納されている第 1 管理情報である。以下、ブロック B 7 ~ B 9 を「多数決対象ブロック」と称す。

#### [0111]

次に図13を参照して、メモリコントローラ2は、第1ブロック群R1の中から、更新後の第1管理情報を格納すべき空きブロックを確保する。具体的には、ブロックB1~B10の中から、先天性不良ブロック、後天性不良ブロック、及び多数決対象ブロックを除外して、3個の空きブロックを確保する。第1管理情報には第1ブロック群R1内の不良ブロックの位置情報が含まれているため、現在有効な第1管理情報(4,4)を参照することにより、第1ブロック群R1内の先天性不良ブロック及び後天性不良ブロックを特定することができる。この例では、無効ブロックであるブロックB2,B4と、消去済みブロックであるブロックB10とが、空きブロックとして確保される。なお、確保できる空きブロックが2個以下である場合は、その制御対象メモリ3は故障であると判定される。

#### [0112]

次に図14を参照して、メモリコントローラ2は、3個の空きブロックの中の任意の1個の空きブロックのデータを消去した後、更新後の第1管理情報(5,5)をそのブロックに書き込む。この例では、ブロックB10のデータが消去された後に、第1管理情報(5,5)がブロックB10に書き込まれる。なお、空きブロックのデータを消去する際、又は第1管理情報(5,5)を書き込む際に、該当ブロックが後天性不良ブロックとなった場合には、メモリコントローラ2は、第1管理情報に含まれている不良ブロックの位置情報を更新するとともに、空きブロックの確保処理からやり直す。

#### [0113]

次に図15を参照して、メモリコントローラ2は、3個の多数決対象ブロックの中の任意の1個のブロックに対して、無効フラグを付加する。この例では、ブロックB7に無効フラグが付加される。なお、無効フラグを付加する際に該当ブロックが後天性不良ブロックとなった場合には、メモリコントローラ2は、第1管理情報に含まれている不良ブロックの位置情報を更新するとともに、空きブロックの確保処理からやり直す。

#### [0114]

次に図16を参照して、メモリコントローラ2は、3個の空きブロックの中の次の空きブロックB2のデータを消去した後、第1管理情報(5,5)をそのブロックB2に書き込む。その後、3個の多数決対象ブロックの中の次のブロックB8に対して、無効フラグを付加する。次に、メモリコントローラ2は、3個の空きブロックの中の最後の空きブロックB4のデータを消去した後、第1管理情報(5,5)をそのブロックB4に書き込む。その後、3個の多数決対象ブロックの中の最後のブロックB9に対して、無効フラグを付加する。これにより、3個の空きブロックB2,B4,B10に同一内容の第1管理情報(5,5)が格納される。

### [0115]

なお、多数決対象ブロック B 7 ~ B 9 に無効フラグを付加する代わりに、データの消去を行っても良い。この場合、 1 個の空きブロックへの第 1 管理情報の書き込みと、 1 個の多数決対象ブロックに対するデータの消去とが、交互に 3 回繰り返されることとなる。

#### [0116]

<実施の形態1の具体例1>

図17は、第1ブロック群R1の他の例を示す図である。この例において、ブロックB5,B9は先天性不良ブロックであり、ブロックB1,B2,B10は無効ブロックである。また、ブロックB4,B8に関しては管理情報ID値とCRC値とが一致している。また、ブロックB3,B6,B7には、第1管理情報(6,6)が格納されている。

#### [0117]

図17に示した第1ブロック群R1を対象とした管理情報の取得処理について、簡単に

説明する。まず、先天性不良ブロックであるブロックB5,B9が除外される。次に、無効ブロックであるブロックB1,B2,B10が除外される。次に、異常ブロックの探索が行われるが、この例では異常ブロックが存在しないため、異常ブロックとしてはどのブロックも除外されない。次に、4個の正常ブロックとしてブロックB3,B4,B6,B7が選択される。

#### [0118]

次に、先頭3個の正常ブロックB3,B4,B6を対象とする1回目の多数決が行われ、その結果、ブロックB3,B6に格納されている第1管理情報(6,6)が妥当な第1管理情報として特定される。

#### [0119]

次に、ブロック B 3 , B 6 のいずれかに格納されている第 1 管理情報 ( 6 , 6 ) に基づいて、第 2 ブロック群 R 2 の中から第 2 管理情報が読み出される。

#### [0120]

<実施の形態1の具体例2>

図18は、第1ブロック群R1の他の例を示す図である。この例において、ブロックB5,B9は先天性不良ブロックであり、ブロックB1,B2,B10は無効ブロックである。また、ブロックB4,B6は後天性不良ブロックである。但し、ブロックB4,B6に関しては管理情報ID値とCRC値とが一致している。また、ブロックB3,B7,B8には、第1管理情報(7,7)が格納されている。

#### [0121]

図18に示した第1ブロック群R1を対象とした管理情報の取得処理について、簡単に説明する。まず、先天性不良ブロックであるブロックB5,B9が除外される。次に、無効ブロックであるブロックB1,B2,B10が除外される。次に、異常ブロックの探索が行われるが、この例では異常ブロックが存在しないため、異常ブロックとしてはどのブロックも除外されない。次に、4個の正常ブロックとしてブロックB3,B4,B6,B7が選択される。

#### [0122]

次に、先頭3個の正常ブロックB3,B4,B6を対象とする1回目の多数決が行われるが、多数決が成立しないため、妥当な第1管理情報はないと判定される。

#### [0123]

次に、末尾3個の正常ブロックB4,B6,B7を対象とする2回目の多数決が行われるが、多数決が成立しないため、妥当な第1管理情報はないと判定される。その結果、その制御対象メモリ3は故障であると判定される。

#### [0124]

< 実施の形態 2 >

以下、本発明の実施の形態 2 に係る半導体記憶装置 1 について、上記実施の形態 1 との相違点を中心に説明する。

#### [0125]

上記実施の形態1と同様に、第1管理情報には、第2管理情報の格納ブロックを示す位置情報が含まれる。また、第1管理情報には、管理情報IDが含まれる。また、第1管理情報には、第1ブロック群R1内の不良ブロックを示す位置情報が含まれる。

#### [0126]

また、本実施の形態では、上記に加えて、第1管理情報には、自身と同一内容の第1管理情報が格納された他の2個のブロックを示す位置情報(本明細書において「グループアドレス」と称す)が含まれる。

#### [0127]

さらに、第1管理情報には、誤り検出符号が含まれる。本実施の形態の例では、グループアドレスを含めた全域のCRC値と、グループアドレスを除いた部分のCRC値とが、第1管理情報内に含められる。グループアドレスを含めた全域のCRC値は、その第1管理情報にデータの誤りが生じているか否かの判定に使用される。また、グループアドレス

10

20

30

40

を除いた部分のCRC値は、妥当な第1管理情報を特定するための多数決に使用される。

#### [0128]

以下、本実施の形態に係る半導体記憶装置1に関して、(1)管理情報の格納例、(2) 管理情報の取得処理、(3)管理情報の更新処理を、順に説明する。

#### [0129]

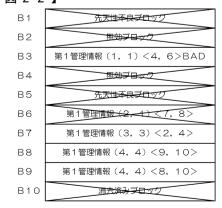

(1)管理情報の格納例

図19は、第1ブロック群R1を示す図である。この例において、ブロックB1,B5 は先天性不良ブロックであり、ブロックB2,B4は無効ブロックであり、ブロックB1 0は消去済みブロックである。

#### [0130]

ブロック B 3 , B 6 ~ B 9 には第 1 管理情報が格納されている。第 1 管理情報に付した 丸括弧内の数字は、管理情報 I D 値及び C R C 値を示している。第 1 管理情報に付した山 括弧内の数字は、グループアドレスを示している。例えば、ブロック B 7 に第 1 管理情報 (3,3)を書き込む際に、ブロック B 2 , B 4 にも同一内容の第 1 管理情報(3,3) が書き込まれたことを意味している。

#### [0131]

(2)管理情報の取得処理

図 2 0 ~ 2 5 は、半導体記憶装置 1 の起動時にメモリコントローラ 2 が実行する管理情報の取得処理を順に示す図である。第 1 ブロック群 R 1 は、図 1 9 に示した状態になっているものとする。

#### [0132]

まず、メモリコントローラ2は、メモリIDを要求するリードコマンドを制御対象メモリ3に発行することにより、制御対象メモリ3からメモリIDを取得する。

#### [0133]

< 先天性不良ブロックの探索ステップ >

次に図20を参照して、メモリコントローラ2は、第1ブロック群R1に属する全てのブロックB1~B10を対象として、先天性不良ブロックを探索する。

#### [0134]

探索の結果、ブロック B 1 ~ B 1 0 内に先天性不良ブロックが存在している場合には、メモリコントローラ 2 は、そのブロックを取得対象ブロックの候補から除外する。図 2 0 に示した例では、先天性不良ブロックであるブロック B 1 , B 5 が候補から除外される。

#### [0135]

<無効ブロックの探索ステップ>

次に図21を参照して、メモリコントローラ2は、良ブロックB2~B4,B6~B10を対象として、無効ブロックを探索する。

#### [0136]

探索の結果、良ブロック内に無効ブロックが存在している場合には、メモリコントローラ2は、そのブロックを取得対象ブロックの候補から除外する。図21に示した例では、無効ブロックであるブロックB2,B4が候補から除外される。

#### [0137]

< 異常ブロックの探索ステップ >

次に図22を参照して、メモリコントローラ2は、有効ブロックB3,B6~B10を対象として、データの誤りが生じているブロックを探索する。具体的には、各有効ブロックに関して、第1管理情報の格納ページにアクセスして第1管理情報を読み出し、グループアドレスを含めた第1管理情報の全域に対してCRC演算を行う。そして、演算により求めた全域のCRC値と、読み出した第1管理情報内に含まれている全域のCRC値とを比較する。メモリコントローラ2は、両CRC値が一致する場合には、そのブロックは正常ブロックであると判定し、一方、両CRC値が一致しない場合には、そのブロックは異常ブロックであると判定する。

#### [0138]

10

20

30

30

40

探索の結果、有効ブロック内に異常ブロックが存在している場合には、メモリコントローラ2は、そのブロックを取得対象ブロックの候補から除外する。図22に示した例では、異常ブロックであるブロックB6,B10が候補から除外される。

#### [0139]

<妥当な第1管理情報の特定ステップ>

次に図23を参照して、メモリコントローラ2は、残った正常プロックB3,B7~B9の中から1個の正常プロックを任意に選択する。例えば、プロックアドレスが最も小さい正常プロックB3を選択する。そして、正常プロックB3に格納されている第1管理情報に含まれているグループアドレス<4,6>を参照することにより、プロックB3,B4,B6に格納されている第1管理情報に含まれている管理情報ID値及びCRC値(グループアドレスを除いた部分のCRC値)を相互に比較することにより、1回目の多数決を行う。この例では、プロックB4,B6は正常プロックではなく、多数決の候補から除外されるため、1回目の多数決は成立しない。

#### [0140]

次に図24を参照して、メモリコントローラ2は、正常ブロックB3,B7~B9の中から次の正常ブロックを任意に選択する。例えば、ブロックアドレスが次に小さい正常ブロックB7を選択する。そして、正常ブロックB7に格納されている第1管理情報に含まれているグループアドレス<2,4>を参照することにより、ブロックB2,B4,B7を対象とする多数決を行う。具体的には、各ブロックB2,B4,B7に格納されている第1管理情報に含まれている管理情報ID値及びCRC値(グループアドレスを除いた部分のCRC値)を相互に比較することにより、2回目の多数決を行う。この例では、ブロックB2,B4は正常ブロックではなく、多数決の候補から除外されるため、2回目の多数決は成立しない。

#### [0141]

次に図25を参照して、メモリコントローラ2は、正常ブロックB3,B7~B9の中から次の正常ブロックを任意に選択する。例えば、ブロックアドレスが次に小さい正常ブロックB8を選択する。そして、正常ブロックB8に格納されている第1管理情報に含まれているグループアドレス<9,10>を参照することにより、ブロックB8~B10を対象とする多数決を行う。具体的には、各ブロックB8~B10に格納されている第1管理情報に含まれている管理情報ID値及びCRC値(グループアドレスを除いた部分のCRC値)を相互に比較することにより、3回目の多数決を行う。この例では、ブロックB10は正常ブロックではないため多数決の候補から除外されるが、ブロックB8,B9に格納されている2個の第1管理情報の管理情報ID値及びCRC値はいずれも(4,4)であり、2個以上で一致する。従って、ブロックB8,B9に格納されている第1管理情報が、妥当な第1管理情報であると判定される。

#### [0142]

なお、全ての正常ブロック B 3 , B 7 ~ B 9 を選択しても妥当な第 1 管理情報を特定できない場合には、その制御対象メモリ 3 は故障と判定される。

#### [0143]

<第2管理情報の取得ステップ>

次に、メモリコントローラ2は、特定した2個以上の妥当な第1管理情報の中から、任意の1個の第1管理情報を確定する。例えば、ブロックB8,B9の中でブロックアドレスの最も小さいブロックB8を選択し、ブロックB8に格納されている第1管理情報(4,4)を、妥当な第1管理情報として確定する。

#### [0144]

次に、メモリコントローラ 2 は、確定した妥当な第 1 管理情報に含まれている位置情報に基づいて、第 2 ブロック群 R 2 の中から第 2 管理情報を読み出すことにより、第 2 管理情報を取得する。

#### [0145]

50

10

20

30

#### (3)管理情報の更新処理

図 2 6 ~ 3 0 は、メモリコントローラ 2 が実行する第 1 管理情報の更新処理を順に示す図である。

#### [0146]

図26を参照して、現在有効な第1管理情報は、ブロックB8,B9に格納されている第1管理情報(4,4)である。また、起動時に妥当な第1管理情報を特定するための多数決の候補となった第1管理情報は、多数決対象ブロックB8~B10に格納されている第1管理情報である。

#### [0147]

次に図27を参照して、メモリコントローラ2は、第1ブロック群R1の中から空きブロックを確保する。具体的には、ブロックB1~B10の中から、先天性不良ブロック、後天性不良ブロック、及び多数決対象ブロックを除外して、3個の空きブロックを確保する。この例では、ブロックB2,B4,B7が、空きブロックとして確保される。

#### [0148]

次に図28を参照して、メモリコントローラ2は、3個の空きブロックの中の任意の1個の空きブロックのデータを消去した後、グループアドレスを含む更新後の第1管理情報をそのブロックに書き込む。この例では、ブロックB2のデータが消去された後に、ブロックB4,B7を示すグループアドレス<4,7>を含む第1管理情報(5,5)<4,7>が、ブロックB2に書き込まれる。

#### [0149]

次に図29を参照して、メモリコントローラ2は、3個の多数決対象ブロックの中の任意の1個のブロックに対して、無効フラグを付加する。この例では、ブロックB8に無効フラグが付加される。

#### [ 0 1 5 0 ]

次に図30を参照して、メモリコントローラ2は、3個の空きブロックの中の次の空きブロックB4のデータを消去した後、グループアドレス<2,7>を含む第1管理情報(5,5)<2,7>を、そのブロックB4に書き込む。その後、3個の多数決対象ブロックの中の次のブロックB9に対して、無効フラグを付加する。次に、メモリコントローラ2は、3個の空きブロックの中の最後の空きブロックB7のデータを消去した後、グループアドレス<2,4>を含む第1管理情報(5,5)<2,4>を次そのブロックB7に書き込む。その後、3個の多数決対象ブロックの中の最後のブロックB10に対して、無効フラグを付加する。これにより、3個の空きブロックB2,B4,B7に同一内容の第1管理情報(5,5)が格納される。

#### [0151]

< 実施の形態2の具体例1 >

図 3 1 は、第 1 ブロック群 R 1 の他の例を示す図である。この例において、ブロック B 5 , B 9 は先天性不良ブロックであり、ブロック B 1 , B 2 , B 1 0 は無効ブロックである。また、ブロック B 4 , B 8 は後天性不良ブロックである。但し、ブロック B 4 , B 8 に関しては管理情報 I D 値と C R C 値とが一致している。また、ブロック B 3 には第 1 管理情報 (6 , 6 ) <6 , 7 > が格納されており、ブロック B 6 には第 1 管理情報 (6 , 6 ) <3 , 7 > が格納されており、ブロック B 7 には第 1 管理情報 (6 , 6 ) <3 , 6 > が格納されている。

#### [0152]

図31に示した第1ブロック群R1を対象とした管理情報の取得処理について、簡単に説明する。まず、先天性不良ブロックであるブロックB5,B9が除外される。次に、無効ブロックであるブロックB1,B2,B10が除外される。次に、異常ブロックの探索が行われるが、この例では異常ブロックが存在しないため、異常ブロックとしてはどのブロックも除外されない。

#### [0153]

次に、先頭の正常ブロックB3が選択され、その正常ブロックB3と、グループアドレ

20

10

30

40

ス < 6 , 7 > で示された正常プロック B 6 , B 7 とを対象とする多数決が行われる。その結果、プロック B 3 , B 6 , B 7 に格納されている第 1 管理情報(6 , 6 ) が妥当な第 1 管理情報として特定される。

#### [0154]

次に、ブロック B 3 , B 6 , B 7 のいずれかに格納されている第 1 管理情報 ( 6 , 6 ) に基づいて、第 2 ブロック群 R 2 の中から第 2 管理情報が読み出される。

#### [0155]

< 実施の形態2の具体例2>

図 3 2 は、第 1 ブロック群 R 1 の他の例を示す図である。この例において、ブロック B 5 , B 9 は先天性不良ブロックであり、ブロック B 1 , B 2 , B 1 0 は無効ブロックである。また、ブロック B 4 , B 6 は後天性不良ブロックである。但し、ブロック B 4 , B 6 に関しては管理情報 I D 値と C R C 値とが一致している。また、ブロック B 3 には第 1 管理情報 (7 , 7 ) < 7 , 8 > が格納されており、ブロック B 7 には第 1 管理情報 (7 , 7 ) < 3 , 8 > が格納されており、ブロック B 8 には第 1 管理情報 (7 , 7 ) < 3 , 7 > が格納されている。

#### [0156]

図32に示した第1ブロック群R1を対象とした管理情報の取得処理について、簡単に説明する。まず、先天性不良ブロックであるブロックB5,B9が除外される。次に、無効ブロックであるブロックB1,B2,B10が除外される。次に、異常ブロックの探索が行われるが、この例では異常ブロックが存在しないため、異常ブロックとしてはどのブロックも除外されない。

#### [0157]

次に、先頭の正常ブロックB3が選択され、その正常ブロックB3と、グループアドレス < 7 , 8 > で示された正常ブロックB7 , B8とを対象とする多数決が行われる。その結果、ブロックB3 , B7 , B8に格納されている第1管理情報(7 , 7)が妥当な第1管理情報として特定される。

#### [0158]

次に、ブロック B 3 , B 7 , B 8 のいずれかに格納されている第 1 管理情報 ( 7 , 7 ) に基づいて、第 2 ブロック群 R 2 の中から第 2 管理情報が読み出される。

#### [0159]

同様のケースである上記実施の形態1の具体例2(図18)では、妥当な第1管理情報を特定できなかった。これに対して図32の例では、グループアドレスに基づく多数決を行うことによって、妥当な第1管理情報の特定に成功している。

#### [0160]

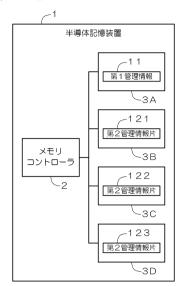

< 変形例 1 >

図33は、変形例1に係る半導体記憶装置1の構成を簡略化して示す図である。半導体記憶装置1は、メモリコントローラ2と、メモリコントローラ2によって制御される複数個の制御対象メモリ(図33の例では4個の制御対象メモリ3A~3D)とを備えている

#### [0161]

このようなシステム構成においては、データサイズが大きい第2管理情報を複数に分割し、各分割片を複数の制御対象メモリに分散して格納しても良い。図33に示した例では、第2管理情報は、3個の第2管理情報片121~123に分割されている。第1管理情報11は制御対象メモリ3Aに格納され、第2管理情報片121は制御対象メモリ3Bに格納され、第2管理情報片122は制御対象メモリ3Cに格納され、第2管理情報片121は制御対象メモリ3Bに格納される。第1管理情報11には、各第2管理情報片121~123の所在を示す位置情報が含まれている。第2管理情報を読み出す場合には、第2管理情報片121~123が制御対象メモリ3B~3Dから並列に読み出される。

#### [0162]

<変形例2>

10

20

30

40

上記実施の形態 1 , 2 では、管理情報を第 1 管理情報と第 2 管理情報とに分割する例について述べたが、管理情報を分割せず、第 2 管理情報の内容を第 1 管理情報内に含めても良い。管理情報のデータサイズが大きくなるため、第 1 ブロック群 R 1 として多数のブロックを割り当てる余裕がある場合に有効である。

#### [0163]

#### < 変形例 3 >

上記実施の形態 1 , 2 では、管理情報を第 1 管理情報と第 2 管理情報との 2 つに分割する例について述べたが、 3 つ以上に分割しても良い。例えば 3 つに分割する場合には、書き換え頻度が低い情報を第 1 管理情報内に含め、書き換え頻度が中程度の情報を第 2 管理情報内に含め、書き換え頻度が高い情報を第 3 管理情報内に含める。第 1 管理情報は、割り当てられるブロック数が少ない第 1 ブロック群内に格納し、第 2 管理情報は、割り当てられるブロック数が多い第 2 ブロック群内に格納し、第 3 管理情報は、全ブロックのうち第 1 ブロック群及び第 2 ブロック群以外の第 3 ブロック群内(ブロック数は最も多い)に格納する。

#### [0164]

#### < 変形例 4 >

上記実施の形態 1 , 2 では、第 1 ブロック群 R 1 として割り当てられるブロックは、ブロック B 1 ~ B 1 0 に限定されている。従って、ブロック B 1 ~ B 1 0 内に先天性不良ブロックが存在している場合には、第 1 ブロック群 R 1 内で実際に使用できるブロック数は、先天性不良ブロックの数に応じて減少する。そこで、第 1 ブロック群を割り当てる際に先天性不良ブロックを除外してもよい。例えばブロック B 5 , B 9 が先天性不良ブロックである場合には、ブロック B 1 ~ B 4 , B 6 ~ B 8 , B 1 0 ~ B 1 2 を第 1 ブロック群として割り当てる。

#### [ 0 1 6 5 ]

#### < 変形例 5 >

上記実施の形態 1 , 2 では、第 2 ブロック群 R 2 に 1 個の第 2 管理情報を格納する例について述べたが、第 2 ブロック群 R 2 に複数個の第 2 管理情報を格納しても良い。

#### [0166]

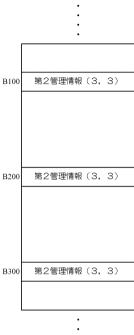

図34は、第2ブロック群R2の第1の例を示す図である。この例では、第2ブロック群R2に属する全てのブロックの中から任意に選択された3個のブロックに、同一内容の第2管理情報が格納される。但し、「3個」の値は一例であり、この値には限定されない

#### [0167]

第2管理情報には、不良ブロックの所在を示す位置情報に加えて、管理情報IDが含まれる。管理情報IDは、第2管理情報のバージョンを示すものであり、第2管理情報が更新される度に管理情報IDの値も更新される。この例では、第2管理情報が更新される度に「1」ずつインクリメントされる整数値が、管理情報IDとして使用される。また、第2管理情報には、誤り検出符号が含まれる。この例では、誤り検出符号としてCRCが使用される。

#### [0168]

図34に示した例では、第2管理情報はブロックB100,B200,B300に格納されている。第2管理情報に付した丸括弧内の数字は、第2管理情報の管理情報ID値(左側)及びCRC値(右側)を示している。説明の便宜上、第2管理情報を書き込む際のCRC値は、第2管理情報の管理情報ID値と同一の値をとるものとする。データの誤りが生じていない正常ブロックに関しては、CRC値と管理情報ID値とは一致し、一方、後天性不良ブロックになったこと等に起因してデータの誤りが生じている異常ブロックに関しては、CRC値と管理情報ID値とは一致しない。

#### [0169]

図34には示さないが、第1管理情報には、第2管理情報を格納している3個のブロックB100,B200,B300の所在を示す3個の位置情報が含まれている。

10

20

30

40

#### [0170]

メモリコントローラ 2 は、妥当な第 1 管理情報を確定すると、確定した第 1 管理情報に含まれている 3 個の位置情報の中から、任意の 1 個の位置情報を選択する。例えば、ブロックアドレスが最も小さいブロック B 1 0 0 を示す位置情報を選択する。

#### [0171]

次に、メモリコントローラ2は、ブロックB100から第2管理情報を読み出し、読み出した第2管理情報に対してCRC演算を行う。そして、演算により求めたCRC値と、読み出した第2管理情報内に含まれているCRC値とを比較する。メモリコントローラ2は、両CRC値が一致する場合には、ブロックB100は正常ブロックであると判定し、ブロックB100から読み出した第2管理情報を妥当な第2管理情報として取得する。

[0172]

一方、両CRC値が一致しない場合には、ブロックB100は異常ブロックであると判定し、3個の位置情報の中から次の位置情報を選択する。例えば、ブロックアドレスが次に小さいブロックB200を示す位置情報を選択する。そして、上記と同様に、ブロックB200から第2管理情報を読み出して、ブロックB200が正常ブロックであるか異常ブロックであるかを判定する。

#### [0173]

ブロック B 2 0 0 が正常ブロックである場合には、メモリコントローラ 2 は、ブロック B 2 0 0 から読み出した第 2 管理情報を妥当な第 2 管理情報として取得する。一方、ブロック B 2 0 0 が異常ブロックである場合には、メモリコントローラ 2 は、 3 個の位置情報の中からブロック B 3 0 0 を示す位置情報を選択する。そして、上記と同様に、ブロック B 3 0 0 から第 2 管理情報を読み出して、ブロック B 3 0 0 が正常ブロックであるか異常ブロックであるかを判定する。ブロック B 3 0 0 が正常ブロックである場合には、メモリコントローラ 2 は、ブロック B 3 0 0 が異常ブロックである場合には、メモリコントローラ 2 は、その制御対象メモリ 3 は故障であると判定する。

#### [0174]

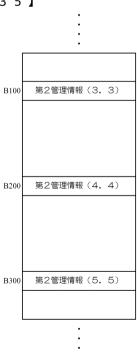

図35は、第2ブロック群R2の第2の例を示す図である。この例では、第2ブロック群R2に属する全てのブロックの中から任意に選択された3個のブロックに、バージョンが異なる3個の第2管理情報が格納される。但し、「3個」の値は一例であり、この値には限定されない。

#### [0175]

図35に示した例では、ブロックB100に第2管理情報(3,3)が格納され、ブロックB200に第2管理情報(4,4)が格納され、ブロックB300に第2管理情報(5,5)が格納されている。

#### [0176]

メモリコントローラ 2 は、妥当な第 1 管理情報を確定すると、確定した第 1 管理情報に含まれている 3 個の位置情報に基づいて、ブロック B 1 0 0 , B 2 0 0 , B 3 0 0 から 3 個の第 2 管理情報を読み出す。そして、各第 2 管理情報に含まれている管理情報 I D 値を比較することにより、最新バージョンの第 2 管理情報を選択する。この例では、ブロック B 3 0 0 から読み出した第 2 管理情報(5 , 5 )が、最新バージョンの第 2 管理情報として選択される。

#### [0177]

次に、メモリコントローラ 2 は、選択した第 2 管理情報に対して C R C 演算を行う。そして、演算により求めた C R C 値と、選択した第 2 管理情報内に含まれている C R C 値とを比較する。メモリコントローラ 2 は、両 C R C 値が一致する場合には、ブロック B 3 0 0 から読み出した第 2 管理情報を妥当な第 2 管理情報として取得する。

#### [0178]

一方、両CRC値が一致しない場合には、ブロックB300は異常ブロックであると判

10

20

30

40

定し、読み出した3個の第2管理情報の中から、次に新しい第2管理情報を選択する。この例では、ブロックB200から読み出した第2管理情報(4,4)が選択される。そして、上記と同様に、ブロックB200が正常ブロックであるか異常ブロックであるかを判定する。

#### [0179]

ブロック B 2 0 0 が正常ブロックである場合には、メモリコントローラ 2 は、ブロック B 2 0 0 から読み出した第 2 管理情報を妥当な第 2 管理情報として取得する。一方、ブロック B 2 0 0 が異常ブロックである場合には、メモリコントローラ 2 は、ブロック B 1 0 0 から読み出した第 2 管理情報を選択する。そして、上記と同様に、ブロック B 1 0 0 が正常ブロックであるか異常ブロックであるかを判定する。ブロック B 1 0 0 が正常ブロックである場合には、メモリコントローラ 2 は、ブロック B 1 0 0 が異常ブロックである場合には、メモリコントローラ 2 は、その制御対象メモリ 3 は故障であると判定する。

#### [0180]

なお、以上の説明では管理情報ID値の比較を行った後にCRC値の比較を行う例について述べたが、これとは逆に、CRC値の比較(異常ブロックの排除)を行った後に管理情報ID値の比較(最新バージョンの選択)を行っても良い。

#### [0181]

また、図35に示した例において第2管理情報を更新する場合には、メモリコントローラ2は、正常ブロックのうち最も古い第2管理情報(3,3)が格納されているブロックB100に、最新の第2管理情報(6,6)を上書きする。

#### [0182]

#### <まとめ>

上記実施の形態1,2に係る半導体記憶装置1によれば、10個(第1所定数個)のブロックB1~B10から成る第1プロック群R1が、管理情報を格納するためのプロックとして限定的に割り当てられている。そして、第1プロック群R1の中からメモリコントローラ2によって選択された、第1所定数個未満の3個(第2所定数個)のプロックの各々に、同一内容の管理情報が格納されている。従って、第2所定数個のプロックに格納されている第2所定数個の管理情報のうちの一つが破壊又は喪失された場合であっても、メモリコントローラ2は、破壊又は喪失されていない残りの管理情報を、制御対象メモリ3から取得することができる。その結果、不良プロックの存在や強制的な電源遮断等に起因して正常動作が阻害されるという事態を回避しつつ、管理情報を制御対象メモリ3に格納することが可能となる。

#### [0183]

また、第2管理情報は、通常のユーザデータが格納される第2ブロック群R2内に格納される。第2ブロック群R2に関しては、後天性不良ブロックとなったブロック又はエラーが発生したブロックを代替ブロックに置き換える処理(いわゆる代替処理)、及び、読み出し時にエラーが発生したデータを訂正して訂正後のデータを再書き込みする処理(いわゆるリフレッシュ処理)等の一般的なエラー処理によって、データの信頼性が確保されている。第2管理情報を第2ブロック群R2内に格納することにより、これらのエラー処理によって第2管理情報の信頼性を確保することができる。

#### [0184]

さらに、第2所定数個は第1所定数個未満に設定されており、上記実施の形態1,2の例では、第2所定数個は3個、第1所定数個は10個に設定されている。従って、同一内容の3個の第1管理情報を1セットとすると、第1ブロック群R1内には3セットの第1管理情報を格納することができる。しかも、第1管理情報を更新する場合には、更新前の第1管理情報が格納されているブロックとは異なるブロックに、更新後の第1管理情報が書き込まれる。従って、第1ブロック群R1内の特定のブロックにアクセスが集中する事態を回避できる。その結果、第1ブロック群R1内における後天性不良ブロックの発生が抑制されるため、装置の信頼性を向上することが可能となる。

10

20

30

#### [0185]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、管理情報は、第 1 管理情報と、第 1 管理情報よりも書き換え頻度の高い第 2 管理情報とに分割されている。 そして、第 1 管理情報は第 1 ブロック群 R 1 内に格納され、第 2 管理情報は第 2 ブロック群 R 2 内に格納される。書き換え頻度に応じて管理情報を第 1 管理情報と第 2 管理情報とに分割し、限定的に割り当てられた第 1 ブロック群 R 1 内には、書き換え頻度の低い第 1 管理情報を格納することにより、第 1 ブロック群 R 1 内ではデータの書き換えが頻繁には発生しない。その結果、第 1 ブロック群 R 1 内における後天性不良ブロックの発生が抑制されるため、装置の信頼性を向上することが可能となる。

#### [0186]

また、上記実施の形態1,2に係る半導体記憶装置1によれば、第1管理情報には、第2管理情報を格納しているブロックを示す位置情報が含まれ、第2管理情報には、不良ブロックを示す位置情報が含まれる。従って、メモリコントローラ2は、第1管理情報を制御対象メモリ3から読み出すことによって、第2管理情報を格納しているブロックを示す位置情報を取得でき、また、当該位置情報に基づいて第2管理情報を制御対象メモリ3から読み出すことによって、不良ブロックを示す位置情報を取得することが可能となる。

#### [0187]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、第 1 管理情報には、第 1 ブロック群 R 1 内の不良ブロックを示す位置情報が含まれ、第 2 管理情報には、第 2 ブロック群 R 2 内の不良ブロックを示す位置情報が含まれる。従って、第 1 ブロック群 R 1 内で後天性不良ブロックが発生した場合には、第 1 管理情報のみを更新すればよく、第 2 管理情報の更新を省略することができる。同様に、第 2 ブロック群 R 2 内で後天性不良ブロックが発生した場合には、第 2 管理情報のみを更新すればよく、第 1 管理情報の更新を省略することができる。

#### [0188]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、 3 個以上かつ第 1 ブロック群のブロック数以下の正常ブロックを、第 1 ブロック群 R 1 の中から特定する。そして、特定した正常ブロックに格納されている第 1 管理情報の中から、多数決によって 1 個の妥当な第 1 管理情報を特定する。従って、更新が繰り返されることで第 1 ブロック群 R 1 内に複数バージョンの第 1 管理情報が格納されている場合であっても、妥当な第 1 管理情報を適切に特定することが可能となる。

#### [0189]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、第 1 ブロック群 R 1 の中から先天性不良ブロックを除外することにより、正常ブロックを特定する。従って、先天性不良ブロックが正常ブロックとして特定されるという事態を回避できるため、妥当な第 1 管理情報を適切に特定することが可能となる。

#### [0190]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、第 1 ブロック群 R 1 の中から無効ブロックを除外することにより、正常ブロックを特定する。従って、無効ブロックが正常ブロックとして特定されるという事態を回避できるため、妥当な第 1 管理情報を適切に特定することが可能となる。

#### [0191]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、第 1 ブロック群 R 1 の中から異常ブロックを除外することにより、正常ブロックを特定する。従って、異常ブロックが正常ブロックとして特定されるという事態を回避できるため、妥当な第 1 管理情報を適切に特定することが可能となる。

#### [0192]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、 3 個の正常プロックを特定し、当該 3 個の正常プロックに格納されている 3 個の第 1

10

20

30

40

管理情報の中から、多数決によって1個の妥当な第1管理情報を特定する。このように、 多数決を行う対象を3個の第1管理情報に限定することによって、簡易に多数決を行うこ とができるため、処理の所要時間を短縮することが可能となる。

#### [0193]

また、上記実施の形態 1 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、ある 1 個の正常ブロックに格納されている第 1 管理情報と、他の任意の 2 個の正常ブロックに格納されている 2 個の第 1 管理情報とを用いて、多数決を行う。従って、多数決を行う対象を限定するための追加の情報を第 1 管理情報に含める必要がないため、処理及び構成を簡略化することが可能となる。

[0194]

また、上記実施の形態 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、ある 1 個の正常プロックに格納されている第 1 管理情報と、当該第 1 管理情報に位置情報が記述されている特定の 2 個のプロックに格納されている 2 個の第 1 管理情報とを用いて、多数決を行う。従って、多数決を行う対象を、更新時に併せて書き込まれた同一内容の第 1 管理情報に限定できるため、多数決によって妥当な第 1 管理情報を特定できる可能性を高めることが可能となる。

#### [ 0 1 9 5 ]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、特定した 3 個の正常ブロックを対象とする多数決によっては妥当な第 1 管理情報を特定できない場合には、他の 3 個の正常ブロックを特定し直して多数決を行う。これにより、妥当な第 1 管理情報を特定できる可能性を高めることが可能となる。

[0196]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、第 1 管理情報を更新する必要が生じた場合には、第 1 ブロック群 R 1 の中で第 2 所定数個の空きブロックを確保し、当該第 2 所定数個の空きブロックの各々に、更新後の第 1 管理情報をそれぞれ書き込む。これにより、更新後においても、同一内容の第 2 所定個数の第 1 管理情報を、第 1 ブロック群 R 1 に格納することが可能となる。

#### [0197]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、更新毎に値が異なるバージョン情報を、第 1 管理情報に含めて書き込む。従って、バージョン情報を用いて多数決を行うことができ、その結果、妥当な第 1 管理情報を適切に特定する精度を向上することが可能となる。

[0198]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、第 1 管理情報を空きブロックに書き込む際に当該空きブロックが後天性不良ブロックとなった場合には、当該第 1 管理情報に含めたバージョン情報の値を、以降の更新時には使用しない。従って、バージョン情報の値を生成するためのカウンタ値が一周した場合であっても、後天性不良ブロックに格納されている第 1 管理情報が、多数決によって妥当な第 1 管理情報として誤って特定されるという事態を回避することが可能となる。

[0199]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、第 1 管理情報の誤り検出符号を、第 1 管理情報に含めて書き込む。従って、誤り検出符号を用いて多数決を行うことができ、その結果、妥当な第 1 管理情報を適切に特定する精度を向上することが可能となる。また、誤り検出符号を用いてデータの誤りが生じているか否かを判定することができ、その結果、第 1 ブロック群の中から正常ブロックを特定する際に、データの誤りが生じている異常ブロックを除外することが可能となる。

#### [0200]

また、上記実施の形態 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、 第 2 所定数個の空きブロックの中の一の空きブロックに書き込む第 1 管理情報に、第 2 所 10

20

30

40

定数個の空きブロックの中の他の空きブロックを示す位置情報(グループアドレス)を含めて書き込む。従って、多数決を行う対象を、更新時に併せて書き込まれた同一内容の第1管理情報に限定できるため、多数決によって妥当な第1管理情報を特定できる可能性を高めることが可能となる。

#### [0201]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、第 1 ブロック群 R 1 の中から、先天性不良ブロックを除外することにより、空きブロックを確保する。従って、更新後の第 1 管理情報を書き込むブロックとして、先天性不良ブロックが選択されるという事態を回避することが可能となる。

#### [0202]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、第 1 ブロック群 R 1 の中から、後天性不良ブロックを除外することにより、空きブロックを確保する。従って、更新後の第 1 管理情報を書き込むブロックとして、後天性不良ブロックが選択されるという事態を回避することが可能となる。

#### [0203]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、第 1 ブロック群 R 1 の中から、更新前の第 1 管理情報が格納されている第 2 所定数個のブロック(多数決対象ブロック)を除外することにより、空きブロックを確保する。従って、第 1 管理情報の更新処理中にユーザの誤操作等によって強制的に電源が遮断され、それによって更新後の第 1 管理情報が消去された場合等であっても、更新前の第 1 管理情報は制御対象メモリ 3 内に残されているため、それを用いて再起動を行うことが可能となる。

#### [0204]

また、上記実施の形態1,2に係る半導体記憶装置によれば、メモリコントローラ2は、1個の空きプロックへの第1管理情報の書き込みが完了すると、更新前の第1管理情報が格納されていた1個のプロックに対して、所定の無効フラグを付加する。これにより、第1管理情報が格納されているプロックとして、少なくとも第2所定数個のプロックを常に確保することが可能となる。しかも、データを消去するのではなく無効フラグを付加するため、消去に伴うメモリセルへのストレスを回避できる。その結果、第1プロック群R1内における後天性不良プロックの発生が抑制されるため、装置の信頼性を向上することが可能となる。

#### [0205]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、メモリコントローラ 2 は、第 2 所定数個の空きブロックの中の 1 個の空きブロックへの第 1 管理情報の書き込みが完了すると、更新前の第 1 管理情報が格納されていた第 2 所定数個のブロックの中の 1 個のブロックに対して、データの消去を行う。これにより、第 1 管理情報が格納されているブロックとして、少なくとも第 2 所定数個のブロックを常に確保することが可能となる

#### [0206]

また、上記変形例 4 に係る半導体記憶装置 1 によれば、先天性不良ブロックを除外した第 1 所定数個のブロックが、第 1 ブロック群 R 1 として割り当てられる。従って、第 1 ブロック群を構成するブロックとして、必ず第 1 所定数個のブロックを確保できるため、装置の信頼性を向上することが可能となる。

#### [0207]

また、上記変形例1に係る半導体記憶装置1によれば、第2管理情報は複数の第2管理情報片121~123に分割される。そして、第1管理情報11は制御対象メモリ3Aに格納され、第2管理情報片121~123は制御対象メモリ3B~3Dにそれぞれ格納される。従って、複数の第2管理情報片121~123を制御対象メモリ3B~3Dから同時に読み出すことができ、その結果、処理の所要時間を短縮することが可能となる。

#### [0208]

10

20

30

また、上記変形例 5 に係る半導体記憶装置 1 によれば、図 3 4 に示したように、第 2 ブロック群 R 2 の中から選択された 3 個(第  $\frac{3}{3}$  所定数個)のブロックの各々に、同一内容の第 2 管理情報が格納されている。そして、メモリコントローラ 2 は、妥当な第 1 管理情報に含まれている位置情報に基づいて、第  $\frac{3}{3}$  所定数個のプロックに格納されている第  $\frac{3}{3}$  所定数個の第 2 管理情報の中から、 1 個の第 2 管理情報を取得する。従って、第  $\frac{3}{3}$  所定数個の第 2 管理情報のつちの一つが破壊又は喪失された場合であっても、メモリコントローラ 2 は、破壊又は喪失されていない残りの第 2 管理情報を、制御対象メモリ 3 から取得することができる。その結果、不良ブロックの存在や強制的な電源遮断等に起因して正常動作が阻害されるという事態を回避しつつ、管理情報を制御対象メモリ 3 に格納することが可能となる。

10

#### [0209]

また、上記変形例 5 に係る半導体記憶装置 1 によれば、図 3 5 に示したように、第 2 ブロック群 R 2 の中から選択された 3 個(第 3 所定数個)のブロックに、バージョンが異なる第 3 所定数個の第 2 管理情報が格納されている。そして、メモリコントローラ 2 は、妥当な第 1 管理情報に含まれている位置情報に基づいて、第 3 所定数個のブロックに格納されている第 3 所定数個のブロックに格納されている第 3 所定数個のブロックに格納されている第 3 所定数個の第 2 管理情報のうちの一つが破壊又は喪失された場合であっても、メモリコントローラ 2 は、破壊又は喪失されていない残りの第 2 管理情報を、制御対象メモリ 3 から取得することができる。その結果、不良ブロックの存在や強制的な電源遮断等に起因して正常動作が阻害されるという事態を回避しつつ、管理情報を制御対象メモリ 3 に格納することが可能となる。

20

30

#### [0210]

また、上記実施の形態 1 , 2 に係る半導体記憶装置 1 によれば、第 1 所定数個のブロックから成る第 1 ブロック群 R 1 が、管理情報を格納するためのブロックとして限定的に割り当てられている。また、管理情報は、第 1 管理情報と、第 1 管理情報よりも書き換え頻度の高い第 2 管理情報とを含む。そして、第 1 管理情報は第 1 ブロック群 R 1 内に格納され、第 2 管理情報は第 2 ブロック群 R 2 内に格納される。このように、書き換え頻度に応じて管理情報を第 1 管理情報と第 2 管理情報とに分割し、限定的に割り当てられた第 1 ブロック群 R 1 内には、書き換え頻度の低い第 1 管理情報を格納することにより、第 1 ブロック群 R 1 内ではデータの書き換えが頻繁には発生しない。その結果、第 1 ブロック群 R 1 内における後天性不良ブロックの発生が抑制されるため、装置の信頼性を向上することが可能となる。

40

#### 【符号の説明】

#### [0211]

- 1 半導体記憶装置

- 2 メモリコントローラ

- 3 制御対象メモリ

### 【図1】

### 【図2】

## 【図5】

### 【図6】

| В1  | 先天性本身プロック      |

|-----|----------------|

| В2  | 無効プロック         |

| ВЗ  | 第1管理情報(1,1)BAD |

| В4  | 無効プロック         |

| В5  | 先天性不良プロック      |

| В6  | 第1管理情報(2,1)    |

| В7  | 第1管理情報(3,3)    |

| В8  | 第1管理情報(4,4)    |

| В9  | 第1管理情報(4,4)    |

| B10 | 消去済みプロック       |

### 【図3】

|          | メモリA           | メモリB              | メモリC             | メモリロ                |

|----------|----------------|-------------------|------------------|---------------------|

| バス幅      | 8              |                   |                  |                     |

| ページサイズ   | 1056Byte       | 2112Byte          | 4224Byte         | 8448Byte            |

| プロックサイズ  | 32Page         | 64Page            | 128Page          | 256Page             |

| 総ブロック数   | 1024Block      | 2048Block         | 4096Block        | 8192Block           |

| 読み出しサイクル | 30ns           | 35ns              | 40ns             | 50ns                |

| 先天性不良フラグ | Page0<br>Byte0 | Page0<br>Byte2048 | Page128<br>Byte0 | Page256<br>Byte8192 |

### 【図4】

| В1  | 先天性不良ブロック      |

|-----|----------------|

| В2  | 無効プロック         |

| ВЗ  | 第1管理情報(1,1)BAD |

| В4  | 無効ブロック         |

| В5  | 先天性不良プロック      |

| В6  | 第1管理情報(2,1)    |

| В7  | 第1管理情報(3,3)    |

| В8  | 第1管理情報(4,4)    |

| В9  | 第1管理情報(4,4)    |

| B10 | 消去済みブロック       |

|     | <u> </u>       |

# 【図7】

| В1  | 先天性不良プロック      |

|-----|----------------|

| В2  | 無効プロック         |

| В3  | 第1管理情報(1,1)BAD |

| В4  | 世級プログラ         |

| В5  | 先天性不良プロック      |

| В6  | 第1管理情報(2,1)    |

| В7  | 第1管理情報(3,3)    |

| В8  | 第1管理情報(4,4)    |

| В9  | 第1管理情報(4,4)    |

| B10 | 消去済みブロック       |

## 【図8】

| В1  | 先天性不良プロック                                                                                                            |

|-----|----------------------------------------------------------------------------------------------------------------------|

| В2  | 無効プロック                                                                                                               |

| ВЗ  | 第1管理情報(1, 1)BAD                                                                                                      |

| В4  | で<br>を<br>を<br>が<br>を<br>が<br>に<br>を<br>を<br>に<br>を<br>に<br>に<br>に<br>に<br>に<br>に<br>に<br>に<br>に<br>に<br>に<br>に<br>に |

| В5  | 先天性不良プロック                                                                                                            |

| В6  | 第1管理情報(2、1)                                                                                                          |

| В7  | 第1管理情報(3,3)                                                                                                          |

| В8  | 第1管理情報(4,4)                                                                                                          |

| В9  | 第1管理情報(4,4)                                                                                                          |

| B10 | 消去済みずロック                                                                                                             |

#### 【図11】 В1 先天性不良プロック В2 無効ブロック ВЗ 第1管理情報(1, 1)BAD В4 先天性不良プロック В5 В6 第1管理情報(2、1) В7 第1管理情報(3,3) 第1管理情報(4,4) В8 第1管理情報(4,4) В9 消去済みブロック B10 【図12】 В1 先天性不良ブロック В2 無効ブロック ВЗ 第1管理情報(1, 1)BAD В4 無効ブロック В5 先天性不良ブロック В6 第1管理情報(2,1) 第1管理情報(3,3) В7 第1管理情報(4,4) В8 В9 第1管理情報(4,4) B10 消去済みブロック

| В7    | 第1管理情報(3,3)    |

|-------|----------------|

| В8    | 第1管理情報(4,4)    |

| В9    | 第1管理情報(4,4)    |

| B10   | 消去済みプロック       |

| 図 1 4 | 1              |

| В1    | 先天性不良プロック      |

| В2    | 無効プロック         |

| ВЗ    | 第1管理情報(1,1)BAD |

| В4    | 無効ブロック         |

| В5    | 先天性不良プロック      |

| В6    | 第1管理情報(2,1)    |

| В7    | 第1管理情報(3,3)    |

| В8    | 第1管理情報(4,4)    |

| В9    | 第1管理情報(4,4)    |

| B10   | 第1管理情報(5,5)    |

| ,     |                |

### 【図17】

| В1  | 無効プロック         |

|-----|----------------|

| В2  | 無効プロック         |

| ВЗ  | 第1管理情報(6,6)    |

| В4  | 第1管理情報(1,1)BAD |

| В5  | 先天性不良プロック      |

| В6  | 第1管理情報(6,6)    |

| В7  | 第1管理情報(6,6)    |

| В8  | 第1管理情報(2,2)BAD |

| В9  | 先天性不良プロック      |

| B10 | 無効ブロック         |

### 【図18】

| В1  | 無効ブロック          |

|-----|-----------------|

| В2  | 無効プロック          |

| В3  | 第1管理情報(7,7)     |

| В4  | 第1管理情報(1,1)BAD  |

| В5  | 先天性不良プロック       |

| В6  | 第1管理情報(2, 2)BAD |

| В7  | 第1管理情報(7,7)     |

| В8  | 第1管理情報(7,7)     |

| В9  | 先天性不良ブロック       |

| B10 | 無効ブロック          |

|     |                 |

### 【図19】

| В1  | 先天性不良ブロック             |

|-----|-----------------------|

| В2  | 無効ブロック                |

| ВЗ  | 第1管理情報(1, 1)<4, 6>BAD |

| В4  | 無効ブロック                |

| В5  | 先天性不良ブロック             |

| В6  | 第1管理情報(2,1)<7,8>      |

| В7  | 第1管理情報 (3,3) <2,4>    |

| В8  | 第1管理情報(4,4)<9,10>     |

| В9  | 第1管理情報(4,4)<8,10>     |

| B10 | 消去済みブロック              |

# 【図20】

| B1  | 先天性不良プロック             |

|-----|-----------------------|

| В2  | 無効ブロック                |

| ВЗ  | 第1管理情報(1, 1)<4, 6>BAD |

| В4  | 無効ブロック                |

| В5  | 先天性不良プロック             |

| В6  | 第1管理情報(2,1)<7,8>      |

| В7  | 第1管理情報 (3,3) <2,4>    |

| В8  | 第1管理情報(4,4)<9,10>     |

| В9  | 第1管理情報(4,4)<8,10>     |

| B10 | 消去済みブロック              |

#### 【図21】

#### 【図22】

#### 【図23】

| В1  | 先天性不良プロック             |

|-----|-----------------------|

| В2  | 無効ブロック                |

| В3  | 第1管理情報(1, 1)<4, 6>BAD |

| В4  | 無効ブロック                |

| В5  | 先天性不良プロック             |

| В6  | 第1管理情報(2, 1)<7,8>     |

| В7  | 第1管理情報(3,3)<2,4>      |

| В8  | 第1管理情報 (4, 4) <9, 10> |

| В9  | 第1管理情報(4,4)<8,10>     |

| B10 | 消去済みブロック              |

### 【図24】

| B 1 | 先天性不良プロック             |

|-----|-----------------------|

| В2  | 無効プロック                |

| В3  | 第1管理情報(1, 1)<4, 6>BAD |

| В4  | 無効ブロック                |

| В5  | 先天性不良プロック             |

| В6  | 第1管理情報(2, 1)<7,8>     |

| В7  | 第1管理情報(3,3)<2,4>      |

| В8  | 第1管理情報(4,4)<9,10>     |

| В9  | 第1管理情報(4,4)<8,10>     |

| B10 | 消去済みプロック              |

### 【図25】

| B1   | 先天性不良プロック             |

|------|-----------------------|

| В2   | 無効プロック                |

| В3   | 第1管理情報(1, 1)<4, 6>BAD |

| В4   | 無効ブロック                |

| В5   | 先天性不良プロック             |

| В6   | 第1管理情報(2、1)<7、8>      |

| В7   | 第1管理情報(3,3)<2,4>      |

| В8   | 第1管理情報(4,4)<9,10>     |

| В9   | 第1管理情報(4,4)<8,10>     |

| B10  | 消去済みプロック              |

| 【図26 | ]                     |

|      |                       |

| B 1 | 先天性不良ブロック             |

|-----|-----------------------|

| В2  | 無効ブロック                |

| ВЗ  | 第1管理情報(1, 1)<4, 6>BAD |

| В4  | 無効ブロック                |

| В5  | 先天性不良ブロック             |

| В6  | 第1管理情報(2,1)<7,8>      |

| В7  | 第1管理情報(3,3)<2,4>      |

| В8  | 第1管理情報(4,4)<9,10>     |

| В9  | 第1管理情報(4,4)<8,10>     |

| B10 | 消去済みブロック              |

# 【図27】

| В1  | 先天性不良プロック            |

|-----|----------------------|

| В2  | 無効プロック               |

| В3  | 第1管理情報(1, 1)<4,6>BAD |

| В4  | 無効プロック               |

| В5  | 先天性不良プロック            |

| В6  | 第1管理情報(2,1)<7,8>     |

| В7  | 第1管理情報(3,3)<2,4>     |

| В8  | 第1管理情報(4,4)<9,10>    |

| В9  | 第1管理情報(4,4)<8,10>    |

| B10 | 消去済みプロック             |

## 【図28】

| В1  | 先天性不良プロック             |

|-----|-----------------------|

| В2  | 第1管理情報(5,5)<4,7>      |

| ВЗ  | 第1管理情報(1, 1)<4, 6>BAD |

| В4  | 無効ブロック                |

| В5  | 先天性不良ブロック             |

| В6  | 第1管理情報(2,1)<7,8>      |

| В7  | 第1管理情報(3,3)<2,4>      |

| В8  | 第1管理情報(4,4)<9,10>     |

| В9  | 第1管理情報(4,4)<8,10>     |

| В10 | 消去済みプロック              |

## 【図29】

| B 1 | 先天性不良ブロック             |

|-----|-----------------------|

| В2  | 第1管理情報(5,5)<4,7>      |

| В3  | 第1管理情報(1, 1)<4, 6>BAD |

| В4  | 無効ブロック                |

| В5  | 先天性不良ブロック             |

| В6  | 第1管理情報(2,1)<7,8>      |

| В7  | 第1管理情報(3,3)<2,4>      |

| В8  | 無効ブロック                |

| В9  | 第1管理情報(4,4)<8,10>     |

| B10 | 消去済みブロック              |

# 【図30】

| В1  | 先天性不良ブロック           |

|-----|---------------------|

| В2  | 第1管理情報(5,5)<4,7>    |

| ВЗ  | 第1管理情報(1,1)<4,6>BAD |

| В4  | 第1管理情報(5,5)<2,7>    |

| В5  | 先天性不良ブロック           |

| В6  | 第1管理情報(2,1)<7,8>    |

| В7  | 第1管理情報(5,5)<2,4>    |

| В8  | 無効ブロック              |

| В9  | 無効ブロック              |

| B10 | 無効ブロック              |

|     |                     |

# 【図31】

| B1    | 無効ブロック                   |  |

|-------|--------------------------|--|

| В2    | 無効ブロック                   |  |

| В3    | 第1管理情報(6,6)<6,7>         |  |

| В4    | 第1管理情報(1, 1)<1, 2>BAD    |  |

| В5    | 先天性不良ブロック                |  |

| В6    | 第1管理情報(6,6)<3,7>         |  |

| В7    | 第1管理情報(6,6)<3,6>         |  |

| В8    | 第1管理情報 (2, 2) <7, 10>BAD |  |

| В9    | 先天性不良ブロック                |  |

| B10   | 無効ブロック                   |  |

| 【図32】 |                          |  |

| В1    | 無効ブロック                   |  |

| B 1 | 無効ブロック                 |

|-----|------------------------|

| В2  | 無効ブロック                 |

| ВЗ  | 第1管理情報(7,7)<7,8>       |

| В4  | 第1管理情報(1,1)<1,2>BAD    |

| В5  | 先天性不良ブロック              |

| В6  | 第1管理情報(2, 2)<7, 10>BAD |

| В7  | 第1管理情報(7,7)<3,8>       |

| В8  | 第1管理情報(7,7)<3,7>       |

| В9  | 先天性不良ブロック              |

| B10 | 無効ブロック                 |

### 【図33】

### 【図34】

### 【図35】

#### フロントページの続き

### (56)参考文献 国際公開第2008/139689(WO,A1)

特開2001-084002(JP,A)

特開2008-262614(JP,A)

特表2009-521049(JP,A)

特開2002-169729(JP,A)

特開2005-234957(JP,A)

特開2006-277395(JP,A)

特開2011-059866(JP,A)

### (58)調査した分野(Int.CI., DB名)

G06F 12/16

G06F 11/10