(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5044818号

(P5044818)

(45) 発行日 平成24年10月10日(2012.10.10)

(24) 登録日 平成24年7月27日(2012.7.27)

(51) Int.Cl.

H01L 29/93 (2006.01)

H01L 21/329 (2006.01)

F 1

H01L 29/93

H

請求項の数 16 (全 13 頁)

(21) 出願番号 特願2007-550400 (P2007-550400)

(86) (22) 出願日 平成17年12月22日 (2005.12.22)

(65) 公表番号 特表2008-527714 (P2008-527714A)

(43) 公表日 平成20年7月24日 (2008.7.24)

(86) 國際出願番号 PCT/US2005/047085

(87) 國際公開番号 WO2006/073943

(87) 國際公開日 平成18年7月13日 (2006.7.13)

審査請求日 平成20年10月7日 (2008.10.7)

(31) 優先権主張番号 10/905,486

(32) 優先日 平成17年1月6日 (2005.1.6)

(33) 優先権主張国 米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】補償されたカソード・コンタクトを使用する1マスク超階段接合バラクタの形成方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板のアノード領域内に配置された超階段接合と、

前記半導体基板のカソード領域内に、前記超階段接合に隣接して配置され、当該接合とは絶縁された、少なくとも1つの補償されたカソード・コンタクトと、

第1の導電型を有し、下にあるサブコレクタまたはカソードのいずれかの領域と接触するリーチスルードーパント領域と、

前記リーチスルードーパント領域の表面上に配置された、前記第1の導電型を有するドーパント領域と

を含み、前記少なくとも1つの補償されたカソード・コンタクトは、前記半導体基板の上面へ延在し、かつ、前記ドーパント領域の表面に垂直に隣接しており、かつ、前記第1の導電型に補償された上側ドーパント領域を含み、かつ、前記ドーパント領域および前記リーチスルードーパント領域に比較して高い濃度の前記第1の導電型のドーパントを有する、半導体構造。

## 【請求項2】

前記アノード領域内の前記超階段接合が、前記第1の導電型と異なる第2の導電型を有する上側ドーパント領域と、当該上側ドーパント領域と反対である前記第1の導電型を有する下側ドーパント領域とを含む、請求項1に記載の半導体構造。

## 【請求項3】

前記アノード領域内の前記超階段接合の前記上側ドーパント領域がp型ドーパントを含

10

20

み、前記アノード領域内の前記超階段接合の前記下側ドーパント領域がn型ドーパントを含む、請求項2に記載の半導体構造。

**【請求項4】**

前記アノード領域内の前記超階段接合の前記上側ドーパント領域がn型ドーパントを含み、前記アノード領域内の前記超階段接合の前記下側ドーパント領域がp型ドーパントを含む、請求項2に記載の半導体構造。

**【請求項5】**

2つの補償されたカソード・コンタクトが前記超階段接合に接して配置される、請求項1に記載の半導体構造。

**【請求項6】**

前記少なくとも1つの補償されたカソード・コンタクトが、10<sup>20</sup>原子/cm<sup>3</sup>以上の濃度でドーピングされた領域を含む、請求項1に記載の半導体構造。

10

**【請求項7】**

前記超階段接合および前記少なくとも1つの補償されたカソード・コンタクトの上に配置されたシリサイドをさらに含む、請求項1に記載の半導体構造。

**【請求項8】**

半導体基板のアノード領域に配置され、p型上側ドーパント領域およびn型下側ドーパント領域を含む超階段接合と、

前記半導体基板のカソード領域内に、前記超階段接合に隣接して配置され、当該接合とは絶縁された、少なくとも1つの補償されたカソード・コンタクトと

20

下にあるn型のサブコレクタまたはカソードのいずれかの領域と接触するn型リーチスルードーパント領域と、

前記n型リーチスルードーパント領域の表面上に配置された、n型ドーパント領域とを含み、前記少なくとも1つの補償されたカソード・コンタクトは、前記半導体基板の上面へ延在し、かつ、前記n型ドーパント領域の表面に垂直に隣接しており、かつ、n型に補償された上側ドーパント領域を含み、かつ、前記n型ドーパント領域および前記n型リーチスルードーパント領域に比較して高い濃度のn型ドーパントを有する、半導体構造。

**【請求項9】**

超階段接合を含む半導体構造を形成する方法であって、

30

半導体基板であって、該半導体基板内でアノード領域および少なくとも1つのカソード領域を画定する複数の分離領域が配置された半導体基板を準備するステップと、

前記少なくとも1つのカソード領域内に、第1の導電型のリーチスルードーパント領域を形成するステップと、

前記リーチスルードーパント領域に接触されるサブコレクタ/カソード、コレクタ/ウェル領域、ならびに前記アノード領域内および前記カソード領域内の両方に配置される超階段接合を単一の注入マスクを使用して前記半導体基板内に形成するステップと、

前記少なくとも1つのカソード領域内へ選択的に前記第1の導電型による注入を行うことによって、前記少なくとも1つのカソード領域に配置された前記超階段接合の、前記第1の導電型と異なる第2の導電型を有する上側ドーパント領域を前記第1の導電型へ補償して、補償されたカソード・コンタクトであって、前記半導体基板の上面へ延在し、かつ、前記リーチスルードーパント領域の表面上に配置された前記第1の導電型を有するドーパント領域の表面に垂直に隣接しており、かつ、前記ドーパント領域および前記リーチスルードーパント領域に比較して高い濃度の前記第1の導電型のドーパントを有する該補償されたカソード・コンタクトへと変更するステップと

を含む、方法。

40

**【請求項10】**

前記リーチスルードーパント領域の前記形成が、前記少なくとも1つのカソード領域を露出する開口部を有する第1の注入マスクを形成すること、および前記露出領域内に前記第1の導電型のドーパントを注入することを含む、請求項9に記載の方法。

50

## 【請求項 1 1】

前記サブコレクタ / カソード、前記コレクタ / ウェル領域、および前記超階段接合の前記形成が、前記单一の注入マスクを介して複数の注入を実行することを含む、請求項 9 に記載の方法。

## 【請求項 1 2】

前記サブコレクタ / カソードおよび前記コレクタ / ウェル領域の前記形成が、单一の注入を使用して実行される、請求項 1 1 に記載の方法。

## 【請求項 1 3】

前記超階段接合の前記形成が、異なる導電型の 2 つの注入を含む、請求項 1 1 に記載の方法。

10

## 【請求項 1 4】

前記カソード領域内への前記選択的な注入が、前記カソード領域内に  $10^{20}$  原子 /  $\text{cm}^3$  以上の濃度でドーピングされた領域を形成する、請求項 9 に記載の方法。

## 【請求項 1 5】

前記超階段接合および前記補償されたカソード・コンタクトの上にシリサイドを形成することをさらに含む、請求項 9 に記載の方法。

## 【請求項 1 6】

前記シリサイドがシリサイド化プロセスによって形成される、請求項 1 5 に記載の方法。

## 【発明の詳細な説明】

20

## 【技術分野】

## 【0001】

本発明は、可同調で高い品質係数  $Q$  を有する超階段接合バラクタを含む半導体構造、およびこのような半導体構造の製作方法に関する。補償されたカソード・コンタクトを有する超階段接合バラクタを含む本発明の半導体構造は、相補型金属酸化物半導体 (CMOS) 技術またはバイポーラ技術あるいはその両方で使用するのに非常に適している。特に、本発明の構造は、移動電話またはセルラ電話、携帯情報端末 (PDA)、およびその他の高い無線周波 (RF) の電子デバイスの構成要素として使用するのに非常に適している。

## 【背景技術】

## 【0002】

30

バラクタは、p-n 接合に通常は由来する同調可能な半導体キャパシタの一種を形成しており、バラクタでは p-n 接合が逆バイアス状態で動作される。バラクタのキャパシタンスは、逆バイアス電圧を調整することによって変えることができる。したがって、バラクタは CV 同調曲線によって特徴づけることができる。バラクタは、発振回路、とりわけ電圧制御発振器 (VCO) において特に有用であり、発振回路では、バラクタの可同調性が回路の発振周波数を同調させるのに使用される。このように、バラクタは、セルラ電話または移動電話、PDA、テレビ、ラジオ、コンピュータ、アクティブ・フィルタ、および第 1 の信号が第 2 の信号に同期されるあらゆるものにおいて用途がある。

## 【0003】

イオン注入された超階段接合を含むバラクタが知られており、当技術においては「超階段接合バラクタ」と呼ばれている。例えば、グッドウィン (Goodwin) 等への米国特許第 4,226,648 号、パブリディス (Pavlidis) 等への米国特許第 4,827,319 号、グエン (Nguyen) 等への米国特許第 5,557,140 号、およびクールボー (Coolbaugh) 等への米国特許第 6,521,506 号を参照。用語「超階段」は、p-n 接合のプロファイルを示すために使用される。超階段接合バラクタは、ドーパント密度が接合部の方へ向かって増加し、接合部で急にゼロまで降下する、制御された非線形形式に変化するドーピング・プロファイルを有する。

40

## 【0004】

超階段接合バラクタは、p-n ダイオード・バラクタ、ショットキー・ダイオード・バラクタ、および金属酸化物半導体 (MOS) ダイオード・バラクタよりも高い同調範囲を有

50

する。さらに、超階段接合バラクタは、高い品質係数 Q に加えて、ほぼ線形の C V 特性を有する。これらの性能指数、すなわち可同調性、高 Q、および線形の C V により、超階段接合バラクタは V C O の設計者たちに好まれるデバイスとなっている。

#### 【 0 0 0 5 】

クリティカルな C M O S プロセスおよび B i C M O S プロセスから独立している超階段接合バラクタを実現するために、従来技術の技法では、少なくとも 2 つの独自のクリティカルな注入マスク・レベルを実現することが必要である。例えば、1 つの注入マスク・レベルが、サブコレクタまたは超階段接合バラクタ用の n 型注入部あるいはその両方を形成するために必要であり、別の注入マスク・レベルが、p + 注入または超階段注入あるいはその両方を実施してアノード・デバイスを形成するために必要である。

10

#### 【 0 0 0 6 】

1 マスク・レベルの超階段接合バラクタを作製するためには、標準の p F E T ソース / ドレイン注入からの p + 型注入またはバイポーラ・エミッタからの同様の p + 型注入を実施することが必要である。しかし、超階段接合を形成するために使用される n 型注入を、特定の p + 型ソース / ドレインまたはエミッタ注入技術に合わせる必要があるため、このような方法は超階段バラクタ・プロセスのモジュール性を制限する。さらに、特定のデバイス、例えば p 型 F E T、p + 型ポリ S i 抵抗、p + 型拡散抵抗、およびバイポーラ・トランジスタを要求仕様 (specification) まで戻すように p + 型注入を調整するのが一般的であるので、p + 型ソース / ドレイン注入またはエミッタ注入を使用することは将来多数の問題を引き起こすであろう。エネルギーまたはドーズ量に対するどのようなわずかな調整も、それを使用する超階段接合バラクタに大きな変化 (shift) を生じさせることがあり得る。

20

#### 【 0 0 0 7 】

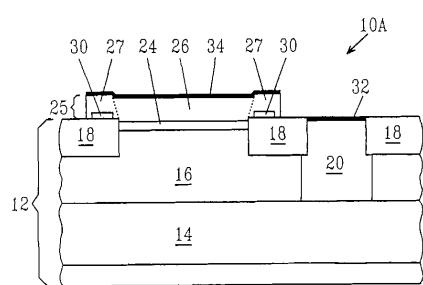

図 1 は、1 つのカソード・コンタクトおよび超階段接合バラクタを含む、従来技術の典型的な半導体構造 1 0 A の断面図である。この従来技術の構造の超階段接合バラクタは、少なくとも 2 つのクリティカルなマスキング・レベルを使用して製作されたものである。図 1 に示す構造 1 0 A は、埋込みサブコレクタ / カソード 1 4、コレクタ 1 6、トレンチ分離領域 1 8、リーチスルー注入領域 2 0、および超階段ドーパント領域 2 4 を含む S i 含有基板 1 2 を含む。リーチスルー注入領域 2 0 は、この従来技術の構造ではサブコレクタ / カソード 1 4 と一箇所で接触している。埋込みサブコレクタ 1 4、コレクタ 1 6、およびリーチスルー注入領域 2 0 は、同じ導電型のドーパント (p 型または n 型であるが、n 型が好ましい) から構成されている。しかし、領域 1 4、1 6、および 2 0 内のドーパント濃度は異なっている。例えば、埋込みサブコレクタ 1 4 およびリーチスルー注入部 2 0 は、コレクタ 1 6 より高濃度にドーピングされている。基板 1 2 上には、リーチスルー注入領域 2 0 と接触するシリサイド領域 3 2 が示されている。基板 1 2 上には誘電体膜 3 0 も示されており、この誘電体膜 3 0 はトレンチ分離領域 1 8 上に配置されている。さらに、例えばドーピングされたポリ S i を含むベース領域 2 5 も、基板 1 2 上に配置されている。ベース領域 2 5 は、S i 含有基板 1 2 上に単結晶部 2 6 を含み、トレンチ分離領域 1 8 および誘電体膜 3 0 上に多結晶部 2 7 を含む。ベース領域 2 5 上には、シリサイド領域 3 4 も配置されている。

30

#### 【 0 0 0 8 】

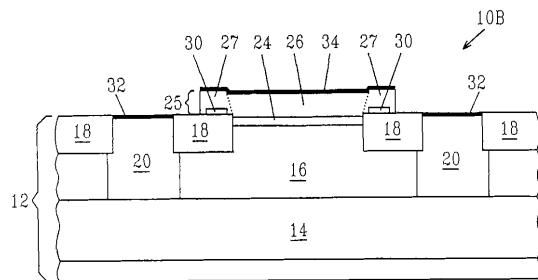

上記の 1 カソード・コンタクトのデザインに加えて、従来技術の方法を利用して 2 カソード・コンタクト構造を形成することも可能である。2 カソード・コンタクト構造を含む 1 0 B が図 2 に示されている。図 2 で使用される参照番号は、図 1 で使用したものと同様であり、したがって図 2 に示す 2 カソード・デザインで表した要素は、図 1 に関して上述したものと同様である。図 2 に示す従来技術の構造の超階段接合バラクタも、少なくとも 2 つのクリティカルなマスキング・レベルを使用して作製されたものである。

40

【特許文献 1】グッドワイン等、米国特許第 4,226,648 号

【特許文献 2】パブリディス等、米国特許第 4,827,319 号

【特許文献 3】グエン等、米国特許第 5,557,140 号

50

【特許文献 4】クールボー等、米国特許第 6,521,506 号

【発明の開示】

【発明が解決しようとする課題】

【0009】

上述の両方の従来技術の構造では、超階段ドーパント領域を形成するために 2 つのクリティカルなマスキング・レベルが必要とされる。半導体産業では、従来技術の超階段接合バラクタを形成するためには、2 つの追加の注入マスク・レベルを超階段接合バラクタが必要とするといった不満が継続している。さらには、前述の課題を回避する、1 マスキング・レベルのデバイスの使用を可能にする解決策を見つける必要がある。

【課題を解決するための手段】

10

【0010】

本発明は、超階段接合および補償されたカソード・コンタクトを含む半導体構造を提供する。超階段接合を含む本発明の構造の超階段接合バラクタは、高度に同調可能で、高 Q および線形 C V 曲線を有する。超階段接合に隣接する基板の領域に配置されたカソード・コンタクトは補償される。「補償される」とは、本発明のカソード・コンタクトが、反対のタイプのドーパントを効率的にカウンタ・ドーピングするのには十分な高さの、あるタイプのドーパント濃度を有することを意味している。

【0011】

特に、幅広い意味では、本発明の半導体構造は、

半導体基板のアノード領域内に配置された超階段接合と、

20

前記超階段接合に隣接して配置されているがそこからは絶縁された、少なくとも 1 つの補償されたカソード・コンタクトとを含み、前記少なくとも 1 つの補償されたカソード・コンタクトがリーチスルー・ドーパント領域の表面で第 1 の導電型のドーパント領域を提供し、前記リーチスルー・ドーパント領域が、サブコレクタまたはカソードあるいはその両方である、下にある第 1 のドーパント領域と接触している。

【0012】

本発明の半導体構造は、CMOS 技術またはバイポーラ技術あるいはその両方における、1 つまたは複数の CMOS デバイスまたはバイポーラ・デバイスあるいはその両方が上に配置された基板として使用することができる。

【0013】

30

上記の本発明の半導体構造を提供することに加えて、本発明は、超階段接合、サブコレクタ / カソード、およびコレクタ / ウェル領域を形成するために単一のマスキング・レベルが使用される、上記の構造の製作方法も提供する。具体的には、本発明は、従来技術の超階段接合バラクタを製作する際に使用される一般的な方法であるエピタキシャル成長法の使用を含まない半導体構造の製作方法、特に CMOS または BiCMOS 処理で超階段接合バラクタを製作する方法を提供する。より具体的には、本発明は、超階段接合、サブコレクタ / カソード、およびコレクタ / ウェル領域を形成するために単一の注入マスクを使用する、垂直な超階段接合バラクタの製作方法を提供する。

【0014】

幅広い意味では、本発明の半導体構造を形成する際に使用される本発明の方法は、

40

半導体基板であって、この半導体基板内でアノード領域および少なくとも 1 つのカソード領域を画定する複数の分離領域が配置された半導体基板を準備するステップと、

前記少なくとも 1 つのカソード領域内にリーチスルー・ドーパント領域を形成するステップと、

サブコレクタ / カソード、コレクタ / ウェル領域、ならびに前記アノード領域内およびカソード領域内の両方に配置される超階段接合を単一の注入マスクを使用して前記半導体基板内に形成するステップと、

前記カソード領域に配置された前記超階段接合を補償されたカソード・コンタクトへと変えるために前記カソード領域内へ選択的に注入するステップとを含む。

【0015】

50

本発明によれば、本発明の超階段接合の形成は、バラクタのダイオード層を形成するのには十分な濃さであるが、カソード・コンタクト領域において補償されるのには十分な薄さのドーズ量で実行される、超階段接合の上側ドーパント領域の注入を含む。

【発明を実施するための最良の形態】

【0016】

次に、補償されたカソード・コンタクトを有する超階段接合バラクタを含む半導体構造、ならびに単一のマスクがサブコレクタ／カソード、コレクタ／ウェルおよび超階段接合を形成するために使用されるその半導体構造の製作方法を提供する本発明を、本願に付属の図面を参照することによって、より詳細に説明する。本願の図面は、例示の目的で本明細書において提供されており、したがって一定の比率では描画されていない。

10

【0017】

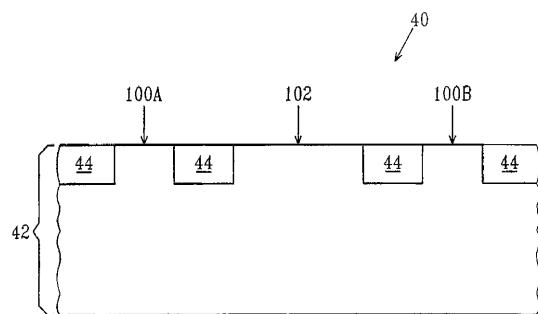

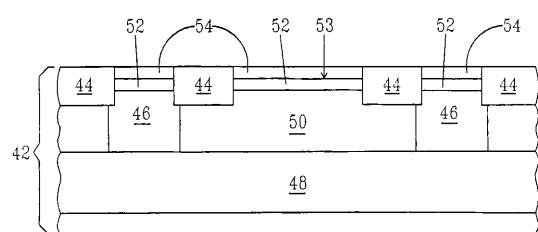

まず、補償されたカソード・コンタクトを有する1マスク超階段接合バラクタを形成するために本発明で使用される基本プロセス・フローを示す図3～図6を参照する。具体的には、図3は、本発明で使用することができる初期構造40を示している。図示のように、初期構造40は、複数の分離領域44が形成された半導体基板42を含む。

【0018】

半導体基板42は、Si、SiGe、SiC、SiGeC、GaAs、InAs、InPと、Si/SiGe、Si/SiGeCなどの層状半導体と、シリコン・オン・インシユレータ(SOI)と、シリコン・ゲルマニウム・オン・インシユレータ(SGOI)とを含むがこれらに限定されない、任意の半導体材料を含む。典型的には、半導体基板42は、SiなどのSi含有半導体を含む。

20

【0019】

複数の分離領域44は、(図示する)トレンチ分離領域を含むことができ、その代わりに分離領域44はフィールド酸化膜(FOX)分離領域(図示せず)を含むこともできる。分離領域44は、当技術で周知の技法を利用して形成される。例えば、分離領域44がFOX分離領域である場合には、従来のシリコンの局所酸化プロセスを使用することができる。その代わりに、分離領域44がトレンチ分離領域から構成される場合には、トレンチ分離領域44は、リソグラフィ、エッチング、およびトレンチ充填によって形成される。リソグラフィ・ステップは、フォトレジストを基板42の表面に付与すること、フォトレジストを所望のパターンの放射線に露光させること、および従来のレジスト現像液を使用して露光したフォトレジストを現像することを含む。トレンチ分離領域44を形成する際に使用するエッチング・ステップには、例えば反応イオン・エッチング、イオン・ビーム・エッチング、プラズマ・エッチング、またはレーザー・アブレーションなどの乾式エッチング・プロセス、あるいは化学エッチング液が使用される湿式エッチング・プロセスが含まれる。トレンチ充填プロセスには、酸化物などのトレンチ誘電体材料の堆積が含まれる。トレンチ分離領域44の形成はさらに、緻密化プロセスまたは平坦化プロセスあるいはその両方を含んでもよい。

30

【0020】

複数の分離領域44は、カソード・コンタクト領域100Aおよび100Bならびにアノード領域102を含む基板のさまざまな領域を画定する。2つのカソード・コンタクト領域を示してあるが、本発明の方法には、単一のカソード・コンタクト領域を含む構造も想定されている。

40

【0021】

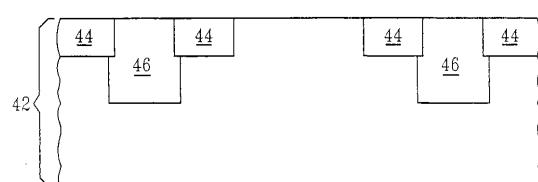

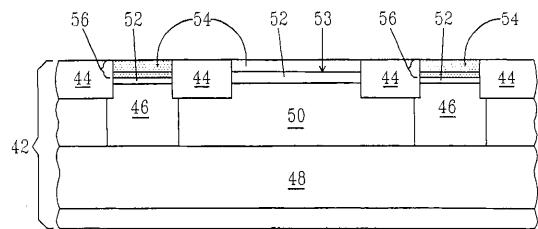

次に、図4に示すように、第1のドーパント領域46は、例えば、カソード・コンタクト領域100Aおよび100B内の基板の露出部内に形成される。第1のドーパント領域46は、リーチスルー・ドーパント領域とも呼ばれることがある。第1のドーパント領域46、すなわちリーチスルー・ドーパント領域は、n型ドーパントまたはp型ドーパントのいずれでもよい第1の導電型のドーパントを含む。好ましくは、第1のドーパント領域46はn型ドーパントを含む。

【0022】

50

第1のドーパント領域46は、リソグラフィおよびイオン注入によって形成される。イオン注入ステップは、当業者には周知の従来のイオン注入条件を利用して実行される。As、Sb、またはPなどのn型ドーパントを含む第1のドーパント領域46を形成するための典型的な条件には、約10<sup>14</sup>～約10<sup>16</sup>原子/cm<sup>2</sup>のイオン・ドーズ量と、約20～約800keVのエネルギーとを選択することが含まれるが、これらには限定されない。本発明のこの点において、BまたはGaなどのp型ドーパントが注入される場合には、約10<sup>14</sup>～約10<sup>16</sup>原子/cm<sup>2</sup>のイオン・ドーズ量と、約10～約400keVのエネルギーとを選択するという条件を使用することができる。この第1のドーパント領域46は、標準的なCMOS FETウェルを利用することによって形成されることが可能、またはバイポーラ・デバイスのサブコレクタと電気的に接触するために一般的に実行されるBiCMOS/バイポーラ・リーチスルーノシャント処理を利用することによって形成することもできる。10

#### 【0023】

使用されるドーズ量およびイオンの種類に応じて、第1のドーパント領域46内のドーパントの濃度は変わる。第1のドーパント領域46内のn型ドーパントの典型的な濃度範囲は、約10<sup>18</sup>～約10<sup>20</sup>原子/cm<sup>3</sup>であり、第1のドーパント領域46内のp型ドーパントの典型的な濃度範囲は、約10<sup>18</sup>～約10<sup>20</sup>原子/cm<sup>3</sup>である。

#### 【0024】

次いで、第1のドーパント領域46を形成する際に使用された注入マスクが、従来の剥離プロセスを利用して構造から除去される。次いで、別の注入マスク(図示せず)が構造上に形成され、第2のドーパント領域48、第3のドーパント領域50、第4のドーパント領域52、および第5のドーパント領域54を形成する際に使用される。第2のドーパント領域48は、サブコレクタ/カソード領域のいずれかを表し、第3のドーパント領域50はコレクタ/ウェル領域を表している。第4のドーパント領域52は超階段接合の下側ドーパント領域を表し、第5のドーパント領域54は超階段接合の上側ドーパント領域を表している。図5は、これらのさまざまなドーパント領域を含む構造を示している。20

#### 【0025】

本発明によれば、第2のドーパント領域48、第3のドーパント領域50、および第4のドーパント領域52はそれぞれ、第1のドーパント領域46と同じ導電型のドーパント、例えば第1の導電型のドーパントを含み、第5のドーパント領域54は、第1の導電型とは反対の第2の導電型ドーパントを含む。非常に好ましい一実施形態では、ドーパント領域46、48、50、および52は、n型ドーパントを含み、領域54はp型ドーパントを含む。それとは反対のドーピング構成も、本明細書では想定されている。第5のドーパント領域54と第4のドーパント領域52との間に形成される界面53は、超階段接合バラクタの接合部を形成する。30

#### 【0026】

本発明では、第2のドーパント領域48の深さD2は、第3のドーパント領域50の深さD3よりも深く、第3のドーパント領域50の深さD3は、第4のドーパント領域52の深さD4よりも深く、第4のドーパント領域52の深さD4は、第5のドーパント領域54の深さD5よりも深い。すなわち、D2 > D3 > D4 > D5である。40

#### 【0027】

本発明によれば、典型的には第2のドーパント領域48が最初に形成され、第4のドーパント領域52および第5のドーパント領域54の形成がそれに続き、第3のドーパント領域50は、第2のドーパント領域48の形成中に形成される。この順序を具体的に記載しているが、注入の他の順序、およびその結果形成されるドーパント領域48、52、および54の他の順序も想定されている。

#### 【0028】

特に、フォトマスクは、従来の堆積プロセスを利用して図4に示した構造の表面に付与される。次いで、リソグラフィ・プロセスが、構造全体を覆うフォトマスクを開口させるために使用される。次いで、第2の注入ステップが実行されて、第1のドーパント領域4

10

20

30

40

50

6、すなわちリーチスルー注入領域と接触するように、基板42の表面下に第2のドーパント領域(サブコレクタ/カソード)48を作製する。図5に示すように、この第2の注入ステップのより浅いテール(tail)により、第2のドーパント領域48の上に第3のドーパント領域50が効果的に作製される。

【0029】

具体的には、第2のドーパント領域48は、サブコレクタ/カソードを基板42内に形成できるイオン注入条件を使用して、第1の導電型、好ましくはn型のドーパントを構造内に注入することによって作製される。第2のドーパント領域48を形成する際に使用されるイオン注入条件は、使用されるドーパント・イオンの種類によって変わることがある。好ましいn型ドーパントの場合、典型的には、約 $5 \times 10^{13}$ ～約 $10^{15}$ 原子/ $\text{cm}^2$ のイオン・ドーズ量、および約300～約1500keVのエネルギーが利用される。<sup>10</sup>p型ドーパントの場合、典型的には、約 $5 \times 10^{13}$ ～約 $10^{15}$ 原子/ $\text{cm}^2$ のイオン・ドーズ量、および約200～約800keVのエネルギーが利用される。第2のドーパント領域48内のドーパント濃度は、注入中に使用されるイオン・ドーズ量に依存している。典型的には、第2のドーパント領域48は、約 $10^{18}$ ～約 $10^{20}$ 原子/ $\text{cm}^3$ のn型ドーパント濃度を有する。p型ドーパントの典型的な濃度は、約 $10^{18}$ ～約 $10^{20}$ 原子/ $\text{cm}^3$ になる。第2のドーパント領域48は、やはりこの第2の注入ステップ中に形成される第3のドーパント領域50よりも高いドーピング濃度を有することに留意されたい。具体的には、第3のドーパント領域50は、第2のドーパント領域48のより浅いドーパント・テールを表している。このため、第3のドーパント領域50は、第2のドーパント48のものと同じ導電型のドーパントを含んでいるが、第3のドーパント領域50のドーパント濃度は、第2のドーパント領域のものよりも低い。典型的には、第3のドーパント領域50、例えばコレクタまたはウェル領域は、約 $10^{17}$ ～約 $10^{19}$ 原子/ $\text{cm}^3$ のn型ドーパント濃度を有する。第3のドーパント領域50の典型的なp型ドーパント濃度は、約 $10^{17}$ ～約 $10^{19}$ 原子/ $\text{cm}^3$ の範囲内となる。<sup>20</sup>

【0030】

次に、第4のドーパント領域52、すなわち超階段接合の下側ドーパント領域が、基板42の露出部内への第1の導電型のドーパントのイオン注入によって形成される。好ましくは、第4のドーパント領域52はn型ドーパントを含む。n型ドーパントが使用される場合には、第4のドーパント領域52を形成する際に使用されるイオン注入ステップには、どのドーパント種が利用されるかに応じて、約 $10^{13}$ ～約 $10^{14}$ 原子/ $\text{cm}^2$ のイオン・ドーズ量、および約30～約300keVのエネルギーが含まれる。p型ドーパントが使用される場合には、注入条件には、約 $10^{13}$ ～約 $10^{14}$ 原子/ $\text{cm}^2$ のイオン・ドーズ量、および約10～約300keVのエネルギーが含まれる。第4のドーパント領域52は、下にある第3のドーパント領域50と比較すると高濃度にドーピングされた領域である。典型的には、第4のドーパント領域52は、約 $10^{17}$ ～約 $10^{19}$ 原子/ $\text{cm}^3$ のn型ドーパント濃度を有する。第4のドーパント領域52の典型的なp型ドーパント濃度は、約 $10^{17}$ ～約 $10^{19}$ 原子/ $\text{cm}^3$ の範囲内となる。<sup>30</sup>

【0031】

第4のドーパント領域52の形成後、第5のドーパント領域54、例えば超階段接合の上側層が、別の注入ステップによって形成される。第1の導電型のドーパントが使用された先の注入とは異なり、第5のドーパント領域54を形成する際に使用される注入ステップは、第1の導電型のドーパントとは導電型の違う第2の導電型ドーパントを利用する。例えば、領域46、48、50、および52がn型の領域を含む好ましい実施形態において、第5のドーパント領域54はp型ドーパントを含む。また、これとは反対のドーパント構成も想定されている。p型ドーパントが第5のドーパント領域54を形成する際に使用される場合、注入条件には、約 $5 \times 10^{14}$ ～約 $10^{16}$ 原子/ $\text{cm}^2$ のイオン・ドーズ量、および約5～約30keVのエネルギーが含まれる。n型ドーパントが使用される場合、第5のドーパント領域54を形成する際に使用される注入条件には、約 $5 \times 10^{14}$ ～約 $10^{16}$ 原子/ $\text{cm}^2$ のドーズ量、および約10～約150keVのエネルギーが<sup>40</sup><sup>50</sup>

含まれる。第5のドーパント領域54内の第2の導電型ドーパントの濃度は、典型的には約 $10^{19}$ ～約 $10^{21}$ 原子/ $\text{cm}^3$ である。

【0032】

第4および第5のドーパント領域52、54それぞれを形成する際に使用されるさまざまな注入物は、カソード領域100Aおよび100B、ならびにアノード領域102のいずれにも有效地に注入されることに留意されたい。本発明によれば、超階段接合、すなわち第5のドーパント領域54の上側ドーパント領域の形成は、バラクタのダイオード層を形成するには十分な濃さであるが、カソード・コンタクト領域において補償されるには十分な薄さのドーズ量で実行される。

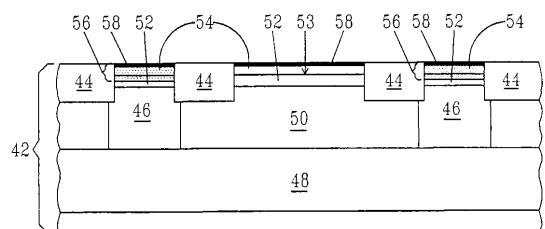

【0033】

次いで、領域48、50、52、および54を作製するために使用された注入マスクが構造から除去され、別の注入マスクが付与されて、カソード領域100Aおよび100Bを露出させるためにパターン化される。次に、第1の導電型のドーパントを用いるCMOS FET処理によって標準的なソース/ドレイン注入が実行され、この注入により、図示のようにカソード領域100Aおよび100B内に高濃度にドーピングされた領域56が形成される。「高濃度にドーピングされた領域」とは、約 $10^{20}$ 原子/ $\text{cm}^3$ 以上のドーパント濃度を有するドーパント領域を意味する。具体的には、図6に示されているように、この注入により、第1のドーパント領域46の表面で第5のドーパント領域54が補償されて、第1のドーパント領域46の表面から下に第2のドーパント領域48まで第1の導電型のドーパント領域を作製する。第5のドーパント領域54が、この第5のドーパント領域54とは反対の導電型である標準的なFETソース/ドレイン注入によって十分に打ち消されるほどに薄いドーズ量で浅い領域で実行される限り、FETのこのソース/ドレインに用いられる注入のみを利用すればよい。

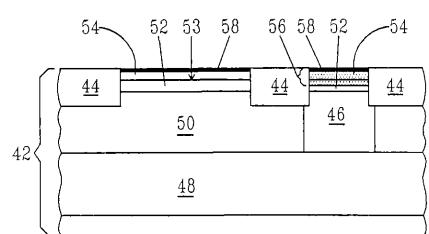

【0034】

上記のように、高濃度にドーピングした領域56で使用される注入マスクが構造から除去され、その後で、シリサイド・コンタクト58が従来のシリサイド化プロセスを利用して形成される。具体的には、シリサイド・コンタクト58は、図6に示す構造の表面上にシリコンと反応可能な金属を堆積させることによって形成される。シリサイドを形成する際に使用される金属には、例えばTi、Ta、Ni、Co、W、Pd、Pt、Rh、Ir、Au、およびそれらの合金などの導電性金属が含まれる。基板がシリコンを含んでいない場合には、金属を形成する前に、例えばEpSiなどのシリコン含有層を基板の表面上に形成することができる。この金属は、例えば化学気相成長法、プラズマ強化化学気相成長法、スパッタリング法、蒸着法、原子層堆積法、化学溶液堆積法、またはその他の同様の方法などの従来の堆積法を利用して形成される。シリサイドの形成を生じさせるのに十分な厚さである限り、金属層の厚さは変えることができ、重要なものではない。次いで、金属を含むこの構造は、金属とシリコンとの間の反応と、それに続く最も低抵抗の相にある安定したシリサイドの形成を生じさせる条件下でアニールされる。シリサイドのアニールは、単一のアニール・ステップを含み、反応しなかった金属を除去するエッチング・ステップがそれに続いてもよく、または通常は第1のアニールよりも高温で第2のアニールが実行される2段階のアニールを含んでもよい。アニールの条件、すなわち時間および温度は、形成されるシリサイドの種類に応じて変えることができ、このような条件は当業者には周知である。

【0035】

図4は、カソード領域100Aおよび100Bならびにアノード領域102の上にシリサイド・コンタクト58を形成するシリサイド層の形成後に形成される構造を示している。図5は、単一のカソード・コンタクトが図示されていること以外は図4に示されたものと同様である構造を示している。

【0036】

図4または図5に示される構造は、1つまたは複数のバイポーラ・デバイス、CMOSデバイス、またはそれらの組合せ(BiCMOSデバイス)を形成できる基板として使用

10

20

30

40

50

することができる。これらの各種デバイスの製作は当業者には周知であり、したがってCMOSまたはバイポーラ・デバイスあるいはその両方の製作は、本明細書では述べる必要がない。

【0037】

本発明の方法が、現行規格に適合する超階段接合バラクタを形成可能であることを説明するために、本発明の超階段接合バラクタと、2マスク・プロセスを使用して作製された従来技術の超階段接合バラクタとを比較した表1を参照する。この従来技術の構造は、カソード領域内にリーチスル注入領域46のみを有する（すなわち、カソード・コンタクト領域から領域56、54、および52を除く）こと以外は、本発明の構造と非常に類似しているように見える。

10

【0038】

【表1】

| 構造  | $C_{max}$<br>(fF/ $\mu m^2$ ) | Tuning<br>Ratio | 2GHz,<br>min Q | 2GHz,<br>max Q | 5GHz,<br>min Q | 5GHz,<br>max Q |

|-----|-------------------------------|-----------------|----------------|----------------|----------------|----------------|

| 従来例 | 2.5                           | 3.4             | 95             | 400            | 35             | 150            |

| 本発明 | 3.0                           | 3.5             | 102            | 415            | 41             | 168            |

20

【0039】

表1に示された結果は、従来技術の超階段接合バラクタよりも単純な方法を使用して作製された本発明の超階段接合バラクタが同様の可同調性および品質係数（Q特性）を有していたことを示している。これらの結果は、本発明の方法が、従来技術の超階段接合バラクタと比較して、可同調性およびQ係数に関して等価な超階段接合バラクタを製造することを示している。本発明の利点は、本発明の超階段接合バラクタが、従来技術において開示された方法よりも単純な方法を利用して形成できるという事実にある。それは、超階段接合バラクタが少なくとも2つのクリティカルなマスキング・レベルを使用して作製される、図1および図2に示された従来技術の構造と異なり、本発明の構造は、補償されたカソード・コンタクトを含むということに留意されたい。

30

【0040】

本発明を、その好ましい実施形態に関して特に示し説明してきたが、本発明の趣旨および範囲から逸脱することなく、形状および詳細において前述の変更およびその他の変更が行えるということが当業者には理解されるであろう。したがって、本発明は、説明され図示された厳密な形状および詳細には限定されず、添付の特許請求項の趣旨および範囲内に含まれることが意図されている。

【図面の簡単な説明】

【0041】

【図1】超階段接合および単一のカソード・コンタクトを含む従来技術の構造を示す断面図である。

40

【図2】超階段接合および2つのカソード・コンタクトまたはラップアラウンド・カソード・コンタクトを含む従来技術の構造を示す断面図である。

【図3】超階段接合および補償されたカソード・コンタクトを含む基板を製作するために本発明において使用される基本処理ステップを示す断面図である。

【図4】超階段接合および補償されたカソード・コンタクトを含む基板を製作するために本発明において使用される基本処理ステップを示す断面図である。

【図5】超階段接合および補償されたカソード・コンタクトを含む基板を製作するために本発明において使用される基本処理ステップを示す断面図である。

【図6】超階段接合および補償されたカソード・コンタクトを含む基板を製作するために本発明において使用される基本処理ステップを示す断面図である。

50

【図7】露出した半導体領域をシリサイド化した後の図6の基板を示す断面図である。

【図8】単一のカソード・コンタクトが形成されること以外は図7に示すものと同様の基板を示す断面図であり、この基板は、単一のリーチスルー注入領域が形成されること以外は図3～図6と同様の基本処理ステップを使用して作製される。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 クールボー、ダグラス、ディー

アメリカ合衆国05452 バーモント州エセックス・ジャンクション セージ・サークル21

(72)発明者 ファーケイ、ステファン、エス

アメリカ合衆国05403 バーモント州サウス・バーリントン ベイ・クレスト・ドライブ11

(72)発明者 ジョンソン、ジェフリー、ビー

アメリカ合衆国05452 バーモント州エセックス・ジャンクション ジュニパー・リッジ・ロード15

(72)発明者 ラッセル、ロバート、エム

アメリカ合衆国05446 バーモント州コルチェスター グラニック・クリーク・ロード225

審査官 村岡 一磨

(56)参考文献 米国特許第06521506(US, B1)

特開平10-256574(JP, A)

特開2002-305309(JP, A)

国際公開第2003/054972(WO, A1)

特開平10-335484(JP, A)

特開平07-147420(JP, A)

特開平01-019779(JP, A)

特開平02-219279(JP, A)

特表2003-526204(JP, A)

特開2003-229581(JP, A)

特開平05-175519(JP, A)

特開2004-193630(JP, A)

米国特許出願公開第2005/0161769(US, A1)

米国特許出願公開第2003/0067026(US, A1)

国際公開第2003/063255(WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/329

H01L 29/93