(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6202972号

(P6202972)

(45) 発行日 平成29年9月27日(2017.9.27)

(24) 登録日 平成29年9月8日(2017.9.8)

(51) Int.Cl.

F 1

G06F 11/10 (2006.01)

G06F 12/00 (2006.01)G06F 11/10 660

G06F 11/10 672

G06F 12/00 597U

請求項の数 30 (全 34 頁)

(21) 出願番号 特願2013-210121 (P2013-210121)

(22) 出願日 平成25年10月7日 (2013.10.7)

(65) 公開番号 特開2014-78229 (P2014-78229A)

(43) 公開日 平成26年5月1日 (2014.5.1)

審査請求日 平成28年10月7日 (2016.10.7)

(31) 優先権主張番号 10-2012-0110859

(32) 優先日 平成24年10月5日 (2012.10.5)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100110364

弁理士 実広 信哉

(72) 発明者 鄭 ▲ヨン▼祐

大韓民国京畿道烏山市陽山洞 (番地なし)

ヒヨクンペクジョンガヤクアパート10

3棟1802号

最終頁に続く

(54) 【発明の名称】メモリシステム及びその読み出し校正方法

## (57) 【特許請求の範囲】

## 【請求項 1】

3ビットデータを格納する複数の第1メモリメモリセル及び1ビットデータを格納する複数の第2メモリセルを含む不揮発性メモリ装置と、

読み出し動作、プログラム動作、及び再プログラム動作を遂行するために前記不揮発性メモリ装置を制御する制御器と、を含み、

前記制御器は、エラー訂正された(ECC(error checking and correction)-performed)第1データを生成するために前記第1データに対するECC動作を遂行するように構成され、

前記第1データは、第1電圧レベルで前記複数の第1メモリセルの第1部分から読み出され、

前記エラー訂正された第1データのエラービットの数が前記ECC動作によって修正可能な閾値(threshold)を超過する時、前記制御器は、エラー訂正された第2データを生成するために第2データに対するリードリトライ(read retry)動作及びECC動作を遂行するように構成され、

前記リードリトライ動作は、第2電圧レベルで前記複数の第1メモリセルの前記第1部分に格納された前記第2データを読み出すことを含み、

ここで、前記第2電圧レベルは、前記第1電圧レベルと異なり、

前記第2データは、前記複数の第1メモリセルの前記第1部分から読み出され、

前記制御器は、前記エラー訂正された第1データ及び前記エラー訂正された第2データ

10

20

のうちのいずれか 1 つを有する第 1 ページデータを前記不揮発性メモリ装置に出力するように構成され、

前記不揮発性メモリ装置は、前記複数の第 2 メモリセルの第 1 部分に前記第 1 ページデータをプログラムするように構成され、

前記不揮発性メモリ装置は、前記複数の第 2 メモリセルの前記第 1 部分で前記プログラムされた第 1 ページデータを読み出すように構成され、

前記不揮発性メモリ装置は、前記複数の第 2 メモリセルの前記第 1 部分から第 1 時間に読み出された前記プログラムされた第 1 ページデータを前記複数の第 1 メモリセルの第 2 部分にプログラムするように構成され、

前記不揮発性メモリ装置は、前記複数の第 2 メモリセルの前記第 1 部分から第 2 時間に読み出された前記プログラムされた第 1 ページデータを前記複数の第 1 メモリセルの前記第 2 部分に再プログラムするように構成されるメモリシステム。

**【請求項 2】**

前記第 1 時間は、前記第 2 時間と異なる請求項 1 に記載のメモリシステム。

**【請求項 3】**

前記制御器は、前記第 1 ページデータに対する前記 E C C 動作を遂行せずに、前記複数の第 2 メモリセルの前記第 1 部分から前記第 1 時間に読み出された前記第 1 ページデータを前記複数の第 1 メモリセルの前記第 2 部分にプログラムするように構成される請求項 1 に記載のメモリシステム。

**【請求項 4】**

前記制御器は、前記複数の第 1 メモリセルの前記第 1 部分から読み出された第 3 データに対する前記リードリトライ動作及び前記 E C C 動作を遂行するように構成される請求項 1 に記載のメモリシステム。

**【請求項 5】**

前記制御器は、前記複数の第 1 メモリセルの前記第 2 部分から読み出された第 3 データに対する前記 E C C 動作を遂行するように構成される請求項 1 に記載のメモリシステム。

**【請求項 6】**

前記複数の第 1 メモリセルの前記第 1 部分及び前記複数の第 1 メモリセルの前記第 2 部分は、同一のメモリブロックに含まれる請求項 5 に記載のメモリシステム。

**【請求項 7】**

前記第 3 データは、第 2 ページデータに含まれ、

前記第 2 ページデータは、前記制御器から前記不揮発性メモリ装置に出力される請求項 5 に記載のメモリシステム。

**【請求項 8】**

前記第 1 ページデータ及び前記第 2 ページデータの各々は、有効なページデータである請求項 7 に記載のメモリシステム。

**【請求項 9】**

前記制御器が外部装置による要請を処理した後に、前記制御器は、前記複数の第 2 メモリセルの前記第 1 部分で前記第 1 ページデータを読み出し書き込むように構成される請求項 1 に記載のメモリシステム。

**【請求項 10】**

前記第 1 ページデータ及び前記第 2 ページデータは、事前に決定された時間周期内に前記制御器から前記不揮発性メモリ装置に出力される請求項 7 に記載のメモリシステム。

**【請求項 11】**

前記不揮発性メモリ装置は、垂直またはスタック型 3 次元アレイ構造 (v e r t i c a l o r s t a c k - t y p e t h r e e - d i m e n s i o n a l a r r a y s t r u c t u r e) を有するメモリセルアレイを含む請求項 1 に記載のメモリシステム。

**【請求項 12】**

複数の第 1 メモリブロックに形成され、セル当たり 1 ビットデータを格納するように構

10

20

30

40

50

成されたフラッシュメモリセルの第1グループと、

複数の第2メモリブロックに形成され、セル当たり3ビットデータを格納するように構成されたフラッシュメモリセルの第2グループと、

を含む不揮発性メモリ装置と、

前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、

前記メモリ制御器は、前記複数の第2メモリブロックのうちのいずれか1つに格納された有効なデータを前記複数の第1メモリブロックのうちの1つ以上のメモリブロックに伝送するためのリードリクライム( read reclaim )動作を遂行するように構成され、

前記リードリクライム動作は、第1時間に前記有効なデータの第1部分に対して遂行され、前記第1時間と異なる第2時間に前記有効なデータの第2部分に対して遂行され、

前記メモリ制御器は、前記複数の第1メモリブロックのうちの前記1つ以上のメモリブロックから読み出された前記有効なデータの第3部分を前記複数の第2メモリブロックの前記いずれか1つと異なる前記複数の第2メモリブロックのうちのいずれか1つに伝送するように1つ以上のプログラム動作を遂行するように構成されるメモリシステム。

#### 【請求項13】

前記メモリ制御器は、前記有効なデータに対するECC動作を遂行せずに、前記有効なデータの前記第3部分を前記複数の第2メモリブロックのうちの他の1つに伝送するように前記1つ以上のプログラム動作を遂行するように構成される請求項12に記載のメモリシステム。

10

#### 【請求項14】

前記1つ以上のプログラム動作の各々は、3段階プログラミング動作である請求項12に記載のメモリシステム。

20

#### 【請求項15】

前記3段階プログラミング動作は、第1プログラム段階及び前記第1プログラム段階の後に発生する第2プログラム段階を含み、

前記第2プログラム段階に対応する第2閾値電圧幅は、前記第1プログラム段階に対応する第1閾値電圧幅より狭い請求項14に記載のメモリシステム。

#### 【請求項16】

前記リードリクライム動作は、前記有効なデータの少なくとも一部に対するリードリトライ動作を含む請求項12に記載のメモリシステム。

30

#### 【請求項17】

前記リードリクライム動作は、第1時間周期及び第2時間周期の間に遂行され、

前記第1時間周期及び前記第2時間周期は、互いに分離される請求項16に記載のメモリシステム。

#### 【請求項18】

前記不揮発性メモリ装置は、垂直またはスタック型3次元アレイ構造を有するメモリセルアレイを含む請求項12に記載のメモリシステム。

#### 【請求項19】

3ビットデータを格納する複数の第1メモリメモリセル及び1ビットデータを格納する複数の第2メモリセルを有する不揮発性メモリ装置及び前記不揮発性メモリ装置を制御する制御器を含む不揮発性メモリシステムの動作方法において、

40

第1電圧レベルで、前記複数の第1メモリセルの第1部分から第1データを読み出す段階と、

エラー訂正された第1データを生成するために前記第1データに対するECC(error checking and correction)動作を遂行する段階と、

前記エラー訂正された第1データのエラービットの個数が前記ECC動作によって訂正可能な閾値を超過する時、第2電圧レベルで、前記複数の第1メモリセルの前記第1部分から第2データを読み出す段階と、

エラー訂正された第2データを生成するために前記第2データに対するECC動作を遂

50

行する段階と、

前記エラー訂正された第1データ及び前記エラー訂正された第2データのうちのいずれか1つを有する第1ページデータを前記不揮発性メモリ装置に出力する段階と、

前記複数の第2メモリセルの第1部分に前記第1ページデータをプログラムする段階と、

第1時間に前記複数の第2メモリセルの前記第1部分から前記プログラムされたページデータを読み出す段階と、

前記第1時間に読み出された前記プログラムされた第1ページデータを前記複数の第1メモリセルの第2部分にプログラムする段階と、

第2時間に前記複数の第2メモリセルの前記第1部分から前記プログラムされた第1ページデータを読み出す段階と、

前記第2時間に読み出された前記プログラムされた第1ページデータを前記複数の第1メモリセルの前記第2部分に再プログラムする段階と、を含む方法。

**【請求項20】**

前記複数の第2メモリセルの前記第2部分に前記第1ページデータをプログラムする段階は、前記第1ページデータに対するECC動作無しで遂行される請求項19に記載の方法。

**【請求項21】**

前記複数の第1メモリセルの第3部分から読み出された第3データに対するECC動作を遂行する段階をさらに含み、

前記第3データは、第2ページデータに含まれ、

前記第2ページデータは、前記制御器から前記不揮発性メモリ装置に出力され、

前記第1ページデータ及び前記第2ページデータは、事前に決定された時間周期内に前記制御器から前記不揮発性メモリ装置に出力される請求項19に記載の方法。

**【請求項22】**

前記制御器が外部装置の要請を処理した後に、前記第1ページデータ及び前記第2ページデータは、前記制御器から前記不揮発性メモリ装置に出力される請求項21に記載の方法。

**【請求項23】**

前記不揮発性メモリ装置は、垂直またはスタック型3次元アレイ構造を有するメモリセルアレイを含む請求項19に記載の方法。

**【請求項24】**

3ビットデータを格納する複数の第1メモリメモリセル及び1ビットデータを格納する複数の第2メモリセルを含むメモリセルアレイを含み、前記メモリセルアレイは、垂直またはスタック型3次元アレイ構造である不揮発性メモリ装置と、

読み出し動作、プログラム動作、及び再プログラム動作を遂行するために前記不揮発性メモリ装置を制御する制御器と、を含み、

前記制御器は、エラー訂正された第1データを生成するために前記第1データに対するECC動作を遂行するように構成され、

前記第1データは、第1電圧レベルで前記複数の第1メモリセルの第1部分から読み出され、

前記エラー訂正された第1データのエラービットの個数が前記ECC動作によって訂正可能な閾値を超過する時、前記制御器は、エラー訂正された第2データを生成するためにリードリトライ動作及びECC動作を遂行するように構成され、

前記リードリトライ動作は、前記第1電圧レベルと異なる第2電圧レベルで前記複数の第1メモリセルの前記第1部分に格納された第2データを読み出すことを含み、

前記第2データは、前記複数の第1メモリセルの前記第1部分から読み出され、

前記制御器は、前記エラー訂正された第1データ及び前記エラー訂正された第2データのうちのいずれか1つを含む第1ページデータを前記不揮発性メモリ装置に出力するように構成され、

10

20

30

40

50

前記不揮発性メモリ装置は、前記複数の第2メモリセルの第1部分に前記第1ページデータをプログラムするように構成され、

前記不揮発性メモリ装置は、前記複数の第2メモリセルの前記第1部分から前記プログラムされた第1ページデータを読み出すように構成され、

前記不揮発性メモリ装置は、第1時間で前記複数の第2メモリセルの前記第1部分から読み出された前記プログラムされた第1ページデータを前記複数の第1メモリセルの第2部分にプログラムするように構成され、

前記不揮発性メモリ装置は、第2時間で前記複数の第2メモリセルの前記第1部分から読み出された前記プログラムされた第1ページデータを前記複数の第1メモリセルの前記第2部分に再プログラムするように構成され、

前記第1時間は、前記第2時間と異なるメモリシステム。

#### 【請求項25】

前記制御器は、前記第1ページデータに対する前記ECC動作を遂行せずに、前記第1時間に前記複数の第2メモリセルの前記第1部分から読み出された前記第1ページデータを前記複数の第1メモリセルの前記第2部分にプログラムするように構成される請求項24に記載のメモリシステム。

#### 【請求項26】

前記制御器は、前記複数の第1メモリセルの前記第1部分から読み出された第3データに対する前記リードリトライ動作及び前記ECC動作を遂行するように構成される請求項24に記載のメモリシステム。

#### 【請求項27】

前記制御器は、前記複数の第1メモリセルの前記第2部分から読み出された第3データに対する前記ECC動作を遂行するように構成される請求項24に記載のメモリシステム。

#### 【請求項28】

前記複数の第1メモリセルの前記第1部分と前記複数の第1メモリセルの前記第2部分とは、同一のメモリブロックに含まれる請求項27に記載のメモリシステム。

#### 【請求項29】

前記第3データは、第2ページデータに含まれ、

前記第2ページデータは、前記制御器から前記不揮発性メモリ装置に出力される請求項27に記載のメモリシステム。

#### 【請求項30】

前記第1ページデータ及び前記第2ページデータの各々は、有効なページデータである請求項29に記載のメモリシステム。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体メモリ装置に係り、さらに具体的には、不揮発性メモリ装置を含むメモリシステムに関する。

#### 【背景技術】

#### 【0002】

半導体メモリは、一般的に、衛星から消費者電子技術までの範囲に属するマイクロプロセッサに基づいたアプリケーション及びコンピュータのようなデジタルロジック設計の最も必須的なマイクロ電子素子である。したがって、高集積度と高速な動作速度のための縮小(scaling)を通じて得られるプロセスの向上及び技術開発を含んだ半導体メモリの製造技術の進歩は、他のデジタルロジック系列の性能基準を確立するのに役立つ。

#### 【0003】

半導体メモリ装置は、大きく、揮発性半導体メモリ装置と不揮発性半導体メモリ装置とに分けられる。揮発性半導体メモリ装置において、ロジック情報は、スタティックRAMの場合、双安定フリップフロップのロジック状態を設定することにより、またはダイナミ

10

20

30

40

50

ツクランダムアクセスメモリの場合、キャパシタの充電を通じて格納される。揮発性半導体メモリ装置の場合、電源が印加される間、データが格納されて読み出され、電源が遮断されれば、データを失う。

#### 【0004】

MROM、PROM、EPROM、EEPROM、PRAMなどのような不揮発性半導体メモリ装置は、電源が遮断されてもデータを格納することができる。不揮発性メモリのデータ格納状態は、使用される製造技術によって永久的、または再プログラム可能である。不揮発性半導体メモリ装置は、コンピュータ、航空電子工学、通信、消費者電子技術産業のような広い範囲の応用で、プログラム及びマイクロコードの格納のために使用されている。高速で、再プログラム可能な不揮発性メモリを要求するシステムで、不揮発性RAM(nvRAM)のような装置でも使用可能である。さらに、応用指向の仕事のためのパフォーマンスを最適化するためにいくつかの追加のロジック回路を含む特定のメモリ構造が開発されている。

#### 【0005】

不揮発性半導体メモリ装置において、MROM、PROM、及びEPROMは、システム自体で消去と書き込みが自由ではなくて、一般ユーザが記憶内容を更新することは容易ではない。これに対し、EEPROM、PRAMなどの不揮発性半導体メモリ装置は、電気的に消去と書き込みが可能なので、継続的な更新が必要なシステムプログラミング(system programming)や補助記憶装置への応用が拡大している。

#### 【先行技術文献】

10

#### 【特許文献】

#### 【0006】

【特許文献1】米国特許出願公開第2011/0222342号明細書

20

【特許文献2】米国特許出願公開第2010/0088574号明細書

【特許文献3】米国特許出願公開第2010/0322007号明細書

【特許文献4】米国特許出願公開第2010/0010040号明細書

【特許文献5】米国特許出願公開第2010/0062715号明細書

【特許文献6】米国特許出願公開第2010/0199081号明細書

【特許文献7】米国特許出願公開第2010/0309237号明細書

【特許文献8】米国特許出願公開第2010/0315325号明細書

30

【特許文献9】米国特許第7529124号明細書

【特許文献10】米国特許第6858906号明細書

【特許文献11】米国特許出願公開第2004/0169238号明細書

【特許文献12】米国特許出願公開第2006/0180851号明細書

【特許文献13】韓国特許第673020号明細書

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

本発明の目的は、ホストのタイムアウトを防止することができるメモリシステムを提供することにある。

40

#### 【課題を解決するための手段】

#### 【0008】

本発明の一特徴は、セルあたりmビットのデータが格納されるメモリブロックで構成された第1メモリ領域とセルあたりnビットのデータが格納されるメモリブロックで構成された第2メモリ領域とを含む不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器とを含み、読み出し動作の時に選択された前記第2メモリ領域のメモリブロックが読み出し校正動作の対象として決められた場合、前記メモリ制御器は、前記読み出し校正動作の対象となる第2メモリ領域のメモリブロックの有効データのすべてが前記第1メモリ領域のメモリブロックのうちの少なくとも一つ以上のメモリブロックにプログラムされる時、前記第2メモリ領域のメモリブロックに対する読み出し校

50

正動作を完了したと処理するメモリシステムを提供することにある。

【0009】

例示的な実施形態において、前記メモリ制御器は、ホストの書き込み要請の時に前記読み出し校正動作の少なくとも一部を実行する。

例示的な実施形態において、前記メモリ制御器は、ホストによって要請された書き込み動作が完了した後、前記読み出し校正動作の少なくとも一部を実行する。

例示的な実施形態において、前記読み出し校正動作の対象となる前記第2メモリ領域のメモリブロックの有効データのうち、前記要請された書き込み動作の時、移動するデータの量は、ホストによって要請された書き込み動作が完了した後、前記ホストのタイムアウト区間のうち、残った時間を考慮して決められる。

10

例示的な実施形態において、書き込み動作が要請される時、前記読み出し校正動作の対象となる前記第2メモリ領域のメモリブロックの有効データのうち、前記第1メモリ領域の一つのメモリブロックの格納容量に対応するデータは、前記第1メモリ領域のメモリブロックに移動する。

【0010】

例示的な実施形態において、前記少なくとも一つ以上のメモリブロックに格納されたデータは、前記メモリ制御器のバックグラウンド動作の時に前記第2メモリ領域のメモリブロックのうちの一つのメモリブロックに移動する。

例示的な実施形態において、前記少なくとも一つ以上のメモリブロックのうち、空の格納空間を有するメモリブロックを除いた残りのメモリブロックに格納されたデータは、前記メモリ制御器のバックグラウンド動作の時、前記第1メモリ領域のメモリブロックのうちデータで完全に満たされたメモリブロックのデータと共に前記第2メモリ領域のメモリブロックのうちで選択されたメモリブロックに移動し、前記第2メモリ領域の選択されたメモリブロックは、オープンワードラインを含まない。

20

例示的な実施形態において、前記mビットのデータは、1ビットのデータであり、前記nビットのデータは、3ビットのデータである。

【0011】

例示的な実施形態において、前記メモリ制御器は、読み出し動作の時、読み出し校正動作の対象として決められた前記第2メモリ領域のメモリブロックを示すキュー情報を格納するバッファメモリを含む。

30

例示的な実施形態において、書き込み動作が要請されるたびに、前記メモリ制御器は、ホストのタイムアウト条件を回避するように、前記バッファメモリのキュー情報に対応する前記第2メモリ領域のメモリブロックに対する前記読み出し校正動作を時分割方式で行う。

例示的な実施形態において、前記読み出し校正動作の対象となる前記第2メモリ領域のメモリブロックの有効データのうち、前記第1メモリ領域の一つのメモリブロックの格納容量に対応するデータは、前記書き込み動作が要請された時、前記第1メモリ領域のメモリブロックに移動する。

【0012】

例示的な実施形態において、前記メモリ制御器は、前記第2メモリ領域のメモリブロックに読み出されたデータの訂正できないエラーに対するソフトウェアエラー訂正動作を実行し、前記第2メモリ領域のメモリブロックに読み出されたデータのエラーがソフトウェアエラー訂正を通じて訂正される時、前記キュー情報を前記バッファメモリに格納する。

40

例示的な実施形態において、前記メモリ制御器は、前記第2メモリ領域のメモリブロックに読み出されたデータが訂正できない場合、読み出しリトライ動作を実行し、前記読み出しリトライ動作を通じて前記第2メモリ領域のメモリブロックに読み出されたデータが訂正可能である時、前記キュー情報を前記バッファメモリに格納する。

例示的な実施形態において、前記メモリ制御器は、前記第2メモリ領域のメモリブロックに読み出されたデータのエラービットの数が基準を超えた時、前記キュー情報を前記バッファメモリに格納する。

50

## 【0013】

本発明の別の特徴は、セルあたり $m$ ビットのデータが格納される第1メモリブロックとセルあたり $n$ ビットのデータが格納される第2メモリブロックとを含む不揮発性メモリ装置を制御するメモリ制御器の読み出し校正方法を提供する。読み出し校正方法は、読み出し校正動作の対象となる第2メモリブロックが存在するか否かを判別し、読み校正動作の対象となる第2メモリブロックが存在する場合、前記第2メモリブロックの有効なデータを前記第1メモリブロックのうちの少なくとも一つ以上のメモリブロックにプログラムすることによって、前記読み出し校正動作を完了したと処理することを含む。

## 【0014】

例示的な実施形態において、読み出し校正動作の対象となる第2メモリブロックに対する読み出し校正動作は、ホストのタイムアウト条件を回避するように時分割方式で実行される。10

例示的な実施形態において、前記読み出し校正動作の少なくとも一部は、書き込み動作が要請される時に実行される。

例示的な実施形態において、前記読み出し校正動作の少なくとも一部は、ホストによって要請された書き込み動作が完了した後に実行される。

## 【0015】

例示的な実施形態において、読み出し校正動作の対象となる前記第2メモリブロックの有効データのうち、ホストによって要請された書き込み動作の時移動されるデータの量は、前記書き込み動作が完了した後、前記ホストのタイムアウト区間のうち、残った時間を考慮して決められる。20

例示的な実施形態において、読み出し校正動作の対象となる前記第2メモリブロックの有効データのうち、第1メモリブロックの格納容量に対応するデータは、書き込み動作が要請される時、前記第1メモリブロックに移動する。

例示的な実施形態において、前記少なくとも一つ以上のメモリブロックに格納されたデータは、前記メモリ制御器のガーベッジコレクションの動作の時に前記第2メモリブロックのうちの一つのメモリブロックに移動する。

## 【0016】

例示的な実施形態において、前記少なくとも一つ以上のメモリブロックのうち、空の格納空間を有するメモリブロックを除いた残りのメモリブロックに格納されたデータは、前記メモリ制御器のガーベッジコレクションの動作の時に前記第1メモリブロックのうち、データで完全に満たされたメモリブロックのデータと共に前記第2メモリブロックのうち選択されたメモリブロックに移動し、選択された前記第2メモリブロックは、オープンワードラインを含まない。30

例示的な実施形態において、前記 $m$ ビットのデータは、1ビットのデータであり、前記 $n$ ビットのデータは、3ビットのデータである。

例示的な実施形態において、前記メモリ制御器から提供されるデータは、バッファプログラム動作により前記第1メモリブロックに格納され、前記第1メモリブロックに格納されたデータは、メインプログラム動作により前記第2メモリブロックに格納される。

## 【0017】

本発明のもう一つの特徴は、セルあたり $m$ ビットのデータが格納される第1メモリブロックとセルあたり $n$ ビットのデータが格納される第2メモリブロックとを含む不揮発性メモリ装置を制御するメモリ制御器の動作方法を提供する。動作方法は、第2メモリブロックから読み出されたデータのエラーが読み出し校正動作を決めるための基準を超えた時に、前記第2メモリブロックが読み出し校正動作の対象であることを示すキュー情報を格納し、ホストの要請の時、前記キュー情報に基づいて、読み出し校正動作の対象となる第2メモリブロックが存在するか否かを判別し、読み出し校正動作の対象となる第2メモリブロックが存在する時、前記第2メモリブロックの有効なデータを前記第1メモリブロックのうちの少なくとも一つ以上のメモリブロックにプログラムし、ガーベッジコレクションの際、前記少なくとも一つ以上のメモリブロックに格納されたデータを前記第2メモリブ4050

ロックのうちの一つのメモリブロックにプログラムすることを含み、前記読み出し校正動作は、前記第2メモリブロックの有効なデータを前記第1メモリブロックのうちの少なくとも一つ以上のメモリブロックにプログラムすることによって完了したと処理される。

#### 【0018】

例示的な実施形態において、読み出し校正動作の対象となる第2メモリブロックが存在するか否かを判別するのは、ホストの書き込み要請の時に行われる。

例示的な実施形態において、前記少なくとも一つ以上のメモリブロックのうち、空の格納空間を有するメモリブロックを除いた残りのメモリブロックに格納されたデータは、前記ガーベッジコレクションの際、前記第1メモリブロックのうちデータで完全に満たされたメモリブロックのデータと共に前記第2メモリブロックのうち選択されたメモリブロックに移動し、前記第2メモリブロックの選択されたメモリブロックは、オープンワードラインを含まない。10

例示的な実施形態において、前記mビットのデータは、1ビットのデータであり、前記nビットのデータは、3ビットのデータである。

例示的な実施形態において、前記第2メモリブロックから読み出されたデータは、LSBページデータ、CSBページデータ、またはMSBページデータである。

#### 【発明の効果】

#### 【0019】

本発明によれば、ホストのタイムアウトを防止すると共に、TLCブロックでオープンワードラインが発生することを防止することができる。20

#### 【図面の簡単な説明】

#### 【0020】

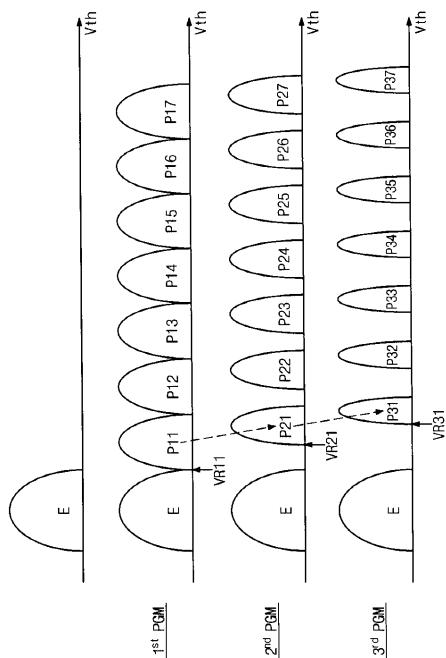

【図1】本発明に係る再プログラミング方式により実行されるメインプログラム動作を示す図である。

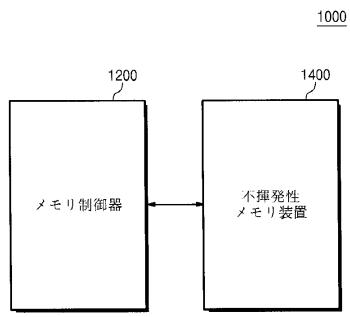

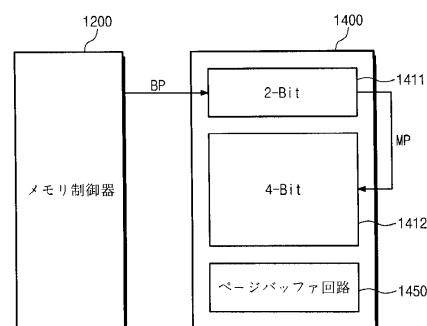

【図2】本発明の例示的な実施形態に係るメモリシステムを概略的に示すブロック図である。

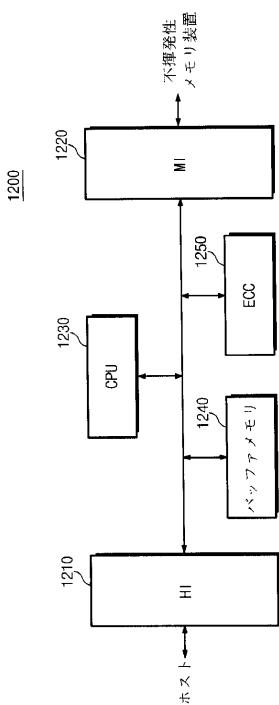

【図3】図2に示したメモリ制御器を概略的に示すブロック図である。

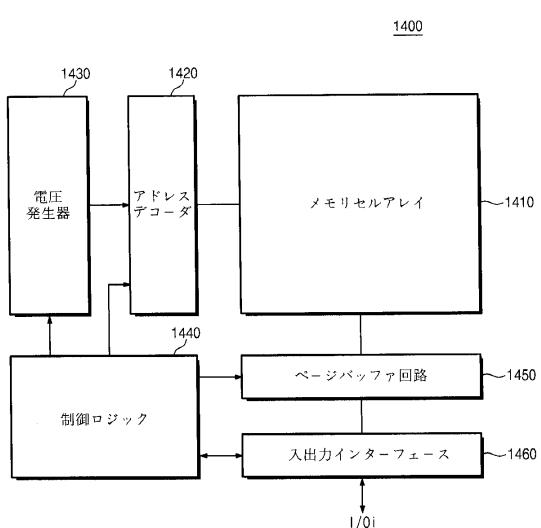

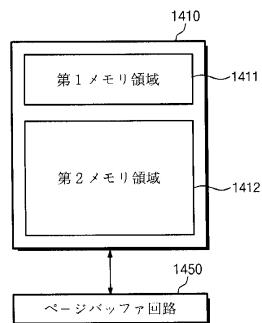

【図4】図2に示した不揮発性メモリ装置を概略的に示すブロック図である。

【図5】図4に示したメモリセルアレイを概略的に示すブロック図である。

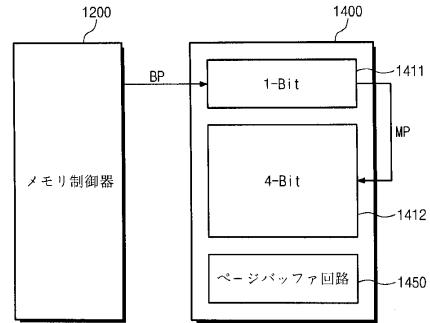

【図6A】本発明の例示的な実施形態に係るマルチビットメモリ装置の第1及び第2メモリ領域に対する様々な組み合わせを説明するための図である。30

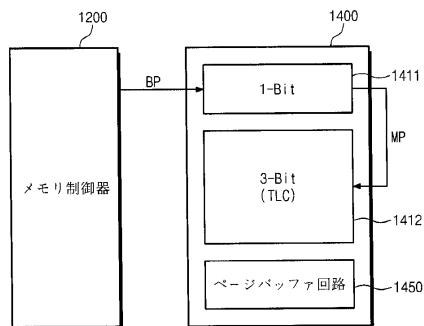

【図6B】本発明の例示的な実施形態に係るマルチビットメモリ装置の第1及び第2メモリ領域に対する様々な組み合わせを説明するための図である。

【図6C】本発明の例示的な実施形態に係るマルチビットメモリ装置の第1及び第2メモリ領域に対する様々な組み合わせを説明するための図である。

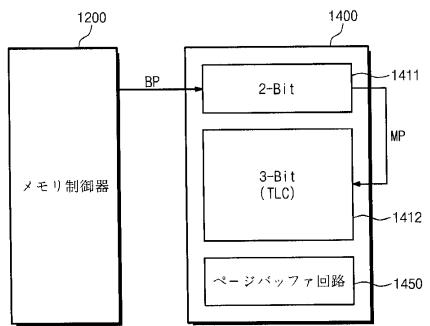

【図6D】本発明の例示的な実施形態に係るマルチビットメモリ装置の第1及び第2メモリ領域に対する様々な組み合わせを説明するための図である。

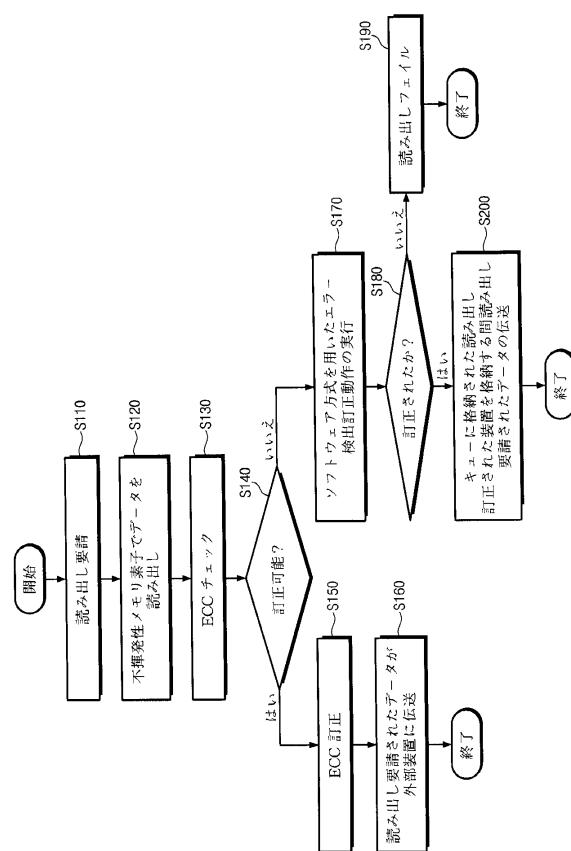

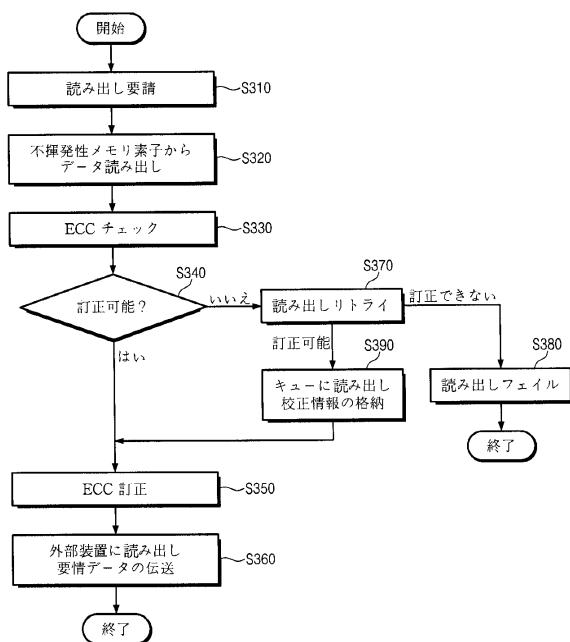

【図7】本発明の例示的な実施形態に係るメモリシステムの読み出し方法を示すフローチャートである。

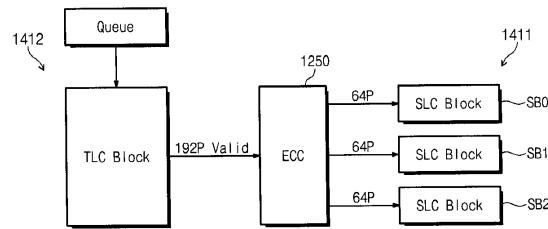

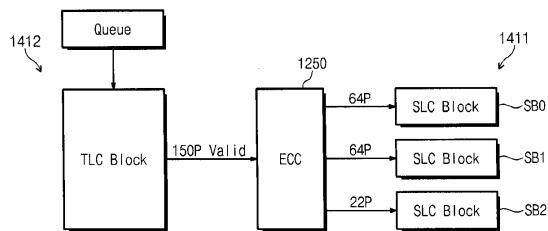

【図8A】本発明の例示的な実施形態に係る読み出し校正動作を示す図である。40

【図8B】本発明の例示的な実施形態に係る読み出し校正動作を示す図である。

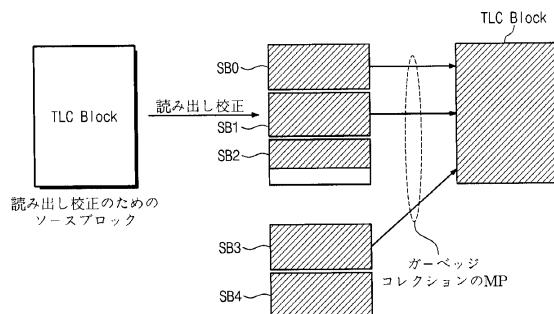

【図9】読み出し校正動作によって生成されたSLCブロックのデータがTLCブロックに格納される例を示す図である。

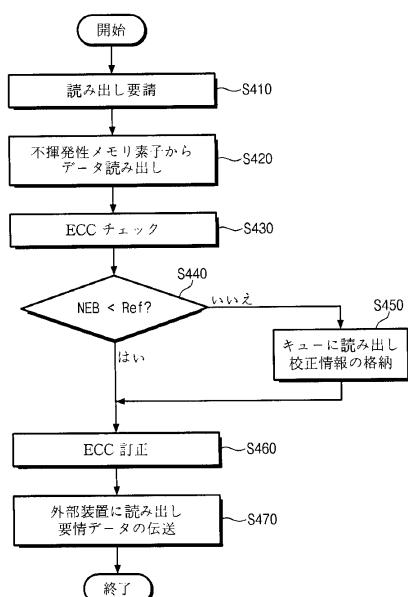

【図10】本発明の別の例示的な実施形態に係るメモリシステムの読み出し方法を示すフローチャートである。

【図11】本発明のさらに別の例示的な実施形態に係るメモリシステムの読み出し方法を示すフローチャートである。

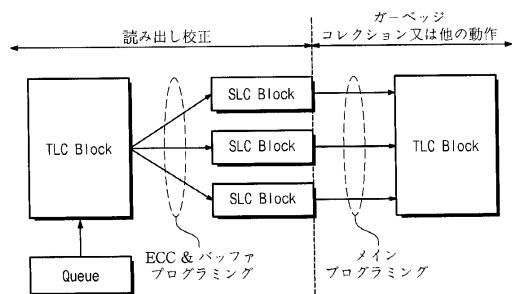

【図12】本発明の例示的な実施形態に係るメモリシステムの読み出し校正方法を示すブロック図である。

【図13】本発明の実施形態に係るコンピューティングシステムを概略的に示すブロック50

図である。

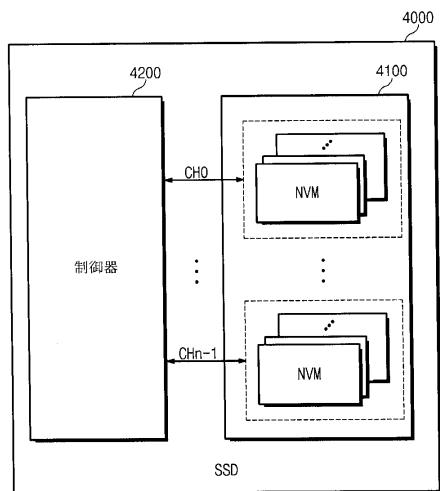

【図14】本発明の実施形態に係る半導体ドライブを概略的に示すブロック図である。

【図15】図14に示した半導体ドライブを利用したストレージを概略的に示すブロック図である。

【図16】図14に示した半導体ドライブを利用したストレージサーバを概略的に示すブロック図である。

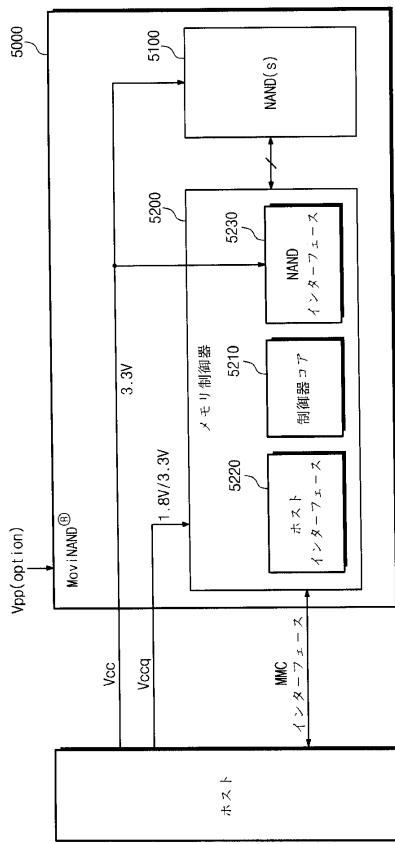

【図17】本発明に係るMoViNANDを概略的に示すブロック図である。

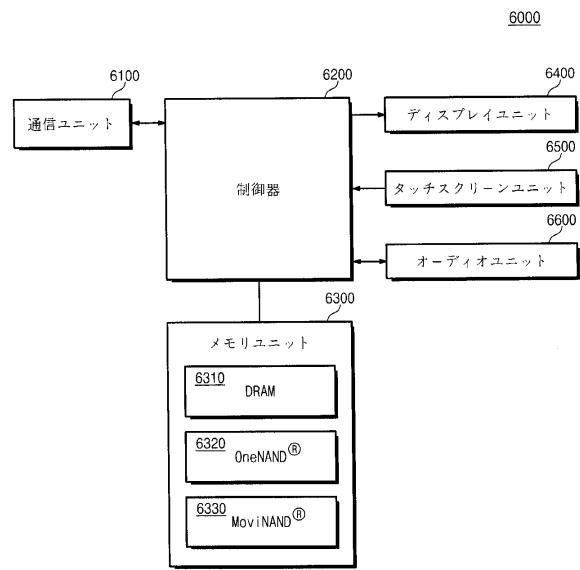

【図18】本発明に係る通信装置を概略的に示すブロック図である。

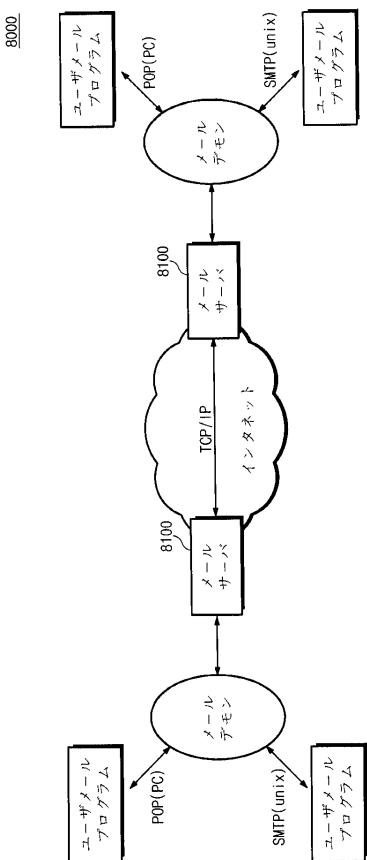

【図19】本発明の実施形態に係る半導体ドライブが適用されるシステムを概略的に示す図である。

10

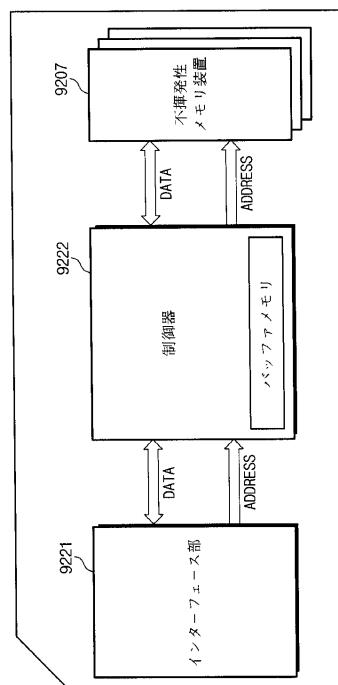

【図20】本発明の実施形態に係るメモリカードを概略的に示すブロック図である。

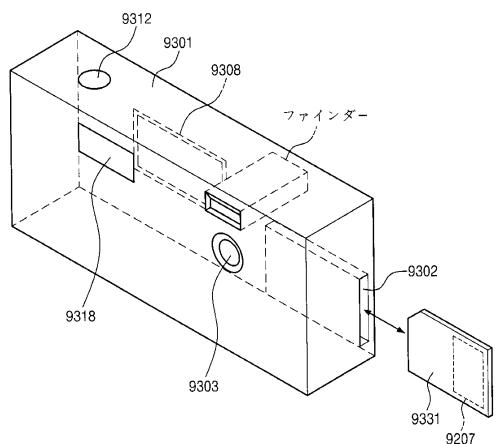

【図21】本発明の実施形態に係るデジタルスチルカメラ(digital still camera)を概略的に示すブロック図である。

【図22】図21のメモリカードが使用される様々な応用分野を示す図である。

【発明を実施するための形態】

【0021】

本発明の利点及び特徴、そしてそれを達成する方法は、添付の図面とともに実施形態を通じて詳細に説明される。しかし、本発明は、ここに説明される実施形態に限定されず、他の形態への具体化も可能である。本実施形態は、本発明が属する技術分野における通常の知識を有する者に本発明の技術的思想を容易に実施できる程度に詳細に説明するためだけに提供されるものである。

20

図面において、本発明の実施形態は、図示された特定の形態に限定されず、明確性のために誇張されている。また、明細書の全体にわたって同一の参照番号として表示された部分は、同一の構成要素を示す。

【0022】

本明細書で「及び／または」という表現は、前後に並べた構成要素の中で少なくとも一つを含む意味として使われる。また、「接続される／結合される」という表現は、他の構成要素に直接接続するか、または他の構成要素を介して間接的に接続されることを含む意味として使われる。本明細書で、単数として使われた用語は、それについての単数であることを示す明白な背景に関する言及がない限り、複数も含むものである。また、本明細書で使われる「含む」に言及された構成要素、段階、動作及び素子は、1つまたはそれ以上の他の構成要素、段階、動作、素子及び装置の存在または付加を意味する。

30

【0023】

各メモリセルに格納されるデータビットの数が増加するにつれて（または、一つのワードラインに対応するページ（または、ページデータ）の数が増加するにつれて）、様々なプログラミング技術が提案されている。例えば、オンチップバッファプログラム方法は、マルチビットメモリ装置を含むメモリシステムに適用されている。オンチップバッファプログラム方法が使われることによって、メモリシステムのメモリ制御器内に備えられたバッファメモリのサイズを減らすことが可能である。オンチップバッファプログラム方法は、メモリ制御器のバッファメモリに一時格納されたデータをマルチビットメモリ装置の第1メモリ領域にプログラムすることと、マルチビットメモリ装置の第1メモリ領域に格納されたデータをマルチビットメモリ装置の第2メモリ領域にプログラムすることとを含む。バッファメモリに一時格納されたデータをマルチビットメモリ装置の第1メモリ領域にプログラムする動作を“バッファプログラム動作”といい、マルチビットメモリ装置の第1メモリ領域に格納されたデータをマルチビットメモリ装置の第2メモリ領域にプログラムする動作を“メインプログラム動作”という。すなわち、オンチップバッファプログラム方法は、バッファプログラム動作とメインプログラム動作とを含む。マルチビットメモリ装置は、第1及び第2メモリ領域の以外のメモリ領域をさらに含むことができる。

40

【0024】

例えば、バッファプログラム動作は、第1メモリ領域に対する最小プログラム単位に対

50

応するデータがメモリ制御器のバッファメモリに集められる時に行われ、メインプログラム動作は、第2メモリ領域に対する最小プログラム単位に対応するデータがマルチビットメモリ装置の第1メモリ領域に集められる時、または第1メモリ領域の使用可能な格納空間が不足する時に行われる。ここで、第1メモリ領域の最小プログラム単位に対応するデータは、1ページのデータであり、第2メモリ領域の最小プログラム単位に対応するデータは、複数のページのデータである。複数のページの数は、セルあたりのビット数に応じて決められる。例えば、セルあたりのビット数が3の場合、第2メモリ領域に対する最小プログラム単位に対応するデータは、3ページのデータである。第1及び第2メモリ領域の各々に対する最小プログラム単位はここに開示されたことに限定されない。上述の説明によると、第1メモリ領域の最小プログラム単位に対応するデータがバッファメモリに集められるたびに、バッファメモリのデータがマルチビットメモリ装置の第1メモリ領域にプログラムされ、その結果、バッファメモリのサイズを小さくすることが可能である。10

#### 【0025】

オンチップバッファプログラム方法を採用するメモリシステムにおいて、メインプログラム動作は、様々なプログラミング方式を用いて実行される。例えば、メインプログラム動作は、再プログラム方式に基づいて行われる。以下、再プログラム方式を用いたメインプログラム動作を図1を参照して詳細に説明する。

図1は、本発明に係る再プログラミング方式により実行されるメインプログラム動作を示す図である。図1は、3ビットデータ（または、LSBページのデータ、CSBページのデータ、MSBページのデータで構成される3ページのデータ）が再プログラム方式によってプログラムされる例を示す。しかし、再プログラム方式は3ビットデータに限定されない。再プログラム方式は、第1プログラム段階、第2プログラム段階、及び第3プログラム段階を含み、これは、以下詳細に説明する。20

#### 【0026】

第1プログラム段階は、各メモリセルが8つの状態E、P11、P12、P13、P14、P15、P16、P17のうち3ビットのデータに対応する状態を有するように行われる。8つの状態E、P11～P17は、図1に示すように、読み出しマージンなしに互いに隣接することができる。すなわち、第1プログラム段階では、3ビットのデータが概略的にプログラムされる。ここで、3ビットのデータは、バッファプログラム動作により、第1メモリ領域にプログラムされたデータであり、第1プログラム段階で、第1メモリ領域から読み出される。30

#### 【0027】

例示的な実施形態において、第1プログラミング段階は、プログラムループの繰り返しの時にプログラム電圧が一定の增加分だけ増加する増加型ステップパルスプログラム（Incremental Step Pulse Programming：ISPP）技術に基づいて行われる。

例示的な実施形態において、第1プログラミング段階は検証動作を含む。検証動作の時、少なくとも一つのプログラム状態のみに対して検証動作を実行することができる。例えば、第1プログラミング段階で、プログラム状態P12、P14、P16の検証動作が実行される一方、プログラム状態P11、P13、P15、P17の検証動作は実行されない。つまり、プログラム状態P12、P14、P16が検証パスされれば、第1プログラミング段階は終了する。40

#### 【0028】

第2プログラミング段階は、第1プログラミング段階を通じて形成された概略的な状態（rough states）P11～P17をより細密な状態P21～P27に再プログラムするために行われる。ここで、状態P21～P27は、図1に示すように、所定の読み出しマージンを有するよう隣接することができる。つまり、第2プログラミング段階では、第1プログラミング段階でプログラムされた3ビットのデータが再プログラムされる。上述のように、第2プログラミング段階で使われる3ビットのデータは、第1プログラミング段階で使われたものと同様であり、第1メモリ領域から再び読み出される。図50

1に示すように、第1プログラミング段階の状態P11は、第2プログラミング段階の状態P21に再プログラムされる。これは、第2プログラミング段階の状態P21に対応する閾値電圧のばらつきが第1プログラミング段階の状態P11に対応する閾値電圧のばらつきより狭く形成されるようにする。すなわち、第2プログラミング段階の状態P21を検証するための検証電圧VR21は、第1プログラミング段階の状態P11を検証するための検証電圧VR11より高い。

#### 【0029】

例示的な実施形態において、第2プログラミング段階は、ISP技術に基づいて行われる。

例示的な実施形態において、第2プログラミング段階は、検証動作を含む。検証動作はすべてのプログラム状態に対して行われる。すべてのプログラム状態P21～P27が検証パスされれば、第2プログラミング段階は終了する。

10

#### 【0030】

第3プログラム段階は、第2プログラミング段階でプログラムされた状態P21～P27をより細密な状態P31～P37に再プログラムするために行われる。

ここで、状態P31～P37は、図1に示すように、第2プログラミング段階の読み出しマージンより大きい読み出しマージンを有するように隣接することができる。すなわち、第3プログラム段階では、第2プログラミング段階でプログラムされた3ビットのデータが再プログラムされる。上述のように、第3プログラム段階で使われる3ビットのデータは、第1及び第2プログラミング段階で使われたものと同様であり、第1メモリ領域から再び読み出される。第3プログラミング段階が行われることによって、第2プログラミング段階の状態P21は、第3プログラミング段階の状態P31に再プログラムされる。これは、第3プログラミング段階の状態P31に対応する閾値電圧のばらつきが第2プログラミング段階の状態P21に対応する閾値電圧のばらつきより狭くする。すなわち、第3プログラム段階の状態31を検証するための検証電圧VR31が第2プログラミング段階の状態P21を検証するための検証電圧VR21より高い。

20

#### 【0031】

例示的な実施形態において、第3プログラム段階は、ISP技術に基づいて行われる。

例示的な実施形態において、第3プログラム段階では、すべてのプログラム状態に対して検証動作が実行される。すべてのプログラム状態P31～P37が検証パスされれば、第3プログラム段階は終了する。

30

#### 【0032】

本発明は、第1プログラミング段階で、3ビットのデータがプログラムされることに限定されない。本発明の第1プログラミング段階で、2ビットのデータがプログラムされることも可能である。2ビットのデータに対する第1プログラミング段階が完了した後、1ビットのデータをプログラムするために、第2プログラミング段階を行うことができる。その後、目標閾値電圧のばらつきを得るために第3プログラミング段階を行うことができる。上述のプログラムの方法は、特許文献1に掲載されている。

40

#### 【0033】

図1に示した3ビットプログラム動作が3ステップ再プログラミング方式によって実行される例を説明した。しかし、本発明は、3ビットプログラム動作が3ステップ再プログラミングによって実行されることに限定されない。本発明に係る再プログラミング方式により実行されるプログラム動作は、格納されるデータ値に対応する閾値電圧のばらつきの幅を狭くするため（または、閾値電圧のばらつきを正確に制御するため）の3つのプログラミング段階で構成することができる。

#### 【0034】

図2は、本発明の例示的な実施形態に係るメモリシステムを概略的に示すブロック図である。

図2を参照すると、本発明の実施形態に係るメモリシステム1000は、メモリ制御器

50

1200と、マルチビットメモリ装置として不揮発性メモリ装置1400とを含む。メモリ制御器1200は、外部(例えば、ホスト)からの要請(例えば、書き込み要請、読み出し要請等)に応答して不揮発性メモリ装置1400を制御する。メモリ制御器1200は、外部からの要請なしに内部的な要請(例えば、サドンパワーオフ(Sudden Power Off)に係る動作、ウエアレベリング動作、読み出し校正(read reclaim)動作など)に応じて不揮発性メモリ装置1400を制御する。メモリ制御器1200の内部的な要請に対応する動作は、ホストからの要請が処理された後、ホストのタイムアウト区間内で行われる。または、メモリ制御器1200の内部的な要請に対応する動作は、メモリ制御器1200の遊休時間に行われる。不揮発性メモリ装置1400は、メモリ制御器1200の制御に応答して動作し、データの情報を格納する一種の格納媒体として使用される。格納媒体は、一つ以上のメモリチップで構成することができる。不揮発性メモリ装置1400とメモリ制御器1200は、一つ以上のチャネルを介して通信する。不揮発性メモリ装置1400は、例えば、NANDフラッシュメモリ装置を含む。

#### 【0035】

メモリシステム1000は、上述のオンチップバッファプログラム(OBP)技術を使用する。以下で説明するように、不揮発性メモリ装置1400は、第1メモリ領域と第2メモリ領域とを有するメモリセルアレイを含む。例示的な実施形態において、第1メモリ領域は、セルあたり1ビットのデータを格納するメモリブロックで構成され、第2メモリ領域は、セル当たり3ビットのデータを格納するメモリブロックで構成される。第1メモリ領域及び第2メモリ領域の各々のセルあたりのビット数は、ここに開示されたものに限定されない。例えば、第1メモリ領域のセルあたりのビット数は、第2メモリ領域のセルあたりのビット数より少ない。メモリ制御器1200は、第2メモリ領域に含まれたメモリブロックのうちのいずれか一つのメモリブロックから読み出されたデータのエラービットの数が基準を超えたか否かに応じて読み出し校正動作(read reclaim operation)を実行する。本発明の読み出し校正動作によると、第2メモリ領域に含まれたメモリブロックに格納されたデータは、第2メモリ領域に含まれたメモリブロックに移動されるのではなく、第1メモリ領域に格納されたメモリブロックに移動する。本発明の場合、第2メモリ領域に含まれたメモリブロックに格納されたデータのすべてが第1メモリ領域に含まれたメモリブロックに移動すれば、第2メモリ領域に含まれたメモリブロックに係る読み出し校正動作は終了する。これは以後詳細に説明する。

#### 【0036】

図3は、図2に示したメモリ制御器を概略的に示すプロック図である。図3を参照すると、メモリ制御器1200は、第1インターフェースとして、ホストインターフェース1210と、第2インターフェースとしてメモリインターフェース1220と、中央処理装置1230と、バッファメモリ1240と、ECC回路1250とを含む。

#### 【0037】

ホストインターフェース1210は、外部(または、ホスト)とインターフェースするように構成される。メモリインターフェース1220は、図2に示した不揮発性メモリ装置1400とインターフェースするように構成される。CPU1230は、メモリ制御器1200の全体的な動作を制御するように構成される。例えば、CPU1230は、フラッシュ変換階層(Flash Translation Layer:FTL)のようなファームウェアを運用するように構成される。FTLは、様々な機能を実行する。例えば、FTLは、アドレスマッピング動作、読み出し校正動作、エラー訂正動作などを実行する様々な階層を含む。バッファメモリ1240は、ホストインターフェース1210を通じて外部に伝達されるデータを一時的に格納するために使用される。バッファメモリ1240は、メモリインターフェース1220を通じて不揮発性メモリ装置1400から伝達されるデータを一時的に格納するために使用される。バッファメモリ1240は、不揮発性メモリ装置1400を制御するために必要な情報(例えば、読み出し校正動作を必要とするソースメモリブロックを示す情報、アドレスマッピング情報など)を格納するために使用される。例えば、バッファメモリ1240は、DRAM、SRAM、またはDRAM

10

20

30

40

50

とSRAMの組み合わせで構成することができる。しかし、バッファメモリ1240として使用されるメモリ装置は、ここに開示されたものに限定されない。ECC回路1250は、不揮発性メモリ装置1400に格納されるデータを符号化するように、そして不揮発性メモリ装置1400から読み出されたデータを復号化するように構成される。

#### 【0038】

例示的な実施形態において、メモリ制御器1200は、図示しないが、不揮発性メモリ装置1400に格納されるデータをランダム化するように、不揮発性メモリ装置1400から読み出されたデータをランダム化しないように構成されたランダマイザをさらに含む。ランダマイザの一例が特許文献2に掲載されている。

#### 【0039】

例示的な実施形態において、ホストインターフェース1210は、コンピュータバス標準、ストレージバス標準、iFCP Peripheralバス標準などのうちの一つ以上の組み合わせで構成することができる。コンピュータバス標準(computer buses standards)は、S-100bus、Mbus、Smbus、Q-Bus、ISA、Zorro II、Zorro III、CAMAC、FASTBUS、LPC、EISA、VME、VXI、NuBus、TURBOchannel、MCA、Sbus、VLB、PCI、PXI、HP GSCbus、CoreConnect、InfiniBand、UPA、PCI-X、AGP、PCIe、Intel QuickPath Interconnect、Hyper Transportなどを含む。ストレージバス標準(Storage bus standards)は、ST-506、ESD I、SMD、Parallel ATA、DMA、SSA、HIPPI、USB MSC、FireWire(1394)、Serial ATA、eSATA、SCSI、Parallel SCSI、Serial Attached SCSI、Fibre Channel、iSCSI、SAS、RapidIO、FCIPなどを含む。iFCP Peripheralバス標準(iFCP Peripheral bus standards)は、Apple Desktop Bus、HIL、MIDI、Multibus、RS-232、DMX512-A、EIA/RS-422、IEEE-1284、UNI/O、1-Wire、I2C、SPI、EIA/RS-485、USB、Camera Link、External PCIe、Light Peak、Multidrop Busなどを含む。

#### 【0040】

図4は、図2に示した不揮発性メモリ装置を概略的に示すブロック図である。

不揮発性メモリ装置1400は、例えば、NANDフラッシュメモリ装置である。しかし、本発明は、NANDフラッシュメモリ装置に限定されない。例えば、不揮発性メモリ装置1400は、NORフラッシュメモリ装置、RRAM(登録商標)(Resistive Random Access Memory)装置、PRAM(Phase-Change Memory)装置、MRAM(Magnetoresistive Random Access Memory)装置、FRAM(登録商標)(Ferroelectric Random Access Memory)装置、STT-RAM(Spin Transfer Torque Random Access Memory)などで構成することができる。また、本発明の不揮発性メモリ装置1400は、3次元アレイ構造を有するように実現することができる。3次元アレイ構造を有する不揮発性メモリ装置は、垂直NANDフラッシュメモリ装置と呼ばれる。本発明は、電荷格納層が伝導性の浮遊ゲートで構成されたフラッシュメモリ装置だけではなく、電荷格納層が絶縁膜で構成されるチャージトラップ型フラッシュ(Charge Trap Flash、“CTF”という)メモリ装置にも適用可能である。

#### 【0041】

図4を参照すると、不揮発性メモリ装置1400は、メモリセルアレイ1410と、アドレスデコーダ1420と、電圧発生器1430と、制御ロジック1440と、ページバッファ回路1450と、入出力インターフェース1460とを含む。

10

20

30

40

50

メモリセルアレイ 1410 は、行（例えば、ワードライン）と、列（例えば、ビットライン）との交差領域に配列されたメモリセルを含む。メモリセルの各々は、1 ビットのデータまたはマルチビットのデータを格納する。アドレスデコーダ 1420 は、制御ロジック 1440 によって制御され、メモリセルアレイ 1410 の行（例えば、ワードライン、ストリング選択ライン、接地選択ライン、共通ソースラインなど）の選択及び駆動を行う。電圧発生器 1430 は、制御ロジック 1440 によって制御され、各動作に必要な電圧（例えば、高電圧、プログラム電圧、読み出し電圧、検証電圧、消去電圧、バス電圧、バルク電圧など）を発生する。電圧発生器 1430 によって生成された電圧は、アドレスデコーダ 1420 を通じてメモリセルアレイ 1410 に提供される。制御ロジック 1440 は、不揮発性メモリ装置 1400 の全体的な動作を制御するように構成される。

10

#### 【0042】

ページバッファ回路 1450 は、制御ロジック 1440 によって制御され、メモリセルアレイ 1410 からデータを読み出すように、またはプログラムデータによってメモリセルアレイ 1410 の列（例えば、ビットライン）を駆動するように構成される。ページバッファ回路 1450 は、ビットライン又はビットライン対に各々対応する複数のページバッファで構成される。ページバッファの各々は、複数のラッチを含む。入出力インターフェース 1460 は、制御ロジック 1440 によって制御され、外部（例えば、図 2 のメモリ制御器 1210）とインターフェースするように構成される。図示しないが、入出力インターフェース 1460 は、ページバッファを選択するための列選択器、データが入力される入力バッファ、データを出力する出力バッファなどを含む。

20

#### 【0043】

図 5 は、図 4 に示したメモリセルアレイを概略的に示すブロック図である。

図 5 を参照すると、メモリセルアレイ 1410 は、複数のメモリブロックで構成され、複数のメモリブロックは、第 1 メモリ領域 1411 と第 2 メモリ領域 1412 とに区分される。ここで、第 1 及び第 2 メモリ領域 1411、1412 の区分は物理的なものではなく、論理的に行われる。第 1 及び第 2 メモリ領域 1411、1412 の区分は、論理的に可変可能である。つまり、第 1 及び第 2 メモリ領域 1411、1412 の物理的なサイズがメモリ制御器 1200 の制御の下に論理的に可変可能である。第 1 メモリ領域 1411 に属するメモリブロックは、第 2 メモリ領域 1412 に属するメモリブロックとは異なる方法でプログラムされる。例えば、第 1 メモリ領域 1411 に属するメモリブロックは、単一ビットプログラム方法（または、SLC プログラム方式という）に基づいてプログラムされ、第 2 メモリ領域 1412 に属するメモリブロックは、マルチビットプログラム方法（または、MLC / TLC プログラム方式という）（例えば、上述の 3 ステップ再プログラム方式）に基づいてプログラムされる。つまり、第 1 メモリ領域 1411 に属するメモリセルの各々は、1 ビットのデータを格納し、第 2 メモリ領域 1412 に属するメモリセルの各々は、M ビットデータ（M は 3 以上の整数）を格納する。また、第 1 メモリ領域 1411 に属するメモリセルの各々は、第 2 メモリ領域 1412 に属するメモリセルの各々に格納されるデータビットの数より少ない数のデータビットを格納する。ここで、第 1 メモリ領域 1411 に属するメモリセルの各々が 1 ビットのデータを格納することに限定されない。例えば、第 1 メモリ領域 1411 に属するメモリセルの各々に格納されるビットの数は、第 2 メモリ領域 1412 に属するメモリセルの各々に格納されるビットの数より少ない。

30

#### 【0044】

上述のように、メモリ制御器 1200 から提供されるデータは、バッファのプログラム動作を通じて、第 1 メモリ領域 1411 にプログラムされる。メインプログラム動作に必要なデータは、第 1 メモリ領域 1411 から読み出され、読み出されたデータは、メインプログラム動作を通じて第 2 メモリ領域 1412 にプログラムされる。

40

#### 【0045】

図 6 A ~ 図 6 D は、本発明の例示的な実施形態に係るマルチビットメモリ装置の第 1 及び第 2 メモリ領域に対する様々な組み合わせを説明するための図である。図面において、

50

“B P”は、第1メモリ領域1411に対するバッファプログラミングを示し、“M P”は、第2メモリ領域1412に対するメインプログラミングを示す。

上述のように、マルチビットメモリ装置1400は、第1メモリ領域1411と第2メモリ領域1412とを含む。ここで、第1メモリ領域1411と第2メモリ領域1412は、マルチビットメモリ装置1400のメモリセルアレイを構成する。図示しないが、メモリセルアレイは、より多くの領域（例えば、メタ領域、予備領域など）を含む。メモリセルアレイのメモリ領域は物理的に区分されず、論理的に区分される。これは、メモリ制御器1200のアドレスマッピングに基づいて、メモリ領域が定義されることを意味する。

#### 【0046】

10

図6Aを参照すると、セル当たり3ビットのデータを格納するマルチビットメモリ装置の場合、第1メモリ領域1411は、1ビットのデータを各々格納するメモリセルのメモリブロックで構成し、第2メモリ領域1412は、3ビットのデータを各々格納するメモリセルのメモリブロックで構成することができる。この場合、バッファプログラミングは、SLCプログラム方式に基づいて行われる。メインプログラミングは、上述のMLC/TLCプログラム方法によって行われる。

#### 【0047】

20

図6Bを参照すると、セル当たり4ビットのデータを格納するマルチビットメモリ装置の場合、第1メモリ領域1411は、1ビットのデータを各々格納するメモリセルのメモリブロックで構成し、第2メモリ領域1412は、4ビットのデータを各々格納するメモリセルのメモリブロックで構成することができる。この場合、バッファプログラミングは、SLCプログラム方式に基づいて行われる。メインプログラミングは、上述のMLC/TLCプログラム方法に基づいて行われる。

#### 【0048】

30

図6Cを参照すると、セル当たり3ビットのデータを格納するマルチビットメモリ装置の場合、第1メモリ領域1411は、2ビットのデータを各々格納するメモリセルのメモリブロックで構成し、第2メモリ領域1412は、3ビットのデータを各々格納するメモリセルのメモリブロックで構成することができる。この場合、バッファプログラミングは、一般的な、または、上述のMLCプログラム方式に基づいて行われる。メインプログラミングは、上述のMLC/TLCプログラム方法（例えば、再プログラム方式）に基づいて行われる。

#### 【0049】

図6Dを参照すると、セル当たり4ビットのデータを格納するマルチビットメモリ装置の場合、第1メモリ領域1411は、2ビットのデータを各々格納するメモリセルのメモリブロックで構成し、第2メモリ領域1412は、4ビットのデータを各々格納するメモリセルのメモリブロックで構成することができる。この場合、バッファのプログラミングは、一般的な、または、上述のMLCプログラム方式に基づいて行われる。メインプログラミングは、上述のMLC/TLCプログラム方法（例えば、再プログラム方式）に基づいて行われる。

#### 【0050】

40

例示的な実施例において、図6A～図6Dに示した第1及び第2メモリ領域1411、1412の定義がここに開示されたものに限定されない。例えば、メモリシステムに含まれる格納媒体が複数のマルチビットメモリ装置で構成される場合、各マルチビットメモリ装置は、メモリセルアレイが第1及び第2メモリ領域1411、1412に区分されるように構成することができる。別の例として、1つまたはそれより多くのマルチビットメモリ装置のメモリセルアレイの各々は、第1メモリ領域1411として使用されるように構成することができる。残りのマルチビットメモリ装置のメモリセルアレイの各々は、第2メモリ領域1412として使用されるように構成することができる。

#### 【0051】

図7は、本発明の例示的な実施形態に係るメモリシステムの読み出し方法を示すフロー

50

チャートである。以下、本発明の例示的な実施形態に係るメモリシステムの読み出し方法を参照の図面に基づいて詳細に説明する。まず、第1メモリ領域1411は、セルあたり1ビットのデータが格納されるメモリブロック（以下、SLCブロックという）で構成され、第2メモリ領域1412は、セル当たり3ビットのデータが格納されるメモリブロック（以下、TLCブロックという）で構成されると仮定する。

#### 【0052】

S110段階において、メモリ制御器1200は、外部装置（例えば、ホスト）からの読み出し要請が入力される。S120段階において、メモリ制御器1200は、読み出し要請されたデータが出力されるように不揮発性メモリ装置1400を制御する。読み出し要請されたデータは、例えば、第2メモリ領域1412のTLCブロックに格納されたデータである。または、読み出し要請されたデータは、第1メモリ領域1411のSLCブロックに格納されたデータである。例示的な実施形態において、読み出し要請されたデータは、第2メモリ領域1412のTLCブロックに格納されたデータである。10

#### 【0053】

S130段階において、不揮発性メモリ装置1400から出力されるデータがメモリ制御器1200のバッファメモリ1240に伝送される間、メモリ制御器1200のECC回路1250は、不揮発性メモリ装置1400から出力されるデータのエラー検出動作を実行する。この時、不揮発性メモリ装置1400から出力されるデータは、メモリ制御器1200のバッファメモリ1240に一時格納される。20

#### 【0054】

S140段階において、不揮発性メモリ装置1400から出力されるデータのエラーが訂正可能であるか否か決められる。もし、不揮発性メモリ装置1400から出力されるデータのエラーが訂正可能であると判断されれば、S150段階に進行する。S150段階において、不揮発性メモリ装置1400から出力されるデータのエラーが訂正される。S160段階において、バッファメモリ1240に格納された訂正されたデータは、読み出し要請されたデータとして外部装置に伝送される。その後、読み出し方法は終了する。20

#### 【0055】

S140段階に戻って、もし不揮発性メモリ装置1400から出力されるデータのエラーが訂正できないと判断されれば、又は不揮発性メモリ装置1400から出力されるデータから出力されたエラービットの数が基準（例えば、ECC回路1250の許容可能なエラービット数）を超えた場合、S170段階に進む。S170段階において、メモリ制御器1200は、ソフトウェア方式で不揮発性メモリ装置1400から出力されるデータのエラー検出訂正動作を実行する。ソフトウェア方式を用いたエラー検出訂正動作は、例えば、FTLによって行われる。S180段階において、不揮発性メモリ装置1400から出力されるデータが訂正されたか否か決められる。たとえ不揮発性メモリ装置1400から出力されるデータに含まれるエラービットの数がECC回路1250の許容可能なエラービット数を超過しても、ソフトウェア方式を用いたエラー検出訂正動作を通じて不揮発性メモリ装置1400から出力されるデータのエラーを訂正することができる。30

#### 【0056】

不揮発性メモリ装置1400から出力されるデータが訂正されていないと判断されれば、S190段階に進む。S190段階において、メモリ制御器1200は、外部装置によつて要請された読み出し動作をフェイルとして処理する。その後、読み出し方法は終了する。例えば、読み出しフェイルフラグが生成される。読み出しフェイルフラグの生成による手続きは多様に決定され得る。以後、方法は終了する。40

#### 【0057】

不揮発性メモリ装置1400から出力されるデータが訂正されたと判断されれば、S200段階に進む。S200段階において、メモリ制御器1200は、バッファメモリ1240に格納された訂正されたデータを読み出し要請されたデータとして外部装置に伝送する。この時、読み出し要請されたデータが格納されたTLCブロックが読み出し校正動作を必要とするメモリブロックであることを示す情報がCPU1230の制御の下にキュー50

(queue)に格納される。以後、読み出し方法は終了する。

#### 【0058】

例示的な実施形態において、キューは、バッファメモリ1240の一部として構成され、キューに格納された情報は、CPU1230によって参照される。キューに格納された情報は、周期的に、または一定の時間に不揮発性メモリ装置1400に格納される。これは、突然の電源遮断によってバッファメモリ1240、またはキューに格納された情報が失われることを防止するために行われる。キューに格納された情報に基づいて、TLCブロックに対する読み出し校正動作が実行され、これは以後詳細に説明する。

#### 【0059】

図8A及び図8Bは、本発明の例示的な実施形態に係る読み出し校正動作を示す図である。10

メモリセルの閾値電圧のばらつきは、様々な原因（例えば、温度変化、読み出し動作の繰り返し等）により移動することがある。閾値電圧のばらつきの移動は、メモリセルから読み出されたページのデータでエラービットが発生するようにする。例えば、閾値電圧のばらつきの移動は、エラービットの数を増加させる。特に、セル当たり3ビットのデータが格納されるTLCブロックの場合、閾値電圧のばらつきの移動は、エラービットの数をさらに増加させる。したがって、読み出されたデータの整合性を確保するために読み出し校正動作を実行することができる。読み出し校正動作は、訂正できないと判断されたページのデータを含んだTLCブロックの有効データを新しいブロックに移動させる動作を意味する。または、読み出し校正動作は、エラービットの数が今後増加する可能性が高いページのデータを含んだTLCブロックの有効データを新しいブロックに移動させる動作を意味する。読み出し校正動作は、ページのデータが格納されたメモリセルの閾値電圧のばらつきの移動が隣接したメモリセルにも影響を与えるため行われる。20

#### 【0060】

図8Aを参照すると、CPU1230は、キューに格納された情報に基づいて、FTLの読み出し校正動作の対象ブロックであるTLCブロックを選択する。例えば、選択されたTLCブロックは64個のワードラインを含むと仮定する。つまり、192個のページのデータが1つのTLCブロックに格納される。選択されたTLCブロックに格納された192個のページのデータが全部有効な場合、選択されたTLCブロックに格納された192個のページのデータを移動するための3つのSLCブロックが要求される。読み出し校正動作を実行するために選択されたTLCブロックから64個のページのデータが読み出され、読み出された64個のページのデータは、メモリ制御器1200のECC回路1250を通じて第1メモリ領域1411の一つのSLCブロックSB0に格納される。次に、読み出し校正動作を実行するために選択されたTLCブロックから64個のページのデータが読み出され、読み出された64個のページのデータは、メモリ制御器1200のECC回路1250を通じて第1メモリ領域1411のSLCブロックSB1に格納される。最後に、読み出し校正動作を実行するために選択されたTLCブロックから64個のページのデータが読み出され、読み出された64個のページのデータは、メモリ制御器1200のECC回路1250を通じて第1メモリ領域1411の一つのSLCブロックSB2に格納される。3040

#### 【0061】

図8Bを参照すると、選択されたTLCブロックに格納された192個のページのうち150個のページのデータが有効な場合、選択されたTLCブロックに格納された150個のページのデータを移動するための3つのSLCブロックが要求される。読み出し校正動作を実行するために選択されたTLCブロックから64個のページのデータが読み出され、読み出された64個のページのデータは、メモリ制御器1200のECC回路1250を通じて第1メモリ領域1411の一つのSLCブロックSB0に格納される。次に、読み出し校正動作を実行するために選択されたTLCブロックから64個のページのデータが読み出され、読み出された64個のページのデータは、メモリ制御器1200のECC回路1250を通じて第1メモリ領域1411のSLCブロックSB1に格納される。50

最後に、読み出し校正動作を実行するために選択された T L C ブロックから 2 2 個のページのデータが読み出され、読み出された 2 2 個のページのデータは、メモリ制御器 1 2 0 0 の E C C 回路 1 2 5 0 を通じて第 1 メモリ領域 1 4 1 1 の一つの S L C ブロック S B 2 に格納される。

T L C ブロックに格納された有効なページのデータのすべてが、第 1 メモリ領域 1 4 1 1 に移動すれば、C P U 1 2 3 0 は、T L C ブロックに対する F T L の読み出し校正動作を完了したと処理する。例えば、キューに格納された情報（読み出し校正動作の対象ブロック）が変更される。

#### 【 0 0 6 2 】

上述のように、本発明の読み出し校正動作によると、読み出し校正動作の対象ブロックである T L C ブロックの有効ページのデータは、第 2 メモリ領域 1 4 1 2 の T L C ブロックではなく、第 1 メモリ領域 1 4 1 1 の S L C ブロックに移動する。第 1 メモリ領域 1 4 1 1 の S L C ブロックへのデータの移動が完了すると、T L C ブロックに対する読み出し校正動作が完了したと処理される。すなわち、本発明の読み出し校正動作の時、読み出し校正動作の対象ブロックである T L C ブロックの有効ページのデータは、第 2 メモリブロック 1 4 1 2 の T L C ブロックに移動しない。

#### 【 0 0 6 3 】

例示的な実施形態において、読み出し校正動作の対象ブロックである T L C ブロックの有効ページのデータは、時分割方式で、第 1 メモリ領域 1 4 1 1 の S L C ブロックに移動する。例えば、読み出し校正動作の対象ブロックである T L C ブロックの有効ページのデータの一部（例えば、一つの S L C ブロックのサイズに対応する有効ページのデータ）が一つの S L C ブロックに移動する。これは、他のページの読み出しありは書き込み動作がホストによって要請されるたびに読み出しありは書き込み動作が完了した後にタイムアウト時間内で行うことができる。T L C ブロックの有効ページのデータのすべてが S L C ブロックに移動する時、T L C ブロックに対する読み出し校正動作は完了する。

#### 【 0 0 6 4 】

例示的な実施形態において、読み出し校正動作の対象ブロックである T L C ブロックの有効ページのデータが移動する第 1 メモリ領域 1 4 1 1 の S L C ブロックの数は、ホストのタイムアウト間隔を考慮して決めることができる。例えば、ホストの書き込み要請が処理された後、タイムアウト区間の残った時間を考慮して、第 1 メモリ領域 1 4 1 1 の S L C ブロックの数を決めることができる。ホストの書き込み要請の時、決められた S L C ブロックに読み出し校正動作の対象ブロックである T L C ブロックのデータが移動する。

#### 【 0 0 6 5 】

T L C ブロックから S L C ブロックに移動したデータは、メインプログラム動作を通じて第 2 メモリ領域 1 4 1 2 に格納される。これらの動作は、ガーベッジコレクション動作の間行うことができる。これは、図 9 を参照して詳細に説明する。

図 9 は、読み出し校正動作を通じて生成された S L C ブロックのデータが T L C ブロックに格納される例を示す図である。

#### 【 0 0 6 6 】

上述のように、本発明の読み出し校正動作は、T L C ブロックの有効ページのデータが第 1 メモリ領域 1 4 1 1 の S L C ブロックに移動する時に完了する。T L C ブロックの有効ページの数に応じて S L C ブロックのうちの一つは、空の格納空間を含む。例えば、図 8 B 及び図 9 を参照すると、選択された T L C ブロックに格納された 1 9 2 個のページのうちで 1 5 0 個のページのデータが有効な場合、選択された T L C ブロックに格納された 1 5 0 個のページのデータを移動するために 3 つの S L C ブロックが要求され、一つの S L C ブロック（例えば、S B 2 ）は空の格納空間を含む。空の格納空間を含む S L C ブロック S B 2 を除いた残りの S L C ブロック S B 0 、 S B 1 のデータは、ガーベッジコレクションの動作の時にデータで完全に満たされた他の S L C ブロック（例えば、S B 3 ）のデータと共に特定の T L C ブロックに格納される。S L C ブロックのデータが上述のような方法で T L C ブロックに格納されれば、T L C ブロックは完全にデータで満たされる。

10

20

30

40

50

すなわち、TLC ブロックのすべてのワードラインがクローズされる。これは、TLC ブロックがオープンワードラインを含まないことを意味する。一方、選択された TLC ブロックに格納された 150 個のページのデータが格納された SLC ブロック SB0、SB1、SB2 のデータが特定の TLC ブロックに格納される場合、特定の TLC ブロックには、空の格納空間が存在する。これは、特定の TLC ブロックがオープンワードラインを含むことを意味する。

#### 【0067】

ここで、n 番目のワードライン WL<sub>n</sub> に接続されたメモリセルに対する 3 ステップ再プログラム動作が完了した一方、隣接した上位ワードライン（例えば、n+1 番目のワードライン WL<sub>n+1</sub>）に接続されたメモリセルに対する 3 ステップ再プログラム動作のうち、第 3 プログラミング段階が実行されない場合、n 番目のワードライン WL<sub>n</sub> をオープンワードラインという。オープンワードラインに接続されたメモリセルの目標閾値電圧のはらつきは、隣接した上位ワードラインに接続されたメモリセルに対する 3 ステップ再プログラム動作が完了した時に形成される。もし、隣接した上位ワードラインに接続されたメモリセルに対する 3 ステップ再プログラム動作が完了しない場合、オープンワードラインに接続されたメモリセルの目標閾値電圧のはらつきが正常に形成されない。例えば、オープンワードラインに接続されたメモリセルは、隣接した上位ワードラインに接続されたメモリセルによって生じるカップリングを十分に受けず、その結果、オープンワードラインに接続されたメモリセルの目標閾値電圧のはらつきが正常に形成されない。このような場合、オープンワードラインに接続されたメモリセルから読み出されたデータは訂正不可能な確率が高くなる。

#### 【0068】

したがって、空の格納空間を含んだ SLC ブロック SB2 を除いた残りの SLC ブロック SB0、SB1 のデータをガーベッジコレクション動作の時、データで完全に満たされた他の SLC ブロック（例えば、SB3）のデータと共に、特定の TLC ブロックに格納することによって、特定の TLC ブロックでオープンワードラインが生じるのを防止することができる。

例示的な実施形態において、空の格納空間を有する SLC ブロック SB2 のデータは、空の格納空間を有する他の SLC ブロックのデータと共に他の SLC ブロックに、または TLC ブロックに移動することができる。

#### 【0069】

図 10 は、本発明の別の例示的な実施形態に係るメモリシステムの読み出し方法を示すフローチャートである。以下、本発明の例示的な実施形態に係るメモリシステムの読み出し方法を、参照の図面に基づいて詳細に説明する。まず、第 1 メモリ領域 1411 は、セルあたり 1 ビットのデータが格納されるメモリブロック（以下、SLC ブロックという）で構成され、第 2 メモリ領域 1412 は、セル当たり 3 ビットのデータが格納されるメモリブロック（以下、TLC ブロックという）で構成されると仮定する。

#### 【0070】

S310 段階において、メモリ制御器 1200 は、外部装置（例えば、ホスト）からの読み出し要請が入力される。S320 段階において、メモリ制御器 1200 は、読み出し要請されたデータが出力されるように不揮発性メモリ装置 1400 を制御する。読み出し要請されたデータは、例えば、第 2 メモリ領域 1412 の TLC ブロックに格納されたデータである。または、読み出し要請されたデータは、第 1 メモリ領域 1411 の SLC ブロックに格納されたデータである。例示的な実施形態において、読み出し要請されたデータは、第 2 メモリ領域 1412 の TLC ブロックに格納されたデータである。

#### 【0071】

S330 段階において、不揮発性メモリ装置 1400 から出力されるデータが、メモリ制御器 1200 のバッファメモリ 1240 に伝送される間、メモリ制御器 1200 の ECC 回路 1250 は、不揮発性メモリ装置 1400 から出力されるデータに対するエラー検出動作を実行する。この時、不揮発性メモリ装置 1400 から出力されるデータは、メモリ

10

20

30

40

50

リ制御器 1200 のバッファメモリ 1240 に一時格納される。

#### 【0072】

S340 段階において、不揮発性メモリ装置 1400 から出力されるデータのエラーが訂正可能であるか否かが決められる。もし、不揮発性メモリ装置 1400 から出力されるデータのエラーが訂正可能であると判断されれば、S350 段階に進む。S350 段階において、不揮発性メモリ装置 1400 から出力されるデータのエラーが訂正される。S360 段階において、バッファメモリ 1240 に格納された訂正されたデータは、読み出し要請されたデータとして外部装置に伝送される。その後、読み出し方法は終了する。

#### 【0073】

S340 段階に戻って、もし不揮発性メモリ装置 1400 から出力されるデータのエラーが訂正できないと判断されるか、又は不揮発性メモリ装置 1400 から出力されるデータから出力されたエラービットの数が基準（例えば、ECC 回路 1250 の許容可能なエラービット数、許容可能なエラービット数より少ないエラービット数など）を超えた場合、S370 段階に進む。S370 段階において、読み出しリトライ動作が行われる。読み出しリトライ動作は、読み出し電圧が決められた回数内で変化する状態で読み出し動作をリトライする動作を意味する。読み出しリトライ動作の一例が特許文献 3 に掲載されている。読み出し電圧が変化するたびに読み出されたデータがエラー訂正可能であるか否かが判別される。読み出しリトライ動作を通じて読み出されたデータがエラー訂正できない場合、S380 段階に進む。S380 段階において、読み出しつェイルフラグが生成される。読み出しつェイルフラグの生成による手続きは多様に決定され得る。以後、方法は終了する。10

#### 【0074】

読み出しリトライ動作を通じて読み出されたデータがエラー訂正可能な場合、S390 段階に進む。S390 段階において、不揮発性メモリ装置 1400 から出力されたデータが格納された第 2 メモリ領域 1412 の TLC ブロックが読み出し校正動作の対象ブロックであることを示す情報がキューに格納される。上述のように、キューは、バッファメモリ 1240 の一部として構成され、キューに格納された情報は、CPU 1230 によって参照される。キューに格納される情報は、周期的に、または一定の時間に不揮発性メモリ装置 1400 に格納される。これは、突然の電源遮断によってバッファメモリ 1240 、またはキューに格納された情報が失われることを防止するために行われる。キューに格納された情報に基づいて、TLC ブロックの読み出し校正動作が実行され、これは以後詳細に説明する。20

#### 【0075】

不揮発性メモリ装置 1400 から出力されたデータが格納された第 2 メモリ領域 1412 の TLC ブロックが読み出し校正動作の対象ブロックであることを示す情報がキューに格納された後、S350 段階に進む。S350 段階において、不揮発性メモリ装置 1400 から出力されるデータのエラーが訂正される。S360 段階において、バッファメモリ 1240 に格納された訂正されたデータは、読み出し要請されたデータとして外部装置に伝送される。以後、読み出し方法は終了する。

メモリ制御器 1200 は、キューに格納された情報に基づいて、読み出し校正動作を実行し、これは図 8A、図 8B、及び図 9 での説明と同様に行われる。40

#### 【0076】

図 11 は、本発明のさらに別の例示的な実施形態に係るメモリシステムの読み出し方法を示すフローチャートである。以下、本発明の例示的な実施形態に係るメモリシステムの読み出し方法を、参照の図面に基づいて詳細に説明する。まず、第 1 メモリ領域 1411 は、セルあたり 1 ビットのデータが格納されるメモリブロック（以下、SLC ブロックという）で構成され、第 2 メモリ領域 1412 は、セル当たり 3 ビットのデータが格納されるメモリブロック（以下、TLC ブロックという）で構成されると仮定する。

#### 【0077】

S410 段階において、メモリ制御器 1200 は、外部装置（例えば、ホスト）からの50

読み出し要請が入力される。S420段階において、メモリ制御器1200は、読み出し要請されたデータが出力されるように不揮発性メモリ装置1400を制御する。読み出し要請されたデータは、例えば、第2メモリ領域1412のTLCブロックに格納されたデータである。または、読み出し要請されたデータは、第1メモリ領域1411のSLCブロックに格納されたデータである。例示的な実施形態において、読み出し要請されたデータは、第2メモリ領域1412のTLCブロックに格納されたデータである。

#### 【0078】

S430段階において、不揮発性メモリ装置1400から出力されるデータが、メモリ制御器1200のバッファメモリ1240に伝送される間、メモリ制御器1200のECC回路1250は、不揮発性メモリ装置1400から出力されるデータに対するエラー検出動作を実行する。この時、不揮発性メモリ装置1400から出力されるデータは、メモリ制御器1200のバッファメモリ1240に一時格納される。10

#### 【0079】

S440段階において、不揮発性メモリ装置1400から出力されるデータに含まれたエラービットの数が基準以下であるか否かが決められる。ここで、基準は、ECC回路1250の許容可能なエラービット数、許容可能なエラービット数より少ないエラービット数などである。もし、不揮発性メモリ装置1400から出力されるデータに含まれたエラービットの数が基準以上であると判断されれば、S450段階に進む。S450段階において、不揮発性メモリ装置1400から出力されたデータが格納された第2メモリ領域1412のTLCブロックが読み出し校正動作の対象ブロックであることを示す情報がキューに格納される。上述のように、キューは、バッファメモリ1240の一部として構成され、キューに格納された情報は、CPU1230によって参照される。キューに格納される情報は、周期的に、または一定の時間に不揮発性メモリ装置1400に格納される。これは、突然の電源遮断によってバッファメモリ1240、またはキューに格納された情報が失われることを防止するために行われる。キューに格納された情報に基づいて、TLCブロックの読み出し校正動作が実行され、これは以後詳細に説明する。20

#### 【0080】

不揮発性メモリ装置1400から出力されたデータが格納された第2メモリ領域1412のTLCブロックが読み出し校正動作の対象ブロックであることを示す情報がキューに格納された後、S460段階に進む。S460段階において、不揮発性メモリ装置1400から出力されるデータのエラーが訂正される。S470段階において、バッファメモリ1240に格納された訂正されたデータは、読み出し要請されたデータとして外部装置に伝送される。以後、読み出し方法は終了する。30

メモリ制御器1200は、キューに格納された情報に基づいて、読み出し校正動作を実行し、これは図8A、8b、及び図9での説明と同様に行われる。

#### 【0081】

図12は、本発明の例示的な実施形態に係るメモリシステムの読み出し校正方法を示すブロック図である。

図12を参照すると、読み出し校正動作は、読み出し動作の時、読み出しぱイルされる可能性が高いページのデータを含んだTLCブロックの有効なデータを新しいブロックに移動させる動作として、データの整合性を確保するために行われる。本発明では、特に、読み出し校正動作の対象ブロックとして決められたTLCブロックを示す情報がキューに格納される。ホストからの要請（例えば、書き込み要請）の時、例えば、要請された動作が完了し、キューに格納された情報に基づいてTLCブロックの有効なページのデータのうちの一部（または、すべて）がSLCブロックに移動する。SLCブロックへのデータ移動は、ECC回路1250の符号化及びバッファプログラミングを通じて行われる。40

#### 【0082】

例示的な実施形態において、ホスト要請の時、SLCブロックに移動するデータの量は、ホストのタイムアウト区間を考慮して決めることができる。例えば、SLCブロックに移動するデータの量は、一つのSLCブロックの格納容量に対応する。または、SLCブ50

ロックに移動するデータの量は、二つのSLCブロックの格納容量の合計に対応する。しかし、本発明は、ここに開示されたものに限定されない。したがって、要請された動作及びSLCブロックへのデータの移動は、ホストのタイムアウト区間内で行われる。

#### 【0083】

読み出し校正動作の対象ブロックとして決められたTLCブロックの有効なページのデータがすべてSLCブロックに移動すれば、図12に示すように、TLCブロックと関連した読み出し校正動作は完了したと処理される。以後、SLCブロックに格納されたデータは、読み出し校正動作ではなく、ガーベッジコレクション動作または他の動作の時、メインプログラム動作によりTLCブロックに格納される。図9を参照して説明したように、読み出し校正動作を通じてプログラムされたSLCブロックのうちの一つが空の格納空間を含む場合、空の格納空間を含むSLCブロックを除いた残りのSLCブロックのデータは、他のSLCブロックのデータと共にメインプログラム動作によりTLCブロックに格納される。10

したがって、本発明の読み出し校正動作は、ホストのタイムアウト条件を満たしながら実行することができる。また、本発明のメモリシステムは、TLCブロックにオープンワードラインが生成されることを防止することができる。

#### 【0084】

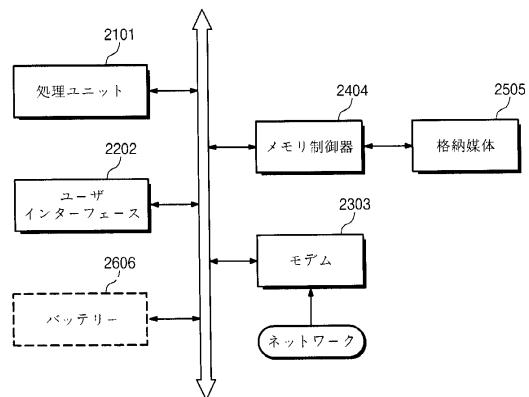

図13は、本発明の実施形態に係るコンピューティングシステムを概略的に示すプロック図である。コンピューティングシステムは、処理ユニット2101と、ユーザインターフェース2202と、ベースバンドチップセット(base band chip set)のようなモデム2303と、メモリ制御器2404と、格納媒体2505とを含む。20

#### 【0085】

メモリ制御器2404は、図2に示したものと実質的に同一に構成され、格納媒体2505は、図4に示した不揮発性メモリ装置で構成される。例えば、メモリ制御器2404は、読み出し校正動作の対象ブロックであるTLCブロックを、キューを利用して管理し、特定の時間(例えば、ホストの書き込み要請の時)に、キューに格納された情報に基づいてTLCブロックを選択し、選択されたTLCブロックの有効なページのデータが格納媒体2505の不揮発性メモリ装置に含まれたSLCブロックに移動するよう格納媒体2505を制御する。メモリ制御器2404は、選択されたTLCブロックの有効なページのデータが格納媒体2505の不揮発性メモリ装置に含まれたSLCブロックに移動する時、選択されたTLCブロックの読み出し校正動作を完了したと処理する。30

#### 【0086】

格納媒体2505には、処理ユニット2101によって処理された/処理されるNビットのデータ(Nは1以上の整数)がメモリ制御器2404を通じて格納される。コンピューティングシステムがモバイル装置の場合、コンピューティングシステムの動作電圧を供給するためのバッテリー2606がさらに提供される。図示しないが、本発明に係るコンピューティングシステムは、アプリケーションチップセット(application chip set)、カメライメージプロセッサ(Camera Image Processor: CIS)、モバイルDRAMなどをさらに提供することができる。

#### 【0087】

図14は、本発明の実施形態に係る半導体ドライブを概略的に示すプロック図である。

図14を参照すると、半導体ドライブ4000(SSD)は、格納媒体4100と、制御器4200とを含む。格納媒体4100は、複数のチャンネルCH0~CHn1を通じて制御器4200と接続する。各チャンネルには、複数の不揮発性メモリが共通に接続するようになる。制御器4200は、図2に示したものと実質的に同一に構成され、格納媒体4100の不揮発性メモリ装置の各々は、図4に示した不揮発性メモリ装置と実質的に同一に構成される。例えば、制御器4200は、読み出し校正動作の対象ブロックであるTLCブロックを、キューを利用して管理し、特定の時間(例えば、ホストの書き込み要請の時)に、キューに格納された情報に基づいてTLCブロックを選択し、選択されたTLCブロックの有効なページのデータが格納媒体4100の不揮発性メモリ装置に含まれ4050

たS L C ブロックに移動するように格納媒体4 1 0 0 を制御する。制御器4 2 0 0 は、選択されたT L C ブロックの有効なページのデータが格納媒体4 1 0 0 の不揮発性メモリ装置に含まれたS L C ブロックに移動する時、選択されたT L C ブロックに対する読み出し校正動作を完了したと処理する。

#### 【 0 0 8 8 】

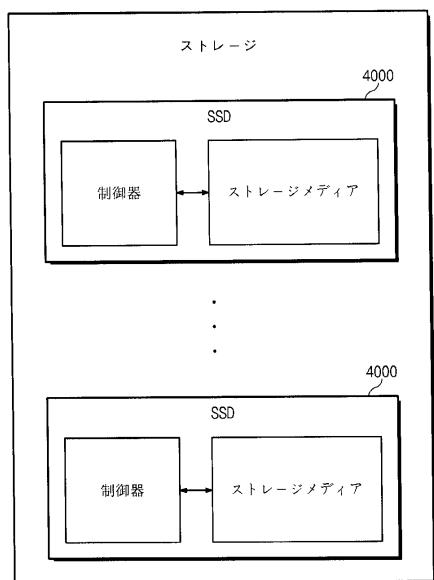

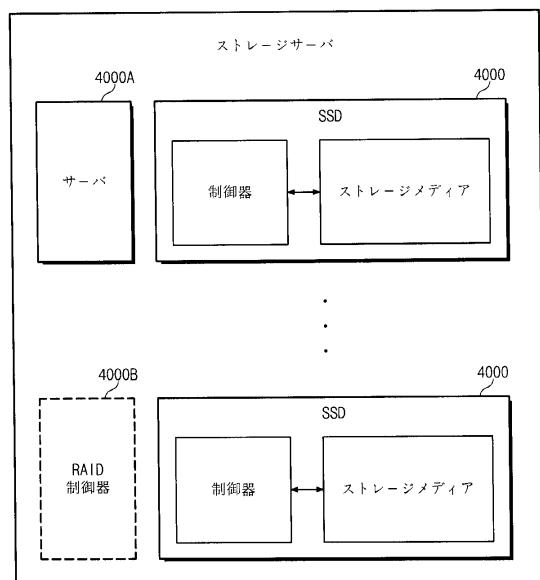

図15は、図14に示した半導体ドライブを利用したストレージを概略的に示すプロック図であり、図16は、図14に示した半導体ドライブを利用したストレージサーバを概略的に示すプロック図である。

本発明の実施形態に係る半導体ドライブ4 0 0 0 は、ストレージを構成するために使用することができる。図15に示すように、ストレージは、図14での説明と実質的に同一に構成される複数の半導体ドライブを含む。本発明の実施形態に係る半導体ドライブ4 0 0 0 は、ストレージサーバを構成するために使用することができる。図16に示すように、ストレージサーバは、図14での説明と実質的に同一に構成される複数の半導体ドライブ4 0 0 0 0 と、サーバ4 0 0 0 Aとを含む。また、この分野でよく知られているR A I D 制御器4 0 0 0 Bをストレージサーバに提供することができることを容易に理解することができる。

#### 【 0 0 8 9 】

図17は、本発明に係るM o v i N A N Dを概略的に示すプロック図である。図17を参照すると、M o v i N A N D 5 0 0 0 は、少なくとも一つのN A N D フラッシュメモリ装置5 1 0 0 と、制御器5 2 0 0 とを含むことができる。M o v i N A N D 5 0 0 0 は、M M C 4 . 4 ( 言い換えれば、e M M C ) 規格をサポートする。

#### 【 0 0 9 0 】

N A N D フラッシュメモリ装置5 1 0 0 は、S D R ( S i n g Data Rate ) N A N D またはD D R ( D o u b l e Data Rate ) N A N D になることができる。例示的な実施形態において、N A N D フラッシュメモリ装置5 1 0 0 は、単品のN A N D フラッシュメモリ装置を含むことができる。ここで、単品のN A N D フラッシュメモリ装置、一つのパッケージ( 例えば、F B G A 、F i n e - p i t c h B a l l G r i d A r r a y ) に積層されて実現され得る。単品のN A N D フラッシュメモリ装置の各々は、図4に示したものと実質的に同一に構成され、制御器5 2 0 0 は、図2に示したものと実質的に同一に動作する。例えば、メモリ制御器5 2 0 0 は、読み出し校正動作の対象ブロックであるT L C ブロックをキューを用いて管理し、特定の時間( 例えば、ホストの書き込み要請の時 ) に、キューに格納された情報に基づいてT L C ブロックを選択し、選択されたT L C ブロックの有効なページのデータがS L C ブロックに移動するようN A N D フラッシュメモリ装置5 1 0 0 を制御する。メモリ制御器5 2 0 0 は、選択されたT L C ブロックの有効なページのデータがN A N D フラッシュメモリ装置5 1 0 0 に含まれたS L C ブロックに移動する時、選択されたT L C ブロックに対する読み出し校正動作を完了したと処理する。

#### 【 0 0 9 1 】

メモリ制御器5 2 0 0 は、複数のチャネルを通じてフラッシュメモリ装置5 1 0 0 に接続する。制御器5 2 0 0 は、少なくとも一つの制御器コア5 2 1 0 と、ホストインターフェース5 2 2 0 と、N A N D インターフェース5 2 3 0 とを含む。少なくとも一つの制御器コア5 2 1 0 は、M o v i N A N D 3 0 0 0 の全体的な動作を制御する。ホストインターフェース5 2 2 0 は、制御器5 2 1 0 とホストのインターフェイシングを実行する。N A N D インターフェース5 2 3 0 は、N A N D フラッシュメモリ装置5 1 0 0 と制御器5 2 0 0 のインターフェイシングを実行する。例示的な実施形態において、ホストインターフェース5 2 2 0 は、並列インターフェース( 例えば、M M C インターフェース ) になることができる。別の実施形態において、M o v i N A N D 5 0 0 0 のホストインターフェース5 2 2 0 は、直列インターフェース( 例えば、U H S - I I 、U F S インターフェース ) になることができる。

#### 【 0 0 9 2 】

10

20

30

40

50

M o v i N A N D 5 0 0 0 は、ホストから電源電圧 V c c 、 V c c q が提供される。ここで、第1電源電圧 ( V c c : 3 . 3 V ) は、N A N D フラッシュメモリ装置 5 1 0 0 と N A N D インターフェース 5 2 3 0 に提供され、第2電源電圧 ( V c c q : 1 . 8 V / 3 . 3 V ) は、制御器 5 2 0 0 に提供される。例示的な実施形態において、M o v i N A N D 5 0 0 0 は、外部の高電圧 V p p が選択的に提供され得る。

本発明に係る M o v i N A N D 5 0 0 0 は、大容量のデータの格納に有利であるだけでなく、向上した読み出し動作特性を有する。本発明の実施形態に係る M o v i N A N D 5 0 0 0 は、小型及び低電力が要求されるモバイル製品（例えば、G A L A X Y S 、 G A L A X Y Note 、 i P h o n e など）に応用可能である。

#### 【 0 0 9 3 】

図 1 8 は、本発明に係る通信装置を概略的に示すブロック図である。図 1 8 を参照すると、モバイル装置 6 0 0 0 は、通信ユニット 6 1 0 0 と、制御器 6 2 0 0 と、メモリユニット 6 3 0 0 と、ディスプレイユニット 6 4 0 0 と、タッチスクリーンユニット 6 5 0 0 と、オーディオユニット 6 6 0 0 とを含む。メモリユニット 6 3 0 0 は、少なくとも一つの D R A M 6 3 1 0 と、少なくとも一つの O n e N A N D 6 3 2 0 と、少なくとも一つの M o v i N A N D 6 3 3 0 とを含む。

モバイル装置に関するより詳細な説明は、特許文献 4 、 5 、 6 、 7 及び 8 に記載されている。

#### 【 0 0 9 4 】

図 1 9 は、本発明の実施形態に係る半導体ドライブが適用されるシステムを概略的に示す図である。

図 1 9 に示すように、本発明の実施形態に係る半導体ドライブは、メールサーバ 8 1 0 0 にも適用可能である。

#### 【 0 0 9 5 】

図 2 0 は、本発明の実施形態に係るメモリカード ( m e m o r y c a r d ) を概略的に示すブロック図である。

メモリカードは、例えば、M M C カード、S D カード、マルチユース ( m u l t i u s e ) カード、マイクロ S D カード、メモリスティック、コンパクト S D カード、I D カード、P C M C I A カード、S S D カード、チップカード ( c h i p c a r d ) 、スマートカード ( s m a r t c a r d ) 、U S B カードなどになることができる。

#### 【 0 0 9 6 】

図 2 0 を参照すると、メモリカードは、外部とのインターフェースを実行するインターフェース部 9 2 2 1 と、バッファメモリを有し、メモリカードの動作を制御する制御器 9 2 2 2 と、1 つ以上の不揮発性メモリ装置 9 2 0 7 とを含む。

制御器 9 2 2 2 は、プロセッサとして、不揮発性メモリ装置 9 2 0 7 のライト動作及びリード動作を制御することができる。具体的に、制御器 9 2 2 2 は、データバス D A T A とアドレスバス A D D R E S S を通じて不揮発性メモリ装置 9 2 0 7 及びインターフェース部 9 2 2 1 とカップリングされている。インターフェース部 9 2 2 1 は、ホストとメモリカードとの間のデータ交換を実行するためのカードプロトコル（例えば、S D / M M C ）を通じてホストとインターフェイシングする。

#### 【 0 0 9 7 】

制御器 9 2 2 2 は、図 2 に示したものと実質的に同一に構成され、不揮発性メモリ装置 9 2 0 7 は、図 4 に示した不揮発性メモリ装置と実質的に同一に構成される。例えば、制御器 9 2 2 2 は、読み出し校正動作の対象ブロックである T L C ブロックを、キューを利用して管理し、特定の時間（例えば、ホストの書き込み要請の時）に、キューに格納された情報に基づいて T L C ブロックを選択し、選択された T L C ブロックの有効なページのデータが不揮発性メモリ装置 9 2 0 7 に含まれた S L C ブロックに移動するよう不揮発性メモリ装置 9 2 0 7 を制御する。制御器 9 2 2 2 は、選択された T L C ブロックの有効なページのデータが不揮発性メモリ装置 9 2 0 7 に含まれた S L C ブロックに移動する時、選択された T L C ブロックに対する読み出し校正動作を完了したと処理する。

10

20

30

40

50

## 【0098】

図21は、本発明の実施形態に係るデジタルスチルカメラ (digital still camera) を概略的に示すブロック図である。

図21を参照すると、デジタルスチルカメラは、ボディ9301と、スロット9302と、レンズ9303と、ディスプレイ部9308と、シャッターボタン9312と、ストローブ(strobe)9318などを含む。特に、スロット9308には、メモリカード9331を挿入することができ、メモリカード9331は、図1で説明したメモリ制御器と不揮発性メモリ装置とを含む。例えば、メモリ制御器は、読み出し校正動作の対象ブロックであるTLCブロックを、キューを利用して管理し、特定の時間(例えば、ホストの書き込み要請の時)に、キューに格納された情報に基づいてTLCブロックを選択し、選択されたTLCブロックの有効なページのデータが不揮発性メモリ装置に含まれたSLCブロックに移動するように不揮発性メモリ装置を制御する。メモリ制御器は、選択されたTLCブロックの有効なページのデータが不揮発性メモリ装置に含まれたSLCブロックに移動する時、選択されたTLCブロックに対する読み出し校正動作を完了したと処理する。10

## 【0099】

メモリカード9331が接触型(contact type)の場合、メモリカード9331がスロット9308に挿入される時、メモリカード9331と回路基板上の特定の電気回路が電気的に接触することになる。メモリカード9331が、非接触型(non contact type)の場合、無線信号を通じてメモリカード9331がアクセスされる。20

## 【0100】

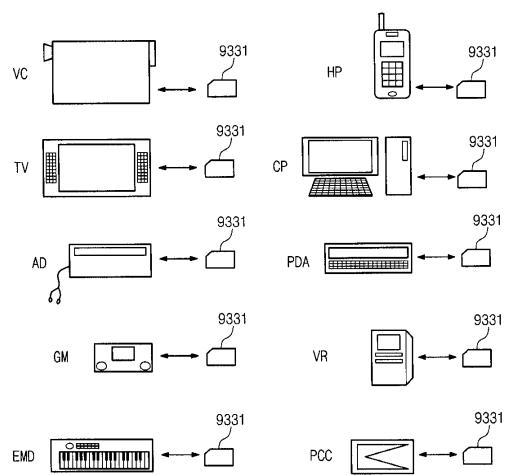

図22は、図21のメモリカードが使用される様々な応用分野を示す図である。

図22を参照すると、メモリカード9331は、ビデオカメラ(VC)、テレビ(TV)、オーディオ装置(AD)、ゲーム装置(GM)、電子音楽装置(EMD)、携帯電話(HP)、コンピュータ(CP)、PDA(Personal Digital Assistant)、ボイスレコーダ(voice recorder)(VR)、PCカード(PCC)などに使用することができる。

本発明の実施形態において、メモリセルは、可変抵抗メモリセルで構成することができ、例示的な可変抵抗メモリセル及びそれを含むメモリ装置は、特許文献9に掲載されている。30

## 【0101】

本発明の別の実施形態において、メモリセルは、電荷格納層を有する多様なセル構造のうちの一つを使用して実現することができる。電荷格納層を有するセル構造は、電荷トラップ層を利用する電荷トラップフラッシュ構造、アレイが多層で積層されるスタックフラッシュ構造、ソース/ドレインがないフラッシュ構造、ピンタイプフラッシュ構造などを含む。

電荷格納層として電荷トラップフラッシュ構造を有するメモリ装置が、特許文献10、11、12に各々掲載されている。ソース/ドレインがないフラッシュ構造は、特許文献13に掲載されている。40

## 【0102】

本発明に係るフラッシュメモリ装置及び/またはメモリ制御器は、多様な形態のパッケージを利用して実装することができる。例えば、本発明に係るフラッシュメモリ装置及び/またはメモリ制御器は、POP(Package on Package)、Ball grid arrays(BGAs)、Chip scale packages(CSPs)、Plastic Leaded Chip Carrier(PLCC)、Plastic Dual In-Line Package(PDIP)、Die in Waffle Pack、Die in Wafer Form、Chip On Board(COB)、Ceramic Dual In-Line Package(CERDIP)、Plastic Metric Quad Flat Pack(MQF)50

P)、Thin Quad Flatpack(TQFP)、Small Outline(SOIC)、Shrink Small Outline Package(SSOP)、Thin Small Outline(TSOP)、Thin Quad Flatpack(TQFP)、System In Package(SIP)、Multi Chip Package(MCP)、Wafer-level Fabricated Package(WFP)、Wafer-Level Processed Stack Package(WSP)などのようなパッケージを利用して実装することができる。

#### 【0103】

本発明の範囲又は技術的思想を逸脱せずに本発明の構造を多様に修正又は変更可能であることはこの分野に熟練している者に自明である。上述の内容を考慮する時、本発明の修正及び変更が添付の特許請求の範囲及びその均等物の範疇内に属すれば、本発明はこの発明の変更及び修正を含むと見なす。10

#### 【符号の説明】

#### 【0104】

1000 メモリシステム

1200 メモリ制御器

1210 ホストインターフェース

1220 メモリインターフェース

1230 CPU

20

1240 バッファメモリ

1250 ECC回路

1400 不揮発性メモリ装置

1410 メモリセルアレイ

1411 第1メモリ領域

1412 第2メモリ領域

1420 アドレスデコーダ

1430 電圧発生器

1440 制御ロジック

1450 ページバッファ回路

30

1460 入出力インターフェース

【図1】

【図2】

【図3】

【図4】

【図5】

【図6B】

【図6A】

【図6C】

【図6D】

【図7】

【図 8 A】

【図 9】

【図 8 B】

【図 10】

【図 11】

【図12】

【図14】

【図13】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

(72)発明者 金 煥忠

大韓民国全羅北道南原市竹巷洞106-3番地

(72)発明者 朴 キョン 奎

大韓民国ソウル特別市江西区登村洞655-27番地 現代アパート101棟1407号

(72)発明者 朴 恩珠

大韓民国京畿道龍仁市器興区下葛洞(番地なし) シナンインスヴィルアパート103棟603号

(72)発明者 薛 峯官

大韓民国ソウル特別市江東区城内洞144-21番地 301号

審査官 塚田 肇

(56)参考文献 特開2011-128984(JP,A)

特表2013-509651(JP,A)

特表2014-517425(JP,A)

特開2012-079403(JP,A)

米国特許出願公開第2011/0047422(US,A1)

米国特許出願公開第2009/0168587(US,A1)

特開2003-015954(JP,A)

米国特許出願公開第2010/0332922(US,A1)

米国特許第6675262(US,B1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 11 / 10

G 06 F 12 / 00