(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5376839号

(P5376839)

(45) 発行日 平成25年12月25日(2013.12.25)

(24) 登録日 平成25年10月4日(2013.10.4)

(51) Int.Cl.

F 1

G 11 C 16/02 (2006.01)

G 11 C 16/04 (2006.01)G 11 C 17/00 612 D

G 11 C 17/00 622 E

G 11 C 17/00 624

請求項の数 16 (全 15 頁)

(21) 出願番号 特願2008-153152 (P2008-153152)

(22) 出願日 平成20年6月11日 (2008.6.11)

(65) 公開番号 特開2008-305536 (P2008-305536A)

(43) 公開日 平成20年12月18日 (2008.12.18)

審査請求日 平成23年6月10日 (2011.6.10)

(31) 優先権主張番号 10-2007-0056792

(32) 優先日 平成19年6月11日 (2007.6.11)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100086368

弁理士 萩原 誠

(72) 発明者 金 杜 坤

大韓民国京畿道華城市盤松洞21番地 示

範ヘッピンマウル韓化クムエグリンアパー

ト235棟2302号

最終頁に続く

(54) 【発明の名称】不揮発性メモリ装置の消去方法

## (57) 【特許請求の範囲】

## 【請求項 1】

NAND型メモリセルアレイを有する不揮発性メモリ装置の消去された複数のメモリセルに対するポストプログラム動作方法において、

第1セレクトトランジスタに隣接する第1ダミーメモリセルに対してポストプログラムを行うステップと、

第1電圧を利用して前記第1ダミーメモリセルのしきい電圧を検証するステップと、

第2セレクトトランジスタに隣接する第2ダミーメモリセルに対してポストプログラムを行うステップと、

前記第1電圧とは異なる第2電圧を利用して前記第2ダミーメモリセルのしきい電圧を検証するステップと、

前記第1ダミーメモリセルと前記第2ダミーメモリセルとの間に配設された複数のノーマルメモリセルに対して前記ポストプログラムを行うステップと、を含み、

前記第1又は第2ダミーメモリセルに対してポストプログラムを行うステップは、

前記第1又は第2ダミーメモリセルに対して前記ポストプログラムを行うように、前記第1ダミーメモリセルに連結された第1ダミーワードライン又は前記第2ダミーメモリセルに連結された第2ダミーワードラインにプログラム電圧を印加するステップと、

前記複数のノーマルメモリセルに連結された複数のノーマルワードラインに、前記プログラム電圧より低い電圧レベルを有するバス電圧を印加するステップと、を含むことを特徴とするポストプログラム動作方法。

10

20

**【請求項 2】**

前記ポストプログラム動作方法は、第3電圧を利用して前記複数のノーマルメモリセルのしきい電圧を検証するステップをさらに含むことを特徴とする請求項1に記載のポストプログラム動作方法。

**【請求項 3】**

前記第1及び第2電圧は、前記第3電圧とは相異なる電圧レベルを有することを特徴とする請求項2に記載のポストプログラム動作方法。

**【請求項 4】**

前記第1及び第2電圧は、

前記第3電圧より高い電圧レベルを有することを特徴とする請求項3に記載のポストプログラム動作方法。 10

**【請求項 5】**

前記ポストプログラム動作方法は、

前記第1ダミーメモリセルのしきい電圧が前記第1電圧より低いと検証された場合、前記第1ダミーメモリセルに対してポストプログラムを再び行うステップと、

前記第2ダミーメモリセルのしきい電圧が前記第2電圧より低いと検証された場合、前記第2ダミーメモリセルに対してポストプログラムを再び行うステップと、

をさらに含むことを特徴とする請求項1に記載のポストプログラム動作方法。

**【請求項 6】**

前記ポストプログラム動作方法は、

20

前記複数のノーマルメモリセルのしきい電圧が前記第3電圧より低いと検証された場合、前記複数のノーマルメモリセルに対してポストプログラムを再び行うステップをさらに含むことを特徴とする請求項2に記載のポストプログラム動作方法。

**【請求項 7】**

前記複数のノーマルメモリセルに対してポストプログラムを行うステップは、

前記複数のノーマルメモリセルに対して前記ポストプログラムを行うように、前記複数のノーマルメモリセルに連結された複数のノーマルワードラインに前記プログラム電圧を印加するステップと、

前記第1及び第2ダミーワードラインに前記バス電圧を印加するステップと、を含むことを特徴とする請求項1に記載のポストプログラム動作方法。 30

**【請求項 8】**

前記第1ダミーメモリセルのしきい電圧を検証するステップは、

前記第1ダミーメモリセルに連結された前記第1ダミーワードラインに前記第1電圧を印加するステップと、

前記複数のノーマルメモリセルに連結された複数のノーマルワードラインに第4電圧を印加するステップと、を含み、

前記第2ダミーメモリセルのしきい電圧を検証するステップは、

前記第2ダミーメモリセルに連結された前記第2ダミーワードラインに前記第2電圧を印加するステップと、

前記複数のノーマルメモリセルに連結された複数のノーマルワードラインに前記第4電圧を印加するステップと、を含み、 40

前記第4電圧は、

前記第1乃至第3電圧よりは高い電圧レベルを有することを特徴とする請求項2に記載のポストプログラム動作方法。

**【請求項 9】**

前記複数のノーマルメモリセルのしきい電圧を検証するステップは、

前記複数のノーマルメモリセルに連結された複数のノーマルワードラインに前記第3電圧を印加するステップと、

前記第1及び第2ダミーワードラインに第4電圧を印加するステップと、を含み、

前記第4電圧は、 50

前記第1乃至第3電圧よりは高い電圧レベルを有することを特徴とする請求項2に記載のポストプログラム動作方法。

【請求項10】

前記複数のノーマルメモリセルに対して前記ポストプログラムを行うステップ及び前記複数のノーマルメモリセルのしきい電圧を検証するステップは、前記第1ダミーメモリセルに対してポストプログラムを行うステップ、前記第1ダミーメモリセルのしきい電圧を検証するステップ、前記第2ダミーメモリセルに対してポストプログラムを行うステップ、及び前記第2ダミーメモリセルのしきい電圧を検証するステップ以前に行われることを特徴とする請求項2に記載のポストプログラム動作方法。

【請求項11】

前記第1ダミーメモリセルに対してポストプログラムを行うステップ、前記第1ダミーメモリセルのしきい電圧を検証するステップ、前記第2ダミーメモリセルに対してポストプログラムを行うステップ、及び前記第2ダミーメモリセルのしきい電圧を検証するステップは、前記複数のノーマルメモリセルに対して前記ポストプログラムを行うステップ及び前記複数のノーマルメモリセルのしきい電圧を検証するステップ以前に行われることを特徴とする請求項2に記載のポストプログラム動作方法。

【請求項12】

NAND型メモリセルアレイを有する不揮発性メモリ装置の消去された複数のメモリセルに対するポストプログラム動作方法において、

第1セレクトトランジスタに隣接する第1ダミーメモリセルと、第2セレクトトランジスタに隣接する第2ダミーメモリセルと、前記第1ダミーメモリセルと第2ダミーメモリセルとの間に配設された複数のノーマルメモリセルとに対してポストプログラムを行うステップと、

前記第1ダミーメモリセル、前記第2ダミーメモリセル、及び前記複数のノーマルメモリセルのしきい電圧を、それぞれ、第1電圧、前記第1電圧とは異なる第2電圧、及び第3電圧を利用して検証するステップと、を含み、

前記第1又は第2ダミーメモリセルに対してポストプログラムを行うステップは、前記第1又は第2ダミーメモリセルに対して前記ポストプログラムを行うように、前記第1ダミーメモリセルに連結された第1ダミーワードライン又は前記第2ダミーメモリセルに連結された第2ダミーワードラインにプログラム電圧を印加するステップと、

前記複数のノーマルメモリセルに連結された複数のノーマルワードラインに、前記プログラム電圧より低い電圧レベルを有するバス電圧を印加するステップと、を含むことを特徴とするポストプログラム動作方法。

【請求項13】

前記ポストプログラム動作方法はさらに、

しきい電圧が前記第1電圧より低い前記第1ダミーメモリセル、しきい電圧が前記第2電圧より低い前記第2ダミーメモリセル、及びしきい電圧が前記第3電圧より低い前記ノーマルメモリセルを、第1メモリセルグループとし、しきい電圧が前記第1電圧以上の前記第1ダミーメモリセル、しきい電圧が前記第2電圧以上の前記第2ダミーメモリセル、及びしきい電圧が前記第3電圧以上の前記ノーマルメモリセルを、第2メモリセルグループとしてグループ分けするステップを含むことを特徴とする請求項12に記載のポストプログラム動作方法。

【請求項14】

前記ポストプログラム動作方法は、前記第1メモリセルグループに対してポストプログラムを再び行うステップをさらに含み、

前記第2メモリセルグループに対してはポストプログラムを再度行わないことを特徴とする請求項13に記載のポストプログラム動作方法。

【請求項15】

前記第1及び第2電圧は、前記第3電圧とは相異なる電圧レベルを有することを特徴とする請求項12に記載のポストプログラム動作方法。

10

20

30

40

50

**【請求項 16】**

前記第1及び第2電圧は、

前記第3電圧より高い電圧レベルを有することを特徴とする請求項15に記載のポストプログラム動作方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体メモリ装置に係り、特に、不揮発性メモリ装置に関する。

**【背景技術】****【0002】**

半導体メモリ装置は、DRAM (Dynamic Random Access Memory) 及びSRAM (Static Random Access Memory) のように、電源が切れるとデータを失い、かつデータの入出力が速い揮発性メモリ装置と、一度データを入力すれば、その状態を維持し、データの入出力が揮発性メモリに比べて相対的に遅い不揮発性メモリ装置とに大別される。不揮発性メモリ装置は、ROM (Read Only Memory)、PROM (Programmable ROM)、EPROM (Erasable PROM) 及びEEPROM (Electrically EPROM) に分類される。EEPROMまたは一括消去機能を有するフラッシュ EEPROM (以下、フラッシュメモリという) は、フローティングゲートと制御ゲートとが積層されたスタック型ゲート構造を有する。

10

フラッシュメモリ装置のメモリアレイは、ストリングを基本単位とし、多数のストリングを備える。このストリングは、セレクトトランジスタと多数のメモリセルとが直列に接続された構造となる。この場合、フラッシュメモリ装置は、ドラインセレクトラインに隣接したワードラインに連結されたメモリセル及びソースセレクトラインに隣接したワードラインに連結されたメモリセルでプログラム速度が落ちる問題が発生した。この問題点を解決するために、最近では、ストリングにダミーワードラインに連結されるメモリセルを追加する構造が使われている。ダミーワードラインを備えるフラッシュメモリ装置の実施形態については、特許文献1に開示されている。

**【0003】**

20

フラッシュメモリ装置の消去動作は、プレプログラム動作、メイン消去動作及びポストプログラム動作に大別される。プレプログラム動作は、次に行う消去動作時に過度に消去されるメモリセルの発生を防止するために、正常的なプログラム動作と同じバイアス条件を利用して行われる。消去されるメモリセルは、何れもプレプログラムされる。プレプログラム以後にセクタの全てのメモリセルがオン - セル状態を有するように、メイン消去動作が行われる。メイン消去動作が開始されれば、セクタ内の全てのメモリセルが同時に消去される。最後に、メイン消去動作によって過度に消去されたメモリセルを治癒するために、ポストプログラム動作が行われる。ポストプログラム動作は、バイアス条件を除外すれば、プレプログラム動作と同一に行われる。

**【0004】**

30

ダミーワードラインを備えたフラッシュメモリ装置でポストプログラム動作を行う場合、従来は、ダミーワードラインに連結されたダミーメモリセル及びノーマルワードラインに連結されたノーマルメモリセルに対して区別なしに一括的にポストプログラム動作を行った。すなわち、ポストプログラムを行った結果、ノーマルメモリセル及びダミーメモリセルは、同じしきい電圧を有する。この場合、消去動作が終了した後にプログラム動作を行うとき、ターンオフされねばならないダミーメモリセルがターンオンされる場合が発生して、ノーマルメモリセルのプログラムを妨害する場合が発生する。

【特許文献1】米国特許公開第2006-13997号公報(2006年6月29日公開)

**【発明の開示】**

40

50

**【発明が解決しようとする課題】****【0006】**

本発明が解決しようとする技術的課題は、ノーマルワードラインに連結されたノーマルメモリセル及びダミーワードラインに連結されたダミーメモリセルに対して別途にポストプログラムを行う不揮発性メモリ装置の消去方法を提供することである。

**【課題を解決するための手段】****【0007】**

前記課題を達成するための本発明の実施形態による不揮発性メモリ装置の消去方法は、不揮発性メモリ装置でポストプログラムを行う消去方法において、ダミーメモリセルに対してポストプログラムを行うステップ、第1電圧を利用して前記ダミーメモリセルのしきい電圧を検証するステップ、ノーマルメモリセルに対して前記ポストプログラムを行うステップ及び第2電圧を利用して前記ノーマルメモリセルのしきい電圧を検証するステップを含み、前記第1電圧は、前記第2電圧とは相異なる電圧レベルを有しうる。10

**【0008】**

前記第1電圧は、前記第2電圧より高い電圧レベルを有することが望ましい。

前記不揮発性メモリ装置の消去方法は、前記ダミーメモリセルのしきい電圧が前記第1電圧より低い場合、前記ダミーメモリセルに対してポストプログラムを再び行うステップをさらに含むことが望ましい。

前記不揮発性メモリ装置の消去方法は、前記ノーマルメモリセルのしきい電圧が前記第2電圧より低い場合、前記ノーマルメモリセルに対してポストプログラムを再び行うステップをさらに含むことが望ましい。20

**【0009】**

前記ダミーメモリセルに対してポストプログラムを行うステップは、前記ダミーメモリセルに対して前記ポストプログラムを行うように、前記ダミーメモリセルに連結されたダミーワードラインにプログラム電圧を印加するステップ及び前記ノーマルメモリセルに対して前記ポストプログラムを行わないように、前記ノーマルメモリセルに連結されたノーマルワードラインにバス電圧を印加するステップを含むことが望ましい。

**【0010】**

前記ノーマルメモリセルに対してポストプログラムを行うステップは、前記ノーマルメモリセルに対して前記ポストプログラムを行うように、前記ノーマルメモリセルに連結されたノーマルワードラインにプログラム電圧を印加するステップ及び前記ダミーメモリセルに対して前記ポストプログラムを行わないように、前記ダミーメモリセルに連結されたダミーワードラインにバス電圧を印加するステップを含むことが望ましい。30

**【0011】**

前記ノーマルメモリセルに対して前記ポストプログラムを行うステップ及び前記ノーマルメモリセルのしきい電圧を検証するステップは、前記ダミーメモリセルに対してポストプログラムを行うステップ及び前記ダミーメモリセルのしきい電圧を検証するステップ以前に行われることが望ましい。

前記ダミーメモリセルに対してポストプログラムを行うステップ及び前記ダミーメモリセルのしきい電圧を検証するステップは、前記ノーマルメモリセルに対して前記ポストプログラムを行うステップ及び前記ノーマルメモリセルのしきい電圧を検証するステップ以前に行われることが望ましい。40

**【0012】**

前記ダミーメモリセルに対してポストプログラムを行うステップ及び前記ノーマルメモリセルに対して前記ポストプログラムを行うステップは、前記ノーマルメモリセルのしきい電圧を検証するステップ及び前記ダミーメモリセルのしきい電圧を検証するステップ以前に行われることが望ましい。

**【0013】**

前記課題を達成するための本発明の他の実施形態による不揮発性メモリ装置の消去方法は、不揮発性メモリ装置でポストプログラムを行う消去方法において、第1ダミーメモリ50

セルに対してポストプログラムを行うステップ、第1電圧を利用して前記第1ダミーメモリセルのしきい電圧を検証するステップ、第2ダミーメモリセルに対して前記ポストプログラムを行うステップ、第2電圧を利用して前記第2ダミーメモリセルのしきい電圧を検証するステップ、ノーマルメモリセルに対して前記ポストプログラムを行うステップ及び第3電圧を利用して前記ノーマルメモリセルのしきい電圧を検証するステップを含み、前記第3電圧は、前記第1電圧及び前記第2電圧とは相異なる電圧レベルを有しうる。

#### 【0014】

前記課題を達成するための本発明のさらに他の実施形態による不揮発性メモリ装置の消去方法は、不揮発性メモリ装置でポストプログラムを行う消去方法において、ノーマルメモリセル及びダミーメモリセルに対してポストプログラムを行うステップ、第1電圧を利用して前記ダミーメモリセルのしきい電圧を検証するステップ、第2電圧を利用して前記ノーマルメモリセルのしきい電圧を検証するステップ及び前記しきい電圧が検証されないダミーメモリセル及び前記しきい電圧が検証されないノーマルメモリセルを含むメモリセルグループに対して前記ポストプログラムを行うステップを含み、前記第1電圧は、前記第2電圧とは相異なる電圧レベルを有しうる。

#### 【0015】

前記課題を達成するための本発明のさらに他の実施形態による不揮発性メモリ装置の消去方法は、不揮発性メモリ装置でポストプログラムを行う消去方法において、ノーマルメモリセル、第1ダミーメモリセル及び第2ダミーメモリセルに対してポストプログラムを行うステップ、第1電圧を利用して前記第1ダミーメモリセルのしきい電圧を検証するステップ、第2電圧を利用して前記第2ダミーメモリセルのしきい電圧を検証するステップ、第3電圧を利用して前記ノーマルメモリセルのしきい電圧を検証するステップ及び前記しきい電圧が検証されない第1ダミーメモリセル、前記しきい電圧が検証されない第2ダミーメモリセル及び前記しきい電圧が検証されないノーマルメモリセルを含むメモリセルグループに対して前記ポストプログラムを行うステップを含み、前記第3電圧は、前記第1電圧及び前記第2電圧とは相異なる電圧レベルを有しうる。

#### 【発明の効果】

#### 【0016】

本発明による不揮発性メモリ装置の消去方法は、ノーマルメモリセル及びダミーメモリセルに対して別途にポストプログラムを行うことによって、接合ポテンシャルが増加してセルの信頼性を向上させ、ダミーメモリセルのターンオンによるノーマルメモリセルのプログラムを妨害する現象を防止しうる。

#### 【発明を実施するための最良の形態】

#### 【0017】

本発明と本発明の動作上の利点及び本発明の実施によって達成される目的を十分に理解するためには、本発明の望ましい実施形態を例示する添付図面及び図面に記載された内容を参照しなければならない。

以下、添付した図面を参照して、本発明の望ましい実施形態を説明することによって、本発明を詳細に説明する。各図面に付された同一参照符号は、同一部材を表す。

#### 【0018】

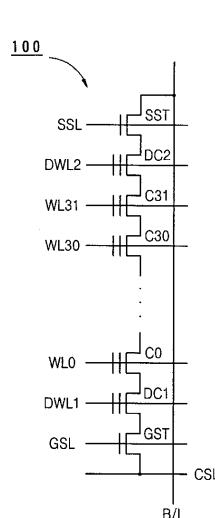

図1は、不揮発性半導体メモリ装置の回路図である。

図1では、不揮発性半導体メモリ装置の一つのストリング100を示した。図1を参照すれば、不揮発性半導体メモリ装置、特に、フラッシュメモリ装置の一つのストリング100は、第1セレクトトランジスタGST、第2セレクトトランジスタSST、第1ダミーメモリセルDC1、第2ダミーメモリセルDC2及び複数のノーマルメモリセルC0,...,C30,C31を備える。図1では、32個のメモリセルが直列に連結された場合について示しているが、16個、64個のメモリセルを直列に連結した場合にも、本発明の方法による場合、同じ効果が得られるというは、当業者に自明な事項である。

#### 【0019】

第1セレクトトランジスタGSTのゲートラインは、第1セレクトラインGSLとなり

10

20

30

40

50

、第2セレクトトランジスタS S Tのゲートラインは、第2セレクトラインS S Lとなり、ノーマルメモリセルC 0, …, C 3 1のゲートラインは、ノーマルワードラインW L 0, …, W L 3 1となる。また、第1ダミーメモリセルD C 1のゲートラインは、第1ダミーワードラインD W L 1となり、第2ダミーメモリセルD C 2のゲートラインは、第2ダミーワードラインD W L 2となる。本発明の実施形態によるポストプログラム動作を行う方法については、以下で詳細に説明する。

#### 【0020】

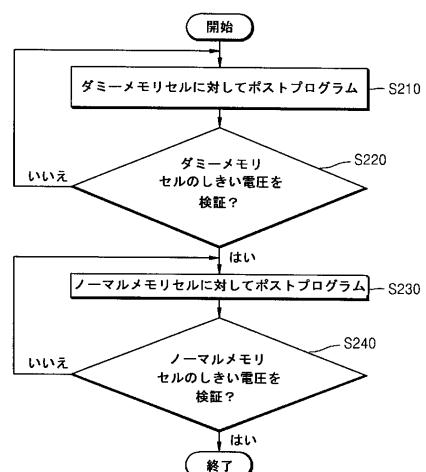

図2は、本発明の実施形態による不揮発性メモリ装置の消去方法を示すフローチャートである。

図2は、不揮発性メモリ装置の消去方法のうち、特にポストプログラム動作を行う方法について示している。図1及び図2を参照して、32個のノーマルメモリセル及び2個のダミーメモリセルが直列に連結されたストリングを有する不揮発性メモリ装置で前記ポストプログラムを行う場合について説明する。一旦、ノーマルワードラインW L 0, …, W L 3 1に連結されたノーマルメモリセルC 0, …, C 3 1については、ポストプログラムを行わず、ダミーワードラインD W L 1, D W 2に連結されたダミーメモリセルD C 1, D C 2に対してポストプログラムを行う(S 2 1 0)。ダミーメモリセルD C 1, D C 2に対するポストプログラムが終了すれば、ダミーメモリセルD C 1, D C 2に対してポストプログラムが正常的に行われたか否かを検証する。すなわち、第1電圧を利用してダミーメモリセルD C 1, D C 2のしきい電圧を検証する(S 2 2 0)。前記第1電圧は、ダミーメモリセルD C 1, D C 2に対して前記ポストプログラムを行って変更しようとするしきい電圧値である。

#### 【0021】

検証の結果、ダミーメモリセルD C 1, D C 2のしきい電圧が前記第1電圧より低い場合、ダミーメモリセルD C 1, D C 2に対して再びポストプログラムを行う(S 2 1 0)。

前記検証結果、ダミーメモリセルD C 1, D C 2のしきい電圧が前記第1電圧以上である場合、ノーマルメモリセルC 0, …, C 3 1に対してポストプログラムを行う(S 2 3 0)。ノーマルメモリセルC 0, …, C 3 1に対してポストプログラムが終了すれば、ポストプログラムが正常的に行われたか否かを検証する。すなわち、第2電圧を利用してポストプログラムが行われたノーマルメモリセルのしきい電圧を検証する(S 2 4 0)。第2電圧は、ノーマルメモリセルC 0, …, C 3 1に対してポストプログラムを行って変更しようとするしきい電圧値である。第1電圧は、第2電圧より高い電圧レベルを有することが望ましい。

検証の結果、ノーマルメモリセルのしきい電圧が第2電圧より低い場合、ノーマルメモリセルに対して再びポストプログラムを行う(S 2 3 0)。

#### 【0022】

図3は、図2の実施形態によるポストプログラムを行う場合、電圧条件を示すテーブルである。

図1ないし図3を参照すれば、ダミーメモリセルD C 1, D C 2に対してポストプログラムを行うS 2 1 0の場合、ダミーワードラインD W L 1, D W L 2には、プログラム電圧V p g mを印加し、ノーマルワードラインW L 0, …, W L 3 1には、バス電圧V p a s sを印加する。プログラム電圧V p g mは、ポストプログラムを行うメモリセルのゲートに連結されたワードラインに印加される電圧であって、例えば、25Vの電圧を使用しうる。バス電圧V p a s sは、ポストプログラムを行わないメモリセルのゲートに連結されたワードラインに印加される電圧であって、例えば、8Vの電圧を使用しうる。

#### 【0023】

第1電圧を利用してダミーメモリセルD C 1, D C 2のしきい電圧を検証するS 2 2 0は、ダミーワードラインD W L 1, D W L 2に第1電圧V r 1を印加し、ノーマルワードラインW L 0, …, W L 3 1に第3電圧V r e a dを印加する。第3電圧V r e a dは、検証しないワードラインに印加される電圧であって、第1電圧V r 1より高い電圧レベル

10

20

30

40

50

を有することが望ましい。例えば、第3電圧V<sub>read</sub>は、6.5Vでありうる。

**【0024】**

ダミーメモリセルDC1, DC2に対する検証が完了して、ノーマルメモリセルC0, ..., C31に対してポストプログラムを行うS230の場合、S210とは逆に、ノーマルメモリセルC0, ..., C31に連結されたノーマルワードラインWL0, ..., WL31に対しては、プログラム電圧V<sub>pgm</sub>を印加し、ダミーワードラインDWL1, DWL2に対しては、バス電圧V<sub>pass</sub>を印加する。第3電圧V<sub>read</sub>は、第2電圧V<sub>r2</sub>より高い電圧レベルを有することが望ましい。

**【0025】**

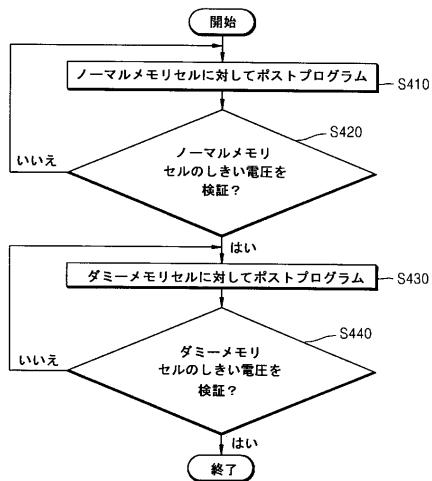

図4は、本発明の他の実施形態による不揮発性メモリ装置の消去方法を示すフローチャートである。

10

図1、図2及び図4を参照すれば、図4の実施形態は、図2の実施形態と順序を異ならせている。すなわち、図2の実施形態は、ダミーメモリセルDC1, DC2に対して、まずポストプログラム(S210)及び検証(S220)を行った後、ノーマルメモリセルC0, ..., C31に対してポストプログラム(S230)及び検証(S240)を行った。しかし、図4の実施形態では、ノーマルメモリセルC0, ..., C31に対して、まずポストプログラム(S410)を行い、第2電圧を利用してノーマルメモリセルC0, ..., C31のしきい電圧を検証する(S420)。前記ノーマルメモリセルC0, ..., C31に対してポストプログラム及び検証を完了した後、ダミーメモリセルDC1, DC2に対してポストプログラム(S430)を行い、第1電圧を利用してダミーメモリセルDC1, DC2のしきい電圧を検証する(S440)。前記各ステップでの動作は、図2の場合と同一であるので、以下では詳細な説明を省略する。

20

**【0026】**

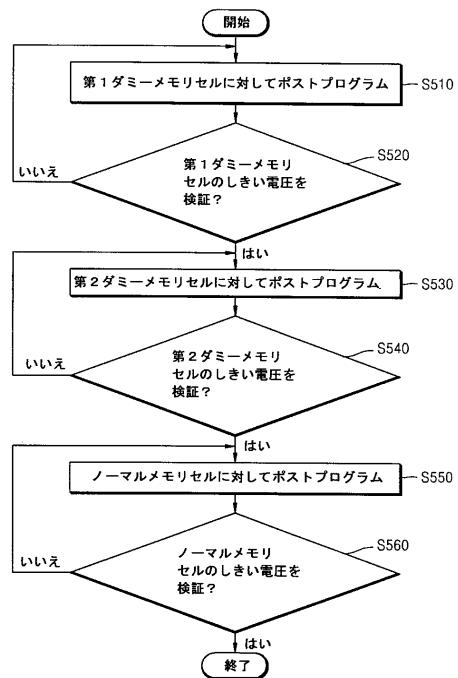

図5は、本発明のさらに他の実施形態による不揮発性メモリ装置の消去方法を示すフローチャートである。

図6は、図5の実施形態によるポストプログラムを行う場合、電圧条件を示すテーブルである。

**【0027】**

図1、図5及び図6を参照すれば、図5の実施形態は、ダミーメモリセルDC1, DC2のそれぞれが異なるしきい電圧を有するようにポストプログラムを行う。すなわち、第1ダミーワードラインDWL1に連結された第1ダミーメモリセルDC1に対して、まずポストプログラムを行う(S510)。第1ダミーワードラインDWL1には、プログラム電圧V<sub>pgm</sub>を印加し、第2ダミーワードラインDWL2及びノーマルワードラインWL0, ..., WL31には、バス電圧V<sub>pass</sub>を印加する。このポストプログラム動作が完了すれば、第1電圧V<sub>r1'</sub>を利用して第1ダミーメモリセルDC1のしきい電圧を検証する(S520)。すなわち、第1ダミーワードラインDWL1には、第1電圧V<sub>r1'</sub>を印加し、第2ダミーワードラインDWL2及びノーマルワードラインWL0, ..., WL31には、第4電圧V<sub>read</sub>を印加する。第4電圧V<sub>read</sub>は、図3の第3電圧V<sub>read</sub>と同じ電圧レベルを有する。

30

**【0028】**

検証の結果、第1ダミーメモリセルDC1のしきい電圧が第1電圧V<sub>r1'</sub>より低い場合、第1ダミーメモリセルDC1に対して再びポストプログラムを行う(S510)。検証の結果、第1ダミーメモリセルDC1のしきい電圧が第1電圧V<sub>r1</sub>以上である場合、第2ダミーメモリセルDC2に対してポストプログラムを行う(S530)。

40

**【0029】**

第2ダミーメモリセルDC1に対してポストプログラムを行う場合(S630)、第2ダミーワードラインDWL2には、プログラム電圧V<sub>pgm</sub>を印加し、第1ダミーワードラインDWL1及びノーマルワードラインWL0, ..., WL31には、バス電圧V<sub>pass</sub>を印加する。このポストプログラム動作が完了すれば、第2電圧V<sub>r2'</sub>を利用して第2ダミーメモリセルDC2のしきい電圧を検証する(S540)。第2電圧V<sub>r2'</sub>は、

50

第2ダミーメモリセルDC2に対してポストプログラムを行って変更しようとするしきい電圧値であって、第1電圧V<sub>r1</sub>'と相異なる電圧レベルを有する。第2ダミーワードラインDWL2には、第2電圧V<sub>r2</sub>'を印加し、第1ダミーワードラインDWL12及びノーマルワードラインWL0, ..., WL31には、第4電圧V<sub>read</sub>を印加する。

#### 【0030】

前記検証結果、第2ダミーメモリセルDC2のしきい電圧が第2電圧V<sub>r2</sub>'より低い場合、第2ダミーメモリセルDC2に対して再びポストプログラムを行う(S530)。検証の結果、第2ダミーメモリセルDC2のしきい電圧が第2電圧V<sub>r2</sub>'以上である場合、それぞれのノーマルメモリセルC0, ..., C31に対してポストプログラムを行う(S550)。

10

#### 【0031】

ノーマルメモリセルC0, ..., C31に対してポストプログラム(S550)及び検証(S560)を行うステップは、図2の場合と同一であるので、以下では説明を省略する。図6の第3電圧V<sub>r3</sub>'は、図2の第2電圧V<sub>r2</sub>と同じ電圧レベルを有する。

但し、図5の実施形態では、第1ダミーメモリセルDC1、第2ダミーメモリセルDC2及びノーマルメモリセルの順序でポストプログラム及び検証を行っているが、順序が変わっても同じ効果が得られるということは、当業者に自明な事項である。

#### 【0032】

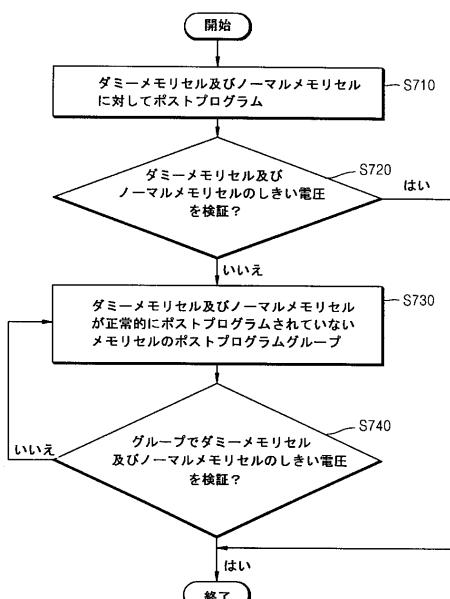

図7は、本発明のさらに他の実施形態による不揮発性メモリ装置の消去方法を示すフローチャートである。

20

図1、図3及び図7を参照すれば、図7の実施形態は、ノーマルメモリセルC0, ..., C31及びダミーメモリセルDC1, DC2に対して同時にポストプログラム動作を行う(S710)。すなわち、ダミーワードラインDWL1, DWL2及びノーマルワードラインWL0, ..., WL31にプログラム電圧V<sub>pgm</sub>を印加する。

#### 【0033】

ポストプログラム動作が完了した後、ダミーメモリセルDC1, DC2及びノーマルメモリセルC0, ..., C31に対してポストプログラムが正常に行われたか否かを検証する(S720)。すなわち、第1電圧V<sub>r1</sub>を利用してダミーメモリセルDC1, DC2のしきい電圧を検証し、第2電圧V<sub>r2</sub>を利用してノーマルメモリセルC0, ..., C31のしきい電圧を検証する。ダミーワードラインDWL1, DWL2に対して検証を行うために、ダミーワードラインDWL1, DWL2には、第1電圧V<sub>r1</sub>を印加し、ノーマルワードラインWL0, ..., WL31には、第3電圧V<sub>read</sub>を印加する。また、ノーマルワードラインWL0, ..., WL31に対して検証を行うために、ノーマルワードラインWL0, ..., WL31には、第2電圧V<sub>r2</sub>を印加し、ダミーワードラインDWL1, DWL2には、第3電圧V<sub>read</sub>を印加する。

30

#### 【0034】

検証の結果、それぞれのしきい電圧が対応する電圧レベルとならないメモリセルに対して再びポストプログラムを行い(S730)、ポストプログラムが正常に行われたか否かを検証する(S740)。すなわち、第1メモリセルグループのメモリセルに対しては、ポストプログラムを行い、第2メモリセルグループのメモリセルに対しては、ポストプログラムを行わない。第1メモリセルグループは、しきい電圧が第1電圧V<sub>r1</sub>より低いダミーメモリセル及びしきい電圧が第2電圧V<sub>r2</sub>より低いノーマルメモリセルのうち少なくとも一つを含む。第2メモリセルグループは、しきい電圧が第1電圧V<sub>r1</sub>以上であるダミーメモリセル及びしきい電圧が第2電圧V<sub>r2</sub>以上であるノーマルメモリセルを含む。

40

#### 【0035】

例えば、検証の結果、ダミーメモリセルDC1, DC2のしきい電圧が第1電圧V<sub>r1</sub>となったならば、第1メモリセルグループは、ノーマルメモリセルC0, ..., C31を含み、第2メモリセルグループは、ダミーメモリセルDC1, DC2を含む。したがって、第2メモリセルグループのダミーメモリセルDC1, DC2に対しては、再びポストプロ

50

グラムを行わず、第1メモリセルグループのノーマルメモリセルC0, …, C31に対してのみ、再びポストプログラムを行う。再びポストプログラムを行った第1メモリセルグループのノーマルメモリセルC0, …, C31に対して検証し、その結果、ノーマルメモリセルC0, …, C31のしきい電圧が第2電圧Vr2以上となつたならば、ポストプログラム動作を完了する。

#### 【0036】

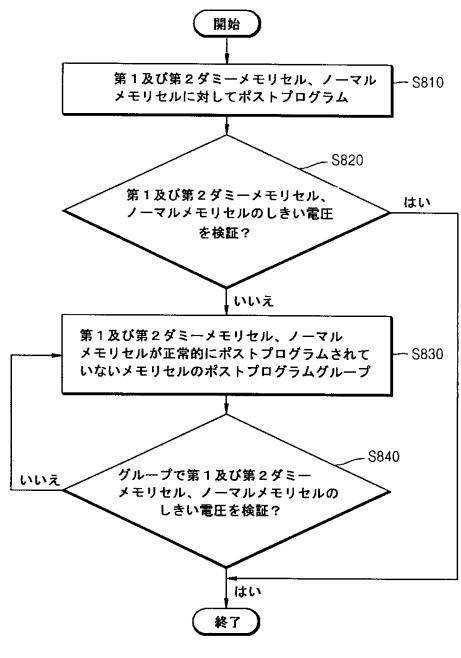

図8は、本発明のさらに他の実施形態による不揮発性メモリ装置の消去方法を示すフローチャートである。

図1、図6、図7及び図8を参照すれば、図8の実施形態は、ダミーメモリセルDC1, DC2のそれぞれが異なるしきい電圧を有するようにポストプログラムを行う。すなわち、図7のように、ノーマルメモリセルC0, …, C31、第1ダミーメモリセルDC1及び第2ダミーメモリセルDC2に対して同時にポストプログラム動作を行う(S810)。

10

#### 【0037】

ポストプログラム動作が完了した後、第1ダミーメモリセルDC1、第2ダミーメモリセルDC2及びノーマルメモリセルC0, …, C31に対してポストプログラムが正常的に行われたか否かを検証する(S820)。すなわち、第1電圧Vr1'を利用して第1ダミーメモリセルDC1のしきい電圧を検証し、第2電圧Vr2'を利用して第2ダミーメモリセルDC2のしきい電圧を検証し、第3電圧Vr3'を利用してノーマルメモリセルC0, …, C31のしきい電圧を検証する。第2電圧Vr2'は、第2ダミーメモリセルDC2に対してポストプログラムを行って変更しようとするしきい電圧値であつて、第1電圧Vr1'とは相異なる電圧レベルを有する。第3電圧Vr3'は、図3の第2電圧Vr2と同じ電圧レベルを有する。

20

#### 【0038】

第1ダミーメモリセルDC1に対して検証を行うために、第1ダミーワードラインDWL1には、第1電圧Vr1'を印加し、第2ダミーワードラインDWL2及びノーマルワードラインWL0, …, WL31には、第4電圧Vreadを印加する。第2ダミーメモリセルDC2に対して検証を行うために、第2ダミーワードラインDWL2には、第2電圧Vr2'を印加し、第1ダミーワードラインDWL1及びノーマルワードラインWL0, …, WL31には、第4電圧Vreadを印加する。また、ノーマルメモリセルC0, …, C31に対して検証を行うために、ノーマルワードラインWL0, …, WL31には、第3電圧Vr3'を印加し、第1ダミーワードライン及び第2ダミーワードラインDWL1, DWL2には、第4電圧Vreadを印加する。第4電圧Vreadは、図3の第3電圧Vreadと同じ電圧レベルを有する。

30

#### 【0039】

検証の結果、それぞれの対応する電圧より低いしきい電圧を有するメモリセルに対して、再びポストプログラムを行い(S830)、ポストプログラムが正常的に行われたか否かを検証する(S840)。すなわち、第1メモリセルグループのメモリセルに対してはポストプログラムを行い、第2メモリセルグループのメモリセル野に対しはポストプログラムを行わない。第1メモリセルグループは、しきい電圧が第1電圧Vr1'より低い第1ダミーメモリセルDC1、しきい電圧が第2電圧Vr2'より低い第2ダミーメモリセルDC2及びしきい電圧が第3電圧Vr3'より低いノーマルメモリセルを少なくとも一つ含む。第2メモリセルグループは、しきい電圧が第1電圧Vr1'以上となつた第1ダミーメモリセルDC1、しきい電圧が第2電圧Vr2'以上となつた第2ダミーメモリセルDC2及び前記しきい電圧が第3電圧Vr3'以上となつた前記ノーマルメモリセルを含む。

40

#### 【0040】

例えば、検証の結果、ノーマルメモリセルC0, …, C31のしきい電圧が第3電圧レベルVr3'となつたならば、第1メモリセルグループは、第1ダミーメモリセルDC1、第2ダミーメモリセルDC2を含む。第2メモリセルグループは、ノーマルメモリセル

50

C<sub>0</sub>, …, C<sub>31</sub>を含む。したがって、第1メモリセルグループのメモリセルDC<sub>1</sub>, DC<sub>2</sub>に対して再びポストプログラムを行う。

#### 【0041】

再びポストプログラムを行って検証した結果、第1ダミーメモリセルDC<sub>1</sub>のしきい電圧が第1電圧レベルV<sub>r1</sub>'以上となったならば、第1メモリセルグループは、第2ダミーメモリセルDC<sub>2</sub>を含み、第2メモリセルグループは、第1ダミーメモリセルDC<sub>1</sub>及びノーマルメモリセルC<sub>0</sub>, …, C<sub>31</sub>を含む。したがって、前記第1メモリセルグループのメモリセルDC<sub>2</sub>に対して再びポストプログラムを行う。

#### 【0042】

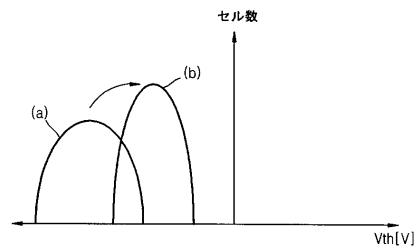

図9Aは、従来の技術によるメモリセルのしきい電圧V<sub>th</sub>の分布度を示すグラフである。

10

図1及び図9Aを参照すれば、メイン消去動作が完了した場合、ノーマルメモリセルC<sub>0</sub>, …, C<sub>31</sub>及びダミーメモリセルDC<sub>1</sub>, DC<sub>2</sub>のしきい電圧V<sub>th</sub>は、(a)のような分布度を有する。従来は、ノーマルメモリセルC<sub>0</sub>, …, C<sub>31</sub>及びダミーメモリセルDC<sub>1</sub>, DC<sub>2</sub>に対して別途のポストプログラムを行わなかったので、ポストプログラムを行った以後には、ノーマルメモリセルC<sub>0</sub>, …, C<sub>31</sub>及びダミーメモリセルDC<sub>1</sub>, DC<sub>2</sub>のしきい電圧V<sub>th</sub>は、(b)のような分布度を有する。

#### 【0043】

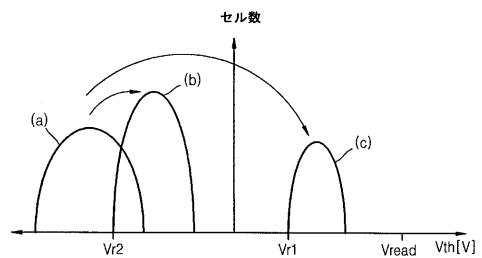

図9Bは、図2、図4及び図7の実施形態によるメモリセルのしきい電圧V<sub>th</sub>の分布度を示すグラフである。

20

図2、図4及び図7の実施形態による場合、図1及び図9Bを参照すれば、メイン消去動作が完了した後には、ノーマルメモリセルC<sub>0</sub>, …, C<sub>31</sub>及びダミーメモリセルDC<sub>1</sub>, DC<sub>2</sub>は、図9Aと同様に、(a)の分布度を有する。但し、前述の実施形態では、ノーマルメモリセルC<sub>0</sub>, …, C<sub>31</sub>及びダミーメモリセルDC<sub>1</sub>, DC<sub>2</sub>に対して別途にポストプログラムを行う。したがって、ポストプログラムを行った場合、ノーマルメモリセルC<sub>0</sub>, …, C<sub>31</sub>のしきい電圧V<sub>th</sub>は、第2電圧V<sub>r2</sub>を含む(b)の分布度に変更される。また、ダミーメモリセルDC<sub>1</sub>, DC<sub>2</sub>のしきい電圧V<sub>th</sub>は、第1電圧V<sub>r1</sub>を含む(c)の分布度に変更される。

#### 【0044】

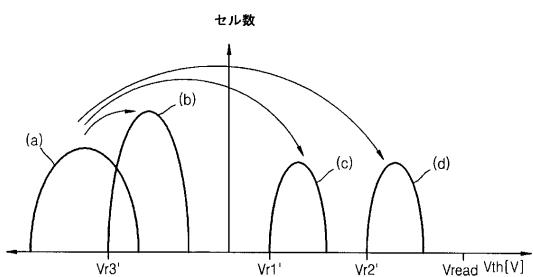

図9Cは、図5及び図8の実施形態によるメモリセルのしきい電圧V<sub>th</sub>の散布度を示すグラフである。

30

図5及び図8の実施形態による場合、図1及び図9Cを参照すれば、メイン消去動作が完了した後には、ノーマルメモリセルC<sub>0</sub>, …, C<sub>31</sub>及びダミーメモリセルDC<sub>1</sub>, DC<sub>2</sub>は、図9Aと同様に、(a)の分布度を有する。但し、前述の実施形態では、ノーマルメモリセルC<sub>0</sub>, …, C<sub>31</sub>、第1ダミーメモリセルDC<sub>1</sub>及び第2ダミーメモリセルDC<sub>2</sub>に対して別途にポストプログラムを行う。したがって、ポストプログラムを行った場合、ノーマルメモリセルC<sub>0</sub>, …, C<sub>31</sub>のしきい電圧V<sub>th</sub>は、第3電圧V<sub>r3</sub>'を含む(b)の分布度に変更される。また、第1ダミーメモリセルDC<sub>1</sub>のしきい電圧V<sub>th</sub>は、第1電圧V<sub>r1</sub>'を含む(c)の分布度に変更され、第2ダミーメモリセルDC<sub>2</sub>のしきい電圧V<sub>th</sub>は、第2電圧V<sub>r2</sub>'を含む(d)の分布度に変更される。

40

#### 【0045】

以上のように、図面及び明細書で最適の実施形態が開示された。ここで、特定の用語が使われたが、これは、単に本発明を説明するための目的で使われたものであり、意味限定や特許請求の範囲に記載された本発明の範囲を制限するために使われたものではない。したがって、当業者ならば、これから多様な変形及び均等な他の実施形態が可能であるということが分かるであろう。したがって、本発明の真の技術的保護範囲は、特許請求の範囲の技術的思想によって決定されねばならない。

#### 【産業上の利用可能性】

#### 【0046】

本発明は、メモリ関連の技術分野に適用可能である。

50

## 【図面の簡単な説明】

【0047】

【図1】不揮発性半導体メモリ装置の回路図である。

【図2】本発明の実施形態による不揮発性メモリ装置の消去方法を示すフローチャートである。

【図3】図2の実施形態によるポストプログラムを行う場合に電圧条件を示すテーブルである。

【図4】本発明の他の実施形態による不揮発性メモリ装置の消去方法を示すフローチャートである。

【図5】本発明のさらに他の実施形態による不揮発性メモリ装置の消去方法を示すフローチャートである。 10

【図6】図5の実施形態によるポストプログラムを行う場合に電圧条件を示すテーブルである。

【図7】本発明のさらに他の実施形態による不揮発性メモリ装置の消去方法を示すフローチャートである。 20

【図8】本発明のさらに他の実施形態による不揮発性メモリ装置の消去方法を示すフローチャートである。

【図9A】従来の技術によるメモリセルのしきい電圧の散布度である。

【図9B】図2、図4及び図7の実施形態によるメモリセルのしきい電圧の分布度である。 20

【図9C】図5及び図8の実施形態によるメモリセルのしきい電圧の分布度である。

【図1】

【図2】

【図3】

| 信号       | DWL<br>ポストPGM | WL[31:0]<br>ポストPGM | DWL<br>検証 | WL[31:0]<br>検証 |

|----------|---------------|--------------------|-----------|----------------|

| DWL1,2   | Vpgm          | Vpass              | Vr1       | Vread          |

| WL[31:0] | Vpass         | Vpgm               | Vread     | Vr2            |

【図4】

【図5】

【図6】

| 信号       | DWL1<br>ポストPGM | DWL2<br>ポストPGM | WL[31:0]<br>ホス-HGM | DWL1<br>検証 | DWL2<br>検証 | Vread | Vread | Vread | Vread | V3' |

|----------|----------------|----------------|--------------------|------------|------------|-------|-------|-------|-------|-----|

| DWL1     | Vgpm           | Vpass          | V1'                | Vread      | Vread      | V12'  | Vread | Vread | Vread | V3' |

| DWL2     | Vpass          | Vpass          | Vpgm               | Vread      | Vread      | Vpgm  | Vread | Vread | Vread |     |

| WL[31:0] |                |                |                    |            |            |       |       |       |       |     |

【図7】

【図8】

【図9 A】

【図9 B】

【図9 C】

---

フロントページの続き

(72)発明者 朴 起 台

大韓民国京畿道城南市盆唐区盆唐洞38番地 セッピヨルマウル三富アパート410棟304号

(72)発明者 李 永 宅

大韓民国ソウル特別市松坡区可樂本洞122-10番地 大林アパート5棟510号

審査官 滝谷 亮一

(56)参考文献 特開2008-140488(JP,A)

特開2008-146771(JP,A)

米国特許出願公開第2007/0239077(US,A1)

特開2008-084471(JP,A)

特開2006-186359(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/02

G11C 16/04