【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成17年12月22日(2005.12.22)

【公開番号】特開2004-72060(P2004-72060A)

【公開日】平成16年3月4日(2004.3.4)

【年通号数】公開・登録公報2004-009

【出願番号】特願2002-322905(P2002-322905)

【国際特許分類第7版】

H 01 L 21/8247

G 11 C 16/02

G 11 C 16/04

H 01 L 27/10

H 01 L 27/115

H 01 L 29/788

H 01 L 29/792

【F I】

H 01 L 27/10 4 3 4

H 01 L 27/10 4 8 1

H 01 L 29/78 3 7 1

G 11 C 17/00 6 4 1

G 11 C 17/00 6 2 1 Z

G 11 C 17/00 6 1 2 Z

G 11 C 17/00 6 1 1 E

【手続補正書】

【提出日】平成17年11月2日(2005.11.2)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】請求項10

【補正方法】変更

【補正の内容】

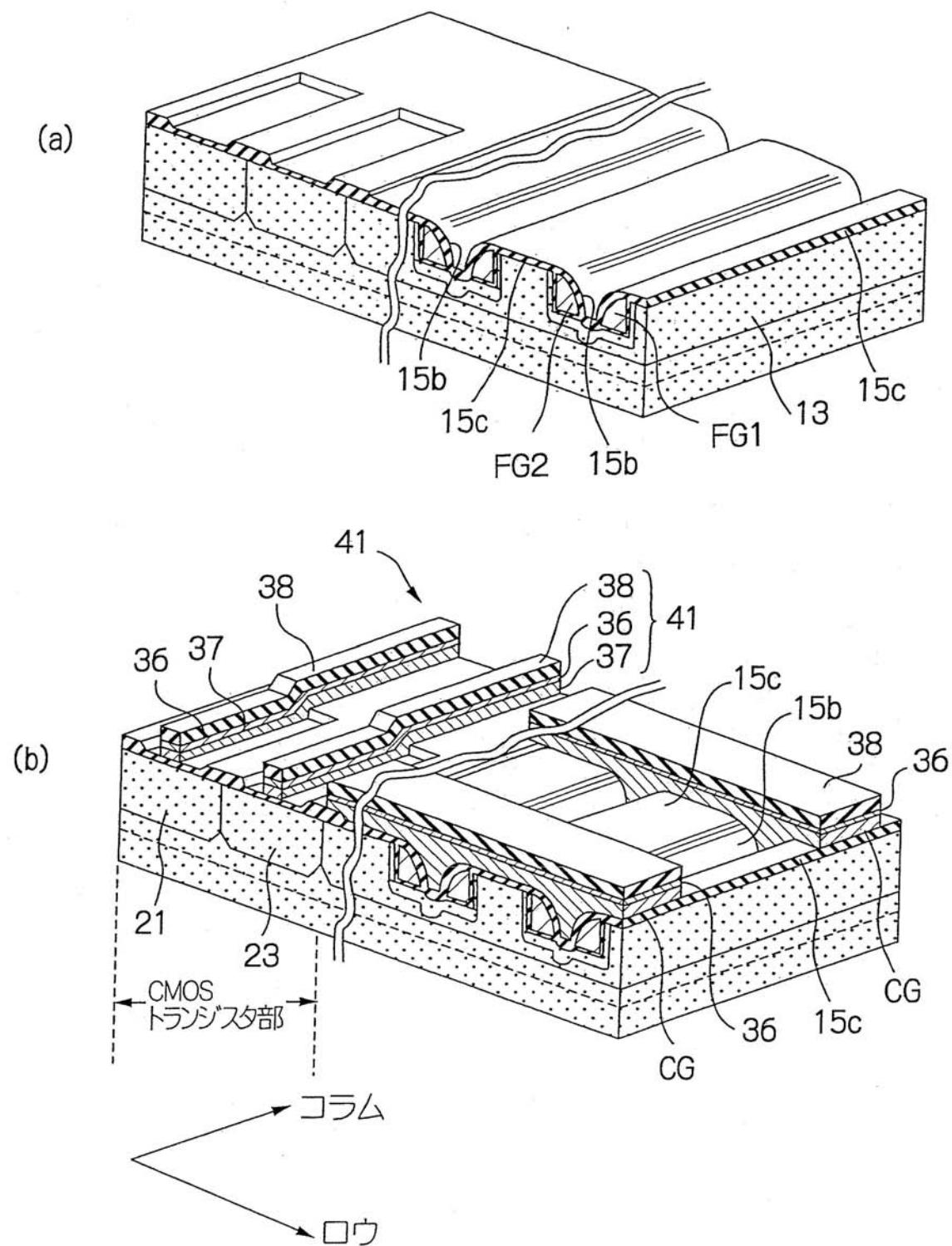

【請求項10】 請求項9に記載の半導体メモリにおいて、前記コラム方向に隣接するトランジスタの前記ソース・ドレイン領域が共通であり、

口ウ方向に隣接する前記トランジスタ同士が、前記コントロールゲートを共有し、かつ、前記トランジスタ間の前記ソース・ドレイン領域を共有することを特徴とする半導体メモリ。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0009

【補正方法】変更

【補正の内容】

【0009】

図28(a)～(d)は、このセルトランジスタ1で達成し得る4値状態を示す。“(1, 1)”状態(図28(a)参照)は、左右のいずれのビットにも電子が蓄積されない。そして、“(0, 0)”状態(図28(d)参照)は、左右の両ビットに電子が蓄積される。こうして、セルトランジスタ1では、2ビットのデータを書き込むことができる。ただし、この書き込み方法は、ホットエレクトロンをシリコン窒化膜5に注入するために、コントロールゲート7に高電位V<sub>G1</sub>を印加する必要がある点で好ましくない。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0067

【補正方法】変更

【補正の内容】

【0067】

電荷注入動作を行なう理由は次の通りである。データの書き込みが行われていない“1”論理状態にあるフローティングゲート(以下では「未書き込みフローティングゲート」と呼ぶ。)に対して、繰返し多数回の過消去を、電荷注入を行なうことなく行うと、未書き込みフローティングゲートは強制的に、電荷(たとえば電子)を抜き取る操作が繰り返し行われることとなる。その結果、過消去状態すなわち飽和状態で安定していた未書き込みフローティングゲートが、飽和状態を越えた電子欠乏状態(以下では「過剰消去状態」と呼ぶ)になり、しきい値電圧等が変化する可能性がある。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0096

【補正方法】変更

【補正の内容】

【0096】

上記を約言すれば、書き込み電圧 $V_G$ を低減するには、i)側面13bにn型領域を設けるか、ii)トンネル絶縁膜の静電容量を大きくして、フローティングゲートをドレイン電圧によって引き上げるか、iii)ゲート絶縁膜15cを厚膜にするか、またはiv)頂面13cに高抵抗領域13eを設ければ良い。これらi)~iv)を任意に組み合わせることで、上述の利点を得ることもできる。i)~iv)のいずれの場合であっても、書き込み電圧 $V_G$ は約2.2V程度で良く、従来例(約12~13V)よりも格段に低くすることができる。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0143

【補正方法】変更

【補正の内容】

【0143】

- ・1回目・・・イオン種： $\text{BF}_2$

加速エネルギー：15(KeV)

ドーズ量： $5.0 \times 10^{11} (\text{cm}^{-2})$

- ・2回目・・・イオン種： $\text{BF}_2$

加速エネルギー：45(KeV)

ドーズ量： $5.0 \times 10^{11} (\text{cm}^{-2})$

- ・3回目・・・イオン種：B(ボロン)

加速エネルギー：20(KeV)

ドーズ量： $6.0 \times 10^{12} (\text{cm}^{-2})$

- ・4回目・・・イオン種：B(ボロン)

加速エネルギー：40(KeV)

ドーズ量： $5.0 \times 10^{12} (\text{cm}^{-2})$

上記4回のイオン注入により、pウエル13は、図31のようなボロン濃度分布を示す。図31は、pウエル13の表面からの深さと、その深さでのボロン濃度との関係を示すグラフである。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0151

【補正方法】変更

【補正の内容】

**【0151】**

続いて、図17(a)に示すように、露出面全体にシリコン酸化膜29(膜厚は約20nm)を形成する。シリコン酸化膜29は、CVD法により成膜される。次に、図17(b)に示すように、シリコン酸化膜29を厚み方向に異方的にエッチングする。このエッチングは、RIE(Reactive Ion Etching)により行われる。これにより、シリコン酸化膜29は、凸部13aの側面13bに形成されたものを残して、除去される。

**【手続補正7】**

【補正対象書類名】明細書

【補正対象項目名】0192

【補正方法】変更

【補正の内容】

**【0192】**

ソース・ドレインに印加されたこれらの電圧値により、図8(a)で説明したように、セルトランジスタTC<sub>i,m,0</sub>に第1のドレイン電流I<sub>d1</sub>が流れる。この第1のドレイン電流I<sub>d1</sub>は、センスアンプ128からビット線ゲート122、仮想接地線VT<sub>k+1</sub>、ノードD、ノードC、偶数バンク選択トランジスタSTE<sub>i,m+1</sub>、ビット線BL<sub>m+1</sub>、セルトランジスタTC<sub>i,m,0</sub>、ビット線BL<sub>m</sub>、偶数バンク選択トランジスタSTE<sub>i,m</sub>、ノードB、ノードA、仮想接地線VT<sub>k</sub>、ビット線ゲート122の順に流れる。

**【手続補正8】**

【補正対象書類名】明細書

【補正対象項目名】0195

【補正方法】変更

【補正の内容】

**【0195】**

この回路構成によれば、第1のドレイン電流I<sub>d1</sub>は、拡散層からなる高抵抗のビット線BL<sub>m</sub>、BL<sub>m+1</sub>内を常に流れるという訳ではなく、目的のバンクBNK<sub>i,m</sub>に到達するまでは低抵抗の仮想接地線VT<sub>k+1</sub>内を流れ、目的のバンクBNK<sub>i,m</sub>に到達してからビット線BL<sub>m+1</sub>を流れようになる。そして、セルトランジスタTC<sub>i,m,0</sub>を流れた後、第1のドレイン電流I<sub>d1</sub>はビット線BL<sub>m</sub>を経由して仮想接地線VT<sub>k</sub>を流れる。

**【手続補正9】**

【補正対象書類名】図面

【補正対象項目名】図22

【補正方法】変更

【補正の内容】

【図22】

【手続補正10】

【補正対象書類名】図面

【補正対象項目名】図40

【補正方法】変更

【補正の内容】

【図40】