(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년02월26일

(11) 등록번호 10-1367545

(24) 등록일자 2014년02월19일

(51) 국제특허분류(Int. Cl.)

H01L 23/48 (2006.01) H01L 21/58 (2006.01)

H01L 21/60 (2006.01) H01L 33/02 (2010.01)

(21) 출원번호 10-2008-7030710

(22) 출원일자(국제) 2007년05월16일

심사청구일자 2012년05월03일

(85) 번역문제출일자 2008년12월17일

(65) 공개번호 10-2009-0027639

(43) 공개일자 2009년03월17일

(86) 국제출원번호 PCT/DE2007/000897

(87) 국제공개번호 WO 2007/134581

국제공개일자 2007년11월29일

(30) 우선권주장

10 2006 023 683.1 2006년05월19일 독일(DE)

10 2006 028 692.8 2006년06월22일 독일(DE)

(56) 선행기술조사문현

US05804882 A

JP60262430 A

전체 청구항 수 : 총 36 항

심사관 : 정구원

(54) 발명의 명칭 결연성 결합 매체를 이용하는 전기 전도적 결합

### (57) 요 약

제1 표면(6)을 가진 제1 소자(5), 제2 표면(9)을 가진 제2 소자(8) 및 상기 제1 소자(5)의 제1 표면(6)과 상기 제2 소자(8)의 제2 표면(9) 사이의 결합층(7)을 포함하고, 이 때, 상기 결합층(7)은 전기 결연성 결착제를 포함하고, 상기 제1 소자(5)의 제1 표면(6)과 제2 소자(8)의 제2 표면(9) 사이에는 전기 전도 접촉이 존재하는 것을 특징으로 하는 장치.

대 표 도 - 도2

## 특허청구의 범위

### 청구항 1

제1 표면(6)을 가진 제1 소자(5)와 제2 표면(9)을 가진 제2 소자(8)를 포함하는 장치에 있어서,

상기 제1 표면과 상기 제2 표면중 적어도 하나의 표면은 지형학적(topographic) 표면 구조들 - 지형학적 표면구

조는 미시적(microscopic) 또는 거시적(macrosopic) 높이 프로파일에 의해 정의됨 - 을 포함하고;

상기 제1 소자(5)의 제1 표면(6)은 상기 제2 소자(8)의 제2 표면(9)과 전기 절연성 결합층(7)을 통해 결합되며;

상기 지형학적 표면 구조들에 의해 상기 제1 표면(6)과 상기 제2 표면(9) 사이의 전기 전도 접촉이 이루어지는

것을 특징으로 하는 장치.

### 청구항 2

청구항 1에 있어서,

상기 제1 및 제2 표면은 상기 지형학적 표면 구조들을 포함하는 것을 특징으로 하는 장치.

### 청구항 3

청구항 1 또는 청구항 2에 있어서,

상기 지형학적 표면 구조들은 상기 제1 표면 또는 상기 제2 표면, 또는 상기 제1 및 제2 표면의 거칠기에 의해

결정되는 것을 특징으로 하는 장치.

### 청구항 4

청구항 1 또는 청구항 2에 있어서,

상기 제1 소자(5) 또는 상기 제2 소자(8), 또는 상기 제1 소자(5) 및 상기 제2 소자(8)는 기판, 웨이퍼, 유리

지지부, 열 싱크, 애피택시총 시퀀스 및 광전자 반도체칩으로 이루어진 그룹에서 선택되는 것을 특징으로 하는

장치.

### 청구항 5

청구항 1 또는 청구항 2에 있어서,

상기 제1 소자(5)의 제1 표면(6) 또는 상기 제2 소자(8)의 제2 표면(9), 또는 상기 제1 소자(5)의 제1 표면(6)

및 상기 제2 소자(8)의 제2 표면(9)은 함몰부들(40)을 포함하는 것을 특징으로 하는 장치.

### 청구항 6

청구항 5에 있어서,

상기 제1 표면(6) 및 상기 제2 표면(9)은 접합 영역(41)을 포함하고, 상기 접합 영역에 상기 결합층(7)이 배치

되며, 상기 함몰부들(40)은 상기 제1 표면(6) 또는 상기 제2 표면(9), 또는 상기 제1 표면(6) 및 상기 제2 표면

(9) 내에서 상기 접합 영역(41)의 둘레에 배치되는 것을 특징으로 하는 장치.

### 청구항 7

청구항 5에 있어서,

상기 함몰부들(40)은 결합층의 접착제를 위한 캐치 저장부들(catch reservoirs)로서 역할하는 것을 특징으로 하

는 장치.

### 청구항 8

청구항 5에 있어서,

상기 함몰부들(40)은 규칙적으로 이격 배치되는 것을 특징으로 하는 장치.

### 청구항 9

청구항 5에 있어서,

상기 핵몰부들(40)은 불규칙적으로 이격 배치되는 것을 특징으로 하는 장치.

### 청구항 10

청구항 1 또는 청구항 2에 있어서,

상기 결합층(7)의 평균 두께(28)는 상기 제1 표면(6)의 거칠기 또는 상기 제2 표면(9)의 거칠기, 또는 상기 제1 표면(6)의 거칠기 및 상기 제2 표면(9)의 거칠기의 자릿수(order of magnitude)를 갖는 것을 특징으로 하는 장치.

### 청구항 11

청구항 3에 있어서,

상기 제1 표면(6)의 거칠기 또는 상기 제2 표면(9)의 거칠기, 또는 상기 제1 표면(6)의 거칠기 및 상기 제2 표면(9)의 거칠기는 적어도 수 나노미터인 것을 특징으로 하는 장치.

### 청구항 12

청구항 1 또는 청구항 2에 있어서,

상기 제1 표면(6) 및 상기 제2 표면(9)은 적어도 부분적으로 전기 전도성으로 형성되는 것을 특징으로 하는 장치.

### 청구항 13

청구항 9에 있어서,

상기 제1 표면(6) 또는 상기 제2 표면(9), 또는 상기 제1 표면(6) 및 상기 제2 표면(9)은 적어도 부분적으로 금속을 포함하여 형성되는 것을 특징으로 하는 장치.

### 청구항 14

청구항 1 또는 청구항 2에 있어서,

상기 결합층은 전기 절연성 접착제를 포함하는 것을 특징으로 하는 장치.

### 청구항 15

청구항 14에 있어서,

상기 접착제는 내용제성, 진공 적합성, 온도 안정성 및 UV-경화성 중 적어도 하나 이상의 특성을 가진 것을 특징으로 하는 장치.

### 청구항 16

청구항 14에 있어서,

상기 접착제는 비스벤졸사이클로부텐(bisbenzocyclobutene, BCB)을 포함하는 것을 특징으로 하는 장치.

### 청구항 17

제1 표면(6)을 가진 제1 소자(5)와 제2 표면(9)을 가진 제2 소자(8) 사이의 전기 전도 결합을 형성하기 위한 방법으로서, 상기 제1 표면과 상기 제2 표면 중 적어도 하나의 표면은 지형학적 표면 구조들 - 지형학적 표면구조는 미시적 또는 거시적 높이 프로파일에 의해 정의됨 - 을 포함하는 것인 방법에 있어서,

상기 제1 표면 또는 상기 제2 표면, 또는 상기 제1 및 제2 표면상에 전기 절연성 결합층(7)을 적층하는 단계;

상기 제1 표면(6) 및 상기 제2 표면(9)을 상호 간에 배치시키는 단계; 및

상기 지형학적 표면 구조들을 통해 상기 제1 및 제2 표면 사이에 전기 전도 접촉이 이루어질 때까지, 상기 제1 소자(5) 또는 상기 제2 소자(8), 또는 상기 제1 소자(5) 및 상기 제2 소자(8)에 힘(10)을 인가하는 단계를 포함하는 방법.

### 청구항 18

청구항 17에 있어서,

상기 제1 표면(6) 및 상기 제2 표면(9)은 상기 지형학적 표면 구조들을 포함하는 것을 특징으로 하는 방법.

### 청구항 19

청구항 17 또는 청구항 18에 있어서,

상기 지형학적 표면 구조들은 상기 결합층이 적층되기 전에 생성되는 것을 특징으로 하는 방법.

### 청구항 20

청구항 19에 있어서,

상기 지형학적 표면 구조들은 식각, 그라인딩(grinding), 포토리소그라피 패터닝 및 샌드 블라스트(sand blast) 중 적어도 하나에 의해 생성되는 것을 특징으로 하는 방법.

### 청구항 21

청구항 17 또는 청구항 18에 있어서,

제1 소자(5) 또는 제2 소자(8), 또는 제1 소자(5) 및 제2 소자(8)는, 기판, 웨이퍼, 유리 지지부, 열 싱크, 애피택시층 시퀀스 및 광전자 반도체칩으로 이루어진 그룹에서 선택되어 사용되는 것을 특징으로 하는 방법.

### 청구항 22

청구항 17 또는 청구항 18에 있어서,

상기 전기 절연성 결합층의 적층 전에, 상기 제1 소자(5)의 제1 표면(6) 또는 상기 제2 소자(8)의 제2 표면(9), 또는 상기 제1 소자(5)의 제1 표면(6) 및 상기 제2 소자(8)의 제2 표면(9)에 함몰부들(40)이 제공되는 것을 특징으로 하는 방법.

### 청구항 23

청구항 22에 있어서,

상기 제1 표면(6) 및 상기 제2 표면(9)은 접합 영역(41)을 포함하고, 상기 접합 영역에 상기 결합층(7)이 배치되며, 이 때 상기 함몰부들(40)은 상기 제1 표면(6) 또는 상기 제2 표면(9), 또는 상기 제1 표면(6) 및 상기 제2 표면(9)에서 상기 접합 영역(41)의 둘레에 배치되는 것을 특징으로 하는 방법.

### 청구항 24

청구항 22에 있어서,

상기 함몰부들(40)은 결합층의 접착제를 위한 캐치 저장부로서 역할하는 것을 특징으로 하는 방법.

### 청구항 25

청구항 22에 있어서,

상기 함몰부들(40)은 규칙적으로 이격 배치되는 것을 특징으로 하는 방법.

### 청구항 26

청구항 22에 있어서,

상기 함몰부들(40)은 불규칙적으로 이격 배치되는 것을 특징으로 하는 방법.

### 청구항 27

청구항 22에 있어서,

상기 합물부들(40)은 식각, 그라인딩, 주조, 포토리소그라피 패터닝 및 샌드 블라스트 중 하나 이상에 의해 생성되는 것을 특징으로 하는 방법.

### 청구항 28

청구항 17에 있어서,

상기 결합층(7)은 패터닝되어 적층되는 것을 특징으로 하는 방법.

### 청구항 29

청구항 28에 있어서,

상기 패터닝 적층은 인쇄법에 의해 이루어지는 것을 특징으로 하는 방법.

### 청구항 30

청구항 17에 있어서,

상기 결합층(7)은 패터닝되지 않은 채로 적층되는 것을 특징으로 하는 방법.

### 청구항 31

청구항 30에 있어서,

상기 패터닝되지 않은 적층은 스픈 코팅(spin coating) 또는 기상 증착에 의해 이루어지는 것을 특징으로 하는 방법.

### 청구항 32

청구항 17에 있어서,

상기 결합층(7)의 적층 후의 결합층(7)의 두께(28)는 100 nm 내지 10  $\mu$ m의 두께를 포함하는 것을 특징으로 하는 방법.

### 청구항 33

청구항 32에 있어서,

상기 힘 인가 이후, 상기 결합층(7)의 두께(28)는 힘(10)의 작용으로 줄어들어, 상기 결합층(7)의 두께(28)가 상기 제1 표면(6)의 거칠기 또는 상기 제2 표면(9)의 거칠기, 또는 상기 제1 표면(6)의 거칠기 및 상기 제2 표면(9)의 거칠기의 자릿수를 갖는 것을 특징으로 하는 방법.

### 청구항 34

청구항 17 또는 청구항 18에 있어서,

접착제를 포함하는 전기 절연성 결합층이 사용되는 것을 특징으로 하는 방법.

### 청구항 35

청구항 34에 있어서,

내용제성, 진공 적합성, 온도 안정성 및 UV-경화성 중 적어도 하나의 특성을 가진 접착제가 사용되는 것을 특징으로 하는 방법.

### 청구항 36

청구항 34에 있어서,

비스벤졸사이클로부텐(BCB)을 포함하는 접착제가 사용되는 것을 특징으로 하는 방법.

## 명세서

### 기술 분야

[0001]

본 발명은 제1 표면을 가진 제1 소자, 제2 표면을 가진 제2 소자, 그리고 상기 제1 소자의 제1 표면과 상기 제2 소자의 제2 표면 사이의 결합층을 포함하는 장치 및 상기 장치의 제조 방법에 관한 것이다.

### 배경 기술

[0002]

두 개의 소자들을 기계적, 전기적으로 및/또는 열에 의해 상호 간 결합시키기 위해, 예컨대, 가령 땜납이나 접착제로 구성된 결합층을 이용하는 방법들이 적용될 수 있다. 예컨대 EP 0905797 A2의 인쇄본에 기재된 바와 같이, 일반적으로, 전기 전도적 결합이 필요한 경우, 전기 전도성 접착제 또는 금속 땜납이 사용되고, 그 반면 전기 절연 결합을 위해서는 전기 절연성 접착제가 사용된다. 그러나, 땜납의 사용은 비교적 가공 온도가 높아서 항상 가능한 것은 아니다. 또한, 일반적으로, 전기 전도성 접착제의 사용은 충전물(filler)때문에 전기 절연성 접착제에 비해 비용이 듈다.

### 발명의 상세한 설명

[0003]

따라서, 본 발명의 과제는, 두 개의 소자들 사이에 전기 절연성 결합층을 포함하되, 이 때 상기 두 개의 소자들 사이에 전기 전도 결합이 이루어지는 장치를 제공하는 것이다. 본 발명의 다른 과제는, 상기와 같은 결합을 형성하기 위한 방법이기도 하다.

[0004]

상기 과제는 특히 청구 범위 1항의 특징들을 포함하는 장치에 의해 해결된다. 상기 장치의 바람직한 실시예들 및 방법은 다른 청구 범위들에 제공된다.

[0005]

본 발명의 일 실시예에 따른 장치는, 제1 표면을 가진 제1 소자 및 제2 표면을 가진 제2 소자를 포함하고, 이 때

- 상기 제1 및 제2 표면들 중 적어도 하나의 표면은 지형학적(topographic)인 표면 구조들을 포함하고,

[0006]

- 상기 제1 소자(5)의 제1 표면(6)은 전기 절연성 결합층(7)에 의해 상기 제2 소자(8)의 제2 표면(9)과 결합하며;

[0007]

- 상기 제1 소자(5)의 제1 표면(6)과 상기 제2 소자(8)의 제2 표면(9) 사이에는 지형학적 표면 구조들에 의해 전기 전도 접촉이 존재한다.

[0008]

이 부분에서 지적해둘 것은, "소자"라는 개념이 예컨대 발광 다이오드들(LEDs) 또는 레이저 다이오드들과 같은 완성된 소자들만 의미하는 것이 아니라, 기판들 또는 에피택시층 시퀀스들도 의미하여, 상기 제1 소자 및 제2 소자가 결합층에 의해 결합하여 그 위에 배치된 제3 소자를 형성하거나 그러한 것의 부분이 되기도 한다는 것이다.

[0009]

이 때, 지형학적 표면 구조를 포함하는 표면은 미시적(microscopic) 및/또는 거시적(macrosopic) 높이 프로파일을 포함할 수 있다. 이 때, 높이 프로파일은, 그 표면에 대해 평행한 하나 또는 두 개의 방향으로, 규칙적 또는 불규칙적으로, 전체의 표면 위로 연장되거나 상기 표면의 단일 또는 복수 개의 부분 영역들 위로 연장될 수 있다.

[0010]

또한, 상기 제1 표면 뿐만아니라 제2 표면도 지형학적 표면 구조들을 포함할 수 있다. 이 때, 지형학적 표면 구조들은 적어도 일부분 영역에서 동일하거나, 유사하거나 서로 다를 수 있다.

[0011]

장치의 일 실시예에서, 지형학적 표면 구조들은 제1 및/또는 제2 표면의 거칠기에 의해 결정된다. 특히, 이러한 점은, 예컨대 제1 및 제2 표면의 거칠기가 서로 달라서, 예컨대, 제1 표면이 포함하는 지형학적 표면 구조들이 제2 표면이 포함하는 지형학적 표면 구조들과 다르다는 것을 의미할 수 있다. 바람직하게는, 제1 표면의 지형학적 표면 구조들과 제2 표면의 지형학적 표면 구조들은 동일하거나 유사할 수 있다. 이는 특히, 제1 및 제2 표면의 거칠기 및 그 깊이는 동일하거나, 적어도 유사하다는 것을 의미할 수 있다.

[0012]

장치의 일 실시예에서, 바람직하게는, 전기 절연성 결합층에 의해, 소자들의 두 표면들 사이의 결합층이 전기 전도성 결합층보다 실질적으로 더 얇게 형성될 수 있다. 특히, 이러한 점은, 전기 절연성 결합층이 전기 절연성

접착제를 포함하는 경우에, 가능할 수 있다. 또한, 이는, 전기 절연성 결합층이 전기 절연성 접착제 또는 전기 절연성 접착제들의 혼합물 또는 전기 절연성 접착제와 다른 전기 절연성 첨가물과의 혼합물로 구성된다는 것을 의미할 수도 있다. 전기 전도성 접착제를 사용하는 것에 비해, 전기 절연성 접착제 또는 전기 절연성 접착제들의 혼합물 또는 전기 절연성 접착제와 다른 전기 절연성 첨가물과의 혼합물은, 예컨대 전기 절연성 접착제가 전기 전도성 충전물들을 포함하지 않는다는 점에서, 유리할 수 있다. 전기 전도성 접착제들을 사용하는 경우, 전기 전도성 접착제들의 충전물들에 의해, 약간의  $10 \mu\text{m}$  범위의 접착 두께들이 필요하다. 그에 반해, 예컨대 전기 절연성 접착제를 이용하여 가능한 매우 얇은 결합층의 경우, 바람직하게는, 상기 결합층의 열 저항이 그보다 큰 두께를 가진 결합층에 비해 작아질 수 있다. 따라서, 평편한 전면 연결 및 열 부하 시, 예컨대 전기 절연성 접착제들을 포함하는 전기 절연성 결합층들은  $100 \text{ nm}$ 의 두께들을 가지고, 열 전달 저항이  $1\text{K/W}$  보다 작을 수 있다. 따라서, 제1 및 제2 소자 사이의 양호한 열적 결합이 보장될 수 있다. 특히, 전기 절연성 접착제는  $0.2$  내지  $0.4 \text{ W/mK}$ 의 범위의 열 전도성, 특히  $24^\circ\text{C}$  일 때  $0.293 \text{ W/mK}$ ,  $45^\circ\text{C}$  일 때  $0.310 \text{ W/mK}$  및  $66^\circ\text{C}$  일 때  $0.324 \text{ W/mK}$ 의 열 전도성을 가질 수 있다.

[0014]

장치의 다른 실시예에서, 전기 절연성 결합층은 전기 절연성 접착제를 포함하고, 이는, 특히, 상기 결합층이 전기 전도성 충전물들을 전혀 포함하지 않는다는 것을 의미할 수 있다. 예컨대 충전물을 포함한 전기 전도성 접착제들을 이용하여 반도체 칩을 전기적으로 접촉시키는 것에 비해, 전기 전도성 충전물들을 포함하지 않는 전기 절연성 결합층을 사용하면, 상기 충전물들 또는 상기 충전물들의 성분들의 가능한 이동에 대한 대비 수단을 마련할 필요가 없게 될 수 있다. 이는, 은을 포함하는 충전물들의 사용 시 상기 은이 반도체칩의 기능 층들로 이동함으로써 반도체칩의 기능성이 저하될 수 있는 경우에, 장점으로 작용할 수 있다. 또한, 예컨대 금이 충전된 전기 전도성 접착제는 공정 비용을 증가시킬 수 있다는 점에서, 전기 전도성 충전물들을 포함하지 않는 전기 절연성 결합층을 사용하는 것이 유리할 수 있다. 또한, 일반적인 전기 전도성 접착제들은 예컨대 박막-LED-제조 시 사용되는 것과 같은 공정 화학 약품과 조화되지 않는 경우가 많다.

[0015]

땜납들을 사용하는 것에 비해, 예컨대 전기 절연성 접착제를 포함하는 전기 절연성 결합층들을 사용하면, 납땜 공정에 비해 현저히 더 낮은 온도에서 전기 절연성 결합층들이 가공될 수 있다는 장점을 얻을 수 있다. 약간 결합을 형성하기 위해, 땃납 결합은  $200^\circ\text{C}$ 보다 높은 공정 온도를 필요로 하는 경우가 많은데, 상기 온도는, 결합되어야 할 소자들의 사양(specification)과 반드시 일치할 수 있는 것은 아니다. 또한, 예컨대 전기 절연성 접착제를 포함하는 전기 절연성 결합층은, 납땜 결합 시 필요한 것과 같이, 분리 및 예컨대 확산 방지부들에 의한 기능층들의 보호와 관련하여 추가 비용이 필요없게 될 수 있다.

[0016]

제1 소자나 제2 소자 또는 두 개의 소자들은 예컨대 기판, 웨이퍼, 유리 지지부, 열 성크, 에피택시층 시퀀스, 발광 다이오드 칩 또는 레이저 다이오드 칩과 같은 반도체 칩, 또는 반도체계 발광 다이오드 또는 유기 발광 다이오드(OLED)와 같은 광전자 소자일 수 있다. 결합층의 래터럴(lateral) 범위는 웨이퍼의 크기부터 칩 접촉부들의 크기에 이를 수 있고, 그보다 더 작을 수 있다.

[0017]

특히, 제1 소자로서, 구동 중에 전자기 광을 생성하는 활성 영역을 포함한 에피택시층 시퀀스가, 제2 소자로서 유리 기판 또는 웨이퍼와 같은 지지부가 사용될 수 있다. 이러한 두 소자들의 상호 간 결합은 예컨대 박막-반도체칩의 제조 시 적합하다.

[0018]

박막-반도체칩은 특히 다음에 특징화된 특성들 중 적어도 하나의 특성에 의해 특징지워지는데:

[0019]

- 지지부를 향하는, 광 생성 에피택시층 시퀀스의 제1 주요면에 반사성 층이 적층 또는 형성되고, 상기 반사성 층은 상기 에피택시층 시퀀스에서 생성되는 전자기 광의 적어도 일 부분을 상기 에피택시층 시퀀스에 다시 반사시키고;

[0020]

- 에피택시층 시퀀스는  $20 \mu\text{m}$  또는 그보다 작은, 특히  $10 \mu\text{m}$ 의 범위의 두께를 가지며;

[0021]

- 에피택시층 시퀀스는 혼합 구조를 포함하는 적어도 하나의 면을 가진 적어도 하나의 반도체층을 포함하고, 이 상적인 경우, 상기 혼합 구조는 에피택시층 시퀀스에서 광의 거의 에르고딕적인(ergodic) 분포를 유도하는데, 즉, 가능한한 에르고딕적 확률적(stochastic)인 분산 거동을 포함한다.

[0022]

박막-발광 다이오드 칩의 기본 원리는, 예컨대 1993년 10월 18일 응용 물리학지 63(16), 2174-2176 쪽에 실린 아이 슈닛처 외(I. Schnitzer et al.)의 글에 기재되어 있으며, 이의 개시 내용은 여기서 참조로 포함된다.

[0023]

박막-반도체 칩에서, 일반적으로, 광 생성 에피택시층 시퀀스의 성장 기판은 제거되거나 얇아지고, 상기 에피택시층 시퀀스는 다른 지지부에 이송될 수 있다. 지지부와 에피택시층 시퀀스의 결합이 전기 전도적으로 되어야 하므로, 상기에 제안된 결합은 특히, 박막-반도체칩을 지지부위에서 접촉시킬 수 있기 위해, 박막-반도체칩에

적합할 수 있다. 또한, 전기 절연성 결합층은, 구동 시 에피택시층 시퀀스에서 발생할 수 있는 열을 효과적으로 유도할 수 있도록, 낮은 열 저항을 포함하기에 충분히 얇을 수 있다는 장점이 있다. 특히, 지지부와 에피택시층 시퀀스 사이의 결합이 전기가 통하지 않는 경우, 지지부와 반대 방향에 있는 에피택시층 시퀀스의 측이 접촉될 필요가 있을 수 있는데, 이러한 점은 에피택시면을 초과 사용하게 되어 그와 관련한 경제성이 낮아질 수도 있다.

[0024] 또한, 제1 소자는 가령 에피택시층 시퀀스와 같은 반도체층 시퀀스를 포함할 수 있고, 상기 층 시퀀스는 일 측에 적어도 두 개의 전기 접촉면들을 포함할 수 있다. 제2 소자는 예컨대 기판 또는 도체 프레임과 같은 지지부 일 수 있고, 상기 지지부도 적어도 두 개의 전기 접촉면들을 포함할 수 있다. 제1 내지 제2 소자의 각각의 적어도 두 개의 전기 접촉면들은 동일하거나, 서로 다른 전기적 극성을 가질 수 있다. 예컨대 제1 소자는, 상기에 기재된 박막-반도체칩을 위한 구조화 에피택시층 시퀀스나, 소위 플립-칩-실장(flip-chip-mintage)을 위한 반도체칩을 의미할 수 있는데, 상기 소자는 서로 다른 전기적 극성을 가진 두 개의 전기 접촉면들을 이용하여 일 측에서 제2 소자와 연결될 수 있다.

[0025] 또한, 여기에 제안된 결합에 따르면 발광 다이오드 칩들 또는 레이저 다이오드 칩들과 같은 광전자 반도체칩들이 열 싱크 또는 소자 하우징에 고정될 수도 있다.

[0026] 바람직한 실시예에서, 제1 표면 또는 제2 표면은 함몰부들을 포함한다. 이 때, 상기 함몰부들은 제1 소자의 제1 표면에만 또는 제2 소자의 제2 표면에만 구비되거나, 두 개의 결합되어야 할 표면들에 구비될 수 있다.

[0027] 다른 실시예에서, 제1 소자의 제1 표면 및/또는 제2 소자의 제2 표면은 접합 영역을 포함하고, 상기 접합 영역 내부에 전기 전도성 결합층을 형성할 수 있는 전기 절연성 접착제가 배치될 수 있다. 이 때 바람직하게는, 제1 및/또는 제2 표면의 함몰부들은 각 접합 영역을 중심으로 배치된다. 바람직하게는, 상기 함몰부들은 접착제를 위한 캐치 저장부(catch reservoir)로서 역할할 수 있다. 이를 통해, 접합 영역으로부터 밀려진 과잉의 접착제가 상기 캐치 저장부로 유출되어 그 곳에 잔류할 수 있다. 또한, 이 때, 함몰부들은 규칙적 또는 불규칙적으로 이격 배치될 수 있다.

[0028] 바람직한 실시예에서, 함몰부들 또는 캐치 저장부들은 균일하게 배치된다. 균일하거나 규칙적인 배치는, 예컨대, 상기 함몰부들이 에피택시층 시퀀스들의 제조 공정에서 일반적인 포토 마스크들을 이용하여 제조될 수 있고, 상기 균일하거나 규칙적인 배치에 의해 에피택시 면의 축소가 방지될 수 있다는 점에서, 바람직할 수 있다.

[0029] 바람직하게는, 상기 표면들 중 적어도 하나의 표면은 구조화 표면을 가질 수 있다. 이 때, 구조화는 예컨대 미소 프리즘(micro prism) 구조화 또는 미소 반사체(micro reflector) 구조화에 의해 제공될 수 있다. 이 때, 함몰부들 또는 캐치 저장부들은 미소 프리즘들 또는 미소 반사체들에 의해 형성될 수 있고, 이들은 예컨대 식각에 의해 생성될 수 있다.

[0030] 함몰부들 또는 캐치 저장부들은 예컨대 메사 트렌치들(mesa trenches) 또는 메사 트렌치들의 일 부분들로서 형성될 수 있고, 이들은 예컨대 전체의 에피택시층 시퀀스 또는 그 일부분을 분할시킬 수 있다. 이 때, 함몰부들의 두께는 에피택시층 시퀀스의 두께에 상응하거나, 그보다 작을 수 있다. 또한, 함몰부들은 메사 트렌치들의 폭에 의해 주어질 수 있는 폭을 포함하고, 예컨대, 상기 메사 트렌치들은 가령 개별화에 같은 차후의 가공 단계에 의해 다시 정해질 수 있다. 이러한 점은, 함몰부들이 상기 밀려들어온 전체의 접착제를 수용할 수 있도록 충분히 큰 부피를 포함하는 경우에, 바람직할 수 있다. 다른 한편으로는, 함몰부들 또는 캐치 저장부들의 부피 및 결합층의 필요 두께에 의해, 도포되어야 할 최대 접착제층을 위한 조건이 도출될 수 있다. 이러한 점은, 예컨대, 함몰부들 내지 캐치 저장부들이 메사 트렌치들로 형성되고, 이들이 약 1000  $\mu\text{m}$ 의 간격 및 약 40  $\mu\text{m}$ 의 트렌치폭을 가지며, 이들의 깊이가 예컨대 약 7  $\mu\text{m}$ 의 에피택시층 시퀀스의 두께에 상응하는 경우에, 바람직할 수 있다. 이를 통해, 도포될 접착제층에 있어서, 약 0.5  $\mu\text{m}$ 의 두께가 바람직한 것으로 증명될 수 있다.

[0031] 다른 실시예에서, 함몰부들 또는 캐치 저장부들은 표면 또는 표면의 일 영역의 거칠기 주어지는 함몰부들로 제공될 수 있다.

[0032] 다른 바람직한 실시예에서, 결합층의 평균 두께는 제1 및/또는 제2 표면의 지형학적 표면 구조들의 자릿수(order of magnitude)에 존재한다. 이는 특히, 결합층의 평균 두께가 제1 표면 및/또는 제2 표면의 거칠기 또는 거칠기 깊이의 자릿수에 존재한다는 것을 의미할 수 있다.

[0033] 거칠기는, 표면의 높이 변화의 rms-값으로 표시할 수 있는데, 상기 값은 표면의 높이 프로파일과 상기 표면의 평균 높이와의 차이의 평균 제곱근으로 정의된다. 표면의 높이 프로파일은 예컨대 원자간력 현미경(atomic

force microscope)을 이용하여 정의될 수 있는데, 표면의 단일 또는 복수 개의 절편들 내부에서 높이 프로파일들이 포함된다. 예컨대 원자간력 현미경, 스타일러스 프로파일로미터(stylus profilometer) 또는 백광 간섭계를 이용하여 얻어진 표면 높이 프로파일로부터, 평균 높이가 정의될 수 있고, 상기 평균 높이는 높이 프로파일의 산술 평균을 나타낸다. 평균 높이 및 산출된 높이 프로파일을 이용하여, 표면 거칠기를 위한 근의 rms-값이 결정될 수 있다.

[0034] 결합층의 두께는 제1 표면의 평균 높이와 제2 표면의 평균 높이 사이의 차로 정의된다.

[0035] 이 때, 표면의 거칠기 또는 표면 영역의 거칠기는 금속층들의 증착 시 발생하는 자연 거칠기에 상응할 수 있다. 상기 금속층들은 가령 전기적 금속-반도체-접촉층들 또는 반사성 금속층들이 있다.

[0036] 예컨대, 표면 또는 표면 영역의 거칠기는, 가령 포토리소그라피 패터닝 또는 샌드 블라스트(sand blast)와 같은 방법에 의해 증가될 수 있다. 또한, 가령 느린 증착률 및/또는 높은 기판 온도와 같이 적합한 증착 조건들을 선택하여 거칠기를 증가시킬 수 있다.

[0037] 예컨대, 제1 표면의 지형학적 표면 구조들의 증가된 영역들이 제2 표면과 직접 접촉하고 및/또는 그 반대의 경우로 함으로써, 소자들의 표면들 사이의 전기 전도 접촉은 충분히 얇은 결합층으로도 보장될 수 있다. 특히, 제1 표면의 지형학적 표면 구조들의 증가된 영역이 제2 표면의 지형학적 표면 구조들과 직접 접촉할 수도 있다. 제1 및/또는 제2 표면의 지형학적 표면 구조들이 제1 및/또는 제2 표면의 거칠기에 의해 주어진다면, 지형학적 표면 구조들의 증가된 영역들은 특히 제1 표면의 거칠기에 의한 끝단들 및/또는 제2 표면의 거칠기 끝단들이거나, 그것들을 포함할 수 있고, 또한, 제1 표면의 거칠기 끝단들이 제2 표면의 거칠기 끝단들과 직접 접촉할 수도 있다.

[0038] 더욱 바람직한 실시예에서, 제1 표면 및/또는 제2 표면의 거칠기는 적어도 접합 영역의 내부에서 적어도 수 나노미터이다.

[0039] 다른 실시예에서, 제1 표면 및 제2 표면은 적어도 부분적으로 전기 전도성으로 형성된다. 특히, 바람직하게는, 접합 영역의 적어도 일부분은 전기 전도성으로 형성될 수 있다. 또한, 특히, 적어도 지형학적 표면 구조들의 부분 영역들은 전기 전도성으로 형성될 수 있다.

[0040] 전기 전도성으로 형성된 제1 표면 및/또는 제2 표면은 예컨대 금속을 포함한다. 제1 및/또는 제2 표면은 전기 전도성으로 형성되거나, 형성될 수 있고, 또한 투명 전도성 산화물(TCO)을 포함하거나, 그것으로 구성될 수도 있다.

[0041] 다른 실시예에서, 결합층을 형성하는 전기 절연성 접착제는 바람직하게는 내 용제로는 예컨대 N-메틸-피롤리돈(N-Methyl-Pyrrolidone, NMP), 예컨대 1-메틸-2-피롤리딘, 아세톤, 이소프로판올, 에탄올 및/또는 메탄올이 있다. 또한, 바람직하게는, 수산화칼륨(KOH), 수산화나트륨(NaOH) 및/또는 인산에 대해 알칼리-내지 산 저항성이 있을 수 있다.

[0042] 또한, 바람직하게는, 전기 절연성 접착제는 0.1 밀리바(millibar)와 수 백 밀리바, 바람직하게는 약 100 밀리바 사이의 일반적 공정 진공과 관련하여 진공 적합성을 가지고, 및/또는 200°C 보다 높은 온도일 때 온도 안정성을 가진다. 상기와 같은 특징들은, 일반적으로, 소자의 다음 공정 단계들 및/또는 추후의 사용 시의 요구 사항들과 관련하여 바람직할 수 있다. 특히, 사용되어야 할 결합 기술은, 상기 장치의 생산 라인에서 사용되는 화학 약품들 및 통용되는 공정 단계들과 조화되어야 한다. 그 외에, 결합층은 장치 또는 개별 소자들의 작동 방식에 부정적 영향을 야기해서는 안된다. 특히, 용제들, 연화제들 또는 다른 성분들의 탈기(degas)에 의한 부정적 영향이 발생하지 않는 것이, 바람직할 수 있다.

[0043] 다른 실시예에서, 전기 절연성 접착제는 UV-경화성이다. 이러한 점은, 결합층이 적어도 일 측에서 광학적으로 연결되는 경우, 즉 예컨대 소자가 투명하여 결합층이 투명한 소자의 일 측으로부터 UV-광으로 조사될 수 있는 경우에, 유리할 수 있다.

[0044] 더욱 바람직한 실시예에서, 전기 절연성 접착제는 비스벤졸사이클로부텐(bisbenzocyclobutene, BCB)을 포함하거나, 그것으로 구성된다. BCB의 가공 특성은 1993년도 제3회 일본 국제 첨단 재료 및 제조 공정 학회(Society for the Advancement of Material and Process Engineering, SAMPE) 심포지움에서의 다카하시(T. Takahashi)의 발표문 826-833쪽에 기재되어 있고, 이의 개시 내용은 상기와 관련하여 참조로 포함된다. BCB는, 예컨대 물과 같은 부산물들의 생성 없이 경화되어 수축이 매우 적다는 것이 장점이다.

[0045] 일 실시예에서, 제1 표면을 가진 제1 소자와 제2 표면을 가진 제2 소자 사이에 전기 전도성 결합을 형성하고,

이 때 상기 제1 및 제2 표면 중 적어도 하나의 표면은 지형학적 표면 구조들을 포함하도록 하는 방법은,

[0046] - 제1 및/또는 제2 표면상에 전기 절연성 결합층을 적층하는 단계,

[0047] - 제1 표면 및 제2 표면(9)을 상호 간에 배치시키는 단계, 및

[0048] - 제1 소자(5) 및/또는 제2 소자(8)에 힘(10)을 가하여, 제1 및 제2 표면 사이에서 상기 지형학적 표면 구조들에 의한 전기 전도 접촉이 이루어지도록 하는 단계를 포함한다.

[0049] 방법의 일 실시예에서, 제1 표면 및 제2 표면은 지형학적 구조들을 포함한다.

[0050] 방법의 다른 실시예에서, 지형학적 구조들은 예컨대 식각 또는 그라인딩(grinding)과 같은 방법에 의해 생성된다.

[0051] 방법의 다른 실시예에서, 결합되어야 할 제1 표면 및 제2 표면 중 적어도 하나의 표면상에는 예컨대 식각 또는 그라인딩과 같이 제거성 구조화 방법에 의해 및/또는 예컨대 주조와 같은 변형성 구조화 방법에 의해 함몰부들이 형성된다. 이 때, 서로 다른 방법에 의해 일 소자 또는 두 개의 소자들에 서로 다른 함몰부들이 형성될 수 있다.

[0052] 방법의 다른 실시예에서, 전기 절연성 결합층 가령 전기 절연성 접착제는 구조화되어 도포된다. 이는, 예컨대, 가령 잉크젯 프린팅 또는 스크린 프린팅과 같은 인쇄 방법에 의해 달성될 수 있다. 이때, 적어도 약 10  $\mu\text{m}$ 의 두께를 가진 결합층은 스크린 프린팅에 의해, 약 10  $\mu\text{m}$ 보다 작은 결합층은 잉크젯 프린팅에 의해 도포되는 것이, 유리할 수 있다. 또한, 예컨대 스템핑(stamping) 방법이 사용될 수도 있다.

[0053] 대안적으로, 전기 절연성 결합층 가령 전기 절연성 접착제가 구조화되지 않고, 예컨대 스핀 코팅(spin coating) 또는 기상 증착에 의해 도포될 수도 있다. 다른 실시예에서, 구조화되지 않고 도포된 결합층은, 상기 도포 이후 구조화된다. 예컨대, 적어도 하나의 표면 또는 적어도 그 표면의 영역들의 적어도 부분 영역들은, 결합층과 관련하여 서로 다른 습윤 특성들을 가짐으로써, 구조화가 이루어질 수 있다. 서로 다른 습윤 특성은 가령 적어도 하나의 표면 또는 적어도 그 표면의 영역들의 부분 영역들이 개질됨으로써 달성될 수 있다. 대안적으로 또는 추가적으로, 결합층이 예컨대 광에 의해 구조화될 수 있는 경우가 바람직할 수 있다. 조사는 예컨대 포토마스크에 의해 이루어질 수 있다. 대안적으로, 결합층이 래커 마스크를 이용하여 건식 또는 습식 식각에 의해 구조화될 수도 있다.

[0054] 적합한 실시예에서, 결합층은 도포된 이후 10 nm과 100  $\mu\text{m}$  사이의 두께를 가진다. 또한, 결합층이 도포된 이후 100 nm과 10  $\mu\text{m}$  사이의 두께를 가지는 것이 바람직할 수도 있다. 결합층이 도포된 이후 500 nm과 5  $\mu\text{m}$  사이의 두께를 포함하는 것이 더욱 바람직할 수 있다. 이 때, 도포된 이후 결합층의 두께는 상기 결합층의 점도 및/또는 구조화에 및/또는 제1 및/또는 제2 표면의 거칠기에 따라 달라질 수 있다.

[0055] 방법의 더욱 바람직한 실시예에서, 결합층의 두께는 적어도 하나의 소자 또는 두 개 소자들에 힘을 가하여 줄어들어, 상기 힘의 작용 이후 결합층의 두께가 제1 및/또는 제2 표면의 거칠기 또는 그 깊이의 자릿수에 존재하게 된다. 이는 특히, 힘의 작용이 결합층의 두께를 축소하여, 적어도, 결합되어야 할 표면들의 거칠기 끝단들이 접촉하도록 한다는 것을 의미한다.

[0056] 방법의 일 실시예에서, 힘은 1 내지 40 kN의 범위로 20 내지 78  $\text{cm}^2$ 의 면위에 작용한다.

[0057] 본 발명의 다른 장점들 및 바람직한 실시예들 및 형성예들은 도면과 관련하여 기재된 실시예들과 함께 이하에서 제공된다.

## 실시예

[0065] 실시예들 및 도면들에서 동일하거나 동일하게 작용하는 구성 요소들은 각각 동일한 참조번호를 가진다. 도시된 요소들 및 이들의 상호 간 크기 비율은 기본적으로 축적에 맞는 것으로 볼 수 없고, 오히려, 예컨대 총 두께 또는 거칠기와 같은 개별 요소들은 더 나은 묘사 및/또는 더 나은 이해를 위해 과장되어 확대 도시될 수 있다.

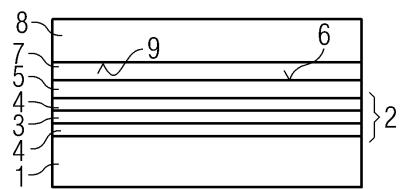

[0066] 도 1A 내지 1F에 따른 실시예에서, 박막 반도체칩의 제조를 위한 공정 순서 내에서, 제1 소자로서의 에피택시층 시퀀스를 제2 소자로서의 지지 웨이퍼와 결합시킨다.

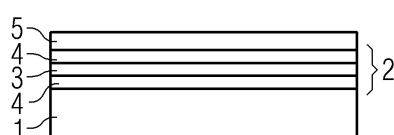

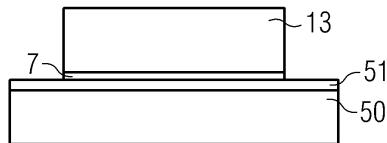

[0067] 도 1A에 따른 발광 박막 반도체칩의 제조를 위해, 가령 SiC-기판 또는 사파이어-기판과 같은 적합한 성장 기판 (1)상에서 에피택시층 시퀀스(2)가 에피택시얼 성장된다. 에피택시층 시퀀스는 활성 영역(3) 및 다른 기능 층들 (4)을 포함하고, 상기 활성 영역 내에서 구동 중에 광이 생성된다. 광 생성을 위해, 활성 영역(3)은 예컨대 pn-

접합, 더블 이종 구조, 단일-양자 우물 또는 다중 양자 우물(MQW)을 포함한다. 여기서 양자 우물 구조라는 명칭은 양자화의 차원성에 대한 정보를 제공하지 않는다. 따라서, 상기 명칭은 특히 양자 흠통들, 양자선들, 양자점들 및 이러한 구조들의 각 조합을 포함한다. MQW-구조들을 위한 예시는 WO 01/39282, US 5,831,277, US 6,172,382 B1 및 US 5,684,309의 인쇄본에 기재되어 있고, 이의 개시 내용은 여기서 참조로 포함된다.

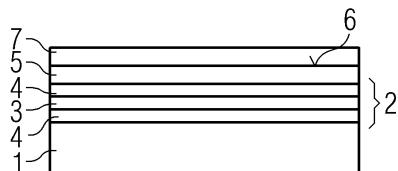

[0068] 또한, 성장 기판(1)과 반대 방향에 있는 에피택시층 시퀀스(2)의 측에는 반사성 층(5)이 적층되고, 상기 반사성 층은 활성 영역(3)에서 생성되는 광을 다시 상기 에피택시층 시퀀스(2)로 재반사시킨다. 상기 광은 성장 기판(1)과 반대 방향에 있는 측에서 에피택시층 시퀀스(2)로부터 방출될 수 있다. 이 때, 반사성 층(5)은 Au, Al이나 Ag, 또는 이러한 금속들로 구성된 합금을 포함하고, 개별층으로서 또는 다른 물질들 소재의 층들을 포함하는 층 시퀀스로서 존재할 수 있다. 종래의 박막 반도체칩의 에피택시층 시퀀스(2)의 층 두께는 수 마이크로미터 내지 수십 마이크로 미터의 범위에 있다.

[0069] 도 1B에 따른 다른 단계에서, 성장 기판(1)과 반대 방향에 있는 반사성 층(5)의 측(6)에는 결합층(7)이 적층된다. 상기 측은 제1 소자의 제1 표면으로서 역할한다. 이 때, 성장 기판(1)과 반대 방향에 있는 반사성 층(5)의 측(6)에는, 미소 프리즘 구조화가 사전 구조화로서 바람직하게 사용될 수 있다. 이는 WO 02/13281 A1에 기재되어 있고, 이의 개시 내용은 여기서 참조로 포함된다. 미소 프리즘들을 위한 리세스들은 예컨대 반도체층에 식각될 수 있고, 그 위에 반사성 층(5)이 증착될 수 있다. 에피택시층 시퀀스(2)가 반사성 층(5)에 의해 접촉될 수 있도록 하려면, 상기 반사성 층(5)이 바람직하게는 전기 전도성 물질로 형성된다. 결합 단계 이후 수 많은 다른 공정 단계들이 이루어지므로, 결합 매체는, 특히 내 용제성, 진공 적합성 및/또는 온도 안정성을 가지고, 모든 다른 공정 및 작업 단계들과 조화되는 것이 필요하다. 결합층(7)을 위한 적합한 물질은 예컨대 BCB(bisbenzocyclobuten, 이는 예컨대 다우 코닝(Dow Corning) 사의 상표명 사이클로부텐 3022-xx에서 얻을 수 있으며, 이 때 "xx"는 메시틸렌 용제에서 선 중합된 BCB-모노머들의 양으로 제공됨)가 있고, 이는 바람직하게는 포토레지스트와 마찬가지로 양호하게 측소될 수 있는 0.5 내지 10 마이크로미터 범위의 두께로 스핀 온 될 수 있고, 일반적으로 결합되어야 할 표면들상에 양호하게 부착된다. 사이클로부텐 3022-35(cyclotene 3022-35) 또는 사이클로부텐 3022-46)을 사용하는 것이 바람직한 것으로 증명될 수 있고, 이를 이용하여 예컨대 도포 시, 약 1.0 내지 약 2.3  $\mu\text{m}$ 의 층 두께 내지는 약 2.4 내지 약 5.5  $\mu\text{m}$ 의 층 두께가 달성될 수 있다.

[0070] 경우에 따라서, 도포된 이후, BCB-막은 티타늄 마스크를 사용하여 반응 이온 식각에 의해 구조화된다.

[0071] 대안적으로, 예컨대 xx=35 또는 xx=46인 사이클로부텐 4022-xx을 사용하는 것도, 포토 구조화가 가능하다는 것을 증명할 수 있다. 도포 시, 예컨대 약 2.6 내지 약 5.2  $\mu\text{m}$ 의 층 두께, 내지는 약 7.3 내지 약 14.2  $\mu\text{m}$ 의 층 두께가 달성될 수 있다.

[0072] 대안적으로 또는 추가적으로, 결합층(7)은 에피택시층 시퀀스(2)와 결합되어야 할 지지 기판(8)상에 적층된다.

[0073] 도 1C에 따른 다른 제조 단계에서, 제2 표면(9)을 가진 제2 소자로서의 지지 기판(8)은, 에피택시층 시퀀스(2)에 관련하는 소기의 위치에서 결합층(7)상에 배치된다. 지지 기판(8)을 위한 적합한 물질들은 가령 규소 또는 금속과 같은 전기 전도성이거나, 전기 절연성이면서 전기 전도성 표면을 가진다. 이를 통해, 다른 방법 단계에서, 에피택시층 시퀀스(2)를 지지 기판(8)에 의해 단순히 전기적으로 접촉시킬 수 있다.

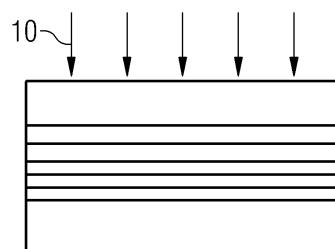

[0074] 도 1D에 따른 다른 제조 단계에서, 에피택시층 시퀀스(2)를 종결하는 반사성 층(5) 및 지지 기판(8)의 결합되어야 할 표면들(6, 9)에 대해 실질적으로 수직으로 힘(10)이 작용한다. 이를 통해, 결합층(7)의 두께가 감소되어, 도 2의 실시예에 따라 에피택시층 시퀀스(2)를 종결하는 반사성 층(5) 및 지지 기판(8)의 표면들(6, 9)의 지형학적 표면 구조들이 닿아서, 전기 전도성 접촉이 이루어지도록 한다. 이 때, 바람직하게는, 표면들(6, 9)의 지형학적 표면 구조들은 도 2의 실시예에 도시된 바와 같은 거칠기 끝단들(20, 21)일 수 있다.

[0075] 도 1E에 따라 두께가 감소된 결합층(7)은 알맞은 압력하에 소정의 온도 범위에서 경화되며, 상기 온도 범위는 폭 넓은 범위에서 자유롭게 선택 가능하다. 이 때, 약 20 내지 78  $\text{cm}^3$ 의 면에 약 1 내지 약 40 kN의 힘이 적합한 것으로 증명될 수 있다.

[0076] 예컨대, 약 150 내지 약 200°C의 범위의 온도에서 BCB는 경화될 수 있다. 경화는 약 150°C의 온도에서 약 12시간동안, 또는 약 200°C의 온도에서 약 30분동안 이루어지는 것이 더욱 바람직한 것으로 증명될 수 있다. 또한, 예컨대 150°C와 같이 낮은 온도에서 약 3분동안 먼저 경화되고, 예컨대 약 200°C와 같이 그보다 높은 온도에서 약 2분동안 나중에 경화되는 것이 바람직할 수도 있다.

[0077] 결합층(7)이 기계적 내구성 및 내온도성과 관련하여 양호한 공정 친화성을 가짐으로써, 장치는 재가공될 수 있다. 특히, 양호한 공정 친화성은, 결합층에 의해 다른 공정 단계가 제한되거나, 부정적 영향을 받지 않도록 하

는 것으로 나타낼 수 있다. 예컨대, 상기 결합층을 이용하면, 다음의 공정 단계에서 전공 상태에서 부정적으로 작용할 수 있는 탈기의 생략, 식각 공정에 대한 내구성 및 다음 공정 단계의 온도들과 상기 결합층의 조화에 의해, 예컨대 반도체칩을 본 발명에 따른 결합층을 이용하여 제조하는 공정에 있어서, 부정적인 효과가 발생하지 않도록 할 수 있다.

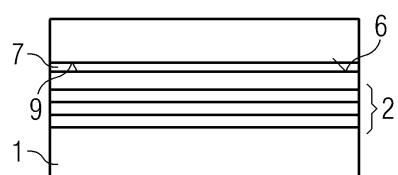

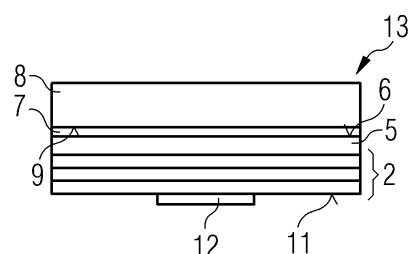

[0078] 성장 기판(1)은 예컨대 그라인딩에 의해 얇아지거나 완전히 제거된다. 다른 방법 단계에서, 지지 기판(8)과 반대 방향에 있는 에피택시층 시퀀스(2)의 표면(11)상에는 에피택시층 시퀀스(2)의 접촉을 위한 본딩 패드(12)가 적층된다(도 1F 참조). 상기와 같이 얻어진 반도체칩(13)의 전기적 접촉은, 지지 기판(8) 및 본딩 패드(12)를 접촉시키는 전기 공급부들에 의해 가능해질 수 있다. 반도체칩(13)이 가령 도체 프레임과 같이 적합한 지지 기판들상에 배치되는 것은, 도 3 내지 5의 실시예들에 도시된다.

[0079] 도시된 방법들은, 지지 웨이퍼를 포함하는 4인치-에피택시 웨이퍼의 대면적 결합을 위해 사용될 수 있으며, 상기 에피택시 웨이퍼는 성장 기판상에서 에피택시층 시퀀스를 포함한다.

[0080] 도 1A 내지 1F에 도시된 방법 및 에피택시층 시퀀스의 구조화에 의해, 예컨대 4인치 지지 웨이퍼상에서 일반적으로 약 50000 개의 박막 반도체칩들이 제조될 수 있고, 상기 지지 웨이퍼에 의한 상기 반도체칩들의 전기적 접촉은 각 박막 반도체칩을 위해 검사 및 입증될 수 있다.

[0081] 또한, 예컨대 본 발명에 따른 방법에 의해 제조되고 약  $90000 \mu\text{m}^2$ 의 결합층면을 포함하는 칩은 적어도 약  $700 \mu\text{m}^2$ 의 접촉부면을 포함하는 것이, 평가 시 확인될 수 있다.

[0082] 일반적인 납땜 결합에 비해, 지지 웨이퍼와 박막 반도체 칩의 전기 전달 저항은 증가되지 않는다.

[0083] 반도체칩(13)의 전기적 접촉이, 도 1F에 따른 실시예와 같이 지지 기판(8)을 향해 있는 반사성 층(5)의 측(6)에서 지지 기판(8)을 지나서, 그리고 지지 기판(8)과 반대 방향에 있는 에피택시층 시퀀스(2)의 측(11)에서 본딩 패드(12)를 지나 이루어지는 것이 아니라, 에피택시층 시퀀스(2)의 일 측에서만 구조화 전기 접촉부들에 의해 이루어짐으로써, 전기 절연성 접착제로 구성된 결합층(7)을 이용하여, 예컨대 구조화 도체 밴드상에서 구조화 전기 공급부들로 구조화 전기 접촉부들이 전기적으로 접촉된다. 소위 상기와 같은 플립-칩-실장은, EP 0905797 A2에 기재되어 있으며, 이의 개시 내용은 여기서 참조로 포함된다. 이 때, 실장되어 접촉되어야 할 박막 반도체 칩(13)은 반사성으로 형성된 접촉부들(5)과 함께 전기 공급부들상에, 예컨대 도체 밴드상에 안착되고, 이 때, 반사성으로 형성된 접촉부들(5)의 구조화에 의해 수용 트렌치들로 작용하는 적합한 함몰부들(40)이 준비된다. 본 발명에 따른 결합층(7)으로서, 전기 절연성 접착제가 사용되고, 상기 접착제는, 실장 공정에서 흔들림에 의한 단락을 기본적으로 방지할 수 있다는 장점을 제공한다. 예컨대, 너무 많이 도포되어, 반도체칩의 측면들 즉 칩 플랭크들(flanks)을 덮을 수 있는 접착제에 의해 에피택시층 시퀀스의 단락이 발생하지 않도록 할 수도 있다.

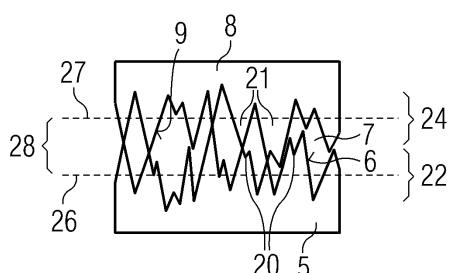

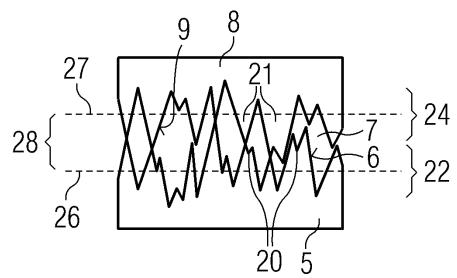

[0084] 도 2에 따른 실시예에서, 본 발명에 따른 장치의 일 부분이 도시된다. 이 때, 제1 소자(5)의 제1 표면(6) 및 제2 소자(8)의 제2 표면(9)은 각각 지형학적 표면 구조들(22, 24)을 포함하고, 상기 구조들은, 예컨대 원자간력 현미경을 이용하여 계측할 때, 높이 프로파일로서 산출될 수 있다. 소자들(5, 8)의 표면들(6, 9)에 있어서, 표면(22)의 평균 높이 라인(26) 및 표면(24)의 평균 높이 라인(27)이 제공될 수 있다. 평균 높이 라인들(26, 27)의 간격은, 결합층(7)의 두께(28)를 정의한다. 도시된 실시예에서, 표면 구조들(22, 24)은 가령 거칠기 끝단들과 같은 용기부들(20, 21)을 포함하고, 상기 용기부들 사이에는 함몰부들이 존재할 수 있다. 도시된 바와 같이, 용기부들은, 가령 구조화되지 않은 거칠기 프로파일과 같이 불규칙적으로 배치될 수 있다. 대안적으로(미도시) 용기부들은 적어도 부분 영역들에서 규칙적으로 배치될 수 있다.

[0085] 예컨대, 제1 소자(5)는 실시예 1A의 반사성 층을 포함한 에피택시층 시퀀스일 수 있고, 이 때 제1 표면은 상기 에피택시층 시퀀스와 반대 방향에 있는 반사성 층의 측이며, 제2 소자(8)는 지지 기판일 수 있다. 대안적으로, 제1 소자(5)는 예컨대 가령 다음의 실시예들 중 어느 하나의 실시예에 따른 박막 반도체 칩과 같은 반도체칩(13)일 수도 있고, 이 때 제1 표면(6)은 에피택시층 시퀀스와 반대 방향에 있는 지지 기판의 측일 수 있으며, 제2 소자(8)는 표면 실장 가능한 소자의 하우징의 도체 프레임 또는 예컨대 이하의 도면들에 도시된 바와 같은 반도체칩(13)을 위한 다른 적합한 기판일 수 있다.

[0086] 힘의 작용(10)에 의해, 소자들(5, 8)은 서로 인접하되, 두 표면들(6, 9)의 지형학적 표면 구조들의 용기부들(20, 21)이 서로 맞닿을 때까지 인접한다. 상기와 같이 서로 맞닿은 용기부들(20, 21)에 의해, 두 소자들(5, 8)의 표면들(6, 9)사이의 전기 전도 접촉이 형성된다. 전기 접촉 저항이 작을 수록, 더 많은 접촉점들이 형성된다. 이 때, 결합층의 두께(28)는 지형학적 표면 구조들(22, 24)의 높이 프로파일, 즉 예컨대 표면들(6, 9)의 거

칠기에 어느 정도 상응할 수 있다.

[0087] 결합층(7)은 소자들(5, 8)사이에 전기 접촉 형성 시 완성될 수 있고, 결합층을 형성하는 전기 절연성 결합 매체는 용기부들(20, 21) 사이에 존재한다. 이를 통해, 소자들(5, 8) 사이에서 접착 본딩(adhesive bonding)식의 접촉이 보장될 수 있다.

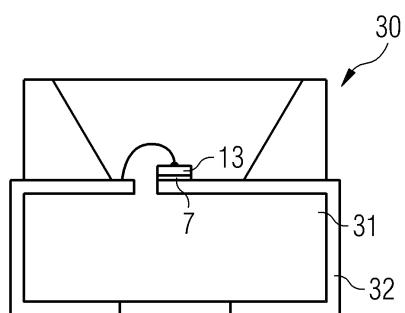

[0088] 도 3에 따른 실시예에서는 예컨대 방법 1A 내지 1F에 따라 제조된 박막 반도체 칩과 같은 반도체칩(13)의 실장을 다루며, 상기 반도체칩은 표면 실장 가능한 소자(30)에 배치된다. 표면 실장 가능한 소자(30)는 예컨대 접착제로 구성된 하우징(31) 및 도체 프레임(32)을 포함하고, 상기 도체 프레임은 표면 실장 가능한 소자(30)를 예컨대 도체 판상에 실장하여 전기적으로 접촉시킬 수 있다. 반도체칩(13)은, 일 측에서, 1F의 실시예에 따른 박막 반도체칩의 경우 에피택시층 시퀀스(2)와 반대 방향에 있는 지지 기판(8)의 측에서 하우징(31) 내부의 도체 프레임(32)에 배치되어, 전기 절연성 접착제로 구성된 결합층(7)을 이용하여 배치되고, 도체 프레임(32)에 전기적 및 열적으로 결합된다. 이 때, 도체 프레임(32)은 전기 공급부로서 뿐만 아니라 열 싱크로도 역할하여, 반도체칩(13)에서 발생되는 열을 유도한다. 전기 전도 접착제에 있어서 전형적인 금속 충전없이, 매우 얇은 전기 절연성 결합층(7)을 사용하여, 상기 열을 매우 양호하게 유도할 수 있다.

[0089] 바람직하게는, BCB소재의 결합층들은 도 1A 내지 1F의 실시예에 따른 방법과 관련하여 그와 유사한 가공 파라미터들로 사용될 수 있다. 반도체칩(13)을 도체 프레임(32)상에 부착 즉 예컨대 안착시키는 것은, 결합층(7)의 경화와 시공간적으로 분리되어 수행될 수 있다.

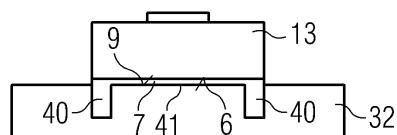

[0090] 도 4A에 따른 실시예에 도시된 반도체칩(13)은 도체 프레임(32)상에 실장되고, 이 때 도체 프레임(32) 즉 일반적으로 금속 밴드는 주조에 의해 변형되며, 결합층(7)의 전기 절연성 접착제를 위한 함몰부들(40)을 포함하도록, 변형된다. 반도체칩(13)이 도체 프레임(32)상에 안착될 때, 접촉힘에 의해, 결합층(7)으로서 적층된 접착제상에 압력이 가해지고, 따라서, 결합층(7)의 두께가 줄어든다. 이 때, 결합층(7)의 과잉의 접착제는 접착제를 위한 캐치 저장부로서 역할하는 함몰부들(40)로 눌려진다. 이 때, 접합 영역(41)에서의 접착제 두께가 줄어들어, 반도체칩(13)과 도체 프레임(32) 사이의 전기 전도 접촉이 발생한다. 캐치 저장부로서 역할하는 함몰부들(40)에 의해, 실장되어야 할 반도체칩(13) 주변에 과잉의 접착제가 밀려들어오지 않고, 이러한 점은 반도체칩(13)이 도체 밴드(32)상에 실장되어 잘 접촉될 수 있도록 한다.

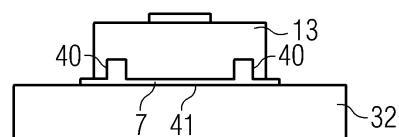

[0091] 도 4B에 따른 실시예에서, 1F의 실시예에 따른 실장되어야 할 반도체칩(13)은 함몰부들(40)을 포함하고, 상기 함몰부들은 접착제를 위한 캐치 저장부로서 역할한다. 이러한 함몰부들(40)은 에피택시층 시퀀스(2)와 반대 방향에 있는 지지 기판(8)의 측의 구조화에 의해 준비되거나, 결정학상의(crystallographic) 식각 어택(etch attack)과 연동하는 그라인딩 공정에 의해 발생된 거칠기에 의해 제공될 수 있다.

[0092] 도 4A의 실시예에 따른 반도체칩(13) 또는 도 4B의 실시예에 따른 반도체칩(13)의 접촉은, 예컨대 도체 프레임과 반대 방향에 있는 반도체칩의 측에서 본딩 패드(12)에 의해 이루어질 수 있다. 대안적으로, 플립-칩-실장시, 도체 밴드(32)를 향해 있는 반도체칩의 측에는, 반도체칩 측들을 위한 접촉가능성들이 구비될 수 있다(미도시). 그렇게하면, 본딩 패드(12)의 설치는 생략될 수 있다.

[0093] 도 5에 따른 실시예에서, 발광 반도체칩(13)은 투명 기판(50)상에 실장되고, 상기 투명 기판은 투명 전도성 산화물(transparent conductive oxide, 약어로 "TCO")을 포함하거나, 그것으로 구성되는 층(51)으로 코팅된다. TCO들은 투명한 전기 전도성 물질들로, 일반적으로, 예컨대 아연 산화물, 주석 산화물, 카드뮴 산화물, 티타늄 산화물, 인듐 산화물 또는 인듐 주석 산화물(ITO)과 같은 금속 산화물이다. 예컨대 ZnO, SnO<sub>2</sub> 또는 In<sub>2</sub>O<sub>3</sub>와 같은 2원 금속 산소 화합물들외에, 예컨대 Zn<sub>2</sub>SnO<sub>4</sub>, CdSnO<sub>3</sub>, ZnSnO<sub>3</sub>, MgIn<sub>2</sub>O<sub>4</sub>, GaInO<sub>3</sub>, Zn<sub>2</sub>In<sub>2</sub>O<sub>5</sub>, In<sub>4</sub>Sn<sub>3</sub>O<sub>12</sub>과 같은 3원 금속 산소 화합물 또는 서로 다른 투명 전도성 산화물의 혼합물이 TCO층에 속한다. 또한, TCO들은 반드시 화학량론적인 구성에 상응할 필요가 없고, p- 또는 n-도핑될 수 있다. 반도체칩(13)은 전기 절연성 접착제 소재의 결합층(7)을 이용하여 투명 기판(50)상에 고정된다. 상기 접착제는 UV-광으로 경화될 수 있다. 이 때, 도 1A 내지 1F의 실시예의 방법에 따라 제조될 수 있는 반도체칩(13)은 기판상에 배치되어, 지지 기판(8)이 상기 기판(50)을 향하도록 배치된다. 바람직하게는, 지지 기판은 투명하게 형성되고, 유리 또는 다른 투명 물질을 포함하거나, 그것으로 구성된다. 이를 통해, 반도체칩(13)으로부터 방출된 광은 반도체칩(13)의 지지 기판(8), 결합층(7), 층(51) 및 투명 기판(50)을 통해 출사될 수 있다. 결합층(7)의 적층 및 반도체칩(13)의 배치 이후, 반도체칩과 층(51) 사이의 간격은 힘에 의해 줄어들어서, 도 2의 실시예에 도시된 바와 같이 반도체칩(8)과 층(51) 사이의 전기 전도 접촉이, 두 소자들의 지형학적 표면 구조들의 용기부들 가령 거칠기 끝단들 사이의 접촉점들의 형성에 의해, 이루어지도록 한다. 그 이후, 전기 절연성 접착제는 예컨대 UV-광으로 경화될 수 있고, 상기 광은

투명 기판(50)의 측으로부터 결합층(7)까지 출사될 수 있다. 전기 접촉은 예컨대 접촉부들에 의해 이루어질 수 있고, 상기 접촉부들은 단일 또는 복수 개의 금속들을 포함하거나, 단일 또는 복수 개의 금속들로 구성된다. 상기와 같은 접촉부는 가령 반도체칩(13) 옆에, 특히 반도체칩과 적합한 간격을 두고 상기 층(51)상에 배치될 수 있다(미도시).

[0094] 기판(50)과 반대 방향에 있는 반도체칩의 측은 유사한 방식으로 접촉될 수 있다. 상기 측은 예컨대 미소 프리즘 구조화를 포함할 수 있다. 이 때, 기판(50)과 반대 방향에 있는 반도체칩(13)의 측에 추가적으로 다른 투명 기판(52)이 배치될 수 있고, 상기 기판은 예컨대 유리를 포함하거나, 유리로 구성된다. 투명 기판(52)은 TCO를 포함하거나, TCO로 구성되는 전기 전도성 층(53)으로 코팅될 수 있다. 반도체칩(13)과 전기 전도성 층(53)의 전기 전도 결합은 결합층(7)에 의해 이루어질 수 있다. 또한, 가령 전기 절연성 접착제와 같은 전기 절연성 물질로 구성되는 결합층(7)을 사용하여, 반도체칩(13)의 측면들(131, 132)에 인접하는 영역들(54)이 결합층 물질로 채워질 수 있다. 전기 절연성 결합층 물질을 사용하여, 반도체칩의 단락이 방지될 수 있다.

[0095] 대안적으로, 기판(50)이 투명하지 않고, 기판(52)은 투명할 수 있다.

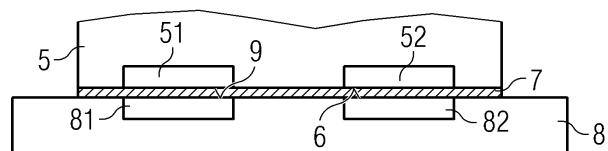

[0096] 도 6A에는, 두 개의 전기 접촉 영역들(51, 52)이 구비된 제1 소자(5)를 포함하는 실시예가 도시된다. 이 때, 일부분으로만 도시된 제1 소자(5)는 에피택시층 시퀀스로서 형성되고, 상기 층 시퀀스는 일 측의 전기 접촉 영역들(51, 52)에 의해 전기적으로 접촉될 수 있다. 이를 위해, 제1 소자(5)는 연속형 제1 표면(6)을 포함하고, 상기 제1 표면은 전기 접촉 영역들(51, 52)에 의해 전기적으로 연결될 수 있다. 도시된 실시예에서, 전기 접촉 영역들(51, 52)은 서로 다른 극성을 가진다. 대안적으로, 전기 접촉 영역들(51, 52)이 동일한 전기적 극성을 포함하여, 제1 소자의 전기적 연결이, 극성과 관련하여서만, 제1 표면(6)상에서 구조화 접촉 영역들(51, 52)에 의해 달성될 수 있다. 대안적으로, 제1 표면(6)은 동일하거나 서로 다른 극성을 가진 두 개 이상의 전기 접촉 영역들을 포함할 수 있다.

[0097] 제1 소자(5)는 제2 소자(8)상에 배치되고, 상기 제2 소자는 두 개의 전기 접촉 영역들(81, 82)을 포함하는 지지부이다. 이 때, 상기 지지부는 제2 표면(9)을 가진 지지 기판 또는 가령 도체 프레임으로서 형성될 수 있고, 상기 제2 표면은 제1 표면(6)상의 전기 접촉 영역들(51, 52)의 개수에 상응하여 전기 접촉 영역들(81, 82)을 포함한다. 대안적으로, 제2 표면(9)상의 전기 접촉 영역은 제2 표면상의 하나 이상의 전기 접촉 영역을 접촉시킬 수 있거나, 그 반대의 경우로도 가능하다(미도시).

[0098] 제1 소자(5)가 제2 소자(8)상에 고정되어 전기적으로 접촉되는 것은, 표면들(6, 9) 사이에 배치되는 결합층(7)을 이용하여 이루어진다. 이 때, 결합층(7)은 앞에 나온 실시예들과 같이 형성되고, 가령 BCB와 같은 전기 절연성 접착제를 포함한다.

[0099] 전기 접촉 영역들(81, 82) 위에 전기 접촉 영역들(51, 52)을 배치하고, 표면들(6, 9)의 각 거칠기 끝단들이 접촉할 수 있도록 결합층(7)의 두께를 감소시킴으로써, 전기 접촉 영역들(51, 81 내지 52, 82) 사이의 전기 접촉이 달성될 수 있다. 이를 위해, 도시된 실시예에서와 같이 결합층(7)은 구조화되지 않은 관통형 연속형 층으로서, 전기 접촉 영역들(51, 52, 81, 82)을 지나 연장될 수 있다. 결합층이 전기 절연성 접착제로 형성됨으로써, 제1 소자(5)가 제2 소자(8)에 대면적으로 접착 본딩 방식으로 고정될 수 있고, 이 때 전기 접촉 영역들(51, 52 내지 81, 82) 사이의 단락은 발생하지 않을 것이다.

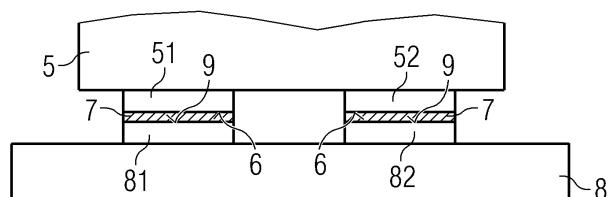

[0100] 도 6B의 실시예에서, 제1 소자(5) 및 제2 소자(8)는 각각 돌출된 전기 접촉 영역들(51, 52 내지 81, 82)을 포함한다. 제1 소자(5)는 가령 플립-칩-실장을 위한 반도체칩일 수 있고, 상기 반도체칩은 도체 프레임들(81, 82)을 포함하는 제2 소자(8)로서의 지지부상에 배치된다. 제1 소자(5)가 제2 소자(8)와 접착 본딩 방식으로 고정되어 전기적으로 연결되는 것은, 상기에 언급된 방식대로 각 전기적 접촉 영역들(51, 82 내지 52, 82) 사이에 배치된 결합층(7)에 의해 이루어진다.

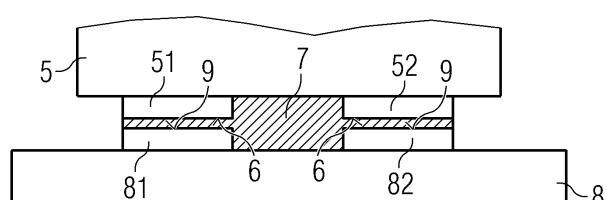

[0101] 도 6C는 다른 실시예를 도시하는데, 여기서 결합층(7)은, 제1 소자(5)가 제2 소자(8)에 더욱 양호하게 접착 본딩 방식으로 고정될 수 있도록, 전기 접촉 영역들(51, 52, 81, 82) 사이에 배치된다.

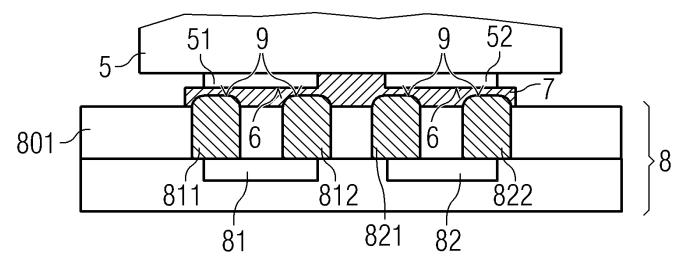

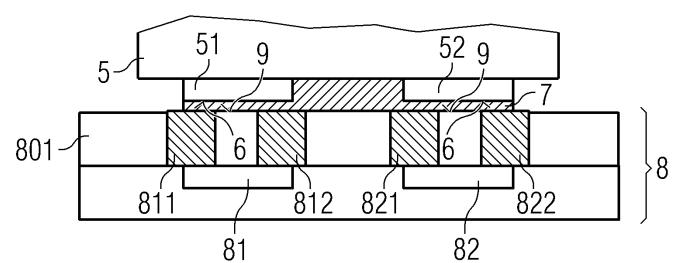

[0102] 도 6D의 실시예는 전기 접촉 영역들(81, 82) 위에서 추가 층을 포함하는 제2 소자(8)를 도시하는데, 상기 추가 층은 가령  $SiO_2$ 라는 산화물과 같은 절연성 물질(801)을 포함하고, 상기 절연성 물질은 제2 소자(8)의 전기 접촉 영역들(81, 82)을 각각 접촉시키는 금속 충전부들(811, 812, 821, 822)을 포함한다. 절연성 물질(801)을 포함한 층상에, 가령 구조화 전기 접촉 영역들(51, 52)을 포함한 에피택시층 시퀀스와 같은 제1 소자(5)가 배치되고, 상기 구조화 전기 접촉 영역들은 상기에 기재된 방식으로 결합층(7)을 이용하여 금속 충전부들(811, 812 내지 821, 822)에 연결되고, 또한 제2 소자(8)의 전기 접촉 영역들(81, 82)에도 연결된다. 예컨대, 제2 소자(8)는 전

기 유입부(81, 82)를 포함한 기판으로서 형성될 수 있고, 상기 제2 소자 위에, 절연성 물질(801) 및 금속 충전부들(811, 812, 821, 822)을 포함한 층이 배치된다. 대안적으로, 금속 충전부들(811, 812, 821, 822)은 물질(801)과의 경계면에서 절연성 물질로 된 층에 의해 둘러싸일 수 있고, 따라서, 상기 물질(801)도 전기가 통할 수 있다.

[0103] 도 6E의 실시예에서, 금속 충전부들(811, 812, 821, 822)은 물질(801) 위에 둘러싸이고, 가령 벼섯 구조로 형성된다. 이 때, 금속 충전부들(811, 812, 821, 822)의 제2 표면(9)과 전기 접촉 영역들(51, 52)의 제1 표면(6) 사이에서 결합층(7)의 두께를 충분히 줄여 전기 접촉이 이루어진다.

[0104] 도시된 실시예들에서, 금속 충전부들(811, 812, 821, 822)의 적합한 분포 및 적합한 치수화 특히 직경에 의해, 제1 소자(5)와 제2 소자(8)의 접촉이 조정 없이 달성될 수 있다. 이 때, 금속 충전부들의 개수는 도시된 개수와 다를 수 있다. 대안적으로 또는 추가적으로, 제1 및/또는 제2 소자는 가령 안내부들 또는 안내 에지들과 같은 조정 요소들을 포함할 수 있어서, 금속 충전부들의 배치 및 그 치수의 제한은 생략될 수 있다.

[0105] 본 발명은 실시예들에 의거한 기재에만 한정되지 않는다. 오히려, 본 발명은 각 새로운 특징 및 특징들의 각 조합을 포함하고, 이는 특히 청구 범위들에서 각 특징들의 조합으로 포함된다. 비록 이러한 특징들 또는 이러한 조합들이 그 자체로 특히 청구 범위들 또는 실시예들에 정확하게 제공되지 않더라도 말이다.

### 도면의 간단한 설명

[0058] 도 1A 내지 1F는 본 발명에 따른 방법의 다양한 단계들에서 장치의 개략적 단면도들을 도시한다.

[0059] 도 2는 제1 실시예에 따른 장치의 일 부분의 개략적 단면도를 도시한다.

[0060] 도 3은 제2 실시예에 따른 장치의 개략적 단면도를 도시한다.

[0061] 도 4A는 제3 실시예에 따른 장치의 개략적 단면도를 도시한다.

[0062] 도 4B는 제 4 실시예에 따른 장치의 개략적 단면도를 도시한다.

[0063] 도 5는 제5 실시예에 따른 장치의 개략적 단면도를 도시한다.

[0064] 도 6A 내지 6E는 다른 실시예들에 따른 다른 장치의 개략적 단면도들을 도시한다.

### 도면

#### 도면1A

#### 도면1B

도면1C

도면1D

도면1E

도면1F

도면2

도면3

도면4A

도면4B

## 도면5

## 도면6A

## 도면6B

## 도면6C

## 도면6D

도면6E