(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6169971号

(P6169971)

(45) 発行日 平成29年7月26日(2017.7.26)

(24) 登録日 平成29年7月7日(2017.7.7)

(51) Int.Cl.

H04R 3/00 (2006.01)

F 1

H04R 3/00 310

請求項の数 21 (全 15 頁)

(21) 出願番号 特願2013-540824 (P2013-540824)

(86) (22) 出願日 平成24年10月25日 (2012.10.25)

(86) 国際出願番号 PCT/JP2012/077570

(87) 国際公開番号 WO2013/062038

(87) 国際公開日 平成25年5月2日 (2013.5.2)

審査請求日 平成27年10月16日 (2015.10.16)

(31) 優先権主張番号 特願2011-233937 (P2011-233937)

(32) 優先日 平成23年10月25日 (2011.10.25)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 506173569

株式会社 Trigence Semiconductor

東京都千代田区外神田2-5-15

(74) 代理人 110000408

特許業務法人高橋・林アンドパートナーズ

(72) 発明者 安田 彰

東京都千代田区外神田4-13-5 株式会社 Trigence Semiconductor 内

(72) 発明者 岡村 淳一

東京都千代田区外神田4-13-5 株式会社 Trigence Semiconductor 内

最終頁に続く

(54) 【発明の名称】デジタル音響システム

## (57) 【特許請求の範囲】

## 【請求項 1】

s個の駆動素子を駆動してアナログ音声に変換する駆動回路を有するデジタル音響システムであり、

前記駆動素子の数sを読み取り、デジタル入力信号を変調し、当該変調により得られたnビットのデジタル信号をミスマッチシェーピングしm個のデジタル信号に変換する変調器と、

前記変調器が変換したm個のデジタル信号をシリアル伝送されるデジタル信号に変換するパラレル・シリアル変換器と、

前記パラレル・シリアル変換器により変換されたデジタル信号をm個のデジタル信号に変換し復元するシリアル・パラレル変換器と、

を有し、

前記駆動回路は、前記シリアル・パラレル変換器により復元されたm個のデジタル信号を受け取り、前記s個の駆動素子を駆動してアナログ音声に変換するデジタル音響システム。

## 【請求項 2】

前記シリアル伝送されるデジタル信号のビット数が1であることを特徴とする請求項1に記載のデジタル音響システム。

## 【請求項 3】

デジタル入力信号を変調しnビットのデジタル信号を出力する変調器と、

10

20

前記　　変調器に接続され前記nビットのデジタル信号をミスマッチシェーピングしm個のデジタル信号に変換する後置フィルターと、

前記後置フィルターが変換したm個のデジタル信号をシリアル伝送されるデジタル信号に変換するパラレル・シリアル変換器と、

前記パラレル・シリアル変換器により変換されたデジタル信号をm個のデジタル信号に変換し復元するシリアル・パラレル変換器と、

を有し、

前記シリアル・パラレル変換器により復元されたm個のデジタル信号を受け取り、s個の駆動素子を駆動してアナログ音声に変換する駆動回路と

前記パラレル・シリアル変換器により変換されたデジタル信号を記憶し、記憶されたデジタル信号を読み出して前記シリアル・パラレル変換器に出力する記憶装置

10

を有し、

前記記憶装置は、着脱可能な記憶媒体に前記パラレル・シリアル変換器により変換されたデジタル信号を記憶し、読み出すことが可能であるデジタル音響システム。

【請求項4】

前記記憶装置は、電子透かしデータが重畳されたデータを記憶することを特徴とする請求項3に記載のデジタル音響システム。

【請求項5】

前記電子透かしデータは、前記アナログ音声の帯域外のデータとして重畳されることを特徴とする請求項4に記載のデジタル音響システム。

20

【請求項6】

デジタル入力信号をm個のデジタル信号に変換するプロセッサと、前記プロセッサが変換したm個のデジタル信号をシリアル伝送されるデジタル信号に変換するパラレル・シリアル変換器と、

前記パラレル・シリアル変換器により変換されたデジタル信号をm個のデジタル信号に変換し復元するシリアル・パラレル変換器と、

前記シリアル・パラレル変換器により復元されたm個のデジタル信号を受け取り、s個の駆動素子を駆動してアナログ音声に変換する駆動回路と

を有し、

前記プロセッサは、前記プロセッサを、前記駆動素子の数sを読み取り、デジタル入力信号を変調しnビットのデジタル信号を出力する　　変調器と、前記　　変調器に接続され前記nビットのデジタル信号をミスマッチシェーピングしm個のデジタル信号に変換する後置フィルターとして、動作させるためのプログラムにより、制御されることを特徴とするデジタル音響システム。

30

【請求項7】

前記プロセッサはデジタルシグナルプロセッサである請求項6に記載のデジタル音響システム。

【請求項8】

デジタル入力信号をm個のデジタル信号に変換するプロセッサと、前記プロセッサが変換したm個のデジタル信号をシリアル伝送されるデジタル信号に変換するパラレル・シリアル変換器と、

40

前記パラレル・シリアル変換器により変換されたデジタル信号をm個のデジタル信号に変換し復元するシリアル・パラレル変換器と、

前記シリアル・パラレル変換器により復元されたm個のデジタル信号を受け取り、s個の駆動素子を駆動してアナログ音声に変換する駆動回路と

を有し、

前記プロセッサは、前記プロセッサを、デジタル入力信号を変調しnビットのデジタル信号を出力する　　変調器と、前記　　変調器に接続され前記nビットのデジタル信号をミスマッチシェーピングしm個のデジタル信号に変換する後置フィルターとして、動作させるためのプログラムにより、制御され、

50

前記パラレル・シリアル変換器の出力する信号の個数は、前記パラレル・シリアル変換器に入力される信号の個数より小さく、前記パラレル・シリアル変換器の出力する信号は、前記シリアル・パラレル変換器での復調に必要な情報を含むデジタル音響システム。

【請求項 9】

デジタル入力信号を、 $s$ 個の駆動素子を駆動してアナログ音声に変換するための $m$ 個のデジタル信号に変換するデジタルシグナルプロセッサと、

前記デジタルプロセッサが変換した $m$ 個のデジタル信号のフォーマットを変換して記憶媒体に記憶するフォーマット変換器とを有し、

前記デジタルシグナルプロセッサは、前記プロセッサを、前記駆動素子の数 $s$ を読み取り、デジタル入力信号を変調し $n$ ビットのデジタル信号を出力する変調器と、前記

10

変調器に接続され前記 $n$ ビットのデジタル信号をミスマッチシェーピングし $m$ 個のデジタル信号に変換して出力する後置フィルターとして、動作させるためのプログラムにより、制御されることを特徴とするデジタル信号出力装置。

【請求項 10】

前記フォーマット変換器によるフォーマットの変換は可逆変換である請求項 9 に記載のデジタル信号出力装置。

【請求項 11】

前記フォーマット変換器によるフォーマットの変換はデータ圧縮を含む請求項 9 に記載のデジタル信号出力装置。

【請求項 12】

前記後置フィルターは、記憶媒体又は伝送路に出力を行う請求項 9 から 11 のいずれかに記載の信号出力装置。

20

【請求項 13】

デジタル入力信号を変調する変調器の出力をミスマッチシェーピングする後置フィルターが output したデジタル信号を記憶した記録媒体から前記デジタル信号を読み取り、駆動素子を駆動してアナログ音声に変換する駆動回路を有し、

前記記録媒体が記憶するデジタル信号には、前記駆動回路の駆動素子の数が含まれるデジタル再生装置。

【請求項 14】

前記記録媒体が記憶するデジタル信号には、電子透かしデータが重畠されたデータを記憶することを特徴とする請求項 13 に記載のデジタル再生装置。

30

【請求項 15】

電子透かしデータは、前記アナログ音声の帯域外のデータとして重畠されることを特徴とする請求項 14 に記載のデジタル再生装置。

【請求項 16】

デジタル入力信号を変調する変調器の出力をミスマッチシェーピングする後置フィルターが output したデジタル信号を受信し、駆動素子を駆動してアナログ音声に変換する駆動回路を有し、

前記受信されるデジタル信号には、前記駆動回路の駆動素子の数が含まれるデジタル再生装置。

40

【請求項 17】

前記受信されるデジタル信号には、電子透かしデータが重畠されたデータを記憶することを特徴とする請求項 16 に記載のデジタル再生装置。

【請求項 18】

電子透かしデータは、前記アナログ音声の帯域外のデータとして重畠されることを特徴とする請求項 17 に記載のデジタル再生装置。

【請求項 19】

$s$ 個の駆動素子を駆動してアナログ音声に変換する駆動回路に受け取られるデジタル信号を出力するデジタル信号出力装置であり、

前記駆動素子の数 $s$ を読み取り、デジタル入力信号を変調し、当該変調により

50

得られたnビットのデジタル信号をミスマッチシェーピングしm個のデジタル信号に変換する変調器を有し、

前記m個のデジタル信号は、前記駆動回路に受け取られ、前記駆動回路において前記s個の駆動素子を駆動してアナログ音声に変換されるデジタル信号出力装置。

【請求項 2 0】

s個の駆動素子を駆動してアナログ音声に変換する駆動回路に受け取られるデジタル信号を出力するデジタル信号出力装置であり、

デジタル入力信号をm個のデジタル信号に変換するプロセッサを有し、

前記プロセッサは、前記プロセッサを、前記駆動素子の数sを読み取り、デジタル入力信号を変調しnビットのデジタル信号を出力する 10 变調器と、前記 变調器に接続され前記nビットのデジタル信号をミスマッチシェーピングしm個のデジタル信号に変換する後置フィルターとして、動作させるためのプログラムにより、制御され、

前記m個のデジタル信号は、前記駆動回路に受け取られ、前記駆動回路において前記s個の駆動素子を駆動してアナログ音声に変換されるデジタル信号出力装置。

【請求項 2 1】

デジタル入力信号をm個のデジタル信号に変換するプロセッサと、

前記プロセッサが変換したm個のデジタル信号をシリアル伝送されるデジタル信号に変換するパラレル・シリアル変換器と、

を有し、

前記プロセッサは、前記プロセッサを、デジタル入力信号を変調しnビットのデジタル信号を出力する 20 变調器と、前記 变調器に接続され前記nビットのデジタル信号をミスマッチシェーピングしm個のデジタル信号に変換する後置フィルターとして、動作させるためのプログラムにより、制御され、

前記パラレル・シリアル変換器の出力する信号の個数は、前記パラレル・シリアル変換器に入力される信号の個数より小さく、前記パラレル・シリアル変換器の出力する信号は、前記パラレル・シリアル変換器により変換されたデジタル信号をm個のデジタル信号に変換し復元するシリアル・パラレル変換器での復調に必要な情報を含むデジタル信号出力装置。

10

20

30

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、デジタル信号をアナログ音声に直接変換するデジタルスピーカー装置を使ったデジタル音響システム及びそのアプリケーションなどに関する。

【背景技術】

【0 0 0 2】

デジタル信号をアナログ音声に直接変換するデジタルスピーカー技術が提案されている (例えは、特許文献1参照。)。

40

【0 0 0 3】

特許文献1のFig. 22には、X (L) およびY (R) の二つのデジタル音声信号を入力とし、 变調器とミスマッチシェーピングフィルター回路により複数のデジタル信号を出力する回路と、前記複数のデジタル信号により駆動される複数のスピーカーもしくは複数の駆動素子とにより、アナログ音声を直接変換する方法が示されている。

【0 0 0 4】

このような、デジタル信号をアナログ音声に直接変換するデジタルスピーカー技術を用いたデジタルスピーカー装置は、アナログ電気信号により駆動されていたアナログスピーカー装置に比べて、消費電力が小さいという特徴がある。また、これに加えて、このようなデジタルスピーカー装置は、複数のスピーカー素子もしくは複数の駆動素子 (コイル等

50

) を使うことから、従来の一つのスピーカー素子もしくは単一の駆動素子を使ったスピーカーに比べて、大きな音を出すことが可能である。

【 0 0 0 5 】

しかしながら、デジタルスピーカー装置ではPCM音源からのデジタル信号を 变調器とミスマッチシェーピングフィルター回路により複数のデジタル信号を出力する回路が必須であり、これらの回路をLSI上に実装する為には微細デジタルプロセスを使う必要がある。

【 0 0 0 6 】

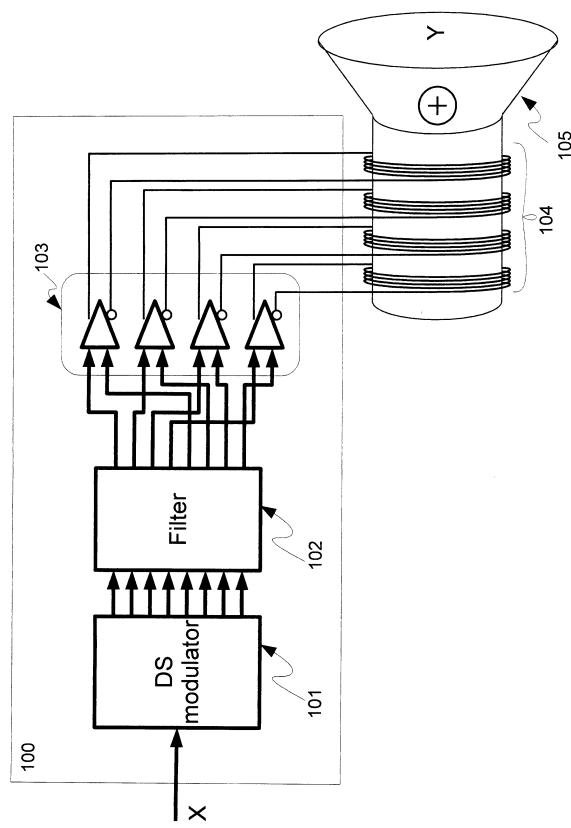

図1に、従来のデジタルスピーカー装置を使ったデジタル音響システムの代表的な例として、デジタルスピーカー装置のシステムの従来例を示す。この従来例のデジタルスピーカー装置のシステムは、 变調器と後置フィルター回路により複数のデジタル信号を出力する回路と複数のスピーカー駆動素子からなる。1ビットのデジタル入力信号(110)は

変調器(101)に入力される、 变調器(101)でnビットの複数のデジタル信号(111)に変換する。nビットの複数のデジタル信号は後置フィルター(102)でミスマッチシェーピングされたm個のデジタル信号(112)に変換される。m個のデジタル信号は、スピーカー駆動回路(103)に入力されs個の駆動素子(104)を駆動してアナログ音声を振動膜(105)により直接変換する。前記 变調器(101)と後置フィルター(102)とスピーカー駆動回路(103)とがデジタルスピーカー装置(100)の構成要素である。

【先行技術文献】

【特許文献】

【 0 0 0 7 】

【特許文献1】国際公開第2007/135928号

【発明の概要】

【発明が解決しようとする課題】

【 0 0 0 8 】

従来例では、 变調器(101)と後置フィルター(102)とスピーカー駆動回路(103)とがスピーカー毎に必要になるので、多数のスピーカーが用いられる映画館や劇場にデジタルスピーカー装置を使う場合に微細デジタルプロセスのLSIを多数必要とする課題がある。

【課題を解決するための手段】

【 0 0 0 9 】

本発明は、デジタル信号により駆動される複数のスピーカー(コイル)によりアナログ音声を直接変換するデジタルスピーカー装置に最適なデジタル音響システムを提案することを目的とする。

【 0 0 1 0 】

本発明の一実施形態として、デジタル入力信号を変調しnビットのデジタル信号を出力する 变調器と、前記 变調器に接続され前記nビットのデジタル信号をミスマッチシェーピングしm個のデジタル信号に変換する後置フィルターと、前記後置フィルターが変換したm個のデジタル信号をシリアル伝送されるデジタル信号に変換するパラレル・シリアル変換器と、前記パラレル・シリアル変換器により変換されたデジタル信号をm個のデジタル信号に変換し復元するシリアル・パラレル変換器と、前記シリアル・パラレル変換器により復元されたm個のデジタル信号を受け取り、s個の駆動素子を駆動してアナログ音声に変換する駆動回路とを有するデジタル音響システムを提供する。

【 0 0 1 1 】

本発明の一実施形態として、デジタル入力信号をm個のデジタル信号に変換するプロセッサと、前記プロセッサが変換したm個のデジタル信号をシリアル伝送されるデジタル信号に変換するパラレル・シリアル変換器と、前記パラレル・シリアル変換器により変換されたデジタル信号をm個のデジタル信号に変換し復元するシリアル・パラレル変換器と、

前記シリアル・パラレル変換器により復元されたm個のデジタル信号を受け取り、s個の駆動素子を駆動してアナログ音声に変換する駆動回路とを有し、前記プロセッサは、前記プロセッサを、デジタル入力信号を変調しnビットのデジタル信号を出力する 变調器

10

20

30

40

50

と、前記 变調器に接続され前記nビットのデジタル信号をミスマッチシェーピングしm個のデジタル信号に変換する後置フィルターとして、動作させるためのプログラムにより、制御されることを特徴とするデジタル音響システムを提供する。

【発明の効果】

【0012】

本発明によれば、デジタルスピーカーの特性として、低消費電力特性を損なうことなく、多数のスピーカーを使う用途である映画館や劇場にデジタルスピーカー装置を使う場合でも、従来のデジタル音響システムに比べ単純な装置の組み合わせでデジタル音響システムを構築することが出来るため、デジタル音響システムのコストの低減が可能になる。

【図面の簡単な説明】

10

【0013】

【図1】従来のデジタル音響システムの構成の一例図

【図2】本発明の第1の実施形態に係るデジタル音響システムの構成図

【図3】本発明の第2の実施形態に係るデジタル音響システムの構成図

【図4】本発明の第3の実施形態に係るデジタル音響システムの構成図

【図5】本発明の第4の実施形態に係るデジタル音響システムの構成図

【図6】本発明の第5の実施形態に係るデジタル音響システムの構成図

【図7】本発明の第6の実施形態に係るデジタル音響システムの構成図

【図8】本発明の第7の実施形態に係るデジタル音響システムの構成図

【図9】本発明の第8の実施形態に係るデジタル音響システムの構成図

20

【発明を実施するための形態】

【0014】

(第1の実施形態)

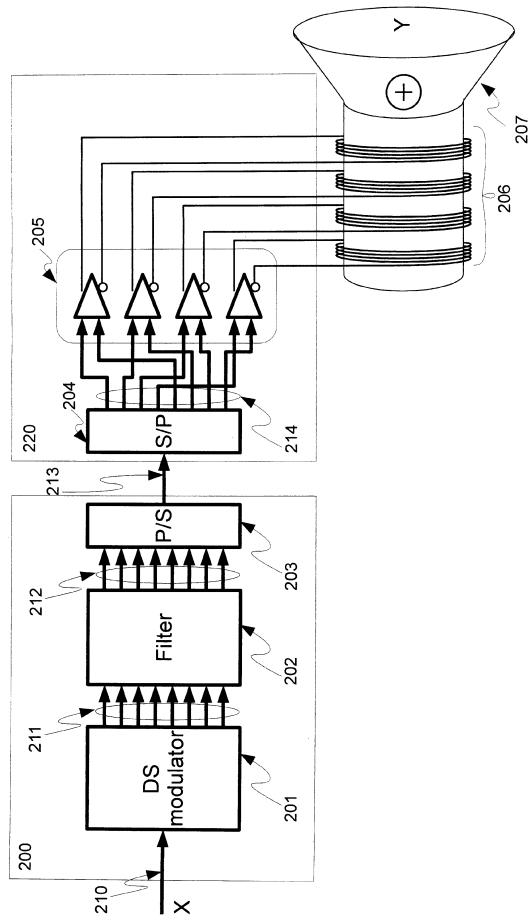

図2に本発明の第1の実施形態に係る、デジタルスピーカー装置を使ったデジタル音響システムの構成を示す。本実施形態に係るデジタルスピーカー装置は、デジタル信号から複数のデジタル信号を出力する装置と、この装置が出力する複数のデジタル信号により複数のスピーカー駆動素子を駆動する駆動装置で構成される。本実施形態の特徴の一つは、複数のデジタル信号を出力する装置とスピーカー駆動素子を駆動する駆動装置の間をパラレル・シリアル変換装置とシリアル・パラレル変換装置により接続する点である。

【0015】

30

図2を参照すると、デジタル入力信号(210)は 变調器(201)に入力され、 变調器(201)でnビットの複数のデジタル信号(211)に変換される。nビットの複数のデジタル信号は後置フィルター(202)でミスマッチシェーピングされたm個のデジタル信号(212)に変換される。m個のデジタル信号は、パラレル・シリアル変換器(203)でシリアル伝送されるデジタル信号(213)に変換され、シリアル・パラレル変換器(204)でm個のデジタル信号(214)に戻される。シリアル伝送されるデジタル信号(213)のビット数としては例えば1を挙げができるが、1に限定はされない。m個のデジタル信号(214)を受け取ったスピーカー駆動回路(205)はs個の駆動素子(206)を駆動してアナログ音声を振動膜(207)により直接変換する。ここで、 变調器(201)と後置フィルター(202)とパラレル・シリアル変換器(203)とがデジタル信号から複数のデジタル信号を出力する装置(200)を構成している。また、シリアル・パラレル変換器(204)とスピーカー駆動回路(205)とがスピーカー駆動素子を駆動する駆動装置(220)を構成している。

40

【0016】

本実施形態のように、入力されたデジタル信号から複数のデジタル信号を出力する装置と、スピーカー駆動素子を駆動する駆動装置をシリアル信号で結ぶことになると、デジタル信号から複数のデジタル信号を出力する装置に対して複数のスピーカー駆動素子を駆動する駆動装置をシリアル信号で接続する事が可能になる。したがって、多数のスピーカーを使う例えば映画館や劇場にデジタルスピーカー装置を使う場合でも、従来のデジタル音響システムに比べ単純な装置の組み合わせでデジタル音響システムを構築することが出来る。これにより、デジタル音響システムのコストの低減が可能になる。

50

## 【0017】

図2に示す第1の実施形態に係る構成の一例として、デジタル信号から複数のデジタル信号を出力する装置と、スピーカー駆動素子を駆動する駆動装置を電気的にシリアル信号で結ぶ例が示されている。しかし、本実施形態は、この例に限定されることはなく、シリアル信号を無線装置で接続したり、光信号で接続したりするなど、電磁誘導や電界の強度により伝送する構成も本実施形態に含まれる。また、図2に示したパラレル・シリアル変換器(203)で、パラレル信号(212)を、複数のシリアル信号に変換する実施例も含まれる。

## 【0018】

また、スピーカー駆動素子を駆動する駆動装置をデジタル信号から複数のデジタル信号を出力する装置に分けることで、それぞれの装置に最適なデバイステクノロジーを用いてLSI化を進めることが可能になる。これにより、システム全体のコストを低減することや、スピーカー駆動素子を駆動する駆動装置側の動作電圧を上げることができる。したがって、大音量を再生することもコストの増大を伴わずに容易に構成することが可能になる。

10

## 【0019】

## (第2の実施形態)

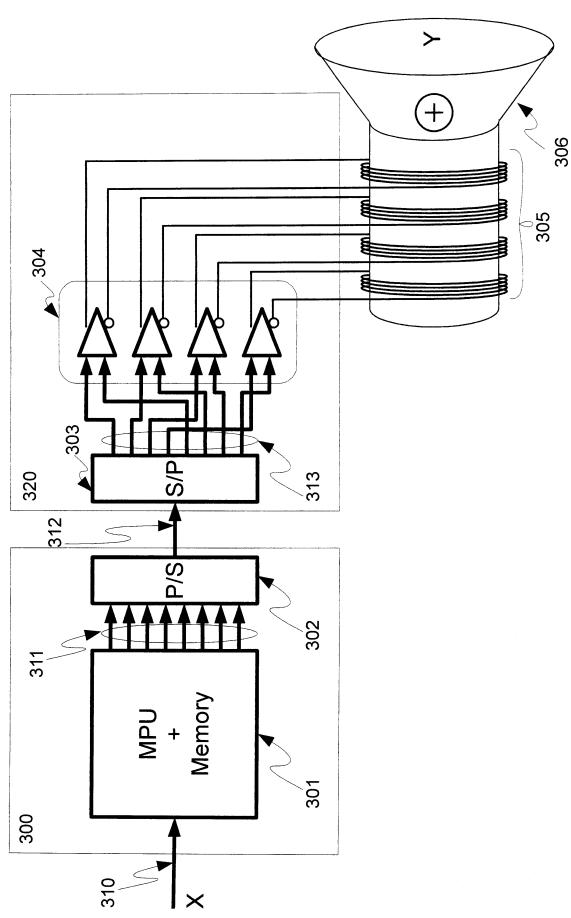

図3に、本発明の第3の実施形態に係る、複数のデジタル信号を出力する回路と複数のスピーカー駆動素子とを備えるデジタルスピーカー装置の構成を示す。デジタル入力信号(310)はマイクロコンピューター装置(301)に入力されミスマッチシェーピングされたm個のデジタル信号(311)に変換される。m個のデジタル信号は、パラレル・シリアル変換器(302)で1ビットのデジタル信号(312)に変換され、シリアル・パラレル変換器(303)でm個のデジタル信号(313)に戻される。m個のデジタル信号(214)を受け取ったスピーカー駆動回路(304)はs個の駆動素子(305)を駆動してアナログ音声を振動膜(306)により直接変換する。

20

## 【0020】

ここで、マイクロコンピューター装置(301)とパラレル・シリアル変換器(302)が、デジタル信号から複数のデジタル信号を出力する装置(300)を構成し、シリアル・パラレル変換器(303)とスピーカー駆動回路(304)とが駆動装置(320)を構成している。駆動装置(320)において、スピーカー駆動素子が駆動される。マイクロコンピューター装置(301)は、プロセッサを有し、プロセッサは、デジタル入力信号を変調しnビットのデジタル信号を出力する変調器と、変調器に接続されnビットのデジタル信号をミスマッチシェーピングしm個のデジタル信号に変換する後置フィルターとして、動作させるためのプログラムにより、制御される

30

## 【0021】

本実施形態のように、入力されたデジタル信号から複数のデジタル信号を出力する装置として、プロセッサを有するマイクロコンピューター装置を用いることで、第1の実施形態の変調器と後置フィルターで行った事と同様のデジタル信号処理を、プログラムで処理することが可能になる。プログラムで処理することで変調器の変調特性や後置フィルターでのフィルター特性をハードウェアの変更無しに更新し改良する事が可能になる。

40

## 【0022】

## (第3の実施形態)

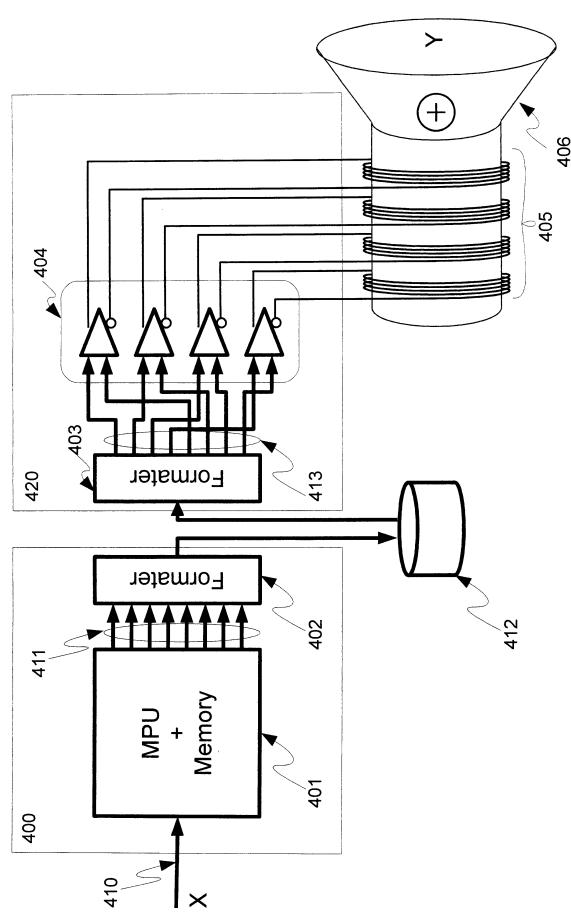

図4に複数のデジタル信号を出力する回路と複数のスピーカー駆動素子からなるデジタルスピーカー装置のシステム形態の第3の実施形態を示す。デジタル入力信号(410)はマイクロコンピューター装置(401)に入力されミスマッチシェーピングされたm個のデジタル信号(411)に変換される。m個のデジタル信号は、フォーマット変換器(402)で記憶装置(312)に一度記録され、再度フォーマット変換器(403)でm個のデジタル信号(413)に戻される。なお、フォーマット変換器(402)の出力をパラレル・シリアル変換器によりシリアル伝送されるデジタル信号に変換し、記憶装置(312)にデジタル信号を記憶してもよい。また、記憶装置(312)から読み出されたデジタル信号は、シリアル・パラレル変換器に入力さ

50

れ、フォーマット変換器(403)に入力されてもよい。また、フォーマット変換器(402)がパラレル・シリアル変換器を含み、フォーマット変換器(403)がシリアル・パラレル変換器を含む構成でもよい。

【0023】

前記m個のデジタル信号(414)を受け取ったスピーカー駆動回路(404)はs個の駆動素子(405)を駆動してアナログ音声を振動膜(406)により直接変換する。ここで、マイクロコンピューター装置(401)とフォーマット変換器(402)とが、デジタル信号から複数のデジタル信号を出力する装置(400)を構成している。また、フォーマット変換器(403)とスピーカー駆動回路(404)とがスピーカー駆動素子を駆動する駆動装置(420)を構成している。

【0024】

第3の実施形態のようにデジタル信号から複数のデジタル信号を出力する装置と、スピーカー駆動素子を駆動する駆動装置を記憶装置で結ぶことが可能になると、音声再生の実時間処理が出来ない、例えば処理速度の遅いマイクロコンピューター装置を用いても、第1の実施形態の変調器と後置フィルターで行った事と同様のデジタル信号処理をプログラムで処理することが可能になるので、従来のデジタル音響システムに比べ、より低消費電力のデジタル音響システムが可能になる。

【0025】

また、デジタル信号処理をプログラムで処理した結果を複数回再生する場合には、記憶装置から事前に計算した結果を読みだすだけでよいので、再計算を行う必要がなくなるので、従来のデジタル音響システムに比べ、より低消費電力のデジタル音響システムが可能になる。

【0026】

また、フォーマット変換器(402)では、ミスマッチシェーピングされたm個のデジタル信号に対しロスレスデータ圧縮を行うことも可能である。フォーマット変換器(403)では、データの伸張を行い元のm個のデジタル信号を再生する。このようにデータを圧縮することで必要な記憶媒体の容量を大幅に低減することが可能となる。ここで、データの圧縮伸張方法には、演算量およびデータ圧縮率を勘案し選択することで記憶媒体およびハードウェア規模の最適を図ることも可能となる。

【0027】

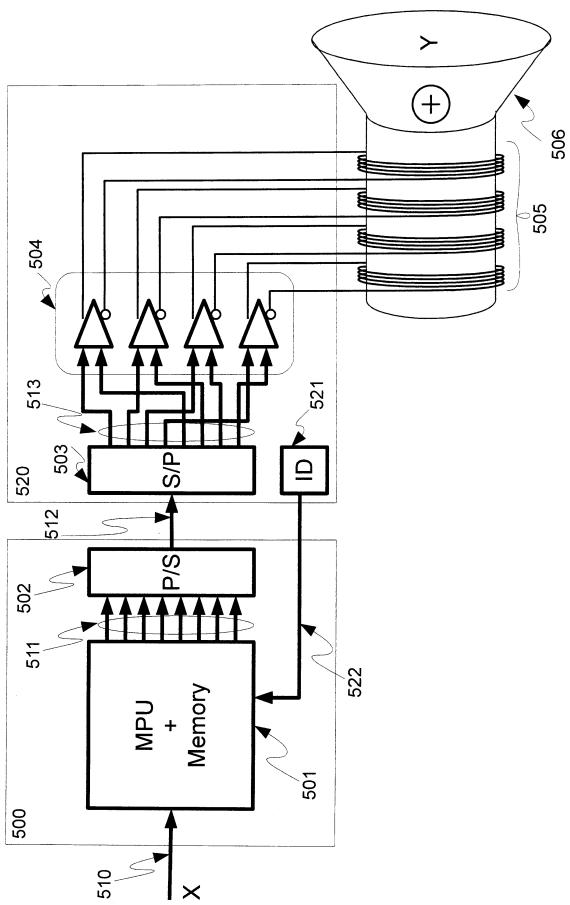

(第4の実施形態)

図5に複数のデジタル信号を出力する回路と複数のスピーカー駆動素子からなるデジタルスピーカー装置のシステム形態の第4の実施形態を示す。デジタル入力信号(510)はマイクロコンピューター装置(501)に入力されミスマッチシェーピングされたm個のデジタル信号(511)に変換される。m個のデジタル信号は、パラレル・シリアル変換器(502)で、シリアル伝送される例えば1ビットのデジタル信号(512)に、一旦変換され、再度シリアル・パラレル変換器(503)でm個のデジタル信号(513)に戻される。前記m個のデジタル信号(514)を受け取ったスピーカー駆動回路(504)はs個の駆動素子(505)を駆動してアナログ音声を振動膜(506)により直接変換する。ここで、マイクロコンピューター装置(501)とパラレル・シリアル変換器(502)とが、デジタル信号から複数のデジタル信号を出力する装置(500)を構成している。また、シリアル・パラレル変換器(503)とスピーカー駆動回路(504)とがスピーカー駆動素子を駆動する駆動装置(520)を構成している。更に駆動装置(520)はスピーカー駆動回路の個数や特性を記憶したID素子(521)を備え、そのID素子からの情報を、複数のデジタル信号を出力する装置(500)に伝える伝送手段(522)を設置する。伝送手段(522)は、マイクロコンピューター装置(501)にID素子(521)からの情報を伝送する。

【0028】

本実施形態のようにデジタル信号から複数のデジタル信号を出力する装置にマイクロコンピューター装置を用いることにより、第1の実施形態の変調器と後置フィルターで行った事と同様のデジタル信号処理をプログラムで処理することが可能になる。さらに、駆動装置(520)の情報を利用することで、駆動回路の個数や特性に適合するデジタル信号処理をプログラムにより対応することが可能になるので、異なる駆動装置を一つの複数の

10

20

30

40

50

デジタル信号を出力する装置に接続することが可能になる。

【0029】

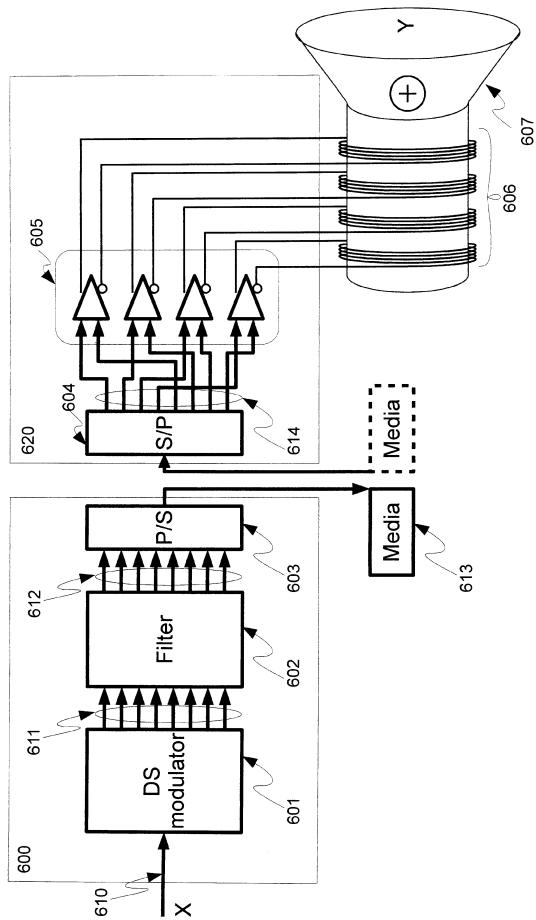

(第5の実施形態)

図6に複数のデジタル信号を出力する回路と複数のスピーカー駆動素子からなるデジタルスピーカー装置のシステム形態の第5の実施形態を示す。図4に示した第3の実施形態と同じように、あらかじめ複数のスピーカー駆動素子を駆動する信号をデジタル信号から複数のデジタル信号を出力する装置(600)により生成して保存メディア(記憶媒体)(613)に保存しておくことが可能である。これにより変換されたデータを、保存メディア(613)を使って流通させることが可能となる。このあらかじめ変換されたデータをネットワークを通じて直接顧客に配信したり、あらかじめ変換されたデータを保存メディア(記憶媒体)に記録し流通させたりすることにより、従来必要であったフォーマッタ変換器(602)を、再生する装置側で用意する必要がなくなり、デジタルスピーカー装置をより廉価に提供することが可能となる。

【0030】

保存メディア(記憶媒体)としては、光ディスク、メモリカードなどの媒体を挙げることができる。これらの媒体は、記憶装置に着脱することができるものであることが好ましい。したがって、これらの光ディスク、メモリカードは据え置き型や携帯型の再生装置としての駆動装置(620)に装着して再生を行ってもよい。また、ネットワークを通じて直接顧客に配信する場合には、ストリーム形式で配信を行ったり、顧客の有する保存メディア(記憶媒体)に配信したデータを一旦記録したりしてもよい。

【0031】

また、あらかじめいくつかの駆動素子数に対応させたデータを生成し、記録することで駆動素子数の異なるデジタルスピーカシステムに対応させることも可能である。この方法は、特に記録媒体の記録密度が上がり単価が低い場合にはコストを低減できる有効な手段となる。

【0032】

また、複数のスピーカー駆動素子を駆動する信号をデジタル信号から複数のデジタル信号を出力する装置(600)からの出力は、デジタル変調されている為に、変調前のデジタル信号に戻すことが困難となる場合がある。したがって、装置(600)からの出力に、コピー・プロテクトされたに等しい効果を持たせることができる。さらにセキュリティ度を増す為に、前記記憶媒体に記録する際に暗号化を施したり、電子透かしデータを重畳したりすることも可能である。変調器(601)を用いているため、音楽信号等の信号帯域以外の帯域(通常信号帯域以上の周波数帯域)に、電子透かし信号を挿入することにより、最終的に音響信号に変換された際の音質の劣化を最小限に電子透かしを用いることが可能となる。暗号化や電子透かしデータの重畳は、例えば変調器(601)、後置フィルター(602)またはパラレル・シリアル変換器(603)に実行させることができる。例えば、変調器(601)、後置フィルター(602)またはパラレル・シリアル変換器(603)に、暗号化や電子透かしデータの重畳のための装置を備えてもよい。また、そのような装置は、独立した装置であってもよい。

【0033】

さらに、用いるコイル数を変更できるデータを記録媒体等に記録することにより、1通りのデータのみを記録することで、複数のコイル数に対応させることが可能となり、利便性を向上させることも可能である。

【0034】

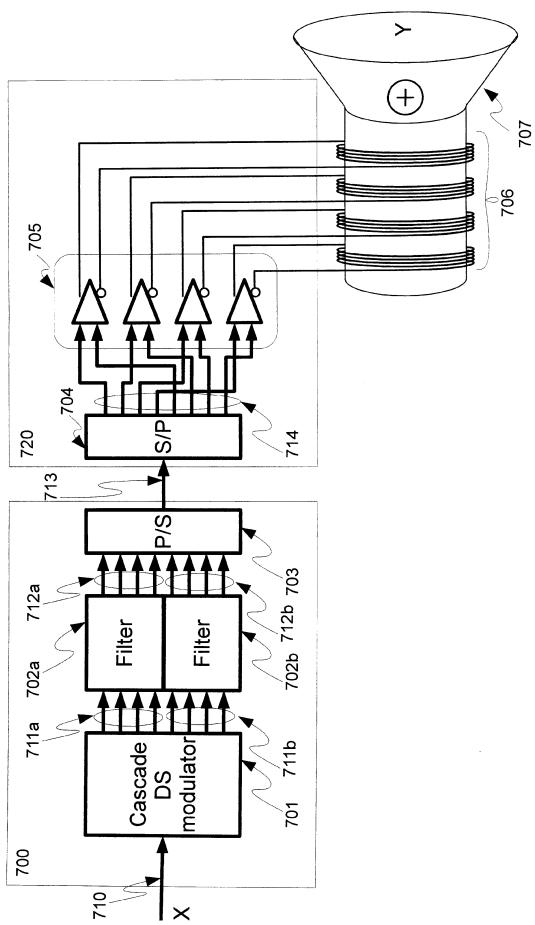

(第6の実施形態)

実施形態1から5における変調器にカスコード型変調器を用いることも可能である。図7にカスコード型変調器の内部量子化器に多ビットのものを用いた場合の実施形態を示す。カスコード型変調器(701)では、初段および2段目以降の複数の内部変調器が outputされる。初段の  $n_1$  ビットの複数のデジタル信号(711a)は後置フィルター(702a)でミスマッチシェーピングされた  $m_1$  個のデジタル信号(712a)に変換される。2段目以

10

20

30

40

50

降の $n_x$ 出力(711b)には後置フィルタ(702b)で周波数特性を付加し、さらにミスマッチシェーピングされた $m_x$ 個のデジタル信号(712b)に変換される。

【0035】

$m_1 + m_2 + \dots + m_x$ 個のデジタル信号は、パラレル・シリアル変換器(703)で1ビットのデジタル信号(713)に一旦変換され、再度シリアル・パラレル変換器(704)で $m_1 + m_2 + \dots + m_x$ 個のデジタル信号(714)に戻される。前記 $m_1 + m_2 + \dots + m_x$ 個のデジタル信号(714)を受け取ったスピーカー駆動回路(705)はs個の駆動素子(706)を駆動してアナログ音声を振動膜(707)により直接変換する。ここで、カスコード型変調器(701)と後置フィルター(702a、b)とパラレル・シリアル変換器(703)とがデジタル信号から複数のデジタル信号を出力する装置(700)を構成している。また、シリアル・パラレル変換器(704)とスピーカー駆動回路(705)とがスピーカー駆動素子を駆動する駆動装置(720)を構成している。 10

【0036】

カスケード型DACと同様に、2段目以降の出力は1段目出力に含まれる雑音成分を打ち消す符号となっている。このため、駆動素子(606)が $m_1 + m_2 + \dots + m_x$ よりも少ない場合は、後段の $m_2 + \dots + m_x$ を使用しないでも十分高精度な変換を行うことが可能である。

【0037】

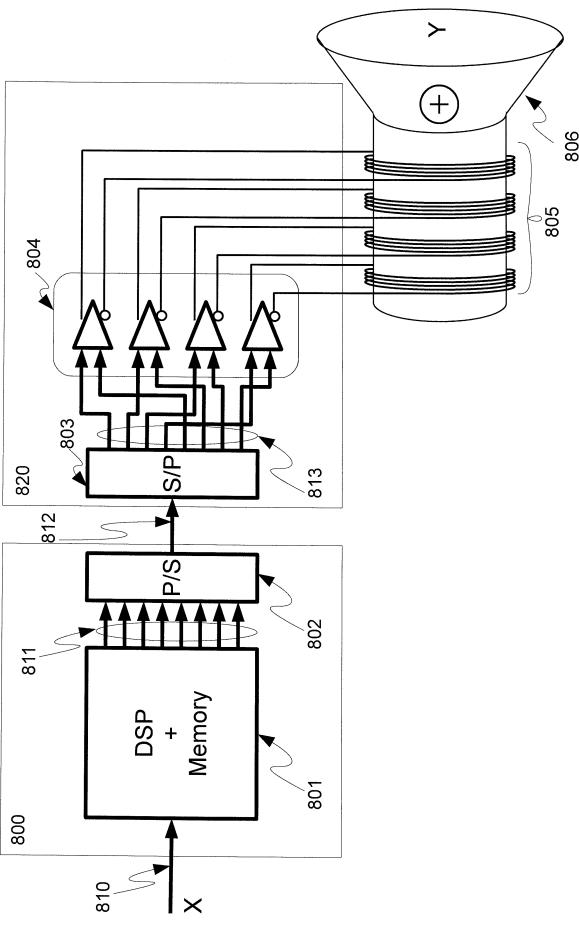

(第7の実施形態)

図8に、本発明の第7の実施形態に係る、複数のデジタル信号を出力する回路と複数のスピーカー駆動素子とを備えるデジタルスピーカー装置の構成を示す。デジタル入力信号(810)はデジタルシグナルプロセッサー装置(DSP)(801)に入力されミスマッチシェーピングされたm個のデジタル信号(811)に変換される。m個のデジタル信号(811)は、パラレル・シリアル変換器(802)でs個のデジタル信号(812)に変換され、シリアル・パラレル変換器(803)でm個のデジタル信号(813)に戻される。m個のデジタル信号(814)を受け取ったスピーカー駆動回路(804)はs個の駆動素子(805)を駆動してアナログ音声を振動膜(806)により直接変換する。 20

【0038】

パラレル・シリアル変換器(802)の入力デジタル信号の個数と出力信号の個数の関係は $s < m$ であり、s個のデジタル信号(812)にはシリアル・パラレル変換器(803)での復調に必要な情報を含んでいる。

【0039】

ここで、デジタルシグナルプロセッサー装置(801)とパラレル・シリアル変換器(802)が、デジタル信号から複数のデジタル信号を出力する装置(800)を構成し、シリアル・パラレル変換器(803)とスピーカー駆動回路(804)とが駆動装置(820)を構成している。駆動装置(820)において、スピーカー駆動素子が駆動される。 30

【0040】

本実施形態のように、入力されたデジタル信号から複数のデジタル信号を出力する装置として、デジタルシグナルプロセッサー装置を用いることで、第1の実施形態の変調器と後置フィルターで行った事と同様のデジタル信号処理を、プログラムで処理することが可能になる。プログラムで処理することで変調器の変調特性や後置フィルターでのフィルター特性をハードウェアの変更無しに更新し改良する事が可能になる。 40

【0041】

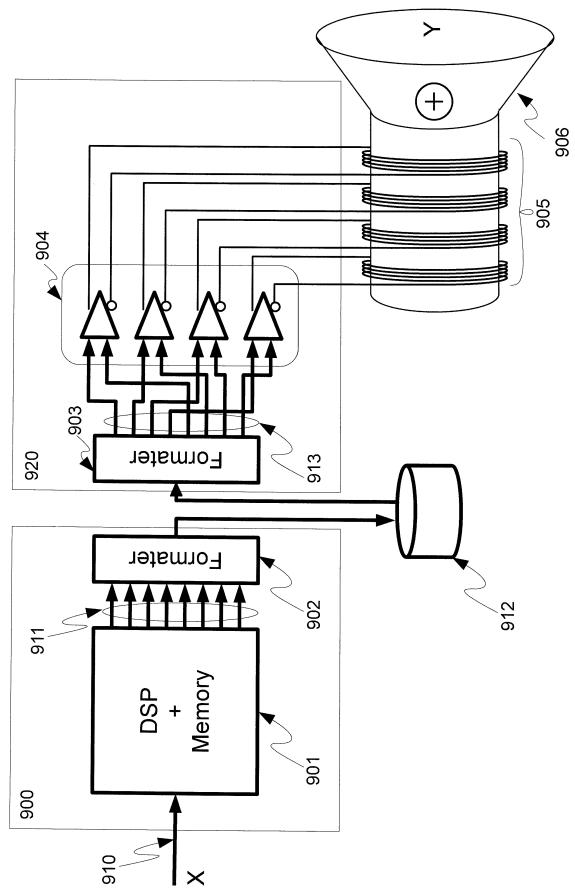

(第8の実施形態)

図9に複数のデジタル信号を出力する回路と複数のスピーカー駆動素子からなるデジタルスピーカー装置のシステム形態の第8の実施形態を示す。デジタル入力信号(910)はデジタルシグナルプロセッサー装置(マイクロコンピュータ装置)(901)に入力されミスマッチシェーピングされたm個のデジタル信号(811)に変換される。m個のデジタル信号は、フォーマット変換器(902)でフォーマットが変換されてm個のデジタル信号を表わす情報として出力される。フォーマット変換器(902)から出力されるm個のデジタル信号は、図9に示すように記憶装置(912)の記憶媒体に一度記録されてもよい。この場合、フォーマット変換器(902)によるフォーマットの変換は、記憶媒体の記憶に適したフォーマットに変 50

換することである。記憶装置(912)の記憶媒体に記録されたm個のデジタル信号を表わす情報は、再度フォーマット変換器(903)でm個のデジタル信号(913)に戻される。前記m個のデジタル信号(913)を受け取ったスピーカー駆動回路(904)はs個の駆動素子(905)を駆動してアナログ音声を振動膜(906)により直接変換する。ここで、マイクロコンピューター装置(901)とフォーマット変換器(902)とが、デジタル信号から複数のデジタル信号を出力する装置(900)を構成している。また、フォーマット変換器(903)とスピーカー駆動回路(904)とがスピーカー駆動素子を駆動する駆動装置(920)を構成している。

#### 【 0 0 4 2 】

また、フォーマット変換器(902)から出力されるm個のデジタル信号は、伝送路に出力され、伝送されてもよい。例えば、通信により送信がされ、あるいは複数の受信者に同時に放送として送信がされてもよい。送信は無線であってもよいし、有線であってもよい。この場合、受信側では、m個のデジタル信号を受信し、フォーマット変換器(903)でm個のデジタル信号(913)に戻される。以降の処理は上述した通りである。

10

#### 【 0 0 4 3 】

ここで、フォーマット変換器(902)にて変換されるフォーマットには、可逆変換可能な如何なる種類のデジタルフォーマットを利用することが出来る。

#### 【 0 0 4 4 】

第8の実施形態のようにデジタル信号から複数のデジタル信号を出力する装置と、スピーカー駆動素子を駆動する駆動装置を記憶装置や伝送路で結ぶことが可能になる。特に記憶装置を用いる場合には、音声再生の実時間処理が出来ない、例えば処理速度の遅いデジタルシグナルプロセッサ装置を用いても、第1の実施形態の変調器と後置フィルターで行った事と同様のデジタル信号処理をプログラムで処理することが可能になるので、従来のデジタル音響システムに比べ、より低消費電力のデジタル音響システムが可能になる。

20

#### 【 0 0 4 5 】

また、デジタル信号処理をプログラムで処理した結果を複数回再生する場合には、記憶装置から事前にフォーマット変調した結果を読みだすだけでよいので、フォーマット復調に必要な計算量を抑えたデジタルフォーマットを利用することで、従来のデジタル音響システムに比べ、より低消費電力のデジタル音響システムが可能になる。

#### 【 0 0 4 6 】

30

また、フォーマット変換器(902)では、ミスマッチシェーピングされたm個のデジタル信号に対しロスレスデータ圧縮を行うことも可能である。フォーマット変換器(903)では、データの伸張を行い元のm個のデジタル信号を再生する。このようにデータを圧縮することで必要な記憶媒体の容量を大幅に低減することが可能となる。ここで、データの圧縮伸張方法には、演算量およびデータ圧縮率を勘案し選択することで記憶媒体およびハードウェア規模の最適を図ることも可能となる。

#### 【 0 0 4 7 】

このように、本実施形態においては、同一のシリアル信号を用いた場合でも、デジタルスピーカユニットにおけるコイルの数を変更することが可能となる。

#### 【 0 0 4 8 】

40

特に第3および第5の実施形態においては、あらかじめデータを生成しておくが、再生側で用いるコイル数を選択できるため、複数コイル数に対応させたデータをあらかじめ用意しておく必要がなく、データ量を削減することが可能となる。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

審査官 富澤 直樹

(56)参考文献 国際公開第2011/074341 (WO, A1)

特開2005-311847 (JP, A)

特開2009-010820 (JP, A)

特開2006-197152 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04R 3/00 - 3/14

H04S 1/00 - 7/00

H03M 1/00 - 1/88