(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7349996号**

**(P7349996)**

(45)発行日 令和5年9月25日(2023.9.25)

(24)登録日 令和5年9月14日(2023.9.14)

## (51)国際特許分類

|         |                 |     |         |              |

|---------|-----------------|-----|---------|--------------|

| G 0 9 G | 3/3225(2016.01) | F I | G 0 9 G | 3/3225       |

| G 0 9 F | 9/30 (2006.01)  |     | G 0 9 F | 9/30 3 3 8   |

| G 0 9 G | 3/20 (2006.01)  |     | G 0 9 F | 9/30 3 6 5   |

| H 0 5 B | 33/12 (2006.01) |     | G 0 9 G | 3/20 6 1 1 A |

| H 1 0 K | 50/10 (2023.01) |     | G 0 9 G | 3/20 6 2 4 B |

請求項の数 6 (全46頁) 最終頁に続く

(21)出願番号 特願2020-537892(P2020-537892)

(86)(22)出願日 令和1年8月8日(2019.8.8)

(86)国際出願番号 PCT/IB2019/056741

(87)国際公開番号 WO2020/039291

(87)国際公開日 令和2年2月27日(2020.2.27)

審査請求日 令和4年7月20日(2022.7.20)

(31)優先権主張番号 特願2018-154714(P2018-154714)

(32)優先日 平成30年8月21日(2018.8.21)

(33)優先権主張国・地域又は機関

日本国(JP)

|          |                                                |

|----------|------------------------------------------------|

| (73)特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72)発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

| (72)発明者  | 楠 純慈<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内        |

| (72)発明者  | 江口 晋吾<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

| 審査官      | 村上 遼太                                          |

最終頁に続く

(54)【発明の名称】 表示装置および電子機器

**(57)【特許請求の範囲】****【請求項1】**

第1の画素と、第2の画素と、を有する表示装置であって、

前記第1の画素は、第1の発光素子を有し、

前記第2の画素は、第2の発光素子を有し、

前記第1の発光素子は、一対の電極間に一つの発光ユニットを有するシングル構造であり、

前記第2の発光素子は、一対の電極間に2以上の発光ユニットが直列に接続されたタンデム構造であり、

前記第1の画素は、第1のデータを格納する機能を有し、

前記第1の発光素子は、前記第1のデータに基づいた発光を行う機能を有し、

前記第2の画素は、第2のデータを格納する機能を有し、

前記第2の画素は、前記第2のデータに第3のデータを付加させて第4のデータを生成する機能を有し、

前記第2の発光素子は、前記第4のデータに基づいた発光を行う機能を有する表示装置。

**【請求項2】**

第1の画素と、第2の画素と、を有する表示装置であって、

前記第1の画素は、第1のトランジスタと、第2のトランジスタと、第1の容量素子と、第1の発光素子と、を有し、

前記第1のトランジスタのソースまたはドレインの一方は、前記第1の容量素子の一方

10

20

の電極と電気的に接続され、

前記第1の容量素子の一方の電極は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2のトランジスタのソースまたはドレインの一方は、前記第1の発光素子の一方の電極と電気的に接続され、

前記第2の画素は、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第2の容量素子と、第3の容量素子と、第2の発光素子と、を有し、

前記第3のトランジスタのソースまたはドレインの一方は、前記第2の容量素子の一方の電極と電気的に接続され、

前記第2の容量素子の一方の電極は、前記第3の容量素子の一方の電極と電気的に接続され、

前記第3の容量素子の他方の電極は、前記第4のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第2の容量素子の一方の電極は、前記第5のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソースまたはドレインの一方は、前記第2の発光素子の一方の電極と電気的に接続され、

前記第1の発光素子は、一対の電極間に一つの発光ユニットを有するシングル構造であり、

前記第2の発光素子は、一対の電極間に2以上の発光ユニットが直列に接続されたタンデム構造である表示装置。

### 【請求項3】

請求項1または請求項2において、

前記第1の発光素子は、赤色または緑色の光を発し、

前記第2の発光素子は、青色または白色の光を発する表示装置。

### 【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記第1の発光素子の他方の電極および前記第2の発光素子の他方の電極は、透光性導電膜であり、

前記透光性導電膜は、前記第1の発光素子および前記第2の発光素子と重ならない金属配線と接している表示装置。

### 【請求項5】

請求項2において、

前記第1のトランジスタ乃至第5のトランジスタは、チャネル形成領域に金属酸化物を有し、

前記金属酸化物は、Inと、Znと、M(MはAl、Ti、Ga、Sn、Y、Zr、La、Ce、NdまたはHf)と、を有する表示装置。

### 【請求項6】

請求項1乃至請求項5のいずれか一項に記載の表示装置と、カメラと、を有する電子機器。

## 【発明の詳細な説明】

### 【技術分野】

### 【0001】

本発明の一態様は、表示装置に関する。

### 【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物(コンポジション・オブ・マター)に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、液晶表示装置、発光装置、照明装

10

20

30

40

50

置、蓄電装置、記憶装置、撮像装置、それらの駆動方法、または、それらの製造方法、を一例として挙げることができる。

#### 【0003】

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。トランジスタ、半導体回路は半導体装置の一態様である。また、記憶装置、表示装置、撮像装置、電子機器は、半導体装置を有する場合がある。

#### 【背景技術】

#### 【0004】

基板上に形成された金属酸化物を用いてトランジスタを構成する技術が注目されている。例えば、酸化亜鉛またはIn-Ga-Zn系酸化物を用いたトランジスタを表示装置の画素のスイッチング素子などに用いる技術が特許文献1および特許文献2に開示されている。10

#### 【0005】

また、オフ電流が極めて低いトランジスタをメモリセルに用いる構成の記憶装置が特許文献3に開示されている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

【文献】特開2007-123861号公報

特開2007-96055号公報

特開2011-119674号公報20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

テレビや携帯情報端末などに用いられる表示装置には、表示部の大型化、高精細化が容易な液晶表示装置が多く用いられている。また、液晶表示装置は、3D画像、VR（仮想現実）、AR（拡張現実）などの技術を支えるための重要な要素となっている。

#### 【0008】

一方で、液晶表示装置は非発光型の表示装置であるため、光源が必要、応答速度が比較的遅い、フレキシブル化が困難などの課題を有している。これらの課題の解決には、EL表示装置への代替えが一つの手段となる。EL表示装置は自発光型の表示装置であり、光源は不要でコントラストが高く、高速応答である。また、視野角も広く、液晶素子特有のセルギャップ制御は不要であるため、フレキシブル化も可能である。30

#### 【0009】

しかしながら、EL表示装置の製造には高度な技術が必要であり、トランジスタの特性ばらつきや発光デバイス（発光素子ともいう）の信頼性などの課題を有している。

#### 【0010】

したがって、本発明の一態様では、信頼性の高いEL表示装置を提供することを目的の一つとする。または、低消費電力のEL表示装置を提供することを目的の一つとする。または、新規なEL表示装置などを提供することを目的の一つとする。または、上記EL表示装置の駆動方法を提供することを目的の一つとする。または、新規な半導体装置などを提供することを目的の一つとする。40

#### 【0011】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

#### 【課題を解決するための手段】

#### 【0012】

本発明の一態様は、信頼性の高いEL表示装置に関する。または、低消費電力化が可能なEL表示装置に関する。

10

20

30

40

50

**【 0 0 1 3 】**

本発明の一態様は、第1の画素と、第2の画素と、を有する表示装置であって、第1の画素は、第1の発光デバイスを有し、第2の画素は、第2の発光デバイスを有し、第1の発光デバイスは、一対の電極間に一つの発光ユニットを有するシングル構造であり、第2の発光デバイスは、一対の電極間に2以上の発光ユニットが直列に接続されたタンデム構造であり、第1の画素は、第1のデータを格納する機能を有し、第1の発光デバイスは、第1のデータに基づいた発光を行う機能を有し、第2の画素は、第2のデータを格納する機能を有し、第2の画素は、第2のデータに第3のデータを附加させて第4のデータを生成する機能を有し、第2の発光デバイスは、第4のデータに基づいた発光を行う機能を有する表示装置である。

10

**【 0 0 1 4 】**

本発明の他の一態様は、第1の画素と、第2の画素と、を有する表示装置であって、第1の画素は、第1のトランジスタと、第2のトランジスタと、第1のキャパシタと、第1の発光デバイスと、を有し、第1のトランジスタのソースまたはドレインの一方は、第1のキャパシタの一方の電極と電気的に接続され、第1のキャパシタの一方の電極は、第2のトランジスタのゲートと電気的に接続され、第2のトランジスタのソースまたはドレインの一方は、第1の発光デバイスの一方の電極と電気的に接続され、第2の画素は、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第2のキャパシタと、第3のキャパシタと、第2の発光デバイスと、を有し、第3のトランジスタのソースまたはドレインの一方は、第2のキャパシタの一方の電極と電気的に接続され、第2のキャパシタの一方の電極は、第3のキャパシタの一方の電極と電気的に接続され、第3のキャパシタの他方の電極は、第4のトランジスタのソースまたはドレインの一方と電気的に接続され、第2のキャパシタの一方の電極は、第5のトランジスタのゲートと電気的に接続され、第5のトランジスタのソースまたはドレインの一方は、第2の発光デバイスの一方の電極と電気的に接続され、第1の発光デバイスは、一対の電極間に一つの発光ユニットを有するシングル構造であり、第2の発光デバイスは、一対の電極間に2以上の発光ユニットが直列に接続されたタンデム構造である表示装置である。

20

**【 0 0 1 5 】**

第1の発光デバイスは、赤色または緑色の光を発し、第2の発光デバイスは、青色または白色の光を発することが好ましい。

30

**【 0 0 1 6 】**

第1の発光デバイスの他方の電極および第2の発光デバイスの他方の電極は、透光性導電膜であり、当該透光性導電膜は、第1の発光デバイスおよび第2の発光デバイスと重ならない金属配線と接していることが好ましい。

**【 0 0 1 7 】**

第1乃至第5のトランジスタは、チャネル形成領域に金属酸化物を有し、金属酸化物は、Inと、Znと、M(MはAl、Ti、Ga、Sn、Y、Zr、La、Ce、NdまたはHf)と、を有することが好ましい。

**【発明の効果】****【 0 0 1 8 】**

本発明の一態様を用いることで、信頼性の高いEL表示装置を提供することができる。または、低消費電力のEL表示装置を提供することができる。または、新規なEL表示装置などを提供することができる。または、上記EL表示装置の駆動方法を提供することができる。または、新規な半導体装置などを提供することができる。

40

**【図面の簡単な説明】****【 0 0 1 9 】**

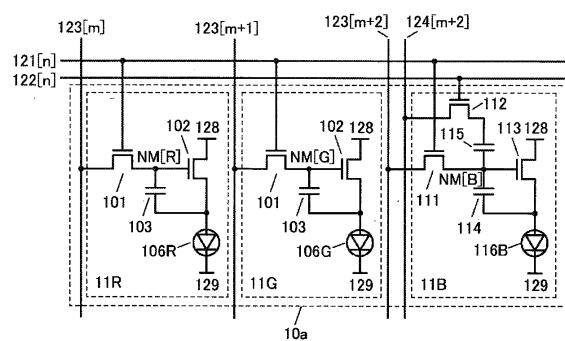

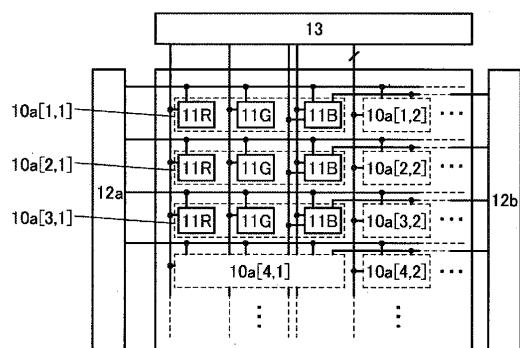

【図1】図1は、画素回路を説明する図である。

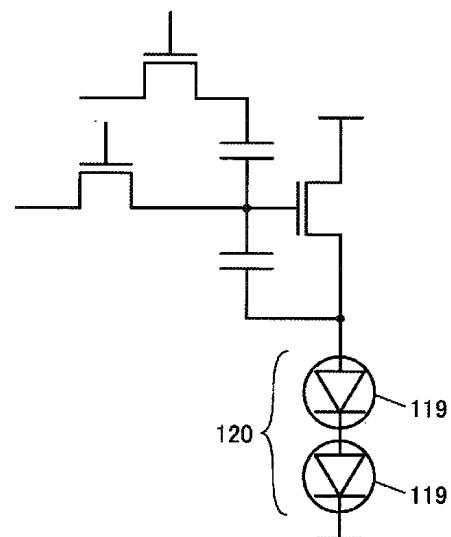

【図2】図2(A)は、発光デバイスの等価回路である。図2(B)は、電圧降下を説明する図である。

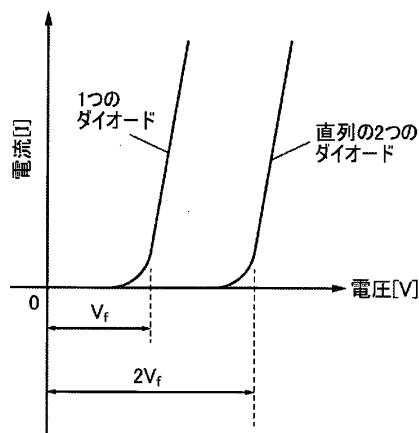

【図3】図3は、画素回路の動作を説明するタイミングチャートである。

50

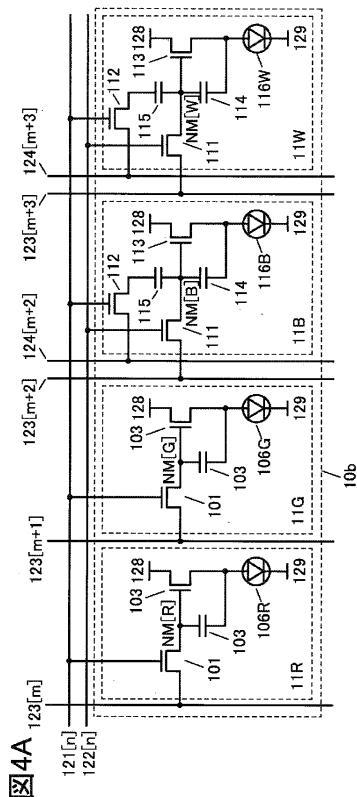

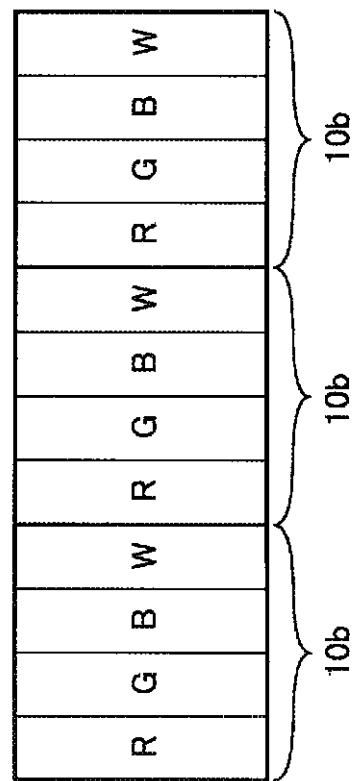

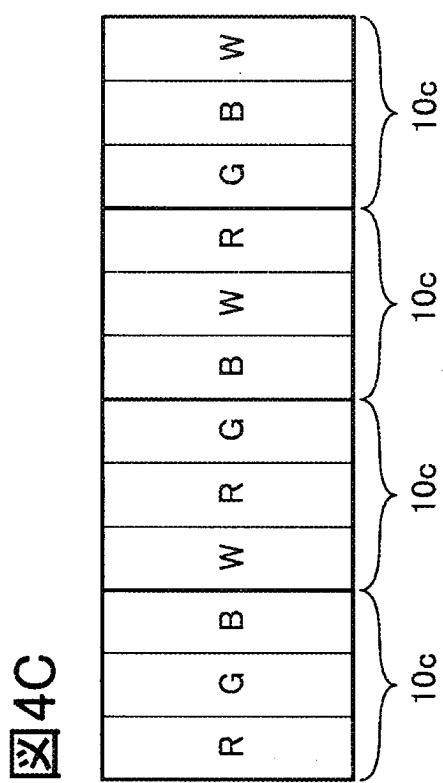

【図4】図4(A)は、画素回路を説明する図である。図4(B)、(C)は、副画素の組み合わせを説明する図である。

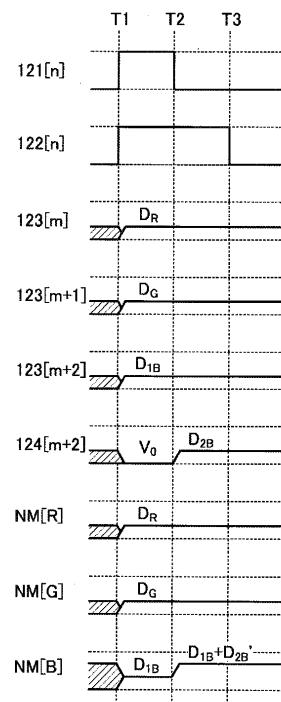

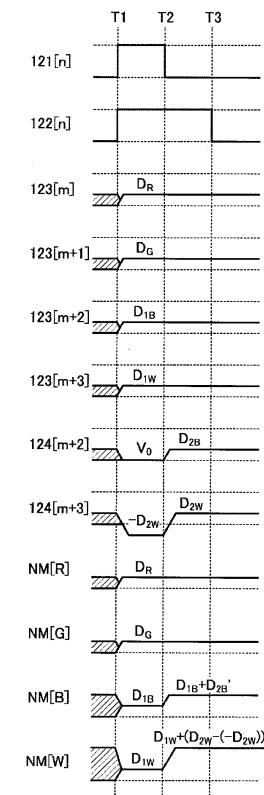

【図5】図5は、画素回路の動作を説明するタイミングチャートである。

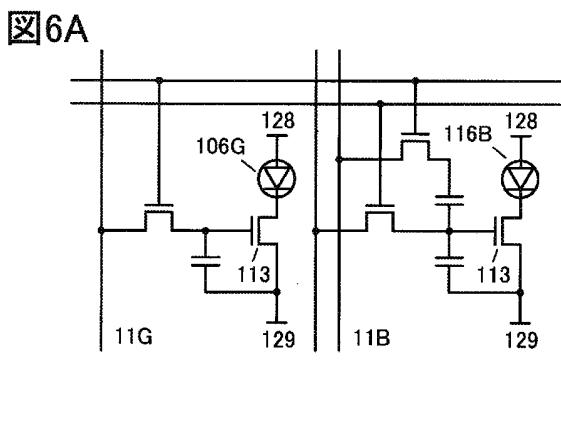

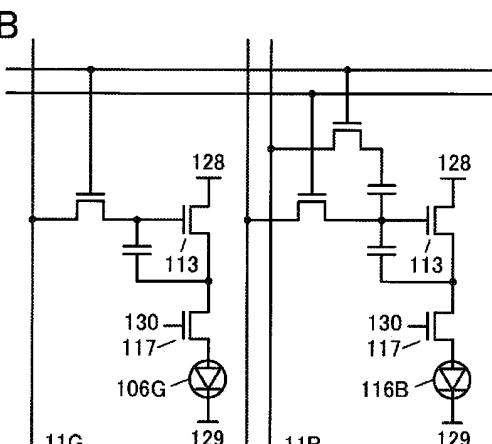

【図6】図6(A)、(B)は、画素回路を説明する図である。

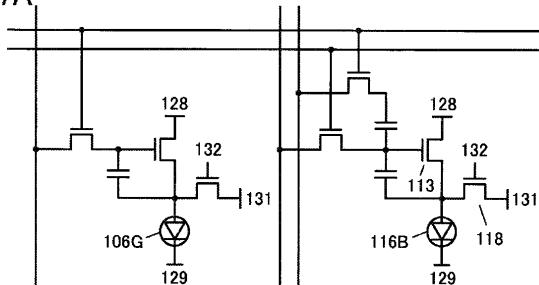

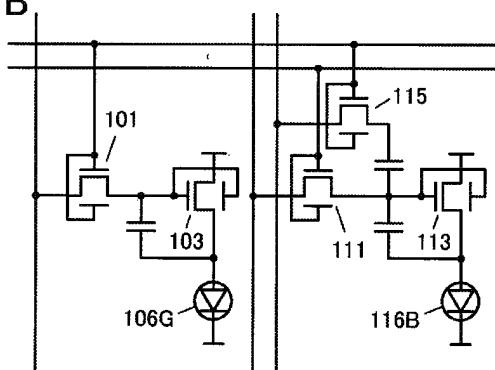

【図7】図7(A)、(B)は、画素回路を説明する図である。

【図8】図8は、表示装置を説明するブロック図である。

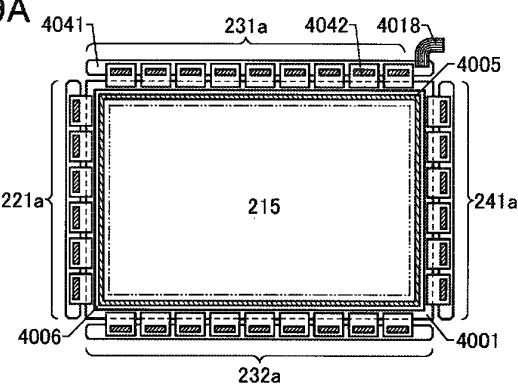

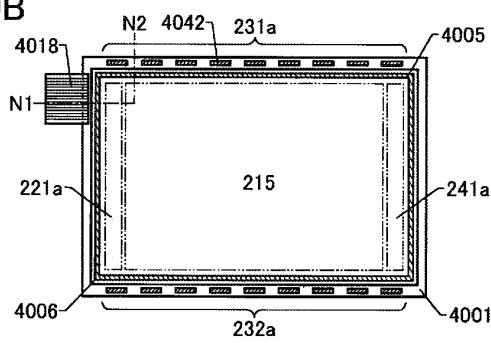

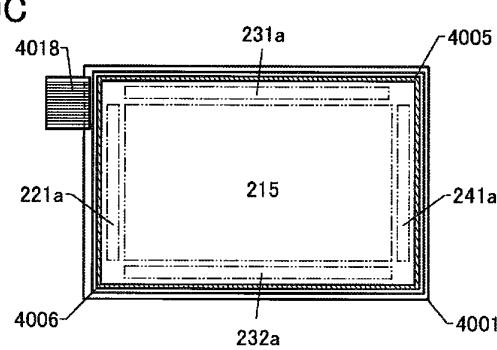

【図9】図9(A)～(C)は、表示装置を説明する図である。

【図10】図10(A)、(B)は、タッチパネルを説明する図である。

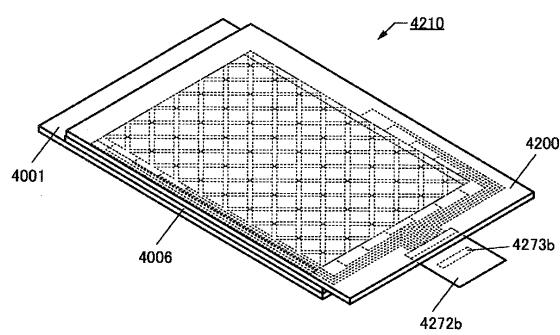

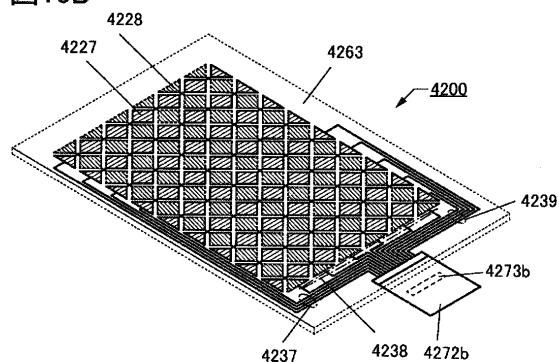

【図11】図11(A)、(B)は、表示装置を説明する図である。

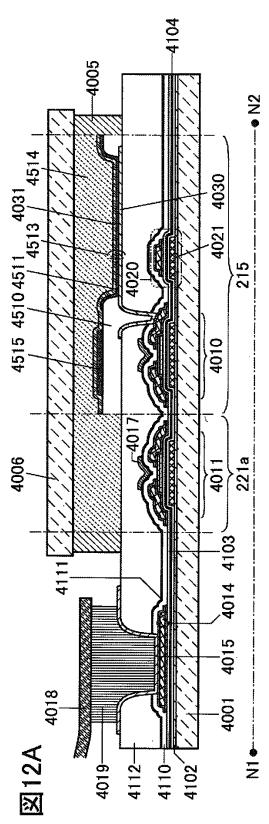

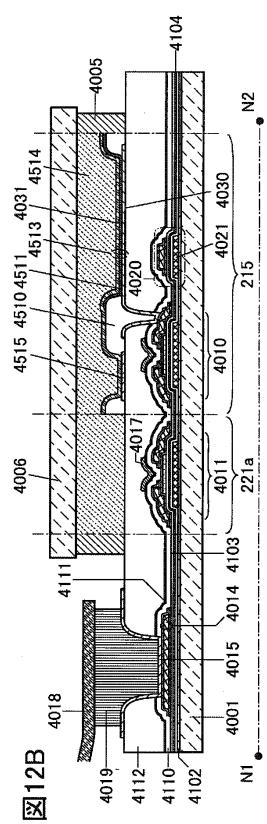

【図12】図12(A)、(B)は、表示装置を説明する図である。

10

【図13】図13(A)～(C)は、補助配線を説明する図である。

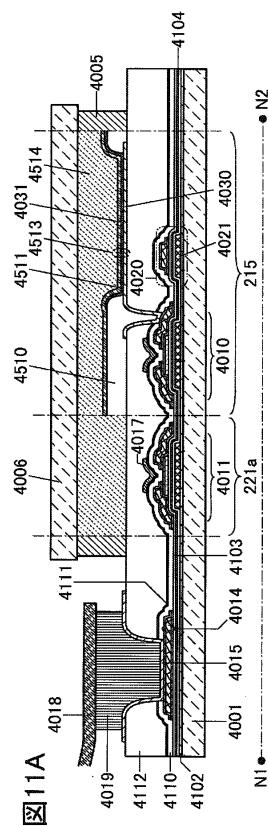

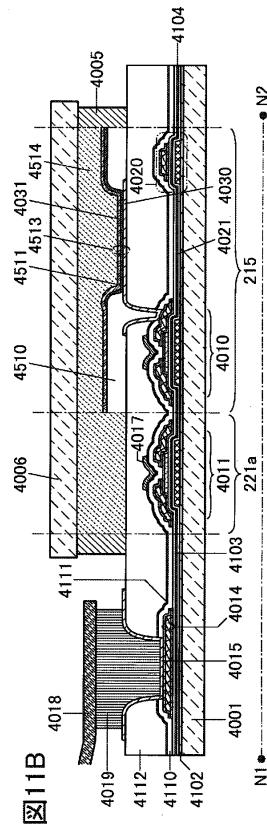

【図14】図14(A)～(C)は、発光デバイスを説明する図である。

【図15】図15(A)～(D)は、発光デバイスを説明する図である。

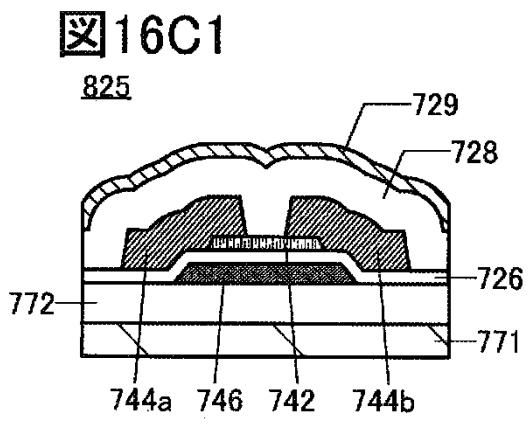

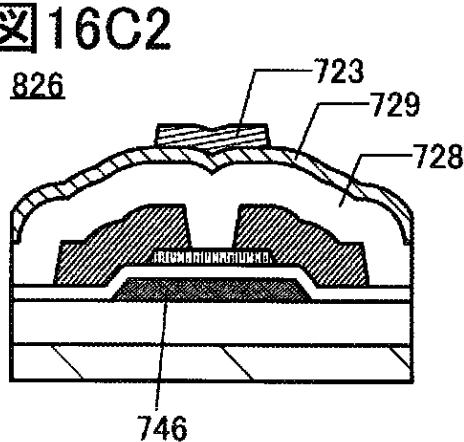

【図16】図16(A1)～(C2)は、トランジスタを説明する図である。

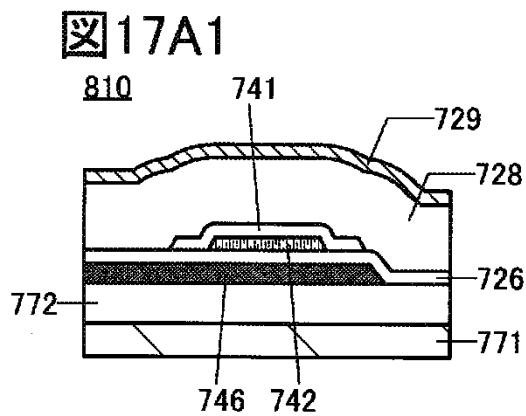

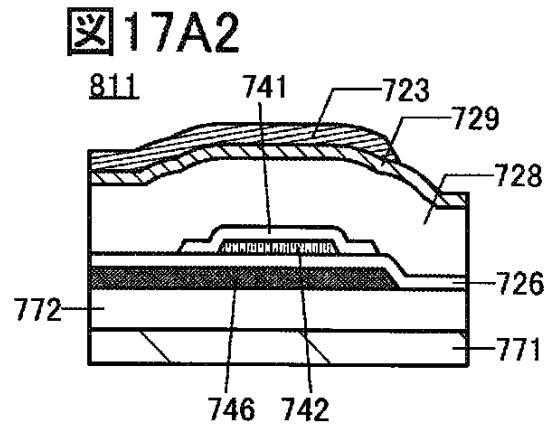

【図17】図17(A1)～(C2)は、トランジスタを説明する図である。

【図18】図18(A1)～(C2)は、トランジスタを説明する図である。

【図19】図19(A1)～(C2)は、トランジスタを説明する図である。

【図20】図20(A)～(F)は、電子機器を説明する図である。

【発明を実施するための形態】

【0020】

20

実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。なお、図を構成する同じ要素のハッチングを異なる図面間で適宜省略または変更する場合もある。

【0021】

また、回路図上では単一の要素として図示されている場合であっても、機能的に不都合がなければ、当該要素が複数で構成されてもよい。例えば、スイッチとして動作するトランジスタは、複数が直列または並列に接続されてもよい場合がある。また、キャパシタ(容量素子ともいう)を分割して複数の位置に配置してもよい場合がある。

30

【0022】

また、一つの導電体が、配線、電極および端子のような複数の機能を併せ持っている場合があり、本明細書においては、同一の要素に対して複数の呼称を用いる場合がある。また、回路図上で要素間が直接接続されているように図示されている場合であっても、実際には当該要素間が複数の導電体を介して接続されている場合があり、本明細書ではこのような構成でも直接接続の範疇に含める。

【0023】

(実施の形態1)

40

本実施の形態では、本発明の一態様である表示装置について、図面を参照して説明する。

【0024】

本発明の一態様は、データを加算する機能を有する画素が設けられたEL表示装置である。当該画素には記憶ノードが設けられ、当該記憶ノードに第1のデータを保持することができる。当該画素では、第1のデータに容量結合で第2のデータを付加し、第3のデータを生成することができる。発光デバイスは、第3のデータに応じて動作する。

【0025】

また、当該EL表示装置には、データを加算する機能を有さない画素も設けられる。したがって、特定の画素のみデータを加算する動作が行われる。この特定の画素には、発光に高い電圧を要する発光デバイス、または高い電圧の印加が好ましい発光デバイスが設けら

50

れている。

#### 【0026】

このように画素ごとに機能を分けることで、書き込みの高速化、および発光デバイスの信頼性を向上させることができる。また、比較的高い電圧を画素内で生成できることから、高い電圧を出力する特別なデータドライバを用いることなく、汎用のデータドライバを用いることができる。したがって、低消費電力化および製造コストを低減させることができる。

#### 【0027】

図1は、本発明の一態様の表示装置に用いることができる画素10aを説明する図である。

10

。画素10aは、第n行第m列（n、mは1以上の自然数）に設けられた画素11R、第n行第m+1列に設けられた画素11G、第n行第m+2列に設けられた画素11Bの3つの副画素を有する。画素11Rは赤色、画素11Gは緑色、画素11Bは青色の光をそれぞれ発し、3つの副画素が発する光で表示のカラー化を可能とする。

#### 【0028】

画素11Rは、トランジスタ101と、トランジスタ102と、キャパシタ103と、発光デバイス106Rを有する。発光デバイス106Rは、赤色の光を発する構成を有している。

#### 【0029】

画素11Gが有する要素は、発光デバイス106Rの代わりに発光デバイス106Gを有している点以外は画素11Rと同様である。発光デバイス106Gは、緑色の光を発する構成を有している。

20

#### 【0030】

画素11Rにおいて、トランジスタ101のソースまたはドレインの一方は、キャパシタ103の一方の電極と電気的に接続される。キャパシタ103の一方の電極は、トランジスタ102のゲートと電気的に接続される。トランジスタ102のソースまたはドレインの一方は、発光デバイス106Rの一方の電極と電気的に接続される。キャパシタ103の他方の電極は、例えばトランジスタ102のソースまたはドレインの一方と電気的に接続される。画素11Gの要素も画素11Rの要素と同様の接続形態とすることができます。

#### 【0031】

画素11Bは、トランジスタ111と、トランジスタ112と、トランジスタ113と、キャパシタ114と、キャパシタ115と、発光デバイス116Bを有する。発光デバイス116Bは、青色の光を発する構成を有している。詳細は後述するが、画素11Bでは、キャパシタ115の容量結合により、トランジスタ111およびトランジスタ112から入力される二つのデータを加算することができる。

30

#### 【0032】

トランジスタ111のソースまたはドレインの一方は、キャパシタ114の一方の電極と電気的に接続される。キャパシタ114の一方の電極は、キャパシタ115の一方の電極と電気的に接続される。キャパシタ115の他方の電極は、トランジスタ112のソースまたはドレインの一方と電気的に接続される。キャパシタ114の一方の電極は、トランジスタ113のゲートと電気的に接続される。トランジスタ113のソースまたはドレインの一方は、発光デバイス116Bの一方の電極と電気的に接続される。キャパシタ114の他方の電極は、例えばトランジスタ113のソースまたはドレインの一方と電気的に接続される。

40

#### 【0033】

トランジスタ101のゲート、およびトランジスタ111のゲートは、配線121[n]と電気的に接続される。トランジスタ112のゲートは、配線122[n]と電気的に接続される。

#### 【0034】

画素11Rにおいて、トランジスタ101のソースまたはドレインの他方は、配線123[m]と電気的に接続される。画素11Gにおいて、トランジスタ101のソースまたは

50

ドレインの他方は、配線 123 [ m + 1 ] と電気的に接続される。画素 11B において、トランジスタ 111 のソースまたはドレインの他方は、配線 123 [ m + 2 ] と電気的に接続され、トランジスタ 112 のソースまたはドレインの他方は、配線 124 [ m + 2 ] と電気的に接続される。

#### 【0035】

トランジスタ 102 のソースまたはドレインの他方、およびトランジスタ 113 のソースまたはドレインの他方は、配線 128 と電気的に接続される。発光デバイス 106R、106G、116B の他方の電極は、配線 129 と電気的に接続される。

#### 【0036】

配線 121 [ n ]、122 [ n ] は、トランジスタの動作を制御するための信号線としての機能を有することができる。配線 123 [ m ] 乃至 [ m + 2 ] は、画像データを供給する信号線としての機能を有することができる。配線 124 [ m + 2 ] は、基準電位または画像データなどを供給する信号線としての機能を有することができる。配線 128、129 は電源線としての機能を有することができる。図 1 に示す発光デバイスの接続形態では、例えば、配線 128 は高電位を供給する電源線、配線 129 は低電位を供給する電源線または GND 電位線とすることができます。

10

#### 【0037】

画素 11R において、トランジスタ 101 のソースまたはドレインの一方、キャパシタ 103 の一方の電極、およびトランジスタ 102 のゲートが接続される配線をノード NM [ R ] とする。同様に画素 11G においては、当該配線をノード NM [ G ] とする。画素 11B において、トランジスタ 111 のソースまたはドレインの一方、キャパシタ 114 の一方の電極、キャパシタ 115 の一方の電極およびトランジスタ 113 のゲートが接続される配線をノード NM [ B ] とする。

20

#### 【0038】

ノード NM [ R ]、ノード NM [ G ]、ノード NM [ B ] は記憶ノードである。例えば、画素 11R において、トランジスタ 101 を導通させることで、配線 123 [ m ] に供給されたデータをノード NM [ R ] に書き込むことができる。また、トランジスタ 101 を非導通とすることで、当該データをノード NM [ R ] に保持することができる。ノード NM [ G ]、ノード NM [ B ] も同様である。

30

#### 【0039】

トランジスタ 101 およびトランジスタ 111 に極めてオフ電流の低いトランジスタを用いることで、ノード NM [ R ]、ノード NM [ G ]、ノード NM [ B ] の電位を長時間保持することが可能となる。したがって、静止画などではデータを書き込むフレーム周波数を低減することができ、表示装置を低消費電力化することができる。また、キャパシタ 115 を介したノード NM [ B ] の電位変化を抑えるため、トランジスタ 112 にもオフ電流の低いトランジスタを用いることが好ましい。

#### 【0040】

当該トランジスタには、例えば、金属酸化物をチャネル形成領域に用いたトランジスタ（以下、OSトランジスタ）を用いることができる。

40

#### 【0041】

なお、トランジスタ 101、111 だけでなく、画素を構成するその他のトランジスタに OSトランジスタを適用してもよい。また、トランジスタ 101、111 に Si をチャネル形成領域に有するトランジスタ（以下、Siトランジスタ）を適用してもよい。または、OSトランジスタと、Siトランジスタとの両方を用いて画素を構成してもよい。なお、上記 Siトランジスタとしては、アモルファスシリコンを有するトランジスタ、結晶性のシリコン（代表的には、低温ポリシリコン、単結晶シリコン）を有するトランジスタなどが挙げられる。

#### 【0042】

OSトランジスタに用いる半導体材料としては、エネルギーギャップが 2 eV 以上、好ましくは 2.5 eV 以上、より好ましくは 3 eV 以上である金属酸化物を用いることができ

50

る。代表的には、インジウムを含む酸化物半導体などであり、例えば、後述する C A A C - O S または C A C - O S などを用いることができる。C A A C - O S は結晶を構成する原子が安定であり、信頼性を重視するトランジスタなどに適する。また、C A C - O S は、高移動度特性を示すため、高速駆動を行うトランジスタなどに適する。

#### 【 0 0 4 3 】

O S トランジスタはエネルギーギャップが大きいため、数  $\gamma$  A /  $\mu$  m (チャネル幅  $1 \mu$  mあたりの電流値) という極めて低いオフ電流特性を示す。また、O S トランジスタは、インパクトイオン化、アバランシェ降伏、および短チャネル効果などが生じないなど S i トランジスタとは異なる特徴を有し、高耐圧で信頼性の高い回路を形成することができる。また、S i トランジスタでは問題となる結晶性の不均一性に起因する電気特性のばらつきも O S トランジスタでは生じにくい。

10

#### 【 0 0 4 4 】

O S トランジスタが有する半導体層は、例えばインジウム、亜鉛およびM (アルミニウム、チタン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、セリウム、スズ、ネオジムまたはハフニウム等の金属) を含む I n - M - Z n 系酸化物で表記される膜とすることができます。I n - M - Z n 系酸化物は代表的には、スパッタリング法で形成することができる。または、A L D (A t o m i c l a y e r d e p o s i t i o n ) 法を用いて形成してもよい。

#### 【 0 0 4 5 】

I n - M - Z n 系酸化物をスパッタリング法で形成するために用いるスパッタリングターゲットの金属元素の原子数比は、I n : M、Z n : M を満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、I n : M : Z n = 1 : 1 : 1 、I n : M : Z n = 1 : 1 : 1 . 2 、I n : M : Z n = 3 : 1 : 2 、I n : M : Z n = 4 : 2 : 3 、I n : M : Z n = 4 : 2 : 4 . 1 、I n : M : Z n = 5 : 1 : 6 、I n : M : Z n = 5 : 1 : 7 、I n : M : Z n = 5 : 1 : 8 等が好ましい。なお、成膜される半導体層の原子数比はそれぞれ、上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス 4 0 % の変動を含む。

20

#### 【 0 0 4 6 】

半導体層としては、キャリア密度の低い酸化物半導体を用いる。例えば、半導体層は、キャリア密度が  $1 \times 10^{17} / \text{cm}^3$  以下、好ましくは  $1 \times 10^{15} / \text{cm}^3$  以下、さらに好ましくは  $1 \times 10^{13} / \text{cm}^3$  以下、より好ましくは  $1 \times 10^{11} / \text{cm}^3$  以下、さらに好ましくは  $1 \times 10^{10} / \text{cm}^3$  未満であり、 $1 \times 10^{-9} / \text{cm}^3$  以上の酸化物半導体を用いることができる。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。当該酸化物半導体は欠陥準位密度が低く、安定な特性を有する酸化物半導体であるといえる。

30

#### 【 0 0 4 7 】

なお、これらに限らず、必要とするトランジスタの半導体特性および電気特性 (電界効果移動度、しきい値電圧等) に応じて適切な組成の酸化物半導体を用いればよい。また、必要とするトランジスタの半導体特性を得るために、半導体層のキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

40

#### 【 0 0 4 8 】

半導体層を構成する酸化物半導体において、第 1 4 族元素の一つであるシリコンや炭素が含まれると、酸素欠損が増加し、n 型化してしまう。このため、半導体層におけるシリコンや炭素の濃度 (二次イオン質量分析法 (S I M S : S e c o n d a r y I o n M a s s S p e c t r o m e t r y ) により得られる濃度) を、 $2 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下、好ましくは  $2 \times 10^{17} \text{ atoms} / \text{cm}^3$  以下とする。

#### 【 0 0 4 9 】

また、アルカリ金属およびアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、半

50

導体層におけるアルカリ金属またはアルカリ土類金属の濃度（S I M Sにより得られる濃度）を、 $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$  atoms / cm<sup>3</sup>以下にする。

#### 【0050】

また、半導体層を構成する酸化物半導体に窒素が含まれていると、キャリアである電子が生じてキャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため半導体層における窒素濃度（S I M Sにより得られる濃度）は、 $5 \times 10^{18}$  atoms / cm<sup>3</sup>以下にすることが好ましい。

#### 【0051】

また、半導体層を構成する酸化物半導体に水素が含まれていると、金属原子と結合する酸素と反応して水になるため、酸化物半導体中に酸素欠損を形成する場合がある。酸化物半導体中のチャネル形成領域に酸素欠損が含まれていると、トランジスタはノーマリーオン特性となる場合がある。さらに、酸素欠損に水素が入った欠陥はドナーとして機能し、キャリアである電子が生成されることがある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成する場合がある。したがって、水素が多く含まれている酸化物半導体を用いたトランジスタは、ノーマリーオン特性となりやすい。

10

#### 【0052】

酸素欠損に水素が入った欠陥は、酸化物半導体のドナーとして機能しうる。しかしながら、当該欠陥を定量的に評価することは困難である。そこで、酸化物半導体においては、ドナー濃度ではなく、キャリア濃度で評価される場合がある。よって、本明細書等では、酸化物半導体のパラメータとして、ドナー濃度ではなく、電界が印加されない状態を想定したキャリア濃度を用いる場合がある。つまり、本明細書等に記載の「キャリア濃度」は、「ドナー濃度」と言い換えることができる場合がある。

20

#### 【0053】

よって、酸化物半導体中の水素はできる限り低減されていることが好ましい。具体的には、酸化物半導体において、S I M Sにより得られる水素濃度を、 $1 \times 10^{20}$  atoms / cm<sup>3</sup>未満、好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup>未満、より好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>未満、さらに好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>未満とする。水素などの不純物が十分に低減された酸化物半導体をトランジスタのチャネル形成領域に用いることで、安定した電気特性を付与することができる。

30

#### 【0054】

また、半導体層は、例えば非単結晶構造でもよい。非単結晶構造は、例えば、c軸に配向した結晶を有するC A A C - O S (C - A x i s A l i g n e d C r y s t a l l i n e O x i d e S e m i c o n d u c t o r)、多結晶構造、微結晶構造、または非晶質構造を含む。非単結晶構造において、非晶質構造は最も欠陥準位密度が高く、C A A C - O S は最も欠陥準位密度が低い。

#### 【0055】

非晶質構造の酸化物半導体膜は、例えば、原子配列が無秩序であり、結晶成分を有さない。または、非晶質構造の酸化物膜は、例えば、完全な非晶質構造であり、結晶部を有さない。

40

#### 【0056】

なお、半導体層が、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、C A A C - O S の領域、単結晶構造の領域のうち、二種以上を有する混合膜であってもよい。混合膜は、例えば上述した領域のうち、いずれか二種以上の領域を含む単層構造、または積層構造を有する場合がある。

#### 【0057】

以下では、非単結晶の半導体層の一態様であるC A C (C l o u d - A l i g n e d C o m p o s i t e) - O S の構成について説明する。

#### 【0058】

50

CAC-OSとは、例えば、酸化物半導体を構成する元素が、0.5 nm以上10 nm以下、好ましくは、1 nm以上2 nm以下、またはその近傍のサイズで偏在した材料の一構成である。なお、以下では、酸化物半導体において、一つあるいはそれ以上の金属元素が偏在し、該金属元素を有する領域が、0.5 nm以上10 nm以下、好ましくは、1 nm以上2 nm以下、またはその近傍のサイズで混合した状態をモザイク状、またはパッチ状ともいう。

#### 【0059】

なお、酸化物半導体は、少なくともインジウムを含むことが好ましい。特にインジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。

#### 【0060】

例えば、In-Ga-Zn酸化物におけるCAC-OS (CAC-OSの中でもIn-Ga-Zn酸化物を、特にCIGZOと呼称してもよい。)とは、インジウム酸化物(以下、 $InO_{X_1}$ ( $X_1$ は0よりも大きい実数)とする。)、またはインジウム亜鉛酸化物(以下、 $In_{X_2}Zn_{Y_2}O_{Z_2}$ ( $X_2$ 、 $Y_2$ 、および $Z_2$ は0よりも大きい実数)とする。)と、ガリウム酸化物(以下、 $GaO_{X_3}$ ( $X_3$ は0よりも大きい実数)とする。)、またはガリウム亜鉛酸化物(以下、 $Ga_{X_4}Zn_{Y_4}O_{Z_4}$ ( $X_4$ 、 $Y_4$ 、および $Z_4$ は0よりも大きい実数)とする。)などと、に材料が分離することでモザイク状となり、モザイク状の $InO_{X_1}$ 、または $In_{X_2}Zn_{Y_2}O_{Z_2}$ が、膜中に均一に分布した構成(以下、クラウド状ともいう。)である。

#### 【0061】

つまり、CAC-OSは、 $GaO_{X_3}$ が主成分である領域と、 $In_{X_2}Zn_{Y_2}O_{Z_2}$ 、または $InO_{X_1}$ が主成分である領域とが、混合している構成を有する複合酸化物半導体である。なお、本明細書において、例えば、第1の領域の元素Mに対するInの原子数比が、第2の領域の元素Mに対するInの原子数比よりも大きいことを、第1の領域は、第2の領域と比較して、Inの濃度が高いとする。

#### 【0062】

なお、IGZOは通称であり、In、Ga、Zn、およびOによる1つの化合物をいう場合がある。代表例として、 $InGaO_3$ ( $ZnO$ ) $m_1$ ( $m_1$ は自然数)、または $In_{(1+x_0)}Ga_{(1-x_0)}O_3$ ( $ZnO$ ) $m_0$ ( $-1 < x_0 < 1$ 、 $m_0$ は任意数)で表される結晶性の化合物が挙げられる。

#### 【0063】

上記結晶性の化合物は、単結晶構造、多結晶構造、またはCAC構造を有する。なお、CAC構造とは、複数のIGZOのナノ結晶がc軸配向を有し、かつa-b面においては配向せずに連結した結晶構造である。

#### 【0064】

一方、CAC-OSは、酸化物半導体の材料構成に関する。CAC-OSとは、In、Ga、Zn、およびOを含む材料構成において、一部にGaを主成分とするナノ粒子状に観察される領域と、一部にInを主成分とするナノ粒子状に観察される領域とが、それぞれモザイク状にランダムに分散している構成をいう。したがって、CAC-OSにおいて、結晶構造は副次的な要素である。

#### 【0065】

なお、CAC-OSは、組成の異なる二種類以上の膜の積層構造は含まないものとする。例えば、Inを主成分とする膜と、Gaを主成分とする膜との2層からなる構造は、含まない。

#### 【0066】

なお、 $GaO_{X_3}$ が主成分である領域と、 $In_{X_2}Zn_{Y_2}O_{Z_2}$ 、または $InO_{X_1}$ が主

10

20

30

40

50

成分である領域とは、明確な境界が観察できない場合がある。

#### 【0067】

なお、ガリウムの代わりに、アルミニウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれている場合、CAC-OSは、一部に該金属元素を主成分とするナノ粒子状に観察される領域と、一部にInを主成分とするナノ粒子状に観察される領域とが、それぞれモザイク状にランダムに分散している構成をいう。

#### 【0068】

CAC-OSは、例えば基板を意図的に加熱しない条件で、スパッタリング法により形成することができる。また、CAC-OSをスパッタリング法で形成する場合、成膜ガスとして、不活性ガス（代表的にはアルゴン）、酸素ガス、および窒素ガスの中から選ばれたいずれか一つまたは複数を用いればよい。また、成膜時の成膜ガスの総流量に対する酸素ガスの流量比は低いほど好ましく、例えば酸素ガスの流量比を0%以上30%未満、好ましくは0%以上10%以下とすることが好ましい。

10

#### 【0069】

CAC-OSは、X線回折(XRD:X-ray diffraction)測定法のひとつであるOut-of-plane法による $/2$ スキャンを用いて測定したときに、明確なピークが観察されないという特徴を有する。すなわち、X線回折測定から、測定領域のa-b面方向、およびc軸方向の配向は見られないことが分かる。

20

#### 【0070】

また、CAC-OSは、プローブ径が1nmの電子線（ナノビーム電子線ともいう。）を照射することで得られる電子線回折パターンにおいて、リング状に輝度の高い領域（リング領域）と、該リング領域に複数の輝点が観測される。したがって、電子線回折パターンから、CAC-OSの結晶構造が、平面方向、および断面方向において、配向性を有さないnc(nano-crystalline)構造を有することがわかる。

#### 【0071】

また、例えば、In-Ga-Zn酸化物におけるCAC-OSでは、エネルギー分散型X線分光法(EDX:Energy Dispersive X-ray spectros copy)を用いて取得したEDXマッピングにより、GaO<sub>3</sub>が主成分である領域と、In<sub>x</sub>Zn<sub>y</sub>O<sub>z</sub>、またはInO<sub>x</sub>が主成分である領域とが、偏在し、混合している構造を有することが確認できる。

30

#### 【0072】

CAC-OSは、金属元素が均一に分布したIGZO化合物とは異なる構造であり、IGZO化合物と異なる性質を有する。つまり、CAC-OSは、GaO<sub>3</sub>などが主成分である領域と、In<sub>x</sub>Zn<sub>y</sub>O<sub>z</sub>、またはInO<sub>x</sub>が主成分である領域と、に互いに相分離し、各元素を主成分とする領域がモザイク状である構造を有する。

#### 【0073】

ここで、In<sub>x</sub>Zn<sub>y</sub>O<sub>z</sub>、またはInO<sub>x</sub>が主成分である領域は、GaO<sub>3</sub>などが主成分である領域と比較して、導電性が高い領域である。つまり、In<sub>x</sub>Zn<sub>y</sub>O<sub>z</sub>、またはInO<sub>x</sub>が主成分である領域を、キャリアが流れることにより、酸化物半導体としての導電性が発現する。したがって、In<sub>x</sub>Zn<sub>y</sub>O<sub>z</sub>、またはInO<sub>x</sub>が主成分である領域が、酸化物半導体中にクラウド状に分布することで、高い電界効果移動度( $\mu$ )が実現できる。

40

#### 【0074】

一方、GaO<sub>3</sub>などが主成分である領域は、In<sub>x</sub>Zn<sub>y</sub>O<sub>z</sub>、またはInO<sub>x</sub>が主成分である領域と比較して、絶縁性が高い領域である。つまり、GaO<sub>3</sub>などが主成分である領域が、酸化物半導体中に分布することで、リーク電流を抑制し、良好なスイッチング動作を実現できる。

50

**【 0 0 7 5 】**

したがって、C A C - O S を半導体素子に用いた場合、G a O x 3 などに起因する絶縁性と、I n x 2 Z n y 2 O z 2 、またはI n O x 1 に起因する導電性とが、相補的に作用することにより、高いオン電流 ( I o n ) 、および高い電界効果移動度 ( μ ) を実現することができる。

**【 0 0 7 6 】**

また、C A C - O S を用いた半導体素子は、信頼性が高い。したがって、C A C - O S は、様々な半導体装置の構成材料として適している。

**【 0 0 7 7 】**

画素 1 1 R では、1 度の書き込み動作でノード N M [ R ] に必要なデータを書き込み、当該データに応じて発光デバイス 1 0 6 R の発光を制御する。画素 1 1 G も同じである。一方、画素 1 1 B では、ノード N M [ B ] に第 1 のデータを書き込んだ後、容量結合により第 2 のデータを第 1 のデータに加算し、生成した第 3 のデータに応じて発光デバイス 1 1 6 B の発光を制御する。

10

**【 0 0 7 8 】**

言い換えると、赤色、緑色の光を発する発光デバイスには比較的低い電圧を印加し、青色の光を発する発光デバイスには比較的高い電圧を印加する。

**【 0 0 7 9 】**

ここで、青色の光を発する発光デバイスに高い電圧を印加する利点を説明する。

20

**【 0 0 8 0 】**

発光デバイスが有する発光層には、蛍光材料またはりん光材料が用いられる。蛍光材料を用いた発光デバイスは比較的寿命が長い反面、入力した電力を最大でも 2 5 % しか光に変換することができず、発光効率が悪い。一方、りん光材料を用いた発光デバイスは、入力した電力を理論上 1 0 0 % 光に変換することができる。しかしながら、りん光材料には高価なレアメタルを用いることが一般的である。また、収率、精製などの生産性にも課題があり、コスト面での問題を有している。現状では、量産に展開できるりん光材料は、赤色および緑色に限られ、青色には蛍光材料が用いられている。

**【 0 0 8 1 】**

したがって、同一の素子構造で同一の投入電力では、青色を発する発光デバイスは赤色または緑色を発する発光デバイスよりも輝度が低くなってしまう。発光デバイスの輝度は電流と比例するため、電圧を高めて大きな電流を流すことで輝度を上昇させることはできる。しかしながら、素子に大電流を流すと電流ストレスにより素子寿命を縮めてしまう問題が生じる。

30

**【 0 0 8 2 】**

そのため、青色の発光デバイスでは、タンデム構造とすることが好ましい。タンデム構造では 1 素子あたりの電流ストレスを少なくすることができ、素子寿命を延ばすことができる。なお、素子寿命の影響が許容できればシングル構造を用いてもよい。

**【 0 0 8 3 】**

なお、本明細書では、一対の電極間において発光ユニットを 2 つ以上直列接続した構造をタンデム構造と呼ぶ。なお、タンデム構造においては、複数の発光ユニットの間に電荷発生層が設けられていると好適である。また、一対の電極間に発光ユニットが一つ設けられた構造をシングル構造と呼ぶ。また、発光ユニットとは、少なくとも発光層を有していればよく、その他の機能層（ホール輸送層、ホール注入層、電子輸送層、電子注入層など）を有していてもよい。なお、発光ユニットの詳細については、実施の形態 2 で説明を行う。

40

**【 0 0 8 4 】**

例えば、図 2 ( A ) に示すように、画素回路に組み込まれた 2 層タンデムの発光デバイス 1 2 0 の等価回路は、2 個のダイオード 1 1 9 が直列接続された形になる。

**【 0 0 8 5 】**

図 2 ( B ) は発光デバイス（ダイオード）の順方向特性を説明する I - V 特性である。ある発光デバイスの順方向電圧が “ V f ” であるとき、同じ発光デバイスが 2 個直列接続され

50

ると、2個の発光デバイスに電流が流れ始める電圧は“ $2V_f$ ”以上となる。

#### 【0086】

一方で、タンデム構造では複数の発光ユニットから発光が得られるため、同じ電流を流した場合ではシングル構造よりも高い発光強度を得ることができる。また、シングル構造で大電流を流して発光強度を高めるよりも信頼性を向上させることができる。

#### 【0087】

上述したようにタンデム構造では、発光デバイスに供給する電圧を高くする必要がある。したがって、高電圧出力のデータドライバが必要となる場合がある。しかしながら、本発明の一態様では、データドライバが出力する電圧を画素回路で加算して比較的高い電圧が生成できるため、低消費電力での動作が可能である。また、高電圧出力のデータドライバを不要とすることことができ、汎用のデータドライバなどを用いることができる。または、高電圧出力のデータドライバを用いても動作が困難な表示デバイス（表示素子ともいう）を動作させることもできる。

10

#### 【0088】

なお、本実施の形態においては、書き込み時間削減のため画素11Bのみにデータの加算機能を設けた例を示しているが、本発明の一態様は、これに限定されず、画素11Rおよび画素11Gにも当該機能を設けてもよい。

#### 【0089】

画素11Bでは、まず、ノードNM[B]に第1のデータ（重み：W）を書き込む。このとき、キャパシタ115の他方の電極には基準電位“ $V_0$ ”を供給し、キャパシタ115には“ $W - V_0$ ”を保持させる。次に、ノードNM[B]をフローティングとし、キャパシタ115の他方の電極に第2のデータ（データ：D）を供給する。

20

#### 【0090】

このとき、キャパシタ115の容量値を $C_{115}$ 、ノードNM[B]の容量値を $C_{NM[B]}$ とすると、ノードNM[B]の電位は、“ $W + (C_{115} / (C_{115} + C_{NM[B]})) \times (D - V_0)$ ”となる。ここで、 $C_{115}$ の値を大きくし、 $C_{NM[B]}$ の値を無視できるようになれば、ノードNMの電位は“ $W + D - V_0$ ”となる。

#### 【0091】

したがって、“ $W = D$ ”、“ $V_0 = 0V$ ”であって、 $C_{115}$ が $C_{NM[B]}$ に比べて十分に大きければノードNM[B]の電位は“ $2D$ ”に近づく。つまり、データドライバから画素に出力された電位の約2倍の電位となる第3のデータ（“ $2D$ ”）をノードNM[B]に供給できることになる。

30

#### 【0092】

図3に示すタイミングチャートを用いて、図1に示す画素10aの動作の一例を説明する。なお、以下の説明においては、高電位を“H”、低電位を“L”で表す。また、画素11[R]に供給するデータを“ $D_R$ ”、画素11[G]に供給するデータを“ $D_G$ ”、画素11[B]に供給する第1のデータ（重みに相当）を“ $D_{1B}$ ”、第2のデータ（データに相当）を“ $D_{2B}$ ”とする。“ $\wedge$ ”としては、例えば0V、GND電位または特定の基準電位を用いることができる。

40

#### 【0093】

なお、ここでは電位の分配、結合または損失において、回路の構成や動作タイミングなどに起因する詳細な変化は勘案しない。また、キャパシタを用いた容量結合による電位の変化は、当該キャパシタと、接続される要素との容量比に依存するが、説明を明瞭にするため、当該要素の容量値は十分に小さい値に仮定する。また、図3では線順次方式のデータ書き込みを例示しているが、点順次方式を用いてもよい。

#### 【0094】

時刻T1に配線121[n]の電位を“H”、配線122[n]の電位を“H”とすると、画素11R、11Gにおいてトランジスタ101が導通する。また、画素11Bにおいてトランジスタ111およびトランジスタ112が導通する。

#### 【0095】

50

時刻 T 1において、画素 11 [ R ] のノード NM [ R ] には配線 123 [ m ] に供給される “ D<sub>R</sub> ” が書き込まれる。

#### 【 0096 】

また、画素 11 [ G ] のノード NM [ G ] には配線 123 [ m + 1 ] に供給される “ D<sub>G</sub> ” が書き込まれる。

#### 【 0097 】

また、画素 11 [ B ] のノード NM [ B ] には配線 123 [ m + 2 ] に供給される “ D<sub>1B</sub> ” が書き込まれる。

#### 【 0098 】

キャパシタ 115 の他方の電極の電位は、配線 124 [ m + 2 ] に供給される電位 “ V<sub>0</sub> ” となる。当該動作は、後の加算動作（容量結合動作）を行うためのリセット動作である。このとき、キャパシタ 115 には、“ D<sub>1B</sub> - V<sub>0</sub> ” が保持される。

#### 【 0099 】

時刻 T 2 に配線 121 [ n ] の電位を “ L ” とするとトランジスタ 101、111 は非導通となり、ノード NM [ R ] 、ノード NM [ G ] およびノード NM [ B ] の電位は保持される。画素 11R および画素 11G においては、ノード NM [ R ] またはノード NM [ G ] の電位に従って次フレームの動作まで表示が継続される。

#### 【 0100 】

また、時刻 T 2 に配線 124 [ m + 2 ] に “ D<sub>2B</sub> ” が供給されると、キャパシタ 115 の他方の電極の電位の変化分 “ D<sub>2B</sub> - V<sub>0</sub> ” がキャパシタ 115 とノード NM [ B ] の容量比に応じてノード NM [ B ] に加算される。当該動作は加算動作であり、ノード NM [ B ] の電位は “ D<sub>1B</sub> + ( D<sub>2B</sub> - V<sub>0</sub> ) ” となる。このとき、 “ r<sub>Lf</sub> ” = 0 であれば、ノード NM [ B ] の電位は、“ D<sub>1B</sub> + D<sub>2B</sub> ” となる。

#### 【 0101 】

ここで、 D<sub>1B</sub> = D<sub>2B</sub> であって、ノード NM [ B ] の容量がキャパシタ 115 の容量より十分に小さい場合は、“ D<sub>1B</sub> + D<sub>2B</sub> ” は “ 2 目 ” に近い値となる。したがって、データドライバの出力するデータ電位の約 2 倍のデータ電位を表示デバイスに供給することができる。

#### 【 0102 】

時刻 T 3 に配線 122 [ n ] の電位を “ L ” とすると、トランジスタ 112 は非導通となり、ノード NM [ B ] の電位は保持され、次フレームの動作まで表示が継続される。以上が画素 10a の動作説明である。このような動作により、入力する電圧は小さくてもタンデム構造の発光デバイスを動作させることができる。

#### 【 0103 】

図 1 に示す画素 10a は、画素 11R 、画素 11G 、画素 11B の 3 つの副画素を有する構成であるが、さらに白色の光を発する画素 11W を副画素に有する構成であってもよい。副画素に白色を加えることにより画面の明るさを増すことができるため、画素 10a を用いた場合より少ない電力で同程度の明るさを実現することができる。総画素数は増加するため、大画面のテレビやデジタルサイネージなどの用途に適している。

#### 【 0104 】

図 4 ( A ) は、画素 11R 、画素 11G 、画素 11B 、画素 11W の 4 つの副画素を有する画素 10b を説明する図である。画素 10b は、画素 10a が有する 3 つの副画素にさらに第 n 行第 m + 3 列に設けられた画素 11W の副画素を加えた構成である。画素 11W の回路構成は画素 11B と同等であり、白色の光を発する発光デバイス 116W を有する。

#### 【 0105 】

白色発光を得るには、赤色、緑色、青色の三色の発光が行える発光デバイス、または互いに補色の関係となる二色の発光が行える発光デバイスなどを用いることができる。したがって、前述した青色発光デバイスと同様にタンデム構造であることが好ましい。ここでは、白色の光を発する発光デバイス 116W として、赤色、緑色、青色のそれぞれの発光ユニットを有する 3 層タンデム構造の発光デバイスを用いる場合を想定して説明する。

10

20

30

40

50

**【 0 1 0 6 】**

画素 1 1 W は、図 4 ( A ) に示すように画素 1 1 B と同等の構成を有し、配線 1 2 3 [ m + 3 ] および配線 1 2 4 [ m + 3 ] と電気的に接続される。

**【 0 1 0 7 】**

図 5 に示すタイミングチャートを用いて、図 4 ( A ) に示す画素 1 0 b の動作の一例を説明する。なお、画素 1 0 a と共に説明の詳細は省略する。以下の説明において、画素 1 1 [ W ] に供給する第 1 のデータ（重みに相当）を “ D<sub>1</sub> W ” 、第 2 のデータ（データに相当）を “ D<sub>2</sub> W ” とする。

**【 0 1 0 8 】**

なお、3層タンデムの発光デバイスの発光には 2 層タンデムの発光デバイスよりも高い電圧を必要とするため、ここでは、ノード NM [ W ] の電位が “ 3 D<sub>1</sub> W ” となるような動作を説明する。

10

**【 0 1 0 9 】**

画素 1 1 R 、画素 1 1 G 、画素 1 1 B の基本動作は画素 1 0 a と同じであるため、ここでは画素 1 1 W の動作のみを説明する。

**【 0 1 1 0 】**

時刻 T<sub>1</sub> に配線 1 2 1 [ n ] の電位を “ H ” 、配線 1 2 2 [ n ] の電位を “ H ” とすると、画素 1 1 W においてトランジスタ 1 1 1 およびトランジスタ 1 1 2 が導通する。

**【 0 1 1 1 】**

時刻 T<sub>1</sub> において、画素 1 1 [ W ] のノード NM [ W ] には配線 1 2 3 [ m + 3 ] に供給される “ D<sub>1</sub> W ” が書き込まれる。

20

**【 0 1 1 2 】**

また、キャパシタ 1 1 5 の他方の電極の電位は、配線 1 2 4 [ m + 3 ] に供給される電位 “ - D<sub>2</sub> W ” となる。当該動作は、後の加算動作（容量結合動作）を行うためのリセット動作である。このとき、キャパシタ 1 1 5 には、 “ D<sub>1</sub> W - ( - D<sub>2</sub> W ) ” が保持される。

**【 0 1 1 3 】**

時刻 T<sub>2</sub> に配線 1 2 1 [ n ] の電位を “ L ” とするとトランジスタ 1 1 1 は非導通となり、ノード NM [ W ] の電位は保持される。

**【 0 1 1 4 】**

また、時刻 T<sub>2</sub> に配線 1 2 4 [ m + 3 ] に “ D<sub>2</sub> W ” が供給されると、キャパシタ 1 1 5 の他方の電極の電位の変化分 “ D<sub>2</sub> W - ( - D<sub>2</sub> W ) ” がキャパシタ 1 1 5 とノード NM [ W ] の容量比に応じて電位ノード NM [ W ] に加算される。当該動作は加算動作であり、ノード NM [ W ] の電位は “ D<sub>1</sub> W + ( D<sub>2</sub> W - ( - D<sub>2</sub> W ) ) ' ” となる。

30

**【 0 1 1 5 】**

ここで、D<sub>1</sub> W = D<sub>2</sub> W であって、ノード NM [ W ] の容量がキャパシタ 1 1 5 の容量より十分に小さい場合は、“ D<sub>1</sub> W + ( D<sub>2</sub> W - ( - D<sub>2</sub> W ) ) ' ” は “ 3 W ” に近い値となる。したがって、データドライバの出力するデータ電位の約 3 倍のデータ電位を表示デバイスに供給することができる。

**【 0 1 1 6 】**

時刻 T<sub>3</sub> に配線 1 2 2 [ n ] の電位を “ L ” とすると、トランジスタ 1 1 2 は非導通となり、ノード NM [ W ] の電位は保持され、次フレームの動作まで表示が継続される。以上が画素 1 0 b における画素 1 1 W の動作説明である。このような動作により、3層タンデム構造の発光デバイスであっても小さい入力電圧で動作させることができる。

40

**【 0 1 1 7 】**

なお、画素 1 0 b は図 4 ( B ) に示すように、R ( 赤 ) 、G ( 緑 ) 、B ( 青 ) 、W ( 白 ) の計 4 つの色を発する副画素で画素を構成している。他のバリエーションとして、図 4 ( C ) に示す画素 1 0 c のように、RGB 、WRG 、BWR 、GBW の組み合わせとして、3 つの色を発する副画素で画素を構成してもよい。なお、副画素の色構成については、RGBW に限定されない。例えば、RGBW のほか、Y ( 黄 ) 、M ( マゼンタ ) 、C ( シアン ) などのいずれか一つ以上の色を発する副画素を含んで画素を構成してもよい。

50

**【 0 1 1 8 】**

本発明の一態様は、図1または図4(A)と異なる構成の画素回路にも適用することができる。なお、以下の説明においては、画素11Bについて説明を行うが、その他の画素も同様の構成とすることができます。

**【 0 1 1 9 】**

例えば、図6(A)に示すように、発光デバイス116Bの一方の電極を配線128と電気的に接続し、発光デバイス116Bの他方の電極をトランジスタ113のソースまたはドレインの他方と電気的に接続してもよい。

**【 0 1 2 0 】**

また、図6(B)に示すように、図1または図4(A)の構成にトランジスタ117を付加した構成としてもよい。トランジスタ117のソースまたはドレインの一方は、トランジスタ113のソースまたはドレインの一方と電気的に接続される。トランジスタ117のソースまたはドレインの他方は、発光デバイス116Bの一方の電極と電気的に接続される。トランジスタ117のゲートは、配線130と電気的に接続される。配線130は、トランジスタの導通を制御する信号線としての機能を有することができる。

10

**【 0 1 2 1 】**

当該構成では、ノードNM[B]の電位がトランジスタ113のしきい値電圧以上であつて、トランジスタ117が導通したときに発光デバイス116Bに電流が流れる。したがって、トランジスタ117の導通を制御することで、重み(W)とデータ(D)の加算動作後の任意のタイミングに発光デバイス116Bの発光を開始することができる。

20

**【 0 1 2 2 】**

また、図7(A)に示すように、図1または図4(A)の構成にトランジスタ118を付加した構成としてもよい。トランジスタ118のソースまたはドレインの一方は、トランジスタ113のソースまたはドレインの一方と電気的に接続される。トランジスタ118のソースまたはドレインの他方は、配線131と電気的に接続される。トランジスタ118のゲートは、配線132と電気的に接続される。配線132は、トランジスタの導通を制御する信号線としての機能を有することができる。

30

**【 0 1 2 3 】**

配線131は、基準電位などの特定の電位の供給源と電気的に接続することができる。配線131からトランジスタ113のソースまたはドレインの一方に特定の電位を供給することで、トランジスタ113のソース電位を確定させ、画像データの書き込みを安定化させることもできる。また、発光デバイス116Bの発光のタイミングを制御することもできる。

**【 0 1 2 4 】**

また、配線131は外部回路と接続することができ、モニタ線としての機能を有することもできる。当該外部回路は、上記特定の電位の供給源、トランジスタ111の電気特性を取得する機能、および補正データを生成する機能の一つ以上を有することができる。

**【 0 1 2 5 】**

また、本発明の一態様の画素回路においては、図7(B)に示すように、トランジスタにバックゲートを設けた構成としてもよい。図7(B)では、バックゲートがフロントゲートと電気的に接続された構成を示しており、オン電流を高める効果を有する。または、バックゲートが定電位を供給できる配線と電気的に接続された構成であつてもよい。当該構成では、トランジスタのしきい値電圧を制御することができる。当該構成は、図6(A)、(B)、図7(A)の構成にも適用することができる。

40

**【 0 1 2 6 】**

図8は、本発明の一態様の表示装置を説明するブロック図である。表示装置は、列方向および行方向に配置された画素10aと、ゲートドライバ12aと、ゲートドライバ12bと、ソースドライバ(データドライバ)13を有する。ゲートドライバ12aは、画素11R、画素11Gおよび画素11Bと電気的に接続される。ゲートドライバ12bは、画素11Bと電気的に接続される。ソースドライバ13は、画素11R、画素11Gおよび

50

画素 11 B と電気的に接続される。なお、ゲートドライバを分割する例を示したが、全ての画素が一つのゲートドライバに接続する形態であってもよい。

【 0 1 2 7 】

ゲートドライバ 12 a、12 b、ソースドライバ 13 には、例えば、シフトレジスタを用いることができる。また、シフトレジスタおよびバッファ回路を組み合わせた構成としてもよい。バッファ回路の導通を制御することにより、選択的に目的の配線に駆動信号または画像データを出力することができる。

【 0 1 2 8 】

なお、上記では画素 10 a を適用した表示装置を例示したが、画素 10 b または画素 10 c を適用した表示装置も同様の構成とすることができます。

10

【 0 1 2 9 】

本実施の形態は、他の実施の形態などに記載した構成と適宜組み合わせて実施することが可能である。

【 0 1 3 0 】

( 実施の形態 2 )

本実施の形態では、発光デバイスを用いた表示装置の構成例について説明する。なお、本実施の形態においては、実施の形態 1 で説明した表示装置の要素、動作および機能の説明は省略する。

【 0 1 3 1 】

図 9 ( A ) 乃至 ( C ) は、本発明の一態様を用いることのできる表示装置の構成を示す図である。

20

【 0 1 3 2 】

図 9 ( A ) において、第 1 の基板 4001 上に設けられた表示部 215 を囲むようにして、シール材 4005 が設けられ、表示部 215 がシール材 4005 および第 2 の基板 4006 によって封止されている。

【 0 1 3 3 】

表示部 215 には、実施の形態 1 の図 1 または図 4 に示した画素を設けることができる。なお、以下に説明する走査線駆動回路はゲートドライバ、信号線駆動回路はソースドライバに相当する。

【 0 1 3 4 】

30

図 9 ( A ) に示す、走査線駆動回路 221 a、信号線駆動回路 231 a、信号線駆動回路 232 a、および共通線駆動回路 241 a は、それぞれがプリント基板 4041 上に設けられた集積回路 4042 を複数有する。集積回路 4042 は、単結晶半導体または多結晶半導体を用いて形成されている。信号線駆動回路 231 a および信号線駆動回路 232 a は、実施の形態 1 に示したソースドライバの機能を有する。走査線駆動回路 221 a は、実施の形態 1 に示したゲートドライバの機能を有する。共通線駆動回路 241 a は、実施の形態 1 に示した電源線などに規定の電位を供給する機能を有する。

【 0 1 3 5 】

走査線駆動回路 221 a、共通線駆動回路 241 a、信号線駆動回路 231 a、および信号線駆動回路 232 a に与えられる各種信号および電位は、F P C ( F l e x i b l e p r i n t e d c i r c u i t ) 4018 を介して供給される。

40

【 0 1 3 6 】

走査線駆動回路 221 a および共通線駆動回路 241 a が有する集積回路 4042 は、表示部 215 に選択信号を供給する機能を有する。信号線駆動回路 231 a および信号線駆動回路 232 a が有する集積回路 4042 は、表示部 215 に画像データを供給する機能を有する。集積回路 4042 は、第 1 の基板 4001 上のシール材 4005 によって囲まれている領域とは異なる領域に実装されている。

【 0 1 3 7 】

なお、集積回路 4042 の接続方法は、特に限定されるものではなく、ワイヤボンディング法、C O G ( C h i p O n G l a s s ) 法、T C P ( T a p e C a r r i e r P

50

a c k a g e ) 法、 C O F ( C h i p O n F i l m ) 法などを用いることができる。

**【 0 1 3 8 】**

図 9 ( B ) は、信号線駆動回路 231a および信号線駆動回路 232a に含まれる集積回路 4042 を C O G 法により実装する例を示している。また、駆動回路の一部または全体を表示部 215 と同じ基板上に一体形成して、システムオンパネルを形成することができる。

**【 0 1 3 9 】**

図 9 ( B ) では、走査線駆動回路 221a および共通線駆動回路 241a を、表示部 215 と同じ基板上に形成する例を示している。駆動回路を表示部 215 内の画素回路と同時に形成することで、部品点数を削減することができる。よって、生産性を高めることができる。

10

**【 0 1 4 0 】**

また、図 9 ( B ) では、第 1 の基板 4001 上に設けられた表示部 215 と、走査線駆動回路 221a および共通線駆動回路 241a と、を囲むようにして、シール材 4005 が設けられている。また表示部 215 、走査線駆動回路 221a 、および共通線駆動回路 241a の上に第 2 の基板 4006 が設けられている。よって、表示部 215 、走査線駆動回路 221a 、および共通線駆動回路 241a は、第 1 の基板 4001 とシール材 4005 と第 2 の基板 4006 とによって、表示デバイスと共に封止されている。

**【 0 1 4 1 】**

また、図 9 ( B ) では、信号線駆動回路 231a および信号線駆動回路 232a を別途形成し、第 1 の基板 4001 に実装している例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して実装してもよいし、信号線駆動回路の一部または走査線駆動回路の一部を別途形成して実装してもよい。また、図 9 ( C ) に示すように、信号線駆動回路 231a および信号線駆動回路 232a を表示部 215 と同じ基板上に形成してもよい。

20

**【 0 1 4 2 】**

また、表示装置は、表示デバイスが封止された状態にあるパネルと、該パネルにコントローラを含む I C 等を実装した状態にあるモジュールとを含む場合がある。

**【 0 1 4 3 】**

また、第 1 の基板上に設けられた表示部および走査線駆動回路は、トランジスタを複数有している。周辺駆動回路が有するトランジスタと、表示部の画素回路が有するトランジスタの構造は同じであってもよく、異なっていてもよい。周辺駆動回路が有するトランジスタは、全て同じ構造であってもよく、2 種類以上の構造が組み合わせて用いられていてよい。同様に、画素回路が有するトランジスタは、全て同じ構造であってもよく、2 種類以上の構造が組み合わせて用いられていてよい。

30

**【 0 1 4 4 】**

また、第 2 の基板 4006 上には入力装置を設けることができる。図 9 に示す表示装置に入力装置を設けた構成はタッチパネルとして機能させることができる。

**【 0 1 4 5 】**

本発明の一態様のタッチパネルが有する検知素子（センサ素子ともいう）に限定は無い。指やスタイルスなどの被検知体の近接または接触を検知することのできる様々なセンサを、検知素子として適用することができる。

40

**【 0 1 4 6 】**

センサの方式としては、例えば、静電容量方式、抵抗膜方式、表面弹性波方式、赤外線方式、光学方式、感圧方式など様々な方式を用いることができる。

**【 0 1 4 7 】**

本実施の形態では、静電容量方式の検知素子を有するタッチパネルを例に挙げて説明する。

**【 0 1 4 8 】**

静電容量方式としては、表面型静電容量方式、投影型静電容量方式等がある。また、投影型静電容量方式としては、自己容量方式、相互容量方式等がある。相互容量方式を用いる

50

と、同時多点検知が可能となるため好ましい。

**【0149】**

本発明の一態様のタッチパネルは、別々に作製された表示装置と検知素子とを貼り合わせる構成、表示デバイスを支持する基板および対向基板の一方または双方に検知素子を構成する電極等を設ける構成等、様々な構成を適用することができる。

**【0150】**

図10(A)、(B)に、タッチパネルの一例を示す。図10(A)は、タッチパネル4210の斜視図である。図10(B)は、入力装置4200の斜視概略図である。なお、明瞭化のため、代表的な構成要素のみを示している。

**【0151】**

タッチパネル4210は、別々に作製された表示装置と検知素子とを貼り合わせた構成である。タッチパネル4210は、入力装置4200と、表示装置とを有し、これらが重ねて設けられている。

**【0152】**

入力装置4200は、基板4263、電極4227、電極4228、複数の配線4237、複数の配線4238および複数の配線4239を有する。例えば、電極4227は配線4237または配線4238と電気的に接続することができる。また、電極4228は配線4239と電気的に接続することができる。FPC4272bは、複数の配線4237および複数の配線4238および配線4239の各々と電気的に接続する。FPC4272bにはIC4273bを設けることができる。

10

**【0153】**

または、表示装置の第1の基板4001と第2の基板4006との間にタッチセンサを設けてもよい。第1の基板4001と第2の基板4006との間にタッチセンサを設ける場合は、静電容量方式のタッチセンサのほか、光電変換素子を用いた光学式のタッチセンサを適用してもよい。

**【0154】**

図11(A)および図11(B)は、図9(B)中でN1-N2の鎖線で示した部位の断面図である。図11(A)は第2の基板4006方向に光を射出するトップエミッション型の表示装置を示しており、図11(B)は第1の基板4001方向に光を射出するボトムエミッション型の表示装置を示している。本発明の一態様はどちらの型にも適用することができる。または、第1の基板4001の方向および第2の基板4006の方向に光を射出するデュアルエミッション型に適用することもできる。

20

**【0155】**

図11(A)および図11(B)に示す表示装置は電極4015を有しており、電極4015はFPC4018が有する端子と異方性導電層4019を介して、電気的に接続されている。また、図11(A)および図11(B)では、電極4015は、絶縁層4112、絶縁層4111、および絶縁層4110に形成された開口において配線4014と電気的に接続されている。

30

**【0156】**

電極4015は、第1の電極層4030と同じ導電層から形成され、配線4014は、トランジスタ4010、およびトランジスタ4011のソース電極およびドレイン電極と同じ導電層で形成されている。

40

**【0157】**

また、第1の基板4001上に設けられた表示部215と走査線駆動回路221aは、トランジスタを複数有しており、図11(A)、および図11(B)では、表示部215に含まれるトランジスタ4010、および走査線駆動回路221aに含まれるトランジスタ4011を例示している。なお、図11(A)および図11(B)では、トランジスタ4010およびトランジスタ4011としてボトムゲート型のトランジスタを例示しているが、トップゲート型のトランジスタであってもよい。

**【0158】**

50

図11(A)および図11(B)では、トランジスタ4010およびトランジスタ4011上に絶縁層4112が設けられている。また、絶縁層4112上に隔壁4510が形成されている。

#### 【0159】

また、トランジスタ4010およびトランジスタ4011は、絶縁層4102上に設けられている。また、トランジスタ4010およびトランジスタ4011は、絶縁層4111上に形成された電極4017を有する。電極4017はバックゲート電極として機能することができる。

#### 【0160】

また、図11(A)および図11(B)に示す表示装置は、キャパシタ4020を有する。キャパシタ4020は、トランジスタ4010のゲート電極と同じ工程で形成された電極4021と、ソース電極およびドレイン電極と同じ工程で形成された電極と、を有する。これらの電極は、絶縁層4103を介して重なっている。

10

#### 【0161】

一般に、表示装置の画素部に設けられるキャパシタの容量は、画素部に配置されるトランジスタのリーク電流等を考慮して、所定の期間の間電荷を保持できるように設定される。キャパシタの容量は、トランジスタのオフ電流等を考慮して設定すればよい。

#### 【0162】

表示部215に設けられたトランジスタ4010は表示デバイスと電気的に接続する。

20

#### 【0163】

また、図11(A)および図11(B)に示す表示装置は、絶縁層4111と絶縁層4104を有する。絶縁層4111と絶縁層4104として、不純物元素を透過しにくい絶縁層を用いる。絶縁層4111と絶縁層4104でトランジスタの半導体層を挟むことで、外部からの不純物の浸入を防ぐことができる。

#### 【0164】

また、表示装置に含まれる表示デバイスとして、エレクトロルミネッセンスを利用する発光デバイス(EL素子)を適用することができる。EL素子は、一対の電極の間に発光性の化合物を含む層(「EL層」ともいう。)を有する。一対の電極間に、EL素子のしきい値電圧よりも大きい電位差を生じさせると、EL層に陽極側から正孔が注入され、陰極側から電子が注入される。注入された電子と正孔はEL層において再結合し、EL層に含まれる発光物質が発光する。

30

#### 【0165】

EL素子としては、例えば、有機EL素子または無機EL素子を用いることができる。なお、発光材料として化合物半導体を用いるLED(ミニLED、マイクロLEDを含む)もEL素子の一つであり、LEDを用いることもできる。

#### 【0166】

有機EL素子は、電圧を印加することにより、一方の電極から電子、他方の電極から正孔がそれぞれEL層に注入される。そして、それらキャリア(電子および正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光デバイスは、電流励起型の発光デバイスと呼ばれる。

40

#### 【0167】

なお、EL層は、発光性の化合物以外に、正孔注入性の高い物質、正孔輸送性の高い物質、正孔ブロック材料、電子輸送性の高い物質、電子注入性の高い物質、またはバイポーラ性の物質(電子輸送性および正孔輸送性が高い物質)などを有していてもよい。

#### 【0168】

EL層は、蒸着法(真空蒸着法を含む)、転写法、印刷法、インクジェット法、塗布法などの方法で形成することができる。

#### 【0169】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分

50

類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー・アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。

#### 【0170】

また、発光デバイスとして、化合物半導体を用いたマイクロLEDを用いてもよい。なお、ここでは、発光デバイスとして有機EL素子を用いて説明する。

#### 【0171】

表示デバイスである発光デバイス4513は、表示部215に設けられたトランジスタ4010と電気的に接続している。なお発光デバイス4513の構成は、第1の電極層4030、EL層4511、第2の電極層4031の積層構造であるが、この構成に限定されない。発光デバイス4513から取り出す光の方向などに合わせて、発光デバイス4513の構成は適宜変えることができる。発光デバイス4513からの発光を取り出すため、発光デバイス4513は少なくとも一対の電極の一方が透光性を有していればよい。

10

#### 【0172】

隔壁4510は、有機絶縁材料、または無機絶縁材料を用いて形成する。特に感光性の樹脂材料を用い、第1の電極層4030上に開口部を形成し、その開口部の側面が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

#### 【0173】

トップエミッション型の場合は、図12(A)に示すように、隔壁4510上に配線4515を設けてもよい。トップエミッション型では第2の電極層4031が共通電極として設けられる。第2の電極層4031は光が射出する側に形成されるため、透光性導電膜が用いられる。透光性導電膜には金属よりも抵抗が高い酸化物導電膜などが用いられるため、電圧降下により表示部面内で表示品位が不均一となることがある。

20

#### 【0174】

したがって、金属などの低抵抗材料で配線4515を形成し、配線4515と第2の電極層4031が直接接するような構成とする。このような構成とすることで、配線4515は第2の電極層4031の抵抗を実質的に低下させるための補助配線として機能させることができ、表示品位を向上させることができる。

30

#### 【0175】

なお、配線4515は、図12(B)に示すように絶縁層4112上に設けてもよい。当該構成の場合、配線4515は第1の電極層4030を形成する工程を利用して作製することができる。または、トランジスタのゲート電極を形成する工程を利用して作製してもよい。または、トランジスタのソース電極(ドレイン電極)を形成する工程を利用して作製してもよい。または、第2の電極層4031上に配線4515を形成してもよい。

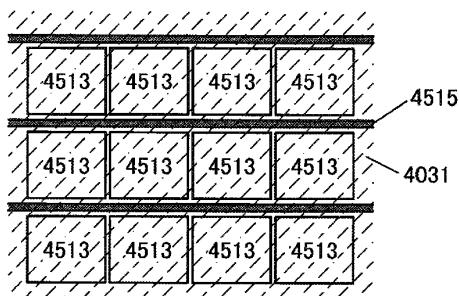

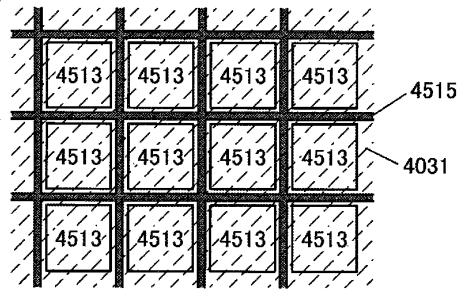

#### 【0176】

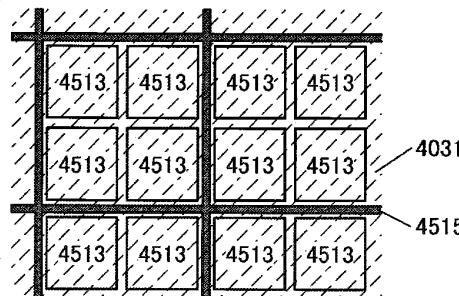

配線4515は、図13(A)乃至(C)に示すように、発光デバイス4513と重ならない領域に設けることができる。図13(A)乃至(C)は、表示部の上面図の一部を示している。例えば、図13(A)に示すように表示部の行方向または列方向に延在するように配線4515を設けることができる。または、図13(B)に示すように、行方向および列方向に延在するように配線4515を設けてもよい。なお、配線4515が設けられる間隔は発光デバイス4513の間隔(画素の間隔)でなくともよく、図13(C)に示すように複数の発光デバイス4513を挟む間隔で設けてもよい。

40

#### 【0177】

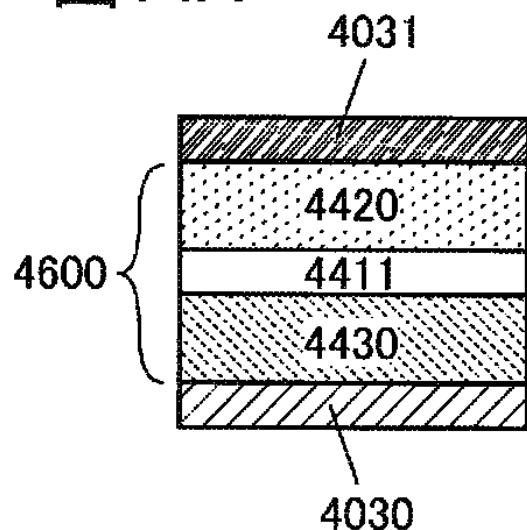

EL層4511は、図14(A)に示すように、層4420、発光層4411、層4430などの複数の層で構成することができる。層4420は、例えば電子注入性の高い物質を含む層(電子注入層)および電子輸送性の高い物質を含む層(電子輸送層)などを有することができる。発光層4411は、例えば発光性の化合物を有する。層4430は、例えば正孔注入性の高い物質を含む層(正孔注入層)および正孔輸送性の高い物質を含む層

50

(正孔輸送層)を有することができる。

**【0178】**

一対の電極間に設けられた層4420、発光層4411および層4430を有する構成は单一の発光ユニット4600として機能することができ、本明細書では図14(A)の構成をシングル構造と呼ぶ。

**【0179】**

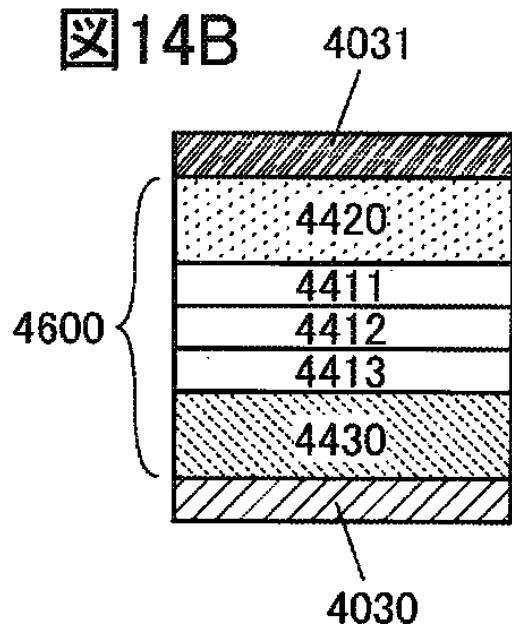

なお、図14(B)に示すように層4420と層4430との間に複数の発光層(発光層4411、4412、4413)が設けられる構成もシングル構造のバリエーションである。

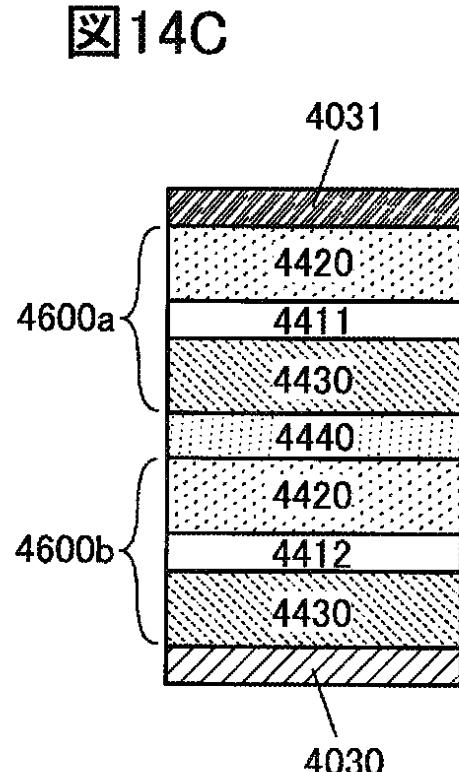

**【0180】**

また、図14(C)に示すように、複数の発光ユニット4600(発光ユニット4600a、4600b)が中間層(電荷発生層)4440を介して直列に接続された構成を本明細書ではタンデム構造と呼ぶ。実施の形態1で説明した2層タンデムの青色発光デバイスの場合は、図14(C)に示す構成とし、発光ユニット4600aが有する発光層4411および発光ユニット4600bが有する発光層4412に青色を発する発光層を用いればよい。なお、本明細書等においては、図14(C)に示すような構成をタンデム構造として呼称するが、これに限定されず、例えば、タンデム構造をスタック構造と呼んでもよい。

10

**【0181】**

発光デバイス4513の発光色は、EL層4511を構成する材料によって、赤、緑、青、シアン、マゼンタ、黄または白などとすることができます。また、発光デバイス4513にマイクロキャビティ構造を付与することにより色純度をさらに高めることができる。

20

**【0182】**

白色の光を発する発光デバイスは、発光層に2種類以上の発光物質を含む構成とすることが好ましい。白色発光を得るには、2以上の発光物質の各々の発光が補色の関係となるような発光物質を選択すればよい。

**【0183】**

発光層には、R(赤)、G(緑)、B(青)、Y(黄)、O(橙)等の発光を示す発光物質を2以上含むことが好ましい。または、発光物質が2以上有し、それぞれの発光物質の発光は、R、G、Bのうち2以上の色のスペクトル成分を含むことが好ましい。

30

**【0184】**

また、発光デバイスからの発光のスペクトルが、可視光領域の波長(例えば350nm乃至750nm)の範囲内に2以上のピークを有する発光デバイスを適用することができます。また、黄色の波長領域にピークを有する材料の発光スペクトルは、緑色および/または赤色の波長領域にもスペクトル成分を有する材料であることが好ましい。

**【0185】**

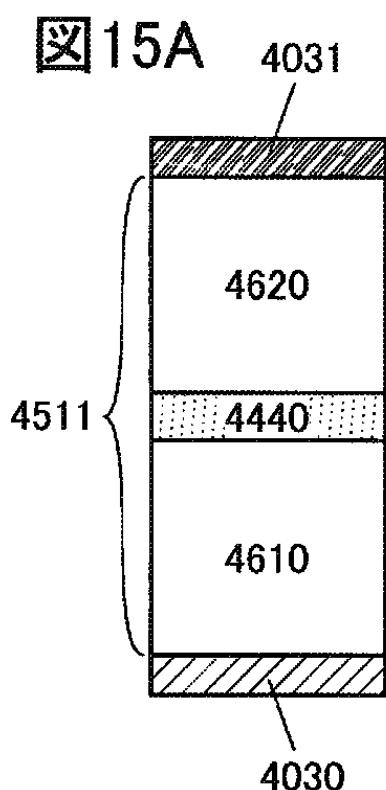

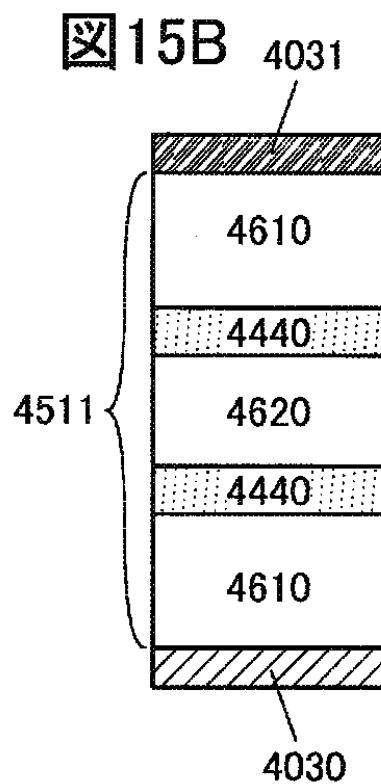

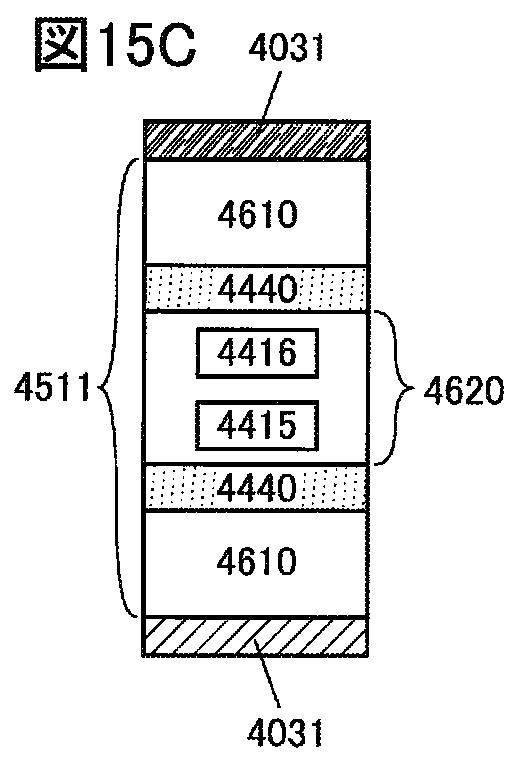

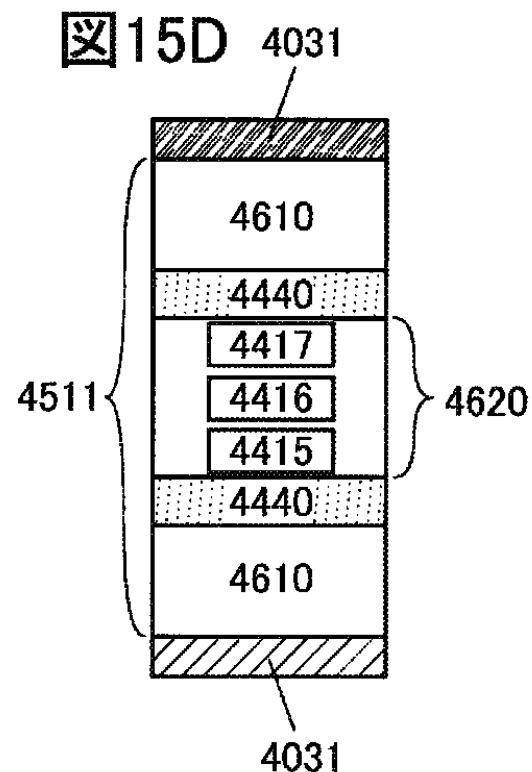

具体的には、図15(A)乃至(D)に示すように、EL層4511は、青の発光を示す発光物質を有する発光ユニット4610と、青の補色である黄の発光を示す発光物質を有する発光ユニット4620を直列接続した2層タンデム構造とすることができる。

**【0186】**

または、図15(B)に示すように、発光ユニット4620を発光ユニット4610で挟む形の3層タンデム構造としてもよい。

40

**【0187】**

また、発光ユニット4620は、図15(C)に示すように、発光層4415および発光層4416を有する構造としてもよい。発光層4415および発光層4416は発光色が異なり、黄の発光を示す発光物質を有する層、赤の発光を示す発光物質を有する層、および緑の発光を示す発光物質を有する層のいずれかを用いることができる。

**【0188】**

また、発光ユニット4620は、図15(D)に示すように、発光層4415、発光層4416および発光層4417を有する構造としてもよい。発光層4415、発光層441

50

6および発光層4417はそれぞれ発光色が異なり、黄の発光を示す発光物質を有する層、赤の発光を示す発光物質を有する層、および緑の発光を示す発光物質を有する層のいずれかを用いることができる。

【0189】

黄の発光を行う層に赤および/または緑の発光を行う層を加えることで、色域を広げることができ、表示品位を向上させることができる。

【0190】

なお、EL層4511は、量子ドットなどの無機化合物を有していてもよい。例えば、量子ドットを発光層に用いることで、発光材料として機能させることもできる。

【0191】

量子ドット材料としては、コロイド状量子ドット材料、合金型量子ドット材料、コア・シェル型量子ドット材料、コア型量子ドット材料などを用いることができる。また、12族と16族、13族と15族、または14族と16族の元素グループを含む材料を用いてもよい。または、カドミウム、セレン、亜鉛、硫黄、リン、インジウム、テルル、鉛、ガリウム、ヒ素、アルミニウム等の元素を含む量子ドット材料を用いてもよい。

10

【0192】

発光デバイス4513に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の電極層4031および隔壁4510上に保護層を形成してもよい。保護層としては、窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、DLC (Diamond Like Carbon)などを形成することができる。また、第1の基板4001、第2の基板4006、およびシール材4005によって封止された空間には充填材4514が設けられ密封されている。このように、外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することが好ましい。

20

【0193】

充填材4514としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル系樹脂、ポリイミド、エポキシ系樹脂、シリコーン系樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)などを用いることができる。また、充填材4514に乾燥剤が含まれていてもよい。

30

【0194】

シール材4005には、ガラスフリットなどのガラス材料や、二液混合型の樹脂などの常温で硬化する硬化樹脂、光硬化性の樹脂、熱硬化性の樹脂などの樹脂材料を用いることができる。また、シール材4005に乾燥剤が含まれていてもよい。

【0195】

また、必要に応じて、発光デバイスの射出面に偏光板、または円偏光板(楕円偏光板を含む)、位相差板(1/4板、1/2板)、カラーフィルタなどの光学フィルムを適宜設けてもよい。また、偏光板または円偏光板に反射防止膜を設けてもよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

40

【0196】

表示デバイスに電圧を印加する第1の電極層および第2の電極層(画素電極層、共通電極層、対向電極層などともいう)においては、取り出す光の方向、電極層が設けられる場所、および電極層のパターン構造によって透光性、反射性を選択すればよい。

【0197】

第1の電極層4030、第2の電極層4031は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、インジウム錫酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

50

**【 0 1 9 8 】**

また、第1の電極層4030、第2の電極層4031はタンゲステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、チタン(Ti)、白金(Pt)、アルミニウム(Al)、銅(Cu)、銀(Ag)などの金属、またはその合金、もしくはその金属窒化物から一種以上を用いて形成することができる。

**【 0 1 9 9 】**

また、第1の電極層4030、第2の電極層4031として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性高分子としては、いわゆる電子共役系導電性高分子を用いることができる。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリチオフェン若しくはその誘導体、または、アニリン、ピロールおよびチオフェンの2種以上からなる共重合体若しくはその誘導体などがあげられる。

10

**【 0 2 0 0 】**

また、表示装置の駆動回路が有するトランジスタは静電気などにより破壊されやすいため、保護回路を設けることが好ましい。保護回路は、非線形素子を用いて構成することができる。

20

**【 0 2 0 1 】**

本実施の形態は、他の実施の形態などに記載した構成と適宜組み合わせて実施することができる。

**【 0 2 0 2 】****( 実施の形態 3 )**

本実施の形態では、上記実施の形態に示した各トランジスタに置き換えて用いることのできるトランジスタの一例について、図面を用いて説明する。

**【 0 2 0 3 】**

本発明の一態様の表示装置は、ボトムゲート型のトランジスタや、トップゲート型トランジスタなどの様々な形態のトランジスタを用いて作製することができる。よって、既存の製造ラインに合わせて、使用する半導体層の材料やトランジスタ構造を容易に置き換えることができる。

30

**【 0 2 0 4 】****( ボトムゲート型トランジスタ )**

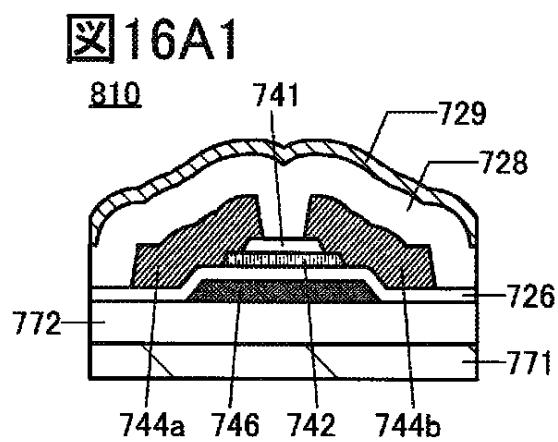

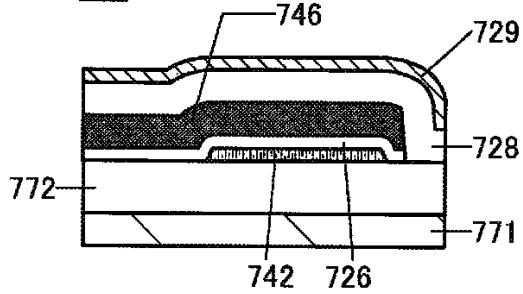

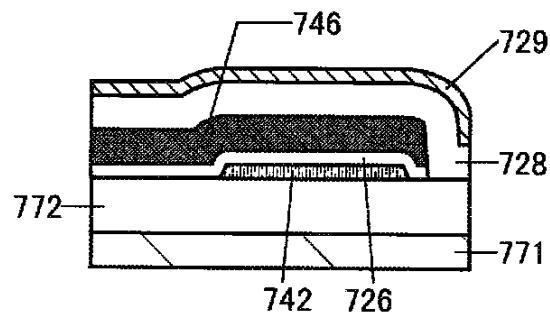

図16(A1)は、ボトムゲート型のトランジスタの一種であるチャネル保護型のトランジスタ810のチャネル長方向の断面図である。図16(A1)において、トランジスタ810は基板771上に形成されている。また、トランジスタ810は、基板771上に絶縁層772を介して電極746を有する。また、電極746上に絶縁層726を介して半導体層742を有する。電極746はゲート電極として機能できる。絶縁層726はゲート絶縁層として機能できる。

**【 0 2 0 5 】**

また、半導体層742のチャネル形成領域上に絶縁層741を有する。また、半導体層742の一部と接して、絶縁層726上に電極744aおよび電極744bを有する。電極744aは、ソース電極またはドレイン電極の一方として機能できる。電極744bは、ソース電極またはドレイン電極の他方として機能できる。電極744aの一部、および電極744bの一部は、絶縁層741上に形成される。

40

**【 0 2 0 6 】**

絶縁層741は、チャネル保護層として機能できる。チャネル形成領域上に絶縁層741を設けることで、電極744aおよび電極744bの形成時に生じる半導体層742の露出を防ぐことができる。よって、電極744aおよび電極744bの形成時に、半導体層742のチャネル形成領域がエッチングされることを防ぐことができる。本発明の一態様によれば、電気特性の良好なトランジスタを実現することができる。

**【 0 2 0 7 】**

50

また、トランジスタ 810 は、電極 744a、電極 744b および絶縁層 741 上に絶縁層 728 を有し、絶縁層 728 の上に絶縁層 729 を有する。

#### 【0208】

半導体層 742 に酸化物半導体を用いる場合、電極 744a および電極 744b の、少なくとも半導体層 742 と接する部分に、半導体層 742 の一部から酸素を奪い、酸素欠損を生じさせることができ材料を用いることが好ましい。半導体層 742 中の酸素欠損が生じた領域はキャリア濃度が増加し、当該領域は n 型化し、n 型領域 (n<sup>+</sup> 領域) となる。したがって、当該領域はソース領域またはドレイン領域として機能することができる。半導体層 742 に酸化物半導体を用いる場合、半導体層 742 から酸素を奪い、酸素欠損を生じさせることができ材料の一例として、タンゲステン、チタン等を挙げることができる。

10

#### 【0209】

半導体層 742 にソース領域およびドレイン領域が形成されることにより、電極 744a および電極 744b と半導体層 742 の接触抵抗を低減することができる。よって、電界効果移動度や、しきい値電圧などの、トランジスタの電気特性を良好なものとすることができる。

#### 【0210】

半導体層 742 にシリコンなどの半導体を用いる場合は、半導体層 742 と電極 744a の間、および半導体層 742 と電極 744b の間に、n 型半導体または p 型半導体として機能する層を設けることが好ましい。n 型半導体または p 型半導体として機能する層は、トランジスタのソース領域またはドレイン領域として機能することができる。

20

#### 【0211】

絶縁層 729 は、外部からのトランジスタへの不純物の拡散を防ぐ、または低減する機能を有する材料を用いて形成することができ。なお、必要に応じて絶縁層 729 を省略することもできる。

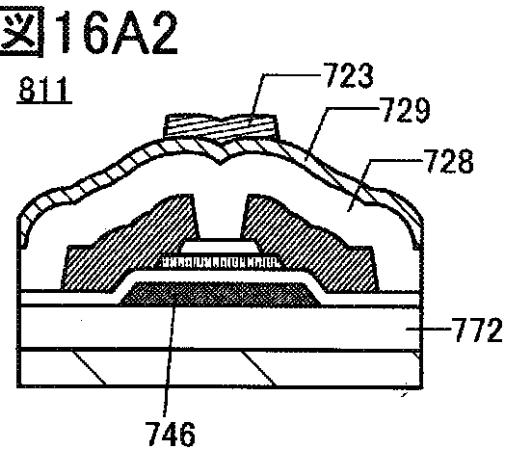

#### 【0212】

図 16 (A2) に示すトランジスタ 811 は、絶縁層 729 上にバックゲート電極として機能できる電極 723 を有する点が、トランジスタ 810 と異なる。電極 723 は、電極 746 と同様の材料および方法で形成することができる。

30

#### 【0213】

一般に、バックゲート電極は導電層で形成され、ゲート電極とバックゲート電極で半導体層のチャネル形成領域を挟むように配置される。よって、バックゲート電極は、ゲート電極と同様に機能させることができ。バックゲート電極の電位は、ゲート電極と同電位としてもよいし、接地電位 (GND 電位) や、任意の電位としてもよい。また、バックゲート電極の電位をゲート電極と連動させず独立して変化させることで、トランジスタのしきい値電圧を変化させることができる。

#### 【0214】

また、電極 746 および電極 723 は、どちらもゲート電極として機能することができる。よって、絶縁層 726、絶縁層 728、および絶縁層 729 は、それぞれがゲート絶縁層として機能することができる。なお、電極 723 は、絶縁層 728 と絶縁層 729 の間に設けてもよい。

40

#### 【0215】

なお、電極 746 または電極 723 の一方を、「ゲート電極」という場合、他方を「バックゲート電極」という。例えば、トランジスタ 811 において、電極 723 を「ゲート電極」と言う場合、電極 746 を「バックゲート電極」と言う。また、電極 723 を「ゲート電極」として用いる場合は、トランジスタ 811 をトップゲート型のトランジスタの一種と考えることができる。また、電極 746 および電極 723 のどちらか一方を、「第 1 のゲート電極」といい、他方を「第 2 のゲート電極」という場合がある。

#### 【0216】

半導体層 742 を挟んで電極 746 および電極 723 を設けることで、更には、電極 74

50

6 および電極 723 を同電位とすることで、半導体層 742 においてキャリアの流れる領域が膜厚方向においてより大きくなるため、キャリアの移動量が増加する。この結果、トランジスタ 811 のオン電流が大きくなると共に、電界効果移動度が高くなる。

#### 【0217】

したがって、トランジスタ 811 は、占有面積に対して大きいオン電流を有するトランジスタである。すなわち、求められるオン電流に対して、トランジスタ 811 の占有面積を小さくすることができる。本発明の一態様によれば、トランジスタの占有面積を小さくすることができる。よって、本発明の一態様によれば、集積度の高い半導体装置を実現することができる。

#### 【0218】

また、ゲート電極とバックゲート電極は導電層で形成されるため、トランジスタの外部で生じる電界が、チャネルが形成される半導体層に作用しないようにする機能（特に静電気などに対する電界遮蔽機能）を有する。なお、バックゲート電極を半導体層よりも大きく形成し、バックゲート電極で半導体層を覆うことで、電界遮蔽機能を高めることができる。

#### 【0219】

また、バックゲート電極を、遮光性を有する導電膜で形成することで、バックゲート電極側から半導体層に光が入射することを防ぐことができる。よって、半導体層の光劣化を防ぎ、トランジスタのしきい値電圧がシフトするなどの電気特性の劣化を防ぐことができる。

#### 【0220】

本発明の一態様によれば、信頼性の良好なトランジスタを実現することができる。また、信頼性の良好な半導体装置を実現することができる。

#### 【0221】

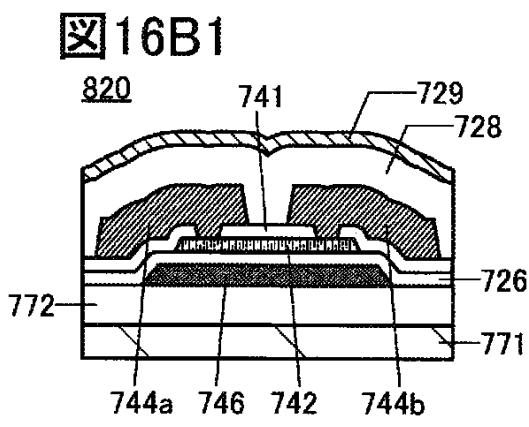

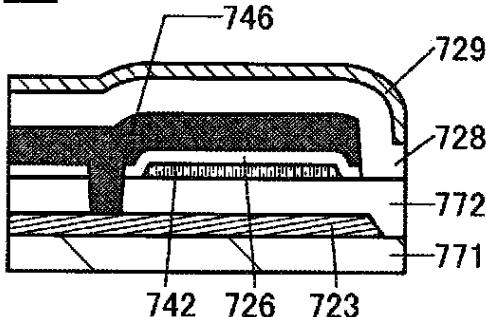

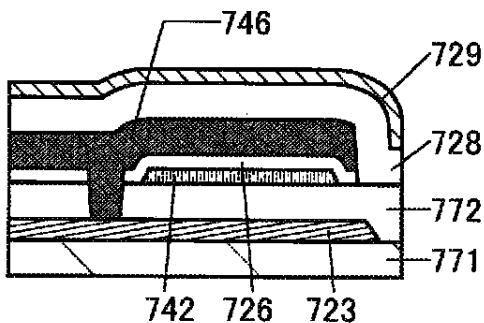

図 16 (B1) は、図 16 (A1) とは異なる構成のチャネル保護型のトランジスタ 820 のチャネル長方向の断面図である。トランジスタ 820 は、トランジスタ 810 とほぼ同様の構造を有しているが、絶縁層 741 が半導体層 742 の端部を覆っている点が異なる。また、半導体層 742 と重なる絶縁層 741 の一部を選択的に除去して形成した開口部において、半導体層 742 と電極 744a が電気的に接続している。また、半導体層 742 と重なる絶縁層 741 の一部を選択的に除去して形成した他の開口部において、半導体層 742 と電極 744b が電気的に接続している。絶縁層 741 の、チャネル形成領域と重なる領域は、チャネル保護層として機能できる。

#### 【0222】

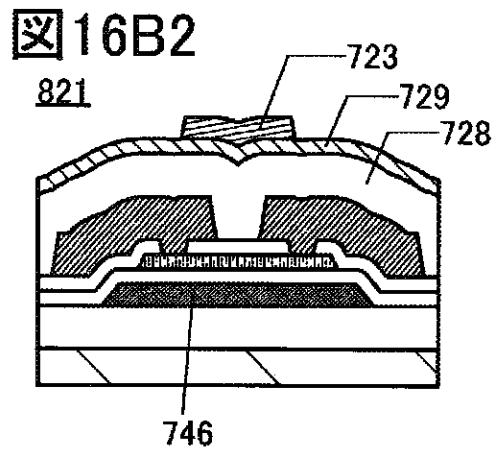

図 16 (B2) に示すトランジスタ 821 は、絶縁層 729 上にバックゲート電極として機能できる電極 723 を有する点が、トランジスタ 820 と異なる。

#### 【0223】

絶縁層 741 を設けることで、電極 744a および電極 744b の形成時に生じる半導体層 742 の露出を防ぐことができる。よって、電極 744a および電極 744b の形成時に半導体層 742 の薄膜化を防ぐことができる。

#### 【0224】

また、トランジスタ 820 およびトランジスタ 821 は、トランジスタ 810 およびトランジスタ 811 よりも、電極 744a と電極 746 の間の距離と、電極 744b と電極 746 の間の距離が長くなる。よって、電極 744a と電極 746 の間に生じる寄生容量を小さくすることができる。また、電極 744b と電極 746 の間に生じる寄生容量を小さくすることができる。本発明の一態様によれば、電気特性の良好なトランジスタを実現できる。

#### 【0225】

図 16 (C1) に示すトランジスタ 825 は、ボトムゲート型のトランジスタの 1 つであるチャネルエッチング型のトランジスタ 825 のチャネル長方向の断面図である。トランジスタ 825 は、絶縁層 741 を用いずに電極 744a および電極 744b を形成する。このため、電極 744a および電極 744b の形成時に露出する半導体層 742 の一部がエッチングされる場合がある。一方、絶縁層 741 を設けないため、トランジスタの生産

10

20

30

40

50

性を高めることができる。

【0226】

図16(C2)に示すトランジスタ826は、絶縁層729上にバックゲート電極として機能できる電極723を有する点が、トランジスタ825と異なる。

【0227】

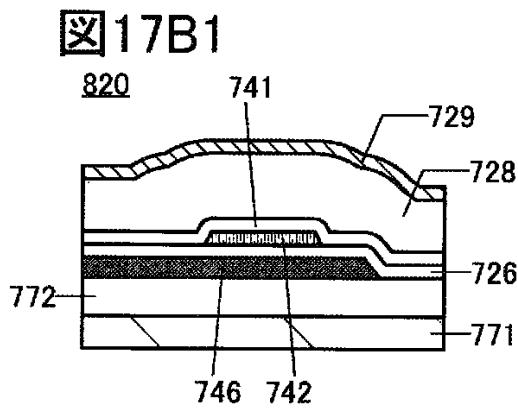

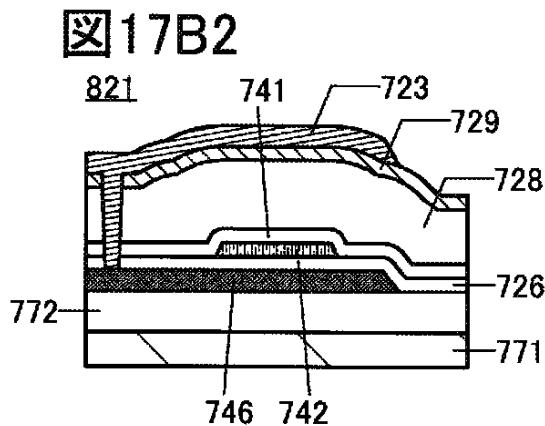

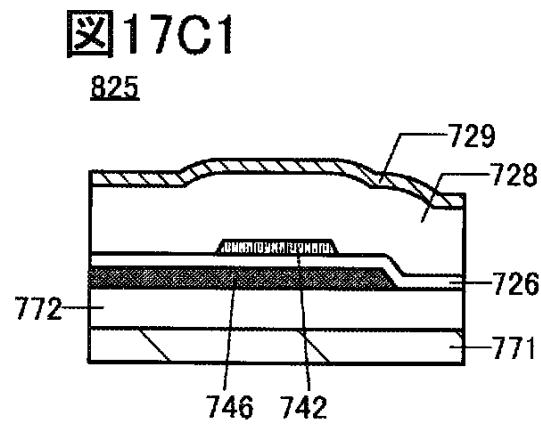

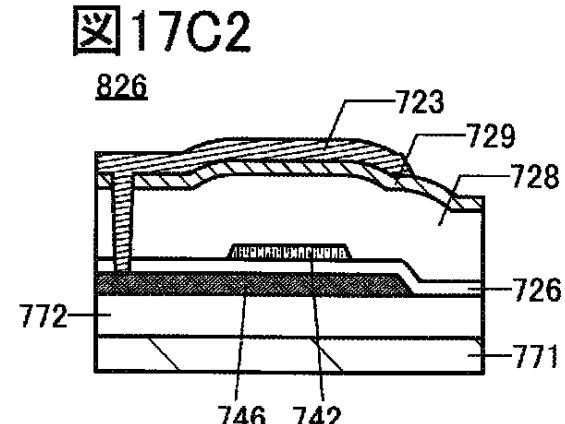

図17(A1)乃至(C2)にトランジスタ810、811、820、821、825、826のチャネル幅方向の断面図をそれぞれ示す。

【0228】

図17(B2)、(C2)に示す構造では、ゲート電極とバックゲート電極とが接続され、ゲート電極とバックゲート電極との電位が同電位となる。また、半導体層742は、ゲート電極とバックゲート電極に挟まれている。10

【0229】

ゲート電極およびバックゲート電極のそれぞれのチャネル幅方向の長さは、半導体層742のチャネル幅方向の長さよりも長く、半導体層742のチャネル幅方向全体は、絶縁層726、741、728、729を間に挟んでゲート電極またはバックゲート電極に覆われた構成である。

【0230】

当該構成とすることで、トランジスタに含まれる半導体層742を、ゲート電極およびバックゲート電極の電界によって電気的に取り囲むことができる。

【0231】

トランジスタ821またはトランジスタ826のように、ゲート電極およびバックゲート電極の電界によって、チャネル形成領域が形成される半導体層742を電気的に取り囲むトランジスタのデバイス構造をSurrounded channel(S-channel)構造と呼ぶことができる。20

【0232】

S-channel構造とすることで、ゲート電極およびバックゲート電極の一方または双方によってチャネルを誘起させるための電界を効果的に半導体層742に印加することができるため、トランジスタの電流駆動能力が向上し、高いオン電流特性を得ることが可能となる。また、オン電流を高くすることが可能であるため、トランジスタを微細化することが可能となる。また、S-channel構造とすることで、トランジスタの機械的強度を高めることができる。30

【0233】

〔トップゲート型トランジスタ〕

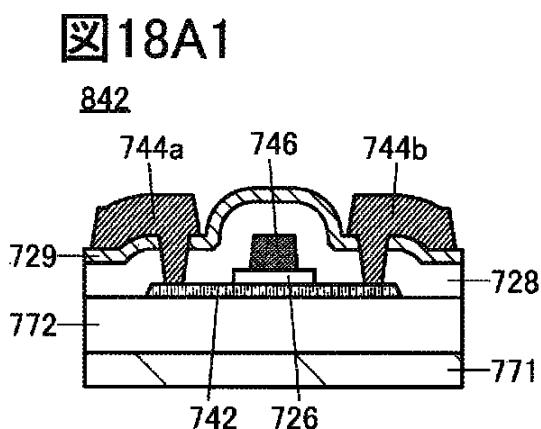

図18(A1)に例示するトランジスタ842は、トップゲート型のトランジスタの1つである。電極744aおよび電極744bは、絶縁層728および絶縁層729に形成した開口部において半導体層742と電気的に接続する。

【0234】

また、電極746と重ならない絶縁層726の一部を除去し、電極746と残りの絶縁層726をマスクとして用いて不純物を半導体層742に導入することで、半導体層742中に自己整合(セルフアライメント)的に不純物領域を形成することができる。トランジスタ842は、絶縁層726が電極746の端部を越えて延伸する領域を有する。半導体層742の絶縁層726を介して不純物が導入された領域の不純物濃度は、絶縁層726を介さずに不純物が導入された領域よりも小さくなる。よって、半導体層742は、絶縁層726と重なる領域であって、電極746と重ならない領域にLDD(Lightly Doped Drain)領域が形成される。40

【0235】

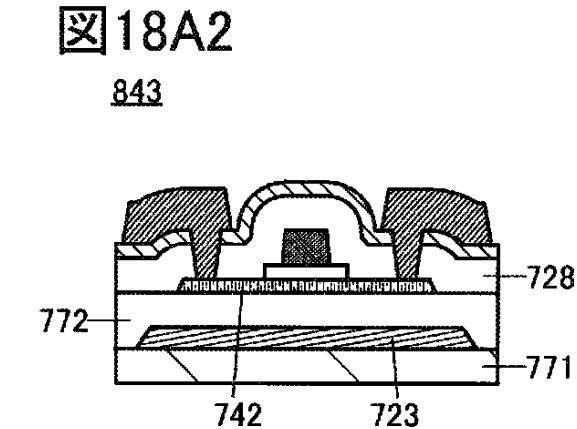

図18(A2)に示すトランジスタ843は、電極723を有する点がトランジスタ842と異なる。トランジスタ843は、基板771の上に形成された電極723を有する。電極723は、絶縁層772を介して半導体層742と重なる領域を有する。電極723は、バックゲート電極として機能することができる。50

**【0236】**

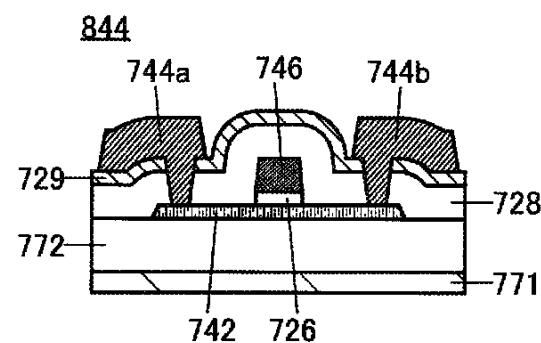

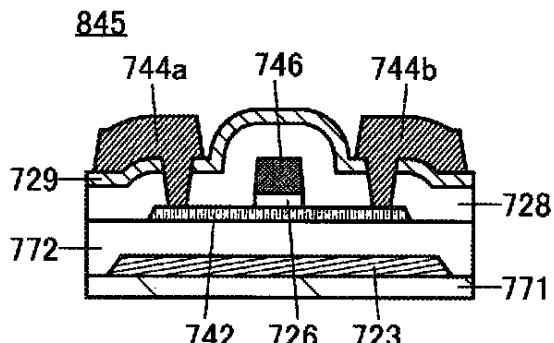

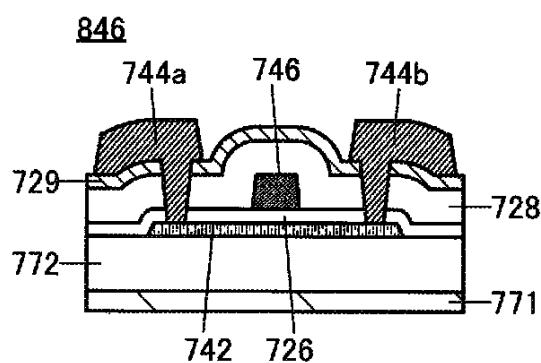

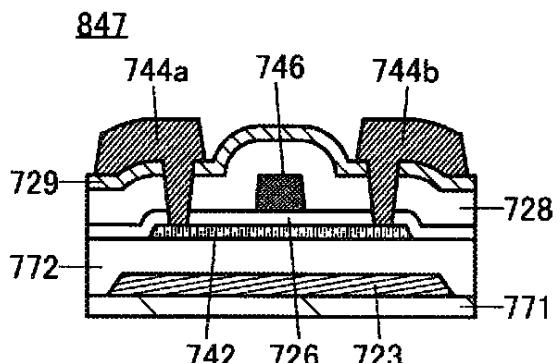

また、図18(B1)に示すトランジスタ844および図18(B2)に示すトランジスタ845のように、電極746と重ならない領域の絶縁層726を全て除去してもよい。また、図18(C1)に示すトランジスタ846および図18(C2)に示すトランジスタ847のように、絶縁層726を残してもよい。

**【0237】**

トランジスタ842乃至トランジスタ847も、電極746を形成した後に、電極746をマスクとして用いて不純物を半導体層742に導入することで、半導体層742中に自己整合的に不純物領域を形成することができる。本発明の一態様によれば、電気特性の良好なトランジスタを実現することができる。また、本発明の一態様によれば、集積度の高い半導体装置を実現することができる。

10

**【0238】**

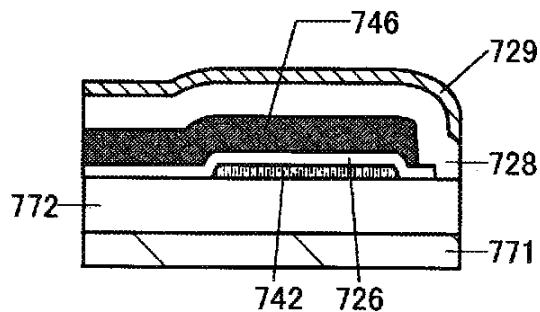

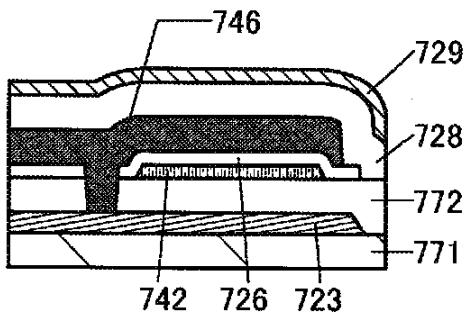

図19(A1)乃至(C2)にトランジスタ842、843、844、845、846、847のチャネル幅方向の断面図をそれぞれ示す。

**【0239】**

トランジスタ843、トランジスタ845、およびトランジスタ847は、それぞれ先に説明したS-channel構造である。ただし、これに限定されず、トランジスタ843、トランジスタ845、およびトランジスタ847をS-channel構造としなくてもよい。

**【0240】**

本実施の形態は、他の実施の形態などに記載した構成と適宜組み合わせて実施することができる。

20

**【0241】****(実施の形態4)**

本発明の一態様に係る表示装置を用いることができる電子機器として、表示機器、パーソナルコンピュータ、記録媒体を備えた画像記憶装置または画像再生装置、携帯電話、携帯型を含むゲーム機、携帯データ端末、電子書籍端末、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレイヤー等)、複写機、ファクシミリ、プリンタ、プリンタ複合機、現金自動預け入れ払い機(ATM)、自動販売機などが挙げられる。これら電子機器の具体例を図20(A)乃至(F)に示す。

30

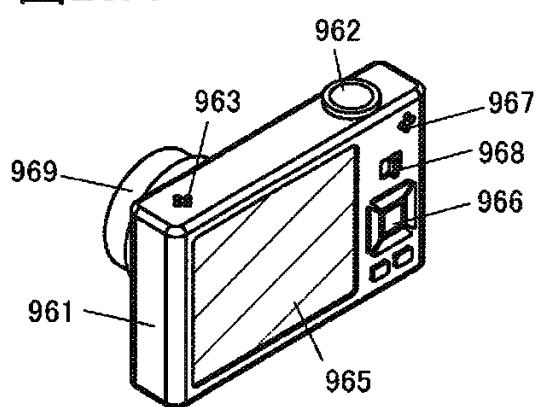

**【0242】**

図20(A)はデジタルカメラであり、筐体961、シャッターボタン962、マイク963、スピーカ967、表示部965、操作キー966、ズームレバー968、レンズ969等を有する。表示部965に本発明の一態様の表示装置を用いることで、様々な画像の表示を行うことができる。表示部965には、特に本発明の一態様である画素10aを用いることが適している。

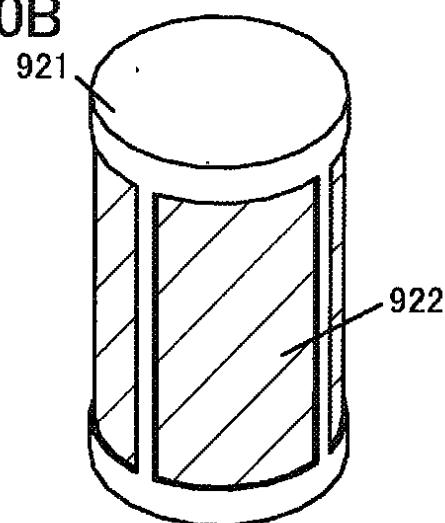

**【0243】**

図20(B)はデジタルサイネージであり、大型の表示部922を有する。例えば、柱921の側面に取り付けることができる。表示部922に本発明の一態様の表示装置を用いることで、表示品位の高い表示を行うことができる。表示部965には、特に本発明の一態様である画素10a、画素10b、または画素10cを用いることが適している。

40

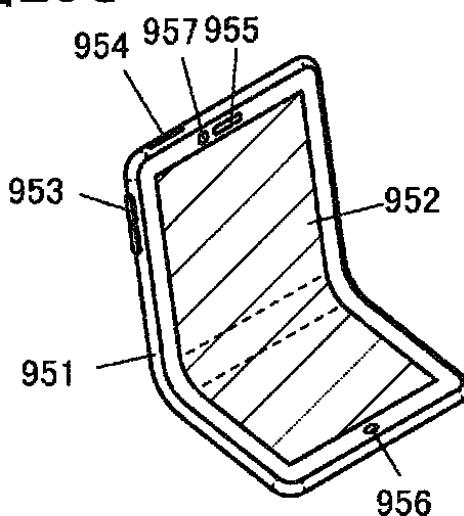

**【0244】**

図20(C)は携帯電話機の一例であり、筐体951、表示部952、操作ボタン953、外部接続ポート954、スピーカ955、マイク956、カメラ957等を有する。当該携帯電話機は、表示部952にタッチセンサを備える。電話を掛ける、或いは文字を入力するなどのあらゆる操作は、指やスタイルスなどで表示部952に触れることで行うことができる。また、筐体951および表示部952は可撓性を有し、図示するように折り曲げて使用することができる。表示部952に本発明の一態様の表示装置を用いることで、様々な画像の表示を行うことができる。表示部965には、特に本発明の一態様である

50

画素 10 a を用いることが適している。

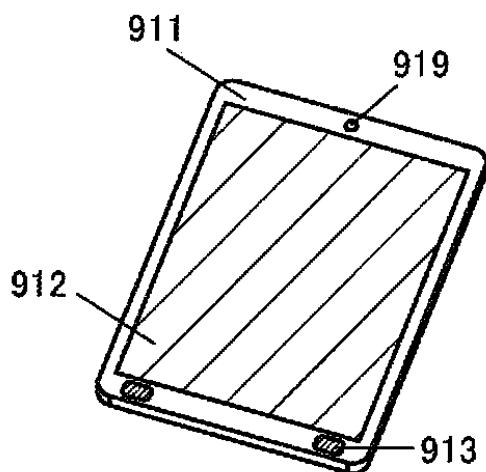

**【 0 2 4 5 】**

図 20 ( D ) は携帯データ端末であり、筐体 911 、表示部 912 、スピーカ 913 、カメラ 919 等を有する。表示部 912 が有するタッチパネルにより情報の入出力を行うことができる。表示部 912 に本発明の一態様の表示装置を用いることで、様々な画像の表示を行うことができる。表示部 965 には、特に本発明の一態様である画素 10 a を用いることが適している。

**【 0 2 4 6 】**

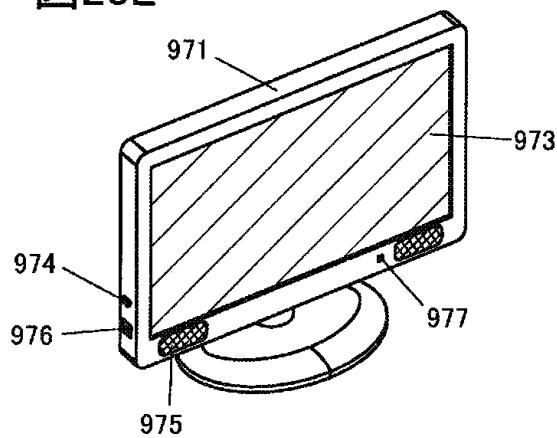

図 20 ( E ) はテレビであり、筐体 971 、表示部 973 、操作キー 974 、スピーカ 975 、通信用接続端子 976 、光センサ 977 等を有する。表示部 973 にはタッチセンサが設けられ、入力操作を行うこともできる。表示部 973 に本発明の一態様の表示装置を用いることで、様々な画像の表示を行うことができる。表示部 973 には、特に本発明の一態様である画素 10 a 、画素 10 b 、または画素 10 c を用いることが適している。

10

**【 0 2 4 7 】**

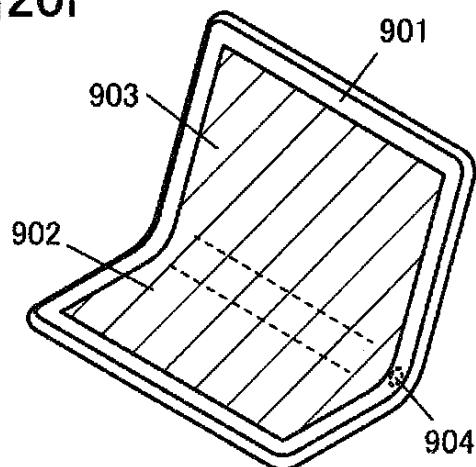

図 20 ( F ) は情報処理端末であり、筐体 901 、表示部 902 、表示部 903 、センサ 904 等を有する。表示部 902 および表示部 903 は一つの表示パネルから成り、可撓性を有する。また、筐体 901 も可撓性を有し、図示するように折り曲げて使用することができるほか、タブレット端末のように平板状にして使用することもできる。センサ 904 は筐体 901 の形状を感知することができ、例えば、筐体が曲げられたときに表示部 902 および表示部 903 の表示を切り替えることができる。表示部 902 および表示部 903 に本発明の一態様の表示装置を用いることで、様々な画像の表示を行うことができる。表示部 902 および表示部 903 には、特に本発明の一態様である画素 10 a を用いることが適している。

20

**【 0 2 4 8 】**

本実施の形態は、他の実施の形態などに記載した構成と適宜組み合わせて実施することが可能である。

**【 符号の説明 】**

**【 0 2 4 9 】**

10 a : 画素、 10 b : 画素、 10 c : 画素、 11 : 画素、 11 B : 画素、 11 G : 画素、 11 R : 画素、 11 W : 画素、 12 a : ゲートドライバ、 12 b : ゲートドライバ、 13 : ソースドライバ、 101 : トランジスタ、 102 : トランジスタ、 103 : キャパシタ、 106 G : 発光デバイス、 106 R : 発光デバイス、 111 : トランジスタ、 112 : トランジスタ、 113 : トランジスタ、 114 : キャパシタ、 115 : キャパシタ、 116 B : 発光デバイス、 116 W : 発光デバイス、 117 : トランジスタ、 118 : トランジスタ、 119 : ダイオード、 120 : 発光デバイス、 121 : 配線、 122 : 配線、 123 : 配線、 124 : 配線、 128 : 配線、 129 : 配線、 130 : 配線、 131 : 配線、 132 : 配線、 215 : 表示部、 221 a : 走査線駆動回路、 231 a : 信号線駆動回路、 232 a : 信号線駆動回路、 241 a : 共通線駆動回路、 723 : 電極、 726 : 絶縁層、 728 : 絶縁層、 729 : 絶縁層、 741 : 絶縁層、 742 : 半導体層、 744 a : 電極、 744 b : 電極、 746 : 電極、 771 : 基板、 772 : 絶縁層、 810 : トランジスタ、 811 : トランジスタ、 820 : トランジスタ、 821 : トランジスタ、 825 : トランジスタ、 826 : トランジスタ、 842 : トランジスタ、 843 : トランジスタ、 844 : トランジスタ、 845 : トランジスタ、 846 : トランジスタ、 847 : トランジスタ、 901 : 筐体、 902 : 表示部、 903 : 表示部、 904 : センサ、 911 : 筐体、 912 : 表示部、 913 : スピーカ、 919 : カメラ、 921 : 柱、 922 : 表示部、 951 : 筐体、 952 : 表示部、 953 : 操作ボタン、 954 : 外部接続ポート、 955 : スピーカ、 956 : マイク、 957 : カメラ、 961 : 筐体、 962 : シャッターボタン、 963 : マイク、 965 : 表示部、 966 : 操作キー、 967 : スピーカ、 968 : ズームレバー、 969 : レンズ、 971 : 筐体、 973 : 表示部、 974 : 操作キー、 975 : スピーカ、 976 : 通信用接続端子、 977 : 光センサ、 4001 : 基板

40

50

、4005：シール材、4006：基板、4010：トランジスタ、4011：トランジ

スタ、4014：配線、4015：電極、4017：電極、4018：FPC、4019

：異方性導電層、4020：キャパシタ、4021：電極、4030：電極層、4031

：電極層、4041：プリント基板、4042：集積回路、4102：絶縁層、4103

：絶縁層、4104：絶縁層、4110：絶縁層、4111：絶縁層、4112：絶縁層

、4200：入力装置、4210：タッチパネル、4227：電極、4228：電極、4

237：配線、4238：配線、4239：配線、4263：基板、4272b：FPC

、4273b：IC、4411：発光層、4412：発光層、4413：発光層、441

5：発光層、4416：発光層、4417：発光層、4420：層、4430：層、45

10：隔壁、4511：EL層、4513：発光デバイス、4514：充填材、4515

：配線、4600：発光ユニット、4600a：発光ユニット、4600b：発光ユニッ

ト、4610：発光ユニット、4620：発光ユニット

10

( 义 面 )

( 义 1 )

1

【図 2 A】

义 2A

20

30

40

50

【図 2 B】

図2B

【図 3】

図3

【図 4 A】

【図 4 B】

図4B

【図 4 C】

【図 5】

10

20

30

40

【図 6 A】

【図 6 B】

50

【図 7 A】

図7A

【図 7 B】

図7B

10

【図 8】

図8

【図 9 A】

図9A

20

30

40

50

【図 9 B】

図9B

【図 9 C】

図9C

10

【図 10 A】

図10A

【図 10 B】

図10B

20

30

40

50

【図 1 1 A】

【図11B】

【図12A】

【図12B】

10

20

30

40

50

【図 13 A】

図13A

【図 13 B】

図13B

10

【図 13 C】

図13C

【図 14 A】

図14A

20

30

40

50

【図14B】

【図14C】

【図15A】

【図15B】

【図 15C】

【図 15D】

10

20

【図 16A1】

【図 16A2】

30

40

50

【図 16 B 1】

【図 16 B 2】

10

【図 16 C 1】

【図 16 C 2】

20

30

40

50

【図 17 A 1】

【図 17 A 2】

【図 17 B 1】

【図 17 B 2】

30

40

50

【図 17C1】

【図 17C2】

【図 18A1】

【図 18A2】

30

40

50

【図 18 B 1】

**図 18B1**

【図 18 B 2】

**図 18B2**

10

【図 18 C 1】

**図 18C1**

【図 18 C 2】

**図 18C2**

20

30

40

50

【図19A1】

**図19A1**

842

【図19A2】

**図19A2**

843

10

【図19B1】

**図19B1**

844

【図19B2】

**図19B2**

845

20

30

40

50

【図 19C1】

**図19C1**846

【図 19C2】

**図19C2**847

10

【図 20A】

**図20A**

【図 20B】

**図20B**

20

30

40

50

【図20C】

図20C

【図20D】

図20D

10

【図20E】

図20E

【図20F】

図20F

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

|                          | F I     |        |         |

|--------------------------|---------|--------|---------|

| H 1 0 K 59/121 (2023.01) | G 0 9 G | 3/20   | 6 8 0 H |

| H 1 0 K 59/35 (2023.01)  | G 0 9 G | 3/20   | 6 8 0 V |

|                          | H 0 5 B | 33/12  | B       |

|                          | H 0 5 B | 33/12  | C       |

|                          | H 0 5 B | 33/14  | A       |

|                          | H 1 0 K | 59/121 |         |

|                          | H 1 0 K | 59/35  |         |

## (56)参考文献

特開2005-266309 (JP, A)

特開2012-185328 (JP, A)

特開2014-120478 (JP, A)

特開2017-027012 (JP, A)

米国特許出願公開第2009/0146929 (US, A1)

米国特許出願公開第2015/0009194 (US, A1)

韓国公開特許第10-2010-0054252 (KR, A)

## (58)調査した分野 (Int.Cl., D B名)

G 0 9 F 9 / 0 0 - 9 / 4 6

G 0 9 G 3 / 0 0 - 3 / 0 8

3 / 1 2 - 3 / 1 6

3 / 1 9 - 3 / 2 6

3 / 3 0 - 3 / 3 4

3 / 3 8

H 0 1 L 3 3 / 0 0

3 3 / 4 8 - 3 3 / 6 4

H 0 5 B 3 3 / 0 0 - 3 3 / 2 8

4 4 / 0 0

4 5 / 6 0

H 1 0 K 5 0 / 0 0 - 9 9 / 0 0