(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6185544号

(P6185544)

(45) 発行日 平成29年8月23日(2017.8.23)

(24) 登録日 平成29年8月4日(2017.8.4)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 29/78 617T

H01L 21/336 (2006.01)

H01L 29/78 618B

H01L 27/146 (2006.01)

H01L 29/78 617N

H01L 29/78 619A

H01L 27/146 A

請求項の数 2 (全 19 頁)

(21) 出願番号

特願2015-234797 (P2015-234797)

(22) 出願日

平成27年12月1日 (2015.12.1)

(62) 分割の表示

特願2013-91232 (P2013-91232)

の分割

原出願日

平成25年4月24日 (2013.4.24)

(65) 公開番号

特開2016-36052 (P2016-36052A)

(43) 公開日

平成28年3月17日 (2016.3.17)

審査請求日

平成28年1月22日 (2016.1.22)

(31) 優先権主張番号

特願2012-100494 (P2012-100494)

(32) 優先日

平成24年4月25日 (2012.4.25)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】 半導体装置

(57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタと、第2のトランジスタと、光電変換素子と、を有し、

前記第1のトランジスタは、単結晶半導体基板にチャネル形成領域を有し、

前記第2のトランジスタは、酸化物半導体層にチャネル形成領域を有する半導体装置であって、

前記単結晶半導体基板の上方に、前記第1のトランジスタのゲート電極を有し、

前記第1のトランジスタのゲート電極の上方に、第1の絶縁層を有し、

前記第1の絶縁層の上方に、前記光電変換素子を有し、

前記光電変換素子の上方に、前記第2のトランジスタのバックゲートとして機能する第1の導電層と、前記第2のトランジスタと前記第1のトランジスタとを電気的に接続する第2の導電層と、酸化アルミニウム層と、前記第1の導電層と前記第2の導電層との間の領域を埋める酸化物絶縁層と、を有し、

10

前記第1の導電層の上方、前記酸化アルミニウム層の上方、及び、前記酸化物絶縁層の上方に、前記酸化物半導体層を有し、

前記酸化物半導体層の上方に、前記第2のトランジスタのゲート電極を有し、

前記第2のトランジスタのゲート電極の上方に、第2の絶縁層を有し、

前記酸化物半導体層の被形成面は、平坦であり、

前記酸化物半導体層は、c軸と前記被形成面とのなす角度が85°以上95°以下である結晶部を有することを特徴とする半導体装置。

10

20

## 【請求項 2】

第1のトランジスタと、第2のトランジスタと、光電変換素子と、を有し、

前記第1のトランジスタは、S O I 基板にチャネル形成領域を有し、

前記第2のトランジスタは、酸化物半導体層にチャネル形成領域を有する半導体装置であつて、

前記S O I 基板の上方に、前記第1のトランジスタのゲート電極を有し、

前記第1のトランジスタのゲート電極の上方に、第1の絶縁層を有し、

前記第1の絶縁層の上方に、前記光電変換素子を有し、

前記光電変換素子の上方に、前記第2のトランジスタのバックゲートとして機能する第1の導電層と、前記第2のトランジスタと前記第1のトランジスタとを電気的に接続する第2の導電層と、酸化アルミニウム層と、前記第1の導電層と前記第2の導電層の間の領域を埋める酸化物絶縁層と、を有し、

前記第1の導電層の上方、前記酸化アルミニウム層の上方、及び、前記酸化物絶縁層の上方に、前記酸化物半導体層を有し、

前記酸化物半導体層の上方に、前記第2のトランジスタのゲート電極を有し、

前記第2のトランジスタのゲート電極の上方に、第2の絶縁層を有し、

前記酸化物半導体層の被形成面は、平坦であり、

前記酸化物半導体層は、c 軸と前記被形成面とのなす角度が 85° 以上 95° 以下である結晶部を有することを特徴とする半導体装置。

## 【発明の詳細な説明】

10

## 【技術分野】

20

## 【0001】

酸化物半導体を用いる半導体装置及びその作製方法に関する。

## 【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

## 【背景技術】

## 【0003】

固体撮像装置は、C C D イメージセンサに代表される電荷転送型固体撮像装置と、C M O S イメージセンサに代表される增幅型固体撮像装置とに大別される。

30

## 【0004】

フォトダイオードなどの光電変換素子と、その光電変換素子で発生した光電荷を出力信号線へ取り出す手段とを含む画素をマトリクス状に配置する二次元固体撮像装置は、様々な用途に用いられている。例えば、カメラ付き携帯電話やP D A などの携帯情報端末に搭載されている。

## 【0005】

また、チャネル形成領域に酸化物半導体層を用いてトランジスタなどを作製する技術が注目されている。例えば、酸化物半導体層として酸化亜鉛 (Z n O) を用いるトランジスタや、I n G a O<sub>3</sub> (Z n O)<sub>m</sub> を用いるトランジスタが挙げられる。

## 【0006】

40

特許文献1には、表示装置の画素に、2つの異なる素子、即ち、酸化物半導体層を用いたトランジスタと、非晶質シリコンを光電変換層に用いたフォトダイオードとを設ける構成が開示されている。

## 【先行技術文献】

## 【特許文献】

## 【0007】

【特許文献1】特開2010-153834号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0008】

50

画素の微細化が進むと、フォトダイオードの占有面積を確保することが困難となっている。画素にはトランジスタも形成するため、トランジスタの占有面積が大きくなると、集積可能な面積全体に対してフォトダイオードの占有面積が小さくなる。

#### 【0009】

画素が微細化しても画素の飽和電荷量を十分確保できる固体撮像装置を有する半導体装置とその製造方法を提供する。

#### 【0010】

また、単結晶シリコンをチャネル形成領域に用いたトランジスタであっても理想的な電気特性を有しているとは言えず、例えばオフ電流（リーク電流などとも呼ぶ）は、実質的にゼロと言えるほど小さいものではない。従って、固体撮像素子など電荷保持型の半導体装置を構成する場合には、十分な電位保持期間の確保が可能であり、よりオフ電流が低減されたデバイスの開発が望まれている。10

#### 【0011】

そこで、開示する本発明の一態様は、安定した電気特性（例えば、オフ電流が極めて低減されている）を有するトランジスタを含む固体撮像素子を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0012】

增幅回路などの駆動回路が設けられた半導体基板上に2つの異なる素子層（酸化物半導体層を含む素子層と、フォトダイオードを含む素子層と）を積層することによって、フォトダイオードの占有面積を確保する。また、フォトダイオードと電気的に接続するトランジスタに酸化物半導体層をチャネル形成領域とするトランジスタを用いることで、半導体装置の消費電力の低減を図る。20

#### 【0013】

本明細書で開示する発明の構成の一形態は、半導体基板に第1のトランジスタを含む駆動回路と、半導体基板上に酸化物半導体層をチャネル形成領域とする第2のトランジスタと、半導体基板上に第2のトランジスタと電気的に接続するフォトダイオードとを有し、第2のトランジスタ上にフォトダイオードが一部重なることを特徴とする半導体装置である。

#### 【0014】

上記構成の作製方法の一例は、半導体基板に増幅回路などを形成した後、酸化物半導体層をチャネル形成領域とするトランジスタを形成し、その上に他の半導体基板から分離した結晶性シリコン層を貼りつけ、その結晶性シリコン層を光電変換層とするフォトダイオードを作製して、酸化物半導体層を含む素子層上にフォトダイオードを含む素子層を積層した半導体装置を作製する。30

#### 【0015】

また、酸化物半導体層を含む素子層は透光性を有するため、2つの異なる素子層の積層順序を反対にする構成とすることもでき、その一形態は、半導体基板に第1のトランジスタを含む駆動回路と、半導体基板上に酸化物半導体層をチャネル形成領域とする第2のトランジスタと、半導体基板上に第2のトランジスタと電気的に接続するフォトダイオードとを有し、フォトダイオード上に第2のトランジスタが一部重なることを特徴とする半導体装置である。40

#### 【0016】

上記構成の作製方法の一例は、半導体基板に増幅回路などを形成した後、他の半導体基板から分離した結晶性シリコン層を貼りつけ、その結晶性シリコン層を光電変換層とするフォトダイオードを作製し、その上に酸化物半導体層をチャネル形成領域とするトランジスタを形成し、フォトダイオードを含む素子層上に酸化物半導体層を含む素子層を積層した半導体装置を作製する。

#### 【0017】

また、3つの異なる素子が重なる構成とすることもでき、その一形態は、半導体基板に第1のトランジスタを含む駆動回路と、半導体基板上に酸化物半導体層をチャネル形成領域

10

20

30

40

50

とする第2のトランジスタと、半導体基板上に第2のトランジスタと電気的に接続するフォトダイオードとを有し、第1のトランジスタと第2のトランジスタとフォトダイオードは、一部重なることを特徴とする半導体装置である。このように3つの異なる素子を重ねて配置することで高集積化を図ることができる。

**【0018】**

また、フォトダイオードと電気的に接続するトランジスタに電気的に接続するリセット用のトランジスタを設ける構成としてもよく、その一形態は、半導体基板に第1のトランジスタを含む駆動回路と、半導体基板上に酸化物半導体層をチャネル形成領域とする第2のトランジスタ及び第3のトランジスタと、半導体基板上に前記第2のトランジスタの一方の端子と電気的に接続するフォトダイオードとを有し、第2のトランジスタのもう一方の端子は、第3のトランジスタと電気的に接続され、且つ、第1のトランジスタのゲート電極層と電気的に接続され、第2のトランジスタまたは第3のトランジスタ上にフォトダイオードが一部重なることを特徴とする半導体装置である。10

**【0019】**

上記各構成において、第1のトランジスタのチャネル形成領域は、結晶性シリコンで構成される。

**【0020】**

また、上記各構成において、フォトダイオードの半導体層は、結晶性シリコンで構成される。

**【0021】**

また、上記各構成において、前記フォトダイオードは、p型半導体領域、i型半導体領域及びn型半導体領域を有する。フォトダイオードの代表的なものは、p i n型フォトダイオードであるが、p n型フォトダイオードや、ショットキー型フォトダイオードがあり、いずれか一を適宜用いればよい。20

**【発明の効果】**

**【0022】**

增幅回路などの駆動回路が設けられた半導体基板上に2つの異なる素子層（酸化物半導体層を含む素子層と、フォトダイオードを含む素子層と）を積層することによって、高集積化を図ることができる。また、表面入射型であり、表面にはダイオードのみを配置するため、フォトダイオードの占有面積を十分確保でき、受光面積を大きくすることができます。従って、画素の信号電荷量の飽和量を増加させることができ、ダイナミックレンジの拡大を図ることができる。また、酸化物半導体層を含む素子層は透光性を有するため、2つの異なる素子層の積層順序を反対にする構成とすることもできる。30

**【0023】**

また、フォトダイオードと電気的に接続するトランジスタに酸化物半導体層をチャネル形成領域とするトランジスタを用いることで、低消費電力の半導体装置を作製することができる。

**【図面の簡単な説明】**

**【0024】**

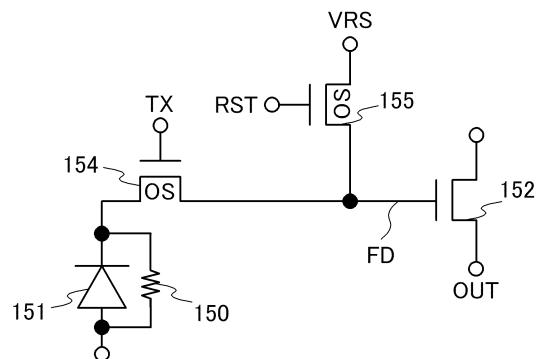

**【図1】**本発明の一態様を示す構成の概念図である。

**【図2】**(A)は、本発明の一態様を示す等価回路の一例であり、(B)はタイミングチャートを示す図である。

**【図3】**本発明の一態様を示す等価回路の一例を示す図である。

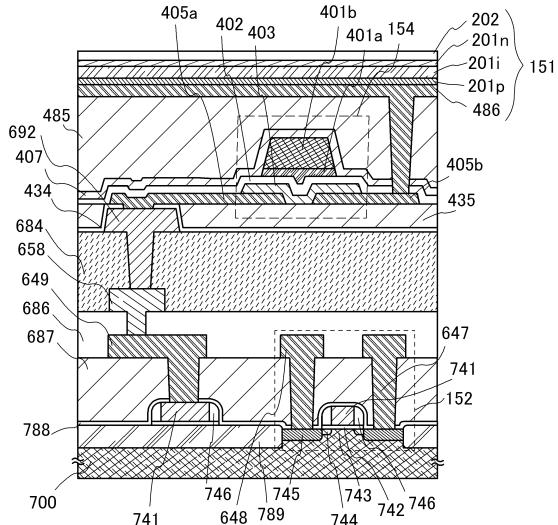

**【図4】**本発明の一態様を示す断面構造を示す図である。

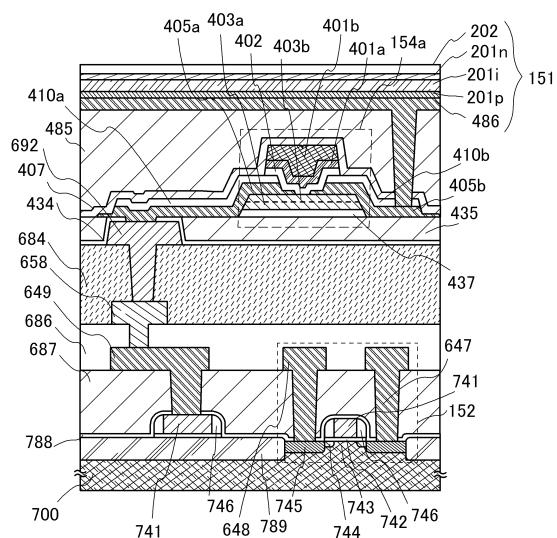

**【図5】**本発明の一態様を示す断面構造を示す図である。

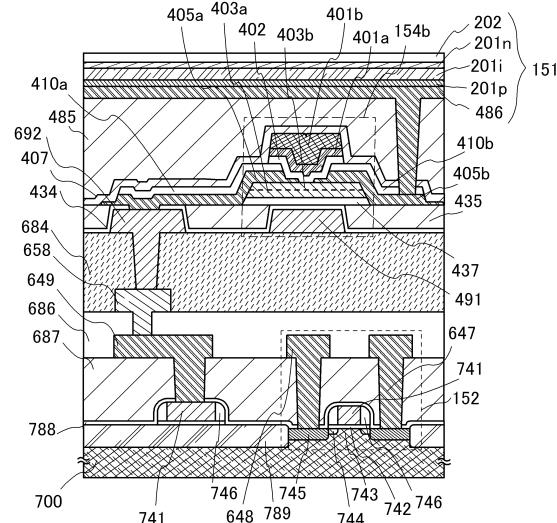

**【図6】**本発明の一態様を示す断面構造を示す図である。

**【図7】**電子機器を説明する図。

**【図8】**電子機器を説明する図。

**【発明を実施するための形態】**

**【0025】**

10

20

30

40

50

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

**【0026】**

(実施の形態1)

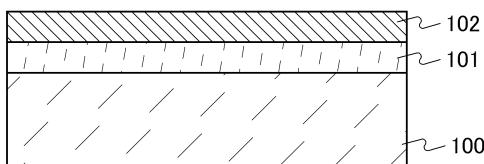

固体撮像装置の構成の一例を図1(A)及び図1(B)を用いて以下に示す。

**【0027】**

図1(A)には、増幅回路などの駆動回路が設けられた半導体基板100上に酸化物半導体層を含む素子層101を設け、酸化物半導体層を含む素子層101上にフォトダイオードを含む素子層102を設けた積層体の断面模式図を示している。

10

**【0028】**

半導体基板100は、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを用いることができ、トランジスタのチャネル形成領域は、半導体基板中、又は半導体基板上に形成することができる。シリコンなどの材料を用いたトランジスタは、高速動作が容易であり、nチャネル型トランジスタやpチャネル型トランジスタなどを用い、増幅回路などの駆動回路を設けた半導体基板100を作製すればよい。

**【0029】**

酸化物半導体層を含む素子層101は、酸化物半導体層をチャネル形成領域とするトランジスタを少なくとも一つ以上有する層である。酸化物半導体層は、二元系金属の酸化物であるIn-Zn系酸化物、In-Mg系酸化物、In-Ga系酸化物、三元系金属の酸化物であるIn-Ga-Zn系酸化物(IGZOとも表記する。)、In-Sn-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Sn-Hf-Zn系酸化物などを用いることができる。

20

30

**【0030】**

なお、ここで、例えば、In-Ga-Zn系酸化物とは、In、Ga及びZnを有する酸化物という意味であり、InとGaとZnの比率は問わない。また、In、Ga及びZn以外の金属元素が含まれていてもよい。

**【0031】**

また、金属酸化物ターゲットの相対密度(充填率)は90%以上100%以下、好ましくは95%以上99.9%以下である。相対密度の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体層は緻密な膜とすることができます。

**【0032】**

酸化物半導体層を形成する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

40

**【0033】**

また、酸化物半導体層は、結晶構造を有することが好ましい。結晶構造を有する酸化物半導体層は、単結晶膜、多結晶膜(ポリクリスタルともいう。)、微結晶膜、またはC A A C - O S (C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

**【0034】**

C A A C - O S 膜は、完全な単結晶ではなく、完全な非晶質でもない。C A A C - O S 膜は、結晶部を有する酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM: Tra

50

nsmission Electron Microscope)による観察像では、C AAC - OS 膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、AAC - OS 膜は、粒界に起因する電子移動度の低下が抑制される。

#### 【0035】

C AAC - OS 膜に含まれる結晶部は、c 軸が C AAC - OS 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつ a b 面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸および b 軸の向きが異なっている。即ち、C AAC - OS 膜は、異なる結晶成分間で c 軸は揃っているが、a 軸及び b 軸が揃っていないことからエピタキシャル成長でない膜である。本明細書において、単に垂直と記載する場合、85°以上 95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上 5°以下の範囲も含まれることとする。

10

#### 【0036】

なお、C AAC - OS 膜において、結晶部の分布が一様でなくてもよい。例えば、C AAC - OS 膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、C AAC - OS 膜へ不純物を添加することにより、当該不純物添加領域において結晶部の結晶性が低下し、不純物の添加条件によっては微結晶領域または非晶質領域になることもある。

20

#### 【0037】

C AAC - OS 膜に含まれる結晶部の c 軸は、C AAC - OS 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、C AAC - OS 膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部の c 軸の方向は、C AAC - OS 膜が形成されたときの被形成面の法線ベクトルまたは表面の法線方向に平行なベクトルとなる。結晶部は、成膜することにより、または成膜後に熱処理などの結晶化処理を行うことにより形成される。

#### 【0038】

また、C AAC - OS のように結晶部を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ( Ra )が 1 nm 以下、好ましくは 0.3 nm 以下、より好ましくは 0.1 nm 以下の表面上に形成するとよい。

30

#### 【0039】

C AAC - OS 膜を用いたトランジスタは、可視光や紫外光の照射による電気的特性の変動を低減することができる。従って、酸化物半導体膜を C AAC - OS 膜として、可視光や紫外光の照射によるトランジスタの電気的特性変化を抑制し、信頼性の高い半導体装置とすることができます。

#### 【0040】

また、トランジスタの構造は、トップゲート型のトランジスタやボトムゲート型のトランジスタや、上下にゲート電極層を有するデュアルゲート型トランジスタを用いることができる。酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

40

#### 【0041】

また、フォトダイオードを含む素子層 102 は、他の半導体基板を用い、水素イオン注入剥離法などを用いて半導体基板の一部を剥離して酸化物半導体層を含む素子層 101 上に単結晶半導体層を形成する。水素イオン注入剥離法は、シリコンウェハーに水素イオンを注入することによって表面から所定の深さに微小気泡層を形成し、該微小気泡層を劈開面とすることで、別のシリコンウェハーに薄いシリコン層を接合する方法である。

#### 【0042】

50

水素イオン注入剥離法によって剥離する前、或いは後に p 型の導電型を付与する不純物元素を含有する p 型不純物層、又は n 型の導電型を付与する不純物元素を含有する n 型不純物層を形成し、フォトダイオードを含む素子層 102 とする。本実施の形態では、p 型の導電型を付与する不純物元素を含有する p 型不純物層上に i 型層と、n 型不純物層とを積層させ、それらを一対の電極で挟んだ p-i-n 型フォトダイオードを形成する。

#### 【0043】

半導体基板 100、素子層 101、及び素子層 102 に含まれる素子を適宜、組み合わせることによって、光検出回路を構成し、固体撮像装置を作製する。

#### 【0044】

フォトダイオードは複数形成し、それらをマトリクス状に配置し、それぞれに重なるように赤色フィルタ、緑色フィルタ、青色フィルタなどのカラーフィルタを固体撮像装置に設けてもよい。赤色フィルタと重なるフォトダイオードは赤色信号に対応する電荷を生成し、緑色フィルタと重なるフォトダイオードは緑色信号に対応する電荷を生成し、青色フィルタと重なるフォトダイオードは青色信号に対応する電荷を生成する。

10

#### 【0045】

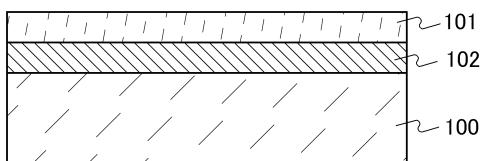

また、酸化物半導体層を含む素子層は透光性を有するため、2つの異なる素子層の積層順序を反対にする構成とすることもでき、その例を図 1 (B) に示す。図 1 (B) では、半導体基板 100 に第 1 のトランジスタを含む駆動回路と、半導体基板 100 上に酸化物半導体層をチャネル形成領域とする第 2 のトランジスタを含む素子層 101 と、半導体基板 100 上にフォトダイオードを含む素子層 102 とを有し、素子層 102 上に素子層 101 を積層する例である。

20

#### 【0046】

図 1 (B) の場合、增幅回路などの駆動回路が設けられた半導体基板 100 上に水素イオン注入剥離法などを用いて半導体基板の一部を剥離して半導体基板 100 上に単結晶半導体層を形成する。水素イオン注入剥離法によって剥離する前、或いは後に p 型の導電型を付与する不純物元素を含有する p 型不純物層、又は n 型の導電型を付与する不純物元素を含有する n 型不純物層を形成し、フォトダイオードを含む素子層 102 とする。そして、フォトダイオードを含む素子層 102 上に酸化物半導体層を形成して酸化物半導体層をチャネル形成領域とするトランジスタを作製することによって、図 1 (B) の構成を得ることができる。

30

#### 【0047】

(実施の形態 2)

本実施の形態では、実施の形態 1 に示した半導体基板 100、素子層 101、及び素子層 102 に含まれる素子を適宜、組み合わせることによって構成される光検出回路の例について説明する。

#### 【0048】

本実施の形態に係る光検出回路の例について、図 2 を参照して説明する。図 2 は、本実施の形態に係る光検出回路の例を説明するための図である。光検出回路の構成は、実施の形態 1 に説明した増幅回路などの駆動回路が設けられた半導体基板上に 2 つの異なる素子層(酸化物半導体層を含む素子層と、フォトダイオードを含む素子層と)を積層したものを使う。

40

#### 【0049】

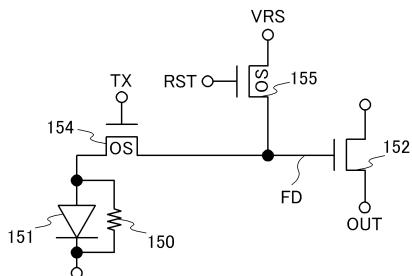

まず、本実施の形態に係る光検出回路の構成例について、図 2 (A) を参照して説明する。

#### 【0050】

図 2 (A) に示す光検出回路は、フォトダイオード 151 と、トランジスタ 152 と、トランジスタ 154 と、トランジスタ 155 と、を備える。

#### 【0051】

フォトダイオード 151 のカソードには、高電源電位 VDD が与えられる。なお、フォトダイオード 151 のアノードとカソードの間には負荷抵抗 150 が存在する。

50

**【0052】**

トランジスタ154のソース及びドレインの一方は、フォトダイオード151のアノードに電気的に接続され、トランジスタ154のゲートには、電荷蓄積制御信号TXが入力される。トランジスタ154は、電荷蓄積制御トランジスタとしての機能を有する。電荷蓄積制御トランジスタは、増幅トランジスタのゲートの電位を、フォトダイオード151により生成される光電流に応じた値に設定するか否かを制御する機能を有する。

**【0053】**

トランジスタ152のソース及びドレインの一方には、低電源電位VSSが与えられ、他方の電位が出力信号OUTの電位となり、光検出回路により出力する光データとなる。さらに、トランジスタ152のゲートは、トランジスタ154のソース及びドレインの他方に電気的に接続される。トランジスタ152のゲートとトランジスタ154のソース及びドレインの他方との接続箇所がノードFDとなる。トランジスタ152は、フォトダイオード151により生成される光電流を増幅する増幅トランジスタとしての機能を有する。なお、トランジスタ152のソース及びドレインの他方を、スイッチトランジスタのソース又はドレインに接続してもよい。

10

**【0054】**

トランジスタ155のソース及びドレインの一方には、リセット電位VRSが与えられ、トランジスタ155のソース及びドレインの他方は、トランジスタ154のソース及びドレインの他方に電気的に接続され、トランジスタ155のゲートには、リセット信号RSTが入力される。トランジスタ155は、光検出リセットトランジスタとしての機能を有する。光検出リセットトランジスタは、増幅トランジスタのゲートの電位（ノードFDの電位）を、リセット電位VRSに設定するか否かを選択する機能を有する。

20

**【0055】**

なお、図2(A)に示す光検出回路を複数具備する場合、全ての光検出回路に同じ電荷蓄積制御信号を入力することもできる。全ての光検出回路に同じ電荷蓄積制御信号を入力して光データを生成する駆動方式をグローバルシャッター方式ともいう。

**【0056】**

なお、トランジスタ152としては、チャネル形成領域にシリコンを含むトランジスタを用いることができる。また、トランジスタ154、155としては、チャネル形成領域に酸化物半導体を含むトランジスタを用いることができる。上記酸化物半導体を含むトランジスタは、オフ電流が低いため、トランジスタ152のゲートの電位の変動を抑制できる。

30

**【0057】**

次に、図2(A)に示す光検出回路の駆動方法例について、図2(B)のタイミングチャートを参照して説明する。なお、ここでは、一例としてリセット電位VRSを低電源電位VSSと同等の値であるとする。

**【0058】**

図2(B)に示すように、図2(A)に示す光検出回路の駆動方法例では、まず期間T1において、リセット信号RSTのパルスが入力され、また、期間T1から期間T2にかけて電荷蓄積制御信号TXのパルスが入力される。なお、期間T1において、リセット信号RSTのパルスの入力開始のタイミングは、電荷蓄積制御信号TXのパルスの入力開始のタイミングより早くてもよい。

40

**【0059】**

このとき、トランジスタ154、155がオン状態になることにより、トランジスタ152のゲートの電位（ノードFDの電位）がリセット電位VRSと同等の値になる。

**【0060】**

さらに、期間T2において、トランジスタ155がオフ状態になり、トランジスタ154がオン状態のままになる。

**【0061】**

このとき、フォトダイオード151に入射した光の照度に応じて、フォトダイオード15

50

1 のアノードとカソードの間に光電流が流れる。さらに、光電流に応じてトランジスタ 152 のゲートの電位（ノード F D の電位）の値が変化する。このとき、トランジスタ 152 のソース及びドレインの間のチャネル抵抗の値が変化する。

#### 【 0 0 6 2 】

さらに、期間 T 3 において、トランジスタ 154 がオフ状態になる。

#### 【 0 0 6 3 】

このとき、トランジスタ 152 のゲートの電位（ノード F D の電位）は、期間 T 2 におけるフォトダイオード 151 の光電流に応じた値に保持される。

#### 【 0 0 6 4 】

さらに、トランジスタ 152 のソース及びドレインの他方の電位が出力信号 O U T として出力されることにより、光検出回路から光データが出力される。以上が図 2 ( A ) に示す光検出回路の駆動方法例である。10

#### 【 0 0 6 5 】

なお、図 3 に示すように、フォトダイオード 151 のアノードとカソードの接続関係を逆にしてもよい。このとき、フォトダイオード 151 のアノードには、低電源電位 V S S が与えられ、カソードはトランジスタ 154 のソース及びドレインの一方電気的に接続され、トランジスタ 152 のソース及びドレインの一方には、高電源電位 V D D が与えられる。

#### 【 0 0 6 6 】

図 2 及び図 3 を参照して説明したように、本実施の形態の光検出回路の一例では、電荷蓄積制御トランジスタ及びリセットトランジスタにオフ電流の低いトランジスタを用いることにより、増幅トランジスタのゲートの電位の変動を抑制できる。よって、生成されるデータの精度を高めることができる。20

#### 【 0 0 6 7 】

また、本実施の形態は実施の形態 1 と自由に組み合わせることができる。

#### 【 0 0 6 8 】

##### ( 実施の形態 3 )

本実施の形態では、実施の形態 2 に示した光検出回路を有する固体撮像装置の断面構造の一例を図 4 に示す。なお、図 2 または図 3 と共通の部分には同じ符号を用いて説明する。

#### 【 0 0 6 9 】

図 4 は、トランジスタ 152 上にトランジスタ 154 が重なり、トランジスタ 154 上にフォトダイオード 151 を重ねた例である。このように積層させることで高集積化させていている。30

#### 【 0 0 7 0 】

図 4 に示す固体撮像装置は、下部に第 1 の半導体材料を用いたトランジスタ 152 を有し、上部に第 2 の半導体材料を用いたトランジスタ 154 を有するものである。

#### 【 0 0 7 1 】

ここで、第 1 の半導体材料と第 2 の半導体材料は異なるバンドギャップを持つ材料とすることが望ましい。例えば、第 1 の半導体材料を酸化物半導体以外の半導体材料（シリコンなど）とし、第 2 の半導体材料を酸化物半導体とすることができる。シリコンなどの材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。40

#### 【 0 0 7 2 】

なお、本実施の形態では、基板 700 として p 型の導電型を有する単結晶シリコン基板を用い、n 型を付与する不純物元素を添加し、L D D ( L i g h t l y D o p e d D r a i n ) 領域やエクステンション領域として機能する n 型不純物領域 744 、ソース領域又はドレイン領域として機能する n 型不純物領域 745 を形成している。トランジスタ 152 は、n チャネル型トランジスタであり、チャネル形成領域 743 、n 型不純物領域 744 、ソース領域又はドレイン領域として機能する n 型不純物領域 745 、ゲート絶縁膜 742 、ゲート電極層 741 を有している。なお、n 型不純物領域 745 の不純物濃度は、50

n型不純物領域744よりも高い。ゲート電極層741の側面には側壁絶縁層746が設けられており、ゲート電極層741及び側壁絶縁層746をマスクとして用いて、不純物濃度が異なるn型不純物領域744、n型不純物領域745を自己整合的に形成することができる。

#### 【0073】

基板700において、トランジスタ152は隣り合うトランジスタと素子分離領域789により分離されており、トランジスタ152上に絶縁膜788、及び絶縁膜687が積層されている。絶縁膜687上には、絶縁膜788及び絶縁膜687に形成された開口を介してn型不純物領域745に接する配線層647、648とを有する。また、絶縁膜687上には、トランジスタ152のゲート電極層741と電気的に接続する配線層649が形成されている。なお、図4に示すように、素子分離領域789上に重なる位置にゲート電極層741が引き回され、素子分離領域789上にコンタクトホールを形成して配線層649と電気的に接続させている。

#### 【0074】

また、本実施の形態の半導体装置は図4に示す構成に限定されず、トランジスタ152としてシリサイド(サリサイド)を有するトランジスタや、側壁絶縁層を有さないトランジスタを用いてもよい。シリサイド(サリサイド)を有する構造であると、ソース領域及びドレイン領域がより低抵抗化でき、半導体装置の高速化が可能である。また、低電圧で動作できるため、半導体装置の消費電力を低減することが可能である。

#### 【0075】

次に、図4の半導体装置における下部のトランジスタ152上に設けられる上部の素子構成を説明する。

#### 【0076】

絶縁膜686及び配線層658上に絶縁膜684が積層され、絶縁膜684上に、配線層692が形成されている。配線層692を覆う絶縁膜434が設けられ、その上に酸化物半導体層403と、ゲート絶縁膜402と、その上にゲート電極層401a、401bが設けられている。

#### 【0077】

配線層692は、絶縁膜684に形成された開口を介して配線層658と電気的に接続する。本実施の形態において、絶縁膜684はCMP法による平坦化処理を行っている例である。

#### 【0078】

絶縁膜434は半導体装置において下部と上部の間に設けられており、上部のトランジスタ154の電気的特性の劣化や変動を招く水素等の不純物が、下部から上部へ侵入しないように、バリア膜として機能する。よって、不純物等の遮断機能の高い、緻密な無機絶縁膜(例えば、酸化アルミニウム膜、窒化シリコン膜など)を用いることが好ましい。

#### 【0079】

以下に、トランジスタ154の作製方法を簡略に説明する。

#### 【0080】

トランジスタ152上に設けた絶縁膜684上に、配線層692を形成する。

#### 【0081】

次いで、配線層692を覆う絶縁膜434を形成する。

#### 【0082】

次いで、絶縁膜434上に表面に配線層692の形状を反映した凸部を有する酸化物絶縁膜を形成する。そして、酸化物絶縁膜にCMP処理を施して、配線層692上の酸化物絶縁膜を選択的に除去することで表面を平坦化し、平坦化した酸化物絶縁膜435を形成する。

#### 【0083】

次いで、配線層692の上面に形成された絶縁膜434を一部選択的に除去して配線層692の上面を露出させる開口を形成する。

10

20

30

40

50

## 【0084】

次いで、スパッタリング法などを用いて導電膜を成膜し、選択的にエッチングしてソース電極またはドレイン電極として機能する電極層405a及び電極層405bを形成する。

## 【0085】

次いで、電極層405a及び電極層405b上に酸化物半導体層403を、スパッタ法により成膜し、1枚のフォトマスクを用いて選択的にエッチングする。

## 【0086】

酸化物半導体層403は、酸素雰囲気（酸素100%雰囲気）下で、組成として、In : Ga : Zn = 1 : 1 : 1 [原子数比] の酸化物ターゲットを用いて成膜し、膜中に、c軸が膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつa b面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している結晶部を含ませ、所謂CAC-O<sub>5</sub>膜とする。なお、本実施の形態では成膜直後に結晶部を有する酸化物半導体膜を形成する例を示したが、成膜後に加熱処理を行うことで結晶部を形成してもよい。

10

## 【0087】

次いで、酸化物半導体層403上にゲート絶縁膜402を形成する。本実施の形態ではゲート絶縁膜402の材料として、酸化ガリウム膜を用いる。

## 【0088】

次いで、ゲート絶縁膜402上に、スパッタリング法、蒸着法などを用いて導電膜を形成し、該導電膜をエッチングして、ゲート電極層401a、401bを形成する。以上の工程でトランジスタ154を形成する。

20

## 【0089】

次いで、トランジスタ154上に絶縁膜407及び層間絶縁膜485を形成する。こうしてトランジスタ154を含む素子層が形成される。そして、層間絶縁膜485に電極層405bに達する開口を形成し、第1の電極層486を形成する。この第1の電極層はマトリクス状に配置される。そして、第1の電極層を覆って絶縁膜を形成した後、CMPなどの平坦化処理を行い、第1の電極層の上面を露出させる。また、層間絶縁膜485に埋め込み配線を形成し、埋め込み配線上方に他の半導体素子や配線などを形成して多層構造を有する半導体装置を作製してもよい。

30

## 【0090】

次いで、トランジスタ154上にフォトダイオード151を作製する一例を示す。

## 【0091】

図示しない他の半導体基板を用意し、水素イオン注入剥離法などを用いて半導体基板の一部を剥離して酸化物半導体層を含む素子層上に単結晶半導体層を形成する。

## 【0092】

次いで、p型不純物元素を単結晶半導体層に添加してp型不純物層201pを形成し、n型不純物元素を単結晶半導体層に添加してn型不純物層201nを形成する。なお、p型不純物層201pとn型不純物層201nの間にはi型層201iが形成される。そして、n型不純物層201n上に透光性を有する導電膜202を形成し、上方入射のフォトダイオード151が作製される。なお、フォトダイオード151の作製方法は上記作製方法に限定されることは言うまでもなく、例えば、p型不純物層201pをプラズマCVD法による成膜によって形成してもよい。

40

## 【0093】

こうして作製される固体撮像装置は、フォトダイオードに多少リークがあってもトランジスタ154をオフ状態とすることで、トランジスタ154とトランジスタ152の間の電荷が保持される。従ってマージン向上及び歩留まり向上を図ることができる。

## 【0094】

また、実施の形態2に示した光検出回路を実現できるのであれば、図4の構成に限定されず、実施の形態1に示した半導体基板100、素子層101、及び素子層102に含まれ

50

る素子を配線によって電極層と適宜接続し、取り出し端子などを作製すればよい。

【0095】

また、図5に図4の構成と異なる他の例を示す。図5は、図4とトランジスタの構造が異なるだけで他の構成は同一であるため、ここでは異なる点のみを説明する。

【0096】

図5に示すトランジスタ154aは、酸化物絶縁膜435と酸化物半導体層の積層の間に酸化ガリウムを含む絶縁膜437を設け、酸化物半導体層の積層上に電極層405a、405bを形成し、電極層405a上に第1の保護層410aと、電極層405b上に第2の保護層410bとを有する例である。

【0097】

また、図5に示すトランジスタ154aは、第1の酸化物半導体層403a上に、第1の酸化物半導体層403aと組成の異なる第2の酸化物半導体層403bを形成して積層構造とする。

【0098】

第1の酸化物半導体層403aとしては、 $In : Ga : Zn = 3 : 1 : 2$ の原子数比のターゲットを用いて成膜されるIn-Ga-Zn系酸化物膜を用いる。なお、第1の酸化物半導体層403aは、原子数比でInをGa及びZnよりも多い半導体膜であればよい。また、第2の酸化物半導体層403bとしては、 $In : Ga : Zn = 1 : 1 : 1$ の原子数比のターゲットを用いて成膜されるIn-Ga-Zn系酸化物膜を用いる。

【0099】

組成の異なる酸化物半導体層の積層を用いる場合、積層の下層、本実施の形態では、第1の酸化物半導体層403aが露出しないように積層の上層を残すように形成する。

【0100】

図5に示すトランジスタ154aは、チャネル形成領域に $In : Ga : Zn = 3 : 1 : 2$ の原子数比のターゲットを用いて成膜されるIn-Ga-Zn系酸化物膜を用いるため、電界効果移動度の向上を図ることができる。

【0101】

また、電極層405a上に第1の保護層410aと、電極層405b上に第2の保護層410bとを形成する方法は、第2の酸化物半導体層403b上に、スパッタリング法などを用いて導電膜を成膜し、その上に酸化シリコン膜を成膜する。次いで、酸化シリコン膜上にレジストマスクを形成し、導電膜の膜厚の半分程度を除去して部分的に薄膜にする第1のエッチングを行う。レジストマスクにアッティングを行ってレジストマスクの面積を小さくする処理を行った後、小さくしたレジストマスクを用いて第2のエッチングを行い、側面から突出した領域を下端部に有する電極層405a、405bをそれぞれ形成する。また、電極層405aの膜厚の厚い領域上には第1の保護層410aが残存し、電極層405bの膜厚の厚い領域上には第2の保護層410bが残存する。第1の保護層410a及び第2の保護層410bは、トランジスタ154aのゲート電極層とソース電極層との間に形成される寄生容量及びゲート電極層とドレイン電極層との間に形成される寄生容量を低減する。

【0102】

また、図6に図5と一部異なる他の例を示す。図6は、図5とトランジスタの構造が異なるだけで他の構成は同一であるため、ここでは異なる点のみを説明する。

【0103】

図6は、酸化物絶縁膜435中に導電層491を設けた例であり、導電層491は、トランジスタ154bのゲート電極層401a、401bとチャネル形成領域を介して重なり、トランジスタ154bの電気的特性を制御する。

【0104】

導電層491はトランジスタ154bの電気的特性を制御する第2のゲート電極層（いわゆるバッゲートともいう）として機能することができる。例えば導電層491の電位をGND（または固定電位）とすることでトランジスタ154bのしきい値電圧をよりラ

10

20

30

40

50

スとし、さらにノーマリーオフのトランジスタとすることができます。

**【0105】**

なお、導電層 491 は配線層 692 と同じ工程で作製することができる。

**【0106】**

また、本実施の形態は、実施の形態 1 または実施の形態 2 と自由に組み合わせができる。

**【0107】**

(実施の形態 4)

本明細書に開示する半導体装置は、さまざまな電子機器（遊技機も含む）に適用することができる。電子機器としては、テレビ、モニタ等の表示装置、照明装置、デスクトップ型

10

或いはノート型のパーソナルコンピュータ、ワードプロセッサ、DVD (Digital Versatile Disc)などの記録媒体に記憶された静止画又は動画を再生する画像再生装置、ポータブルCDプレーヤ、ラジオ、テープレコーダ、ヘッドホンステレオ、ステレオ、コードレス電話子機、トランシーバ、携帯無線機、携帯電話、自動車電話、携帯型ゲーム機、電卓、携帯情報端末、電子手帳、電子書籍、電子翻訳機、音声入力機器、ビデオカメラ、デジタルスチルカメラ、電気シェーバ、電子レンジ等の高周波加熱装置、電気炊飯器、電気洗濯機、電気掃除機、エアコンディショナーなどの空調設備、食器洗い器、食器乾燥器、衣類乾燥器、布団乾燥器、電気冷蔵庫、電気冷凍庫、電気冷凍冷蔵庫、DNA保存用冷凍庫、煙感知器、放射線測定器、透析装置等の医療機器、などが挙げられる。さらに、誘導灯、信号機、ベルトコンベア、エレベータ、エスカレータ、産業用

20

ロボット、電力貯蔵システム等の産業機器も挙げられる。また、石油を用いたエンジンや、非水系二次電池からの電力を用いて電動機により推進する移動体なども、電気機器の範疇に含まれるものとする。上記移動体として、例えば、電気自動車 (EV)、内燃機関と電動機を併せ持ったハイブリッド車 (HEV)、プラグインハイブリッド車 (PHEV)、これらのタイヤ車輪を無限軌道に変えた装軌車両、電動アシスト自転車を含む原動機付自転車、自動二輪車、電動車椅子、ゴルフ用カート、小型又は大型船舶、潜水艦、ヘリコプター、航空機、ロケット、人工衛星、宇宙探査機や惑星探査機、宇宙船が挙げられる。これらの電子機器の具体例を図 7 及び図 8 に示す。

**【0108】**

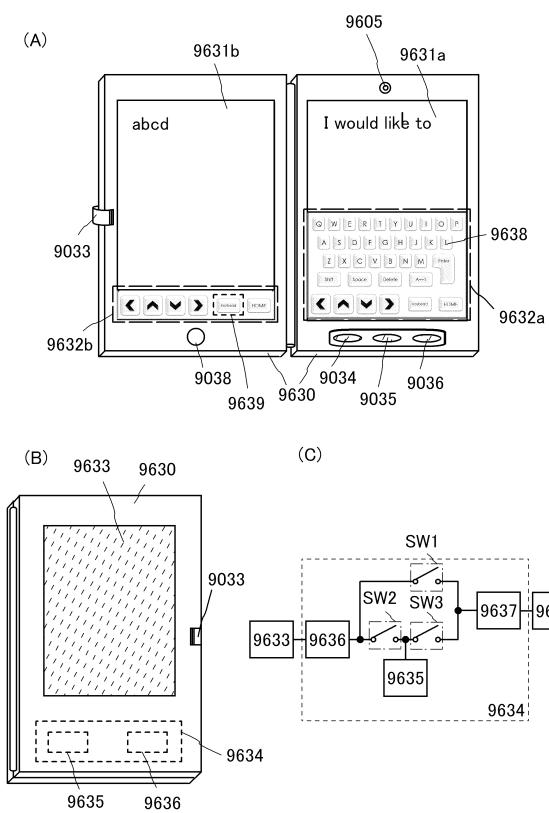

図 7 (A) 及び図 7 (B) は 2 つ折り可能なタブレット型端末である。図 7 (A) は、開いた状態であり、タブレット型端末は、筐体 9630、表示部 9631a、表示部 9631b、表示モード切り替えスイッチ 9034、電源スイッチ 9035、省電力モード切り替えスイッチ 9036、留め具 9033、操作スイッチ 9038、固体撮像装置 9605 を有する。本明細書では、固体撮像装置 9605 はレンズなどの光学系を含んで呼んでもよいこととする。

30

**【0109】**

図 7 (A) 及び図 7 (B) に示すような携帯機器においては、画像データの一時記憶などにメモリとして SRAM または DRAM が使用されている。例えば、実施の形態 1 に説明した半導体装置を固体撮像装置 9605 として使用することができる。実施の形態 1 で説明した固体撮像装置 9605 を採用することによって、撮像の検出感度がよく、且つ消費電力が十分に低減することができる。

40

**【0110】**

また、表示部 9631a は、一部をタッチパネルの領域 9632a とすることができます、表示された操作キー 9638 にふれることでデータ入力をすることができる。なお、表示部 9631a においては、一例として半分の領域が表示のみの機能を有する構成、もう半分の領域がタッチパネルの機能を有する構成を示しているが該構成に限定されない。表示部 9631a の全ての領域がタッチパネルの機能を有する構成としても良い。例えば、表示部 9631a の全面をキーボードボタン表示させてタッチパネルとし、表示部 9631b を表示画面として用いることができる。

**【0111】**

50

また、表示部 9631b においても表示部 9631a と同様に、表示部 9631b の一部をタッチパネルの領域 9632b とすることができる。また、タッチパネルのキーボード表示切り替えボタン 9639 が表示されている位置に指やスタイルスなどでふれることで表示部 9631b にキーボードボタン表示することができる。

#### 【0112】

また、タッチパネルの領域 9632a とタッチパネルの領域 9632b に対して同時にタッチ入力することもできる。

#### 【0113】

また、表示モード切り替えスイッチ 9034 は、縦表示又は横表示などの表示の向きを切り替え、白黒表示やカラー表示の切り替えなどを選択できる。省電力モード切り替えスイッチ 9036 は、タブレット型端末に内蔵している固体撮像装置で検出される使用時の外光の光量に応じて表示の輝度を最適なものとすることができる。タブレット型端末は固体撮像装置だけでなく、ジャイロ、加速度センサ等の傾きを検出するセンサなどの他の検出装置を内蔵させててもよい。10

#### 【0114】

また、図 7 (A) では表示部 9631b と表示部 9631a の表示面積が同じ例を示しているが特に限定されず、一方のサイズともう一方のサイズが異なっていてもよく、表示の品質も異なっていてもよい。例えば一方が他方よりも高精細な表示を行える表示パネルとしてもよい。

#### 【0115】

図 7 (B) は、閉じた状態であり、タブレット型端末は、筐体 9630、太陽電池 9633、充放電制御回路 9634、バッテリー 9635、DCDC コンバータ 9636 を有する。なお、図 7 (B) では充放電制御回路 9634 の一例としてバッテリー 9635、DCDC コンバータ 9636 を有する構成について示している。20

#### 【0116】

なお、タブレット型端末は 2 つ折り可能なため、未使用時に筐体 9630 を閉じた状態にすることができる。従って、表示部 9631a、表示部 9631b を保護できるため、耐久性に優れ、長期使用の観点からも信頼性の優れたタブレット型端末を提供できる。

#### 【0117】

また、この他にも図 7 (A) 及び図 7 (B) に示したタブレット型端末は、様々な情報（静止画、動画、テキスト画像など）を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報をタッチ入力操作又は編集するタッチ入力機能、様々なソフトウェア（プログラム）によって処理を制御する機能、等を有することができる。30

#### 【0118】

タブレット型端末の表面に装着された太陽電池 9633 によって、電力をタッチパネル、表示部、又は映像信号処理部等に供給することができる。なお、太陽電池 9633 は、筐体 9630 の片面又は両面に設けることができ、バッテリー 9635 の充電を効率的に行う構成とすることができるため好適である。なおバッテリー 9635 としては、リチウムイオン電池を用いると、小型化を図れる等の利点がある。40

#### 【0119】

また、図 7 (B) に示す充放電制御回路 9634 の構成、及び動作について図 7 (C) にプロック図を示し説明する。図 7 (C) には、太陽電池 9633、バッテリー 9635、DCDC コンバータ 9636、コンバータ 9637、スイッチ SW1 乃至 SW3、表示部 9631 について示しており、バッテリー 9635、DCDC コンバータ 9636、コンバータ 9637、スイッチ SW1 乃至 SW3 が、図 7 (B) に示す充放電制御回路 9634 に対応する箇所となる。

#### 【0120】

まず外光により太陽電池 9633 により発電がされる場合の動作の例について説明する。太陽電池で発電した電力は、バッテリー 9635 を充電するための電圧となるよう DCDC

Cコンバータ9636で昇圧又は降圧がなされる。そして、表示部9631の動作に太陽電池9633からの電力が用いられる際にはスイッチSW1をオンにし、コンバータ9637で表示部9631に必要な電圧に昇圧又は降圧をすることとなる。また、表示部9631での表示を行わない際には、SW1をオフにし、SW2をオンにしてバッテリー9635の充電を行う構成とすればよい。

#### 【0121】

なお太陽電池9633については、発電手段の一例として示したが、特に限定されず、圧電素子（ピエゾ素子）や熱電変換素子（ペルティエ素子）などの他の発電手段によるバッテリー9635の充電を行う構成であってもよい。例えば、無線（非接触）で電力を送受信して充電する無接点電力伝送モジュールや、また他の充電手段を組み合わせて行う構成としてもよい。10

#### 【0122】

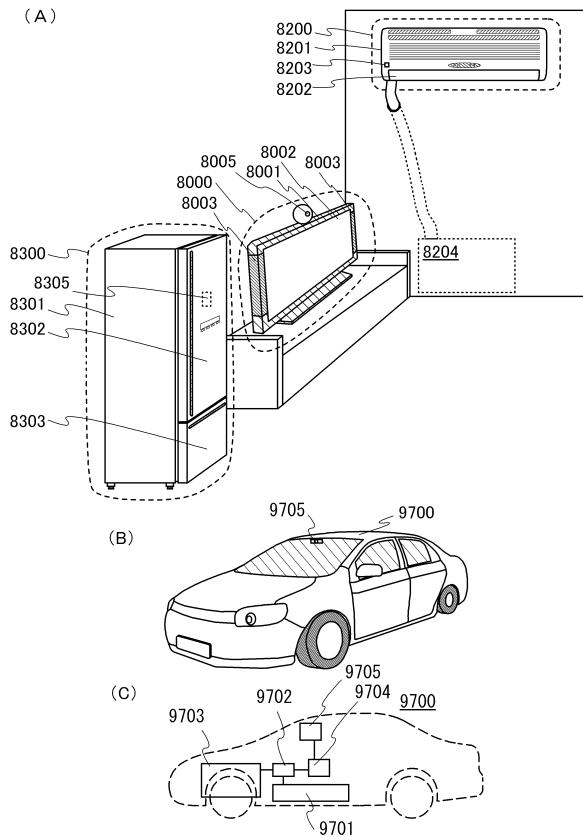

図8(A)において、テレビジョン装置8000は、筐体8001に表示部8002が組み込まれてあり、表示部8002により映像を表示し、スピーカ部8003から音声を出力することが可能である。また、固体撮像装置8005で撮像が可能である。実施の形態1に示す固体撮像装置を固体撮像装置8005に用いることが可能である。

#### 【0123】

表示部8002は、液晶表示装置、有機EL素子などの発光素子を各画素に備えた発光装置、電気泳動表示装置、DMD(Digital Micromirror Device)、PDP(Plasma Display Panel)などの、半導体表示装置を用いることができる。20

#### 【0124】

テレビジョン装置8000は、受信機やモデムなどを備えていてもよい。テレビジョン装置8000は、受信機により一般的のテレビ放送の受信を行うことができ、さらにモデムを介して有線又は無線による通信ネットワークに接続することにより、一方向（送信者から受信者）又は双方向（送信者と受信者間、あるいは受信者間同士など）の情報通信を行うことも可能である。例えば、固体撮像装置8005で撮像した映像を通信ネットワークを介して送信することができる。

#### 【0125】

図8(A)において、室内機8200及び室外機8204を有するエアコンディショナーは、実施の形態1の固体撮像装置8005を用いた電気機器の一例である。具体的に、室内機8200は、筐体8201、送風口8202、固体撮像装置8203等を有する。図8(A)において、固体撮像装置8203が、室内機8200に設けられている場合を例示している。実施の形態1に示した固体撮像装置8203は、撮像することができ、室内の人数などを認識することができ、その情報に基づいて温度調節を行うエアコンディショナーを実現できる。また、固体撮像装置8203により室内に人数が確認できない場合には、自動で停止する設定として消費電力を抑えることができる。30

#### 【0126】

図8(A)において、電気冷凍冷蔵庫8300は、固体撮像装置8305を備える電気機器の一例である。具体的に、電気冷凍冷蔵庫8300は、筐体8301、冷蔵室用扉8302、冷凍室用扉8303、固体撮像装置8305等を有する。図8(A)では、固体撮像装置8305が、筐体8301の内部に設けられている。実施の形態1に示した固体撮像装置を電気冷凍冷蔵庫8300の固体撮像装置8305に用いることによって、内部の映像を撮像でき、その映像に基づいて温度調節を行うことができるため、省電力化が図れる。また、電気冷凍冷蔵庫8300の内部の映像を固体撮像装置8305で撮像し、テレビジョン装置8000に送信し、表示させることで、電気冷凍冷蔵庫8300の扉を開けないことなく、電気冷凍冷蔵庫8300の内部に何があるかを確認でき、開け閉めによる温度変化を調節するための消費電力を抑えることができる。勿論、電気冷凍冷蔵庫8300の内部の映像を固体撮像装置8305で撮像する場合には、内部の照明をつけて撮像する。なお、電気冷凍冷蔵庫8300の内部の映像を詳細に把握するために、複数の固体撮像4050

装置 8305 を設置してもよい。

**【0127】**

図 8 (B)において、電気機器の一例である電気自動車の例を示す。電気自動車 9700 には、二次電池 9701 が搭載されている。二次電池 9701 の電力は、制御回路 9702 により出力が調整されて、駆動装置 9703 に供給される。制御回路 9702 は、図示しないROM、RAM、CPU等を有する処理装置 9704 によって制御される。実施の形態 1 に示した固体撮像装置 9705 を電気自動車 9700 に搭載し、ドライブレコーダとして用いることができる。

**【0128】**

駆動装置 9703 は、直流電動機若しくは交流電動機単体、又は電動機と内燃機関と、を組み合わせて構成される。処理装置 9704 は、電気自動車 9700 の運転者の操作情報（加速、減速、停止など）や走行時の情報（上り坂や下り坂等の情報、駆動輪にかかる負荷情報、固体撮像装置 9705 で撮像された前方映像など）の入力情報に基づき、制御回路 9702 に制御信号を出力する。制御回路 9702 は、処理装置 9704 の制御信号により、二次電池 9701 から供給される電気エネルギーを調整して駆動装置 9703 の出力を制御する。交流電動機を搭載している場合は、図示していないが、直流を交流に変換するインバータも内蔵される。

**【0129】**

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

**【符号の説明】**

**【0130】**

100：半導体基板

101：素子層

102：素子層

10

20

**【図 1】**

(A)

(B)

**【図 2】**

(A)

(B)

【図3】

【 四 4 】

【 図 5 】

【 6 】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開2011-142314(JP,A)

米国特許出願公開第2011/0140099(US,A1)

特開2010-141230(JP,A)

米国特許出願公開第2010/0148171(US,A1)

特開2012-028731(JP,A)

米国特許出願公開第2011/0309353(US,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 21/336

H01L 27/146