(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6250906号

(P6250906)

(45) 発行日 平成29年12月20日(2017.12.20)

(24) 登録日 平成29年12月1日(2017.12.1)

|              |           |             |      |

|--------------|-----------|-------------|------|

| (51) Int.Cl. | F 1       |             |      |

| HO1L 21/336  | (2006.01) | HO1L 29/78  | 626C |

| HO1L 29/786  | (2006.01) | HO1L 27/108 | 321  |

| HO1L 21/8242 | (2006.01) | HO1L 27/105 | 441  |

| HO1L 27/108  | (2006.01) | HO1L 27/10  | 461  |

| HO1L 21/8239 | (2006.01) | HO1L 27/108 | 671C |

請求項の数 3 (全 99 頁) 最終頁に続く

|              |                                   |                 |                              |

|--------------|-----------------------------------|-----------------|------------------------------|

| (21) 出願番号    | 特願2016-93804 (P2016-93804)        | (73) 特許権者       | 000153878                    |

| (22) 出願日     | 平成28年5月9日(2016.5.9)               | 株式会社半導体エネルギー研究所 |                              |

| (62) 分割の表示   | 特願2012-97372 (P2012-97372)<br>の分割 | 神奈川県厚木市長谷398番地  |                              |

| 原出願日         | 平成24年4月23日(2012.4.23)             | (72) 発明者        | 冢田 義紀<br>神奈川県厚木市長谷398番地 株式会社 |

| (65) 公開番号    | 特開2016-184748 (P2016-184748A)     | 半導体エネルギー研究所内    |                              |

| (43) 公開日     | 平成28年10月20日(2016.10.20)           | (72) 発明者        | 磯部 敦生<br>神奈川県厚木市長谷398番地 株式会社 |

| 審査請求日        | 平成28年6月3日(2016.6.3)               | 半導体エネルギー研究所内    |                              |

| (31) 優先権主張番号 | 特願2011-102569 (P2011-102569)      | (72) 発明者        | 塙野入 豊<br>神奈川県厚木市長谷398番地 株式会社 |

| (32) 優先日     | 平成23年4月29日(2011.4.29)             | 半導体エネルギー研究所内    |                              |

| (33) 優先権主張国  | 日本国(JP)                           | (72) 発明者        | 熱海 知昭<br>神奈川県厚木市長谷398番地 株式会社 |

| (31) 優先権主張番号 | 特願2011-102571 (P2011-102571)      | 半導体エネルギー研究所内    |                              |

| (32) 優先日     | 平成23年4月29日(2011.4.29)             | (72) 発明者        |                              |

| (33) 優先権主張国  | 日本国(JP)                           | 半導体エネルギー研究所内    |                              |

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

## 【請求項1】

酸化物半導体層と、

前記酸化物半導体層の端部と接する絶縁層と、を有し、

前記絶縁層は、前記端部の側面と接する第1の酸化絶縁層と、前記端部と接しない第2の酸化絶縁層と、前記端部の下面と接する第3の酸化絶縁層とが積層された部分を有し、

前記絶縁層は、酸化アルミニウムを有し、前記酸化物半導体層の端部において、キャリアの移動経路の形成を抑制する機能を有することを特徴とする半導体装置。

## 【請求項2】

酸化物半導体層と、

前記酸化物半導体層の端部と接する絶縁層と、を有し、

前記絶縁層は、前記端部と接する第1の酸化絶縁層と、前記端部と接しない第2の酸化絶縁層とが積層された部分を有し、

前記絶縁層は、酸化アルミニウムを有し、前記酸化物半導体層の端部において、キャリアの移動経路の形成を抑制する機能を有することを特徴とする半導体装置。

## 【請求項3】

酸化物半導体層と、

前記酸化物半導体層の端部と接する絶縁層と、

前記酸化物半導体層の端部と接する導電層と、を有し、

前記絶縁層は、前記端部の側面と接する第1の酸化絶縁層と、前記端部と接しない第2の酸化絶縁層とが積層された部分を有し、

10

20

の酸化絶縁層と、前記端部の下面と接する第3の酸化絶縁層とが積層された部分を有し、前記導電層は、前記酸化物半導体層の上面と接し、

前記絶縁層は、酸化アルミニウムを有し、前記酸化物半導体層の端部において、キャリアの移動経路の形成を抑制する機能を有することを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、記憶装置を用いた半導体装置に関する。

【背景技術】

【0002】

中央演算処理装置(CPU: Central Processing Unit)などの半導体装置は、その用途によって多種多様な構成を有しているが、一般的に、データや命令を記憶するための主記憶装置の他に、高速でデータの書き込みと読み出しができるレジスタ、キャッシュなどの緩衝記憶装置が設けられている。緩衝記憶装置は、演算装置と主記憶装置の間に介在し、低速な主記憶装置へのアクセスを減らして演算処理を高速化させることを目的として、CPUに設けられている。

【0003】

通常は、レジスタとしてフリップフロップが、キャッシュとしてSRAM(Static Random Access Memory)が用いられる。下記特許文献1には、キャッシュとして、SRAMなどの揮発性メモリと、不揮発性メモリとを併用する構成について記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平7-121444号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、中央演算処理装置などの半導体装置には、高速動作のみならず、消費電力の低さと、集積度の高さが要求される。しかし、例えば、トランジスタのサイズにもよるが、ハイレベルの電源電位が与えられているノードと、ローレベルの電源電位が与えられているノードの間ににおいて、直列に接続されたpチャネル型トランジスタ及びnチャネル型トランジスタを、バルクのシリコンを用いて作製した場合、室温下にて、ノード間の電圧が約3Vの状態にて、1pA程度のオフ電流が生じる。中央演算処理装置や、緩衝記憶装置の規模が大型化してトランジスタ数が多くなるほど、或いは、中央演算処理装置や、緩衝記憶装置が設けられたICチップの温度が上昇するほど、上記オフ電流の総量は大きくなるため、消費電力が嵩んでしまう。よって、中央演算処理装置を構成しているトランジスタは、オフ電流が小さくなるように、その構造に工夫を凝らす必要がある。しかし、高速動作とオフ電流の小ささとを兼ね備えたトランジスタの実現は、開発に時間と費用を要する。

【0006】

半導体装置の消費電力を抑えるため、緩衝記憶装置への電源の供給を停止するという一つの方法が提案されている。緩衝記憶装置に用いられるフリップフロップやSRAMは揮発性であるため、上記方法では、揮発性の記憶装置の周辺に不揮発性の記憶装置を配置し、電源停止の前にデータを不揮発性の記憶装置へ一時的に移している。しかし、これらの不揮発性の記憶装置は、主に磁気素子や強誘電体が用いられているため、作製工程が複雑である。

【0007】

また、長時間の電源停止を行う際には、データをハードディスク、フラッシュメモリ等の記憶装置に移してから電源停止を行うこともできるが、それらの記憶装置はデータを元に

10

20

30

40

50

戻すのに時間を必要とするため、短時間の電源停止には適さない。

【0008】

上述の問題に鑑み、本発明は、高速動作を確保しつつ、消費電力を抑えることができる半導体装置の提供を目的の一つとする。或いは、本発明は、高速動作を確保しつつ、消費電力を抑えることができ、高集積化を実現できる半導体装置の提供を目的の一つとする。

【課題を解決するための手段】

【0009】

上記課題を解決するために、本発明の一態様では、結晶性を有するシリコン、またはゲルマニウムなどの半導体をチャネル形成領域に有するトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するスイッチング素子とを、半導体装置に設ける。さらに、本発明の一態様では、上記記憶素子を構成するトランジスタが形成されている層上に、上記スイッチング素子を構成するトランジスタが形成されており、なおかつ、記憶素子を構成するトランジスタが有するソース電極及びドレイン電極のいずれか一方が、スイッチング素子を構成するトランジスタが有するソース電極及びドレイン電極のいずれか一方として、機能しているものとする。

10

【0010】

或いは、上記課題を解決するために、本発明の一態様では、結晶性を有するシリコン、またはゲルマニウムなどの半導体をチャネル形成領域に有するトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するスイッチング素子とを、半導体装置に設ける。さらに、本発明の一態様では、上記記憶素子を構成するトランジスタが形成されている層上に、上記スイッチング素子を構成するトランジスタが形成されているものとする。

20

【0011】

上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。よって、酸化物半導体をチャネル形成領域に有するトランジスタは、通常のシリコンやゲルマニウムなどの半導体で形成されたトランジスタに比べて、オフ電流が極めて小さい。

【0012】

30

また、本発明の一態様では、酸化物半導体をチャネル形成領域に有するトランジスタのオフ電流をさらに小さくするために、半導体装置に以下の第1の構成を採用する。具体的に、本発明の一態様に係る半導体装置において、上記スイッチング素子を構成するトランジスタは、絶縁膜上に形成される酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を間に挟んで酸化物半導体膜と重なる位置に設けられたゲート電極と、酸化物半導体膜に接続された一対の導電膜と、を有する。酸化物半導体膜は、ゲート電極と重なり、少なくとも一部がチャネル形成領域として機能する第1の領域と、第1の領域を挟む一対の第2の領域とを有している。また、上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有する。そして、上記酸化物半導体膜は、第1の領域において上記第1の酸化絶縁膜に接し、第2の領域において第1の酸化絶縁膜及び第2の酸化絶縁膜に接する。

40

【0013】

上記構成により、第1の酸化絶縁膜から放出された酸素は、第2の酸化絶縁膜への拡散が妨げられるため、第1の領域における酸化物半導体膜の端部に効率よく供給される。なお、酸化物半導体をチャネル形成領域に有するトランジスタは、酸化物半導体膜を所望の形状にエッティングするためのエッティング処理、酸化物半導体膜の端部の減圧雰囲気における暴露等により、酸化物半導体膜の端部において酸素の脱離による酸素欠損が形成されやすい。そして、酸素欠損はキャリアの移動経路となるため、酸化物半導体膜の端部に酸素欠損が形成されると、寄生チャネルが生じ、それによりトランジスタのオフ電流が大きくな

50

る。しかし、本発明の一態様では、上記構成により、第1の領域における酸化物半導体膜の端部に酸素欠損が形成されるのを防ぎ、オフ電流を小さくさせることができる。

【0014】

或いは、本発明の一態様では、酸化物半導体をチャネル形成領域に有するトランジスタのオフ電流をさらに小さくさせるために、半導体装置に上記第1の構成の代わりに、以下の第2の構成を採用しても良い。具体的に、本発明の一態様に係る半導体装置において、上記スイッチング素子を構成するトランジスタは、酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を間に挟んで酸化物半導体膜と重なる位置に設けられたゲート電極と、酸化物半導体膜に接続された一対の導電膜と、を有する。さらに、上記半導体装置は、酸化物半導体膜の端部と接するように、酸化物半導体膜の周囲に設けられ、なおかつ加熱により一部の酸素が脱離する第1の酸化絶縁膜と、当該第1の酸化絶縁膜を間に挟んで酸化物半導体膜の周囲に設けられ、なおかつ酸素の拡散を防ぐ第2の酸化絶縁膜と、酸化物半導体膜の下部に設けられ、なおかつ加熱により一部の酸素が脱離する第3の酸化絶縁膜と、を有する。また、酸化物半導体膜は、ゲート電極と重なり、少なくとも一部がチャネル形成領域として機能する第1の領域と、第1の領域を挟む一対の第2の領域とを有している。

10

【0015】

上記構成により、第1の酸化絶縁膜から放出された酸素は、第2の酸化絶縁膜への拡散が妨げられるため、酸化物半導体膜の端部に効率よく供給される。また、第3の酸化絶縁膜から放出された酸素は、酸化物半導体膜の下部に供給される。上述したように、酸化物半導体をチャネル形成領域に有するトランジスタは、酸化物半導体膜を所望の形状にエッチングするためのエッチング処理、酸化物半導体膜の端部の減圧雰囲気における暴露等により、酸化物半導体膜の端部において酸素の脱離による酸素欠損が形成されやすい。そして、酸素欠損はキャリアの移動経路となるため、酸化物半導体膜の端部に酸素欠損が形成されると、寄生チャネルが生じ、それによりトランジスタのオフ電流が大きくなる。しかし、本発明の一態様では、酸化物半導体膜の端部、特に、第1の領域における酸化物半導体膜の端部に酸素が効率よく供給されることにより、第1の領域における酸化物半導体膜の端部に酸素欠損が形成されるのを防ぎ、オフ電流を小さくさせることができる。

20

【0016】

なお、上記第1の構成或いは第2の構成を有する半導体装置において、上記酸化物半導体膜は、第2の領域が、ドーパントを含んでいても良い。或いは、上記酸化物半導体膜は、第2の領域が、ドーパントを含む一対の第3の領域と、上記ドーパントの濃度が第3の領域よりも高い一対の第4の領域とを有していても良い。具体的に、酸化物半導体膜は、第1の領域と、第1の領域を挟む一対の第2の領域とを有し、第2の領域は、第1の領域を挟む一対の第3の領域と、第1の領域及び一対の第3の領域を挟む一対の第4の領域とを有する。上記第3の領域は、電界緩和領域として機能する。

30

【0017】

酸化物半導体膜を活性層として用いたトランジスタのオフ電流が小さいことは、いろいろな実験により証明できる。例えば、チャネル幅が  $1 \times 10^6 \mu\text{m}$  でチャネル長が  $10 \mu\text{m}$  の素子であっても、ソース端子とドレイン端子間の電圧（ドレイン電圧）が  $1\text{V}$  から  $10\text{V}$  の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち  $1 \times 10^{-13} \text{ A}$  以下という特性を得ることができる。この場合、オフ電流をトランジスタのチャネル幅で除した数値に相当するオフ電流密度は、 $100\text{zA}/\mu\text{m}$  以下であることが分かる。

40

【0018】

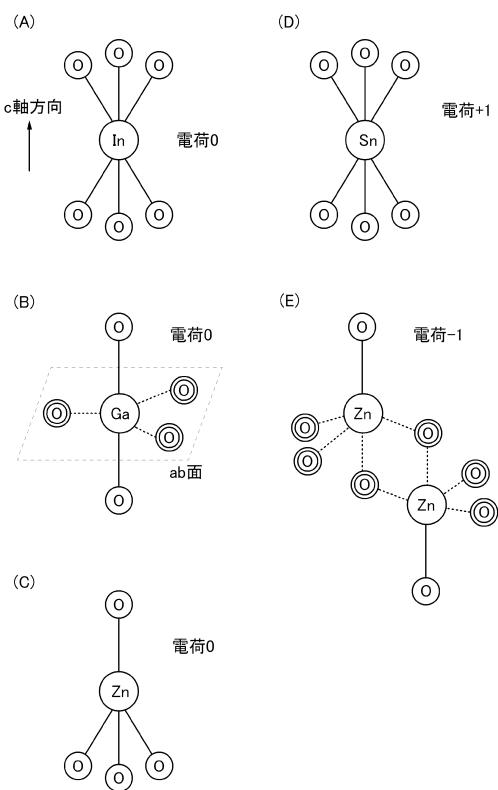

用いる酸化物半導体としては、少なくともインジウム（In）あるいは亜鉛（Zn）を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム（Ga）を有することが好ましい。また、スタビライザーとしてスズ（Sn）を有することが好ましい。また、スタビライザーとしてハフニウム（Hf）を有する

50

ことが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

#### 【0019】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

#### 【0020】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、三元系金属の酸化物であるIn-Ga-Zn系酸化物(IGZOとも表記する)、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。

10

#### 【0021】

なお、ここで、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

20

#### 【0022】

また、酸化物半導体として、 $InMO_3 (ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、 $In_3SnO_5 (ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数)で表記される材料を用いてもよい。

30

#### 【0023】

例えば、 $In : Ga : Zn = 1 : 1 : 1$  ( $= 1/3 : 1/3 : 1/3$ )あるいは $In : Ga : Zn = 2 : 2 : 1$  ( $= 2/5 : 2/5 : 1/5$ )の原子数比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1$  ( $= 1/3 : 1/3 : 1/3$ )、 $In : Sn : Zn = 2 : 1 : 3$  ( $= 1/3 : 1/6 : 1/2$ )あるいは $In : Sn : Zn = 2 : 1 : 5$  ( $= 1/4 : 1/8 : 5/8$ )の原子数比のIn-Sn-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0024】

40

しかし、これらに限られず、必要とする電気的特性(移動度、しきい値電圧、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする電気的特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

#### 【0025】

例えば、In-Sn-Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In-Ga-Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

#### 【0026】

なお、例えば、In、Ga、Znの原子数比が $In : Ga : Zn = a : b : c$  ( $a + b +$

50

$c = 1$  ) である酸化物の組成が、原子数比が  $In : Ga : Zn = A : B : C$  ( $A + B + C = 1$  ) の酸化物の組成の近傍であるとは、 $a$ 、 $b$ 、 $c$  が、 $(a - A)^2 + (b - B)^2 + (c - C)^2 = r^2$  を満たすことを言い、 $r$  は、例えば、0.05 とすればよい。他の酸化物でも同様である。

【0027】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0028】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0029】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ ( $R_a$ ) が  $1 \text{ nm}$  以下、好ましくは  $0.3 \text{ nm}$  以下、より好ましくは  $0.1 \text{ nm}$  以下の表面上に形成するとよい。

【0030】

なお、 $R_a$  は、JIS B 0601 で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の数式 1 にて定義される。

【0031】

【数1】

$$Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy \cdots \quad (\text{式1})$$

【0032】

なお、上記において、 $S_0$  は、測定面 (座標  $(x_1, y_1)$   $(x_1, y_2)$   $(x_2, y_1)$   $(x_2, y_2)$  ) で表される 4 点によって囲まれる長方形の領域) の面積を指し、 $Z_0$  は測定面の平均高さを指す。 $R_a$  は原子間力顕微鏡 (AFM: Atomic Force Microscope) にて評価可能である。

【発明の効果】

【0033】

本発明の一態様では、記憶素子を構成するトランジスタが、結晶性を有するシリコン、またはゲルマニウムなどの半導体をチャネル形成領域に有することで、半導体装置の高速動作を確保することができる。また、本発明の一態様では、オフ電流が極めて小さいトランジスタでスイッチング素子を構成することで、スイッチング素子を介して容量素子からリードする電荷の量を小さく抑えることができる。すなわち、本発明の一態様では、記憶素子とスイッチング素子に要求される特性に合わせて、最適な構造のトランジスタを容易に作り分けることができる。また、本発明の一態様では、記憶素子を構成するトランジスタと、スイッチング素子を構成するトランジスタとを積層することで、半導体装置の高集積化を実現することができる。

【0034】

よって、本発明の一態様では、上記構成により、高速動作を確保しつつ、消費電力を抑えることができる半導体装置を実現できる。或いは、本発明の一態様では、高速動作を確保しつつ、消費電力を抑えることができ、高集積化を実現できる半導体装置を実現できる。

【図面の簡単な説明】

【0035】

10

20

30

40

50

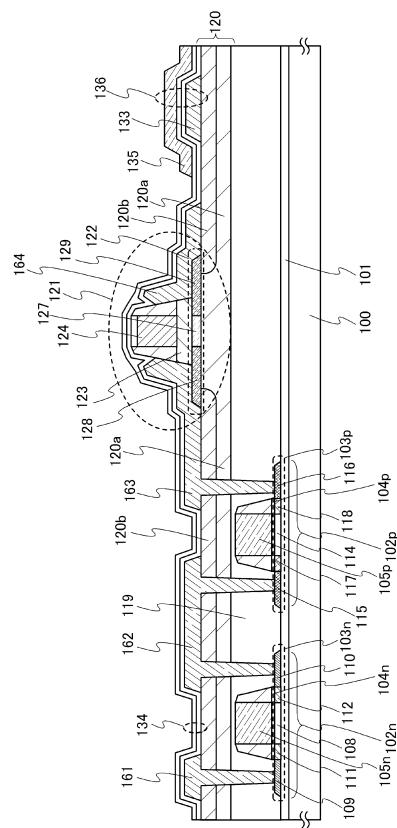

- 【図 1】半導体装置の断面図。

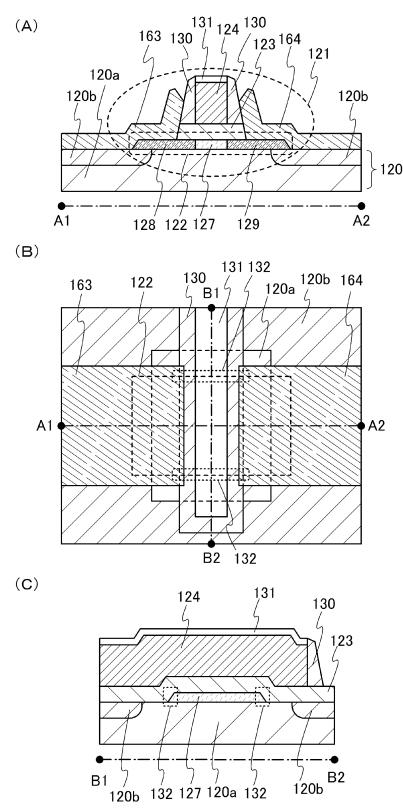

- 【図 2】トランジスタの断面図、及び上面図。

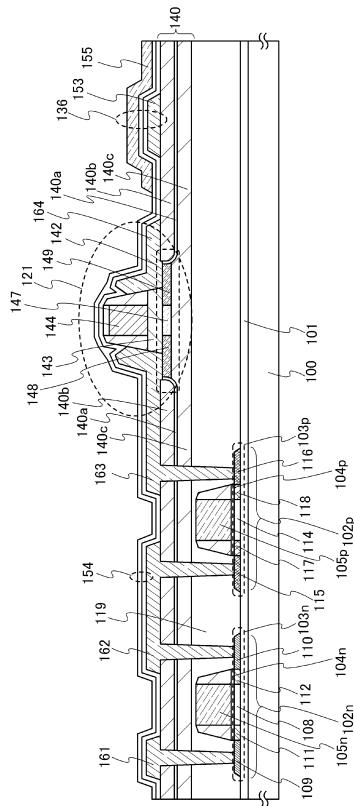

- 【図 3】半導体装置の断面図。

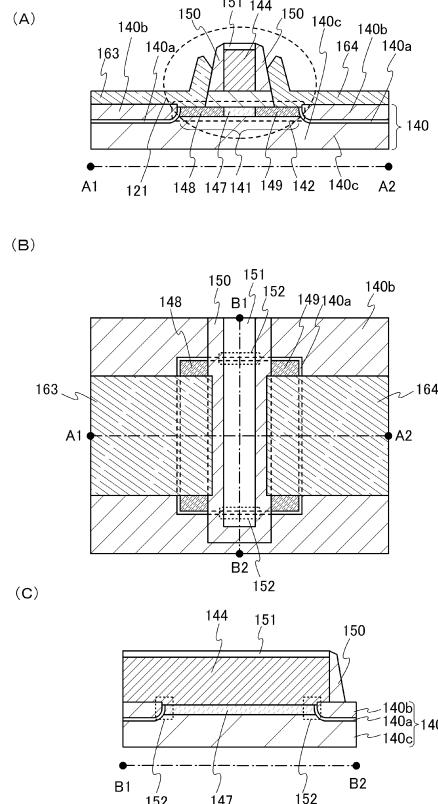

- 【図 4】トランジスタの断面図、及び上面図。

- 【図 5】記憶回路の回路図。

- 【図 6】記憶装置の構成を示す図。

- 【図 7】半導体装置のブロック図。

- 【図 8】半導体装置の作製方法を示す図。

- 【図 9】半導体装置の作製方法を示す図。

- 【図 10】半導体装置の作製方法を示す図。

- 【図 11】半導体装置の作製方法を示す図。

- 【図 12】半導体装置の作製方法を示す図。

- 【図 13】半導体装置の作製方法を示す図。

- 【図 14】半導体装置の作製方法を示す図。

- 【図 15】半導体装置の作製方法を示す図。

- 【図 16】半導体装置の作製方法を示す図。

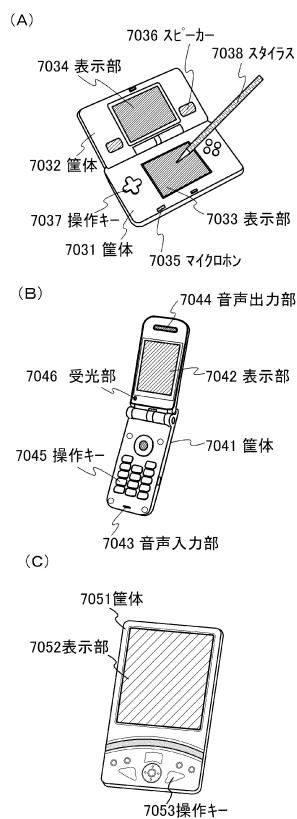

- 【図 17】電子機器の図。

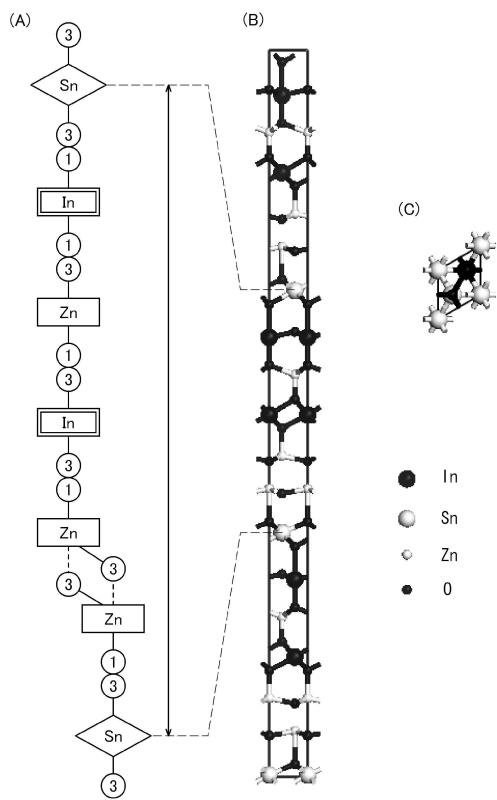

- 【図 18】本発明の一態様に係る酸化物半導体の構造を説明する図。

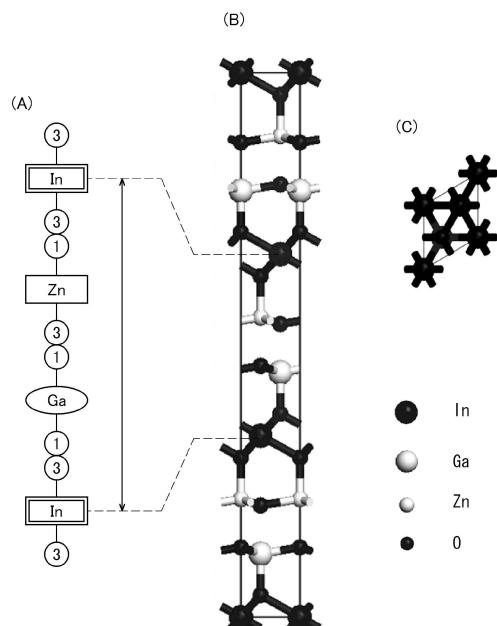

- 【図 19】本発明の一態様に係る酸化物半導体の構造を説明する図。

- 【図 20】本発明の一態様に係る酸化物半導体の構造を説明する図。

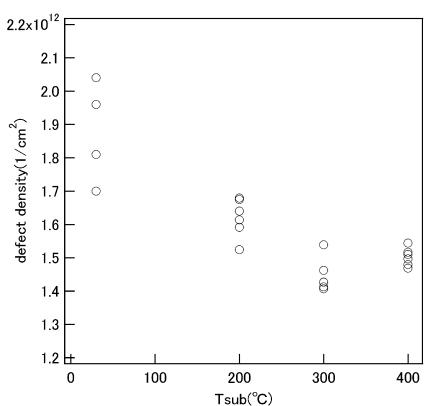

- 【図 21】基板加熱温度と欠陥密度の関係を示す図。

- 【図 22】計算によって得られた移動度のゲート電圧依存性を説明する図。

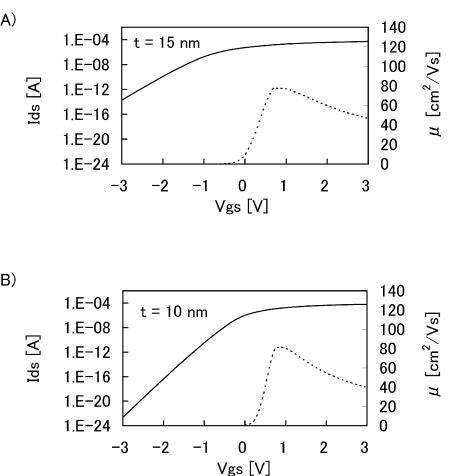

- 【図 23】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図。

- 【図 24】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図。

- 【図 25】計算によって得られたドレイン電流と移動度のゲート電圧依存性を説明する図。

- 【図 26】計算に用いたトランジスタの断面構造を説明する図。

- 【図 27】酸化物半導体膜を用いたトランジスタ特性のグラフ。

- 【図 28】試料 1 のトランジスタの B T 試験後の  $V_{g_s}$  -  $I_{d_s}$  特性を示す図。

- 【図 29】試料 2 であるトランジスタの B T 試験後の  $V_{g_s}$  -  $I_{d_s}$  特性を示す図。

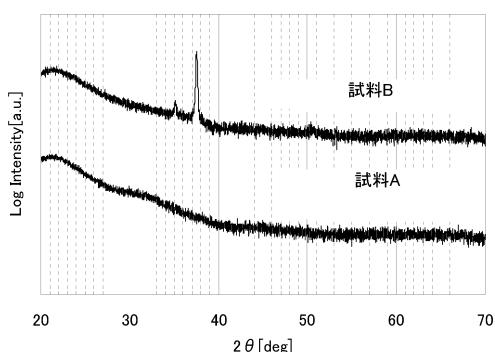

- 【図 30】試料 A および試料 B の X R D スペクトルを示す図。

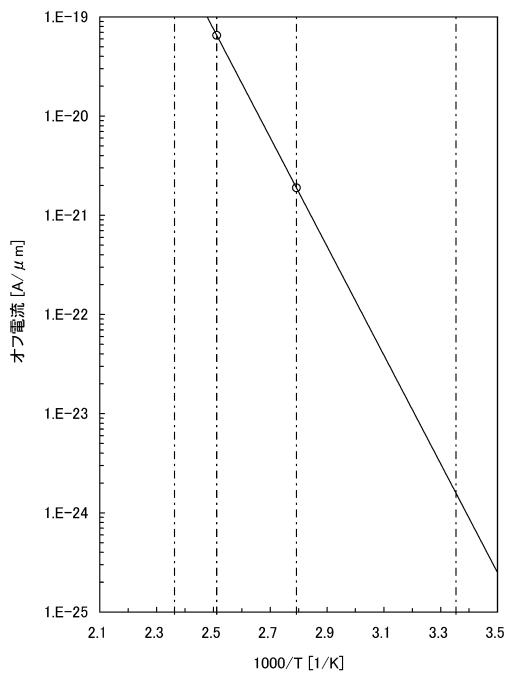

- 【図 31】トランジスタのオフ電流と測定時基板温度との関係を示す図。

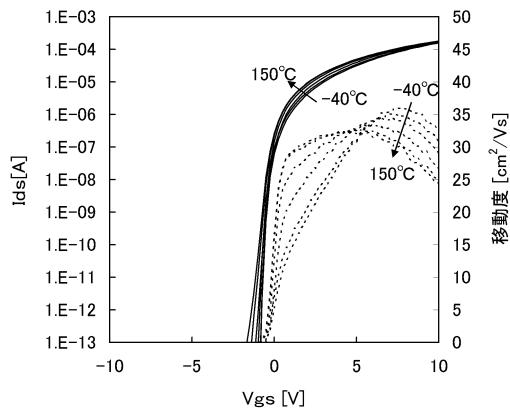

- 【図 32】 $I_{d_s}$  および移動度の  $V_{g_s}$  依存性を示す図。

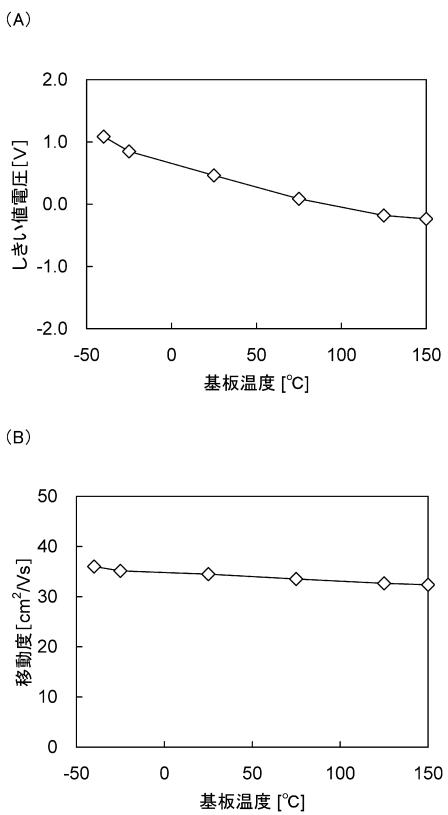

- 【図 33】基板温度としきい値電圧の関係および基板温度と移動度の関係を示す図。

- 【図 34】半導体装置の上面図及び断面図。

- 【図 35】半導体装置の上面図及び断面図。

- 【図 36】半導体装置の断面図。

- 【図 37】トランジスタの断面図、及び上面図。

- 【図 38】半導体装置の断面図。

- 【図 39】半導体装置の断面図。

- 【図 40】トランジスタの断面図、及び上面図。

- 【図 41】半導体装置の断面図。

- 【図 42】半導体装置の作製方法を示す図。

- 【図 43】半導体装置の作製方法を示す図。

- 【図 44】半導体装置の作製方法を示す図。

- 【図 45】半導体装置の作製方法を示す図。

- 【図 46】半導体装置の作製方法を示す図。

- 【図 47】半導体装置の作製方法を示す図。

10

20

30

40

50

【図48】半導体装置の作製方法を示す図。

【図49】半導体装置の作製方法を示す図。

【図50】半導体装置の作製方法を示す図。

【図51】半導体装置の作製方法を示す図。

【図52】半導体装置の作製方法を示す図。

【発明を実施するための形態】

【0036】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

10

【0037】

なお、集積回路や、RFタグ、半導体表示装置など、記憶装置を用いることができるありとあらゆる半導体装置が、本発明の範疇に含まれる。集積回路には、マイクロプロセッサ、画像処理回路、DSP(Digital Signal Processor)、マイクロコントローラ等を含むLSI(Large Scale Integrated Circuit)、FPGA(Field Programmable Gate Array)やCPLD(Complex PLD)などのプログラマブル論理回路(PLD:Programmable Logic Device)が、その範疇に含まれる。また、半導体表示装置には、液晶表示装置、有機発光素子(OLED)に代表される発光素子を各画素に備えた発光装置、電子ペーパー、DMD(Digital Micromirror Device)、PDP(Plasma Display Panel)、FED(Field Emission Display)など、半導体膜を用いた回路素子を駆動回路に有している半導体表示装置が、その範疇に含まれる。

20

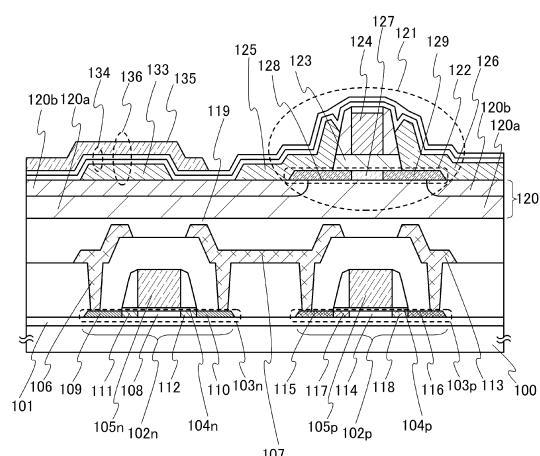

【0038】

(実施の形態1)

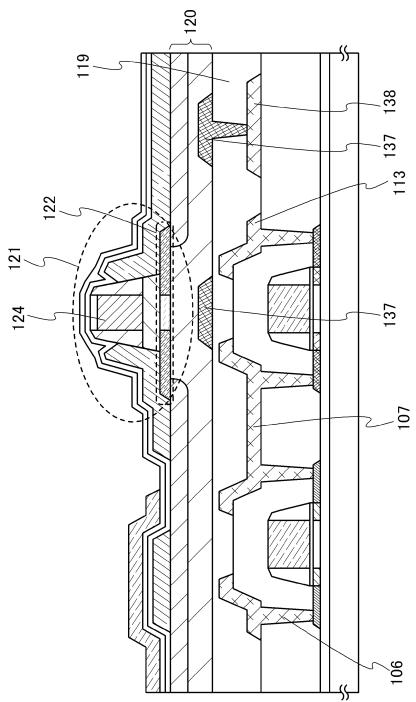

本発明の一態様に係る半導体装置は、結晶性を有するシリコン、またはゲルマニウムなどの半導体をチャネル形成領域に有するトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するスイッチング素子とを有する。図1に、記憶素子が有するnチャネル型トランジスタ102n及びpチャネル型トランジスタ102pと、容量素子136と、スイッチング素子が有するトランジスタ121との構成を断面図で一例として示す。

30

【0039】

図1に示す半導体装置は、その表面に絶縁膜101が形成された基板100上に、nチャネル型トランジスタ102nと、pチャネル型トランジスタ102pとを有する。

【0040】

nチャネル型トランジスタ102nは、結晶性を有するシリコンを有する半導体膜103nと、半導体膜103n上のゲート絶縁膜104nと、ゲート絶縁膜104nを間に挟んで半導体膜103nと重なる位置に設けられたゲート電極105nと、半導体膜103nに接続され、ソース電極またはドレイン電極として機能する導電膜161及び導電膜162とを有する。そして、半導体膜103nは、チャネル形成領域として機能する第1の領域108と、ソースまたはドレインとして機能する第2の領域109及び第2の領域110とを有する。第2の領域109及び第2の領域110は、第1の領域108を間に挟んでいる。なお、図1では、半導体膜103nが、第1の領域108と第2の領域109及び第2の領域110との間に、LDD(Lightly Doped Drain)領域として機能する第3の領域111及び第3の領域112を有している場合を例示している。

40

【0041】

また、pチャネル型トランジスタ102pは、結晶性を有するシリコンを有する半導体膜103pと、半導体膜103p上のゲート絶縁膜104pと、ゲート絶縁膜104pを間

50

に挟んで半導体膜 103p と重なる位置に設けられたゲート電極 105p と、半導体膜 103p に接続され、ソース電極またはドレイン電極として機能する導電膜 162 及び導電膜 163 とを有する。そして、半導体膜 103p は、チャネル形成領域として機能する第 1 の領域 114 と、ソースまたはドレインとして機能する第 2 の領域 115 及び第 2 の領域 116 とを有する。第 2 の領域 115 及び第 2 の領域 116 は、第 1 の領域 114 を間に挟んでいる。なお、図 1 では、半導体膜 103p が、第 1 の領域 114 と第 2 の領域 115 及び第 2 の領域 116 との間に、LDD 領域として機能する第 3 の領域 117 及び第 3 の領域 118 を有している場合を例示している。

#### 【0042】

なお、図 1 では、n チャネル型トランジスタ 102n と、p チャネル型トランジスタ 102p とが導電膜 162 を共有している場合を例示しているが、上記 2 つのトランジスタが互いに独立した導電膜を有していても良い。

#### 【0043】

また、図 1 では、n チャネル型トランジスタ 102n と、p チャネル型トランジスタ 102p とが、薄膜の半導体膜を用いている場合を例示しているが、n チャネル型トランジスタ 102n と、p チャネル型トランジスタ 102p とが、バルクの半導体基板にチャネル形成領域を有するトランジスタであっても良い。

#### 【0044】

また、図 1 に示す半導体装置では、n チャネル型トランジスタ 102n が有する半導体膜 103n、ゲート絶縁膜 104n、及びゲート電極 105n を覆うように、なおかつ、p チャネル型トランジスタ 102p が有する半導体膜 103p、ゲート絶縁膜 104p、及びゲート電極 105p を覆うように、絶縁膜 119 が設けられている。そして、絶縁膜 119 上には、第 1 の酸化絶縁膜 120a 及び第 2 の酸化絶縁膜 120b を有する絶縁膜 120 が設けられている。

#### 【0045】

導電膜 161 は、絶縁膜 119 及び絶縁膜 120 に設けられた開口部において第 2 の領域 109 に接するように、絶縁膜 120 上に設けられている。導電膜 162 は、絶縁膜 119 及び絶縁膜 120 に設けられた開口部において第 2 の領域 110 及び第 2 の領域 115 に接するように、絶縁膜 120 上に設けられている。導電膜 163 は、絶縁膜 119 及び絶縁膜 120 に設けられた開口部において第 2 の領域 116 に接するように、絶縁膜 120 上に設けられている。

#### 【0046】

第 1 の酸化絶縁膜 120a は、加熱により一部の酸素が脱離する酸化絶縁膜を用いて形成する。加熱により一部の酸素が脱離する酸化絶縁膜としては、化学量論的組成比を満たす酸素よりも多くの酸素を含む絶縁膜を用いることが好ましい。第 1 の酸化絶縁膜 120a として、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム等を用いることができる。

#### 【0047】

第 2 の酸化絶縁膜 120b は、酸素の拡散を防ぐ酸化絶縁膜で形成する。第 2 の酸化絶縁膜 120b の一例としては、酸化アルミニウム、酸化窒化アルミニウム等がある。なお、酸化アルミニウムは、化学量論的組成比を満たす酸素を含む酸化アルミニウム、または化学量論的組成比を満たす酸素よりも多くの酸素を含む酸化アルミニウム (A10<sub>x</sub>、x は 3 / 2 以上) とすることが好ましい。また、酸化窒化アルミニウムは、化学量論的組成比を満たす酸素を含む酸化アルミニウムの一部の酸素が窒素で置換されている。

#### 【0048】

なお、「加熱により一部の酸素が脱離する」とは、TDS (Thermal Desorption Spectroscopy : 昇温脱離ガス分光法) 分析にて、酸素原子に換算しての酸素の放出量が  $1.0 \times 10^{18}$  atoms / cm<sup>3</sup> 以上、好ましくは  $3.0 \times 10^{20}$  atoms / cm<sup>3</sup> 以上であることをいう。

#### 【0049】

10

20

30

40

50

ここで、TDS分析にて、酸素原子に換算しての酸素の脱離量の測定方法について、以下に説明する。

【0050】

TDS分析したときの気体の脱離量は、スペクトルの積分値に比例する。このため、絶縁膜のスペクトルの積分値と、標準試料の基準値に対する比とにより、気体の放出量を計算することができる。標準試料の基準値とは、所定の原子を含む試料の、スペクトルの積分値に対する原子の密度の割合である。

【0051】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、及び絶縁膜のTDS分析結果から、絶縁膜の酸素分子の脱離量( $N_{O_2}$ )は、数式2で求めることができる。質量数32のものとして $CH_3OH$ があるが、絶縁膜中に存在する可能性は低い。よって、TDS分析で得られる質量数32で検出されるスペクトルの全ては、酸素分子由来であると仮定する。また、酸素原子の同位体である質量数17の酸素原子及び質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため、存在しないものと仮定する。

【0052】

$$N_{O_2} = N_{H_2} / S_{H_2} \times S_{O_2} \times \quad \text{(数式2)}$$

【0053】

$N_{H_2}$ は、標準試料から脱離した水素分子を密度で換算した値である。 $S_{H_2}$ は、標準試料をTDS分析したときのスペクトルの積分値である。標準試料の基準値は、 $N_{H_2} / S_{H_2}$ とする。 $S_{O_2}$ は、絶縁膜をTDS分析したときのスペクトルの積分値である。は、TDS分析におけるスペクトル強度に影響する係数である。数式2の詳細に関しては、特開平6-275697公報を参照する。なお、上記絶縁膜の酸素の脱離量は、電子科学株式会社製の昇温脱離分析装置EMD-WA1000S/Wを用い、標準試料として $1 \times 10^{16} atoms/cm^3$ の水素原子を含むシリコンウェハを用いて測定する。

【0054】

また、TDS分析において、一部の酸素は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の脱離量についても見積もることができる。

【0055】

なお、 $N_{O_2}$ は酸素分子の脱離量である。絶縁膜においては、酸素原子に換算したときの酸素の放出量は、酸素分子の脱離量の2倍となる。

【0056】

上記構成において、加熱により酸素放出される絶縁膜は、酸素が過剰な酸化シリコン( $SiO_x$  ( $X > 2$ ))であってもよい。酸素が過剰な酸化シリコン( $SiO_x$  ( $X > 2$ ))とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数及び酸素原子数は、ラザフォード後方散乱法により測定した値である。

【0057】

絶縁膜120上には、スイッチング素子が有するトランジスタ121が設けられている。具体的に、トランジスタ121は、絶縁膜120上に位置する酸化物半導体膜122と、酸化物半導体膜122上のゲート絶縁膜123と、ゲート絶縁膜123を間に挟んで酸化物半導体膜122と重なる位置に設けられたゲート電極124と、酸化物半導体膜122に接続され、ソース電極またはドレイン電極として機能する導電膜163及び導電膜164とを有する。酸化物半導体膜122は、ゲート電極124と重なり、少なくとも一部がチャネル形成領域として機能する第1の領域127と、ソースまたはドレインとして機能し、第1の領域127を挟む第2の領域128及び第2の領域129とを有している。具体的に、導電膜163は、酸化物半導体膜122が有する第2の領域128に接続されている。また、導電膜164は、酸化物半導体膜122が有する第2の領域129に接続さ

10

20

30

40

50

れている。

【0058】

シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料の一例として、酸化物半導体の他に、炭化珪素(SiC)、窒化ガリウム(GaN)などの化合物半導体などがある。酸化物半導体は、炭化珪素や窒化ガリウムと異なり、スパッタリング法や湿式法により作製可能であり、量産性に優れるといった利点がある。また、炭化シリコンまたは窒化ガリウムとは異なり、酸化物半導体は室温でも成膜が可能なため、ガラス基板上への成膜、或いはシリコンを用いた集積回路上への成膜が可能である。また、基板の大型化にも対応が可能である。よって、上述したワイドギャップ半導体の中でも、特に酸化物半導体は量産性が高いというメリットを有する。また、トランジスタの性能(例えば移動度)を向上させるために結晶性の酸化物半導体を得ようとする場合でも、200から800の熱処理によって容易に結晶性の酸化物半導体を得ることができる。

【0059】

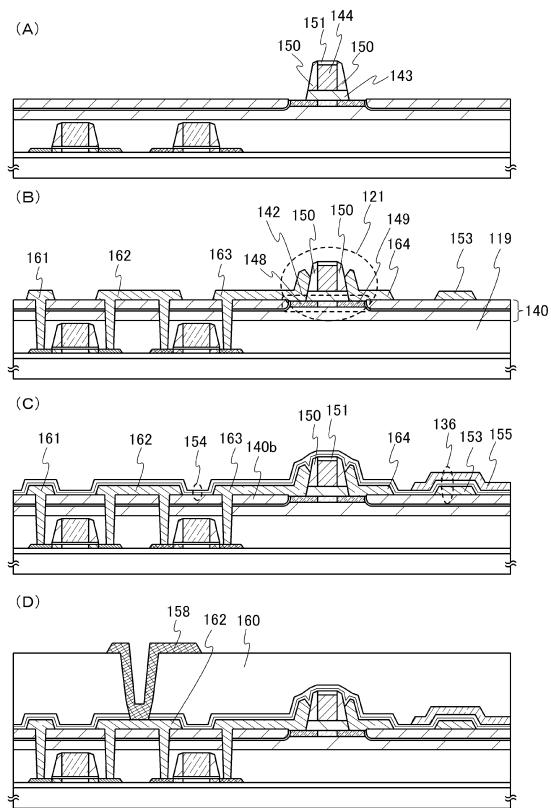

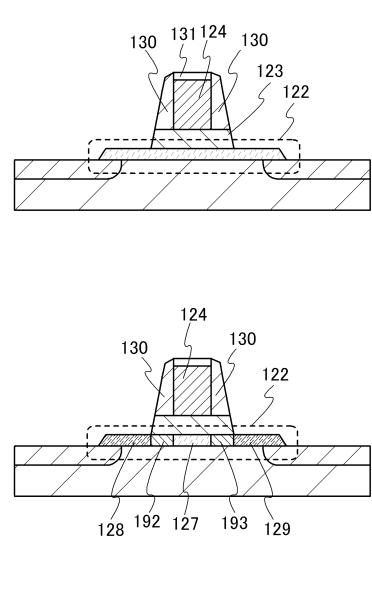

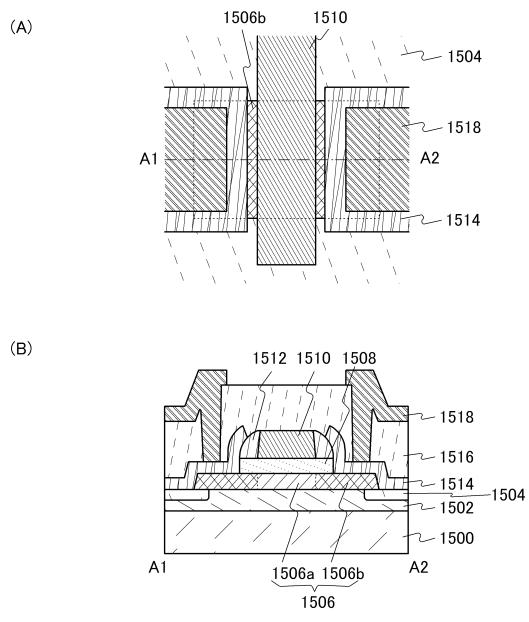

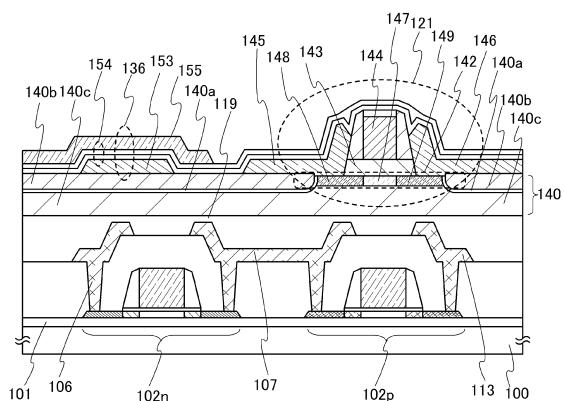

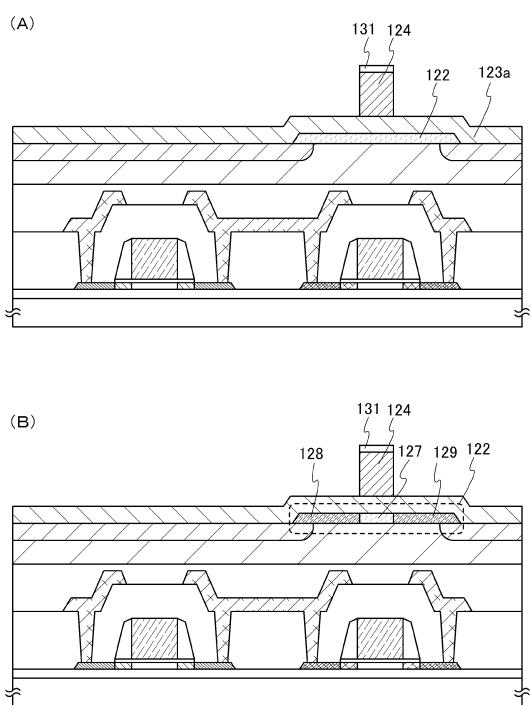

次いで、図2を用いて、酸化物半導体膜122が有する第1の領域127、第2の領域128及び第2の領域129と、絶縁膜120が有する第1の酸化絶縁膜120a及び第2の酸化絶縁膜120bとの位置関係について説明する。

【0060】

図2(A)は、絶縁膜120及びトランジスタ121の断面図であり、図2(B)は、絶縁膜120及びトランジスタ121の上面図である。図2(B)の破線A1-A2における断面図が、図2(A)に相当する。また、図2(C)は、図2(B)の破線B1-B2における、絶縁膜120及びトランジスタ121の断面図である。

【0061】

トランジスタ121は、ゲート電極124の側部に、絶縁膜を有するサイドウォール130が設けられており、ゲート電極124の上部に、絶縁膜131が設けられている。そして、導電膜163及び導電膜164は、その一部がサイドウォール130に接している。導電膜163及び導電膜164は必ずしもサイドウォール130に接している必要は無いが、サイドウォール130に接するように導電膜163及び導電膜164を形成することで、導電膜163及び導電膜164の位置が多少ずれて形成されたとしても、導電膜163及び導電膜164と酸化物半導体膜122との接する面積が、変動するのを防ぐことができる。よって、導電膜163及び導電膜164の位置がずれることによる、トランジスタ121のオン電流の変動を防ぐことができる。

【0062】

なお、ゲート電極124の上部に位置する絶縁膜131は必ずしも設ける必要は無いが、絶縁膜131を設けることで、導電膜163及び導電膜164の位置がずれて形成され、ゲート電極124の上部にかかっても、導電膜163及び導電膜164とゲート電極124が導通するのを防ぐことができる。

【0063】

そして、絶縁膜120は、第1の酸化絶縁膜120aの周囲に第2の酸化絶縁膜120bが設けられている。そして、酸化物半導体膜122は、第1の領域127において上記第1の酸化絶縁膜120aに接し、第2の領域128及び第2の領域129において第1の酸化絶縁膜120a及び第2の酸化絶縁膜120bに接する。

【0064】

上記構成により、加熱により第1の酸化絶縁膜120aから放出された酸素が、第2の酸化絶縁膜120bを通過するのを抑制することができるので、上記酸素が第1の領域127における酸化物半導体膜122の端部132に効率よく供給される。なお、酸化物半導体をチャネル形成領域に有するトランジスタ121は、酸化物半導体膜122を所望の形状にエッティングするためのエッティング処理、酸化物半導体膜122の端部の減圧雰囲気における暴露等により、酸化物半導体膜122の端部において酸素の脱離による酸素欠損が形成されやすい。そして、酸素欠損はキャリアの移動経路となるため、酸化物半導体膜1

22の端部に酸素欠損が形成されると、寄生チャネルが生じ、それによりトランジスタ121のオフ電流が大きくなる。しかし、本発明の一態様では、上記構成により、第1の領域127における酸化物半導体膜122の端部132に酸素欠損が形成されるのを防ぎ、オフ電流を小さくさせることができる。

【0065】

なお、特に断りがない限り、本明細書でオフ電流とは、nチャネル型トランジスタにおいては、ドレインをソースとゲート電極よりも高い電位とした状態において、ソースの電位を基準としたときのゲート電極の電位が0以下であるときに、ソースとドレインの間に流れる電流のことを意味する。或いは、本明細書でオフ電流とは、pチャネル型トランジスタにおいては、ドレインをソースとゲート電極よりも低い電位とした状態において、ソースの電位を基準としたときのゲート電極の電位が0以上であるときに、ソースとドレインの間に流れる電流のことを意味する。

10

【0066】

また、図1に示すように、容量素子136は、絶縁膜120上の導電膜133と、導電膜133上の絶縁膜134と、絶縁膜134を間に挟んで導電膜133と重なる位置に設けられた導電膜135とを有する。絶縁膜134は、トランジスタ121上にも設けられている。また、導電膜133と導電膜164とは電気的に接続されていても良いし、或いは、導電膜133と導電膜164とが一の連続した導電膜で構成されていても良い。

【0067】

なお、図1では、容量素子136をトランジスタ121と共に絶縁膜120の上に設けている場合を例示しているが、容量素子136は、nチャネル型トランジスタ102n及びpチャネル型トランジスタ102pと共に、絶縁膜120の下に設けられていても良い。

20

【0068】

また、トランジスタ121は、ゲート電極124を酸化物半導体膜122の片側において少なくとも有していれば良いが、酸化物半導体膜122を間に挟んで存在する一対のゲート電極を有していても良い。

【0069】

次いで、図1に示した構成とは異なる、本発明の一態様に係る半導体装置の構成について説明する。図3に、記憶素子が有するnチャネル型トランジスタ102n及びpチャネル型トランジスタ102pと、容量素子136と、スイッチング素子が有するトランジスタ121との構成を断面図で一例として示す。

30

【0070】

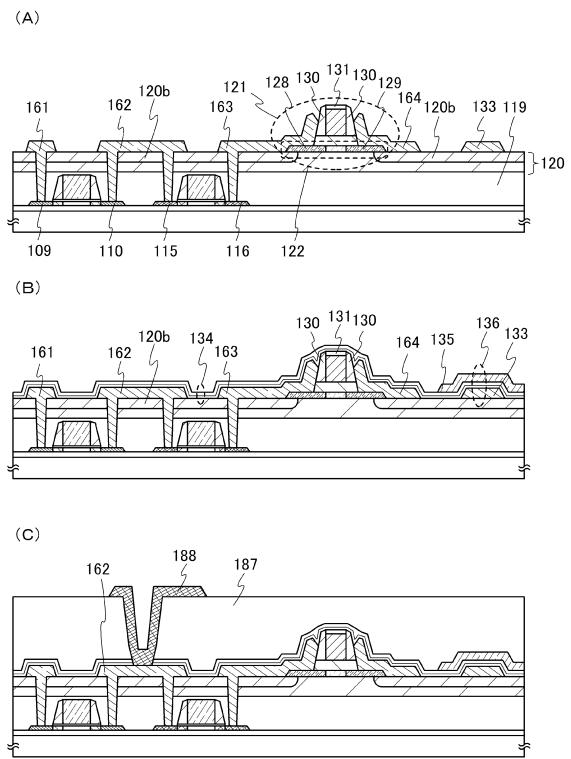

図3に示す半導体装置は、図1に示す半導体装置と同様に、その表面に絶縁膜101が形成された基板100上に、nチャネル型トランジスタ102nと、pチャネル型トランジスタ102pとを有する。nチャネル型トランジスタ102nと、pチャネル型トランジスタ102pの具体的な構成については、図1と同様である。

【0071】

そして、図3に示す半導体装置は、図1と同様に、nチャネル型トランジスタ102nが有する半導体膜103n、ゲート絶縁膜104n、及びゲート電極105nを覆うように、なおかつ、pチャネル型トランジスタ102pが有する半導体膜103p、ゲート絶縁膜104p、及びゲート電極105pを覆うように、絶縁膜119が設けられている。そして、絶縁膜119上には、第1の酸化絶縁膜140a、第2の酸化絶縁膜140b、及び第3の酸化絶縁膜140cを有する絶縁膜140が設けられている。絶縁膜140上には、スイッチング素子が有するトランジスタ121が設けられている。

40

【0072】

導電膜161は、絶縁膜119及び絶縁膜140に設けられた開口部において第2の領域109に接するように、絶縁膜140上に設けられている。導電膜162は、絶縁膜119及び絶縁膜140に設けられた開口部において第2の領域110及び第2の領域115に接するように、絶縁膜140上に設けられている。導電膜163は、絶縁膜119及び絶縁膜140に設けられた開口部において第2の領域115に接するように、絶縁膜140

50

0上に設けられている。

【0073】

第1の酸化絶縁膜140a及び第3の酸化絶縁膜140cは、加熱により一部の酸素が脱離する酸化絶縁膜を用いて形成する。加熱により一部の酸素が脱離する酸化絶縁膜としては、化学量論的組成比を満たす酸素よりも多くの酸素を含む絶縁膜を用いることが好ましい。第1の酸化絶縁膜140aとして、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム等を用いることができる。

【0074】

第2の酸化絶縁膜140bは、酸素の拡散を防ぐ酸化絶縁膜で形成する。第2の酸化絶縁膜140bの一例としては、酸化アルミニウム、酸化窒化アルミニウム等がある。なお、酸化アルミニウムは、化学量論的組成比を満たす酸素を含む酸化アルミニウム、または化学量論的組成比を満たす酸素よりも多くの酸素を含む酸化アルミニウム(A10<sub>x</sub>、xは3/2以上)とすることが好ましい。また、酸化窒化アルミニウムは、化学量論的組成比を満たす酸素を含む酸化アルミニウムの一部の酸素が窒素で置換されている。

10

【0075】

また、具体的に、トランジスタ121は、酸化物半導体膜142と、酸化物半導体膜142上のゲート絶縁膜143と、ゲート絶縁膜143を間に挟んで酸化物半導体膜142と重なる位置に設けられたゲート電極144と、酸化物半導体膜142に接続され、ソース電極またはドレイン電極として機能する導電膜163及び導電膜164とを有する。酸化物半導体膜142は、ゲート電極144と重なり、少なくとも一部がチャネル形成領域として機能する第1の領域147と、ソースまたはドレインとして機能し、第1の領域147を挟む第2の領域148及び第2の領域149とを有している。

20

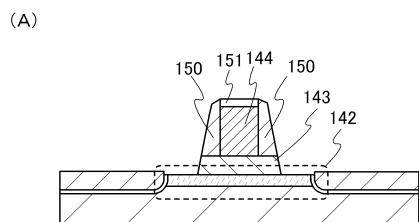

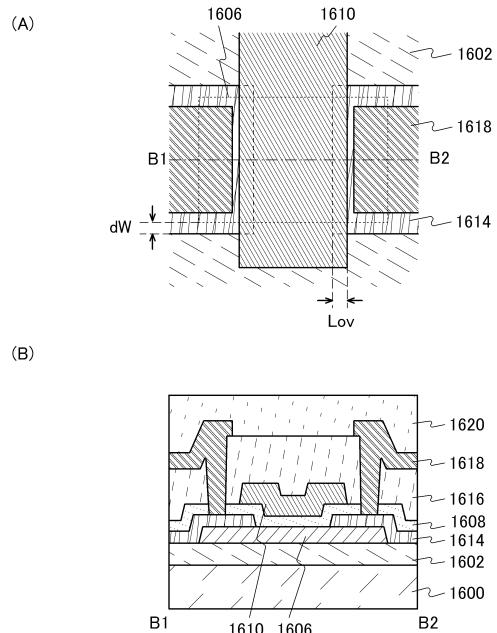

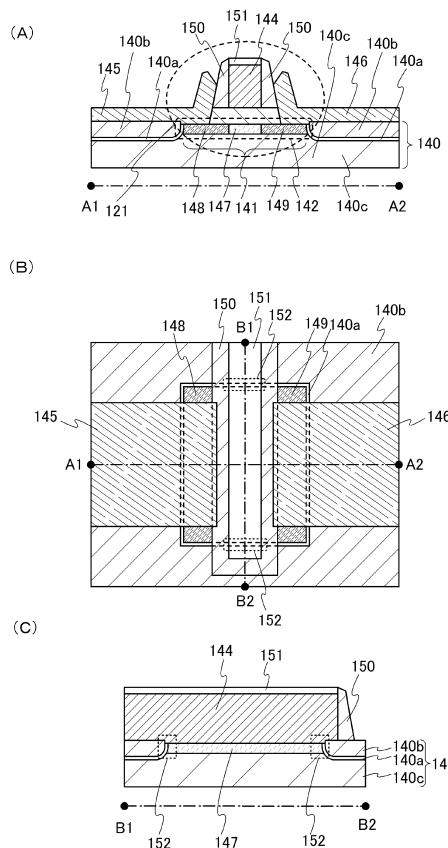

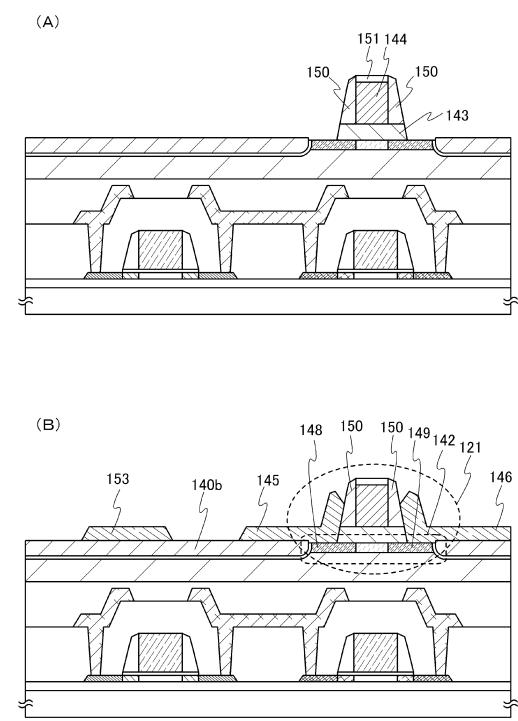

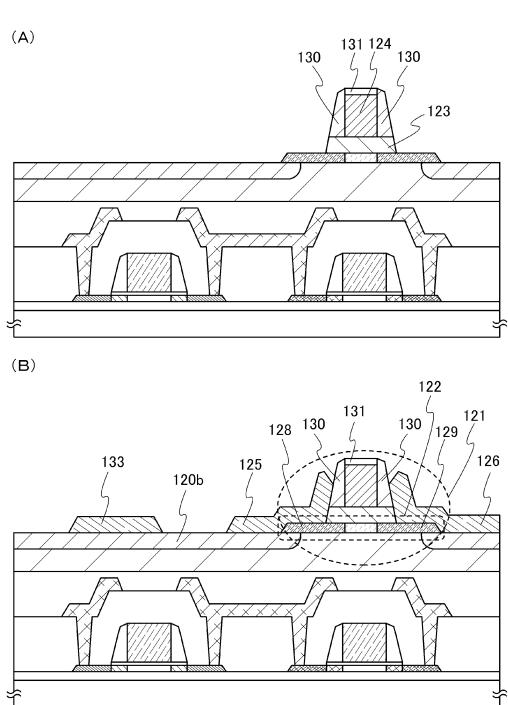

【0076】

次いで、図4を用いて、図3に示したトランジスタ121の具体的な断面構造について説明する。

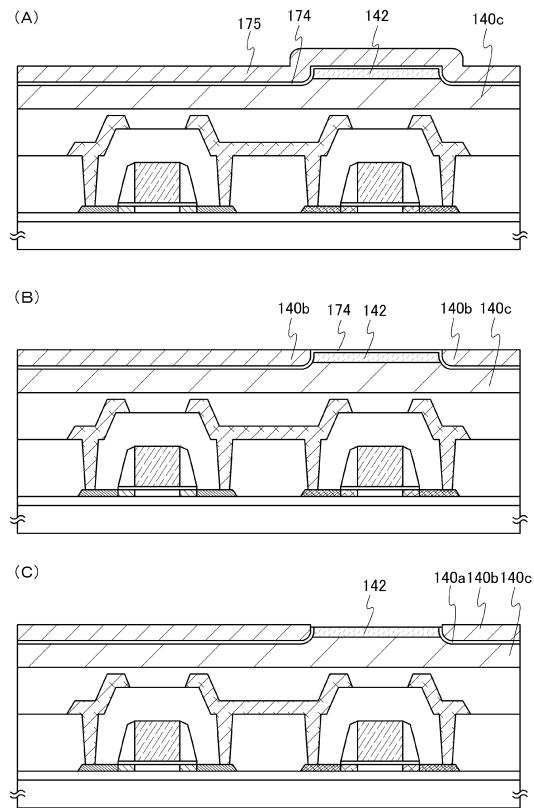

【0077】

図4(A)は、絶縁膜140及びトランジスタ121の断面図であり、図4(B)は、絶縁膜140及びトランジスタ121の上面図である。図4(B)の破線A1-A2における断面図が、図4(A)に相当する。また、図4(C)は、図4(B)の破線B1-B2における、絶縁膜140及びトランジスタ121の断面図である。

30

【0078】

トランジスタ121は、ゲート電極144の側部に、絶縁膜を有するサイドウォール150が設けられており、ゲート電極144の上部に、絶縁膜151が設けられている。そして、導電膜163及び導電膜164は、その一部がサイドウォール150に接している。導電膜163及び導電膜164は必ずしもサイドウォール150に接している必要は無いが、サイドウォール150に接するように導電膜163及び導電膜164を形成することで、導電膜163及び導電膜164の位置が多少ずれて形成されたとしても、導電膜163及び導電膜164と酸化物半導体膜142との接する面積が、変動するのを防ぐことができる。よって、導電膜163及び導電膜164の位置がずれることによる、トランジスタ121のオン電流の変動を防ぐことができる。

40

【0079】

なお、ゲート電極144の上部に位置する絶縁膜151は必ずしも設ける必要は無いが、絶縁膜151を設けることで、導電膜163及び導電膜164の位置がずれて形成され、ゲート電極144の上部にかかっても、導電膜163及び導電膜164とゲート電極144が導通するのを防ぐことができる。

【0080】

絶縁膜140では、下層に位置する第3の酸化絶縁膜140c上に、第1の酸化絶縁膜140aと、第2の酸化絶縁膜140bとが順に積層するように設けられている。そして、第1の酸化絶縁膜140a及び第2の酸化絶縁膜140bには開口部141が設けられており、上記開口部141には、トランジスタ121が有する酸化物半導体膜142が設け

50

られている。そして、第1の酸化絶縁膜140aは、酸化物半導体膜142の端部に接するように、酸化物半導体膜142の周囲に設けられている。また、第2の酸化絶縁膜140bは、第1の酸化絶縁膜140aを間に挟んで酸化物半導体膜142の周囲に設けられている。第3の酸化絶縁膜140cは、酸化物半導体膜142の下部に設けられている。

【0081】

上記構成により、加熱により第1の酸化絶縁膜140aから放出された酸素が、第2の酸化絶縁膜140bを通過するのを抑制することができるので、上記酸素が第1の領域147における酸化物半導体膜142の端部152に効率よく供給される。また、第3の酸化絶縁膜140cから放出された酸素は、酸化物半導体膜142の下部に供給される。なお、酸化物半導体をチャネル形成領域に有するトランジスタ121は、酸化物半導体膜142を所望の形状にエッチングするためのエッチング処理、酸化物半導体膜142の端部の減圧雰囲気における暴露等により、酸化物半導体膜142の端部において酸素の脱離による酸素欠損が形成されやすい。そして、酸素欠損はキャリアの移動経路となるため、酸化物半導体膜142の端部に酸素欠損が形成されると、寄生チャネルが生じ、それによりトランジスタ121のオフ電流が大きくなる。しかし、本発明の一態様では、上記構成により、第1の領域147における酸化物半導体膜142の端部152に酸素欠損が形成されるのを防ぎ、オフ電流を小さくさせることができる。

【0082】

また、図3に示すように、容量素子136は、絶縁膜140上の導電膜153と、導電膜153上の絶縁膜154と、絶縁膜154を間に挟んで導電膜153と重なる位置に設けられた導電膜155とを有する。絶縁膜154は、トランジスタ121上にも設けられている。また、導電膜153と導電膜164とは電気的に接続されていても良いし、或いは、導電膜153と導電膜164とが一の連続した導電膜で構成されていても良い。

【0083】

なお、図3では、容量素子136をトランジスタ121と共に絶縁膜140の上に設けている場合を例示しているが、容量素子136は、nチャネル型トランジスタ102n及びpチャネル型トランジスタ102pと共に、絶縁膜140の下に設けられていても良い。

【0084】

また、トランジスタ121は、ゲート電極144を酸化物半導体膜142の片側において少なくとも有していれば良いが、酸化物半導体膜142を間に挟んで存在する一対のゲート電極を有していても良い。

【0085】

本発明の一態様では、記憶素子を構成するnチャネル型トランジスタ102n及びpチャネル型トランジスタ102pが、結晶性を有するシリコン、またはゲルマニウムなどの半導体をチャネル形成領域に有することで、半導体装置の高速動作を確保することができる。また、本発明の一態様では、オフ電流が極めて小さいトランジスタ121でスイッチング素子を構成することで、スイッチング素子を介して容量素子136からリーキする電荷の量を小さく抑えることができる。すなわち、本発明の一態様では、記憶素子とスイッチング素子に要求される特性に合わせて、最適な構造のトランジスタを容易に作り分けることができる。また、本発明の一態様では、記憶素子を構成するnチャネル型トランジスタ102n及びpチャネル型トランジスタ102pと、スイッチング素子を構成するトランジスタ121とを積層することで、半導体装置の高集積化を実現することができる。

【0086】

よって、本発明の一態様では、上記構成により、高速動作を確保しつつ、消費電力を抑えることができる半導体装置を実現できる。或いは、本発明の一態様では、高速動作を確保しつつ、消費電力を抑えることができ、高集積化を実現できる半導体装置を実現できる。

【0087】

また、図3に、記憶素子が有するnチャネル型トランジスタ102n及びpチャネル型トランジスタ102pと、容量素子136と、スイッチング素子が有するトランジスタ121との構成を断面図で一例として示す。

10

20

30

40

50

## 【0088】

図36に示す半導体装置は、その表面に絶縁膜101が形成された基板100上に、nチャネル型トランジスタ102nと、pチャネル型トランジスタ102pとを有する。

## 【0089】

nチャネル型トランジスタ102nは、結晶性を有するシリコンを有する半導体膜103nと、半導体膜103n上のゲート絶縁膜104nと、ゲート絶縁膜104nを間に挟んで半導体膜103nと重なる位置に設けられたゲート電極105nと、半導体膜103nに接続された導電膜106及び導電膜107とを有する。そして、半導体膜103nは、チャネル形成領域として機能する第1の領域108と、ソースまたはドレインとして機能する第2の領域109及び第2の領域110とを有する。第2の領域109及び第2の領域110は、第1の領域108を間に挟んでいる。なお、図36では、半導体膜103nが、第1の領域108と第2の領域109及び第2の領域110との間に、LDD(Lightly Doped Drain)領域として機能する第3の領域111及び第3の領域112を有している場合を例示している。

## 【0090】

また、pチャネル型トランジスタ102pは、結晶性を有するシリコンを有する半導体膜103pと、半導体膜103p上のゲート絶縁膜104pと、ゲート絶縁膜104pを間に挟んで半導体膜103pと重なる位置に設けられたゲート電極105pと、半導体膜103pに接続された導電膜107及び導電膜113とを有する。そして、半導体膜103pは、チャネル形成領域として機能する第1の領域114と、ソースまたはドレインとして機能する第2の領域115及び第2の領域116とを有する。第2の領域115及び第2の領域116は、第1の領域114を間に挟んでいる。なお、図36では、半導体膜103pが、第1の領域114と第2の領域115及び第2の領域116との間に、LDD領域として機能する第3の領域117及び第3の領域118を有している場合を例示している。

## 【0091】

なお、図36では、nチャネル型トランジスタ102nと、pチャネル型トランジスタ102pとが導電膜107を共有している場合を例示しているが、上記2つのトランジスタが互いに独立した導電膜を有していても良い。

## 【0092】

また、図36では、nチャネル型トランジスタ102nと、pチャネル型トランジスタ102pとが、薄膜の半導体膜を用いている場合を例示しているが、nチャネル型トランジスタ102nと、pチャネル型トランジスタ102pとが、バルクの半導体基板にチャネル形成領域を有するトランジスタであっても良い。

## 【0093】

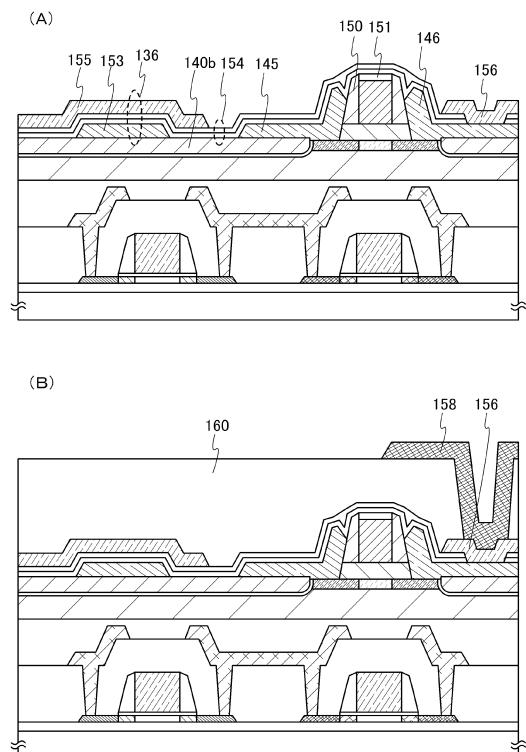

また、図36に示す半導体装置では、導電膜106、導電膜107、及び導電膜113上に絶縁膜119が設けられている。そして、絶縁膜119上には、第1の酸化絶縁膜120a及び第2の酸化絶縁膜120bを有する絶縁膜120が設けられている。

## 【0094】

第1の酸化絶縁膜120aは、加熱により一部の酸素が脱離する酸化絶縁膜を用いて形成する。加熱により一部の酸素が脱離する酸化絶縁膜としては、化学量論的組成比を満たす酸素よりも多くの酸素を含む絶縁膜を用いることが好ましい。第1の酸化絶縁膜120aとして、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム等を用いることができる。

## 【0095】

第2の酸化絶縁膜120bは、酸素の拡散を防ぐ酸化絶縁膜で形成する。第2の酸化絶縁膜120bの一例としては、酸化アルミニウム、酸化窒化アルミニウム等がある。なお、酸化アルミニウムは、化学量論的組成比を満たす酸素を含む酸化アルミニウム、または化学量論的組成比を満たす酸素よりも多くの酸素を含む酸化アルミニウム(A1O<sub>x</sub>、xは3/2以上)とすることが好ましい。また、酸化窒化アルミニウムは、化学量論的組成比

を満たす酸素を含む酸化アルミニウムの一部の酸素が窒素で置換されている。

【0096】

絶縁膜120上には、スイッチング素子が有するトランジスタ121が設けられている。具体的に、トランジスタ121は、絶縁膜120上に位置する酸化物半導体膜122と、酸化物半導体膜122上のゲート絶縁膜123と、ゲート絶縁膜123を間に挟んで酸化物半導体膜122と重なる位置に設けられたゲート電極124と、酸化物半導体膜122に接続された導電膜125及び導電膜126とを有する。酸化物半導体膜122は、ゲート電極124と重なり、少なくとも一部がチャネル形成領域として機能する第1の領域127と、ソースまたはドレインとして機能し、第1の領域127を挟む第2の領域128及び第2の領域129とを有している。

10

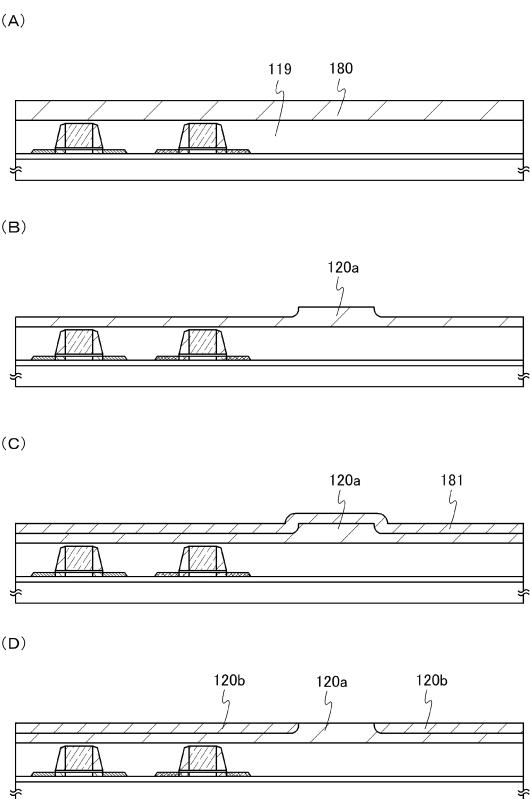

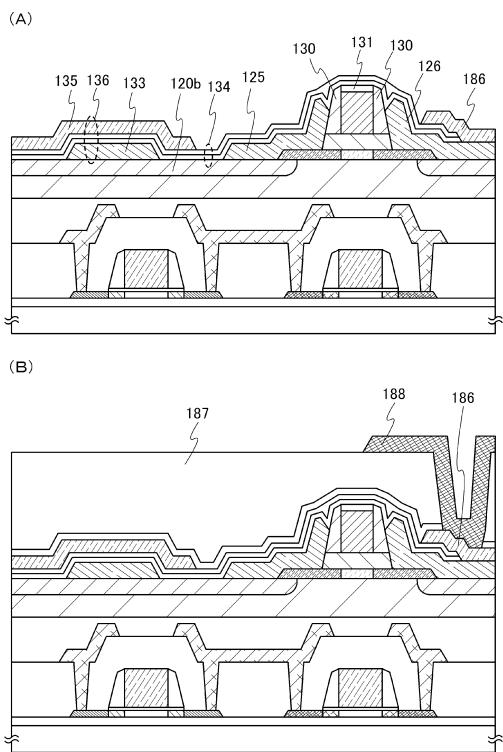

【0097】

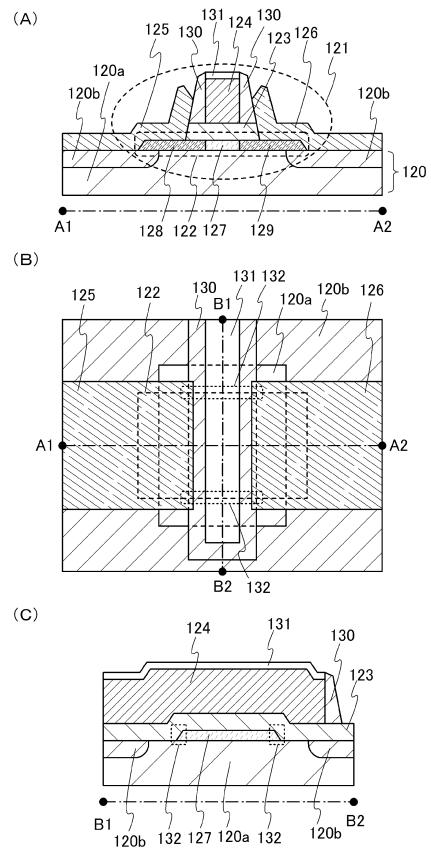

次いで、図37を用いて、酸化物半導体膜122が有する第1の領域127、第2の領域128及び第2の領域129と、絶縁膜120が有する第1の酸化絶縁膜120a及び第2の酸化絶縁膜120bとの位置関係について説明する。

【0098】

図37(A)は、絶縁膜120及びトランジスタ121の断面図であり、図37(B)は、絶縁膜120及びトランジスタ121の上面図である。図37(B)の破線A1-A2における断面図が、図37(A)に相当する。また、図37(C)は、図37(B)の破線B1-B2における、絶縁膜120及びトランジスタ121の断面図である。

20

【0099】

トランジスタ121は、ゲート電極124の側部に、絶縁膜を有するサイドウォール130が設けられており、ゲート電極124の上部に、絶縁膜131が設けられている。そして、導電膜125及び導電膜126は、その一部がサイドウォール130に接している。導電膜125及び導電膜126は必ずしもサイドウォール130に接している必要は無いが、サイドウォール130に接するように導電膜125及び導電膜126を形成することで、導電膜125及び導電膜126の位置が多少ずれて形成されたとしても、導電膜125及び導電膜126と酸化物半導体膜122との接する面積が、変動するのを防ぐことができる。よって、導電膜125及び導電膜126の位置がずれることによる、トランジスタ121のオン電流の変動を防ぐことができる。

【0100】

30

なお、ゲート電極124の上部に位置する絶縁膜131は必ずしも設ける必要は無いが、絶縁膜131を設けることで、導電膜125及び導電膜126の位置がずれて形成され、ゲート電極124の上部にかかるても、導電膜125及び導電膜126とゲート電極124が導通するのを防ぐことができる。

【0101】

そして、絶縁膜120は、第1の酸化絶縁膜120aの周囲に第2の酸化絶縁膜120bが設けられている。そして、酸化物半導体膜122は、第1の領域127において上記第1の酸化絶縁膜120aに接し、第2の領域128及び第2の領域129において第1の酸化絶縁膜120a及び第2の酸化絶縁膜120bに接する。

【0102】

40

上記構成により、加熱により第1の酸化絶縁膜120aから放出された酸素が、第2の酸化絶縁膜120bを通過するのを抑制することができるので、上記酸素が第1の領域127における酸化物半導体膜122の端部132に効率よく供給される。なお、酸化物半導体をチャネル形成領域に有するトランジスタ121は、酸化物半導体膜122を所望の形状にエッチングするためのエッチング処理、酸化物半導体膜122の端部の減圧雰囲気における暴露等により、酸化物半導体膜122の端部において酸素の脱離による酸素欠損が形成されやすい。そして、酸素欠損はキャリアの移動経路となるため、酸化物半導体膜122の端部に酸素欠損が形成されると、寄生チャネルが生じ、それによりトランジスタ121のオフ電流が大きくなる。しかし、本発明の一態様では、上記構成により、第1の領域127における酸化物半導体膜122の端部132に酸素欠損が形成されるのを防ぎ、

50

オフ電流を小さくすることができる。

【0103】

また、図36に示すように、容量素子136は、絶縁膜120上の導電膜133と、導電膜133上の絶縁膜134と、絶縁膜134を間に挟んで導電膜133と重なる位置に設けられた導電膜135とを有する。絶縁膜134は、トランジスタ121上にも設けられている。また、導電膜133と導電膜125とは電気的に接続されても良いし、或いは、導電膜133と導電膜125とが一の連続した導電膜で構成されていても良い。

【0104】

なお、図36では、容量素子136をトランジスタ121と共に絶縁膜120の上に設けている場合を例示しているが、容量素子136は、nチャネル型トランジスタ102n及びpチャネル型トランジスタ102pと共に、絶縁膜120の下に設けられていても良い。

10

【0105】

また、図36では、絶縁膜120と、nチャネル型トランジスタ102n及びpチャネル型トランジスタ102pとの間に、絶縁膜119を設けている場合を例示しているが、絶縁膜119は必ずしも設ける必要は無い。絶縁膜119を設けない場合、導電膜106、導電膜107、及び導電膜113に接するように、絶縁膜120が設けられる。

【0106】

また、トランジスタ121は、ゲート電極124を酸化物半導体膜122の片側において少なくとも有していれば良いが、酸化物半導体膜122を間に挟んで存在する一対のゲート電極を有していても良い。

20

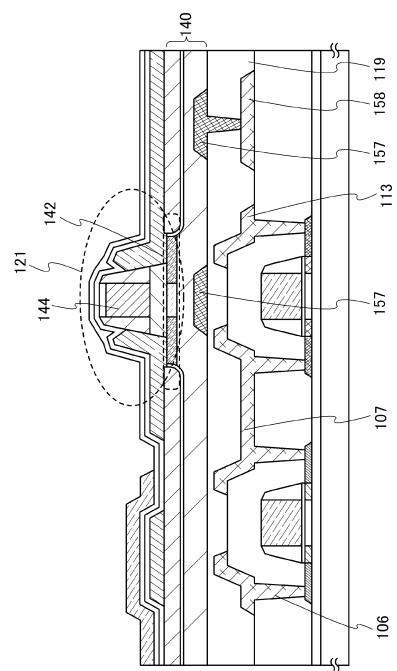

【0107】

図38に、図36に示した半導体装置において、トランジスタ121が、ゲート電極124に加えて、絶縁膜119と絶縁膜120の間にバックゲート電極137を有する場合を例示する。バックゲート電極137は、絶縁膜120を間に挟んで、酸化物半導体膜122と重なる位置に設けられている。

【0108】

バックゲート電極137は、電気的に絶縁しているフローティングの状態であっても良いし、電位が他から与えられている状態であっても良い。後者の場合、バックゲート電極137には、ゲート電極124と同じ高さの電位が与えられても良いし、バックゲート電極137にのみ接地電位などの固定の電位が与えられても良い。バックゲート電極137に与える電位の高さを制御することで、トランジスタ121の閾値電圧を制御することができる。図38では、絶縁膜119に形成された開口部を介して、バックゲート電極137が、導電膜106、導電膜107及び導電膜113と同じ層に形成された導電膜138に接続されている場合を例示している。

30

【0109】

次いで、図36に示した構成とは異なる、本発明の一態様に係る半導体装置の構成について説明する。図39に、記憶素子が有するnチャネル型トランジスタ102n及びpチャネル型トランジスタ102pと、容量素子136と、スイッチング素子が有するトランジスタ121との構成を断面図で一例として示す。

40

【0110】

図39に示す半導体装置は、図36に示す半導体装置と同様に、その表面に絶縁膜101が形成された基板100上に、nチャネル型トランジスタ102nと、pチャネル型トランジスタ102pとを有する。nチャネル型トランジスタ102nと、pチャネル型トランジスタ102pの具体的な構成については、図36と同様である。

【0111】

そして、図39に示す半導体装置は、図36と同様に、導電膜106、導電膜107、及び導電膜113上に絶縁膜119が設けられている。そして、絶縁膜119上には、第1の酸化絶縁膜140a、第2の酸化絶縁膜140b、及び第3の酸化絶縁膜140cを有する絶縁膜140が設けられている。絶縁膜140上には、スイッチング素子が有するト

50

ランジスタ 121 が設けられている。

【0112】

第1の酸化絶縁膜 140a 及び第3の酸化絶縁膜 140c は、加熱により一部の酸素が脱離する酸化絶縁膜を用いて形成する。加熱により一部の酸素が脱離する酸化絶縁膜としては、化学量論的組成比を満たす酸素よりも多くの酸素を含む絶縁膜を用いることが好ましい。第1の酸化絶縁膜 140a として、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム等を用いることができる。

【0113】

第2の酸化絶縁膜 140b は、酸素の拡散を防ぐ酸化絶縁膜で形成する。第2の酸化絶縁膜 140b の一例としては、酸化アルミニウム、酸化窒化アルミニウム等がある。なお、酸化アルミニウムは、化学量論的組成比を満たす酸素を含む酸化アルミニウム、または化学量論的組成比を満たす酸素よりも多くの酸素を含む酸化アルミニウム (Al<sub>10x</sub>、x は 3/2 以上) とすることが好ましい。また、酸化窒化アルミニウムは、化学量論的組成比を満たす酸素を含む酸化アルミニウムの一部の酸素が窒素で置換されている。

10

【0114】

また、具体的に、トランジスタ 121 は、酸化物半導体膜 142 と、酸化物半導体膜 142 上のゲート絶縁膜 143 と、ゲート絶縁膜 143 を間に挟んで酸化物半導体膜 142 と重なる位置に設けられたゲート電極 144 と、酸化物半導体膜 142 に接続された導電膜 145 及び導電膜 146 とを有する。酸化物半導体膜 142 は、ゲート電極 144 と重なり、少なくとも一部がチャネル形成領域として機能する第1の領域 147 と、ソースまたはドレインとして機能し、第1の領域 147 を挟む第2の領域 148 及び第2の領域 149 とを有している。

20

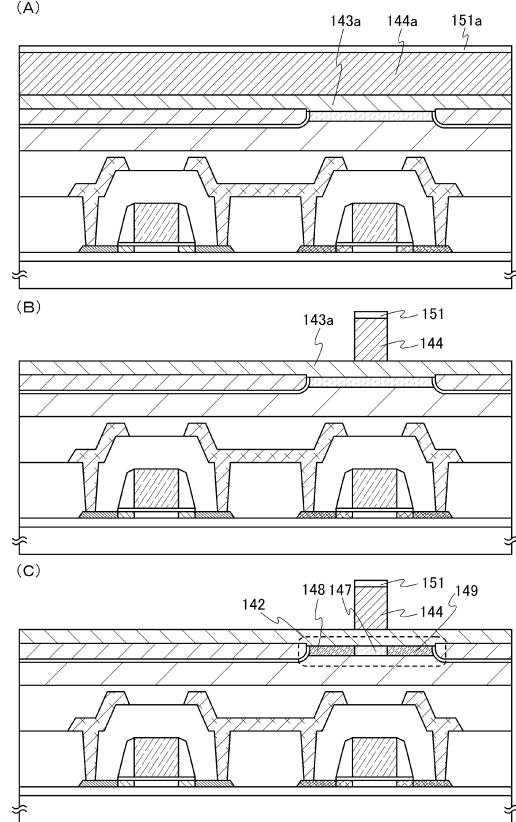

【0115】

次いで、図 40 を用いて、図 39 に示したトランジスタ 121 の具体的な断面構造について説明する。

【0116】

図 40 (A) は、絶縁膜 140 及びトランジスタ 121 の断面図であり、図 40 (B) は、絶縁膜 140 及びトランジスタ 121 の上面図である。図 40 (B) の破線 A1 - A2 における断面図が、図 40 (A) に相当する。また、図 40 (C) は、図 40 (B) の破線 B1 - B2 における、絶縁膜 140 及びトランジスタ 121 の断面図である。

30

【0117】

トランジスタ 121 は、ゲート電極 144 の側部に、絶縁膜を有するサイドウォール 150 が設けられており、ゲート電極 144 の上部に、絶縁膜 151 が設けられている。そして、導電膜 145 及び導電膜 146 は、その一部がサイドウォール 150 に接している。導電膜 145 及び導電膜 146 は必ずしもサイドウォール 150 に接している必要は無いが、サイドウォール 150 に接するように導電膜 145 及び導電膜 146 を形成することで、導電膜 145 及び導電膜 146 の位置が多少ずれて形成されたとしても、導電膜 145 及び導電膜 146 と酸化物半導体膜 142 との接する面積が、変動するのを防ぐことができる。よって、導電膜 145 及び導電膜 146 の位置がずれることによる、トランジスタ 121 のオン電流の変動を防ぐことができる。

40

【0118】

なお、ゲート電極 144 の上部に位置する絶縁膜 151 は必ずしも設ける必要は無いが、絶縁膜 151 を設けることで、導電膜 145 及び導電膜 146 の位置がずれて形成され、ゲート電極 144 の上部にかかっても、導電膜 145 及び導電膜 146 とゲート電極 144 が導通するのを防ぐことができる。

【0119】

絶縁膜 140 では、下層に位置する第3の酸化絶縁膜 140c 上に、第1の酸化絶縁膜 140a と、第2の酸化絶縁膜 140b とが順に積層するように設けられている。そして、第1の酸化絶縁膜 140a 及び第2の酸化絶縁膜 140b には開口部 141 が設けられており、上記開口部 141 には、トランジスタ 121 が有する酸化物半導体膜 142 が設け

50

られている。そして、第1の酸化絶縁膜140aは、酸化物半導体膜142の端部に接するように、酸化物半導体膜142の周囲に設けられている。また、第2の酸化絶縁膜140bは、第1の酸化絶縁膜140aを間に挟んで酸化物半導体膜142の周囲に設けられている。第3の酸化絶縁膜140cは、酸化物半導体膜142の下部に設けられている。

【0120】

上記構成により、加熱により第1の酸化絶縁膜140aから放出された酸素が、第2の酸化絶縁膜140bを通過するのを抑制することができるので、上記酸素が第1の領域147における酸化物半導体膜142の端部152に効率よく供給される。また、第3の酸化絶縁膜140cから放出された酸素は、酸化物半導体膜142の下部に供給される。なお、酸化物半導体をチャネル形成領域に有するトランジスタ121は、酸化物半導体膜142を所望の形状にエッチングするためのエッチング処理、酸化物半導体膜142の端部の減圧雰囲気における暴露等により、酸化物半導体膜142の端部において酸素の脱離による酸素欠損が形成されやすい。そして、酸素欠損はキャリアの移動経路となるため、酸化物半導体膜142の端部に酸素欠損が形成されると、寄生チャネルが生じ、それによりトランジスタ121のオフ電流が大きくなる。しかし、本発明の一態様では、上記構成により、第1の領域147における酸化物半導体膜142の端部152に酸素欠損が形成されるのを防ぎ、オフ電流を小さくすることができる。

【0121】

また、図39に示すように、容量素子136は、絶縁膜140上の導電膜153と、導電膜153上の絶縁膜154と、絶縁膜154を間に挟んで導電膜153と重なる位置に設けられた導電膜155とを有する。絶縁膜154は、トランジスタ121上にも設けられている。また、導電膜153と導電膜145とは電気的に接続されていても良いし、或いは、導電膜153と導電膜145とが一の連続した導電膜で構成されていても良い。

【0122】

なお、図39では、容量素子136をトランジスタ121と共に絶縁膜140の上に設けている場合を例示しているが、容量素子136は、nチャネル型トランジスタ102n及びpチャネル型トランジスタ102pと共に、絶縁膜140の下に設けられていても良い。

【0123】

また、図39では、絶縁膜140と、nチャネル型トランジスタ102n及びpチャネル型トランジスタ102pとの間に、絶縁膜119を設けている場合を例示しているが、絶縁膜119は必ずしも設ける必要は無い。絶縁膜119を設けない場合、導電膜106、導電膜107、及び導電膜113に接するように、絶縁膜140が設けられる。

【0124】

また、トランジスタ121は、ゲート電極144を酸化物半導体膜142の片側において少なくとも有していれば良いが、酸化物半導体膜142を間に挟んで存在する一対のゲート電極を有していても良い。

【0125】

図41に、図39に示した半導体装置において、トランジスタ121が、ゲート電極144に加えて、絶縁膜119と絶縁膜140の間にバックゲート電極157を有する場合を例示する。バックゲート電極157は、絶縁膜140を間に挟んで、酸化物半導体膜142と重なる位置に設けられている。

【0126】

バックゲート電極157は、電気的に絶縁しているフローティングの状態であっても良いし、電位が他から与えられている状態であっても良い。後者の場合、バックゲート電極157には、ゲート電極144と同じ高さの電位が与えられていても良いし、バックゲート電極157にのみ接地電位などの固定の電位が与えられていても良い。バックゲート電極157に与える電位の高さを制御することで、トランジスタ121の閾値電圧を制御することができる。図41では、絶縁膜119に形成された開口部を介して、バックゲート電極157が、導電膜106、導電膜107及び導電膜113と同じ層に形成された導電膜

10

20

30

40

50

158に接続されている場合を例示している。

#### 【0127】

本発明の一態様では、記憶素子を構成するnチャネル型トランジスタ102n及びpチャネル型トランジスタ102pが、結晶性を有するシリコン、またはゲルマニウムなどの半導体をチャネル形成領域に有することで、半導体装置の高速動作を確保することができる。また、本発明の一態様では、オフ電流が極めて小さいトランジスタ121でスイッチング素子を構成することで、スイッチング素子を介して容量素子136からリーキする電荷の量を小さく抑えることができる。すなわち、本発明の一態様では、記憶素子とスイッチング素子に要求される特性に合わせて、最適な構造のトランジスタを容易に作り分けることができる。また、本発明の一態様では、記憶素子を構成するnチャネル型トランジスタ102n及びpチャネル型トランジスタ102pと、スイッチング素子を構成するトランジスタ121とを積層することで、半導体装置の高集積化を実現することができる。

10

#### 【0128】

よって、本発明の一態様では、上記構成により、高速動作を確保しつつ、消費電力を抑えることができる半導体装置を実現できる。或いは、本発明の一態様では、高速動作を確保しつつ、消費電力を抑えることができ、高集積化を実現できる半導体装置を実現できる。

#### 【0129】

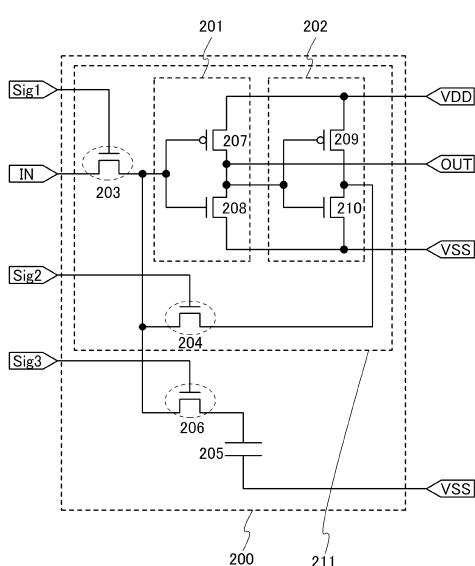

次いで、本発明の一態様に係る半導体装置の、具体的な回路構成の一例について説明する。本発明の一態様に係る半導体装置は、1ビットのデータを記憶することができる記憶回路を、単数または複数、記憶装置に有する。図5に、上記記憶装置が有する記憶回路の一例を示す。図5に示す記憶回路200は、記憶素子211と、容量素子205と、スイッチング素子206とを有する。記憶素子211は、入力された信号の位相を反転させて出力する第1の位相反転素子201及び第2の位相反転素子202と、トランジスタ203と、トランジスタ204とを有する。

20

#### 【0130】

記憶回路200に入力されたデータを含む信号INは、トランジスタ203を介して第1の位相反転素子201の入力端子に与えられる。第1の位相反転素子201の出力端子は、第2の位相反転素子202の入力端子に接続されている。第2の位相反転素子202の出力端子は、トランジスタ204を介して、第1の位相反転素子201の入力端子に接続されている。第1の位相反転素子201の出力端子または第2の位相反転素子202の入力端子の電位が、信号OUTとして後段の記憶回路、或いは他の回路に出力される。

30

#### 【0131】

なお、図5では、第1の位相反転素子201及び第2の位相反転素子202としてインバータを用いる例を示しているが、第1の位相反転素子201または第2の位相反転素子202として、インバータの他に、クロックドインバータを用いることもできる。

#### 【0132】

容量素子205は、記憶回路200に入力された信号INのデータを必要に応じて記憶できるように、トランジスタ203及びスイッチング素子206を介して、記憶回路200の入力端子、すなわち信号INの電位が与えられるノードに接続されている。具体的に、容量素子205は、一対の電極間に誘電体を有するコンデンサであり、その一方の電極は、スイッチング素子206を介して第1の位相反転素子201の入力端子に接続され、他方の電極は、ローレベルの電源電位VSS、グラウンドなどの固定電位が与えられているノードに接続されている。

40

#### 【0133】

また、スイッチング素子206は、酸化物半導体をチャネル形成領域に有するトランジスタを用いる。酸化物半導体をチャネル形成領域に有するトランジスタは、通常のシリコンやゲルマニウムなどの半導体で形成されたトランジスタに比べて、オフ電流が極めて小さい。さらに、本発明の一態様では、図2または図4に示したような、オフ電流をより小さくさせることができる構成のトランジスタ121をスイッチング素子206として用いる。容量素子205におけるデータの保持期間の長さは、容量素子205に蓄積されている

50

電荷が、スイッチング素子 206 を介してリークする量に依存する。よって、上述したような、オフ電流の著しく小さいスイッチング素子 206 により、容量素子 205 に蓄積された電荷を保持することで、容量素子 205 からの電荷のリークを防ぐことができ、データの保持期間を長く確保することができる。

【0134】

なお、図 5 では、スイッチング素子 206 を構成するトランジスタがシングルゲート構造である場合を例示しているが、上記トランジスタは、電気的に接続された複数のゲート電極を有することで、チャネル形成領域を複数有する、マルチゲート構造であっても良い。

【0135】

また、図 5 では、スイッチング素子 206 がトランジスタを一つだけ有する構成を示しているが、本発明はこの構成に限定されない。本発明の一態様では、スイッチング素子 206 が、トランジスタを複数有していても良い。スイッチング素子 206 が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていても良いし、直列に接続されていても良いし、直列と並列が組み合わされて接続されていても良い。

【0136】

なお、本明細書において、トランジスタが直列に接続されている状態とは、第 1 のトランジスタのソースとドレインのいずれか一方のみが、第 2 のトランジスタのソースとドレインのいずれか一方のみに接続されている状態を意味する。また、トランジスタが並列に接続されている状態とは、第 1 のトランジスタのソースとドレインのいずれか一方が、第 2 のトランジスタのソースとドレインのいずれか一方に接続され、第 1 のトランジスタのソースとドレインの他方が第 2 のトランジスタのソースとドレインの他方に接続されている状態を意味する。

【0137】

なお、トランジスタが有するソースとドレインは、トランジスタの極性及びソースとドレインに与えられる電位の高低によって、その呼び方が入れ替わる。一般的に、n チャネル型トランジスタでは、ソースとドレインのうち、低い電位が与えられる方がソースと呼ばれ、高い電位が与えられる方がドレインと呼ばれる。また、p チャネル型トランジスタでは、ソースとドレインのうち、低い電位が与えられる方がドレインと呼ばれ、高い電位が与えられる方がソースと呼ばれる。本明細書では、便宜上、ソースとドレインとが固定されているものと仮定して、トランジスタの接続関係を説明する場合があるが、実際には上記電位の関係に従ってソースとドレインの呼び方が入れ替わる。

【0138】

また、記憶回路 200 は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の回路素子を、さらに有していても良い。

【0139】

第 1 の位相反転素子 201 は、ゲート電極が互いに接続された p チャネル型トランジスタ 207 と、n チャネル型トランジスタ 208 とが、ハイレベルの電源電位 VDD が与えられる第 1 のノードと、ローレベルの電源電位 VSS が与えられる第 2 のノードの間ににおいて、直列に接続された構成を有する。具体的に、p チャネル型トランジスタ 207 のソースが、電源電位 VDD の与えられる第 1 のノードに接続され、n チャネル型トランジスタ 208 のソースが、電源電位 VSS の与えられる第 2 のノードに接続される。また、p チャネル型トランジスタ 207 のドレインと、n チャネル型トランジスタ 208 のドレインとが接続されており、上記 2 つのドレインの電位は、第 1 の位相反転素子 201 の出力端子の電位とみなすことができる。また、p チャネル型トランジスタ 207 のゲート電極、及び n チャネル型トランジスタ 208 のゲート電極の電位は、第 1 の位相反転素子 201 の入力端子の電位とみなすことができる。

【0140】

第 2 の位相反転素子 202 は、ゲート電極が互いに接続された p チャネル型トランジスタ 209 と、n チャネル型トランジスタ 210 とが、ハイレベルの電源電位 VDD が与えら

10

20

30

40

50

れる第1のノードと、ローレベルの電源電位VSSが与えられる第2のノードの間において、直列に接続された構成を有する。具体的に、pチャネル型トランジスタ209のソースが、電源電位VDDの与えられる第1のノードに接続され、nチャネル型トランジスタ210のソースが、電源電位VSSの与えられる第2のノードに接続される。また、pチャネル型トランジスタ209のドレインと、nチャネル型トランジスタ210のドレインとが接続されており、上記2つのドレインの電位は、第2の位相反転素子202の出力端子の電位とみなすことができる。また、pチャネル型トランジスタ209のゲート電極、及びnチャネル型トランジスタ210のゲート電極の電位は、第2の位相反転素子202の入力端子の電位とみなすことができる。

【0141】

10

また、トランジスタ203は、そのゲート電極に与えられる信号Sig1によりスイッチングが制御される。また、トランジスタ204は、そのゲート電極に与えられる信号Sig2によりスイッチングが制御される。スイッチング素子206に用いられるトランジスタは、そのゲート電極に与えられる信号Sig3によりスイッチングが制御される。

【0142】

また、本発明の一態様では、第1の位相反転素子201、第2の位相反転素子202には、高速動作が要求される。よって、図1、図3、図36、または図39に示したような、結晶性を有するシリコンを半導体膜に有するnチャネル型トランジスタ102n、またはpチャネル型トランジスタ102pを、第1の位相反転素子201が有するnチャネル型トランジスタ208、またはpチャネル型トランジスタ207として、或いは、第2の位相反転素子202が有するnチャネル型トランジスタ210、またはpチャネル型トランジスタ209として用いる。

20

【0143】

なお、トランジスタ203、またはトランジスタ204として、図1、図3、図36、または図39に示したような、結晶性を有するシリコンを半導体膜に有するnチャネル型トランジスタ102n、またはpチャネル型トランジスタ102pを用いても良い。

【0144】

次いで、図5に示す記憶回路200の動作の一例について説明する。

【0145】

30

まず、データの書き込み時において、トランジスタ203はオン、トランジスタ204はオフ、スイッチング素子206はオフとする。そして、第1のノードに電源電位VDDを与え、第2のノードに電源電位VSSを与えることで、第1のノードと第2のノード間に電源電圧が印加される。記憶回路200に与えられる信号INの電位は、トランジスタ203を介して第1の位相反転素子201の入力端子に与えられるので、第1の位相反転素子201の出力端子は、信号INの位相が反転した電位になる。そして、トランジスタ204をオンにし、第1の位相反転素子201の入力端子と第2の位相反転素子202の出力端子とを接続することで、第1の位相反転素子201及び第2の位相反転素子202にデータが書き込まれる。

【0146】

40

次いで、入力されたデータの保持を、第1の位相反転素子201及び第2の位相反転素子202によって行う場合、トランジスタ204をオン、スイッチング素子206をオフの状態にしたままで、トランジスタ203をオフにする。トランジスタ203をオフすることで、入力されたデータは、第1の位相反転素子201及び第2の位相反転素子202によって保持される。このとき、第1のノードに電源電位VDDを与え、第2のノードに電源電位VSSを与えることで、第1のノードと第2のノード間に電源電圧が印加されている状態を維持する。

【0147】

そして、第1の位相反転素子201の出力端子の電位には、第1の位相反転素子201及び第2の位相反転素子202によって保持されているデータが反映されている。よって、上記電位を読み取ることで、データを記憶回路200から読み出すことができる。

50

## 【0148】

なお、データの保持時における消費電力を削減するために、入力されたデータの保持を、容量素子205において行う場合、まず、トランジスタ203はオフ、トランジスタ204はオン、スイッチング素子206はオンとする。そして、スイッチング素子206を介して、第1の位相反転素子201及び第2の位相反転素子202によって保持されているデータの値に見合った量の電荷が容量素子205に蓄積されることで、容量素子205へのデータの書き込みが行われる。容量素子205にデータが記憶された後、スイッチング素子206をオフにすることで、容量素子205に記憶されたデータは保持される。スイッチング素子206をオフにした後は、第1のノードと第2のノードとに、例えば電源電位VSSを与えて等電位とすることで、第1のノードと第2のノード間の電源電圧の印加を停止する。なお、容量素子205にデータが記憶された後は、トランジスタ204をオフにしても良い。10

## 【0149】

このように、入力されたデータの保持を容量素子205において行う場合は、第1のノードと第2のノード間に電源電圧を印加する必要がないので、第1の位相反転素子201が有するpチャネル型トランジスタ207及びnチャネル型トランジスタ208、或いは、第2の位相反転素子202が有するpチャネル型トランジスタ209及びnチャネル型トランジスタ210を介して、第1のノードと第2のノードの間に流れるオフ電流を限りなく0にすることができます。したがって、データの保持時における記憶素子のオフ電流に起因する消費電力を大幅に削減することができ、記憶装置、延いては記憶装置を用いた半導体装置全体の、消費電力を低く抑えることが可能となる。20

## 【0150】

また、上述したように、スイッチング素子206に用いられているトランジスタはオフ電流が著しく小さい。よって、上記トランジスタを用いたスイッチング素子206がオフである時、容量素子205に蓄積された電荷はリークしにくいため、データは保持される。20

## 【0151】

また、容量素子205に記憶されているデータを読み出す場合は、トランジスタ203をオフとする。そして、再び、第1のノードに電源電位VDDを与え、第2のノードに電源電位VSSを与えることで、第1のノードと第2のノード間に電源電圧を印加する。そして、スイッチング素子206をオンにすることで、データが反映された電位を有する信号OUTを、記憶回路200から読み出すことができる。30

## 【0152】

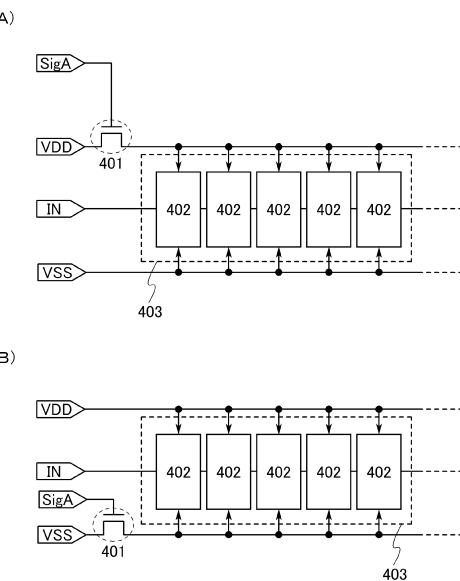

なお、酸化物半導体をチャネル形成領域に有するトランジスタを用いて、第1のノードと第2のノード間の電源電圧の印加を制御する構成としても良い。図6(A)に、上記構成を有する記憶装置を一例として示す。

## 【0153】

図6(A)に示す記憶装置は、スイッチング素子401と、記憶回路402を複数有する記憶回路群403とを有している。具体的に、各記憶回路402には、図5に示した記憶回路200を用いることができる。記憶回路群403が有する各記憶回路402には、スイッチング素子401を介して、ハイレベルの電源電位VDDが供給されている。さらに、記憶回路群403が有する各記憶回路402には、信号INの電位と、ローレベルの電源電位VSSの電位が与えられている。40

## 【0154】

図6(A)では、スイッチング素子401として、酸化物半導体をチャネル形成領域に有するトランジスタを用いており、当該トランジスタは、そのゲート電極に与えられる信号SigAによりスイッチングが制御される。スイッチング素子401に用いるトランジスタは、酸化物半導体をチャネル形成領域に有するため、そのオフ電流は、上述したとおり著しく小さい。

## 【0155】

なお、図6(A)では、スイッチング素子401がトランジスタを一つだけ有する構成を50

示しているが、本発明はこの構成に限定されない。本発明の一態様では、スイッチング素子 401 が、トランジスタを複数有していても良い。スイッチング素子 401 が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていても良いし、直列に接続されていても良いし、直列と並列が組み合わされて接続されていても良い。

【0156】

また、図 6 (A) では、スイッチング素子 401 により、記憶回路群 403 が有する各記憶回路 402 への、ハイレベルの電源電位 VDD の供給が制御されているが、スイッチング素子 401 により、ローレベルの電源電位 VSS の供給が制御されていても良い。図 6 (B) に、記憶回路群 403 が有する各記憶回路 402 に、スイッチング素子 401 を介して、ローレベルの電源電位 VSS が供給されている、記憶装置の一例を示す。スイッチング素子 401 により、記憶回路群 403 が有する各記憶回路 402 への、ローレベルの電源電位 VSS の供給を制御することができる。

10

【0157】

ところで、不揮発性のランダムアクセスメモリとして磁気トンネル接合素子 (MTJ 素子) が知られている。MTJ 素子は、絶縁膜を介して上下に配置している膜中のスピニの向きが平行であれば低抵抗状態、反平行であれば高抵抗状態となることで情報を記憶する素子である。したがって、本実施の形態で示す酸化物半導体を用いた記憶装置とは原理が全く異なっている。表 1 は MTJ 素子と、本実施の形態に係る記憶装置との対比を示す。

【0158】

20

【表 1】

|                          | スピントロニクス(MTJ 素子)                                                        | OS/Si                                        |

|--------------------------|-------------------------------------------------------------------------|----------------------------------------------|

| 1) 耐熱性                   | キュリー温度                                                                  | プロセス温度 500°C<br>(信頼性 150°C)                  |

| 2) 駆動方式                  | 電流駆動                                                                    | 電圧駆動                                         |

| 3) 書き込み原理                | 磁性体のスピニの向きを変える                                                          | FET のオン/オフ                                   |

| 4) Si LSI                | バイポーラ LSI 向き<br>(バイポーラは高集積化には不向きなため、高集積化回路では MOS の方が好ましい。ただし、W が大きくなる。) | MOSLSI 向き                                    |

| 5) オーバーヘッド               | 大きい<br>(ジュール熱が大きいため)                                                    | 2~3 枠以上小さい<br>(寄生容量の充放電)                     |

| 6) 不揮発性                  | スピニを利用                                                                  | オフ電流が小さいことを利用                                |

| 7) 読み出し回数                | 無制限                                                                     | 無制限                                          |

| 8) 3D 化                  | 難(できても二層まで)                                                             | 容易(何層でも可)                                    |

| 9) 集積化度(F <sup>2</sup> ) | 4F <sup>2</sup> ~15F <sup>2</sup>                                       | 3D 化の積層数で決まる<br>(上層 OSFET 工程のプロセス耐熱性の確保が必要)  |

| 10) 材料                   | 磁性を有する希土類                                                               | OS 材料                                        |

| 11) ビットコスト               | 高い                                                                      | 低い<br>(OS を構成する材料によっては (In など)、多少コスト高の可能性有り) |

| 12) 磁界耐性                 | 弱い                                                                      | 強い                                           |

30

【0159】

MTJ 素子は磁性材料を使用するためキュリー温度以上にすると磁性が失われてしまうという欠点がある。また、MTJ 素子は電流駆動であるため、シリコンのバイポーラデバイスと相性が良いが、バイポーラデバイスは集積化に不向きである。そして、MTJ 素子は書き込み電流が微少とはいえメモリの大容量化によって消費電力が増大してしまうといっ

50

た問題がある。

【0160】

原理的にMTJ素子は磁界耐性に弱く強磁界にさらされるとスピンの向きが狂いやすい。また、MTJ素子に用いる磁性体のナノスケール化によって生じる磁化揺らぎを制御する必要がある。

【0161】

さらに、MTJ素子は希土類元素を使用するため、金属汚染を嫌うシリコン半導体のプロセスに組み入れるには相当の注意を要する。MTJ素子はピット当たりの材料コストから見ても高価であると考えられる。

【0162】

一方、本実施の形態で示す酸化物半導体を用いたトランジスタは、チャネルを形成する半導体材料が金属酸化物であること以外は、素子構造や動作原理がシリコンMOSFETと同様である。また、酸化物半導体を用いたトランジスタは磁界の影響を受けず、ソフトエラーも生じ得ないといった特質を有する。このことからシリコン集積回路と非常に整合性が良いといえる。

【0163】

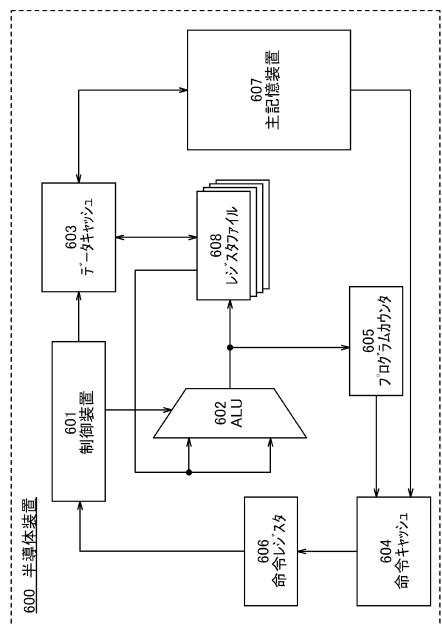

次いで、本発明の半導体装置の具体的な一形態について説明する。図7に、半導体装置の構成をブロックで一例として示す。

【0164】

半導体装置600は、制御装置601と、演算装置に相当するALU(Arithmetic logic unit)602と、データキャッシュ603と、命令キャッシュ604と、プログラムカウンタ605と、命令レジスタ606と、主記憶装置607と、レジスタファイル608とを有する。

【0165】

制御装置601は、入力された命令をデコードし、実行する機能を有する。ALU602は、四則演算、論理演算などの各種演算処理を行う機能を有する。データキャッシュ603は、使用頻度の高いデータを一時的に記憶しておく緩衝記憶装置である。命令キャッシュ604は、制御装置601に送られる命令(プログラム)のうち、使用頻度の高い命令を一時的に記憶しておく緩衝記憶装置である。プログラムカウンタ605は、次に実行する命令のアドレスを記憶するレジスタである。命令レジスタ606は、次に実行する命令を記憶するレジスタである。主記憶装置607には、ALU602における演算処理に用いられるデータや、制御装置601において実行される命令が記憶されている。レジスタファイル608は、汎用レジスタを含む複数のレジスタを有しており、主記憶装置607から読み出されたデータ、ALU602の演算処理の途中で得られたデータ、或いはALU602の演算処理の結果得られたデータ、などを記憶することができる。

【0166】

次いで、半導体装置600の動作について説明する。

【0167】

制御装置601は、プログラムカウンタ605に記憶されている、次に実行する命令のアドレスに従い、命令キャッシュ604の対応するアドレスから命令を読み出し、命令レジスタ606に上記命令を記憶させる。命令キャッシュ604の対応するアドレスに、該当する命令が記憶されていない場合は、主記憶装置607の対応するアドレスにアクセスし、主記憶装置607から命令を読み出し、命令レジスタ606に記憶させる。この場合、上記命令を命令キャッシュ604にも記憶させておく。

【0168】

制御装置601は、命令レジスタ606に記憶されている命令をデコードし、命令を実行する。具体的には、上記命令に従ってALU602の動作を制御するための各種信号を生成する。

【0169】

実行すべき命令が演算命令の場合は、レジスタファイル608に記憶されているデータを

10

20

30

40

50

用いて A L U 6 0 2 に演算処理を行わせ、その演算処理の結果をレジスタファイル 6 0 8 に格納する。

【 0 1 7 0 】

実行すべき命令がロード命令の場合は、制御装置 6 0 1 は、まずデータキャッシュ 6 0 3 の対応するアドレスにアクセスし、該当するデータがデータキャッシュ 6 0 3 中にあるか否かを確認する。該当するデータがある場合は、上記データをデータキャッシュ 6 0 3 の対応するアドレスからレジスタファイル 6 0 8 にコピーする。該当するデータがない場合は、上記データを主記憶装置 6 0 7 の対応するアドレスからデータキャッシュ 6 0 3 の対応するアドレスにコピーした後、データキャッシュ 6 0 3 の対応するアドレスからレジスタファイル 6 0 8 に上記データをコピーする。なお、該当するデータがない場合は、低速な主記憶装置 6 0 7 にアクセスする必要があるため、データキャッシュ 6 0 3 などの緩衝記憶装置にのみアクセスする場合よりも、命令の実行に時間を要する。しかし、上記データのコピーに加えて、主記憶装置 6 0 7 における当該データのアドレス及びその近傍のアドレスのデータも緩衝記憶装置にコピーしておくことで、主記憶装置 6 0 7 における当該データのアドレス及びその近傍のアドレスへの 2 度目以降のアクセスを、高速に行うことができる。

10

【 0 1 7 1 】

実行すべき命令がストア命令の場合は、レジスタファイル 6 0 8 のデータを、データキャッシュ 6 0 3 の対応するアドレスに記憶させる。このとき、制御装置 6 0 1 は、まずデータキャッシュ 6 0 3 の対応するアドレスにアクセスし、該当するデータがデータキャッシュ 6 0 3 中に格納できるか否かを確認する。格納できる場合は、上記データをレジスタファイル 6 0 8 からデータキャッシュ 6 0 3 の対応するアドレスにコピーする。格納できない場合は、データキャッシュ 6 0 3 の一部領域に新たに対応するアドレスを割り振り、上記データをレジスタファイル 6 0 8 からデータキャッシュ 6 0 3 の対応するアドレスにコピーする。なお、データキャッシュ 6 0 3 にデータをコピーしたら直ちに、主記憶装置 6 0 7 にも上記データをコピーする構成も可能である。また、幾つかのデータをデータキャッシュ 6 0 3 にコピーした後、それらのデータをまとめて主記憶装置 6 0 7 にコピーする構成も可能である。

20

【 0 1 7 2 】

そして、制御装置 6 0 1 は、命令の実行が終了すると、再度プログラムカウンタ 6 0 5 にアクセスし、命令レジスタ 6 0 6 から読み出した命令をデコード、実行するという上記動作を繰り返す。

30

【 0 1 7 3 】

なお、図 7 に示す半導体装置 6 0 0 では、データキャッシュ 6 0 3 や命令キャッシュ 6 0 4 などの緩衝記憶装置に、上記構成を有する記憶装置が設けられている。A L U 6 0 2 は、上記データキャッシュ 6 0 3 や命令キャッシュ 6 0 4 などの緩衝記憶装置における保持動作の選択を行う。すなわち、データキャッシュ 6 0 3 や命令キャッシュ 6 0 4 において、記憶素子にデータを保持するか、容量素子にデータを保持するかを、選択する。記憶素子によるデータの保持が選択されている場合、データキャッシュ 6 0 3 や命令キャッシュ 6 0 4 内の記憶素子への、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、データキャッシュ 6 0 3 や命令キャッシュ 6 0 4 内の記憶素子への電源電圧の供給が停止される。電源停止に関しては、図 6 に示すように、記憶回路群と、電源電位 V D D または電源電位 V S S の与えられているノード間に、スイッチング素子を設けることにより行うことができる。

40

【 0 1 7 4 】

本発明の一態様では、高速駆動が要求される記憶素子においては、結晶性を有するシリコン、またはゲルマニウムなどの半導体をチャネル形成領域に有するトランジスタを用いることで、半導体装置 6 0 0 の高速駆動を実現することができる。また、本発明の一態様では、酸化物半導体をチャネル形成領域に有するトランジスタを、容量素子の電荷を保持するためのスイッチング素子として用いる構成とすることで、容量素子からリーキする電荷

50

の量を小さく抑えることができる。よって、本発明の一態様では、データキャッシュ 603 や命令キャッシュ 604 などの緩衝記憶装置に、上記構成を有する記憶装置を用いることで、電源の供給を停止してもデータの消失を防ぐことができる。よって、半導体装置 600 全体、もしくは半導体装置 600 を構成する制御装置 601、ALU 602 などの論理回路において、短い時間でも電源の供給を停止することができる。従って、半導体装置 600 の消費電力を小さく抑えることができる。そして、本発明の一態様では、記憶装置において、記憶素子を構成するトランジスタと、スイッチング素子を構成するトランジスタとを積層することで、半導体装置 600 の高集積化を実現することができる。

## 【0175】

なお、酸化物半導体をチャネル形成領域に用いたトランジスタに限らず、実際に測定されるトランジスタの移動度は、様々な理由によって本来の移動度よりも低くなる。実際に測定される移動度が低い要因として、半導体内部の欠陥や半導体と絶縁膜との界面の欠陥があるが、Levinson モデルを用いると、半導体内部に欠陥がないと仮定した場合の移動度を理論的に導き出せる。半導体の本来の移動度を  $\mu_0$  とし、半導体中に何らかのボテンシャル障壁（粒界等）が存在すると仮定すると、測定される移動度  $\mu$  は以下の数式 3 で表される。

## 【0176】

## 【数 2】

$$\mu = \mu_0 \exp\left(-\frac{E}{kT}\right) \quad (数式 3)$$

10

20

## 【0177】

なお、E はボテンシャル障壁の高さであり、k はボルツマン定数、T は絶対温度である。また、ボテンシャル障壁が欠陥に由来すると仮定すると、Levinson モデルを用いると、E は以下の数式 4 で表される。

## 【0178】

## 【数 3】

$$E = \frac{e^2 N^2}{8\epsilon n} = \frac{e^3 N^2 t}{8\epsilon C_{ox} V_{gs}} \quad (数式 4)$$

30

## 【0179】

なお、e は電気素量、N はチャネル形成領域内の単位面積当たりの平均欠陥密度、 $\epsilon$  は半導体の誘電率、n はチャネル形成領域のキャリア面密度、 $C_{ox}$  は単位面積当たりの容量、 $V_{gs}$  はゲート電圧、t はチャネル形成領域の厚さである。なお、厚さ 30 nm 以下の半導体膜であれば、チャネル形成領域の厚さは半導体膜の厚さと同一として差し支えない。

## 【0180】

線形領域におけるドレイン電流  $I_{ds}$  は、以下の数式 5 で表される。

## 【0181】

## 【数 4】

$$I_{ds} = \frac{W \mu V_{gs} V_{ds} C_{ox}}{L} \exp\left(-\frac{E}{kT}\right) \quad (数式 5)$$

40

## 【0182】

L はチャネル長、W はチャネル幅であり、L = W = 10 μm であるものとする。また、 $V_{ds}$  はドレイン電圧である。数式 5 の両辺を  $V_{gs}$  で除し、更に両辺の対数を取ると、以下の数式 6 が得られる。

## 【0183】

## 【数5】

$$\ln\left(\frac{I_{ds}}{V_{gs}}\right) = \ln\left(\frac{W\mu V_{ds} C_{ox}}{L}\right) - \frac{E}{kT} = \ln\left(\frac{W\mu V_{ds} C_{ox}}{L}\right) - \frac{e^3 N^2 t}{8kT \epsilon C_{ox} V_{gs}} \quad (\text{数式6})$$

となる。数式6の右辺は $V_{gs}$ の関数である。数式6からわかるように、縦軸を $I_n$  ( $I_{ds} / V_{gs}$ )、横軸を $1 / V_{gs}$ とする直線の傾きから、欠陥密度 $N$ が求められる。すなわち、トランジスタの $I_{ds}$   $V_{gs}$ 特性から、欠陥密度を評価できる。

## 【0184】

欠陥密度は酸化物半導体の成膜時の基板温度に依存する。図21に、基板加熱温度と欠陥密度の関係を示す。酸化物半導体としては、インジウム ( $I_n$ )、ガリウム ( $Ga$ )、亜鉛 ( $Zn$ )の比率が、 $I_n : Ga : Zn = 1 : 1 : 1$ のものを用いた。図21では、基板加熱温度が高いものは室温で成膜したものよりも欠陥密度が低下することが示される。

## 【0185】

このようにして求めた欠陥密度等をもとに、数式3及び数式4により、 $\mu_0 = 120 \text{ cm}^2 / \text{Vs}$ が導出される。欠陥のある $I_n - Sn - Zn$ 酸化物で測定される移動度は $35 \text{ cm}^2 / \text{Vs}$ 程度である。しかし、半導体内部および半導体と絶縁膜との界面の欠陥が無い酸化物半導体の移動度 $\mu_0$ は $120 \text{ cm}^2 / \text{Vs}$ となると予想できる。

## 【0186】

ただし、半導体内部に欠陥がなくても、チャネル形成領域とゲート絶縁膜との界面での散乱によってトランジスタの移動度は影響を受ける。すなわち、ゲート絶縁膜界面から $\times$ だけ離れた場所における移動度 $\mu_1$ は、以下の数式7で表される。

## 【0187】

## 【数6】

$$\frac{1}{\mu_1} = \frac{1}{\mu_0} + \frac{D}{B} \exp\left(-\frac{x}{G}\right) \quad (\text{数式7})$$

## 【0188】

ここで、 $D$ はゲート方向の電界、 $B$ 、 $G$ は定数である。 $B$ および $G$ は、実際の測定結果より求めることができ、上記の測定結果からは、 $B = 4.75 \times 10^7 \text{ cm/s}$ 、 $G = 10 \text{ nm}$  (界面散乱が及ぶ深さ) である。 $D$ が増加する (すなわち、ゲート電圧が高くなる) と数式7の第2項が増加するため、移動度 $\mu_1$ は低下することがわかる。

## 【0189】

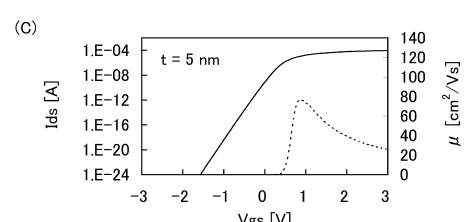

半導体内部の欠陥が無い理想的な酸化物半導体をチャネル形成領域に用いたトランジスタの移動度 $\mu_2$ を計算した結果を図22に示す。なお、計算にはシノプシス社製デバイスシミュレーションソフト、*Sentaurus Device*を使用し、酸化物半導体のバンドギャップ、電子親和力、比誘電率、厚さをそれぞれ、 $2.8$ 電子ボルト、 $4.7$ 電子ボルト、 $15$ 、 $15 \text{ nm}$ とした。これらの値は、スパッタリング法により形成された薄膜を測定して得られたものである。

## 【0190】

さらに、ゲート、ソース、ドレインの仕事関数をそれぞれ、 $5.5$ 電子ボルト、 $4.6$ 電子ボルト、 $4.6$ 電子ボルトとした。また、ゲート絶縁膜の厚さは $100 \text{ nm}$ 、比誘電率は $4.1$ とした。チャネル長およびチャネル幅はともに $10 \mu\text{m}$ 、ドレイン電圧 $V_{ds}$ は $0.1 \text{ V}$ である。

## 【0191】

図22で示されるように、ゲート電圧 $1 \text{ V}$ 強で移動度 $100 \text{ cm}^2 / \text{Vs}$ 以上のピークをつけるが、ゲート電圧がさらに高くなると、界面散乱が大きくなり、移動度が低下する。なお、界面散乱を低減するためには、半導体層表面を原子レベルで平坦にすること (Atomic Layer Flatness) が望ましい。

## 【0192】

10

20

30

40

50

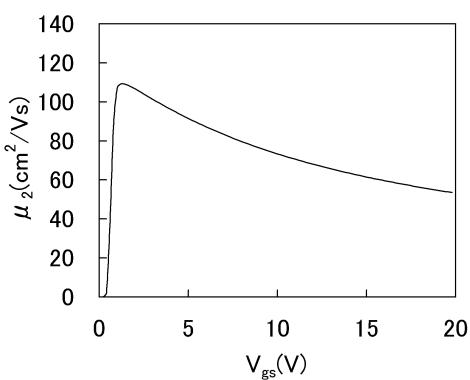

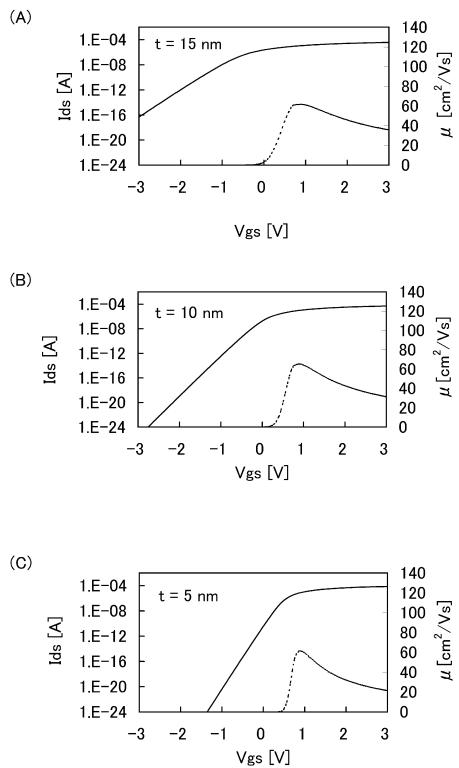

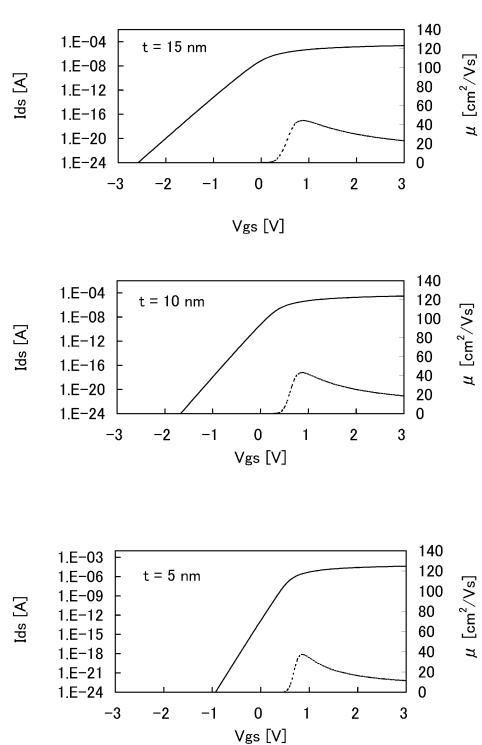

このような移動度を有する酸化物半導体を用いて微細なトランジスタを作製した場合の特性を計算した結果を図23乃至図25に示す。なお、計算に用いたトランジスタの断面構造を図26に示す。図26に示すトランジスタは酸化物半導体層に $n^+$ の導電型を呈する半導体領域1103aおよび半導体領域1103cを有する。半導体領域1103aおよび半導体領域1103cの抵抗率は $2 \times 10^{-3} \text{ cm}$ とする。

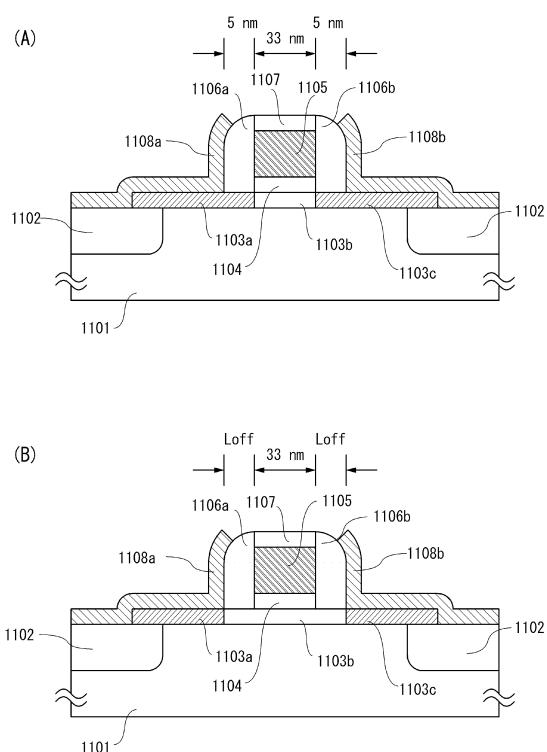

#### 【0193】

図26(A)に示すトランジスタは、下地絶縁層1101と、下地絶縁層1101に埋め込まれるように形成された酸化アルミニウムよりなる埋め込み絶縁物1102の上に形成される。トランジスタは半導体領域1103a、半導体領域1103cと、それらに挟まれ、チャネル形成領域となる真性の半導体領域1103bと、ゲート電極1105を有する。ゲート電極1105の幅を33nmとする。

10

#### 【0194】

ゲート電極1105と半導体領域1103bの間には、ゲート絶縁膜1104を有し、また、ゲート電極1105の両側面には側壁絶縁物1106aおよび側壁絶縁物1106b、ゲート電極1105の上部には、ゲート電極1105と他の配線との短絡を防止するための絶縁物1107を有する。側壁絶縁物の幅は5nmとする。また、半導体領域1103aおよび半導体領域1103cに接して、ソース電極1108aおよびドレイン電極1108bを有する。なお、このトランジスタにおけるチャネル幅を40nmとする。

#### 【0195】

図26(B)に示すトランジスタは、下地絶縁層1101と、酸化アルミニウムよりなる埋め込み絶縁物1102の上に形成され、半導体領域1103a、半導体領域1103cと、それらに挟まれた真性の半導体領域1103bと、幅33nmのゲート電極1105とゲート絶縁膜1104と側壁絶縁物1106aおよび側壁絶縁物1106bと絶縁物1107とソース電極1108aおよびドレイン電極1108bを有する点で図26(A)に示すトランジスタと同じである。

20

#### 【0196】

図26(A)に示すトランジスタと図26(B)に示すトランジスタの相違点は、側壁絶縁物1106aおよび側壁絶縁物1106bの下の半導体領域の導電型である。図26(A)に示すトランジスタでは、側壁絶縁物1106aおよび側壁絶縁物1106bの下の半導体領域は $n^+$ の導電型を呈する半導体領域1103aおよび半導体領域1103cであるが、図26(B)に示すトランジスタでは、真性の半導体領域1103bである。すなわち、半導体領域1103a(半導体領域1103c)とゲート電極1105がLooffだけ重ならない領域ができている。この領域をオフセット領域といい、その幅Looffをオフセット長という。図から明らかなように、オフセット長は、側壁絶縁物1106a(側壁絶縁物1106b)の幅と同じである。

30

#### 【0197】

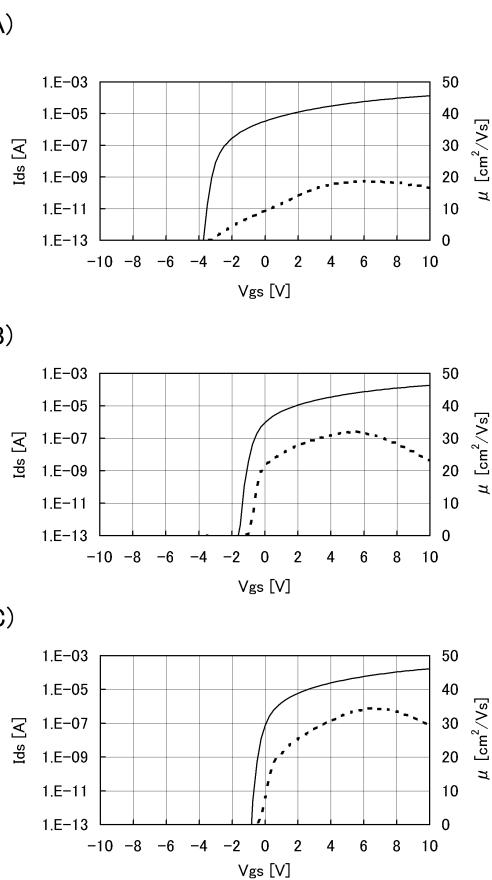

その他の計算に使用するパラメータは上述の通りである。計算にはシノプシス社製デバイスシミュレーションソフト、Santaurus Deviceを使用した。図23は、図26(A)に示される構造のトランジスタのドレイン電流( $I_{ds}$ 、実線)および移動度( $\mu$ 、点線)のゲート電圧( $V_{gs}$ 、ゲートとソースの電位差)依存性を示す。ドレイン電流 $I_{ds}$ は、ドレイン電圧(ドレインとソースの電位差)を+1Vとし、移動度 $\mu$ はドレイン電圧を+0.1Vとして計算したものである。

40

#### 【0198】

図23(A)はゲート絶縁膜の厚さを15nmとしたものであり、図23(B)は10nmとしたものであり、図23(C)は5nmとしたものである。ゲート絶縁膜が薄くなるほど、特にオフ状態でのドレイン電流 $I_{ds}$ (オフ電流)が顕著に小さくなる。一方、移動度 $\mu$ のピーク値やオン状態でのドレイン電流 $I_{ds}$ (オン電流)には目立った変化がない。ゲート電圧1V前後で、ドレイン電流はメモリ素子等で必要とされる10 $\mu$ Aを超えることが示された。

#### 【0199】

50

図24は、図26(B)に示される構造のトランジスタで、オフセット長 $L_{off}$ を5nmとしたもののドレン電流 $I_{ds}$ (実線)および移動度 $\mu$ (点線)のゲート電圧 $V_{gs}$ 依存性を示す。ドレン電流 $I_{ds}$ は、ドレン電圧を+1Vとし、移動度 $\mu$ はドレン電圧を+0.1Vとして計算したものである。図24(A)はゲート絶縁膜の厚さを15nmとしたものであり、図24(B)は10nmとしたものであり、図24(C)は5nmとしたものである。

#### 【0200】

また、図25は、図26(B)に示される構造のトランジスタで、オフセット長 $L_{off}$ を15nmとしたもののドレン電流 $I_{ds}$ (実線)および移動度 $\mu$ (点線)のゲート電圧依存性を示す。ドレン電流 $I_{ds}$ は、ドレン電圧を+1Vとし、移動度 $\mu$ はドレン電圧を+0.1Vとして計算したものである。図25(A)はゲート絶縁膜の厚さを15nmとしたものであり、図25(B)は10nmとしたものであり、図25(C)は5nmとしたものである。

10

#### 【0201】

いずれもゲート絶縁膜が薄くなるほど、オフ電流が顕著に小さくなる一方、移動度 $\mu$ のピーク値やオン電流には目立った変化が無い。

#### 【0202】

なお、移動度 $\mu$ のピークは、図23では $80\text{ cm}^2/\text{Vs}$ 程度であるが、図24では $60\text{ cm}^2/\text{Vs}$ 程度、図25では $40\text{ cm}^2/\text{Vs}$ と、オフセット長 $L_{off}$ が増加するほど低下する。また、オフ電流も同様な傾向がある。一方、オン電流にはオフセット長 $L_{off}$ の増加にともなって小さくなるが、オフ電流が小さくなるのに比べるとはるかに緩やかである。また、いずれもゲート電圧1V前後で、ドレン電流はメモリ素子等で必要とされる $10\mu\text{A}$ を超えることが示された。

20

#### 【0203】

また、In、Sn、Znを主成分とする酸化物半導体をチャネル形成領域とするトランジスタは、該酸化物半導体を形成する際に基板を加熱して成膜すること、或いは酸化物半導体膜を形成した後に熱処理を行うことで良好な特性を得ることができる。なお、主成分とは組成比で5atomic%以上含まれる元素をいう。

#### 【0204】

In、Sn、Znを主成分とする酸化物半導体膜の成膜後に基板を意図的に加熱することで、トランジスタの移動度を向上させることが可能となる。また、トランジスタのしきい値電圧をプラスシフトさせ、ノーマリ・オフ化させることが可能となる。

30

#### 【0205】

例えば、図27(A)～図27(C)は、In、Sn、Znを主成分とし、チャネル長 $L$ が $3\mu\text{m}$ 、チャネル幅 $W$ が $10\mu\text{m}$ である酸化物半導体膜と、厚さ $100\text{nm}$ のゲート絶縁膜を用いたトランジスタの特性である。なお、 $V_{ds}$ は $10\text{V}$ とした。

#### 【0206】

図27(A)は基板を意図的に加熱せずにスパッタリング法でIn、Sn、Znを主成分とする酸化物半導体膜を形成したときのトランジスタ特性である。このとき移動度は $18.8\text{ cm}^2/\text{Vs}$ が得られている。一方、基板を意図的に加熱してIn、Sn、Znを主成分とする酸化物半導体膜を形成すると移動度を向上させることが可能となる。図27(B)は基板を $200$ に加熱してIn、Sn、Znを主成分とする酸化物半導体膜を形成したときのトランジスタ特性を示すが、移動度は $32.2\text{ cm}^2/\text{Vs}$ が得られている。

40

#### 【0207】

移動度は、In、Sn、Znを主成分とする酸化物半導体膜を形成した後に熱処理することによって、さらに高めることができる。図27(C)は、In、Sn、Znを主成分とする酸化物半導体膜を $200$ でスパッタリング成膜した後、 $650$ で熱処理をしたときのトランジスタ特性を示す。このとき移動度は $34.5\text{ cm}^2/\text{Vs}$ が得られている。

#### 【0208】

50

基板を意図的に加熱することでスパッタリング成膜中の水分が酸化物半導体膜中に取り込まれるのを低減する効果が期待できる。また、成膜後に熱処理をすることによっても、酸化物半導体膜から水素や水酸基若しくは水分を放出させ除去することができ、上記のように移動度を向上させることができる。このような移動度の向上は、脱水化・脱水素化による不純物の除去のみならず、高密度化により原子間距離が短くなるためとも推定される。また、酸化物半導体から不純物を除去して高純度化することで結晶化を図ることができる。このように高純度化された非単結晶酸化物半導体は、理想的には  $100 \text{ cm}^2 / \text{Vs}$  を超える移動度を実現することも可能になると推定される。

#### 【0209】

In、Sn、Znを主成分とする酸化物半導体に酸素イオンを注入し、熱処理により該酸化物半導体に含まれる水素や水酸基若しくは水分を放出させ、その熱処理と同時に又はその後の熱処理により酸化物半導体を結晶化させても良い。このような結晶化若しくは再結晶化の処理により結晶性の良い非単結晶酸化物半導体を得ることができる。10

#### 【0210】

基板を意図的に加熱して成膜すること及び/又は成膜後に熱処理することの効果は、移動度の向上のみならず、トランジスタのノーマリ・オフ化を図ることにも寄与している。基板を意図的に加熱しないで形成されたIn、Sn、Znを主成分とする酸化物半導体膜をチャネル形成領域としたトランジスタは、しきい値電圧がマイナスシフトしてしまう傾向がある。しかし、基板を意図的に加熱して形成された酸化物半導体膜を用いた場合、このしきい値電圧のマイナスシフト化は解消される。つまり、しきい値電圧はトランジスタがノーマリ・オフとなる方向に動き、このような傾向は図27(A)と図27(B)の対比からも確認することができる。20

#### 【0211】

なお、しきい値電圧はIn、Sn及びZnの比率を変えることによっても制御することができる、組成比としてIn:Sn:Zn = 2:1:3とすることでトランジスタのノーマリ・オフ化を期待することができる。また、ターゲットの組成比をIn:Sn:Zn = 2:1:3とすることで結晶性の高い酸化物半導体膜を得ることができる。

#### 【0212】

意図的な基板加熱温度若しくは熱処理温度は、150以上、好ましくは200以上、より好ましくは400以上であり、より高温で成膜し或いは熱処理することでトランジスタのノーマリ・オフ化を図ることが可能となる。30

#### 【0213】

また、意図的に基板を加熱した成膜及び/又は成膜後に熱処理をすることで、ゲートバイアス・ストレスに対する安定性を高めることができる。例えば、2MV/cm、150、1時間印加の条件において、ドリフトがそれぞれ  $\pm 1.5 \text{ V}$  未満、好ましくは  $1.0 \text{ V}$  未満を得ることができる。

#### 【0214】

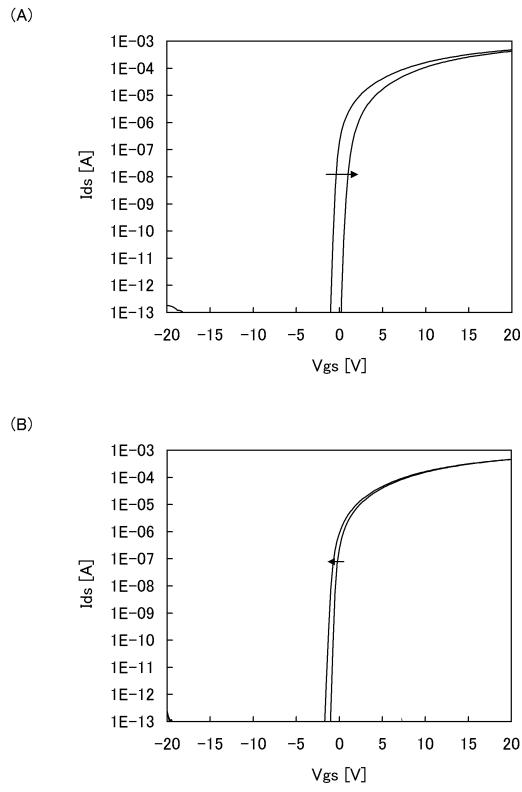

実際に、酸化物半導体膜成膜後に加熱処理を行っていない試料1と、650の加熱処理を行った試料2のトランジスタに対してBT試験を行った。

#### 【0215】

まず基板温度を25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_{gs}$ - $I_{ds}$ 特性の測定を行った。次に、基板温度を150とし、 $V_{ds}$ を0.1Vとした。次に、ゲート絶縁膜に印加される電界強度が2MV/cmとなるように $V_{gs}$ に20Vを印加し、そのまま1時間保持した。次に、 $V_{gs}$ を0Vとした。次に、基板温度25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_{gs}$ - $I_{ds}$ 測定を行った。これをプラスBT試験と呼ぶ。

#### 【0216】

同様に、まず基板温度を25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_{gs}$ - $I_{ds}$ 特性の測定を行った。次に、基板温度を150とし、 $V_{ds}$ を0.1Vとした。次に、ゲート絶縁膜に印加される電界強度が-2MV/cmとなるように $V_{gs}$ に-20Vを

40

50

印加し、そのまま1時間保持した。次に、 $V_{g_s}$ を0Vとした。次に、基板温度25<sup>10</sup>とし、 $V_{d_s}$ を10Vとし、トランジスタの $V_{g_s}$ - $I_{d_s}$ 測定を行った。これをマイナスBT試験と呼ぶ。

#### 【0217】

試料1のプラスBT試験の結果を図28(A)に、マイナスBT試験の結果を図28(B)に示す。また、試料2のプラスBT試験の結果を図29(A)に、マイナスBT試験の結果を図29(B)に示す。

#### 【0218】

試料1のプラスBT試験およびマイナスBT試験によるしきい値電圧の変動は、それぞれ1.80Vおよび-0.42Vであった。また、試料2のプラスBT試験およびマイナスBT試験によるしきい値電圧の変動は、それぞれ0.79Vおよび0.76Vであった。試料1および試料2のいずれも、BT試験前後におけるしきい値電圧の変動が小さく、信頼性が高いことがわかる。

#### 【0219】

熱処理は酸素雰囲気中で行うことができるが、まず窒素若しくは不活性ガス、または減圧下で熱処理を行ってから酸素を含む雰囲気中で熱処理を行っても良い。最初に脱水化・脱水素化を行ってから酸素を酸化物半導体に加えることで、熱処理の効果をより高めることができる。また、後から酸素を加えるには、酸素イオンを電界で加速して酸化物半導体膜に注入する方法を適用しても良い。

#### 【0220】

酸化物半導体中及び積層される膜との界面には、酸素欠損による欠陥が生成されやすいが、かかる熱処理により酸化物半導体中に酸素を過剰に含ませることにより、定常的に生成される酸素欠損を過剰な酸素によって補償することが可能となる。過剰酸素は主に格子間に存在する酸素であり、その酸素濃度は $1 \times 10^{16} / \text{cm}^3$ 以上 $2 \times 10^{20} / \text{cm}^3$ 以下とすれば、結晶に歪み等を与えることなく酸化物半導体中に含ませることができる。

#### 【0221】

また、熱処理によって酸化物半導体に結晶が少なくとも一部に含まれるようにすることでも、より安定な酸化物半導体膜を得ることができる。例えば、組成比 $In : Sn : Zn = 1 : 1 : 1$ のターゲットを用いて、基板を意図的に加熱せずにスパッタリング成膜した酸化物半導体膜は、X線回折(XRD : X-Ray Diffraction)でハローパターンが観測される。この成膜された酸化物半導体膜を熱処理することによって結晶化させることができる。熱処理温度は任意であるが、例えば650<sup>30</sup>の熱処理を行うことで、X線回折により明確な回折ピークを観測することができる。

#### 【0222】

実際に、 $In - Sn - Zn$ 系酸化物半導体膜のXRD分析を行った。XRD分析には、Bruker AXS社製X線回折装置D8 ADVANCEを用い、Out-of-Plane法で測定した。

#### 【0223】

XRD分析を行った試料として、試料Aおよび試料Bを用意した。以下に試料Aおよび試料Bの作製方法を説明する。

#### 【0224】

脱水素化処理済みの石英基板上に $In - Sn - Zn$ 系酸化物半導体膜を100nmの厚さで成膜した。

#### 【0225】

$In - Sn - Zn$ 系酸化物半導体膜は、スパッタリング装置を用い、酸素雰囲気で電力を100W(DC)として成膜した。ターゲットは、 $In : Sn : Zn = 1 : 1 : 1$ [原子数比]の $In - Sn - Zn$ 系酸化物ターゲットを用いた。なお、成膜時の基板加熱温度は200<sup>40</sup>とした。このようにして作製した試料を試料Aとした。

#### 【0226】

次に、試料Aと同様の方法で作製した試料に対し加熱処理を650<sup>50</sup>の温度で行った。加

熱処理は、はじめに窒素雰囲気で1時間の加熱処理を行い、温度を下げずに酸素雰囲気でさらに1時間の加熱処理を行っている。このようにして作製した試料を試料Bとした。

【0227】

図30に試料Aおよび試料BのXRDスペクトルを示す。試料Aでは、結晶由来のピークが観測されなかったが、試料Bでは、2°が35deg近傍および37deg～38degに結晶由来のピークが観測された。

【0228】

このように、In、Sn、Znを主成分とする酸化物半導体は成膜時に意図的に加熱すること及び/又は成膜後に熱処理することによりトランジスタの特性を向上させることができる。

10

【0229】

この基板加熱や熱処理は、酸化物半導体にとって悪性の不純物である水素や水酸基を膜中に含ませないようにすること、或いは膜中から除去する作用がある。すなわち、酸化物半導体中でドナー不純物となる水素を除去することで高純度化を図ることができ、それによつてトランジスタのノーマリ・オフ化を図ることができ、酸化物半導体が高純度化されることによりオフ電流を1aA/μm以下にすることができる。ここで、上記オフ電流値の単位は、チャネル幅1μmあたりの電流値を示す。

【0230】

図31に、トランジスタのオフ電流と測定時の基板温度(絶対温度)の逆数との関係を示す。ここでは、簡単のため測定時の基板温度の逆数に1000を掛けた数値(1000/T)を横軸としている。

20

【0231】

具体的には、図31に示すように、基板温度が125°の場合には1aA/μm( $1 \times 10^{-18}$ A/μm)以下、85°の場合には100zA/μm( $1 \times 10^{-19}$ A/μm)以下、室温(27°)の場合には1zA/μm( $1 \times 10^{-21}$ A/μm)以下にすることができる。好ましくは、125°において0.1aA/μm( $1 \times 10^{-19}$ A/μm)以下に、85°において10zA/μm( $1 \times 10^{-20}$ A/μm)以下に、室温において0.1zA/μm( $1 \times 10^{-22}$ A/μm)以下にすることができる。これらのオフ電流値は、Siを半導体膜として用いたトランジスタに比べて、極めて小さいものであることは明らかである。

30

【0232】

もっとも、酸化物半導体膜の成膜時に水素や水分が膜中に混入しないように、成膜室外部からのリークや成膜室内の内壁からの脱ガスを十分抑え、スパッタガスの高純度化を図ることが好ましい。例えば、スパッタガスは水分が膜中に含まれないように露点-70°以下であるガスを用いることが好ましい。また、ターゲットそのものに水素や水分などの不純物が含まれていないように、高純度化されたターゲットを用いることが好ましい。In、Sn、Znを主成分とする酸化物半導体は熱処理によって膜中の水分を除去することができるが、In、Ga、Znを主成分とする酸化物半導体と比べて水分の放出温度が高いため、好ましくは最初から水分の含まれない膜を形成しておくことが好ましい。

40

【0233】

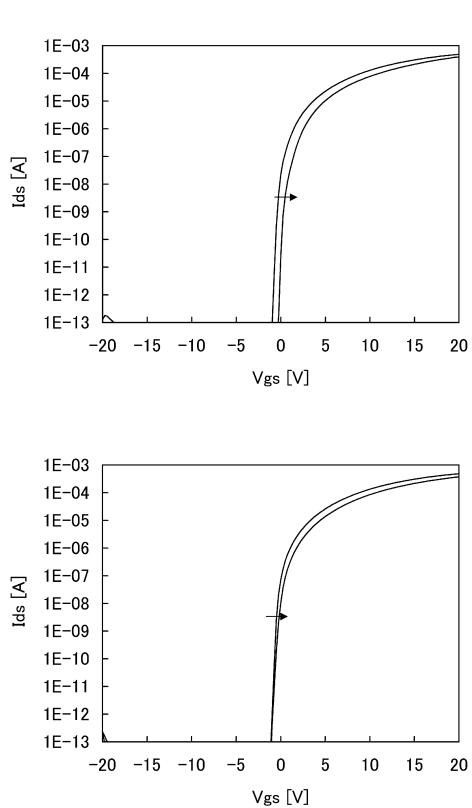

また、酸化物半導体膜成膜後に650°の加熱処理を行った試料Bのトランジスタにおいて、基板温度と電気的特性の関係について評価した。

【0234】

測定に用いたトランジスタは、チャネル長Lが3μm、チャネル幅Wが10μm、LoVが0μm、dWが0μmである。なお、V<sub>ds</sub>は10Vとした。なお、基板温度は-40°、-25°、25°、75°、125°および150°で行った。ここで、トランジスタにおいて、ゲート電極と一対の電極との重畳する幅をLoVと呼び、酸化物半導体膜に対する一対の電極のはみ出しをdWと呼ぶ。

【0235】

図32に、I<sub>ds</sub>(実線)および移動度(点線)のV<sub>gs</sub>依存性を示す。また、図33(

50

A)に基板温度としきい値電圧の関係を、図33(B)に基板温度と移動度の関係を示す。

【0236】

図33(A)より、基板温度が高いほどしきい値電圧は低くなることがわかる。なお、その範囲は-40 ~ 150 で1.09V ~ -0.23Vであった。

【0237】

また、図33(B)より、基板温度が高いほど移動度が低くなることがわかる。なお、その範囲は-40 ~ 150 で36cm<sup>2</sup>/Vs ~ 32cm<sup>2</sup>/Vsであった。従って、上述の温度範囲において電気的特性の変動が小さいことがわかる。

【0238】

上記のようなIn、Sn、Znを主成分とする酸化物半導体をチャネル形成領域とするトランジスタによれば、オフ電流を1aA/μm以下に保ちつつ、移動度を30cm<sup>2</sup>/Vs以上、好ましくは40cm<sup>2</sup>/Vs以上、より好ましくは60cm<sup>2</sup>/Vs以上とし、LSIで要求されるオン電流の値を満たすことができる。例えば、L/W=33nm/40nmのFETで、ゲート電圧2.7V、ドレイン電圧1.0Vのとき12μA以上のオン電流を流すことができる。またトランジスタの動作に求められる温度範囲においても、十分な電気的特性を確保することができる。このような特性であれば、Si半導体で作られる集積回路の中に酸化物半導体で形成されるトランジスタを混載しても、動作速度を犠牲にすることなく新たな機能を有する集積回路を実現することができる。

【0239】

(実施の形態2)

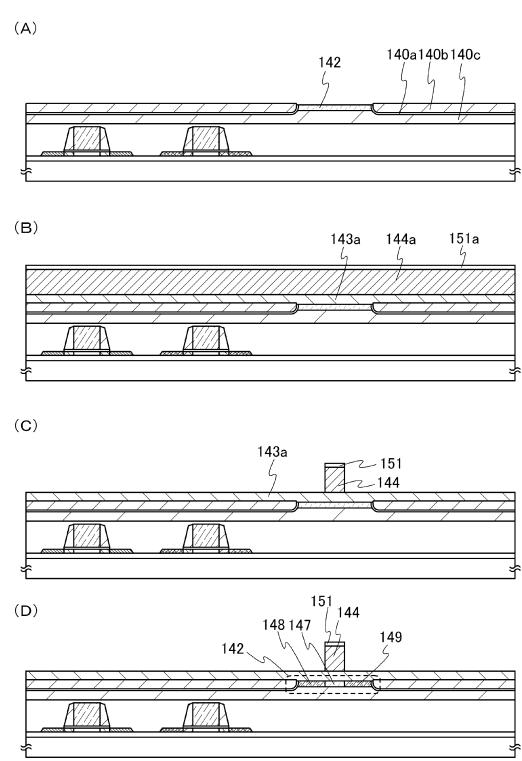

本実施の形態では、図3に示す構成をその一部に有する半導体装置の、作製方法の一例について説明する。

【0240】

ただし、記憶素子が有するnチャネル型トランジスタ102n及びpチャネル型トランジスタ102pは、シリコンの他、ゲルマニウム、シリコンゲルマニウム、単結晶炭化シリコンなどの半導体材料を用いていても良い。また、例えば、シリコンを用いたnチャネル型トランジスタ102n及びpチャネル型トランジスタ102pは、シリコンウェハなどの単結晶半導体基板、SOI法により作製されたシリコン薄膜、気相成長法により作製されたシリコン薄膜などを用いて形成することができる。

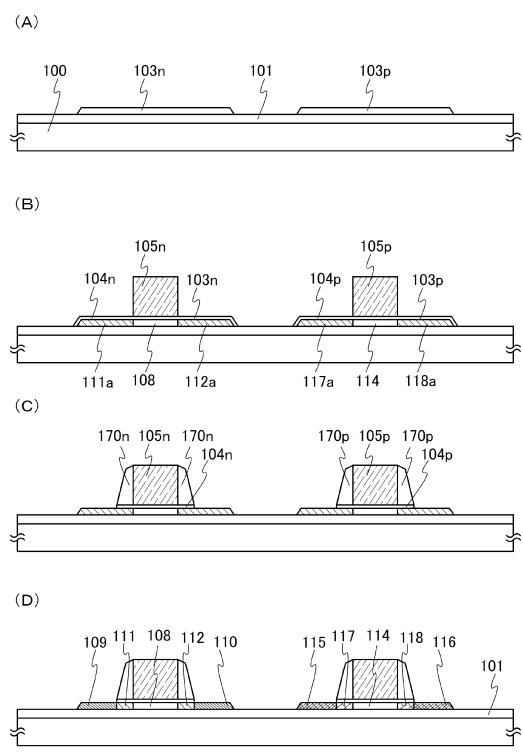

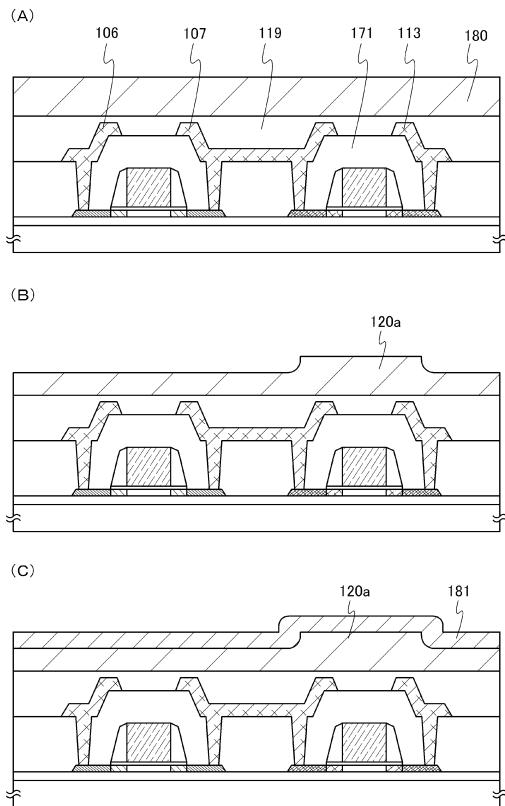

【0241】

本実施の形態では、まず、図8(A)に示すように、基板100上に絶縁膜101と、島状である単結晶の半導体膜103n及び半導体膜103pを形成する。

【0242】

基板100として使用することができる素材に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、基板100には、フュージョン法やフロート法で作製されるガラス基板、石英基板、半導体基板、セラミック基板等を用いることができる。ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730 以上のものを用いると良い。

【0243】

本実施の形態では、単結晶シリコンの半導体基板を基板100として用いる。単結晶の半導体基板はガラス基板よりも表面の平坦性が高い。よって、基板のうねりに起因して絶縁膜や導電膜などの膜厚がばらつくのを防ぐことができるため、トランジスタなどの半導体素子を微細化しても半導体素子の電気的特性を均一にすることができます。

【0244】

絶縁膜101は、酸化シリコン、窒化酸化シリコン、酸化窒化シリコン、窒化シリコン等の絶縁性を有する材料を用いて形成する。絶縁膜101は、単数の絶縁膜を用いたものであっても、複数の絶縁膜を積層して用いたものであっても良い。

【0245】

例えば酸化シリコンを絶縁膜101として用いる場合、絶縁膜101はシランと酸素、T

10

20

30

40

50

EOS(テトラエトキシシラン)と酸素等の混合ガスを用い、熱CVD、プラズマCVD、常圧CVD、バイアスECR CVD等の気相成長法によって形成することができる。この場合、絶縁膜101の表面を酸素プラズマ処理で緻密化しても良い。また、窒化シリコンを絶縁膜101として用いる場合、シランとアンモニアの混合ガスを用い、プラズマCVD等の気相成長法によって形成することができる。また、窒化酸化シリコンを絶縁膜101として用いる場合、シランとアンモニアの混合ガス、またはシランと酸化窒素の混合ガスを用い、プラズマCVD等の気相成長法によって形成することができる。

【0246】

また絶縁膜101として、有機シランガスを用いて化学気相成長法により作製される酸化シリコンを用いていても良い。有機シランガスとしては、珪酸エチル(TEOS:化学式 $\text{Si}(\text{OC}_2\text{H}_5)_4$ )、テトラメチルシラン(TMS:化学式 $\text{Si}(\text{CH}_3)_4$ )、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH $(\text{OC}_2\text{H}_5)_3$ )、トリスジメチルアミノシラン(SiH $(\text{N}(\text{CH}_3)_2)_3$ )等のシリコン含有化合物を用いることができる。

【0247】

また、基板100が単結晶シリコンの半導体基板である場合、基板100の表面を酸化することで得られる酸化膜で、絶縁膜101を構成することもできる。上記酸化膜を形成するための、熱酸化処理には、ドライ酸化でも良いが、酸化雰囲気中にハロゲンを含むガスを添加しても良い。ハロゲンを含むガスとして、HCl、HF、NF<sub>3</sub>、HBr、Cl<sub>2</sub>、ClF、BCl<sub>3</sub>、F<sub>2</sub>、Br<sub>2</sub>などから選ばれた一種又は複数種ガスを用いることができる。

【0248】

例えばHClを用いる場合、酸素に対しHClを0.5~10体積%(好ましくは3体積%)の割合で含む雰囲気中で、700以上の中温で熱処理を行う。950以上1100以下の加熱温度で熱酸化を行うとよい。処理時間は0.1~6時間、好ましくは0.5~1時間とすればよい。形成される絶縁膜101の膜厚は、15nm~1100nm(好ましくは60nm~300nm)、例えば150nmとすることができる。

【0249】

このハロゲンを含む雰囲気での熱酸化処理により、絶縁膜101にハロゲンを含ませることができる。ハロゲン元素を $1 \times 10^{17}$ atoms/cm<sup>3</sup>~ $5 \times 10^{20}$ atoms/cm<sup>3</sup>の濃度で絶縁膜101に含ませることにより、金属などの不純物を絶縁膜101が捕獲するので、後に形成される半導体膜103n及び半導体膜103pの汚染を防止することができる。例えば、塩素の作用により、金属などの不純物が揮発性の塩化物となつて気相中へ離脱して、半導体膜103n及び半導体膜103pから除去される。

【0250】

また、本実施の形態では、半導体膜103n及び半導体膜103pが単結晶のシリコンである場合を例に挙げて、以下、記憶素子が有するトランジスタの作製方法について説明する。なお、具体的な単結晶の半導体膜103n及び半導体膜103pの作製方法の一例について、簡単に説明する。まず、単結晶シリコンの半導体基板であるボンド基板に、電界で加速されたイオンでなるイオンビームを注入し、ボンド基板の表面から一定の深さの領域に、結晶構造が乱されることで局所的に脆化された脆化層を形成する。脆化層が形成される領域の深さは、イオンビームの加速エネルギーとイオンビームの入射角によって調節することができる。そして、ボンド基板と、表面に絶縁膜が形成された基板100とを、間に当該絶縁膜が挟まるように貼り合わせる。貼り合わせは、ボンド基板と基板100とを重ね合わせた後、ボンド基板と基板100の一部に、1N/cm<sup>2</sup>以上500N/cm<sup>2</sup>以下、好ましくは11N/cm<sup>2</sup>以上20N/cm<sup>2</sup>以下程度の圧力を加える。圧力を加えると、その部分からボンド基板と絶縁膜101とが接合を開始し、最終的には密着した面全体に接合が及ぶ。次いで、加熱処理を行うことで、脆化層に存在する微小ボイド同士が結合して、微小ボイドの体積が増大する。その結果、脆化層においてボンド基板の

10

20

30

40

50

一部である単結晶半導体膜が、ボンド基板から分離する。上記加熱処理の温度は、基板100の歪み点を越えない温度とする。そして、上記単結晶半導体膜をエッティング等により所望の形状に加工することで、半導体膜103n及び半導体膜103pを形成することができる。

#### 【0251】

本実施の形態では、単結晶シリコンの半導体基板である基板100に、酸素雰囲気中で950の温度で加熱処理を施すことで、基板100上に膜厚400nmの酸化シリコン膜を形成する。次いで、酸化シリコン膜上に、プラズマCVDにより、膜厚50nmの窒化酸化シリコン膜を形成する。一方、単結晶シリコンの半導体基板であるボンド基板に、酸素にHClを含ませた雰囲気中で、950の温度で加熱処理を行うことで、ボンド基板上に膜厚100nmの酸化シリコン膜を形成する。そして、上記基板100と、ボンド基板とを、基板100上の窒化酸化シリコン膜と、ボンド基板上の酸化シリコン膜とが接するように貼り合わせる。そして、脆化層においてボンド基板の一部である単結晶の半導体膜を、ボンド基板から分離させる。従って、本実施の形態では、絶縁膜101が、基板100側から、膜厚400nmの酸化シリコン膜、膜厚50nmの窒化酸化シリコン膜、膜厚100nmの酸化シリコン膜が、順に積層された構成を有する。

#### 【0252】

半導体膜103n及び半導体膜103pには、閾値電圧を制御するために、硼素、アルミニウム、ガリウムなどのp型の導電性を付与する不純物元素、若しくはリン、砒素などのn型の導電性を付与する不純物元素を添加しても良い。閾値電圧を制御するための不純物元素の添加は、パターニングする前の半導体膜に対して行っても良いし、パターニング後に形成された半導体膜103n及び半導体膜103pに対して行っても良い。また、閾値電圧を制御するための不純物元素の添加を、ボンド基板に対して行っても良い。若しくは、不純物元素の添加を、閾値電圧を大まかに調整するためにボンド基板に対して行った上で、閾値電圧を微調整するために、パターニング前の半導体膜に対して、又はパターニングにより形成された半導体膜103n及び半導体膜103pに対してても行っても良い。

#### 【0253】

なお、本実施の形態では、単結晶の半導体膜を用いる例について説明しているが、本発明はこの構成に限定されない。例えば、絶縁膜101上に気相成長法を用いて形成された多結晶の半導体膜を用いても良いし、気相成長法を用いて形成された半導体膜を公知の技術により結晶化して多結晶の半導体膜を形成しても良い。公知の結晶化方法としては、レーザ光を用いたレーザ結晶化法、触媒元素を用いる結晶化法がある。或いは、触媒元素を用いる結晶化法とレーザ結晶化法とを組み合わせて用いることもできる。また、石英基板のような耐熱性に優れている基板を用いる場合、電熱炉を使用した熱結晶化方法、赤外光を用いたランプアニール結晶化法、触媒元素を用いる結晶化法、950程度の高温アニール法を用いた結晶化法を用いても良い。

#### 【0254】

次に、図8(B)に示すように、半導体膜103n及び半導体膜103p上にゲート絶縁膜104n及びゲート絶縁膜104pをそれぞれ形成した後、半導体膜103nと重なる位置においてゲート絶縁膜104n上にゲート電極105nを、半導体膜103pと重なる位置においてゲート絶縁膜104p上にゲート電極105pを形成する。そして、ゲート電極105n及びゲート電極105pをマスクとして、一導電性を付与する不純物元素を半導体膜103n及び半導体膜103pに添加する。具体的には、まず、半導体膜103nを覆うようにマスクを形成した後、半導体膜103pに、p型の導電性を付与する不純物元素を添加する。上記不純物元素の添加により、半導体膜103pには、ゲート電極105pと重なる第1の領域114と、第1の領域114を間に挟む低濃度不純物領域117a及び低濃度不純物領域118aとが形成される。次いで、半導体膜103pを覆うようにマスクを形成した後、半導体膜103nに、n型の導電性を付与する不純物元素を添加する。上記不純物元素の添加により、半導体膜103nには、ゲート電極105nと重なる第1の領域108と、第1の領域108を間に挟む低濃度不純物領域111a及び

10

20

30

40

50

低濃度不純物領域 112a とが形成される。

【0255】

ゲート絶縁膜 104n 及びゲート絶縁膜 104p は、高密度プラズマ処理、熱酸化処理などを行うことにより半導体膜 103n 及び半導体膜 103p の表面を酸化又は窒化することで形成することができる。ゲート絶縁膜 104n 及びゲート絶縁膜 104p の厚さは、例えば、1 nm 以上 100 nm 以下、好ましくは 10 nm 以上 50 nm 以下とすることができる。

【0256】

本実施の形態では、酸素雰囲気中において 25 分間 950 °C にて加熱処理を行った後、窒素雰囲気中において 1 時間 950 °C にて加熱処理を行うことにより、半導体膜 103n 及び半導体膜 103p の表面を熱酸化し、膜厚 15 nm の酸化シリコン膜で構成されるゲート絶縁膜 104n 及びゲート絶縁膜 104p を形成する。

10

【0257】

高密度プラズマ処理を用いる場合は、例えば He、Ar、Kr、Xe などの希ガスと酸素、酸化窒素、アンモニア、窒素などの混合ガスとを用いる。この場合、プラズマの励起をマイクロ波の導入により行うことで、低電子温度で高密度のプラズマを生成することができる。このような高密度のプラズマで生成された酸素ラジカル (OH ラジカルを含む場合もある) や窒素ラジカル (NH ラジカルを含む場合もある) によって、半導体膜の表面を酸化又は窒化することにより、1 ~ 20 nm、好ましくは 5 ~ 10 nm の絶縁膜が半導体膜に接するように形成できる。例えば、亜酸化窒素 (N<sub>2</sub>O) を Ar で 1 ~ 3 倍 (流量比) に希釈して、10 Pa ~ 30 Pa の圧力にて 3 kW ~ 5 kW のマイクロ波 (2.45 GHz) 電力を印加して半導体膜 103n 及び半導体膜 103p の表面を酸化若しくは窒化させる。この処理により 1 nm ~ 10 nm (好ましくは 2 nm ~ 6 nm) の絶縁膜を形成する。更に亜酸化窒素 (N<sub>2</sub>O) とシラン (SiH<sub>4</sub>) を導入し、10 Pa ~ 30 Pa の圧力にて 3 kW ~ 5 kW のマイクロ波 (2.45 GHz) 電力を印加して気相成長法により酸化窒化シリコン膜を形成することにより、ゲート絶縁膜を形成する。固相反応と気相成長法による反応を組み合わせることにより界面準位密度が低く絶縁耐圧の優れたゲート絶縁膜を形成することができる。

20

【0258】

上述した高密度プラズマ処理による半導体膜の酸化又は窒化は固相反応で進むため、ゲート絶縁膜 104n 及びゲート絶縁膜 104p と半導体膜 103n 及び半導体膜 103p との界面準位密度を極めて低くすることができる。また高密度プラズマ処理により半導体膜 103n 及び半導体膜 103p を直接酸化又は窒化することで、形成される絶縁膜の厚さのばらつきを抑えることができる。また半導体膜が結晶性を有する場合、高密度プラズマ処理を用いて半導体膜の表面を固相反応で酸化させることにより、結晶粒界においてのみ酸化が速く進んでしまうのを抑え、均一性が良く、界面準位密度の低いゲート絶縁膜を形成することができる。高密度プラズマ処理により形成された絶縁膜を、ゲート絶縁膜の一部又は全部に含んで形成されるトランジスタは、電気的特性のばらつきを抑えることができる。

30

【0259】

また、プラズマ CVD 法又はスパッタ法などを用い、酸化シリコン、窒化酸化シリコン、酸化窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム又は酸化タンタル、酸化イットリウム、ハフニウムシリケート (HfSi<sub>x</sub>O<sub>y</sub> (x > 0, y > 0))、窒素が添加されたハフニウムシリケート (HfSi<sub>x</sub>O<sub>y</sub> (x > 0, y > 0))、窒素が添加されたハフニウムアルミネート (HfAl<sub>x</sub>O<sub>y</sub> (x > 0, y > 0)) 等を含む膜を、単層で、又は積層させることで、ゲート絶縁膜を形成しても良い。

40

【0260】

なお、本明細書において酸化窒化物とは、その組成として、窒素よりも酸素の含有量が多い物質であり、また、窒化酸化物とは、その組成として、酸素よりも窒素の含有量が多い物質を意味する。

50

## 【0261】

ゲート電極 105n 及びゲート電極 105p は、ゲート絶縁膜 104n 及びゲート絶縁膜 104p を覆うように導電膜を形成した後、該導電膜を所定の形状に加工（パターニング）することで、形成することができる。上記導電膜の形成には CVD 法、スパッタ法、蒸着法、スピンドル法等を用いることができる。また、導電膜は、タンタル（Ta）、タンゲステン（W）、チタン（Ti）、モリブデン（Mo）、アルミニウム（Al）、銅（Cu）、クロム（Cr）、ニオブ（Nb）等を用いることができる。上記金属を主成分とする合金を用いても良いし、上記金属を含む化合物を用いても良い。又は、半導体膜に導電性を付与するリン等の不純物元素をドーピングした、多結晶シリコンなどの半導体を用いて形成しても良い。

10

## 【0262】

なお、ゲート電極 105n 及びゲート電極 105p は、単層の導電膜で構成されていても良いし、積層された複数の導電膜で構成されていても良い。

## 【0263】

2つの導電膜の組み合わせとして、1層目に窒化タンタル又はタンタルを、2層目にタンゲステンを用いることができる。上記例の他に、窒化タンゲステンとタンゲステン、窒化モリブデンとモリブデン、アルミニウムとタンタル、アルミニウムとチタン等が挙げられる。タンゲステンや窒化タンタルは、耐熱性が高いため、2層の導電膜を形成した後の工程において、熱活性化を目的とした加熱処理を行うことができる。また、2層の導電膜の組み合わせとして、例えば、n型の導電性を付与する不純物元素がドーピングされたシリコンとニッケルシリサイド、n型の導電性を付与する不純物元素がドーピングされたシリコンとタンゲステンシリサイド等も用いることができる。

20

## 【0264】

3つの導電膜を積層する3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

## 【0265】

また、ゲート電極 105n 及びゲート電極 105p に酸化インジウム、酸化インジウム酸化スズ混合物、酸化インジウム酸化亜鉛混合物、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、又は酸化亜鉛ガリウム等の透光性を有する酸化物導電膜を用いることもできる。

30

## 【0266】

本実施の形態では、膜厚 30nm 程度の窒化タンタル上に、膜厚 170nm 程度のタンゲステンを積層したゲート電極 105n 及びゲート電極 105p を用いる。

## 【0267】

なお、マスクを用いずに、液滴吐出法を用いて選択的にゲート電極 105n 及びゲート電極 105p を形成しても良い。液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出又は噴出することで所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。

## 【0268】

また、ゲート電極 105n 及びゲート電極 105p は、導電膜を形成後、ICP（Inductive Coupled Plasma：誘導結合型プラズマ）エッチング法を用い、エッチング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節することにより、所望のテーパー形状を有するようにエッチングすることができる。また、テーパー形状は、マスクの形状によっても角度等を制御することができる。なお、エッチング用ガスとしては、塩素、塩化硼素、塩化シリコンもしくは四塩化炭素などの塩素系ガス、四弗化炭素、弗化硫黄もしくは弗化窒素などのフッ素系ガス又は酸素を適宜用いることができる。

40

## 【0269】

次いで、ゲート絶縁膜 104n 及びゲート絶縁膜 104p と、ゲート電極 105n 及びゲート電極 105p とを覆うように絶縁膜を形成した後、エッチング等により、上記絶縁膜

50

の形状を加工することで、図 8 ( C ) に示すように、サイドウォール 170n をゲート電極 105n の側部に、サイドウォール 170p をゲート電極 105p の側部に、それぞれ形成する。本実施の形態では、膜厚 100nm の酸化窒化シリコン膜と、膜厚 200nm の酸化シリコン膜とが順に積層された絶縁膜を、ゲート電極 105n 及びゲート電極 105p を覆うように形成した後、ドライエッチングによりその形状を加工することで、サイドウォール 170n 及びサイドウォール 170p を形成する。

【 0270 】

なお、上記エッチングにより、ゲート絶縁膜 104n のうち、サイドウォール 170n の下部以外の部分が除去され、また、ゲート絶縁膜 104p のうち、サイドウォール 170p の下部以外の部分が除去される。

10

【 0271 】

次に、図 8 ( D ) に示すように、ゲート電極 105n 及びゲート電極 105p と、サイドウォール 170n 及びサイドウォール 170p とをマスクとして、一導電性を付与する不純物元素を半導体膜 103n 及び半導体膜 103p に添加する。具体的には、まず、半導体膜 103n を覆うようにマスクを形成した後、半導体膜 103p に、p 型の導電性を付与する不純物元素を添加する。上記不純物元素の添加により、半導体膜 103p において、一部の低濃度不純物領域 117a 及び低濃度不純物領域 118a にさらに不純物が添加され、ゲート電極 105p と重なる第 1 の領域 114 と、サイドウォール 170p と重なり、なおかつ第 1 の領域 114 を間に挟む第 3 の領域 117 及び第 3 の領域 118 と、第 1 の領域 114 、第 3 の領域 117 及び第 3 の領域 118 を間に挟む第 2 の領域 115 及び第 2 の領域 116 とが形成される。次いで、半導体膜 103p を覆うようにマスクを形成した後、半導体膜 103n に、n 型の導電性を付与する不純物元素を添加する。上記不純物元素の添加により、半導体膜 103n において、一部の低濃度不純物領域 111a 及び低濃度不純物領域 112a にさらに不純物が添加され、ゲート電極 105n と重なる第 1 の領域 108 と、サイドウォール 170n と重なり、なおかつ第 1 の領域 108 を間に挟む第 3 の領域 111 及び第 3 の領域 112 と、第 1 の領域 108 、第 3 の領域 111 及び第 3 の領域 112 を間に挟む第 2 の領域 109 及び第 2 の領域 110 とが形成される。

20

【 0272 】

第 3 の領域 117 及び第 3 の領域 118 は、サイドウォール 170p と重なっていることにより、第 2 の領域 115 及び第 2 の領域 116 よりも、p 型の導電性を付与する不純物元素の濃度が低い。また、第 3 の領域 111 及び第 3 の領域 112 は、サイドウォール 170n と重なっていることにより、第 2 の領域 109 及び第 2 の領域 110 よりも、n 型の導電性を付与する不純物元素の濃度が低い。

30

【 0273 】

なお、本実施の形態では、1 回目の不純物の添加により低濃度不純物領域 111a 及び低濃度不純物領域 112a と、低濃度不純物領域 117a 及び低濃度不純物領域 118a とを形成してから、2 回目の不純物の添加を行うことで LDD 領域として機能する第 3 の領域 111 及び第 3 の領域 112 と、第 3 の領域 117 及び第 3 の領域 118 とを形成しているが、本発明の一態様はこの構成に限定されない。例えば、上記 1 回目の不純物の添加を行わずに、2 回目の不純物の添加を、サイドウォール 170n 及びサイドウォール 170p の下部に不純物が回り込むような条件で行うことで、LDD 領域として機能する第 3 の領域 111 及び第 3 の領域 112 と、第 3 の領域 117 及び第 3 の領域 118 とを形成することも可能である。また、上記 1 回目の不純物の添加を行わず、なおかつ 2 回目の不純物の添加を、サイドウォール 170n 及びサイドウォール 170p の下部に不純物が入りにくい条件で行うことで、第 1 の領域 108 と第 2 の領域 109 及び第 2 の領域 110 との間に、または、第 1 の領域 114 と第 2 の領域 115 及び第 2 の領域 116 との間に、オフセット領域を設けても良い。オフセット領域における不純物濃度は、第 1 の領域 108 または第 1 の領域 114 と同程度であることが望ましい。

40

【 0274 】

次いで、図 8 ( E ) に示すように、半導体膜 103n 及び半導体膜 103p と、ゲート電

50

極 105n 及びゲート電極 105p と、サイドウォール 170p 及びサイドウォール 170n と、絶縁膜 101 とを覆うように、絶縁膜 119 を形成する。

【0275】

具体的に、絶縁膜 119 は、酸化シリコン、窒化シリコン、窒化酸化シリコン、酸化窒化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの無機の絶縁膜を用いることができる。特に、誘電率の低い (low-k) 材料を絶縁膜 119 に用いることで、各種電極や配線の重なりに起因する容量を十分に低減することが可能になるため好ましい。なお、絶縁膜 119 に、上記材料を用いた多孔性の絶縁膜を適用しても良い。多孔性の絶縁膜では、密度の高い絶縁膜と比較して誘電率が低下するため、電極や配線に起因する寄生容量を更に低減することが可能である。

10

【0276】

また、絶縁膜 119 として、有機シランを用いて化学気相成長法により作製される酸化シリコン膜を用いることもできる。有機シランとしては、珪酸エチル (TEOS: Si(O<sub>2</sub>H<sub>5</sub>)<sub>4</sub>)、トリメチルシラン (TMS: (CH<sub>3</sub>)<sub>3</sub>SiH)、テトラメチルシクロロテトラシロキサン (TMCTS)、オクタメチルシクロロテトラシロキサン (OMCTS)、ヘキサメチルジシラザン (HMDS)、トリエトキシシラン (SiH(O<sub>2</sub>H<sub>5</sub>)<sub>3</sub>)、トリスジメチルアミノシラン (SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>) 等を用いることができる。もちろん、モノシラン、ジシラン、又はトリシラン等の無機シランを用いて、酸化シリコン、酸化窒化シリコン、窒化シリコン、窒化酸化シリコンなどを形成しても良い。

20

【0277】

本実施の形態では、絶縁膜 119 として膜厚 500 nm の酸化窒化シリコン膜を用いる。なお、本実施の形態では、絶縁膜 119 が単層の絶縁膜で構成されている場合を例示しているが、絶縁膜 119 は、積層された複数の絶縁膜で構成されていても良い。

【0278】

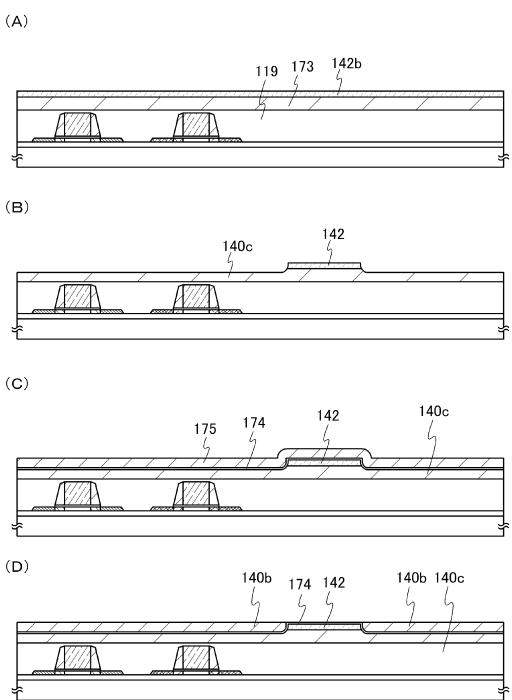

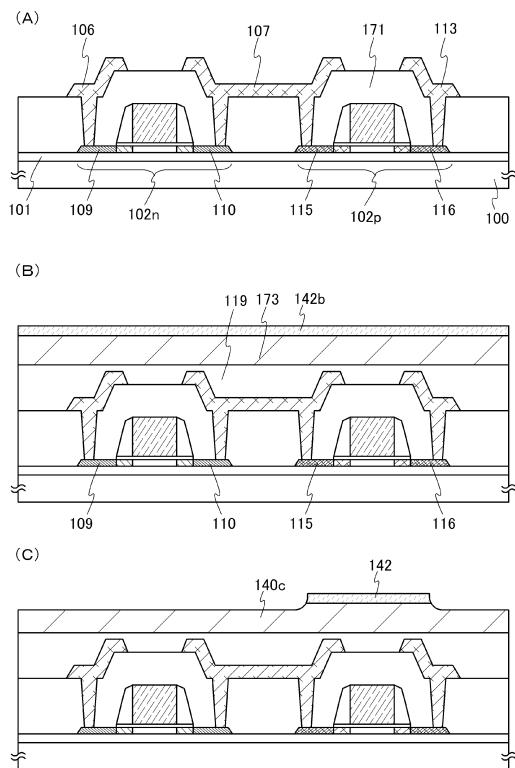

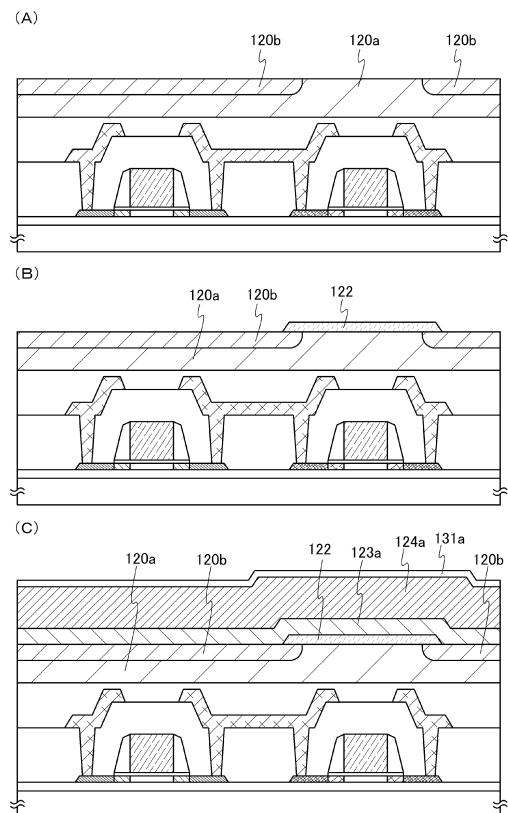

次いで、絶縁膜 119 の表面を表面に平坦化処理を施した後、図 9 (A) に示すように、絶縁膜 119 上に絶縁膜 173 と、酸化物半導体膜 142b とを、順に積層するように形成する。

【0279】

なお、後に形成されるトランジスタ 121 の、電気的特性のばらつきを抑えるためには、酸化物半導体膜 142b の表面は高い平坦性を有していることが望ましい。そして、酸化物半導体膜 142b の平坦性を高めるためには、絶縁膜 173 の表面が高い平坦性が確保していることが望ましい。しかし、絶縁膜 173 と酸化物半導体膜 142b の界面近傍に水素などの不純物が混入するのを防ぐためには、絶縁膜 173 を形成した後、絶縁膜 173 を大気にさらすことなく、連続的に酸化物半導体膜 142b を形成することが望ましい。よって、本実施の形態のように、絶縁膜 173 の下に位置する絶縁膜 119 の表面に平坦化処理を施しておくことにより、絶縁膜 173 の表面に平坦化処理を施さなくとも、絶縁膜 173 の表面の平坦性を確保することができる。そして、絶縁膜 173 の表面の平坦性を確保しつつ、絶縁膜 173 と酸化物半導体膜 142b の連続成膜を実現することができる。

30

【0280】

絶縁膜 119 の平坦化処理は、化学的機械研磨法 (Chemical Mechanical Polishing: CMP 法)、液体ジェット研磨法等の研磨処理、ドライエッティング又はウェットエッティング等のエッティング処理、または研磨処理とエッティング処理を組み合わせて行うことができる。

40

【0281】

本実施の形態では、CMP 法を用いて、絶縁膜 119 に平坦化処理を施す場合について説明する。絶縁膜 119 の平坦化処理は、例えば、ポリウレタン地の研磨布を用い、スラリーはシリカ系スラリー (粒径 60 nm)、スラリー流量 100 ml/min 以上 500 ml/min 以下、研磨圧 0.005 MPa 以上 0.08 MPa 以下、スピンドル回転数 20 rpm 以上 50 rpm 以下、テーブル回転数 20 rpm 以上 50 rpm 以下で行うこと

50

ができる。

#### 【0282】

本実施の形態では、上記C M P法による研磨後の絶縁膜119の膜厚を、300nmとする。

#### 【0283】

また、絶縁膜173は、スパッタ法、CVD法等により形成する。絶縁膜173は、熱が与えられることにより酸素が脱離する絶縁膜であることが好ましい。熱が与えられることにより酸素が脱離する絶縁膜としては、化学量論的組成比を満たす酸素よりも多くの酸素を含む絶縁膜を用いることが好ましい。熱が与えられることにより酸素が脱離する絶縁膜は、加熱処理の際に、酸素が脱離することにより、後に形成される酸化物半導体膜に酸素を拡散（又は供給）させることができる。絶縁膜173として、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム等を用いることができる。スパッタ法を用いて絶縁膜173を形成することにより、熱が与えられることにより酸素が脱離しやすい絶縁膜とすることができるため、好ましい。絶縁膜173は、単数の絶縁膜で構成されていても良いし、積層された複数の絶縁膜で構成されていても良い。

10

#### 【0284】

絶縁膜173は、50nm以上800nm以下、好ましくは200nm以上500nm以下とする。絶縁膜173を厚く形成することで、絶縁膜173から放出される酸素の量を増加させることができると共に、絶縁膜173及び後に形成される酸化物半導体膜142bとの界面における界面準位を低減することができる。

20

#### 【0285】

本実施の形態では、スパッタ法を用いて形成した、膜厚200nmの酸化シリコン膜を、絶縁膜173として用いる。絶縁膜173をスパッタ法により形成する場合は、成膜ガスとして、酸素ガス、又は酸素及び希ガスの混合ガス等を用いることができる。また、成膜ガス中の酸素量を高くすることにより、絶縁膜173に含まれる酸素の量を増加させることができると共に、好ましい。代表的には、成膜ガス中の酸素濃度を6%以上100%以下にするといい。

#### 【0286】

絶縁膜173として、酸化シリコン膜を形成する場合、石英（好ましくは合成石英）をターゲットに用い、基板温度30以上450以下（好ましくは70以上200以下）、ターゲットと基板の間の距離（T-S間距離）を20mm以上400mm以下（好ましくは40mm以上200mm以下）、圧力を0.1Pa以上4Pa以下（好ましくは0.2Pa以上1.2Pa以下）、高周波電源を0.5kW以上12kW以下（好ましくは1kW以上5kW以下）、成膜ガス中のO<sub>2</sub>/（O<sub>2</sub>+Ar）割合を1%以上100%以下（好ましくは6%以上100%以下）として、RFスパッタ法を用いることができる。なお、石英（好ましくは合成石英）ターゲットに代えてシリコンターゲットを用いることもできる。なお、成膜ガスとしては、酸素のみを用いてよい。

30

#### 【0287】

上記酸化物半導体膜142bの膜厚は、2nm以上200nm以下、好ましくは3nm以上50nm以下、更に好ましくは3nm以上20nm以下とする。酸化物半導体膜は、酸化物半導体をターゲットとして用い、スパッタ法により成膜する。また、酸化物半導体膜は、希ガス（例えばアルゴン）雰囲気下、酸素雰囲気下、又は希ガス（例えばアルゴン）及び酸素混合雰囲気下においてスパッタ法により形成することができる。

40

#### 【0288】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、絶縁膜173の表面に付着している塵埃を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてよい。また、

50

アルゴン雰囲気に酸素、亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、四フッ化炭素などを加えた雰囲気で行ってもよい。

#### 【0289】

酸化物半導体膜には、上述したような材料を用いることができる。本実施の形態では、In (インジウム)、Ga (ガリウム)、及びZn (亜鉛)を含むターゲットを用いたスパッタ法により得られる膜厚20nmのIn-Ga-Zn系酸化物半導体の薄膜を、酸化物半導体膜として用いる。上記ターゲットとして、例えば、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol数比] の組成比を有するターゲットを用いる。また、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 2 [mol数比] の組成比を有するターゲット、またはIn<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 4 [mol数比] を有するターゲットを用いることができる。また、In、Ga、及びZnを含むターゲットの充填率は90%以上100%以下、好ましくは95%以上100%未満である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

#### 【0290】

なお、酸化物半導体としてIn-Zn系酸化物半導体の材料を用いる場合、用いるターゲットの組成比は、原子数比で、In : Zn = 50 : 1 ~ 1 : 2 (モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 25 : 1 ~ 1 : 4)、好ましくはIn : Zn = 20 : 1 ~ 1 : 1 (モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 10 : 1 ~ 1 : 2)、さらに好ましくはIn : Zn = 1.5 : 1 ~ 1.5 : 1 (モル数比に換算するとIn<sub>2</sub>O<sub>3</sub> : ZnO = 3 : 4 ~ 1.5 : 2)とする。例えば、In-Zn系酸化物半導体の形成に用いるターゲットは、原子数比がIn : Zn : O = X : Y : Zのとき、Z > 1.5X + Yとする。Znの比率を上記範囲に收めることで、移動度の向上を実現することができる。

#### 【0291】

また、酸化物半導体としてIn-Sn-Zn系酸化物半導体の材料を用いる場合、用いるターゲットの組成比は、In : Sn : Znの原子数比を、1 : 2 : 2、2 : 1 : 3、1 : 1 : 1、または4 : 9 : 7とすれば良い。

#### 【0292】

本実施の形態では、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて酸化物半導体膜を成膜する。成膜時に、基板温度を100以上600以下、好ましくは200以上400以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて処理室を排気すると、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該処理室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。