(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6907984号

(P6907984)

(45) 発行日 令和3年7月21日(2021.7.21)

(24) 登録日 令和3年7月5日(2021.7.5)

|                       |               |

|-----------------------|---------------|

| (51) Int.Cl.          | F 1           |

| HO3K 17/00 (2006.01)  | HO3K 17/00 B  |

| HO3K 17/08 (2006.01)  | HO3K 17/08 C  |

| HO3K 17/687 (2006.01) | HO3K 17/687 A |

| HO2J 7/00 (2006.01)   | HO2J 7/00 S   |

請求項の数 6 (全 22 頁)

(21) 出願番号 特願2018-56897 (P2018-56897)

(22) 出願日 平成30年3月23日 (2018.3.23)

(65) 公開番号 特開2019-169873 (P2019-169873A)

(43) 公開日 令和1年10月3日 (2019.10.3)

審査請求日 令和2年6月18日 (2020.6.18)

(73) 特許権者 395011665

株式会社オートネットワーク技術研究所

三重県四日市市西末広町1番14号

(73) 特許権者 000183406

住友電装株式会社

三重県四日市市西末広町1番14号

(73) 特許権者 000002130

住友電気工業株式会社

大阪府大阪市中央区北浜四丁目5番33号

(74) 代理人 100114557

弁理士 河野 英仁

(74) 代理人 100078868

弁理士 河野 登夫

最終頁に続く

(54) 【発明の名称】制御装置、制御方法及びコンピュータプログラム

## (57) 【特許請求の範囲】

## 【請求項1】

直列に接続された第1スイッチ及び第1抵抗を有する第1直列回路と、

直列に接続された第2スイッチ及び第2抵抗を有し、前記第1直列回路に並列に接続される第2直列回路と、

前記第1スイッチ及び第2スイッチのオンへの切替えを指示する指示部と、

前記第1抵抗の両端間の電圧値に比例する電圧値を出力する電圧出力回路と、

前記第1スイッチ、第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知する検知部と

を備え、

前記電圧出力回路が出力する電圧値は、前記第1抵抗の両端間の電圧値が上昇した場合に上昇し、

前記検知部は、

前記指示部が前記第1スイッチ及び第2スイッチのオンへの切替えを指示している場合にて、前記電圧出力回路が出力した電圧値が第1閾値未満であるとき、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知し、

前記指示部が前記第1スイッチ及び第2スイッチのオンへの切替えを指示している場合にて、前記電圧出力回路が出力した電圧値が第2閾値以上であるとき、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知し、

前記第1閾値は前記第2閾値未満である

10

20

制御装置。

**【請求項 2】**

前記第1スイッチ及び第1抵抗間の接続ノードの電圧値を検出する電圧検出回路を備え、

前記検知部は、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知した場合に、前記電圧検出回路が検出した電圧値に基づいて、前記第1スイッチでの故障の発生を検知する

請求項1に記載の制御装置。

**【請求項 3】**

前記第2スイッチ及び第2抵抗間の接続ノードの電圧値を検出する第2の電圧検出回路を備え、

10

前記検知部は、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知した場合に、前記第2の電圧検出回路が検出した電圧値に基づいて、前記第2スイッチでの故障の発生を検知する

請求項1又は請求項2に記載の制御装置。

**【請求項 4】**

電流は、前記第1スイッチ及び第1抵抗の順に流れ、

前記電圧出力回路は、

前記第1スイッチ及び第1抵抗間の接続ノードから電流を引き込み、引き込んだ電流を出力する電流出力部と、

20

前記電流出力部が出力した電流が流れる電流抵抗と

を有し、

前記電圧出力回路は、前記電流抵抗の両端間の電圧値を出力する

請求項1から請求項3のいずれか1つに記載の制御装置。

**【請求項 5】**

第1抵抗に直列に接続される第1スイッチ、及び、第2抵抗に直列に接続される第2スイッチのオンへの切替えを指示するステップと、

前記第1抵抗の両端間の電圧値に比例する電圧値を取得するステップと、

前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第1閾値未満であるとき、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップと、

30

前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第2閾値以上であるとき、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップと

を含み、

前記第1スイッチ及び第1抵抗を有する第1直列回路は、前記第2スイッチ及び第2抵抗を有する第2直列回路に並列に接続され、

取得する電圧値は、前記第1抵抗の両端間の電圧値が上昇した場合に上昇し、

前記第1閾値は前記第2閾値未満である

制御方法。

40

**【請求項 6】**

コンピュータに、

第1抵抗に直列に接続される第1スイッチ、及び、第2抵抗に直列に接続される第2スイッチのオンへの切替えを指示するステップと、

前記第1抵抗の両端間の電圧値に比例する電圧値を取得するステップと、

前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第1閾値未満であるとき、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップと、

前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第2閾値以上であるとき、前記第2スイッチ、第1抵抗及び第2抵抗中の少

50

なくとも 1 つでの故障の発生を検知するステップと

を実行させるために用いられ、

前記第 1 スイッチ及び第 1 抵抗を有する第 1 直列回路は、前記第 2 スイッチ及び第 2 抵抗を有する第 2 直列回路に並列に接続され、

取得する電圧値は、前記第 1 抵抗の両端間の電圧値が上昇した場合に上昇し、

前記第 1 閾値は前記第 2 閾値未満である

コンピュータプログラム。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、制御装置、制御方法及びコンピュータプログラムに関する。

【背景技術】

【0002】

車両には、バッテリから負荷への給電を制御する制御装置（例えば、特許文献 1 を参照）が搭載されている。特許文献 1 に記載の制御装置では、2つの半導体スイッチ夫々の一端がバッテリの正極に接続されている。2つの半導体スイッチ夫々の他端は負荷の一端に接続されている。バッテリの負極と、負荷の他端とは接地されている。

【0003】

2つの半導体スイッチをオン又はオフに切替える。2つの半導体スイッチがオンである場合、バッテリから負荷に電力が供給される。2つの半導体スイッチがオフである場合、バッテリから負荷への給電が停止する。

20

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特開 2014 - 239293 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献 1において、2つの半導体スイッチ中的一方の半導体スイッチが故障してオフに固定されたと仮定する。この場合において、他方の半導体スイッチがオンに切替わった場合、大きな電流が他方の半導体スイッチを介して流れる。大きな電流が他方の半導体スイッチを介して流れた場合、他方の半導体スイッチで大きな電力が消費される。これにより、他方の半導体スイッチの温度が異常な温度に上昇し、他方の半導体スイッチも故障する可能性がある。

30

【0006】

本発明は斯かる事情に鑑みてなされたものであり、その目的とするところは、スイッチがオフに固定された場合に故障の発生を検知することができる制御装置、制御方法及びコンピュータプログラムを提供することにある。

【課題を解決するための手段】

【0007】

40

本発明の一態様に係る制御装置は、直列に接続された第 1 スイッチ及び第 1 抵抗を有する第 1 直列回路と、直列に接続された第 2 スイッチ及び第 2 抵抗を有し、前記第 1 直列回路に並列に接続される第 2 直列回路と、前記第 1 スイッチ及び第 2 スイッチのオンへの切替えを指示する指示部と、前記第 1 抵抗の両端間の電圧値に比例する電圧値を出力する電圧出力回路と、前記第 1 スイッチ、第 2 スイッチ、第 1 抵抗及び第 2 抵抗中の少なくとも 1 つでの故障の発生を検知する検知部とを備え、前記電圧出力回路が出力する電圧値は、前記第 1 抵抗の両端間の電圧値が上昇した場合に上昇し、前記検知部は、前記指示部が前記第 1 スイッチ及び第 2 スイッチのオンへの切替えを指示している場合にて、前記電圧出力回路が出力した電圧値が第 1 閾値未満であるとき、前記第 1 スイッチ、第 1 抵抗及び第 2 抵抗中の少なくとも 1 つでの故障の発生を検知し、前記指示部が前記第 1 スイッチ及び

50

第2スイッチのオンへの切替えを指示している場合にて、前記電圧出力回路が出力した電圧値が第2閾値以上であるとき、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知し、前記第1閾値は前記第2閾値未満である。

#### 【0008】

本発明の一態様に係る制御方法は、第1抵抗に直列に接続される第1スイッチ、及び、第2抵抗に直列に接続される第2スイッチのオンへの切替えを指示するステップと、前記第1抵抗の両端間の電圧値に比例する電圧値を取得するステップと、前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第1閾値未満であるとき、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップと、前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第2閾値以上であるとき、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップとを含み、前記第1スイッチ及び第1抵抗を有する第1直列回路は、前記第2スイッチ及び第2抵抗を有する第2直列回路に並列に接続され、取得する電圧値は、前記第1抵抗の両端間の電圧値が上昇した場合に上昇し、前記第1閾値は前記第2閾値未満である。10

#### 【0009】

本発明の一態様に係るコンピュータプログラムは、コンピュータに、第1抵抗に直列に接続される第1スイッチ、及び、第2抵抗に直列に接続される第2スイッチのオンへの切替えを指示するステップと、前記第1抵抗の両端間の電圧値に比例する電圧値を取得するステップと、前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第1閾値未満であるとき、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップと、前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値が第2閾値以上であるとき、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップとを実行させるために用いられ、前記第1スイッチ及び第1抵抗を有する第1直列回路は、前記第2スイッチ及び第2抵抗を有する第2直列回路に並列に接続され、取得する電圧値は、前記第1抵抗の両端間の電圧値が上昇した場合に上昇し、前記第1閾値は前記第2閾値未満である。20

#### 【0010】

なお、本発明を、このような特徴的な処理部を備える制御装置として実現することができるだけでなく、かかる特徴的な処理をステップとする制御方法として実現したり、かかるステップをコンピュータに実行させるためのコンピュータプログラムとして実現したりすることができる。また、本発明を、制御装置の一部又は全部を実現する半導体集積回路として実現したり、制御装置を含む電源システムとして実現したりすることができる。30

#### 【発明の効果】

#### 【0011】

上記の態様によれば、スイッチがオフに固定された場合に故障の発生を検知することができる。

#### 【図面の簡単な説明】

#### 【0012】

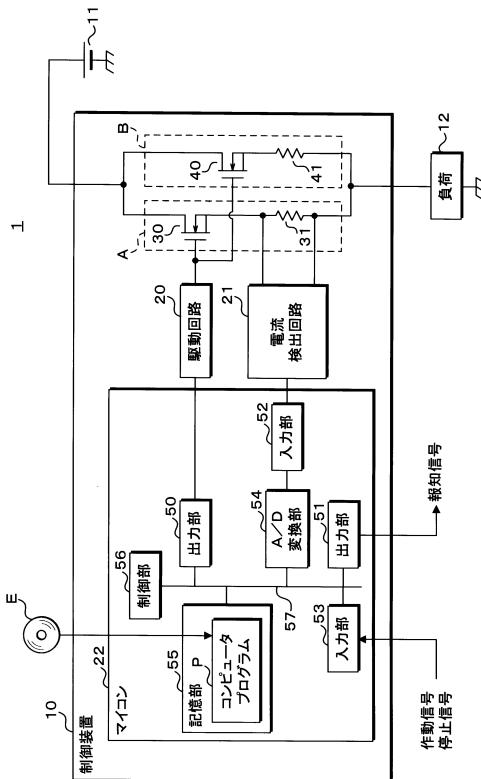

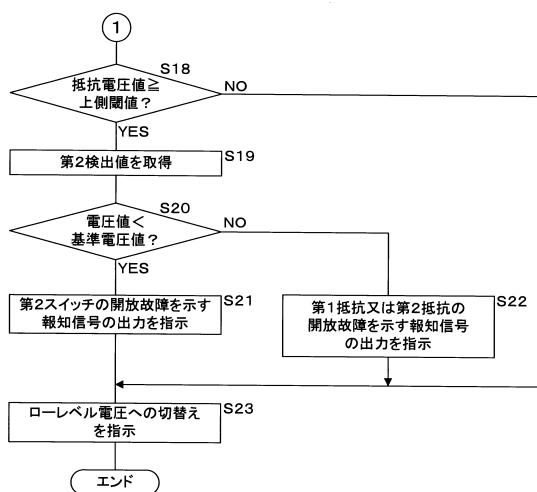

【図1】実施形態1における電源システムの要部構成を示すブロック図である。40

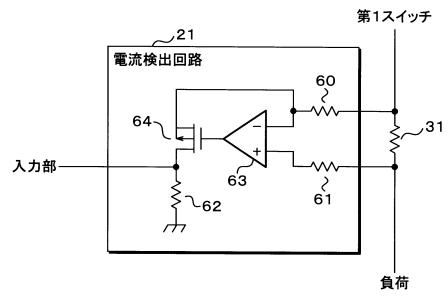

【図2】電流検出回路の回路図である。

【図3】故障によって生じる現象の説明図である。

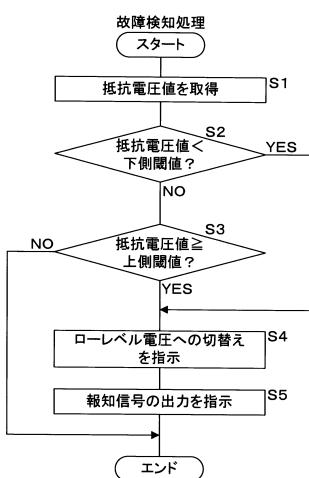

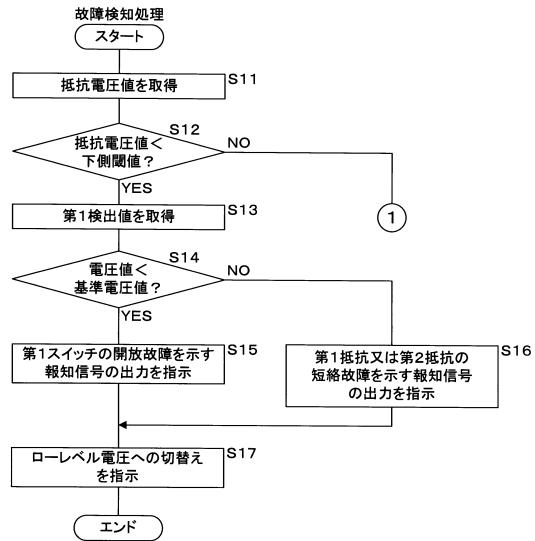

【図4】故障検知処理の手順を示すフローチャートである。

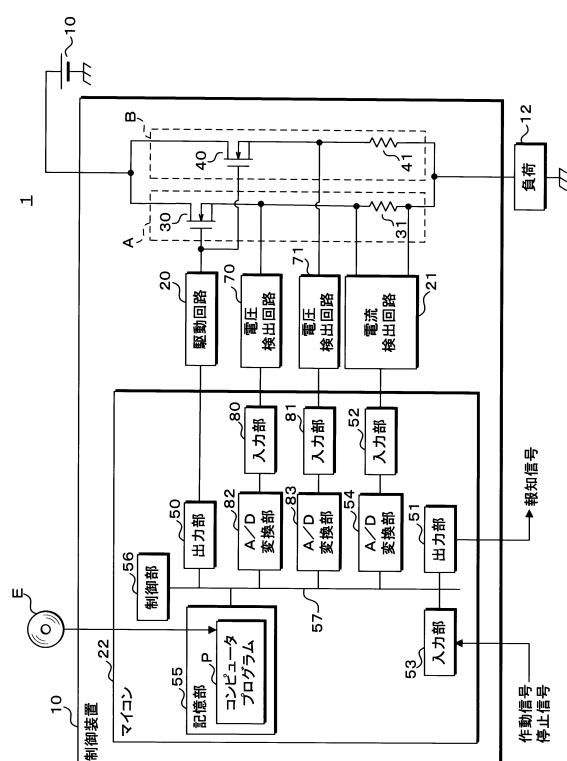

【図5】実施形態2における電源システムの要部構成を示すブロック図である。

【図6】故障によって生じる現象の説明図である。

【図7】故障検知処理の手順を示すフローチャートである。

【図8】故障検知処理の手順を示すフローチャートである。

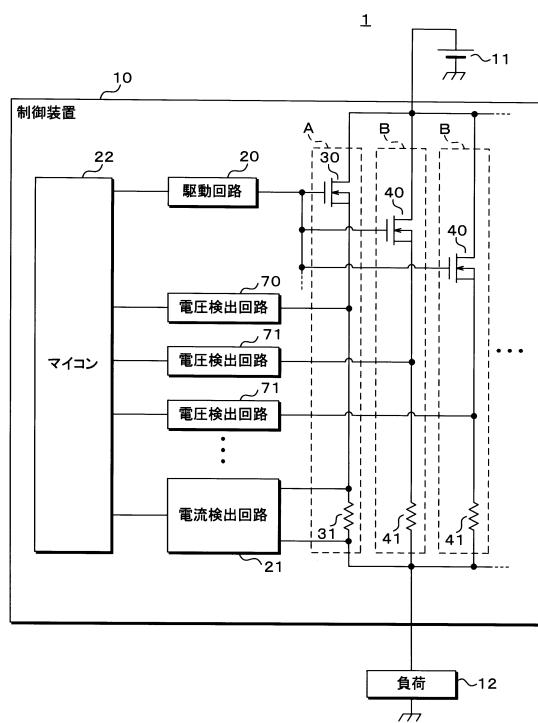

【図9】実施形態3における電源システムの要部構成を示すブロック図である。

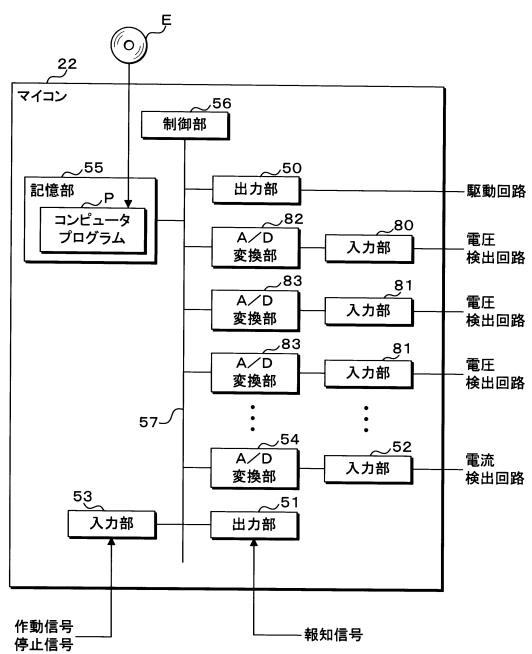

【図10】マイコンの要部構成を示すブロック図である。50

**【発明を実施するための形態】****【0013】****[本発明の実施形態の説明]**

最初に本発明の実施態様を列挙して説明する。以下に記載する実施形態の少なくとも一部を任意に組み合わせてもよい。

**【0014】**

(1) 本発明の一態様に係る制御装置は、直列に接続された第1スイッチ及び第1抵抗を有する第1直列回路と、直列に接続された第2スイッチ及び第2抵抗を有し、前記第1直列回路に並列に接続される第2直列回路と、前記第1スイッチ及び第2スイッチのオンへの切替えを指示する指示部と、前記第1抵抗の両端間の電圧値に応じた電圧値を出力する電圧出力回路と、前記指示部が前記第1スイッチ及び第2スイッチのオンへの切替えを指示している場合にて、前記電圧出力回路が出力した電圧値に基づいて、前記第1スイッチ、第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知する検知部とを備える。10

**【0015】**

(2) 本発明の一態様に係る制御装置では、前記電圧出力回路が出力する電圧値は、前記第1抵抗の両端間の電圧値が上昇した場合に上昇し、前記検知部は、前記電圧出力回路が出力した電圧値が第1閾値未満である場合、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知し、前記電圧出力回路が出力した電圧値が第2閾値以上である場合、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知し、前記第1閾値は前記第2閾値未満である。20

**【0016】**

(3) 本発明の一態様に係る制御装置は、前記第1スイッチ及び第1抵抗間の接続ノードの電圧値を検出する電圧検出回路を備え、前記検知部は、前記第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知した場合に、前記電圧検出回路が検出した電圧値に基づいて、前記第1スイッチでの故障の発生を検知する。

**【0017】**

(4) 本発明の一態様に係る制御装置は、前記第2スイッチ及び第2抵抗間の接続ノードの電圧値を検出する第2の電圧検出回路を備え、前記検知部は、前記第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知した場合に、前記第2の電圧検出回路が検出した電圧値に基づいて、前記第2スイッチでの故障の発生を検知する。30

**【0018】**

(5) 本発明の一態様に係る制御装置では、電流は、前記第1スイッチ及び第1抵抗の順に流れ、前記電圧出力回路は、前記第1スイッチ及び第1抵抗間の接続ノードから電流を引き込み、引き込んだ電流を出力する電流出力部と、前記電流出力部が出力した電流が流れる電流抵抗とを有し、前記電圧出力回路は、前記電流抵抗の両端間の電圧値を出力する。

**【0019】**

(6) 本発明の一態様に係る制御方法は、第1抵抗に直列に接続される第1スイッチ、及び、第2抵抗に直列に接続される第2スイッチのオンへの切替えを指示するステップと、前記第1抵抗の両端間の電圧値に応じた電圧値を取得するステップと、前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場合にて、取得した電圧値に基づいて、前記第1スイッチ、第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップとを含み、前記第1スイッチ及び第1抵抗を有する第1直列回路は、前記第2スイッチ及び第2抵抗を有する第2直列回路に並列に接続されている。40

**【0020】**

(7) 本発明の一態様に係るコンピュータプログラムは、コンピュータに、第1抵抗に直列に接続される第1スイッチ、及び、第2抵抗に直列に接続される第2スイッチのオンへの切替えを指示するステップと、前記第1抵抗の両端間の電圧値に応じた電圧値を取得するステップと、前記第1スイッチ及び第2スイッチへのオンへの切替えを指示している場50

合にて、取得した電圧値に基づいて、前記第1スイッチ、第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知するステップとを実行させるために用いられ、前記第1スイッチ及び第1抵抗を有する第1直列回路は、前記第2スイッチ及び第2抵抗を有する第2直列回路に並列に接続されている。

#### 【0021】

上記の一態様に係る制御装置、制御方法及びコンピュータプログラムにあっては、第1スイッチがオンである場合、第1抵抗の両端間の電圧値は、第1直列回路及び第2直列回路を含む並列回路の両端間の電圧値である。第1スイッチ及び第2スイッチのオンへの切替えを指示している場合において、第2スイッチがオフに固定されているとき、又は、第1抵抗若しくは第2抵抗が開放しているとき、並列回路の抵抗値が大きく、第1抵抗の両端間の電圧値が大きい。10

#### 【0022】

第1スイッチ及び第2スイッチのオンへの切替えを指示している場合において、第1スイッチがオフに固定されているとき、又は、第1抵抗若しくは第2抵抗が短絡しているとき、第1抵抗の両端間の電圧値はゼロVである。電圧出力回路は、第1抵抗の両端間の電圧値に応じた電圧値を出力する。

第1スイッチ又は第2スイッチがオフで固定された場合、電圧出力部が出力した電圧値が大きく変動する。これにより、第1スイッチ、第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生が検知される。20

#### 【0023】

上記の一態様に係る制御装置にあっては、電圧出力部が出力した電圧値は第1閾値未満である場合、第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知する。電圧出力部が出力した電圧値は第2閾値以上である場合、第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知する。

#### 【0024】

上記の一態様に係る制御装置にあっては、第1スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知した場合、第1スイッチ及び第1抵抗間の接続ノードの電圧値に基づいて、第1スイッチでの故障の発生を検知する。

#### 【0025】

上記の一態様に係る制御装置にあっては、第2スイッチ、第1抵抗及び第2抵抗中の少なくとも1つでの故障の発生を検知した場合、第2スイッチ及び第2抵抗間の接続ノードの電圧値に基づいて、第2スイッチでの故障の発生を検知する。30

#### 【0026】

上記の一態様に係る制御装置にあっては、電圧出力回路では、第1スイッチがオンである場合のみ、電流抵抗に電流が流れ電力が消費される。結果、消費電力が低い。

#### 【0027】

##### [本発明の実施形態の詳細]

本発明の実施形態に係る電源システムの具体例を、以下に図面を参照しつつ説明する。なお、本発明はこれらの例示に限定されるものではなく、特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。40

#### 【0028】

##### (実施形態1)

図1は、実施形態1における電源システム1の要部構成を示すブロック図である。電源システム1は、車両に好適に搭載されており、制御装置10、バッテリ11及び負荷12を備える。制御装置10は、バッテリ11の正極と、負荷12の一端とに接続されている。バッテリ11の負極と、負荷12の他端とは接地されている。

#### 【0029】

負荷12は、車両に搭載される電気機器である。負荷12に電力が供給されている場合、負荷12は作動する。負荷12への給電が停止した場合、負荷12は動作を停止する。50

**【0030】**

制御装置10には、負荷12の作動を指示する作動信号と、負荷12の動作の停止を指示する停止信号とが入力される。制御装置10は、作動信号が入力された場合、バッテリ11の正極と、負荷12の一端とを電気的に接続する。これにより、バッテリ11は、制御装置10を介して負荷12に電力を供給する。

**【0031】**

制御装置10は、停止信号が入力された場合、バッテリ11及び負荷12間の電気的な接続を遮断する。これにより、バッテリ11から負荷12への給電が停止し、負荷12は動作を停止する。

以上のように、制御装置10は、バッテリ11及び負荷12の電気的な接続と、この電気的な接続の遮断とを行うことによって、バッテリ11から負荷12への給電を制御する。

10

**【0032】**

また、制御装置10内で故障が発生した場合、制御装置10は、故障の発生を検知し、故障の発生を報知する報知信号を図示しない装置に出力する。これにより、例えば、車両内において、ランプの点灯又はメッセージの表示等が行われ、車両の乗員に故障の発生が報知される。

**【0033】**

制御装置10は、駆動回路20、電流検出回路21、マイクロコンピュータ（以下、マイコンという）22、第1直列回路A及び第2直列回路Bを有する。マイコン22は、出力部50, 51、入力部52, 53、A/D変換部54、記憶部55及び制御部56を有する。第1直列回路Aは、第1スイッチ30及び第1抵抗31を有する。第2直列回路Bは、第2スイッチ40及び第2抵抗41を有する。第1スイッチ30及び第2スイッチ40夫々は、Nチャネル型のFET(Field Effect Transistor)である。第1抵抗31として、抵抗素子、又は、基板上に形成されたパターン（導道）の抵抗等が用いられる。同様に、第2抵抗41として、抵抗素子、又は、基板上に形成されたパターンの抵抗等が用いられる。

20

**【0034】**

第2直列回路Bは第1直列回路Aに並列に接続されている。第1直列回路Aでは、第1スイッチ30及び第1抵抗31が直列に接続されている。具体的には、第1スイッチ30のソースが第1抵抗31の一端に接続されている。第2直列回路Bでは、第2スイッチ40が第2抵抗41に直列に接続されている。具体的には、第2スイッチ40のソースが第2抵抗41の一端に接続されている。第1スイッチ30及び第2スイッチ40のドレインはバッテリ11の正極に接続されている。第1抵抗31及び第2抵抗41夫々の他端は、負荷12の一端に接続されている。

30

**【0035】**

第1スイッチ30及び第2スイッチ40のゲートは、駆動回路20の出力端に接続されている。駆動回路20の入力端は、マイコン22の出力部50に接続されている。第1抵抗31の両端は電流検出回路21に接続されている。電流検出回路21は、更に、マイコン22の入力部52に接続されている。マイコン22内では、入力部52は、更に、A/D変換部54に接続されている。出力部50, 51、入力部53、A/D変換部54、記憶部55及び制御部56は内部バス57に接続されている。

40

**【0036】**

第1スイッチ30及び第2スイッチ40夫々について、ソースの電位を基準としたゲートの電圧値が一定のオン閾値以上である場合、電流がドレイン及びソースを介して流れることが可能である。このとき、第1スイッチ30及び第2スイッチ40夫々はオンである。また、ソースの電位を基準としたゲートの電圧が一定のオフ閾値未満である場合、電流がドレイン及びソースを介して流れることはない。このとき、第1スイッチ30及び第2スイッチ40夫々はオフである。第1スイッチ30及び第2スイッチ40夫々について、オン閾値は、オフ閾値を超えている。

50

**【 0 0 3 7 】**

出力部 5 0 は、駆動回路 2 0 にハイレベル電圧又はローレベル電圧を出力している。出力部 5 0 は、制御部 5 6 の指示に従って、駆動回路 2 0 に出力している電圧をハイレベル電圧又はローレベル電圧に切替える。駆動回路 2 0 は、出力部 5 0 から入力されている電圧がローレベル電圧からハイレベル電圧に切替わった場合、接地電位を基準とした第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 のゲートの電圧値を上昇させる。

**【 0 0 3 8 】**

これにより、第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 夫々では、ソースの電位を基準としたゲートの電圧値がオン閾値以上となり、第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 はオンに切替わる。第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 がオンに切替わった場合、バッテリ 1 1 の正極と負荷 1 2 の一端とが電気的に接続され、バッテリ 1 1 から負荷 1 2 に電力が供給され、負荷 1 2 は作動する。10

**【 0 0 3 9 】**

このとき、第 1 直列回路 A では、電流が第 1 スイッチ 3 0 及び第 1 抵抗 3 1 の順に流れ、第 2 直列回路 B では、電流が第 2 スイッチ 4 0 及び第 2 抵抗 4 1 の順に流れれる。

**【 0 0 4 0 】**

なお、第 1 抵抗 3 1 及び第 2 抵抗 4 1 の抵抗値は一致していることが好ましい。この場合、第 1 直列回路 A 及び第 2 直列回路 B を流れる電流の電流値が略一致し、第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 の劣化の速度が略一致する。第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 の一方が急速に劣化することが防止される。20

**【 0 0 4 1 】**

駆動回路 2 0 は、出力部 5 0 から入力されている電圧がハイレベル電圧からローレベル電圧に切替わった場合、接地電位を基準とした第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 のゲートの電圧値を低下させる。これにより、第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 夫々では、ソースの電位を基準としたゲートの電圧値がオフ閾値未満となり、第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 はオフに切替わる。

**【 0 0 4 2 】**

以上のように、駆動回路 2 0 は、接地電位を基準とした第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 のゲートの電圧値を調整することによって、第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 をオン又はオフに切替える。30

**【 0 0 4 3 】**

第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 がオフに切替わった場合、バッテリ 1 1 及び負荷 1 2 間の電気的な接続が遮断され、負荷 1 2 は動作を停止する。このとき、第 1 直列回路 A 及び第 2 直列回路 B では、電流は流れることはない。

**【 0 0 4 4 】**

以下では、第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 がオンである場合、ドレイン及びソース間の抵抗値はゼロオームであるとみなす。また、第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 がオフである場合、ドレイン及びソース間の抵抗値は無限大であるとみなす。

**【 0 0 4 5 】**

電流検出回路 2 1 は、第 1 抵抗 3 1 の両端間の電圧値に比例するアナログの電圧値をマイコン 2 2 の入力部 5 2 に出力する。以下では、電流検出回路 2 1 が出力する電圧値を抵抗電圧値と記載する。40

**【 0 0 4 6 】**

図 2 は電流検出回路 2 1 の回路図である。電流検出回路 2 1 は、回路抵抗 6 0 , 6 1 , 6 2 、差動增幅器 6 3 、P チャネル型の F E T 6 4 を有する。差動增幅器 6 3 は、所謂オペアンプであり、プラス端、マイナス端及び出力端を有する。

**【 0 0 4 7 】**

回路抵抗 6 0 の一端は、第 1 抵抗 3 1 の第 1 スイッチ 3 0 側の一端に接続されている。回路抵抗 6 1 の一端は、第 1 抵抗 3 1 の負荷 1 2 側の一端に接続されている。回路抵抗 6 0 , 6 1 夫々の他端は、差動增幅器 6 3 のプラス端及びマイナス端に接続されている。回50

路抵抗 6 0 の他端は、更に、FET 6 4 のソースに接続されている。差動増幅器 6 3 の出力端は FET 6 4 のゲートに接続されている。FET 6 4 のドレインは、マイコン 2 2 の入力部 5 2 と、回路抵抗 6 2 の一端とに接続されている。回路抵抗 6 2 の他端は接地されている。

#### 【0048】

FET 6 4 は可変抵抗器として機能する。FET 6 4 では、ドレイン及びソースを介して電流が流れる。FET 6 4 について、ソースの電位を基準としたゲートの電圧値が低い程、ドレイン及びソース間の抵抗値が小さい。第 1 スイッチ 3 0 がオンである場合、電流が、バッテリ 1 1 の正極から、第 1 スイッチ 3 0 、回路抵抗 6 0 、FET 6 4 及び回路抵抗 6 2 の順に流れる。回路抵抗 6 2 に流れる電流の電流値は、FET 6 4 のドレイン及びソース間の抵抗値が小さい程、大きい。回路抵抗 6 2 の両端間の電圧値が抵抗電圧値としてマイコン 2 2 の入力部 5 2 に出力される。回路抵抗 6 2 の両端間の電圧値は、回路抵抗 6 2 を流れる電流の電流値が大きい程、大きい。10

#### 【0049】

以上のように、電流検出回路 2 1 では、FET 6 4 は、第 1 スイッチ 3 0 及び第 1 抵抗 3 1 間の接続ノードから電流を引き込み、引き込んだ電流を出力する。FET 6 4 が出力した電流は回路抵抗 6 2 を流れる。電流検出回路 2 1 、FET 6 4 及び回路抵抗 6 2 夫々は、電圧出力回路、電流出力部及び電流抵抗として機能する。

#### 【0050】

差動増幅器 6 3 は、接地電位を基準とした FET 6 4 のゲートの電圧値を調整する。差動増幅器 6 3 は、第 1 抵抗 3 1 の両端間の電圧値が大きい程、接地電位を基準とした FET 6 4 のゲートの電圧値を低下させる。FET 6 4 において、接地電位を基準としたゲートの電圧値が低い程、ソースの電位を基準としたゲートの電圧値も低い。前述したように、FET 6 4 において、ソース電位を基準としたゲートの電圧値が低い程、ドレイン及びソース間の抵抗値が小さい。20

#### 【0051】

第 1 スイッチ 3 0 がオンである場合において、第 1 抵抗 3 1 の両端間の電圧値が上昇したとき、差動増幅器 6 3 が FET 6 4 のゲートの電圧値を低下させる。これにより、FET 6 4 のドレイン及びソース間の抵抗値が低下し、回路抵抗 6 2 を流れる電流の電流値が上昇する。結果、回路抵抗 6 2 の両端間の電圧値が上昇する。同様の場合において、第 1 抵抗 3 1 の両端間の電圧値が低下したとき、差動増幅器 6 3 が FET 6 4 のゲートの電圧値を上昇させる。これにより、FET 6 4 のドレイン及びソース間の抵抗値が上昇し、回路抵抗 6 2 を流れる電流の電流値が低下する。結果、回路抵抗 6 2 の両端間の電圧値が低下する。30

#### 【0052】

回路抵抗 6 0 , 6 2 夫々の抵抗値を  $r_{60}$  ,  $r_{62}$  と記載する。第 1 抵抗 3 1 の両端間の電圧値を  $V_{31}$  と記載する。抵抗電圧値、即ち、回路抵抗 6 2 の両端間の電圧値を  $V_{62}$  と記載する。抵抗電圧値  $V_{62}$  は、下記の(1)式で表される。「・」は積を表す。

$$V_{62} = V_{31} \cdot r_{62} / r_{60} \cdots (1)$$

従って、抵抗電圧値  $V_{62}$  は、第 1 抵抗 3 1 の両端間の電圧値  $V_{31}$  に比例する。第 1 抵抗 3 1 の両端間の電圧値  $V_{31}$  が上昇した場合、抵抗電圧値  $V_{62}$  は上昇する。40

#### 【0053】

負荷 1 2 に流れる電流の電流値を  $I_t$  と記載する。第 1 直列回路 A 及び第 2 直列回路 B の並列回路の合成抵抗値を  $r_s$  と記載する。この場合、第 1 抵抗 3 1 の両端間の電圧値  $V_{31}$  は、下記の(2)式で表される。

$$V_{31} = r_s \cdot I_t \cdots (2)$$

#### 【0054】

(1)式及び(2)式より、電圧値  $V_{31}$  を消去した場合、電流値  $I_t$  は、下記の(3)式で表される。

$$I_t = V_{62} \cdot r_{60} / (r_s \cdot r_{62}) \cdots (3)$$

**【 0 0 5 5 】**

第1抵抗31に電流が流れていらない場合、又は、第1抵抗31の両端が短絡した場合、第1抵抗31の両端間の電圧値V31はゼロVである。(1)式に示すように、第1抵抗31の両端間の電圧値V31がゼロVである場合、抵抗電圧値V62はゼロVである。

**【 0 0 5 6 】**

第1スイッチ30がオフである場合、第1抵抗31及び回路抵抗62に電流が流れず、電流検出回路21で電力が消費されることはない。電流検出回路21では、第1スイッチ30がオンである場合のみ、回路抵抗62に電流が流れ電力が消費される。このため、制御装置10の消費電力が低い。

**【 0 0 5 7 】**

10

電流検出回路21からマイコン22の入力部52に、アナログの抵抗電圧値が入力される。入力部52は、入力されたアナログの抵抗電圧値をA/D変換部54に出力する。A/D変換部54は、入力部52から入力されたアナログの抵抗電圧値を、デジタルの抵抗電圧値に変換する。制御部56は、A/D変換部54からデジタルの抵抗電圧値を取得する。

**【 0 0 5 8 】**

出力部51は、制御部56の指示に従って報知信号を図示しない装置に出力する。

入力部53には、作動信号及び停止信号が入力される。入力部53は、作動信号又は停止信号が入力された場合、入力された信号を制御部56に通知する。

**【 0 0 5 9 】**

20

記憶部55は不揮発性メモリである。記憶部55には、コンピュータプログラムPが記憶されている。制御部56は、一又は複数のCPU(Central Processing Unit)を有する。制御部56が有する一又は複数のCPUは、コンピュータプログラムPを実行することによって、作動処理、停止処理、保護処理及び故障検知処理を実行する。作動処理は、負荷12を作動させる処理である。停止処理は、負荷12の動作を停止する処理である。保護処理は、負荷12を過電流から保護する処理である。故障検知処理は、故障の発生を検知する処理である。コンピュータプログラムPは、制御部56が有する一又は複数のCPUに作動処理、停止処理、保護処理及び故障検知処理を実行させるために用いられる。

**【 0 0 6 0 】**

30

なお、コンピュータプログラムPは、制御部56が有する一又は複数のCPUが読み取り可能に、記憶媒体Eに記憶されていてもよい。この場合、図示しない読み出し装置によって記憶媒体Eから読み出されたコンピュータプログラムPが記憶部55に記憶される。記憶媒体Eは、光ディスク、フレキシブルディスク、磁気ディスク、磁気光ディスク又は半導体メモリ等である。光ディスクは、CD(Compact Disc)-ROM(Read Only Memory)、DVD(Digital Versatile Disc)-ROM、又は、BD(Blu-ray(登録商標)Disc)等である。磁気ディスクは、例えばハードディスクである。また、図示しない通信網に接続されている図示しない外部装置からコンピュータプログラムPをダウンロードし、ダウンロードしたコンピュータプログラムPを記憶部55に記憶してもよい。

**【 0 0 6 1 】**

40

制御部56は、入力部53に作動信号が入力された場合、作動処理を実行する。作動処理では、制御部56は、出力部50にハイレベル電圧への切替えを指示する。これにより、出力部50は、駆動回路20に出力している電圧をハイレベル電圧に切替え、駆動回路20は第1スイッチ30及び第2スイッチ40をオンに切替える。従って、出力部50にハイレベル電圧への切替えを指示することは、駆動回路20に第1スイッチ30及び第2スイッチ40のオンへの切替えを指示することに相当する。制御部56は指示部として機能する。

**【 0 0 6 2 】**

第1スイッチ30及び第2スイッチ40がオンに切替わった場合、バッテリ11から負荷12に電力が供給され、負荷12が作動する。制御部56は、出力部50にハイレベル電圧への切替えを指示した後、作動処理を終了する。

50

**【0063】**

制御部56は、入力部53に停止信号が入力された場合、停止処理を実行する。停止処理では、制御部56は、出力部50にローレベル電圧への切替えを指示する。これにより、出力部50は、駆動回路20に出力している電圧をローレベル電圧に切替え、駆動回路20は第1スイッチ30及び第2スイッチ40をオフに切替える。

**【0064】**

従って、出力部50にローレベル電圧への切替えを指示することは、駆動回路20に第1スイッチ30及び第2スイッチ40のオフへの切替えを指示することに相当する。第1スイッチ30及び第2スイッチ40がオフに切替わった場合、バッテリ11から負荷12への給電が停止し、負荷12が動作を停止する。制御部56は、出力部50にローレベル電圧への切替えを指示した後、停止処理を終了する。10

**【0065】**

制御部56は、出力部50にハイレベル電圧への切替えを指示している場合、即ち、駆動回路20に第1スイッチ30及び第2スイッチ40のオンへの切替えを指示している場合において、保護処理を周期的に実行する。保護処理では、制御部56は、A/D変換部54から抵抗電圧値を取得し、取得した抵抗電圧値を(3)式に代入することによって、負荷12に流れる電流の電流値を算出する。制御部56は、算出した電流値が所定電流値以上であるか否かを判定する。

**【0066】**

制御部56は、算出した電流値が所定電流値以上であると判定した場合、出力部50にローレベル電圧への切替えを指示する。これにより、出力部50は、駆動回路20に出力している電圧をローレベル電圧に切替え、駆動回路20は第1スイッチ30及び第2スイッチ40をオフに切替える。結果、負荷12に過電流が流れることが防止される。その後、制御部56は保護処理を終了する。制御部56は、算出した電流値が所定電流値未満であると判定した場合も保護処理を終了する。20

**【0067】**

制御部56は、出力部50にハイレベル電圧への切替えを指示している場合、即ち、駆動回路20に第1スイッチ30及び第2スイッチ40のオンへの切替えを指示している場合において、故障検知処理を周期的に実行する。故障検知処理では、制御部56は、電流検出回路21から入力部52に出力された抵抗電圧値に基づいて、第1スイッチ30、第1抵抗31、第2スイッチ40及び第2抵抗41中の少なくとも1つでの故障の発生を検知する。30

**【0068】**

図3は、故障によって生じる現象の説明図である。以下では、スイッチがオフに固定される故障、又は、抵抗の両端が開放される故障を開放故障と記載する。抵抗の両端が短絡される故障を短絡故障と記載する。抵抗電圧値に係る閾値として、下側閾値及び上側閾値が設定されている。下側閾値は、上側閾値未満であり、ゼロを超える。

**【0069】**

前述したように、制御部56は、駆動回路20に第1スイッチ30及び第2スイッチ40のオンへの切替えを指示している状態で故障検知処理を実行する。第1スイッチ30で開放故障が発生した場合、第1抵抗31を電流が流れることはない。このため、第1抵抗31の両端間の電圧値はゼロVであり、抵抗電圧値はゼロVである。更に、第1抵抗31又は第2抵抗41で短絡故障が発生した場合、バッテリ11から負荷12に電流が流れ。しかしながら、第1抵抗31の両端間で電圧降下が発生しないため、第1抵抗31の両端間の電圧値はゼロVであり、抵抗電圧値はゼロVである。40

**【0070】**

以上のように、第1スイッチ30で開放故障が発生した場合、又は、第1抵抗31若しくは第2抵抗41で短絡故障が発生した場合、抵抗電圧値は、ゼロVであり、下側閾値未満である。

**【0071】**

10

20

30

40

50

バッテリ 1 1 の出力電圧値（以下、バッテリ電圧値という）を  $V_b$  と記載する。第 2 抵抗 4 1 が第 1 抵抗 3 1 に並列に接続されている並列回路の合成抵抗値を  $r_p$  と記載する。負荷 1 2 の抵抗値を  $r_{12}$  と記載する。前述したように、制御部 5 6 は、駆動回路 2 0 に第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 のオンへの切替えを指示している。従って、第 1 抵抗 3 1 の両端間の抵抗値は、通常、第 2 抵抗 4 1 が第 1 抵抗 3 1 に並列に接続されている並列回路の合成抵抗値である。この場合、第 1 抵抗 3 1 の両端間の電圧値  $V_{31}$  は、 $V_b \cdot r_p / (r_p + r_{12})$  で表される。

#### 【 0 0 7 2 】

第 1 抵抗 3 1 の抵抗値を  $r_{31}$  と記載する。第 2 スイッチ 4 0 又は第 2 抵抗 4 1 で開放故障が発生した場合、第 1 抵抗 3 1 の両端間の抵抗値は、第 1 抵抗 3 1 の抵抗値  $r_{31}$  である。この場合、第 1 抵抗 3 1 の両端間の電圧値  $V_{31}$  は、 $V_b \cdot r_{31} / (r_{12} + r_{31})$  で表される。抵抗値  $r_{31}$  は抵抗値  $r_p$  を超えている。このため、 $V_b \cdot r_{31} / (r_{12} + r_{31})$  は  $V_b \cdot r_p / (r_p + r_{12})$  を超えている。

#### 【 0 0 7 3 】

第 2 抵抗 4 1 の抵抗値を  $r_{41}$  と記載する。第 1 抵抗 3 1 で開放故障が発生した場合、第 1 抵抗 3 1 の両端間の抵抗値は、第 2 抵抗 4 1 の抵抗値  $r_{41}$  である。この場合、第 1 抵抗 3 1 の両端間の電圧値  $V_{31}$  は、 $V_b \cdot r_{41} / (r_{12} + r_{41})$  で表される。抵抗値  $r_{41}$  は抵抗値  $r_p$  を超えている。このため、 $V_b \cdot r_{41} / (r_{12} + r_{41})$  は  $V_b \cdot r_p / (r_p + r_{12})$  を超えている。

抵抗電圧値  $V_{62}$  は、(1) 式に示すように、第 1 抵抗 3 1 の両端間の電圧値  $V_{31}$  に比例する。

#### 【 0 0 7 4 】

上側閾値は、第 1 抵抗 3 1 及び第 2 抵抗 4 1 夫々で開放故障が発生した場合における抵抗電圧値中の低い電圧値以下であり、かつ、通常状態における抵抗電圧値よりも高い電圧値に設定されている。このため、第 2 スイッチ 4 0、第 1 抵抗 3 1 又は第 2 抵抗 4 1 で開放故障が発生した場合、抵抗電圧値は上側閾値以上である。

#### 【 0 0 7 5 】

図 4 は、故障検知処理の手順を示すフローチャートである。前述したように、制御部 5 6 は、駆動回路 2 0 にオンへの切替えを指示している場合に故障検知処理を周期的に実行する。

#### 【 0 0 7 6 】

故障検知処理では、まず、制御部 5 6 は、A/D 変換部 5 4 から抵抗電圧値を取得し(ステップ S1)、取得した抵抗電圧値が下側閾値未満であるか否かを判定する(ステップ S2)。前述したように、抵抗電圧値が下側閾値未満である場合、第 1 スイッチ 3 0、第 1 抵抗 3 1 及び第 2 抵抗 4 1 中の少なくとも 1 つで故障が発生している。従って、抵抗電圧値が下側閾値未満であると判定することは、第 1 スイッチ 3 0、第 1 抵抗 3 1 及び第 2 抵抗 4 1 中の少なくとも 1 つの故障の発生を検知することに相当する。下側閾値は第 1 閾値に相当する。制御部 5 6 は検知部としても機能する。

#### 【 0 0 7 7 】

制御部 5 6 は、抵抗電圧値が下側閾値以上であると判定した場合(S2: NO)、ステップ S1 で取得した抵抗電圧値が上側閾値以上であるか否かを判定する(ステップ S3)。前述したように、抵抗電圧値が上側閾値以上である場合、第 2 スイッチ 4 0、第 1 抵抗 3 1 及び第 2 抵抗 4 1 中の少なくとも 1 つが故障している。従って、抵抗電圧値が上側閾値以上であると判定することは、第 2 スイッチ 4 0、第 1 抵抗 3 1 及び第 2 抵抗 4 1 中の少なくとも 1 つの故障の発生を検知することに相当する。上側閾値は第 2 閾値に相当する。

#### 【 0 0 7 8 】

制御部 5 6 は、抵抗電圧値が下側閾値未満であると判定した場合(S2: YES)、又は、抵抗電圧値が上側閾値以上であると判定した場合(S3: YES)、出力部 5 0 にローレベル電圧への切替えを指示する(ステップ S4)。これにより、出力部 5 0 は、駆動

10

20

30

40

50

回路 2 0 に出力している電圧をローレベル電圧に切替え、駆動回路 2 0 は、第 1 スイッチ 3 0 及び第 2 スイッチ 4 0 をオフに切替える。これにより、第 1 スイッチ 3 0 又は第 2 スイッチ 4 0 に大きな電流が流れることはなく、第 1 スイッチ 3 0 又は第 2 スイッチ 4 0 の温度が異常な温度に上昇することはない。

#### 【 0 0 7 9 】

次に、制御部 5 6 は、出力部 5 1 に報知信号の出力を指示する（ステップ S 5）。これにより、出力部 5 1 は報知信号を出力し、故障の発生が報知される。制御部 5 6 は、抵抗電圧値が上側閾値未満であると判定した場合（S 3 : N O）、又は、ステップ S 5 を実行した後、故障検知処理を終了する。

#### 【 0 0 8 0 】

以上のように、制御装置 1 0 では、第 1 スイッチ 3 0 で開放故障が発生した場合、抵抗電圧値が下側閾値未満となり、第 2 スイッチ 4 0 で開放故障が発生した場合、抵抗電圧値が上側閾値以上となる。このため、第 1 スイッチ 3 0 又は第 2 スイッチ 4 0 で開放故障が発生した場合、制御部 5 6 は、第 1 スイッチ 3 0 、第 2 スイッチ 4 0 、第 1 抵抗 3 1 及び第 2 抵抗 4 1 中の少なくとも 1 つでの故障の発生を検知する。

#### 【 0 0 8 1 】

なお、電流検出回路 2 1 において、F E T 6 4 の型は、N チャネル型であってもよい。この場合、差動増幅器 6 3 のプラス端及びマイナス端夫々は、回路抵抗 6 0 , 6 1 夫々の他端に接続される。更に、F E T 6 4 について、ドレインが回路抵抗 6 0 の他端に接続され、ソースが回路抵抗 6 2 の一端に接続される。この場合、第 1 抵抗 3 1 の両端間の電圧値が大きい程、差動増幅器 6 3 は、F E T 6 4 のゲートの電圧値を高い電圧値に調整する。F E T 6 4 のドレイン及びソース間の抵抗値は、ゲートの電圧値が高い程、小さい。

#### 【 0 0 8 2 】

また、F E T 6 4 は可変抵抗器として機能すればよい。このため、F E T 6 4 の代わりに、バイポーラトランジスタを用いてもよい。P チャネル型のF E T は、P N P 型のバイポーラトランジスタに対応する。N チャネル型のF E T は、N P N 型のバイポーラトランジスタに対応する。

更に、電流検出回路 2 1 は、第 1 抵抗 3 1 の第 1 スイッチ 3 0 側の一端から電流を引き込む回路に限定されず、第 1 抵抗 3 1 の両端間の電圧値に応じた電圧値を出力する回路であってもよい。

#### 【 0 0 8 3 】

##### ( 実施形態 2 )

図 5 は、実施形態 2 における電源システム 1 の要部構成を示すブロック図である。

以下では、実施形態 2 について、実施形態 1 と異なる点を説明する。後述する構成を除く他の構成については、実施形態 1 と共に通しているため、実施形態 1 と共に通する構成部には実施形態 1 と同一の参照符号を付してその説明を省略する。

#### 【 0 0 8 4 】

実施形態 2 を実施形態 1 と比較した場合、制御装置 1 0 の構成が異なる。実施形態 2 における制御装置 1 0 は、実施形態 1 における制御装置 1 0 が有する構成部に加えて、電圧検出回路 7 0 , 7 1 を有する。実施形態 2 におけるマイコン 2 2 は、実施形態 1 におけるマイコン 2 2 が有する構成部に加えて、入力部 8 0 , 8 1 及び A / D 変換部 8 2 , 8 3 を有する。

#### 【 0 0 8 5 】

電圧検出回路 7 0 は、第 1 スイッチ 3 0 及び第 1 抵抗 3 1 間の接続ノードと、マイコン 2 2 の入力部 8 0 に接続されている。入力部 8 0 は、更に、A / D 変換部 8 2 に接続されている。A / D 変換部 8 2 は、更に、内部バス 5 7 に接続されている。電圧検出回路 7 1 は、第 2 スイッチ 4 0 及び第 2 抵抗 4 1 間の接続ノードと、マイコン 2 2 の入力部 8 1 に接続されている。入力部 8 1 は、更に、A / D 変換部 8 3 に接続されている。A / D 変換部 8 3 は、更に、内部バス 5 7 に接続されている。

#### 【 0 0 8 6 】

10

20

30

40

50

電圧検出回路 7 0 は、第 1 スイッチ 3 0 及び第 1 抵抗 3 1 間の接続ノードの電圧値を検出する。この電圧値は、接地電位を基準とした電圧値である。電圧検出回路 7 0 は、検出した電圧値を示すアナログの第 1 検出値を入力部 8 0 に出力する。

#### 【 0 0 8 7 】

入力部 8 0 は、電圧検出回路 7 0 からアナログの第 1 検出値が入力された場合、入力されたアナログの第 1 検出値を A / D 変換部 8 2 に出力する。A / D 変換部 8 2 は、入力部 8 0 から入力されたアナログの第 1 検出値をデジタルの第 1 検出値に変換する。制御部 5 6 は、A / D 変換部 8 2 からデジタルの第 1 検出値を取得する。

#### 【 0 0 8 8 】

電圧検出回路 7 1 は、第 2 スイッチ 4 0 及び第 2 抵抗 4 1 間の接続ノードの電圧値を検出する。この電圧値は、接地電位を基準とした電圧値である。電圧検出回路 7 1 は、検出した電圧値を示すアナログの第 2 検出値を入力部 8 0 に出力する。電圧検出回路 7 1 は第 2 の電圧検出回路として機能する。10

#### 【 0 0 8 9 】

入力部 8 0 は、電圧検出回路 7 1 からアナログの第 2 検出値が入力された場合、入力されたアナログの第 2 検出値を A / D 変換部 8 3 に出力する。A / D 変換部 8 3 は、入力部 8 1 から入力されたアナログの第 2 検出値をデジタルの第 2 検出値に変換する。制御部 5 6 は、A / D 変換部 8 3 からデジタルの第 2 検出値を取得する。

#### 【 0 0 9 0 】

制御部 5 6 は、実施形態 1 と同様に、コンピュータプログラム P を実行することによって、作動処理、停止処理、保護処理及び故障検知処理を実行する。実施形態 2 における作動処理、停止処理及び保護処理夫々は、実施形態 1 における作動処理、停止処理及び保護処理と同様である。実施形態 2 における故障検知処理は、実施形態 1 における故障検知処理と異なる。20

#### 【 0 0 9 1 】

図 6 は、故障によって生じる現象の説明図である。実施形態 1 の説明で述べたように、第 1 スイッチ 3 0 で開放故障が発生した場合、又は、第 1 抵抗 3 1 若しくは第 2 抵抗 4 1 で短絡故障が発生した場合、抵抗電圧値は下側閾値未満である。

#### 【 0 0 9 2 】

第 1 スイッチ 3 0 で開放故障が発生している場合、電圧検出回路 7 0 が検出する電圧値、即ち、第 1 検出値が示す電圧値は、負荷 1 2 の両端間に印加されている電圧値（以下、負荷電圧値という）である。この電圧値はバッテリ電圧値よりも低い。第 1 抵抗 3 1 又は第 2 抵抗 4 1 で短絡故障が発生した場合、第 1 検出値が示す電圧値は、バッテリ電圧値である。30

#### 【 0 0 9 3 】

実施形態 1 の説明で述べたように、第 2 スイッチ 4 0 、第 1 抵抗 3 1 又は第 2 抵抗 4 1 で開放故障が発生した場合、抵抗電圧値は上側閾値以上である。第 2 スイッチ 4 0 で開放故障が発生している場合、電圧検出回路 7 1 が検出する電圧値、即ち、第 2 検出値が示す電圧値は、負荷電圧値である。この電圧値はバッテリ電圧値よりも低い。第 1 抵抗 3 1 又は第 2 抵抗 4 1 で開放故障が発生した場合、第 2 検出値が示す電圧値は、バッテリ電圧値である。40

#### 【 0 0 9 4 】

一定の基準電圧値が予め設定されている。基準電圧値は、第 1 スイッチ 3 0 で開放故障が発生している場合における負荷電圧値、及び、第 2 スイッチ 4 0 で開放故障が発生している場合における負荷電圧値よりも高い。更に、基準電圧値は、バッテリ電圧値以下である。

#### 【 0 0 9 5 】

従って、抵抗電圧値が下側閾値未満である場合、即ち、第 1 スイッチ 3 0 、第 1 抵抗 3 1 及び第 2 抵抗 4 1 中の少なくとも 1 つで故障が発生している場合において、第 1 スイッチ 3 0 で開放故障が発生しているとき、第 1 検出値が示す電圧値は基準電圧値未満である50

。また、抵抗電圧値が上側閾値以上である場合、即ち、第2スイッチ40、第1抵抗31及び第2抵抗41中の少なくとも1つで故障が発生している場合において、第2スイッチ40で開放故障が発生しているとき、第2検出値が示す電圧値は基準電圧値未満である。

#### 【0096】

図7及び図8は、故障検知処理の手順を示すフローチャートである。実施形態1と同様に、制御部56は、駆動回路20にオンへの切替えを指示している場合に故障検知処理を周期的に実行する。実施形態2における故障検知処理のステップS11、S12、S18夫々は、実施形態1における故障検知処理のステップS1、S2、S3と同様である。実施形態2における故障検知処理のステップS17、S23夫々は、実施形態1における故障検知処理のステップS4と同様である。このため、ステップS11、S12、S17、S18、S23の詳細な説明を省略する。

10

#### 【0097】

制御部56は、ステップS11で取得した抵抗電圧値が下側閾値未満であると判定した場合(S12: YES)、A/D変換部82から第1検出値を取得する(ステップS13)。次に、制御部56は、ステップS13で取得した第1検出値が示す電圧値が基準電圧値未満であるか否かを判定する(ステップS14)。

#### 【0098】

前述したように、抵抗電圧値が下側閾値未満である場合において、第1検出値が示す電圧値が基準電圧値未満であるとき、第1スイッチ30で開放故障が発生している。従って、ステップS13で第1検出値が示す電圧値が基準電圧値未満であると判定することは、第1スイッチ30での故障の発生を検知することに相当する。制御部56は、第1スイッチ30及び第1抵抗31間の接続ノードの電圧値に基づいて、第1スイッチ30での開放故障の発生を検知する。

20

#### 【0099】

制御部56は、電圧値が基準電圧値未満であると判定した場合(S14: YES)、第1スイッチ30の開放故障を示す報知信号の出力を出力部51に指示する(ステップS15)。これにより、出力部51は、報知信号を出力し、第1スイッチ30での開放故障の発生が報知される。

#### 【0100】

制御部56は、電圧値が基準電圧値以上であると判定した場合(S14: NO)、第1抵抗31又は第2抵抗41の短絡故障を示す報知信号の出力を出力部51に指示する(ステップS16)。これにより、出力部51は、報知信号を出力し、第1抵抗31又は第2抵抗41の短絡故障の発生が報知される。制御部56は、ステップS15、S16の一方を実行した後、ステップS17を実行し、故障検知処理を終了する。

30

#### 【0101】

制御部56は、ステップS11で取得した抵抗電圧値が下側閾値以上であると判定した場合(S12: NO)、ステップS18を実行する。次に、制御部56は、ステップS11で取得した抵抗電圧値が上側閾値以上であると判定した場合(S18: YES)、A/D変換部82から第2検出値を取得する(ステップS19)。制御部56は、ステップS19で取得した第2検出値が示す電圧値が基準電圧値未満であるか否かを判定する(ステップS20)。

40

#### 【0102】

前述したように、抵抗電圧値が上側閾値以上である場合において、第2検出値が示す電圧値が基準電圧値未満であるとき、第2スイッチ40で開放故障が発生している。従って、ステップS20で第2検出値が示す電圧値が基準電圧値未満であると判定することは、第2スイッチ40での故障の発生を検知することに相当する。制御部56は、第2スイッチ40及び第2抵抗41間の接続ノードの電圧値に基づいて、第2スイッチ40での開放故障の発生を検知する。

#### 【0103】

制御部56は、電圧値が基準電圧値未満であると判定した場合(S20: YES)、第

50

2スイッチ40の開放故障を示す報知信号の出力を出力部51に指示する(ステップS21)。これにより、出力部51は、報知信号を出力し、第2スイッチ40の開放故障の発生が報知される。

#### 【0104】

制御部56は、電圧値が基準電圧値以上であると判定した場合(S20:NO)、第1抵抗31又は第2抵抗41の開放故障を示す報知信号の出力を出力部51に指示する(ステップS22)。これにより、出力部51は、報知信号を出力し、第1抵抗31又は第2抵抗41の開放故障の発生が報知される。制御部56は、ステップS11で取得した抵抗電圧値が上側閾値未満であると判定した場合(S18:NO)、又は、ステップS21,S22の一方を実行した後、ステップS23を実行し、故障検知処理を終了する。

10

#### 【0105】

実施形態2における制御装置10は、実施形態1における制御装置10が奏する効果を同様に奏する。

#### 【0106】

なお、実施形態2では、制御装置10の制御部56は、第1スイッチ30及び第2スイッチ40中の少なくとも1つでの短絡故障の発生を検知することができる。ここで、短絡故障は、スイッチがオンに固定される故障である。制御部56は、駆動回路20に第1スイッチ30及び第2スイッチ40のオフへの切替えを指示している状態で、A/D変換部82,83から取得した第1検出値及び第2検出値が示す電圧値、即ち、電圧検出回路70,71が検出した電圧値に基づいて、第1スイッチ30及び第2スイッチ40中の少なくとも1つでの短絡故障の発生を検知する。具体的には、制御部56は、駆動回路20に第1スイッチ30及び第2スイッチ40のオフへの切替えを指示している状態で第1検出値及び第2検出値が示す電圧値がゼロVを超えている場合、第1スイッチ30及び第2スイッチ40中の少なくとも1つでの短絡故障の発生を検知する。第1検出値及び第2検出値の中で、バッテリ電圧値と同様の電圧値を示す検出値に対応するスイッチが、短絡故障が発生しているスイッチである。

20

#### 【0107】

##### (実施形態3)

図9は、実施形態3における電源システム1の要部構成を示すブロック図である。

以下では、実施形態3について、実施形態2と異なる点を説明する。後述する構成を除く他の構成については、実施形態2と共に通しているため、実施形態2と共に通する構成部には実施形態2と同一の参照符号を付してその説明を省略する。

30

#### 【0108】

実施形態3を実施形態2と比較した場合、制御装置10の構成が異なる。実施形態3における制御装置10は、実施形態2と同様に、駆動回路20、電流検出回路21、マイコン22、電圧検出回路70及び第1直列回路Aを有する。実施形態3における制御装置10は、更に、N個の第2直列回路B,B,···と、N個の電圧検出回路71,71,···とを有する。Nは2以上の整数である。

#### 【0109】

各第2直列回路Bでは、第2スイッチ40及び第2抵抗41は、実施形態2と同様に接続されている。従って、第2スイッチ40のドレインは、バッテリ11の正極に接続されている。第2スイッチ40のソースは第2抵抗41の一端に接続されている。第2抵抗41の他端は、負荷12の一端に接続されている。第2スイッチ40のゲートは、駆動回路20の出力端に接続されている。

40

#### 【0110】

各第2直列回路Bにおいて、第2スイッチ40及び第2抵抗41間の接続ノードは電圧検出回路71に接続されている。N個の電圧検出回路71,71,···夫々は、マイコン22に接続されている。

#### 【0111】

図10はマイコン22の要部構成を示すブロック図である。実施形態3におけるマイコ

50

ン 2 2 は、実施形態 2 と同様に、出力部 5 0 , 5 1 、入力部 5 2 , 5 3 , 8 0 、A / D 変換部 5 4 , 8 2 、記憶部 5 5 及び制御部 5 6 を有する。実施形態 3 におけるマイコン 2 2 は、更に、N 個の入力部 8 1 , 8 1 , ··· 及び N 個の A / D 変換部 8 3 , 8 3 , ··· を有する。

#### 【 0 1 1 2 】

N 個の入力部 8 1 , 8 1 , ··· 夫々は、N 個の電圧検出回路 7 1 , 7 1 , ··· に接続されている。N 個の入力部 8 1 , 8 1 , ··· 夫々は、更に、N 個の A / D 変換部 8 3 , 8 3 , ··· に接続されている。N 個の A / D 変換部 8 3 , 8 3 , ··· 夫々は、更に、内部バス 5 7 に接続されている。

#### 【 0 1 1 3 】

電圧検出回路 7 1 、入力部 8 1 及び A / D 変換部 8 3 は、実施形態 2 と同様に作用する。制御部 5 6 は、実施形態 2 と同様に、作動処理、停止処理、保護処理及び故障検知処理を実行する。

#### 【 0 1 1 4 】

基準電圧値は、第 1 スイッチ 3 0 で開放故障が発生している場合における負荷電圧値、及び、N 個の第 2 スイッチ 4 0 , 4 0 , ··· 夫々で開放故障が発生している場合における負荷電圧値よりも高い。更に、基準電圧値は、バッテリ電圧値以下である。

N 個の第 2 抵抗 4 1 夫々の抵抗値は、他の第 2 抵抗 4 1 の抵抗値中の少なくとも 1 つと異なっていてもよい。

#### 【 0 1 1 5 】

故障検知処理のステップ S 1 9 では、制御部 5 6 は、N 個の A / D 変換部 8 3 , 8 3 , ··· から N 個の第 2 検出値を取得する。故障検知処理のステップ S 2 0 では、制御部 5 6 は、ステップ S 1 9 で取得した N 個の第 2 検出値が示す N 個の電圧値の少なくとも 1 つが基準電圧値未満であるか否かを判定する。

#### 【 0 1 1 6 】

制御部 5 6 は、N 個の電圧値中の少なくとも 1 つが基準電圧値未満であると判定した場合 (S 2 0 : YES) 、ステップ S 2 1 を実行する。ステップ S 2 1 では、制御部 5 6 は、基準電圧値未満である一又は複数の電圧値に対応する一又は複数の第 2 スイッチ 4 0 , 4 0 , ··· の開放故障を示す報知信号の出力を出力部 5 1 に指示する。これにより、一又は複数の第 2 スイッチ 4 0 , 4 0 , ··· での開放故障の発生が報知される。

#### 【 0 1 1 7 】

制御部 5 6 は、N 個の電圧値中の少なくとも 1 つが基準電圧値未満ではない、即ち、N 個の電圧値の全てが基準電圧値以上であると判定した場合 (S 2 0 : NO) 、ステップ S 2 2 を実行する。

実施形態 3 における制御装置 1 0 は、実施形態 2 における制御装置 1 0 が奏する効果を同様に奏する。

#### 【 0 1 1 8 】

なお、実施形態 3 においても、制御装置 1 0 の制御部 5 6 は、第 1 スイッチ 3 0 及び N 個の第 2 スイッチ 4 0 , 4 0 , ··· 中の少なくとも 1 つでの短絡故障の発生を検知することができる。制御部 5 6 は、駆動回路 2 0 に第 1 スイッチ 3 0 及び N 個の第 2 スイッチ 4 0 , 4 0 , ··· のオフへの切替えを指示している状態で、A / D 変換部 8 2 及び N 個の A / D 変換部 8 3 , 8 3 , ··· から取得した第 1 検出値及び N 個の第 2 検出値が示す電圧値に基づいて、第 1 スイッチ 3 0 及び N 個の第 2 スイッチ 4 0 , 4 0 , ··· 中の少なくとも 1 つでの短絡故障の発生を検知する。具体的には、制御部 5 6 は、駆動回路 2 0 に第 1 スイッチ 3 0 及び N 個の第 2 スイッチ 4 0 , 4 0 , ··· のオフへの切替えを指示している状態で第 1 検出値及び N 個の第 2 検出値が示す電圧値がゼロ V を超えている場合、第 1 スイッチ 3 0 及び N 個の第 2 スイッチ 4 0 , 4 0 , ··· 中の少なくとも 1 つでの短絡故障の発生を検知する。第 1 検出値及び N 個の第 2 検出値の中で、バッテリ電圧値と同様の電圧値を示す検出値に対応するスイッチが、短絡故障が発生しているスイッチである。

10

20

30

40

50

## 【0119】

なお、実施形態1～3において、第1スイッチ30及び第2スイッチ40夫々は、Nチャネル型のFETに限定されず、Pチャネル型のFET又はバイポーラトランジスタ等であってもよい。

また、電流検出回路21が出力した抵抗電圧値に基づいて算出した電流値を用いる処理は、保護処理に限定されず、例えば、電流値からバッテリ11及び負荷12間に接続される電線温度を算出する処理であってもよい。

## 【0120】

更に、第1直列回路Aでは、第1スイッチ30及び第1抵抗31が直列に接続されればよい。このため、例えば、第1スイッチ30及び第1抵抗31に加えて、インダクタが更に直列に接続されてもよい。同様に、第2直列回路Bでは、第2スイッチ40及び第2抵抗41が直列に接続されればよい。このため、例えば、第2スイッチ40及び第2抵抗41に加えて、インダクタが更に直列に接続されてもよい。

## 【0121】

開示された実施形態1～3はすべての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は、上述した意味ではなく、特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内でのすべての変更が含まれることが意図される。

## 【符号の説明】

## 【0122】

|        |                   |    |

|--------|-------------------|----|

| 1      | 電源システム            | 20 |

| 10     | 制御装置              |    |

| 11     | バッテリ              |    |

| 12     | 負荷                |    |

| 20     | 駆動回路              |    |

| 21     | 電流検出回路(電圧出力回路)    |    |

| 22     | マイコン              |    |

| 30     | 第1スイッチ            |    |

| 31     | 第1抵抗              |    |

| 40     | 第2スイッチ            | 30 |

| 41     | 第2抵抗              |    |

| 50, 51 | 出力部               |    |

| 52, 53 | 入力部               |    |

| 54     | A/D変換部            |    |

| 55     | 記憶部               |    |

| 56     | 制御部(指示部、検知部)      |    |

| 57     | 内部バス              |    |

| 60, 61 | 回路抵抗              |    |

| 62     | 回路抵抗(電流抵抗)        |    |

| 63     | 差動増幅器             | 40 |

| 64     | FET(電流出力部)        |    |

| 70     | 電圧検出回路            |    |

| 71     | 電圧検出回路(第2の電圧検出回路) |    |

| 80, 81 | 入力部               |    |

| 82, 83 | A/D変換部            |    |

| A      | 第1直列回路            |    |

| B      | 第2直列回路            |    |

| E      | 記憶媒体              |    |

| P      | コンピュータプログラム       |    |

【図1】

【図2】

【図3】

| 故障部品   | 故障内容 | 抵抗電圧値  |

|--------|------|--------|

| 第1スイッチ | 開放故障 | 下側閾値未満 |

| 第2スイッチ | 開放故障 | 上側閾値以上 |

| 第1抵抗   | 開放故障 | 上側閾値以上 |

| 第1抵抗   | 短絡故障 | 下側閾値未満 |

| 第2抵抗   | 開放故障 | 上側閾値以上 |

| 第2抵抗   | 短絡故障 | 下側閾値未満 |

【図4】

【図5】

【図 6】

| 故障部位   | 故障内容 | 抵抗電圧値  | 第2検出值   | 第1検出值   |

|--------|------|--------|---------|---------|

| 第1スイッチ | 開放故障 | 下側閾値未満 | 基準電圧値以上 | 基準電圧値以上 |

| 第2スイッチ | 開放故障 | 上側閾値以上 | 基準電圧値以上 | 基準電圧値未満 |

| 第1抵抗   | 開放故障 | 上側閾値以上 | 基準電圧値以上 | 基準電圧値以上 |

| 第2抵抗   | 開放故障 | 下側閾値未満 | 上側閾値以上  | 基準電圧値未満 |

|        | 短絡故障 | 下側閾値以上 | 上側閾値以上  | 基準電圧値以上 |

【図 7】

【図 8】

【図 9】

【図10】

---

フロントページの続き

(72)発明者 内野 剛雄

三重県四日市市西末広町1番14号 株式会社オートネットワーク技術研究所内

(72)発明者 澤野 峻一

三重県四日市市西末広町1番14号 株式会社オートネットワーク技術研究所内

(72)発明者 加藤 雅幸

三重県四日市市西末広町1番14号 株式会社オートネットワーク技術研究所内

審査官 工藤 一光

(56)参考文献 特開2007-285969(JP,A)

特開2008-175804(JP,A)

特開2009-38218(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02H3/08 - 3/10

H02J7/00

H03K17/00

H03K17/08 - 17/082

H03K17/687 - 17/695