(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2019-525480

(P2019-525480A)

(43) 公表日 令和1年9月5日(2019.9.5)

(51) Int.Cl.

H01L 21/336 (2006.01)

H01L 29/78 (2006.01)

F 1

H01L 29/78

301C

テーマコード(参考)

5F14O

審査請求 未請求 予備審査請求 有 (全 28 頁)

(21) 出願番号 特願2019-506475 (P2019-506475)

(86) (22) 出願日 平成29年8月21日 (2017.8.21)

(85) 翻訳文提出日 平成31年2月6日 (2019.2.6)

(86) 國際出願番号 PCT/US2017/047747

(87) 國際公開番号 WO2018/039108

(87) 國際公開日 平成30年3月1日 (2018.3.1)

(31) 優先権主張番号 15/245,777

(32) 優先日 平成28年8月24日 (2016.8.24)

(33) 優先権主張国・地域又は機関

米国(US)

(71) 出願人 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ヨン・ソン・チエ

アメリカ合衆国・カリフォルニア・921

21・サン・ディエゴ・モアハウス・ドラ

イブ・5775

最終頁に続く

(54) 【発明の名称】隣接する非対称アクティブゲート/ダミーゲート幅レイアウトを採用する電界効果トランジスタ(FET)デバイス

## (57) 【要約】

隣接する非対称アクティブゲート/ダミーゲート幅レイアウトを採用する電界効果トランジスタ(FET)デバイスを開示する。例示的な態様では、アクティブゲートと、ソース領域と、ドレイン領域とを有するFETデバイスを含む、FETセルが提供される。FETセルはまた、ソース領域およびドレイン領域のうちの1つに隣接して位置するディフュージョンブレーク上に、ダミーゲートを備える、分離構造を含む。FETセルは、アクティブゲートの幅が隣接するダミーゲートの幅よりも大きいという点で、非対称アクティブゲート/ダミーゲート幅レイアウトを有する。アクティブゲートの幅の増大は、ゲート制御の増大をもたらし、ダミーゲートの幅の縮小は、ダミーゲートからの分離を増大し、したがって、ダミーゲートを通したサブスレッショルドリークが低減される。

## 【特許請求の範囲】

## 【請求項 1】

非対称ゲート幅レイアウトを有する電界効果トランジスタ( F E T )セルであって、上面を有する本体を備える基板と、

F E T デバイスであって、

前記基板中に配設されたソースと、

前記基板中に配設されたドレインと、

前記ソースと前記ドレインとの間に形成された、アクティブゲート幅のアクティブゲートと

を備える、F E T デバイスと、

前記F E T デバイスに隣接して、前記基板中に配設された分離構造であって、

前記F E T デバイスの前記ソースおよび前記ドレインのうちの1つに隣接して、前記基板中に配設されたディフュージョンブレークであって、前記ディフュージョンブレークに隣接する、前記ソースおよび前記ドレインのうちの前記1つの深さが、前記ディフュージョンブレークに隣接していない、前記ソースおよび前記ドレインのうちの前記1つの深さよりも大きい、ディフュージョンブレークと、

前記アクティブゲートに隣接して、前記ディフュージョンブレークの上方に形成された、ダミーゲート幅のダミーゲートであって、前記ダミーゲート幅が、前記アクティブゲート幅よりもゲート幅マージンだけ小さい、ダミーゲートと

を備える、分離構造と

を備える、F E T セル。

10

20

30

40

50

## 【請求項 2】

前記F E T セルが、

前記アクティブゲートに隣接して、前記ソースの上方に配設されたソースコンタクトと、

前記アクティブゲートに隣接して、前記ドレインの上方に配設されたドレインコンタクトと

をさらに備え、

前記ディフュージョンブレークに隣接する、前記ソースおよび前記ドレインのうちの前記1つに対応する、前記ソースコンタクトおよび前記ドレインコンタクトのうちの1つが、前記アクティブゲートと前記ダミーゲートとの間に配設され、前記アクティブゲートから第1の距離だけ分離され、前記ダミーゲートから、分離マージンだけ前記第1の距離とは異なる第2の距離だけ分離され、

前記分離マージンが、前記ゲート幅マージンの約半分である、請求項1に記載のF E T セル。

## 【請求項 3】

前記アクティブゲート幅が約15ナノメートル( n m )であり、

前記ダミーゲート幅が約13n mであり、

前記分離マージンが約1n mである、請求項2に記載のF E T セル。

## 【請求項 4】

前記アクティブゲート幅が約18ナノメートル( n m )であり、

前記ダミーゲート幅が約14n mであり、

前記分離マージンが約2n mである、請求項2に記載のF E T セル。

## 【請求項 5】

前記ゲート幅マージンが、少なくとも2ナノメートル( n m )である、請求項1に記載のF E T セル。

## 【請求項 6】

前記アクティブゲート幅が約15n mであり、

前記ダミーゲート幅が約13n mである、請求項5に記載のF E T セル。

## 【請求項 7】

前記アクティブゲート幅が約17nmであり、

前記ダミーゲート幅が約14nmである、請求項5に記載のFETセル。

**【請求項8】**

前記ゲート幅マージンが、少なくとも4ナノメートル(nm)であり、

前記アクティブゲート幅が約18nmである、請求項1に記載のFETセル。

**【請求項9】**

集積回路(IC)に組み込まれる、請求項1に記載のFETセル。

**【請求項10】**

セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイルフォン、セルラーフォン、スマートフォン、タブレット、ファブレット、サーバ、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビ、チューナー、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、ポータブルデジタルビデオプレーヤ、および自動車からなる群から選択されたデバイスに組み込まれる、請求項1に記載のFETセル。

10

**【請求項11】**

半導体ダイにおいて電界効果トランジスタ(FET)セルを作製する方法であって、基板中に配設されたディフュージョンブレークを形成するステップと、

20

前記基板上にアクティブゲート幅のアクティブゲートを形成するステップと、

前記ディフュージョンブレークの上方に、および前記アクティブゲートに隣接して、ダミーゲート幅のダミーゲートを形成するステップであって、前記ダミーゲート幅が、前記アクティブゲート幅よりもゲート幅マージンだけ小さい、ステップと、

前記アクティブゲートに隣接して、前記基板中にFETデバイスのソースエピタキシャル領域を形成するステップと、

前記基板の上面から第1の深さにおいて、前記ソースエピタキシャル領域中にソースを形成するステップと、

前記アクティブゲートと前記ダミーゲートとの間で、前記ディフュージョンブレークに隣接して、前記基板中に前記FETデバイスのドレインエピタキシャル領域を形成するステップであって、前記ドレインエピタキシャル領域の一部分が前記ディフュージョンブレークと接触している、ステップと、

30

前記第1の深さよりも大きい、前記基板の前記上面からの第2の深さにおいて、前記ドレインエピタキシャル領域中にドレインを形成するステップと、

前記ソースと前記ドレインとの間で、前記基板中に前記FETデバイスのチャネル領域を形成するステップと

を含む、方法。

**【請求項12】**

前記ダミーゲートを形成するステップが、少なくとも2ナノメートル(nm)の前記ゲート幅マージンだけ、前記アクティブゲート幅よりも小さい前記ダミーゲート幅を備える、前記ダミーゲートを形成するステップを含む、請求項11に記載の方法。

40

**【請求項13】**

前記アクティブゲートを形成するステップが、約15nmである前記アクティブゲート幅を備える、前記アクティブゲートを形成するステップを含み、

前記ダミーゲートを形成するステップが、約13nmである前記ダミーゲート幅を備える、前記ダミーゲートを形成するステップを含む、請求項12に記載の方法。

**【請求項14】**

前記アクティブゲートを形成するステップが、約17nmである前記アクティブゲート幅を備える、前記アクティブゲートを形成するステップを含み、

前記ダミーゲートを形成するステップが、約14nmである前記ダミーゲート幅を備え

50

る、前記ダミーゲートを形成するステップを含む、請求項 1 2 に記載の方法。

【請求項 1 5】

前記ダミーゲートを形成するステップが、少なくとも 4 ナノメートル ( nm ) の前記ゲート幅マージンだけ、前記アクティブゲート幅よりも小さい前記ダミーゲート幅を備える、前記ダミーゲートを形成するステップを含み、

前記アクティブゲートを形成するステップが、約 18 nm である前記アクティブゲート幅を備える、前記アクティブゲートを形成するステップを含む、請求項 1 1 に記載の方法。

【請求項 1 6】

前記方法が、

前記アクティブゲートに隣接して、前記ソースエピタキシャル領域上にソースコンタクトを配設するステップと、

前記アクティブゲートと前記ダミーゲートとの間で、前記ドレインエピタキシャル領域上にドレインコンタクトを配設するステップであって、前記ドレインコンタクトが、前記アクティブゲートから第 1 の距離だけ分離され、前記ダミーゲートから、分離マージンだけ前記第 1 の距離よりも大きい第 2 の距離だけ分離される、ステップとをさらに含み、

前記分離マージンが、前記ゲート幅マージンの約半分である、請求項 1 1 に記載の方法。

【請求項 1 7】

前記アクティブゲートを形成するステップが、約 15 ナノメートル ( nm ) である前記アクティブゲート幅を備える、前記アクティブゲートを形成するステップを含み、

前記ダミーゲートを形成するステップが、約 1 nm である前記分離マージンを設けるために、約 13 nm である前記ダミーゲート幅を備える、前記ダミーゲートを形成するステップを含む、請求項 1 6 に記載の方法。

【請求項 1 8】

前記アクティブゲートを形成するステップが、約 18 nm である前記アクティブゲート幅を備える、前記アクティブゲートを形成するステップを含み、

前記ダミーゲートを形成するステップが、約 2 nm である前記分離マージンを設けるために、約 14 nm である前記ダミーゲート幅を備える、前記ダミーゲートを形成するステップを含む、請求項 1 6 に記載の方法。

【請求項 1 9】

前記ソースエピタキシャル領域中に前記ソースを形成するステップが、前記基板の前記上面から前記第 1 の深さにおいて、前記ソースエピタキシャル領域中に前記ソースを注入するステップを含み、

前記ドレインエピタキシャル領域中に前記ドレインを形成するステップが、前記第 1 の深さよりも大きい、前記基板の前記上面からの前記第 2 の深さにおいて、前記ドレインエピタキシャル領域中に前記ドレインを注入するステップを含む、請求項 1 1 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

優先権出願

本出願は、その全体が参照により本明細書に組み込まれる、2016年8月24日に出願された「FIELD-EFFECT TRANSISTOR (FET) DEVICE EMPLOYING ADJACENT ASYMMETRIC ACTIVE GATE / DUMMY GATE WIDTH LAYOUT」と題する米国特許出願第 15 / 245,777 号の優先権を主張する。

【0 0 0 2】

本開示の技術は、一般に電界効果トランジスタ (FET) に関し、より詳細には、F E

10

20

30

40

50

Tにおけるゲート構造のレイアウトに関する。

**【背景技術】**

**【0003】**

トランジスタは、近代の電子デバイスにおいて必須の構成要素である。大量のトランジスタが、多数の現代の電子デバイスにおける集積回路（I C）において採用されている。たとえば、中央処理ユニット（C P U）およびメモリユニットなど、現代の電子デバイスの構成要素は、論理回路およびデータストレージのための大量のトランジスタを採用している。

**【0004】**

I C発展の過程において、機能密度（すなわち、チップ面積当たりの相互接続されたデバイスの数）が増大している。この機能密度の増大は、部分的に、I Cにおけるトランジスタセルをスケールダウンするための継続的な努力（たとえば、ますますより多くのトランジスタノードと同じ量の空間に配置するために、トランジスタノードのサイズを低減すること）を通して達成される。トランジスタセルは、たとえば、その中のトランジスタノードのゲート幅および／またはチャネル長の低減によって、スケールダウンされ得る。トランジスタセルはまた、隣接するトランジスタセルからその中のトランジスタノードを分離する分離構造のサイズを低減することによっても、スケールダウンされ得る。たとえば、ダブルディフュージョンブレーク（D D B : d o u b l e   d i f f u s i o n   b r e a k ）を備える分離構造を含むトランジスタセルは、代わりにシングルディフュージョンブレーク（S D B : s i n g l e   d i f f u s i o n   b r e a k ）を実装することによってスケールダウンされ得る。

**【0005】**

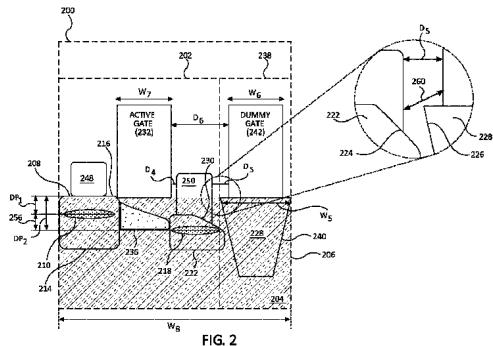

たとえば、図1は、従来のフィン電界効果トランジスタ（F E T）（F i n F E T）セル100の断面である。F i n F E Tセル100は、幅W<sub>1</sub>（たとえば、14または16ナノメートル（n m））のアクティブゲート104を含むF i n F E T102を含む。F i n F E T102は、基板112上で成長したソースエピタキシャル領域108およびドレインエピタキシャル領域110をさらに含む。ソースエピタキシャル領域108およびドレインエピタキシャル領域110は、それぞれのソース列114およびドレイン列116内に位置する。ソースエピタキシャル領域108およびドレインエピタキシャル領域110は、たとえば、シリコングルマニウム（S i G e ）またはゲルマニウム（G e ）のエピタキシャル成長を備え得る。ソースエピタキシャル領域108およびドレインエピタキシャル領域110は、ソースエピタキシャル領域108およびドレインエピタキシャル領域110の各々に、対応するソースまたはドレインを設けるために、それぞれ、ソースインプラント118およびドレインインプラント120を含む。ソースインプラント118およびドレインインプラント120は、たとえば、イオン注入によって形成され得る。F i n F E T102は、それぞれ、ソースエピタキシャル領域108およびドレインエピタキシャル領域110へのアクセスを与えるため、およびしたがって、アクティブゲート104の下で、ソースエピタキシャル領域108とドレインエピタキシャル領域110との間のアクティブチャネル領域126へのアクセスを与えるために、ソースコンタクト122およびドレインコンタクト124をさらに含む。ドレインコンタクト124は、アクティブゲート104から距離D<sub>1</sub>だけ、およびダミーゲート134から距離D<sub>2</sub>だけ分離される。ダミーゲート134は、図1においてW<sub>4</sub>として示された幅を有する。F i n F E T102において、距離D<sub>1</sub>およびD<sub>2</sub>は実質的に同様である。明快のために、エピタキシャル領域108は、ソースエピタキシャル領域108として定義されており、エピタキシャル領域108のインプラント118は、ソースインプラント118として定義されており、エピタキシャル領域110は、ドレインエピタキシャル領域110として定義されており、エピタキシャル領域110のインプラント120は、ドレインインプラント120として定義されていることに留意されたい。しかしながら、これらの要素のソース／ドレイン指示は一例であり、F i n F E Tセル100が回路においてどのように接続されるかに基づいて、ソースまたはドレインのいずれのためのものとしても指示されることがあ

10

20

30

40

50

り、その理由は、アクティブチャネル領域 126 が固有の極性を有していないからである。

#### 【0006】

*F i n F E T* セル 100 は、*F i n F E T* 102 と、たとえば、隣接する *F i n F E T* セル（図示せず）との間の分離をもたらすために、SDB 分離構造 129 をさらに含む。SDB 分離構造 129 は、幅  $W_2$  の SDB 130 を備える。SDB 130 は、たとえば、シャロートレンチ分離酸化物を含み得る。SDB 分離構造 129 は、ダミーゲート 134 をさらに含む。

#### 【0007】

上記で説明した *F i n F E T* セル 100 の構成の下で、*F i n F E T* セル 100 は、たとえば、アクティブゲート 104 の幅  $W_1$ 、アクティブゲート 104 とダミーゲート 134 との間の距離  $D_3$ 、および SDB 130 の幅  $W_2$  によって決まる、幅  $W_3$ （すなわち、セルのアレイにおいて単一の *F i n F E T* セルによって占有された空間）を有する。したがって、*F i n F E T* セル 100 は、たとえば、アクティブゲート 104 の幅  $W_1$ 、アクティブゲート 104 とダミーゲート 134 との間の距離  $D_3$ 、または SDB 130 の幅  $W_2$  のうちの 1 つまたは複数を低減することによって、スケールダウンされ得る。しかしながら、このような *F i n F E T* セル 100 のスケールダウンは、作製および性能の問題によって制限され得る。たとえば、作製の制限および／または分離の要件のために、距離  $D_3$  を低減することによって、ドレインエピタキシャル領域 110 が SDB 130 のより近くに配置されることがある。したがって、作製中に、ドレインエピタキシャル領域 110 のエピタキシャル成長は、ドレインエピタキシャル領域 110 のファセット 140 と、SDB 130 のファセット 144 との間のファセット不整合のために、ドレインエピタキシャル領域 110 の上面 142 にわたって不均一であり得る。具体的には、ドレインエピタキシャル領域 110 のファセット 140 は、SDB 130 のファセット 144 と整合しないことがあり、したがって、SDB 130 のファセット 144 の近くのドレインエピタキシャル領域 110 の成長を妨害することがある。したがって、SDB 130 のファセット 144 の近くのドレインエピタキシャル領域 110 の成長は、SDB 130 のファセット 144 から離れたドレインエピタキシャル領域 110 の成長よりも遅くなる。この不均一な成長は、図 1において、ドレインエピタキシャル領域 110 の不均一な上面 142 によって示されている。ドレインエピタキシャル領域 110 のこの不均一な成長は、ゲート制御の低減、および *F i n F E T* 102 におけるサブスレッショルド電流の増大を生じ得る。具体的には、それぞれソースエピタキシャル領域 108 およびドレインエピタキシャル領域 110 における、ソースインプラント 118 およびドレインインプラント 120 の後の形成中に、ドレインインプラント 120 は、ソース／ドレインインプラントマージン 146 だけ、ドレインエピタキシャル領域 110 において望まれるよりも深く、およびソースエピタキシャル領域 108 におけるソースインプラント 118 よりも深くに配設され得る。これによって、基板 112 において望まれるよりも低く、したがって、望まれるよりもアクティブゲート 104 から遠い、アクティブチャネル領域 126 が生じる。アクティブチャネル領域 126 を、望まれるよりもアクティブゲート 104 から遠くに有することによって、アクティブチャネル領域 126 のゲート制御の低減、およびしたがって、*F i n F E T* 102 の性能の低下が生じ得る。さらに、アクティブチャネル領域 126 を、望まれるよりもアクティブゲート 104 から遠くに有することによって、*F i n F E T* 102 のために望まれるよりも低い電圧しきい値が生じ得る。この低減された電圧しきい値によって、サブスレッショルド電流が増大し、その理由は、アクティブゲート 104 が、*F i n F E T* セル 100 の「オフ」状態中にアクティブチャネル領域 126 を完全に閉じることが可能でないことがあり、したがって、電力消費を増大させ、性能を低下させ得るからである。

#### 【0008】

電流漏れもまた、ダミーゲート 134 がドレインエピタキシャル領域 110 およびドレインコンタクト 124 の近くに位置することに基づいて生じ得る。*F i n F E T* 102 の

10

20

30

40

50

ピッチが低減されるにつれて、ダミーゲート134とドレインエピタキシャル領域110およびドレインコンタクト124との間の距離が低減され得る。たとえば、距離D<sub>2</sub>は、ピッチが低減されるにつれて低減され得る。ドレインコンタクト124とダミーゲート134との間がこのように極めて近接していることで、ダミーゲート134を通して潜在的なリーク電流経路148が生じることがあり、したがって、FinFET102の電力消費も増大し、性能も低下することがある。

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0009】

発明を実施するための形態で開示する態様は、隣接する非対称アクティブゲートノダミーゲート幅レイアウトを採用する電界効果トランジスタ(FET)デバイスを含む。例示的な態様では、ソース領域とドレイン領域との間のチャネル領域を制御するように構成されたアクティブゲートを有するFETデバイスを含む、FETセルが提供される。FETセルはまた、FETデバイスに隣接して配設された分離構造を含む。分離構造は、FETデバイスのソース領域およびドレイン領域のうちの1つに隣接して位置するディフュージョンブレークと、ディフュージョンブレークをオーバーレイするダミーゲートとを備える。FETセルは、ダミーゲートの幅がアクティブゲートの幅よりも小さいという点で、非対称アクティブゲートノダミーゲート幅レイアウトを有する。アクティブゲートの幅がより大きいことによって、チャネル領域に対するゲート制御の増大、およびしたがって、サブスレッショルドリーク電流の低減をもたらすことができる。

10

20

#### 【0010】

追加の例として、隣接する非対称アクティブゲートノダミーゲート幅レイアウトを提供することによって、より深いソースまたはドレインインプラントを生じる、ソースおよび/またはドレイン領域の理想的でない成長の悪影響も軽減され得る。ソースおよび/またはドレイン領域の理想的でない成長は、FETデバイスのチャネル領域を低下させ、したがって、アクティブゲートからより遠くにチャネル領域を配置する。さらに、別の例として、FETセルにおいてダミーゲートの幅をより小さくすることによって、FETデバイスのアクティブゲートがより大きい幅を有するにもかかわらず、FETセルがセルピッチを維持することが可能になる。さらに、別の例として、幅が縮小されたダミーゲートを設けることによって、現在の作製プロセスによるソース/ドレイン領域、インプラント、およびコンタクトの形成が可能になり得る。さらに、一例として、幅が縮小されたダミーゲートを設けることによって、ダミーゲートと隣接するソースおよび/またはドレイン領域との間の分離が増大し、したがって、FETデバイスとダミーゲートとの間の距離および分離が増大し、それによって、ダミーゲートを通したリーク電流が減少する。

30

#### 【0011】

この点について、一態様では、非対称ゲート幅レイアウトを有するFETセルが提供される。FETセルは、上面を有する本体を備える基板と、FETデバイスとを備える。FETデバイスは、基板中に配設されたソースを備える。FETデバイスは、基板中に配設されたドレインをさらに備える。FETデバイスは、ソースとドレインとの間に形成された、アクティブゲート幅のアクティブゲートをさらに備える。FETセルは、FETデバイスに隣接して、基板中に配設された分離構造をさらに備える。分離構造は、FETデバイスのソースおよびドレインのうちの1つに隣接して、基板中に配設されたディフュージョンブレークであって、ディフュージョンブレークに隣接する、ソースおよびドレインのうちの1つの深さが、ディフュージョンブレークに隣接していない、ソースおよびドレインのうちの1つの深さよりも大きい、ディフュージョンブレークを備える。分離構造は、アクティブゲートに隣接して、ディフュージョンブレークの上方に形成された、ダミーゲート幅のダミーゲートをさらに備える。ダミーゲート幅は、アクティブゲート幅よりもゲート幅マージンだけ小さい。

40

#### 【0012】

別の態様では、半導体ダイにおいてFETセルを作製する方法が提供される。方法は、

50

基板中に配設されたディフュージョンブレークを形成するステップを含む。方法は、基板上にアクティブゲート幅のアクティブゲートを形成するステップと、ディフュージョンブレークの上方に、およびアクティブゲートに隣接して、ダミーゲート幅のダミーゲートを形成するステップであって、ダミーゲート幅が、アクティブゲート幅よりもゲート幅マージンだけ小さい、ステップとをさらに含む。方法は、アクティブゲートに隣接して、基板中に FET デバイスのソースエピタキシャル領域を形成するステップと、基板の上面から第 1 の深さにおいて、ソースエピタキシャル領域中にソースを形成するステップとをさらに含む。方法は、アクティブゲートとダミーゲートとの間で、ディフュージョンブレークに隣接して、基板中に FET デバイスのドレンエピタキシャル領域を形成するステップであって、ドレンエピタキシャル領域の一部分がディフュージョンブレークと接触している、ステップと、第 1 の深さよりも大きい、基板の上面からの第 2 の深さにおいて、ドレンエピタキシャル領域中にドレンを形成するステップとをさらに含む。方法は、ソースとドレンとの間で、基板中に FET デバイスのチャネル領域を形成するステップをさらに含む。

10

#### 【0013】

別の態様では、非対称ゲート幅レイアウトを有する FET セルが提供される。FET セルは、上面を有する本体を備える基板を設けるための手段を備える。FET セルは、基板を設けるための手段の上面から第 1 の深さにおいて、基板を設けるための手段中に配設された、ソースを設けるための手段と、基板を設けるための手段の上面から第 2 の深さにおいて、基板を設けるための手段中に配設された、ドレンを設けるための手段とを備える、FET デバイスを設けるための手段をさらに備える。FET デバイスを設けるための手段は、ソースを設けるための手段とドレンを設けるための手段との間に形成された、アクティブゲート幅のアクティブゲートを設けるための手段をさらに備える。アクティブゲートを設けるための手段は、ソースを設けるための手段とドレンを設けるための手段との間で、アクティブゲートを設けるための手段の下方のチャネル領域における伝導率を制御するように構成される。FET セルは、FET デバイスを設けるための手段に隣接して、基板を設けるための手段中に配設された分離構造を設けるための手段をさらに備える。分離構造を設けるための手段は、FET デバイスを設けるための手段の、ソースを設けるための手段およびドレンを設けるための手段のうちの 1 つに隣接して、基板を設けるための手段中に配設された、ディフュージョンブレークを設けるための手段を備える。ディフュージョンブレークを設けるための手段に隣接する、ソースを設けるための手段およびドレンを設けるための手段のうちの 1 つの深さが、ディフュージョンブレークを設けるための手段に隣接していない、ソースを設けるための手段およびドレンを設けるための手段のうちの 1 つの深さよりも大きい。分離構造を設けるための手段は、アクティブゲートを設けるための手段に隣接して、ディフュージョンブレークを設けるための手段の上方に形成された、ダミーゲート幅のダミーゲートを設けるための手段をさらに備え、ダミーゲート幅が、アクティブゲート幅よりもゲート幅マージンだけ小さい。

20

30

#### 【図面の簡単な説明】

#### 【0014】

【図 1】従来のフィン電界効果トランジスタ (FET) (FinFET) セルの断面を示す図である。

40

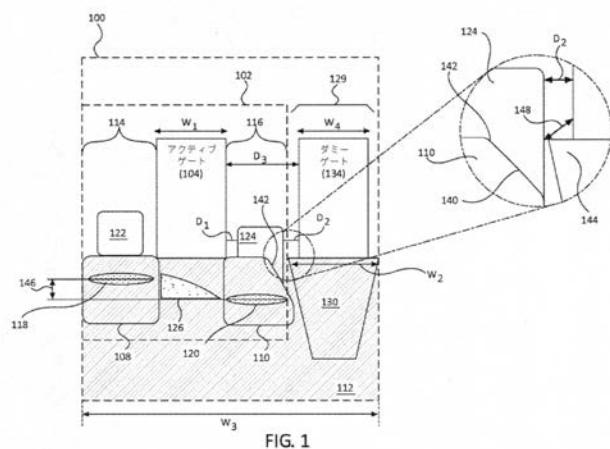

【図 2】リーク電流を低減するためのゲート制御の増大を促進することができる、隣接する非対称アクティブゲート / ダミーゲート幅レイアウトを採用する例示的な FinFET を含む、例示的な FinFET セルの断面を示す図である。

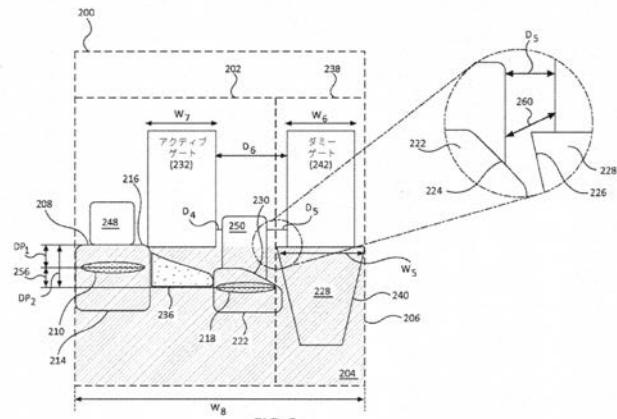

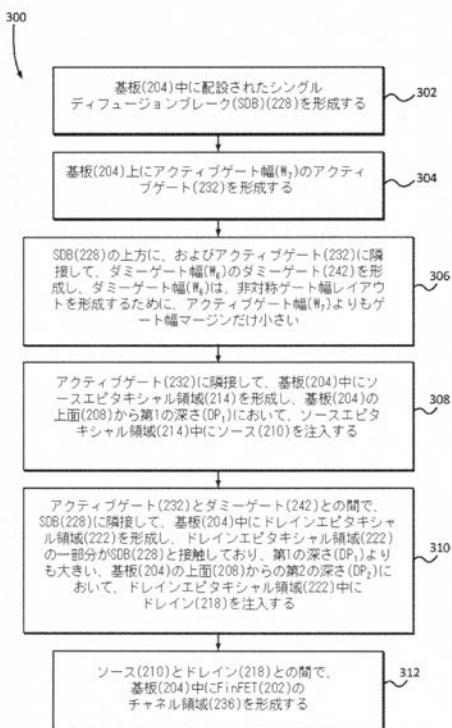

【図 3】図 2 の例示的な FinFET セルを作製するための例示的なプロセスを示すフローチャートである。

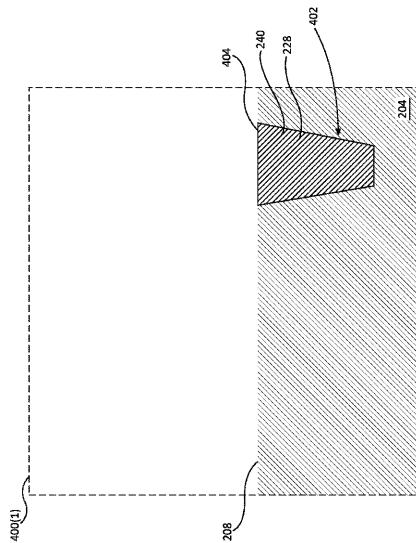

【図 4A】図 2 に示す例示的な FinFET セルを作製するため、基板中にディフュージョンブレークを形成する例示的な作製段階の断面図である。

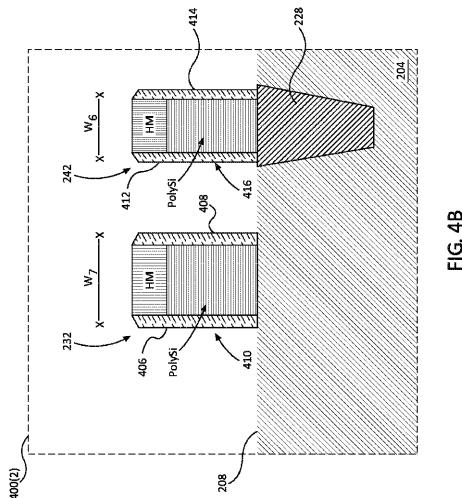

【図 4B】図 2 に示す例示的な FinFET セルを作製するため、基板上にアクティブゲート幅のアクティブゲートを形成し、ディフュージョンブレークの上方に、およびアク

50

ティップゲートに隣接して、ダミーゲート幅のダミーゲートを形成する例示的な作製段階の断面図であって、非対称ゲート幅レイアウトを形成するために、ダミーゲート幅がアクティブゲート幅よりもゲート幅マージンだけ小さい、断面図である。

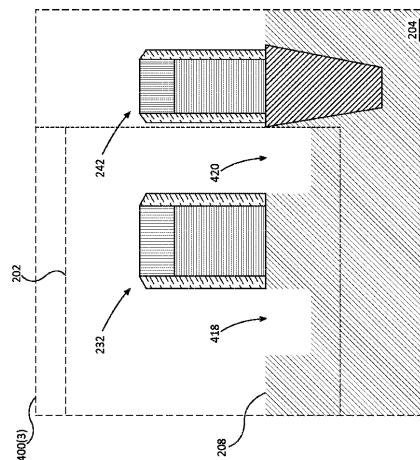

【図4C】図2に示す例示的なFinFETセルを作製するための、ソースエピタキシャル領域およびドレインエピタキシャル領域を堆積させるための基板上のエッチング凹部の例示的な作製段階の断面図である。

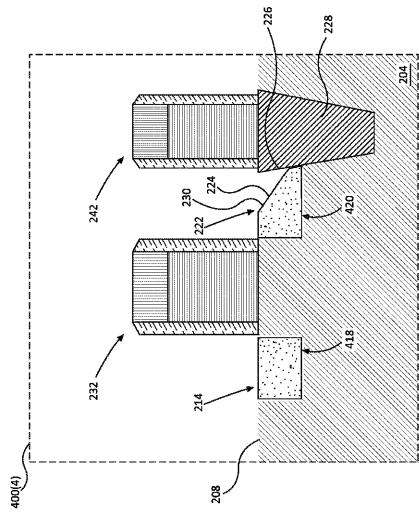

【図4D】図2に示す例示的なFinFETセルを作製するための、対応する凹部上のソースエピタキシャル領域およびドレインエピタキシャル領域の堆積の例示的な作製段階の断面図である。

【図4E】図2に示す例示的なFinFETセルを作製するための、ソースエピタキシャル領域およびドレインエピタキシャル領域中にそれぞれソースおよびドレインを形成する、例示的な作製段階の断面図である。

【図4F】図2に示す例示的なFinFETセルを作製するための、アクティブゲートに隣接して、ソースエピタキシャル領域上にソースコンタクトを配設し、アクティブゲートとダミーゲートとの間で、ドレインエピタキシャル領域上にドレインコンタクトを配設する、例示的な作製段階の断面図である。

【図5】図2に示す例示的なFinFETセルを含み得る、例示的なプロセッサベースシステムのブロック図である。

【図6】本明細書で開示する例示的な態様による、隣接する非対称アクティブゲート／ダミーゲート幅レイアウトを採用する例示的なFinFETを含む、FinFETセルを含む、無線周波数(RF)構成要素を含む例示的なワイヤレス通信デバイスのブロック図である。

#### 【発明を実施するための形態】

##### 【0015】

次に、図面を参照して、本開示のいくつかの例示的な態様について説明する。「例示的」という語は、「例、事例、または例示として機能すること」を意味するために本明細書で使用される。「例示的」として本明細書で説明するいずれの態様も、必ずしも他の態様よりも好ましいか、または有利であると解釈されるべきではない。

##### 【0016】

発明を実施するための形態で開示する態様は、隣接する非対称アクティブゲート／ダミーゲート幅レイアウトを採用する電界効果トランジスタ(FET)デバイスを含む。例示的な態様では、ソース領域とドレイン領域との間のチャネル領域を制御するように構成されたアクティブゲートを有するFETデバイスを含む、FETセルが提供される。FETセルはまた、FETデバイスに隣接して配設された分離構造を含む。分離構造は、FETデバイスのソース領域およびドレイン領域のうちの1つに隣接して位置するディフュージョンブレークと、ディフュージョンブレークをオーバーレイするダミーゲートとを備える。FETセルは、ダミーゲートの幅がアクティブゲートの幅よりも小さいという点で、非対称アクティブゲート／ダミーゲート幅レイアウトを有する。アクティブゲートの幅がより大きいことによって、チャネル領域に対するゲート制御の増大、およびしたがって、サブスレッショルドリーク電流の低減をもたらすことができる。

##### 【0017】

追加の例として、隣接する非対称アクティブゲート／ダミーゲート幅レイアウトを提供することによって、より深いソースまたはドレインインプラン트を生じる、ソースおよび／またはドレイン領域の理想的でない成長の悪影響も軽減され得る。ソースおよび／またはドレイン領域の理想的でない成長は、FETデバイスのチャネル領域を低下させ、したがって、アクティブゲートからより遠くにチャネル領域を配置する。さらに、別の例として、FETセルにおいてダミーゲートの幅をより小さくすることによって、FETデバイスのアクティブゲートがより大きい幅を有するにもかかわらず、FETセルがセルピッチを維持することが可能になる。さらに、別の例として、幅が縮小されたダミーゲートを設けることによって、現在の作製プロセスによるソース／ドレイン領域、インプラント、お

10

20

30

40

50

およびコンタクトの形成が可能になり得る。さらに、一例として、幅が縮小されたダミーゲートを設けることによって、ダミーゲートと隣接するソースおよび／またはドレイン領域との間の分離が増大し、したがって、FETデバイスとダミーゲートとの間の距離および分離が増大し、それによって、ダミーゲートを通したリーク電流が減少する。

#### 【0018】

この点について、図2は、隣接する非対称アクティブゲート／ダミーゲート幅レイアウトを採用する例示的なFinFET202を含む、例示的なFinFETセル200の断面を示す。図2に示すように、FinFETセル200は、上面208を有する本体206を備える基板204を含む。FinFETセル200は、FinFET202に隣接して、基板204中に配設された分離構造238を備える。分離構造238は、たとえば、隣接するFinFETセルなど、隣接するセル（図示せず）からFinFET202を分離させるために、FinFETセル200中に配設される。分離構造238は、シングルディフュージョンブレーク（SDB）228を備え、FinFET202のドレイン218に隣接して、基板204中に配設される。SDB228は、幅W<sub>5</sub>を有し、たとえば、シャロートレンチ分離（STI）酸化物240を備え得る。分離構造238は、アクティブゲート232に隣接して、SDB228の上方に形成された、ダミーゲート幅W<sub>6</sub>のダミーゲート242をさらに備える。

10

#### 【0019】

FinFETセル200のFinFET202は、基板204の上面208から深さD<sub>P</sub><sub>1</sub>において、基板204中に配設されたソース210を備える。FinFET202のソース210は、イオン注入によって、基板204中のソースエピタキシャル領域214上に形成される。一例として、ソースエピタキシャル領域214は、基板204中で、シリコンゲルマニウム（SiGe）またはゲルマニウム（Ge）のエピタキシャル成長を含み得る。FinFETセル200のソースエピタキシャル領域214は、基板204の上面208と面一である平坦な上面216を有し得る。

20

#### 【0020】

引き続き図2を参照すると、FinFET202は、基板204の上面208から深さD<sub>P</sub><sub>2</sub>において、基板204中に配設されたドレイン218をさらに備え、深さD<sub>P</sub><sub>2</sub>は、深さD<sub>P</sub><sub>1</sub>よりも大きい。ドレイン218は、イオン注入によって、ドレインエピタキシャル領域222上に形成される。一例として、ドレインエピタキシャル領域222は、たとえば、基板204上で、シリコンゲルマニウム（SiGe）またはゲルマニウム（Ge）のエピタキシャル成長を備える。ドレイン218の深さD<sub>P</sub><sub>2</sub>は、ソース210の深さD<sub>P</sub><sub>1</sub>よりも大きく、その理由は、これらの深さD<sub>P</sub><sub>1</sub>、D<sub>P</sub><sub>2</sub>が、それぞれ、ソースエピタキシャル領域214およびドレインエピタキシャル領域222の上面216および上面230の高さおよび形状の関数であるからである。以下でさらに詳細に説明するように、ドレインエピタキシャル領域222の上面230は、平坦でなく、ソースエピタキシャル領域214の上面216よりも低い。したがって、ドレイン218は、基板204の上面208に対して、ソース210よりも低く形成される。明快のために、エピタキシャル領域214は、ソースエピタキシャル領域214として定義されており、エピタキシャル領域214のソース210は、ソース210として定義されており、エピタキシャル領域222は、ドレインエピタキシャル領域222として定義されており、エピタキシャル領域222のドレイン218は、ドレイン218として定義されていることに留意されたい。しかしながら、これらの要素のソース／ドレイン指示は一例であり、FinFET202が回路においてどのように接続されるかに基づいて、ソースまたはドレインのためのものとして指示されることがあり、その理由は、チャネル領域236が固有の極性を有していないからである。

30

#### 【0021】

図2における例示的なFinFETセル200に示すように、ドレインエピタキシャル領域222は不均一に成長させられた。この不均一な成長は、ドレインエピタキシャル領域222のファセット224と、ドレインエピタキシャル領域222に隣接して配設され

40

50

た S D B 2 2 8 のファセット 2 2 6 との間の、ファセット不整合に起因し、したがって、S D B 2 2 8 のファセット 2 2 6 の近くのドレインエピタキシャル領域 2 2 2 の成長が妨害される。したがって、S D B 2 2 8 のファセット 2 2 6 の近くのドレインエピタキシャル領域 2 2 2 の成長は、S D B 2 2 8 のファセット 2 2 6 から離れたドレインエピタキシャル領域 2 2 2 の成長よりも遅く、およびしたがって基板 2 0 4 中でより低くなる。したがって、ドレインエピタキシャル領域 2 2 2 は、S D B 2 2 8 の近くでより低い、平坦でない上面 2 3 0 を有する。

#### 【 0 0 2 2 】

引き続き図 2 を参照すると、F i n F E T 2 0 2 はまた、ソース 2 1 0 とドレイン 2 1 8 との間に形成された、アクティブゲート幅 W<sub>7</sub> のアクティブゲート 2 3 2 を備える。F i n F E T 2 0 2 は、ソース 2 1 0 とドレイン 2 1 8 との間で、アクティブゲート 2 3 2 の下方にチャネル領域 2 3 6 をさらに備える。したがって、アクティブゲート 2 3 2 は、電圧がそれに印加されるとき、アクティブゲート 2 3 2 によって生成された電界（図示せず）に基づいて、ソース 2 1 0 とドレイン 2 1 8 との間のチャネル領域 2 3 6 における伝導率を制御するように構成される。

10

#### 【 0 0 2 3 】

F i n F E T 2 0 2 は、ソース 2 1 0 へのアクセスを与るために、アクティブゲート 2 3 2 に隣接して、ソースエピタキシャル領域 2 1 4 上に配設されたソースコンタクト 2 4 8 をさらに含む。F i n F E T 2 0 2 は、ドレイン 2 1 8 へのアクセスを与るために、アクティブゲート 2 3 2 とダミーゲート 2 4 2 との間で、ドレインエピタキシャル領域 2 2 2 上に配設されたドレインコンタクト 2 5 0 をさらに含む。ドレインコンタクト 2 5 0 は、アクティブゲート 2 3 2 から距離 D<sub>4</sub> だけ分離される。ドレインコンタクト 2 5 0 は、ダミーゲート 2 4 2 から距離 D<sub>5</sub> だけ分離される。

20

#### 【 0 0 2 4 】

F i n F E T セル 2 0 0 において、ドレインエピタキシャル領域 2 2 2 の不均一な成長は、ゲート制御の低減、およびサブスレッショルド電流の増大を生じ得る。具体的には、F i n F E T 2 0 2 中のソース 2 1 0 およびドレイン 2 1 8 の形成中に、たとえば、イオン注入を通して、ドレイン 2 1 8 が、ソース / ドレインインプラントマージン 2 5 6 だけ、ドレインエピタキシャル領域 2 2 2 において望まれるよりも深く、およびソース 2 1 0 よりも深くに配設され得る。これによって、基板 2 0 4 において望まれるよりも低く、したがって、望まれるよりもアクティブゲート 2 3 2 から遠い、チャネル領域 2 3 6 が生じる。チャネル領域 2 3 6 を、望まれるよりもアクティブゲート 2 3 2 から遠くに有することによって、チャネル領域 2 3 6 のゲート制御の低減、およびしたがって、F i n F E T 2 0 2 の性能の低下が生じ得る。

30

#### 【 0 0 2 5 】

この点について、図 2 における例示的な F i n F E T セル 2 0 0 において、チャネル領域 2 3 6 が基板 2 0 4 中でより低くに位置することに起因する、チャネル領域 2 3 6 のゲート制御の低減を軽減またはオフセットするために、ゲート幅マージン、すなわち、アクティブゲート幅 W<sub>7</sub> とダミーゲート幅 W<sub>6</sub> との間の差だけ、アクティブゲート幅 W<sub>7</sub> よりも小さいダミーゲート幅 W<sub>6</sub> を有するように、ダミーゲート 2 4 2 が F i n F E T セル 2 0 0 中に形成される。一例として、このゲート幅マージンは、少なくとも 2 ナノメートル (nm) であり得る。たとえば、約 2 nm であるゲート幅マージンでは、アクティブゲート幅 W<sub>7</sub> は約 1 5 nm であり得、ダミーゲート幅 W<sub>6</sub> は約 1 3 nm であり得る。この例示的な態様に鑑みて、F i n F E T セル 2 0 0 は、非対称アクティブゲート / ダミーゲートレイアウトを有し、その理由は、アクティブゲート 2 3 2 のアクティブゲート幅 W<sub>7</sub> が、隣接するダミーゲート 2 4 2 のダミーゲート幅 W<sub>6</sub> よりも大きいからである。増大したアクティブゲート幅 W<sub>7</sub> を有することによって、アクティブゲート 2 3 2 は、チャネル領域 2 3 6 に対する制御の改善をもたらす。この改善されたゲート制御によって、図 1 に示した F i n F E T セル 1 0 0 など、対称アクティブゲート / ダミーゲートレイアウトの F E T セルのアクティブゲートによってもたらされるゲート制御と比較して、F i n F E T 2

40

02におけるサブスレッショルドリーク電流が減少し、ドレインエピタキシャル領域222の理想的でない成長によって引き起こされるサブスレッショルドリーク電流の増大の少なくとも一部が無効になる。

#### 【0026】

しかしながら、アクティブゲート幅 $W_7$ を増大することによって、アクティブゲート232とダミーゲート242との間の距離 $D_6$ が低減し、それによって、ドレインエピタキシャル領域222のエピタキシャル成長と、ドレインエピタキシャル領域222へのドレイン218の注入とが妨害され得る。具体的には、距離 $D_6$ を低減することで、基板204中で材料を配設、エッチング、注入、または別法により形成するために、アクティブゲート232とダミーゲート242との間の必要な空間が設けられないことがある。この点について、例示的な態様では、ダミーゲート242のダミーゲート幅 $W_6$ は、ゲート幅マージン、すなわち、アクティブゲート幅 $W_7$ とダミーゲート幅 $W_6$ との間の差だけ、アクティブゲート幅 $W_7$ よりも小さく形成される。ダミーゲート幅 $W_6$ を縮小することによって、現在の作製プロセス、たとえば、図1に示したFinFETセル100を作製するために使用される作製プロセスによる、ドレインエピタキシャル領域222の形成が可能になる。さらに、ダミーゲート幅 $W_6$ を縮小することによって、ドレインコンタクト250とダミーゲート242との間の距離 $D_5$ 、および、ダミーゲート242と隣接するドレインコンタクト250との間の分離260が増大し、したがって、FinFET202をダミーゲート242からさらに分離させ、それによって、ダミーゲート242を通したリーク電流を減少させる。さらに、アクティブゲート幅 $W_7$ の増大が、ダミーゲート幅 $W_6$ の縮小に一致する一態様では、アクティブゲート232およびダミーゲート242に対する、ドレインコンタクト250の分離マージン（すなわち、距離 $D_5$ と距離 $D_4$ との間の差）は、ゲート幅マージン、すなわち、アクティブゲート幅 $W_7$ とダミーゲート幅 $W_6$ との間の差の約半分である。具体的には、アクティブゲート幅 $W_7$ の増大は、アクティブゲート232を、ソースコンタクト248およびドレインコンタクト250に向かって等しく拡大する。したがって、アクティブゲート232とドレインコンタクト250との間の距離 $D_4$ は、ドレインコンタクト250に向かうアクティブゲート幅 $W_7$ の増大だけ低減される。したがって、アクティブゲート232とドレインコンタクト250との間の距離 $D_4$ は、アクティブゲート幅 $W_7$ の増大の半分だけ低減される。

#### 【0027】

具体的には、FinFETセル100のための図1に示したレイアウトなど、対称アクティブゲート/ダミーゲートレイアウトでは、アクティブゲート幅 $W_1$ がいくつかのファクタによって制限される。たとえば、アクティブゲート104のアクティブゲート幅 $W_1$ は、FinFETセル100の全体の幅 $W_3$ が、基板112中のソースエピタキシャル領域108およびドレインエピタキシャル領域110の配設を可能にするために必要とされた、アクティブゲート幅 $W_1$ と、ダミーゲート134の幅 $W_4$ と、アクティブゲート104とダミーゲート134との間の距離 $D_3$ とを用いて、アクティブゲート104を形成しなければならないことによって制限される。したがって、FinFETセル100のための図1に示したレイアウトなど、対称アクティブゲート/ダミーゲートレイアウトにおけるゲート制御は、アクティブゲート幅 $W_1$ がなり得る最大幅によって制限される。しかしながら、本出願のFinFETセル200の非対称アクティブゲート/ダミーゲートレイアウトでは、アクティブゲート232のアクティブゲート幅 $W_7$ は、隣接するダミーゲート242のダミーゲート幅 $W_6$ よりも大きく形成され、したがって、図1に示したFinFETセル100のほぼ同じ幅 $W_3$ である幅 $W_8$ を有しながら、ゲート制御を増大させる。

#### 【0028】

追加として、低減されたダミーゲート幅 $W_6$ を有することによって、FinFETセル200が、アクティブゲート232の増大したアクティブゲート幅 $W_7$ を有するときでも、FinFETセル200が、図1に示したFinFETセル100の幅 $W_3$ と同様である幅 $W_8$ を維持することが可能になる。具体的には、一態様では、ダミーゲート242の

10

20

30

40

50

幅 $W_6$ は、アクティブゲート幅 $W_7$ が増大される同じ量だけ縮小され得る。これによって、FinFETセル200のアクティブゲート232とダミーゲート242との間の距離 $D_6$ が、図1に示したFinFETセル100のアクティブゲート104とダミーゲート134との間の距離 $D_3$ と同様またはほぼ同じであるように設けられることになる。また、これによって、FinFETセル200の幅 $W_8$ が、図1に示したFinFETセル100の幅 $W_3$ と同様またはほぼ同じであるように設けられ得る。ダミーゲート242の幅 $W_6$ を低減することによって、ダミーゲート242と隣接するドレインコンタクト250との間の距離 $D_5$ を増大し、したがって、ダミーゲート242とドレインコンタクト250との間の短絡の危険性を低減することができる。したがって、FinFETセル200は、図1に示したFinFETセル100を作製するために使用される同様の作製方法を使用して作製され得る。

10

20

30

**【0029】**

上記で説明した例示的な態様では、ゲート幅マージンは、一例として、少なくとも2nmとして定義された。さらなる一例として、アクティブゲート幅 $W_7$ は約15nmとして、ダミーゲート幅 $W_6$ は約13nmとして定義され、約2nmであるゲート幅マージンがもたらされた。さらなる一例では、約3nmであるゲート幅マージンをもたらすために、アクティブゲート幅 $W_7$ は約17nmであり得、ダミーゲート幅 $W_6$ は約14nmであり得る。別の態様では、ゲート幅マージンは、たとえば、少なくとも4nmであり得る。したがって、たとえば、約4nmであるゲート幅マージンをもたらすために、アクティブゲート幅 $W_7$ は約18nmであり得、ダミーゲート幅 $W_6$ は約14nmであり得る。より大きいゲート幅マージンを有することによって、ゲート幅マージンのない実装形態よりも増大したゲート制御がもたらされ、その理由は、より大きいアクティブゲート幅 $W_7$ が、チャネル領域236上で増大した電界(図示せず)、およびしたがって、チャネル領域236に対する制御の増大を生じるからである。さらに、より大きいゲート幅マージンを有することによって、ゲート幅マージンのない実装形態よりも、ダミーゲート242を通したリーキ電流が減少し、その理由は、より狭いダミーゲート幅 $W_6$ によって、ダミーゲート242と隣接するドレインコンタクト250との間の分離260の増大が生じ、したがって、FinFET202がダミーゲート242からさらに分離され、それによって、ダミーゲート242を通したリーキ電流が減少するからである。

30

**【0030】**

図2におけるFinFETセル200など、隣接する非対称アクティブゲート/ダミーゲート幅レイアウトを採用するFinFETセルは、任意の所望の作製プロセスに従って作製され得る。たとえば、図3は、図2における隣接する非対称アクティブゲート/ダミーゲート幅レイアウトを採用する例示的なFinFETセル200を作製するための、例示的なプロセス300を示すフローチャートである。プロセス300におけるステップを、それぞれ図4A～図4Fに示す。図4A～図4Fは、以下で説明する図3におけるプロセス300における例示的なステップとして参照される。

40

**【0031】**

図2に示すFinFETセル200を作製するための第1の例示的なステップは、基板204中に配設されたSDB228を形成することを含む(図3におけるプロック302)。この点について、図4Aは、SDB228が基板204中に形成されている段階400(1)を示す。たとえば、基板204中にSDB228を形成することは、たとえば、SDB228をシャロートレンチ分離(STI)酸化物240として形成するために、基板204上で凹部402をエッチングすること、および、酸化物などの絶縁材料を堆積させることによって実行され得る。SDB228を形成することは、たとえば、基板204の上面208と面一のSDB228の上面404を形成するために、化学機械平坦化(CMPs)を使用して、SDB228を研磨することをさらに含み得る。

40

**【0032】**

図2に示すFinFETセル200を作製するための第2の例示的なステップは、基板204上にアクティブゲート幅 $W_7$ のアクティブゲート232を形成することを含む(図

50

3におけるブロック304)。図2に示すFinFETセル200を作製するための第3の例示的なステップは、SDB228の上方に、およびアクティブゲート232に隣接して、ダミーゲート幅W<sub>6</sub>のダミーゲート242を形成することを含む。ダミーゲート幅W<sub>6</sub>は、非対称ゲート幅レイアウトを形成するために、アクティブゲート幅W<sub>7</sub>よりもゲート幅マージンだけ小さく形成される(図3におけるブロック306)。この点について、図4Bは、アクティブゲート幅W<sub>7</sub>のアクティブゲート232が基板204上に形成されている段階400(2)を示す。段階400(2)は、ダミーゲート幅W<sub>6</sub>のダミーゲート242がSDB228の上方に形成されている場合をさらに示す。アクティブゲート232およびダミーゲート242を形成することは、ポリシリコン(PolySi)層およびハードマスク(HM)層を配設すること、ならびに、ポリシリコン層およびハードマスク層をエッチングすることによって実行され得る。アクティブゲート232およびダミーゲート242を形成することは、スペーサ層406および408を堆積させて、ゲート電極ピラー410を形成すること、ならびに、スペーサ層412および414を堆積させて、ゲート電極ピラー416を形成することをさらに含み得る。ゲート電極ピラー410および416は、それぞれアクティブゲート232およびダミーゲート242に対応する。

#### 【0033】

図2に示すFinFETセル200を作製するための第4の例示的なステップは、アクティブゲート232に隣接して、基板204中にFinFET202のソースエピタキシャル領域214を形成すること、および、基板204の上面208から深さDP<sub>1</sub>において、ソースエピタキシャル領域214中にソース210を注入することを含む(図3におけるブロック308)。図2に示すFinFETセル200を作製するための第5の例示的なステップは、アクティブゲート232とダミーゲート242との間で、SDB228に隣接して、基板204中にドレインエピタキシャル領域222を形成することであって、ドレインエピタキシャル領域222の一部分がSDB228と接触していること、および、深さDP<sub>1</sub>よりも大きい、基板204の上面208からの深さDP<sub>2</sub>において、ドレインエピタキシャル領域222中にドレイン218を注入することを含む(図3におけるブロック310)。この点について、図4Cは、それぞれソースエピタキシャル領域214およびドレインエピタキシャル領域222を堆積させるための、基板204上の凹部418および凹部420のエッチングが、基板204上で実行されている段階400(3)を示す。

#### 【0034】

さらに、図4Dは、それぞれ、凹部418および420上のソースエピタキシャル領域214およびドレインエピタキシャル領域222の堆積が実行されている段階400(4)を示す。段階400(4)は、特に、ドレインエピタキシャル領域222が不均一に成長することを示す。この不均一な成長は、ドレインエピタキシャル領域222のファセット224と、SDB228のファセット226との間のファセット不整合に起因する。このファセット224、226の不整合は、SDB228のファセット226の近くのドレインエピタキシャル領域222の成長を妨害する。したがって、ドレインエピタキシャル領域222の成長は、SDB228のファセット226の近くで、SDB228のファセット226から離れたドレインエピタキシャル領域222の成長よりも遅く、およびしたがって低くなる。したがって、ドレインエピタキシャル領域222は、SDB228の近くでより低く、アクティブゲート232の近くでより高い、平坦でない上面230を有する。

#### 【0035】

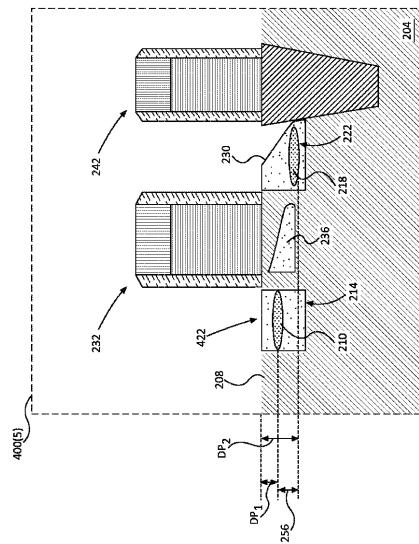

さらに、図4Eは、それぞれ、ソースエピタキシャル領域214およびドレインエピタキシャル領域222中のソース210およびドレイン218の注入が実行されている段階400(5)を示す。図4Eは、ソース210が、基板204の上面208から深さDP<sub>1</sub>において注入されることを示す。図4Eは、ドレイン218が、深さDP<sub>1</sub>よりもソース/ドレインインプラントマージン256だけ大きい、基板204の上面208からの深さDP<sub>2</sub>において注入されることをさらに示す。これらの注入は、たとえば、イオン注入

10

20

30

40

50

によって実行され得る。ドレイン 218 のより深い注入は、ドレインエピタキシャル領域 222 の不均一な成長の結果である。具体的には、注入は、たとえば、ソースエピタキシャル領域 214 およびドレインエピタキシャル領域 222 上で等しく実行される時間ベースのプロセスに基づいて実行される。ドレインエピタキシャル領域 222 の不均一な成長は、上面 230 が、部分的に、ソースエピタキシャル領域 214 の上面 422 よりも低くなることを引き起こし、それによって、ドレイン 218 の注入に、ソース 210 と比較してより深いドレイン 218 を生じさせる。

#### 【0036】

図 2 に示す FinFET セル 200 を作製するための第 6 の例示的なステップは、ソース 210 とドレイン 218 との間で、基板 204 中に FinFET 202 のチャネル領域 236 を形成することを含む（図 3 におけるブロック 312）。この点について、図 4 E に示す段階 400 (5) は、チャネル領域 236 を示し、チャネル領域 236 は、ソース 210 とドレイン 218 との間で、基板 204 中に形成され、たとえば、電圧（図示せず）がアクティブゲート 232 に印加されるとき、アクティブ化される。

10

#### 【0037】

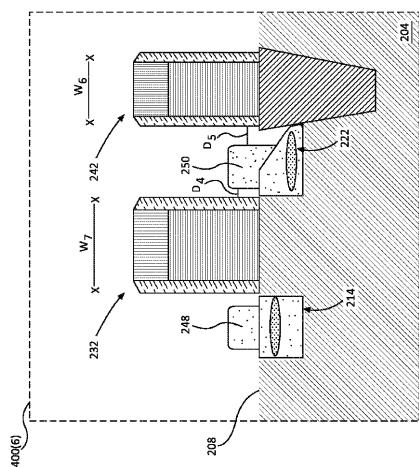

図 2 に示す FinFET セル 200 を作製するための第 7 の例示的なステップは、アクティブゲート 232 に隣接して、ソースエピタキシャル領域 214 上にソースコンタクト 248 を配設すること、および、アクティブゲート 232 とダミーゲート 242との間で、ドレインエピタキシャル領域 222 上にドレインコンタクト 250 を配設することであって、ドレインコンタクト 250 が、隣接するアクティブゲート 232 から距離  $D_4$  だけ分離され、隣接するダミーゲート 242 から距離  $D_5$  だけ分離されることを含む。この点について、図 4 F は、断面図において第 7 のステップの段階 400 (6) を示す。段階 400 (6) は、アクティブゲート 232 に隣接して、ソースエピタキシャル領域 214 上に配設されたソースコンタクト 248 を示す。段階 400 (6) は、アクティブゲート 232 とダミーゲート 242 の間で、ドレインエピタキシャル領域 222 上に配設された、ドレインコンタクト 250 をさらに示す。前に説明したように、増大したアクティブゲート幅  $W_7$  および低減したダミーゲート幅  $W_6$  は、距離  $D_5$  が距離  $D_4$  よりも大きくなることを生じる。これによって、ダミーゲート 242 からの FinFET 202 の分離を向上させ、それによって、ダミーゲート 242 を通したリーク電流を減少させる。

20

#### 【0038】

他の態様では、リーク電流を低減するためのゲート制御の増大を促進することができる、隣接する非対称アクティブゲート / ダミーゲート幅レイアウトを採用する例示的な FinFET を含む、例示的な FinFET セルはまた、基板を設けるための手段を含み得る。基板を設けるための手段の一例を、図 2 および図 4 A ~ 図 4 F において基板 204 として示す。FinFET セルはまた、基板を設けるための手段中に配設された、ソースを設けるための手段と、基板を設けるための手段中に配設された、ドレインを設けるための手段と、ソースを設けるための手段とドレインを設けるための手段との間に形成された、アクティブゲート幅のアクティブゲートを設けるための手段とを備える、FET デバイスを設けるための手段を含み得る。FET デバイスを設けるためのそのような手段の一例を、図 2 において FinFET 202 として示す。アクティブゲートを設けるための手段の一例を、図 2 および図 4 B ~ 図 4 F において示すアクティブゲート 232 として示す。FinFET セルはまた、FET デバイスを設けるための手段の、ソースを設けるための手段およびドレインを設けるための手段のうちの 1 つに隣接して、基板を設けるための手段中に配設された、ディフュージョンブレークを設けるための手段を備える、基板を設けるための手段中に配設された、分離構造を設けるための手段を含み得る。分離構造を設けるための手段は、アクティブゲートを設けるための手段に隣接して、ディフュージョンブレークを設けるための手段の上方に形成された、ダミーゲート幅のダミーゲートを設けるための手段をさらに備える。分離構造を設けるためのそのような手段の一例を、図 2 において示す分離構造 238 として示す。

30

#### 【0039】

40

50

本明細書で開示する態様による、隣接する非対称アクティブゲート／ダミーゲート幅レイアウトを採用するF E Tデバイスは、任意のプロセッサベースデバイスにおいて設けられ、またはそれに組み込まれ得る。この例には、限定はしないが、セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイルフォン、セルラーフォン、スマートフォン、タブレット、ファブレット、サーバ、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末（P D A）、モニタ、コンピュータモニタ、テレビ、チューナー、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク（D V D）プレーヤ、ポータブルデジタルビデオプレーヤ、および自動車が含まれる。

10

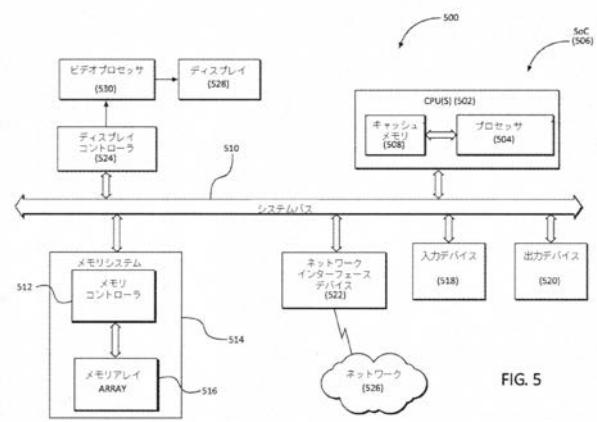

#### 【0040】

この点について、図5は、図2に示す例示的なF i n F E Tセル200を含み得る、例示的なプロセッサベースシステム500のブロック図である。この例では、プロセッサベースシステム500は、1つまたは複数のプロセッサ504を各々が含む、1つまたは複数のC P U 5 0 2を含む。プロセッサベースシステム500は、システムオンチップ（S o C）506として設けられ得る。C P U 5 0 2は、一時的に記憶されたデータに迅速にアクセスするために、プロセッサ504に結合されたキャッシュメモリ508を有する場合がある。C P U 5 0 2は、システムバス510に結合され、プロセッサベースシステム500内に含まれるマスタデバイスとスレーブデバイスとを相互結合することができる。よく知られているように、C P U 5 0 2は、システムバス510を介してアドレス情報、制御情報、およびデータ情報を交換することによって、これらの他のデバイスと通信する。たとえば、C P U 5 0 2は、スレーブデバイスの一例として、メモリシステム514内のメモリコントローラ512にバストランザクション要求を通信することができる。図5には示さないが、複数のシステムバス510を設けることができ、各システムバス510は異なるファブリックを構成する。この例では、メモリコントローラ512は、メモリシステム514の中のメモリアレイ516にメモリアクセス要求を与えるように構成される。

20

#### 【0041】

他のデバイスがシステムバス510に接続され得る。図5に示すように、これらのデバイスは、例として、メモリシステム514、1つまたは複数の入力デバイス518、1つまたは複数の出力デバイス520、1つまたは複数のネットワークインターフェースデバイス522、ならびに1つまたは複数のディスプレイコントローラ524を含み得る。入力デバイス518は、限定はしないが、入力キー、スイッチ、音声プロセッサなどを含む、任意のタイプの入力デバイスを含み得る。出力デバイス520は、限定はしないが、オーディオ、ビデオ、他の視覚的インジケータなどを含む、任意のタイプの出力デバイスを含み得る。ネットワークインターフェースデバイス522は、ネットワーク526との間のデータの交換を可能にするように構成された任意のデバイスであり得る。ネットワーク526は、限定はしないが、ワイヤードネットワークまたはワイヤレスネットワーク、プライベートネットワークまたは公衆ネットワーク、ローカルエリアネットワーク（L A N）、ワイヤレスローカルエリアネットワーク（W L A N）、ワイドエリアネットワーク（W A N）、B L U E T O O T H（登録商標）ネットワーク、およびインターネットを含む、任意のタイプのネットワークであり得る。ネットワークインターフェースデバイス522は、任意のタイプの所望の通信プロトコルをサポートするように構成され得る。

30

#### 【0042】

C P U 5 0 2はまた、1つまたは複数のディスプレイ528に送られる情報を制御するために、システムバス510を介してディスプレイコントローラ524にアクセスするように構成され得る。ディスプレイコントローラ524は、1つまたは複数のビデオプロセッサ530を介して表示されるべき情報をディスプレイ528に送り、1つまたは複数のビデオプロセッサ530は、表示されるべき情報をディスプレイ528に適したフォーマ

40

50

ットになるように処理する。ディスプレイ 528 は、限定はしないが、陰極線管（C R T）、液晶ディスプレイ（L C D）、プラズマディスプレイなどを含む任意のタイプのディスプレイを含み得る。

#### 【0043】

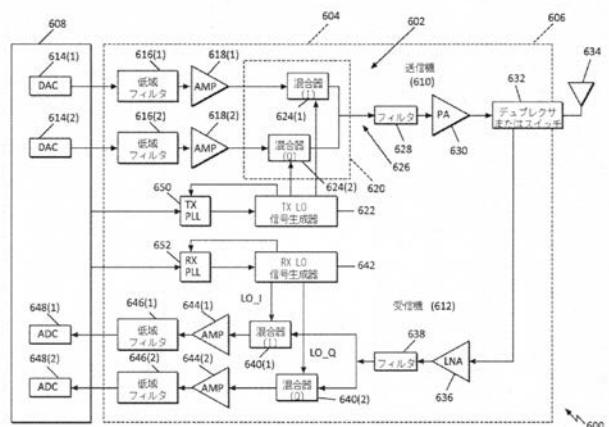

図 6 は、限定はしないが、図 2 における F i n F E T セル 200 を含む、隣接する非対称アクティブゲート / ダミーゲート幅レイアウトを採用する例示的な F i n F E T を含む、F i n F E T セルが含まれ得る、R F 構成要素を含み得る、ワイヤレス通信デバイス 600 の一例を示す。この点について、隣接する非対称アクティブゲート / ダミーゲート幅レイアウトを採用する例示的な F i n F E T を含む、F i n F E T セルを含む、ワイヤレス通信デバイス 600 は、集積回路（I C）606 中に設けられ得る。ワイヤレス通信デバイス 600 は、例として、上記のデバイスのうちのいずれかを含んでもよく、またはその中に設けられてもよい。図 6 に示すように、ワイヤレス通信デバイス 600 は、トランシーバ 604 とデータプロセッサ 608 とを含む。データプロセッサ 608 は、データおよびプログラムコードを記憶するためのメモリ（図示せず）を含み得る。トランシーバ 604 は、双方向通信をサポートする送信機 610 と受信機 612 とを含む。一般に、ワイヤレス通信デバイス 600 は、任意の数の通信システム向けおよび周波数バンド向けに、任意の数の送信機および / または受信機を含んでもよい。トランシーバ 604 の全部または一部は、1つまたは複数のアナログ I C、R F I C（R F I C）、混成信号 I C などの上に実装され得る。

10

#### 【0044】

送信機 610 または受信機 612 は、スーパー・ヘテロダイニアーキテクチャまたは直接変換アーキテクチャを用いて実装され得る。スーパー・ヘテロダイニアーキテクチャでは、信号は、受信機 612 に関して、複数の段において R F とベースバンドとの間で、たとえば、1つの段において R F から中間周波数（I F）に、次いで、別の段において I F からベースバンドに周波数変換される。直接変換アーキテクチャでは、信号は、1つの段において、R F とベースバンドとの間で周波数変換される。スーパー・ヘテロダイニアーキテクチャおよび直接変換アーキテクチャは、異なる回路ブロックを使用すること、および / または異なる要件を有することがある。図 6 におけるワイヤレス通信デバイス 600 では、送信機 610 および受信機 612 は、直接変換アーキテクチャを用いて実装される。

20

#### 【0045】

送信経路では、データプロセッサ 608 は、送信されるべきデータを処理し、I および Q アナログ出力信号を送信機 610 に提供する。例示的なワイヤレス通信デバイス 600 では、データプロセッサ 608 は、データプロセッサ 608 によって生成されるデジタル信号を、さらなる処理のために、I および Q アナログ出力信号、たとえば、I および Q 出力電流へと変換するための、デジタルアナログ変換器（D A C）614（1）および 614（2）を含む。

30

#### 【0046】

送信機 610 内で、低域フィルタ 616（1）、616（2）が、それぞれ、I および Q アナログ出力信号をフィルタ処理して、前のデジタルアナログ変換によって引き起こされた不要なイメージを除去する。増幅器（A M P）618（1）、618（2）は、それぞれ、低域フィルタ 616（1）、616（2）からの信号を増幅し、I および Q ベースバンド信号を供給する。アップコンバータ 620 は、送信（T X）局部発振器（L O）信号生成器 622 から混合器 624（1）、624（2）を通る I および Q T X L O 信号で、I および Q ベースバンド信号をアップコンバートして、アップコンバートされた信号 626 を提供する。フィルタ 628 は、アップコンバートされた信号 626 をフィルタ処理して、周波数アップコンバージョンによって引き起こされた不要なイメージ、ならびに受信周波数バンドの中の雑音を除去する。電力増幅器（P A）630 は、所望の出力電力レベルを取得するために、フィルタ 628 からのアップコンバートされた信号 626 を増幅して、送信 R F 信号を提供する。送信 R F 信号は、デュプレクサまたはスイッチ 632 を通して経路指定され、アンテナ 634 を介して送信される。

40

50

## 【0047】

受信経路では、アンテナ 634 は、基地局によって送信された信号を受け取り、受信 R F 信号を提供し、受信 R F 信号は、デュプレクサまたはスイッチ 632 を通して経路指定され、低雑音増幅器 (LNA) 636 に提供される。デュプレクサまたはスイッチ 632 は、R X 信号が T X 信号から隔離されるように、特定の R X - T X デュプレクサ周波数分離で動作するように設計される。受信 R F 信号は、LNA 636 によって増幅され、フィルタ 638 によってフィルタ処理されて、所望の R F 入力信号が取得される。ダウンコンバージョン混合器 640(1)、640(2) は、フィルタ 638 の出力を、受信 (R X ) L O 信号生成器 642 からの I および Q R X L O 信号 (すなわち、L O\_I および L O\_Q) と混合し、I および Q ベースバンド信号を生成する。I および Q ベースバンド信号は、増幅器 (AMP) 644(1)、644(2) によって増幅され、低域フィルタ 646(1)、646(2) によってさらにフィルタ処理されて、I および Q アナログ入力信号が取得され、I および Q アナログ入力信号はデータプロセッサ 608 に提供される。この例では、データプロセッサ 608 は、データプロセッサ 608 によってさらに処理するために、アナログ入力信号をデジタル信号へと変換するためのアナログデジタル変換器 (ADC) 648(1)、648(2) を含む。

10

## 【0048】

図 6 におけるワイヤレス通信デバイス 600 では、T X L O 信号生成器 622 が、周波数アップコンバージョンに使用される I および Q T X L O 信号を生成する一方で、R X L O 信号生成器 642 が、周波数ダウンコンバージョンに使用される I および Q R X L O 信号を生成する。各 L O 信号は、特定の基本周波数を有する周期信号である。送信 (T X ) 位相ロックループ (PLL) 回路 650 は、データプロセッサ 608 からタイミング情報を受け取り、T X L O 信号生成器 622 からの T X L O 信号の周波数および / または位相を調整するために使用される制御信号を生成する。同様に、受信 (R X ) 位相ロックループ (PLL) 回路 652 は、データプロセッサ 608 からタイミング情報を受け取り、R X L O 信号生成器 642 からの R X L O 信号の周波数および / または位相を調整するために使用される制御信号を生成する。

20

## 【0049】

当業者は、本明細書で開示する態様に関して説明する様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムが、電子ハードウェア、メモリ内もしくは別のコンピュータ可読媒体内に記憶され、プロセッサもしくは他の処理デバイスによって実行される命令、または両方の組合せとして実装され得ることをさらに諒解されよう。本明細書で説明するマスタデバイスおよびスレーブデバイスは、例として、任意の回路、ハードウェア構成要素、集積回路 (IC)、または IC チップにおいて採用され得る。本明細書で開示するメモリは、任意のタイプおよびサイズのメモリであってよく、任意のタイプの希望の情報を記憶するように構成され得る。この互換性を明確に示すために、様々な例示的な構成要素、ブロック、モジュール、回路、およびステップについて、上記では概してそれらの機能性に関して説明した。そのような機能性がどのように実装されるのかは、特定の適用例、設計選択、および / またはシステム全体に課される設計制約によって決まる。当業者は、特定の適用例ごとに様々な方式で記載の機能を実装してもよいが、そのような実装の決定が、本開示の範囲からの逸脱を引き起こすと解釈されるべきではない。

30

## 【0050】

本明細書で開示する態様に関して説明する様々な例示的な論理ブロック、モジュール、および回路は、プロセッサ、デジタル信号プロセッサ (DSP)、特定用途向け集積回路 (ASIC)、フィールドプログラマブルゲートアレイ (FPGA) もしくは他のプログラマブル論理デバイス、個別ゲートもしくはトランジスタ論理、個別ハードウェア構成要素、または本明細書で説明する機能を実行するように設計されたこれらの任意の組合せを用いて実装または実行され得る。プロセッサは、マイクロプロセッサであってもよいが、代替としてプロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、またはステートマシンであってもよい。プロセッサはまた、コンピューティングデバ

40

50

イスの組合せ、たとえば、D S Pとマイクロプロセッサとの組合せ、複数のマイクロプロセッサ、D S Pコアと連携した1つもしくは複数のマイクロプロセッサ、または任意の他のそのような構成として実装され得る。

#### 【0051】

本明細書で開示する態様は、ハードウェアにおいて具現化されてもよく、かつハードウェア内に記憶され、たとえば、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、電気的プログラマブルROM(E PROM)、電気的消去可能プログラマブルROM(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野において知られている任意の他の形態のコンピュータ可読媒体の中に存在し得る命令において具現化されてもよい。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取るとともに記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替として、記憶媒体は、プロセッサと一緒にある場合がある。プロセッサおよび記憶媒体は、A S I Cの中に存在する場合がある。A S I Cは、リモート局の中に存在する場合がある。代替として、プロセッサおよび記憶媒体は、個別構成要素としてリモート局、基地局、またはサーバの中に存在する場合がある。

10

#### 【0052】

本明細書の例示的な態様のいずれかで説明した動作ステップが、例示および説明を提供するために記載されていることにも留意されたい。説明する動作は、図示のシーケンス以外の多数の異なるシーケンスにおいて実行される場合がある。さらに、単一の動作ステップにおいて説明する動作は、実際にはいくつかの異なるステップにおいて実行される場合がある。さらに、例示的な態様において説明する1つまたは複数の動作ステップは、組み合わせられる場合がある。フローチャート図に示した動作ステップは、当業者には容易に明らかであるように、多数の異なる変更を受ける場合があることを理解されたい。当業者であれば、様々な異なる技術および技法のいずれかを使用して情報および信号が表され得ることも理解するであろう。たとえば、上記の説明全体にわたって参照される場合があるデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁気粒子、光場もしくは光学粒子、またはそれらの任意の組合せによって表される場合がある。

20

#### 【0053】

本開示のこれまでの説明は、任意の当業者が本開示を作製または使用できるようにするために提供される。本開示の様々な変更が当業者に容易に明らかになり、本明細書で定義する一般原理は、本開示の趣旨または範囲から逸脱することなく他の変形形態に適用され得る。したがって、本開示は、本明細書で説明した例および設計に限定されるものではなく、本明細書で開示した原理および新規の特徴と一致する最も広い範囲を与えられるべきである。

30

#### 【符号の説明】

#### 【0054】

2 0 0 F i n F E T セル

40

2 0 2 F i n F E T

2 0 4 基板

2 0 6 本体

2 0 8 、 2 1 6 、 2 3 0 、 4 0 4 、 4 2 2 上面

2 1 0 ソース

2 1 4 ソースエピタキシャル領域、エピタキシャル領域

2 1 8 ドレイン

2 2 2 ドレインエピタキシャル領域、エピタキシャル領域

2 2 4 、 2 2 6 ファセット

2 2 8 シングルディフュージョンブレーク(S D B)、S D B

2 3 2 アクティブゲート

50

|                                                                   |                                          |    |

|-------------------------------------------------------------------|------------------------------------------|----|

| 2 3 6                                                             | チャネル領域                                   |    |

| 2 3 8                                                             | 分離構造                                     |    |

| 2 4 0                                                             | シャロートレンチ分離( S T I )酸化物                   |    |

| 2 4 2                                                             | ダミーゲート                                   |    |

| 2 4 8                                                             | ソースコンタクト                                 |    |

| 2 5 0                                                             | ドレインコンタクト                                |    |

| 2 5 6                                                             | ソース/ドレインインプラントマージン                       |    |

| 2 6 0                                                             | 分離                                       |    |

| 4 0 0 ( 1 )、4 0 0 ( 2 )、4 0 0 ( 3 )、4 0 0 ( 4 )、4 0 0 ( 5 )、4 0 0 |                                          |    |

| ( 6 ) 段階                                                          |                                          | 10 |

| 4 0 2、4 1 8、4 2 0                                                 | 凹部                                       |    |

| 4 0 6、4 0 8、4 1 2、4 1 4                                           | スペーサ層                                    |    |

| 4 1 0、4 1 6                                                       | ゲート電極ピラー                                 |    |

| 5 0 0                                                             | プロセッサベースシステム                             |    |

| 5 0 2                                                             | C P U                                    |    |

| 5 0 4                                                             | プロセッサ                                    |    |

| 5 0 6                                                             | システムオンチップ( S o C )                       |    |

| 5 0 8                                                             | キャッシュメモリ                                 |    |

| 5 1 0                                                             | システムバス                                   |    |

| 5 1 2                                                             | メモリコントローラ                                | 20 |

| 5 1 4                                                             | メモリシステム                                  |    |

| 5 1 6                                                             | メモリアレイ                                   |    |

| 5 1 8                                                             | 入力デバイス                                   |    |

| 5 2 0                                                             | 出力デバイス                                   |    |

| 5 2 2                                                             | ネットワークインターフェースデバイス                       |    |

| 5 2 4                                                             | ディスプレイコントローラ                             |    |

| 5 2 6                                                             | ネットワーク                                   |    |

| 5 2 8                                                             | ディスプレイ                                   |    |

| 5 3 0                                                             | ビデオプロセッサ                                 |    |

| 6 0 0                                                             | ワイヤレス通信デバイス                              | 30 |

| 6 0 4                                                             | トランシーバ                                   |    |

| 6 0 6                                                             | 集積回路( I C )                              |    |

| 6 0 8                                                             | データプロセッサ                                 |    |

| 6 1 0                                                             | 送信機                                      |    |

| 6 1 2                                                             | 受信機                                      |    |

| 6 1 4 ( 1 )、6 1 4 ( 2 )                                           | デジタルアナログ変換器( D A C )                     |    |

| 6 1 6 ( 1 )、6 1 6 ( 2 )、6 4 6 ( 1 )、6 4 6 ( 2 )                   | 低域フィルタ                                   |    |

| 6 1 8 ( 1 )、6 1 8 ( 2 )、6 4 4 ( 1 )、6 4 4 ( 2 )                   | 増幅器( A M P )                             |    |

| 6 2 0                                                             | アップコンバータ                                 |    |

| 6 2 2                                                             | 送信( T X )局部発振器( L O )信号生成器、T X L O 信号生成器 | 40 |

| 6 2 4 ( 1 )、6 2 4 ( 2 )                                           | 混合器                                      |    |

| 6 2 6                                                             | アップコンバートされた信号                            |    |

| 6 2 8、6 3 8                                                       | フィルタ                                     |    |

| 6 3 0                                                             | 電力増幅器( P A )                             |    |

| 6 3 2                                                             | デュプレクサまたはスイッチ                            |    |

| 6 3 4                                                             | アンテナ                                     |    |

| 6 3 6                                                             | 低雑音増幅器( L N A )、L N A                    |    |

| 6 4 0 ( 1 )、6 4 0 ( 2 )                                           | ダウンコンバージョン混合器                            |    |

| 6 4 2                                                             | 受信( R X )L O 信号生成器、R X L O 信号生成器         |    |

| 6 4 8 ( 1 )、6 4 8 ( 2 )                                           | アナログデジタル変換器( A D C )                     | 50 |

650 送信(TX)位相ロックループ(PLL)回路

652 受信(RX)位相ロックループ(PLL)回路

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4A】

FIG. 4A

【図4B】

FIG. 4B

【図4C】

FIG. 4C

【図4D】

FIG. 4D

【図4E】

FIG. 4E

【図4F】

FIG. 4F

【図5】

FIG. 5

【図 6】

FIG. 6

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2017/047747

A. CLASSIFICATION OF SUBJECT MATTER

INV. H01L21/336 H01L29/78

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                       | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2014/264572 A1 (KIM SUNG-MIN [KR] ET AL) 18 September 2014 (2014-09-18)<br>paragraph [0065] - paragraph [0068];<br>figure 24<br>----- | 1-19                  |

| A         | US 2015/243659 A1 (HUANG YU-LIEN [TW] ET AL) 27 August 2015 (2015-08-27)<br>paragraph [0023] - paragraph [0024]<br>-----                 | 1-19                  |

| X         | US 2015/115373 A1 (YU SHAO-MING [TW] ET AL) 30 April 2015 (2015-04-30)<br>paragraph [0022] - paragraph [0030];<br>figure 3<br>-----      | 1-19                  |

| A         | US 9 368 496 B1 (YU HONG [US] ET AL)<br>14 June 2016 (2016-06-14)<br>figure 1A<br>-----<br>-/-                                           | 1-19                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

27 November 2017

04/12/2017

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Hoffmann, Niels

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2017/047747 |

|---------------------------------------------------|

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                   | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 2016/111320 A1 (SHEN HONGLIANG [US] ET AL) 21 April 2016 (2016-04-21)<br>paragraph [0025]<br>paragraph [0030]<br>paragraph [0052]<br>-----<br>A US 2015/021695 A1 (HU ZHENYU [US] ET AL) 22 January 2015 (2015-01-22)<br>the whole document<br>-----<br>A US 2013/015524 A1 (HSU CHUN-WEI [TW] ET AL) 17 January 2013 (2013-01-17)<br>the whole document<br>----- | 1-19                  |

| 1         |                                                                                                                                                                                                                                                                                                                                                                      |                       |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2017/047747 |

|---------------------------------------------------|

| Patent document cited in search report |    | Publication date |                      | Patent family member(s)                                      |  | Publication date                                     |

|----------------------------------------|----|------------------|----------------------|--------------------------------------------------------------|--|------------------------------------------------------|

| US 2014264572                          | A1 | 18-09-2014       | CN<br>KR<br>TW<br>US | 104051270 A<br>20140113141 A<br>201435975 A<br>2014264572 A1 |  | 17-09-2014<br>24-09-2014<br>16-09-2014<br>18-09-2014 |

| US 2015243659                          | A1 | 27-08-2015       | US<br>US             | 2015243659 A1<br>2017338228 A1                               |  | 27-08-2015<br>23-11-2017                             |

| US 2015115373                          | A1 | 30-04-2015       |                      | NONE                                                         |  |                                                      |

| US 9368496                             | B1 | 14-06-2016       |                      | NONE                                                         |  |                                                      |

| US 2016111320                          | A1 | 21-04-2016       |                      | NONE                                                         |  |                                                      |

| US 2015021695                          | A1 | 22-01-2015       | US<br>US             | 2015021695 A1<br>2016163862 A1                               |  | 22-01-2015<br>09-06-2016                             |

| US 2013015524                          | A1 | 17-01-2013       | US<br>US             | 2013015524 A1<br>2014106558 A1                               |  | 17-01-2013<br>17-04-2014                             |

---

フロントページの続き

(81)指定国・地域 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,ST,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,R0,RS,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DJ,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IR,IS,JO,JP,KE,KG,KH,KN,KP,KR,KW,KZ,LA,LK,LR,LS,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT

(72)発明者 ウクジン・ロー

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 シャシャンク・エクボテ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

F ターム(参考) 5F140 AA24 AB01 BB05 BF04 BG08 BH07 BH27 BK13 BK18 CB04

CB06 CE07