(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6302871号

(P6302871)

(45) 発行日 平成30年3月28日(2018.3.28)

(24) 登録日 平成30年3月9日(2018.3.9)

(51) Int.Cl.

F 1

|             |                |                  |      |         |   |

|-------------|----------------|------------------|------|---------|---|

| <b>H05K</b> | <b>3/36</b>    | <b>(2006.01)</b> | H05K | 3/36    | Z |

| <b>H01R</b> | <b>13/6469</b> | <b>(2011.01)</b> | H01R | 13/6469 |   |

| <b>H01R</b> | <b>12/57</b>   | <b>(2011.01)</b> | H01R | 12/57   |   |

| <b>H05K</b> | <b>1/02</b>    | <b>(2006.01)</b> | H05K | 1/02    | J |

| <b>H01P</b> | <b>3/04</b>    | <b>(2006.01)</b> | H01P | 3/04    |   |

請求項の数 13 外国語出願 (全 23 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2015-116738 (P2015-116738) |

| (22) 出願日     | 平成27年6月9日(2015.6.9)          |

| (65) 公開番号    | 特開2016-6874 (P2016-6874A)    |

| (43) 公開日     | 平成28年1月14日(2016.1.14)        |

| 審査請求日        | 平成28年2月12日(2016.2.12)        |

| (31) 優先権主張番号 | 62/009, 801                  |

| (32) 優先日     | 平成26年6月9日(2014.6.9)          |

| (33) 優先権主張国  | 米国(US)                       |

| (31) 優先権主張番号 | 14/707, 965                  |

| (32) 優先日     | 平成27年5月8日(2015.5.8)          |

| (33) 優先権主張国  | 米国(US)                       |

前置審査

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 390005049<br>ヒロセ電機株式会社<br>東京都品川区大崎5丁目5番23号 |

| (74) 代理人  | 100094569<br>弁理士 田中 伸一郎                    |

| (74) 代理人  | 100088694<br>弁理士 弟子丸 健                     |

| (74) 代理人  | 100067013<br>弁理士 大塚 文昭                     |

| (74) 代理人  | 100086771<br>弁理士 西島 幸喜                     |

| (74) 代理人  | 100109070<br>弁理士 須田 洋之                     |

| (74) 代理人  | 100109335<br>弁理士 上杉 浩                      |

最終頁に続く

(54) 【発明の名称】電気コネクタにおける遠端クロストークを低減するための方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の極性の差動遠端クロストーク(FEXT)を有する第1の電気構成要素と、前記第1の電気構成要素に結合されかつ第2の極性の差動FEXTを有する第2の電気構成要素と、を備え、

前記第1の極性は、FEXTキャンセレーションを生じさせるために前記第2の極性の反対の極性であり、

前記第1の電気構成要素が、少なくとも2つの信号ビアの対を備えるプリント回路基板を備え、前記第2の電気構成要素が、複数の信号導体を備える電気コネクタを備え、前記少なくとも2つの信号ビアの対が、前記電気コネクタの前記複数の信号導体によって取り付けられるように構成された少なくとも2つの信号パッドの対に接続され。

10

前記複数の信号導体が、正極性の差動FEXTを誘起するように構成されたエッジ結合型のビアに接続される、及び/又は、負極性の差動FEXTを誘起するように構成されたプロードサイド結合型のビアに接続される、電気システム。

## 【請求項 2】

前記少なくとも2つの信号ビアの対の第1の対が、前記少なくとも2つの信号ビアの第2の対に関連する第1の位置に、前記少なくとも2つの信号ビアの前記第1の対および前記第2の対の少なくとも一方の極性が前記複数の信号導体の少なくとも1つの対の差動FEXTの極性の反対の差動FEXTの極性を有するように配置される、請求項1に記載の電気システム。

**【請求項 3】**

前記第1の電気構成要素が前記第2の電気構成要素に表面実装によって結合される、請求項1に記載の電気システム。

**【請求項 4】**

前記第1の電気構成要素が前記第2の電気構成要素にポールグリッドアレイ（BGA）によって結合される、請求項1に記載の電気システム。

**【請求項 5】**

前記第1の電気構成要素および前記第2の電気構成要素の一方が、負極性の差動FEXTを誘起するように構成されたブロードサイド結合型のビアを備え、かつ、前記第1の電気構成要素および前記第2の電気構成要素の他方が、正極性の差動FEXTを誘起するように構成されたエッジ結合型のビアを備える、請求項1に記載の電気システム。10

**【請求項 6】**

前記第1の電気構成要素および前記第2の電気構成要素の一方が、負極性の差動FEXTを誘起するように構成されたブロードサイド結合型のビアを備える、請求項1に記載の電気システム。

**【請求項 7】**

前記第1の電気構成要素および前記第2の電気構成要素の一方が、正極性の差動FEXTを誘起するように構成されたエッジ結合型のビアを備える、請求項1に記載の電気システム。

**【請求項 8】**

コネクタを備え、前記第1の電気構成要素が、正極性の差動FEXT極性を誘起するように構成されたエッジ結合構造を有する前記コネクタの第1の部分を備え、前記第2の電気構成要素が、負極性の差動FEXTを誘起するように構成されたブロードサイド結合構造を有する前記コネクタの第2の部分を備え、前記コネクタの前記第1の部分において誘起された前記正極性の差動FEXT極性のFEXTキャンセレーションをもたらす、請求項1に記載の電気システム。20

**【請求項 9】**

電気コネクタの信号導体が上に取り付けられた少なくとも2つの信号パッドの対に電気的に接続された少なくとも2つの信号ビアの対を備えるプリント回路基板（PCB）であって、30

前記少なくとも2つの信号ビアの対の第1の対が、前記少なくとも2つの信号ビアの第2の対に関連する位置に配置され、前記第1の対および前記第2の対の一方であるアグレッサのビアの対によってもたらされる差動FEXTの極性が、前記信号導体のうちのアグレッサの信号導体によってもたらされる差動FEXTの極性と反対であり、

前記信号導体が、正極性の差動FEXTを誘起するように構成された前記PCBのエッジ結合型のビアに接続される、及び／又は、負極性の差動FEXTを誘起するように構成された前記PCBのブロードサイド結合型のビアに接続される、

プリント回路基板（PCB）。

**【請求項 10】**

前記第1の対が、第1の入力ポートおよび第2の入力ポートを備える入力差動ポートを備え、前記第2の対が、第1の出力ポートおよび第2の出力ポートを備える出力差動ポートを備え、前記第1の対および前記第2の対が、40

前記第1の入力ポートから前記第1の出力ポートまでの第1のシングルエンド散乱パラメータと前記第2の入力ポートから前記第2の出力ポートまでの第2のシングルエンド散乱パラメータとの和と、

前記第1の入力ポートから前記第2の出力ポートまでの第3のシングルエンド散乱パラメータと前記第2の入力ポートから前記第1の出力ポートまでの第2のシングルエンド散乱パラメータとの和と、の差に、前記入力差動ポートから前記出力差動ポートまでの差動FEXTが基づくように配置される、請求項9に記載のPCB。

**【請求項 11】**

前記第1の対が、前記第2の対に関連する前記位置に、前記第1の対および前記第2の対の少なくとも一方の極性が前記信号導体のうちの少なくとも1つの対の差動F E X Tの極性の反対の差動F E X Tの極性を有するように、配置される、請求項9に記載のP C B。

【請求項12】

前記信号導体に表面実装によって結合される、請求項9に記載のP C B。

【請求項13】

前記信号導体にボールグリッドアレイ(B G A)によって結合される、請求項9に記載のP C B。

【発明の詳細な説明】

10

【技術分野】

【0001】

関連出願の相互参照

本出願は、あらゆる目的のために参照によりその全体が本明細書に組み込まれている、2014年6月9日に出願された米国仮特許出願第62/009,801号の優先権を主張する。

【0002】

本明細書に記載するシステム、装置、方法、および実施形態は、一般には遠端クロストーク(F E X T)を低減するためのシステムを、また、さらに具体的には差動信号を送信している電気コネクタおよびめっきスルーホールにおけるF E X Tの低減を対象とする。

20

【背景技術】

【0003】

電気通信産業においてより高い帯域幅に対する需要が増大し続ける中で、各デバイスはより高い計算処理能力およびルーティング能力を必要とし得る。各信号チャネルのデータ転送速度は、信号密度が増大し続けるにつれて増大し続ける。結果として、望ましくないノイズ、または隣接するチャネルの間で発生する電磁結合が、著しく増大する。シングルエンドデータ線と比較して高速での適用可能性およびノイズの低減を求めて、差動シグナリングがデータ送信のための好ましい関連技術の方法となっている。

【0004】

差動ピクティム対に関して考えると、隣接するアグレッサ対からの望ましくない電磁結合(たとえば、クロストーク)は、これらの隣接する対のうちの少なくとも1つが作動しているときに、データ送信経路全体にわたって発生する。アグレッサの送信機およびピクティムの受信機が物理的に互いに遠く離れている(たとえば、異なるチップに位置する)場合、信号と同じ方向に誘起されたクロストークは遠端クロストーク、またはF E X Tと呼ばれる。

30

【0005】

一般に、チップパッケージ、コネクタ、およびビアは、信号線に非常に近接していることから、F E X Tの主要な発生源となる。プリント回路基板(P C B)上のビア領域におけるF E X Tを、スペースを増大させること、差動対同士の間に接地を追加すること、差動対の中の結合を密にすること、または誘導結合係数および容量結合係数のバランスをとることによって低減しようとする、いくつかの試みがなされている。関連技術の一実施形態では、2つの隣接するビアの対は、ビア自体のF E X Tを低減するために対称的につつ等距離とされる。

40

【0006】

しかし、そのような関連技術の試みは、割り振られた表面積の消費を増大させ、設計および実施において困難をもたらし、また、特により高周波数のシステムで累積合計F E X Tを低減することにおいて比較的不十分であった。したがって、合計F E X Tを低減するための追加の方法の必要性がある。

【発明の概要】

【課題を解決するための手段】

50

**【0007】**

実施形態では、FEXTを低減するための1つの方法は、容量結合および誘導結合のバランスをとることによるものである。FEXTが容量結合と誘導結合との差に比例するという概念は、少なくとも、低周波数における2線の無損失システムに関して有効である。FEXTは、インピーダンス不整合ならびに抵抗結合および導電結合にも依存する。マルチラインシステムにおいてはまたは高周波数では、RLGC結合（ここでRは抵抗性、Lは誘導性、Gは導電性、およびCは容量性である）の代わりにモード分解を使用してFEXTを説明することができる。

**【0008】**

本明細書に記載する本開示および例は、FEXT（または差動FEXT）が累積的であるという概念に基づいて、システム中の（シングルエンドFEXTではなく）合計差動FEXTを低減することを対象とする。本開示は、本開示が差動FEXT結合において正または負のいずれかの極性を与えるように4つの個々のシングルエンドの項を操作することによって高周波数でマルチラインかつ有損失システムに適用されるという点において、関連技術におけるような容量結合および誘導結合のバランスをとることとは異なる。

10

**【0009】**

入力としてのポート1および2（集合的に差動ポート1とする）と出力としてのポート5および6（集合的に差動ポート3とする）とを有する第1の対、ならびに入力としてのポート3および4（集合的に差動ポート2とする）と出力としてのポート7および8（集合的に差動ポート4とする）とを有する第2の対を備える、2つの結合された差動対のシステムについて、差動ポート1から差動ポート4までの差動FEXTすなわちSDD41は、 $S_{D D \ 4 \ 1} = (S_{7 \ 1} + S_{8 \ 2} - S_{7 \ 2} - S_{8 \ 1}) / 2$ によって与えられ、式中*Sij*はポート*j*からポート*i*までのシングルエンド散乱パラメータ（またはSパラメータ）を表す。したがって、 $S_{7 \ 1} + S_{8 \ 2}$ が $S_{8 \ 1} + S_{7 \ 2}$ より大きい場合、正極性の差動FEXTが存在し、また、 $S_{8 \ 1} + S_{7 \ 2}$ が $S_{7 \ 1} + S_{8 \ 2}$ より大きい場合、負極性の差動FEXTが存在する。シングルエンドの各項 $S_{7 \ 1}$ 、 $S_{8 \ 1}$ 、 $S_{7 \ 2}$ 、または $S_{8 \ 2}$ が、より誘導的に結合するかより容量的に結合するかは低周波数での検知では重要ではない。

20

**【0010】**

構造の幾何学形状および／または位置を構成することによって、 $S_{8 \ 1} + S_{7 \ 2}$ よりも $S_{7 \ 1} + S_{8 \ 2}$ を大きくまたは小さくすることのいずれかができる、このことは正極性のまたは負極性のSDD41をもたらし得る。一例は、ブロードサイド結合された（ブロードサイド結合型の）構造が負極性の差動FEXTをもたらし、またエッジ結合された（エッジ結合型の）構造が正極性の差動FEXTをもたらすというものである。したがって、システムがブロードサイド結合型の構造およびエッジ結合型の構造の両方を含む場合、合計累積差動FEXTはより小さくなる傾向を有する。このFEXT極性最適化技法は、チップパッケージ、コネクタ、プリント回路基板（PCB）、またはFEXTを経験する任意の差動システムに適用可能である。

30

**【0011】**

実施形態では、反対の極性を有する電気構成要素を含む任意の電気システムを利用してFEXTを低減することができる。本明細書に記載する実施形態は、データ伝送のための方法として高速差動シグナリングが使用されるパーソナルコンピュータ、サーバ、スイッチ、およびルータなどの用途に適用され得る。

40

**【0012】**

一実施形態では、第1の極性を有する第1の電気構成要素は第2の極性を有する第2の電気構成要素に接続され、この場合第2の極性は第1の極性と反対である。構成要素間の反対の極性を利用することによって、電気システムにわたる累積差動FEXTを低減し得る。本開示の実施形態では、コネクタ構成要素に接続されたビアまたはPCB構成要素が存在する。しかし、反対の極性の構成要素の実施は、パッケージングすべきビア／PCB構成要素、コネクタの第2の部分に機械的に接続されたコネクタの第1の部分（たとえば、ツーピースコネクタ、スリーピースコネクタ）など、複数の構成要素を含む任意の電気

50

システムにおいて実施され得る。

**【0013】**

本開示の一態様では、この着想は、電気コネクタなどのような隣接する発生源で誘起された差動FEXTを考慮することによって、PCBビア設計において実施される。既存のビア設計技術を用いて、ビアの差動対同士の間に多くの接地ビアがシールドとして配置されるが、残留差動FEXTは依然としてコネクタのFEXTとともに累積する。実施形態では、FEXTキャンセレーションは、ブロードサイド結合型の差動対が差動FEXTの負極性をもたらす一方、エッジ結合型の差動対が正極性をもたらすことを理解することによって実現される。このことは、コネクタの差動FEXTを理解することによって、PCB設計者が自身のシステムにおいて差動FEXTキャンセレーションを実現するようにビア設計を選択することを可能にする。10

**【0014】**

本開示の実施のさらなる属性の例は、限定するものではないが、スペースの節約、PCBトレースの引き回しの容易さ、およびコネクタを介した安定した電力分配を含み得る。間隔を置いて配置される接地ビアおよび信号ビアを過度に多く配置することは、PCBの利用可能な場所をビア領域によって大きく消費し、ビアを回避してトレースを引き回すためのスペースが限られ、また電源層上に密に組み込まれたアンチパッドのためコネクタでの電力分配が不十分となるという結果をもたらす。本明細書に記載の実施形態を用いて、より少ない数の接地ビアを利用して、多くの場合、ビアよりもはるかに大きいものであるコネクタからのFEXTを相殺するための、十分なFEXTをビアで実現することができる。20

**【0015】**

先のおよび以下の記載は、例示的かつ説明的なものに過ぎず、いかなる点においても特許請求される発明またはその適用を限定することを意図していないことを理解されたい。

**【0016】**

本明細書に組み込まれかつその一部を構成する添付の図面は、本発明の実施形態を例証し、また、その説明とともに、本発明の技法の原理を説明し例示する役割を果たす。

**【図面の簡単な説明】**

**【0017】**

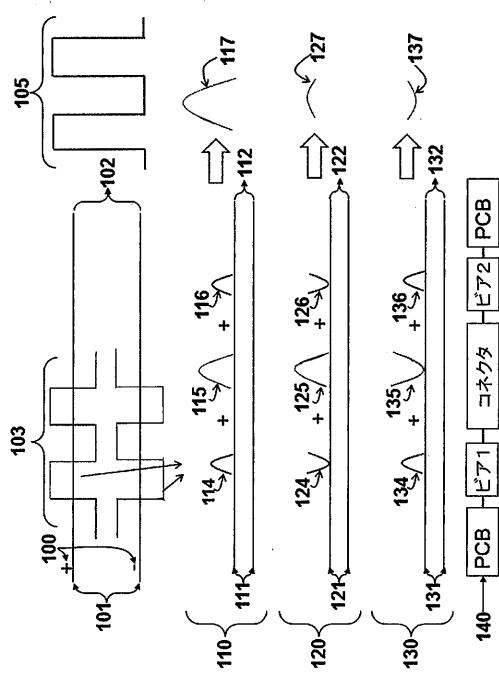

**【図1】**一実施形態による、コネクタ信号のPCB内へのルーティングのために使用されるビアのFEXT極性の最適化を行うおよびこれを行わない場合の、通信チャネル全体にわたるピクティムによるFEXTの累積を示す図である。30

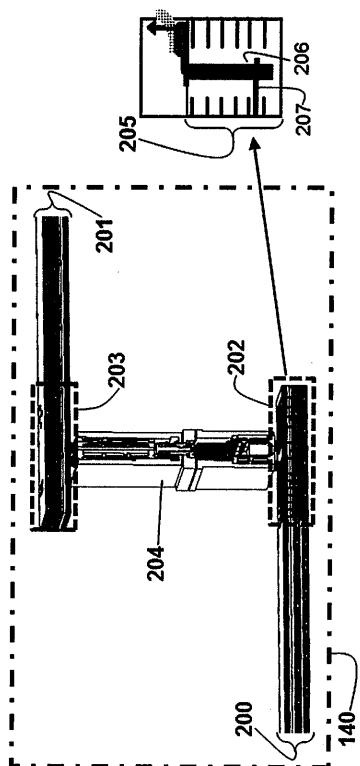

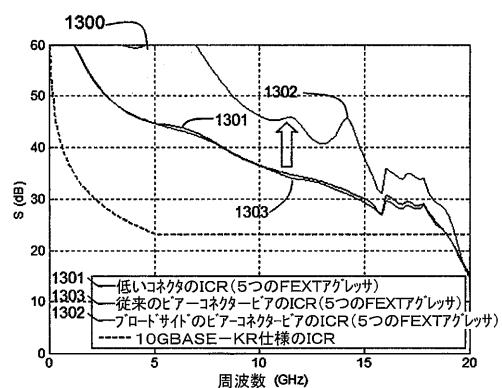

**【図2】**一実施形態による、図1に示すチャネル概略図の3D画像を示す図である。

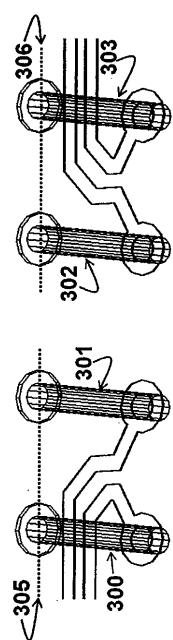

**【図3(a)】**一実施形態による、エッジ結合型のビアの例を示す図である。

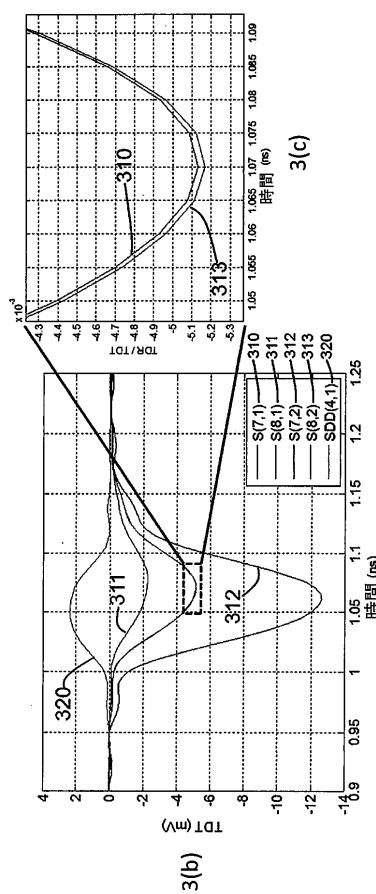

**【図3(b)-(c)】**一実施形態による、図3(a)のエッジ結合のビアに関する例示のグラフを示す図である。

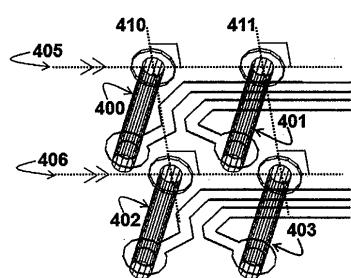

**【図4(a)】**一実施形態による、ブロードサイド結合型のビアの例を示す図である。

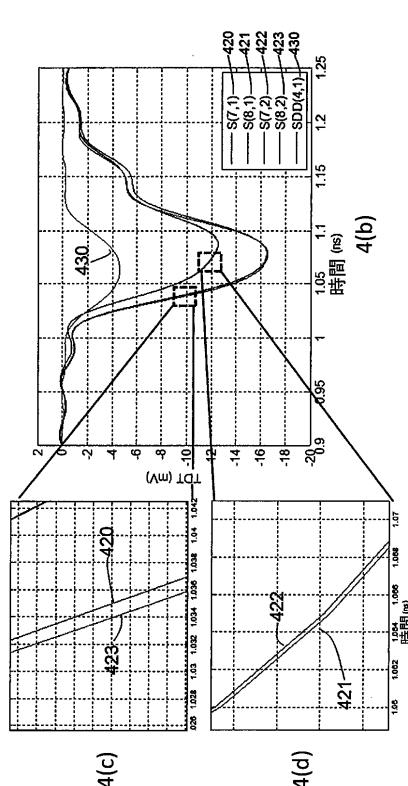

**【図4(b)-(d)】**一実施形態によるブロードサイド結合型のビアに関する例示のグラフを示す図である。

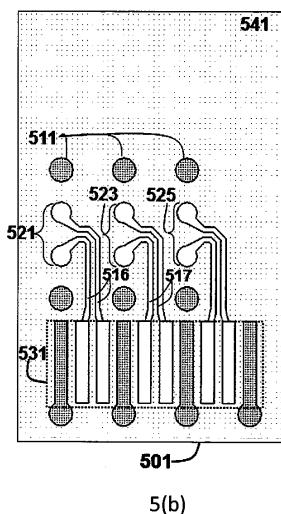

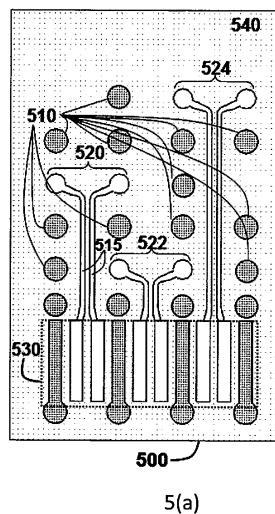

**【図5(a)-(b)】**従来のビアの引き回しおよび一実施形態による新規なビアの引き回しのレイアウトを示す、PCBの上面図である。40

**【図6(a)-(b)】**従来のビアの引き回しおよび一実施形態による新規なビアの引き回しの両方に関する、接地層上のアンチパッドを示す図である。

**【図7(a)-(b)】**一実施形態による、ビア領域における電源層上でのアンチパッドの組み込みを示す図である。

**【図8(a)-(d)】**エッジ結合型のビアが後に続く2つの差動マイクロストリップ対の正極性のFEXTによる、FEXT累積の一例を示す図である。

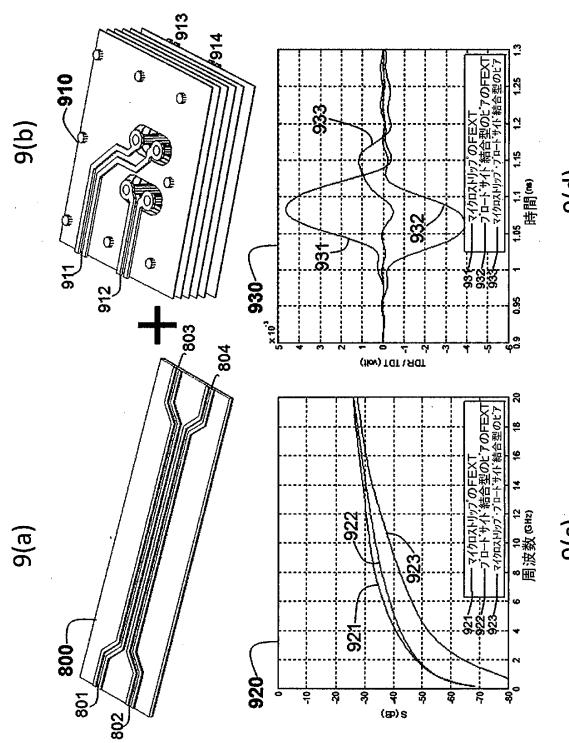

**【図9(a)-(d)】**一実施形態による、ブロードサイド結合型のビアの負極性のFEXTによって取り消される2つの差動マイクロストリップ対の正のFEXTの例を示す図である。50

【図10】一実施形態による、ビアのFEXTの大きさおよび極性に影響を及ぼす変形例を示す図である。

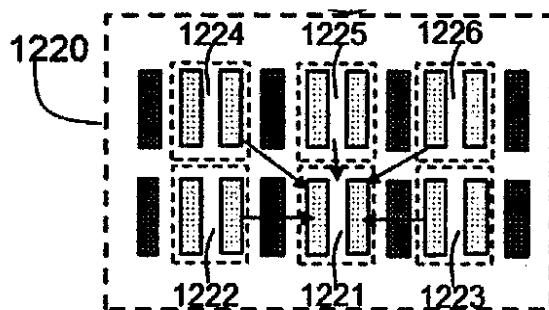

【図11】高速で、積層高さの低い、表面実装(SMT)型のコネクタに適用されるような、一実施形態を示す図である。

【図12(a)】一実施形態による、PCBのパッドのレイアウトを示す図である。

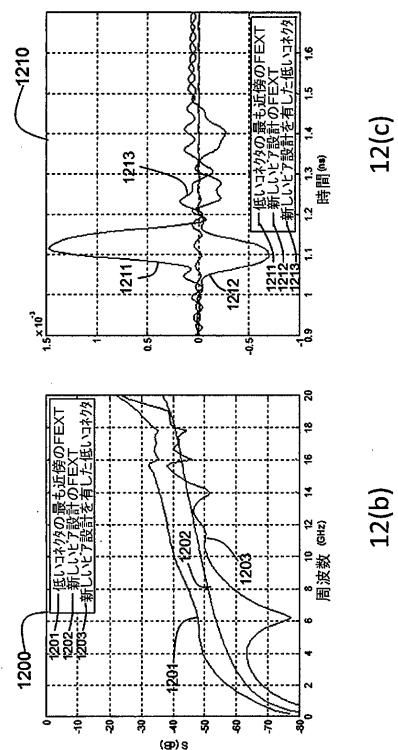

【図12(b)-(c)】一実施形態による、コネクタのみのモデル、ビアのみのモデル、およびビア-コネクタ-ビアのカスケード接続型のモデルに関する、周波数領域および時間領域における差動FEXTのグラフを示す図である。

【図13(a)】一実施形態による、対を示す図である。

【図13(b)】一実施形態による、SMT型のコネクタを示す図である。 10

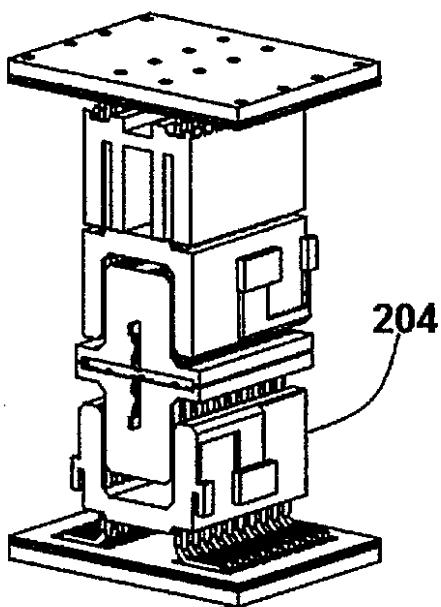

【図13(c)】一実施形態による、ビアモデルがカスケード接続されたおよびカスケード接続されていないコネクタの、挿入損失対クロストーク比(IRC:insertion loss-to-cross talk ratio)のグラフを示す図である。

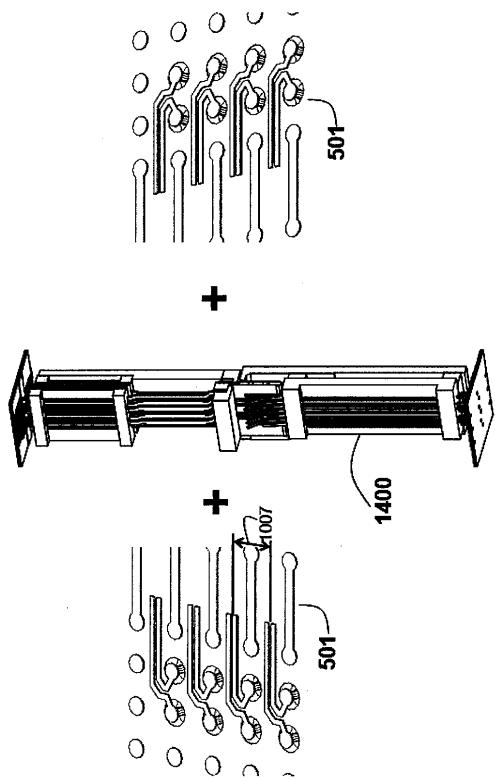

【図14】高速で、積層高さの高い、表面実装(SMT)型のコネクタに適用されるような、一実施形態を示す図である。

【図15(a)】一実施形態による、対を示す図である。

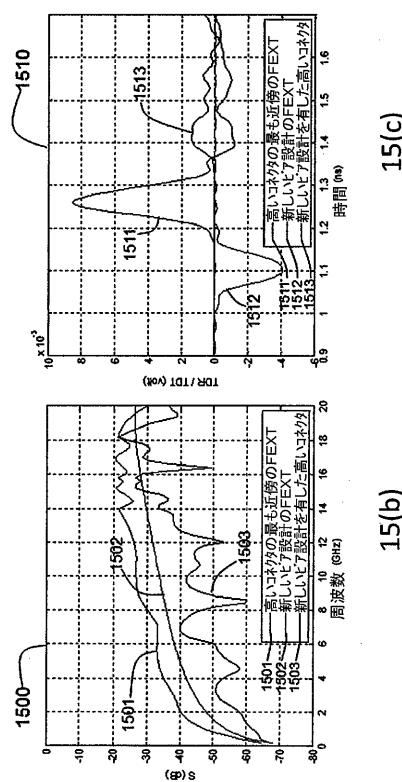

【図15(b)-(c)】一実施形態による、コネクタのみのモデル、ビアのみのモデル、およびビア-コネクタ-ビアのカスケード接続されたモデルに関する、周波数領域および時間領域における差動FEXTを示す図である。 20

【図16(a)】一実施形態による、対を示す図である。

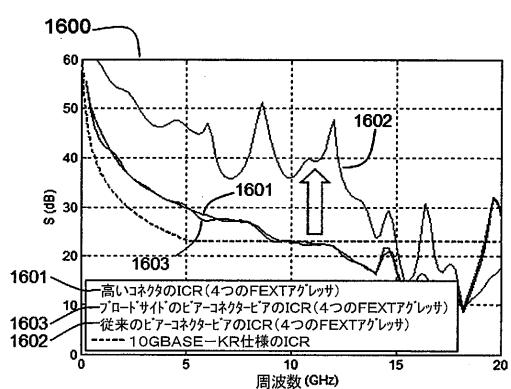

【図16(b)】一実施形態による、ビアモデルがカスケード接続されたおよびカスケード接続されていないコネクタの、挿入損失対クロストーク比(IRC)のグラフを示す図である。

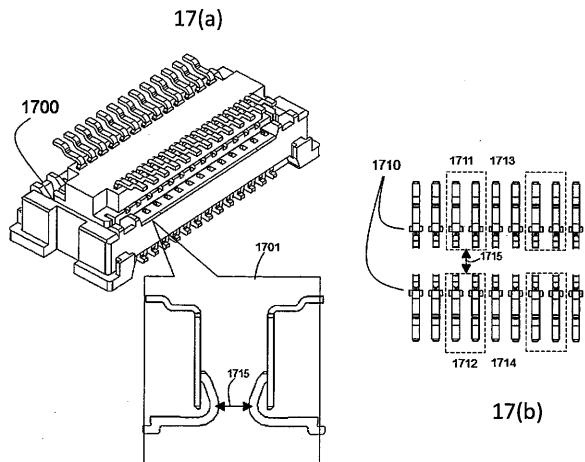

【図17(a)-(b)】負極性のFEXTを有する電気コネクタおよび正のFEXTを有するビア設計に適用されるような、一実施形態を示す図である。

【図17(c)-(d)】負極性のFEXTを有する電気コネクタおよび正のFEXTを有するビア設計に適用されるような、一実施形態を示す図である。

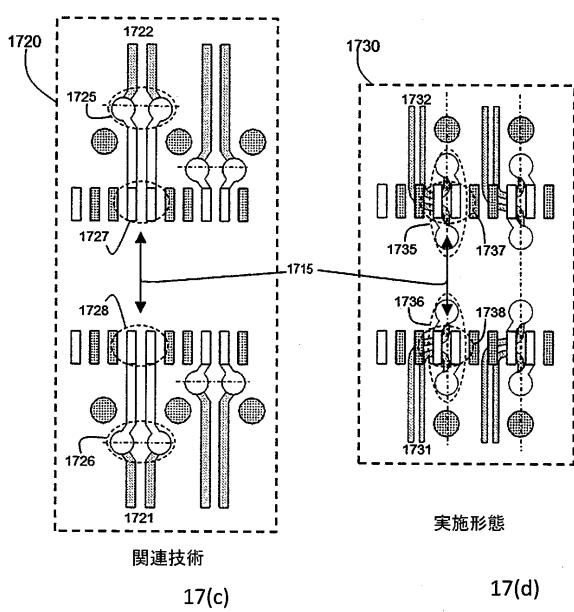

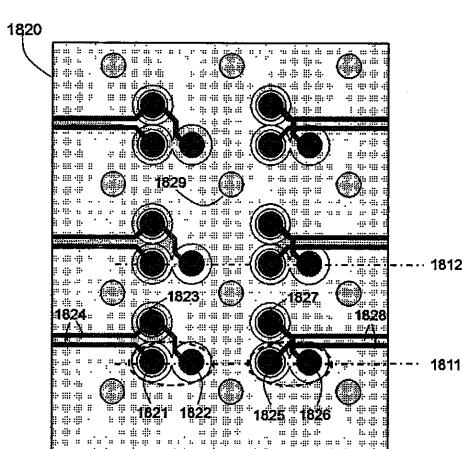

【図18(a)】BGAコネクタに適用されるような、一実施形態を示す図である。

【図18(b)】BGAコネクタに適用されるような、一実施形態を示す図である。 30

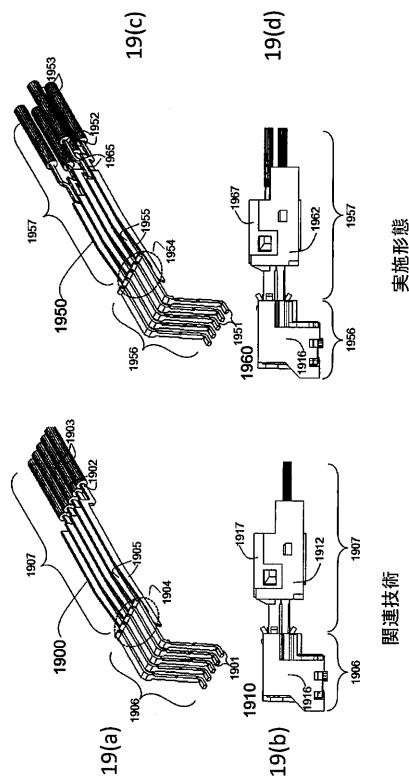

【図19(a)-(d)】図19(a)及び(b)は、電気コネクタに適用されるような、関連技術の構成を示す図、図19(c)及び(d)は、電気コネクタに適用されるような、実施形態を示す図である。

#### 【発明を実施するための形態】

##### 【0018】

以下の詳細な説明は、本出願の図面および実施形態のさらなる詳細を提供する。図面間で重複する要素の参照符号および説明は、見やすくするために省略されている。説明の全体を通して使用される用語は、例として提供されており、限定するものではない。たとえば、用語「FEXTキャンセレーション」の使用は、本出願の実施形態を実施する当業者の実施に応じた、FEXTの何らかの低減または実質的な低減に関与し得る。

##### 【0019】

図1は、一実施形態による、コネクタ信号のPCB内へのルーティングのために使用されるビアのFEXT極性の最適化を行うおよびこれを行わない場合の、通信チャネル全体にわたるピクティムによるFEXTの累積を示す。別段の記述がない限り、本文書におけるFEXTは「差動FEXT」を意味するものである。差動対100は、アクティブチャネル、またはアグレッサとしての役割を果たし、入力101と出力102を有する。略図140は、アグレッサおよびピクティムに関するチャネルの中の構成要素(PCB、ビア1、コネクタ、ビア2、PCB)の例を示す。チャネル110、120、および130はピクティムチャネルであり、また、各チャネルはFEXT累積の異なる場合を示す。具体的には、入力111および出力112を有するピクティムチャネル110は、関連技術のFEXT累積を示す。信号103が差動対100を通って伝搬するとき、チャネル110 40

において、FEXT114がビア1で、115がコネクタで、および116がビア2で、観測される。各FEXT成分の極性は正であるので、出力112で生じる合計クロストークは117として示される。

#### 【0020】

入力121および出力122を有するピクティムチャネル120は、コネクタと反対の極性を生じさせるようにビアを設計することによるFEXTキャンセレーションの例を示す。具体的には、ビアのFEXT124および126は負であり、コネクタのFEXT125は正である。出力122での加算の後、結果として得られるFEXTは127として示される。

#### 【0021】

入力131および出力132を有するピクティムチャネル130は、ビアのFEXT134および136が正でありコネクタのFEXT135が負であるFEXTキャンセレーションの別の例を示す。出力132で加算することによって、チャネル130に関する合計FEXT137が示される。

#### 【0022】

図2は、一実施形態による、図1に示すチャネル概略図140の例を示す。多層PCB200および201が提供され、この場合表面実装型のコネクタ204はビア領域202および203の近傍に取り付けられる。ビア領域202および203の詳細な断面図205では、トレース207はPCBの中にストリップラインとして引き回されており、コネクタと結び付けるためにビア206を使用して表面を持って来られる。

10

#### 【0023】

図3(a)はエッジ結合型のビアの一例を示す。ビア300および301は第1の差動対を示し、また、ビア302および303は第1の差動対と並んで配置された第2の差動対を示す。エッジ結合型のビアは、ビア300および301の中心を通過して引かれた直線305がビア302および303の中心を通過して引かれた直線306と重なるところとして言及される。第1の差動対のビアと第2の差動対のビアとの間のこのエッジ結合型の構成により、正のFEXTが生じる。

20

#### 【0024】

図3(b)のグラフは、差動FEXT320、ならびに対応するシングルエンドの項310(ビア300から302までのクロストーク)、311(ビア300から303までのクロストーク)、312(ビア301から302までのクロストーク)、および313(ビア301から303までのクロストーク)を示す、時間領域におけるクロストークを表す。シングルエンドの項310および313は対称性のため実質的に同様であり、したがってそれらの線は図3(b)および図3(c)の拡大図で示されるように実質的に重なることに留意されたい。ポート1を入力かつポート5を出力としてビア300に、ポート2を入力かつポート6を出力としてビア301に、ポート3を入力かつポート7を出力としてビア302に、ポート4を入力かつポート8を出力としてビア303に割り当てて、FEXTを( $S71 + S82 - S72 - S81$ ) / 2として視覚化すると、320で示すような正のFEXT値が得られる。図3(b)および後のグラフにおける時間領域のクロストークが、一般性を失うことなく、各入力ポートに注入された50ピコ秒(20%から80%まで)の立ち上がり時間と1ボルトのスイングのステップ入力を用いて計算されている。

30

#### 【0025】

図4(a)は、一実施形態による、プロードサイド結合型のビアの例を示す。ビア400および401は第1の差動対を示し、また、ビア402および403は第1の差動対に対してプロードサイド構成で配置された第2の差動対を示す。プロードサイドビアは、ビア400および401の中心を通過して引かれた直線405がビア402および403の中心を通過して引かれた直線406と平行であるところとして言及され、この場合、第1の差動対のビア400および第2の差動対のビア402を通過して引かれた直線410ならびに第1の差動対のビア401および第2の差動対のビア403を通過して引かれた直

40

50

線 4 1 1 が直線 4 0 5 および 4 0 6 に対して直交する。並行な直線 4 0 5 および 4 0 6 の角度が直線 4 1 0 および 4 1 1 に対して直交する状態から僅かに外れている場合、その後の構成はオフセットを有するプロードサイドとして言及されることになる。第 1 の差動対のビアと第 2 の差動対のビアとの間のこのプロードサイド結合型の構造により、負の F E X T が生じる。

#### 【 0 0 2 6 】

図 4 ( b ) のグラフは、差動 F E X T 4 3 0 ならびに対応するシングルエンドの項 4 2 0 ( ビア 4 0 0 から 4 0 2 までのクロストーク ) 、 4 2 1 ( ビア 4 0 0 から 4 0 3 までのクロストーク ) 、 4 2 2 ( ビア 4 0 1 から 4 0 2 までのクロストーク ) 、および 4 2 3 ( ビア 4 0 1 から 4 0 3 までのクロストーク ) を示す、時間領域のクロストークを表す。 4 2 0 および 4 2 3 は対称性のため実質的に同様であり、また 4 2 1 および 4 2 2 も対称性のため実質的に同様であり、したがって、図 4 ( c ) および 4 ( d ) の拡大図で示されるように、それぞれ、 4 2 0 のグラフ線は 4 2 3 のグラフ線と実質的に重なり、また 4 2 1 のグラフ線は 4 2 2 のグラフ線と実質的に重なることに留意されたい。ポート 1 を入力かつポート 5 を出力としてビア 4 0 0 に、ポート 2 を入力かつポート 6 を出力としてビア 4 0 1 に、ポート 3 を入力かつポート 7 を出力としてビア 4 0 2 に、ポート 4 を入力かつポート 8 を出力としてビア 4 0 3 に割り当てて、 F E X T を ( S 7 1 + S 8 2 - S 7 2 - S 8 1 ) / 2 として視覚化すると、 4 3 0 で示すような負の F E X T 値が得られる。その大きさは、 4 2 0 と 4 2 1 との差および 4 2 2 と 4 2 3 との差を、大きくするかまたは小さくすることによって制御可能である。このことを実現するための 1 つの方法は、第 1 および第 2 の差動対のビアの間の距離を大きくするかまたは小さくするかのいずれかであり、この場合距離は、線 4 0 5 および 4 0 6 との交点の間にある線 4 1 0 または 4 1 1 で表される。距離が大きくなるほど、生まれる差、したがって負の差動 F E X T はより小さくなり、また、距離が小さくなるほど、生まれる差、したがって負の差動 F E X T はより大きくなる。

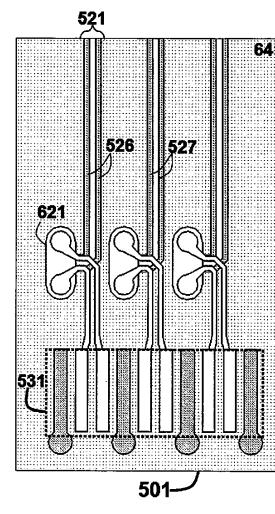

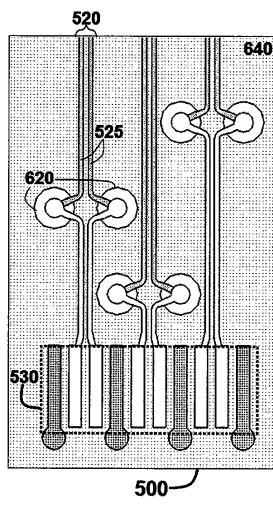

#### 【 0 0 2 7 】

図 5 ( a ) および 5 ( b ) は、関連技術のビアの引き回しおよび一実施形態でのビアの引き回しのレイアウトを示す、 P C B 5 4 0 および 5 4 1 の上面図である。図 5 ( a ) のレイアウト 5 0 0 は、隣り合う差動対のビアの間のクロストークをシールドするための接地ビア 5 1 0 の分布を用いる関連技術のビアの引き回しを示し、また、レイアウト 5 0 1 は、接地ビア 5 1 1 を減らした一実施形態のビアの引き回しを示す。図 5 ( a ) のレイアウト 5 0 0 では、表面実装パッド 5 3 0 は、コネクタを取り付けられるように図面の底部近傍に並べられる。 5 1 5 などの差動トレースは内部の層の中に引き回すために表面実装パッドを差動対 5 2 0 のビアに接続する。

#### 【 0 0 2 8 】

接地ビア 5 1 0 は差動対 5 2 0 の右信号ビアと差動対 5 2 2 の左信号ビアとの間、または差動対 5 2 2 の右信号ビアと差動対 5 2 4 の左信号ビアとの間など、隣接する差動対の 2 つの信号ビアの間または近傍に常に存在する。図 5 ( a ) のレイアウトのパターン、またはセルは、コネクタ上のピンの数の全体を通して繰り返され、したがって各セルの中に追加の接地ビアが必要とされる。図 5 ( b ) のレイアウト 5 0 1 では、表面実装パッド 5 3 1 は、コネクタを取り付けられるように図面の底部近傍に並べられる。このレイアウトでのコネクタピンが、ピンが図 3 のビアとちょうど同じように並んで整列されることになるため、エッジ結合配向を有することになることに留意されたい。 5 1 6 などの差動トレースは内部の層の中に引き回すために表面実装パッドを差動対 5 2 1 のビアに接続する。全ての隣接する対のビアはプロードサイド構成であり、負極性の F E X T を生じさせる。接地ビア 5 1 1 は、 P C B 5 4 1 の全ての接地層の間に電気接続をもたらすために、および内部のストリップライン層に関して使用されるビアフェンス ( via fence ) の半波長共振を制御するために存在する。隣接する対の間のビア結合を反対の極性であるコネクタの F E X T を相殺するのに十分な大きさに高めるために、差動対 5 2 1 および 5 2 3 の信号ビアの間ならびに差動対 5 2 3 および 5 2 5 の信号ビアの間に存在する接地ビア 5 1 1 が

無いことに留意されたい。

#### 【0029】

図6(a)および6(b)は、従来のビアの引き回しおよび一実施形態による新規なビアの引き回しの両方に関する、接地層上のアンチパッドを示す。図5(a)および5(b)に加えてこのレイアウトに見ることのできる態様には、ビアから遠ざかるように引き回される差動対520および521のストリップ線路525および526を含む。図6(a)の層640および図6(b)の層641は、接地層を表し、また、アンチパッド620および621は全ての接地層上に存在する。

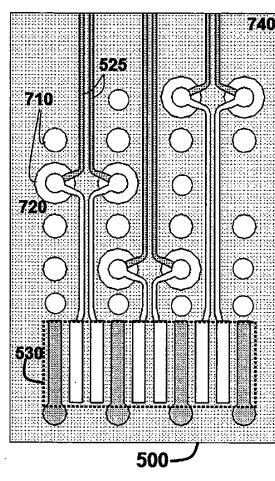

#### 【0030】

図7(a)および7(b)は、一実施形態による、ビア領域における電源層上でのアンチパッドの分布を示す。図7(a)の関連技術のレイアウトは、信号ビアおよび接地ビアが電源層とショートするのを防ぐために電源層740上に密に組み込まれたアンチパッド710を示す。密に組み込まれた穴は、直流(DC)の密集を引き起こし、またPCBに悪影響を及ぼし得る所望されない熱を生じさせる可能性がある。図7(b)の新規なビアレイアウト501は、電源層741上のより少ないアンチパッド711を示すが、このことは必要な接地ビアの数が比較して著しく少ないとによる。

10

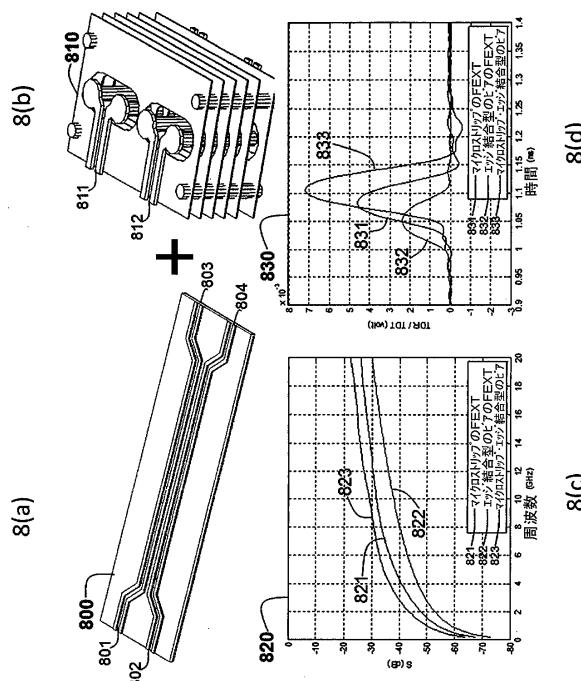

#### 【0031】

図8(a)～8(d)は、エッジ結合型のビアが後に続く2つの差動マイクロストリップ対の正極性のFEXTによる、FEXT累積の一例を示す。図8(a)に示すマイクロストリップには、PCBモデル800に示すように、第1の差動対に関して入力801および出力803を、ならびに第2の差動対に関して入力802および出力804を有する、2つの差動対が存在する。図8(b)のビアモデル810は、入力811および出力813を有する第1の差動対、ならびに入力812および出力814を有する第2の差動対を含む。差動対のビアのそれぞれは、エッジ結合型の構成で並んで配置される。PCBモデル800のデータおよびビアモデル810のデータはカスケード接続されて、この場合PCBモデル800の出力803はビアモデル810の入力811に接続しましたPCBモデル800の出力804はビアモデル810の入力812に接続し、累積された合計のFEXTを観測する。図8(c)のグラフ820は、マイクロストリップモデル821、エッジ結合型のビアモデル822、およびカスケード接続されたマイクロストリップ対エッジ結合型のビア(cascaded-microstrip-to-edge-coupled vias)823の、周波数領域におけるFEXTを示す。図8(d)のグラフ830は、マイクロストリップモデル831、エッジ結合型のビアモデル832、およびカスケード接続されたマイクロストリップ対エッジ結合型のビア833の、時間領域におけるFEXTを示す。両方の場合に、FEXTが累積するという概念および正の値のFEXTを生じさせる個々のモデルの両方を有することから予測されるように、カスケード接続されたモデルは、低減されていないFEXTを示すことが観測され得る。

20

#### 【0032】

図9(a)～9(d)は、一実施形態による、ブロードサイド結合型のビアの負極性のFEXTとカスケード接続されたときの、2つの差動マイクロストリップ対の低減された正のFEXTの一例を示す図である。図8(a)からの同じPCBモデル800が図9(a)で使用される。図9(b)のビアモデル910は、入力911および出力913を有する第1の差動対、ならびに入力912および出力914を有する第2の差動対を含む。差動対のビアはそれぞれ、ブロードサイド結合型の構成で配置される。PCBモデル800のデータおよびビアモデル910のデータは、累積された合計のFEXTを観測するためにカスケード接続され、この場合PCBモデルの出力803はビアモデルの入力911に接続し、またPCBモデルの出力804はビアモデルの入力912に接続する。図9(c)のグラフ920は、マイクロストリップモデル921、ブロードサイド結合型のビアモデル922、およびカスケード接続されたマイクロストリップ対ブロードサイド結合型のビア923の、周波数領域におけるFEXTを示す。グラフ920に示すように、合計FEXTは低減される。図9(d)のグラフ930は、マイクロストリップモデル931

30

40

50

、ブロードサイド結合型のビアモデル 932、およびカスケード接続されたマイクロストリップ対ブロードサイド結合型のビア (cascaded-microstrip-to-broadside-coupled vias) 933 の、時間領域における FEXT を示す。マイクロストリップのクロストーク FEXT およびビアのクロストーク FEXT は極性が反対なので、累積された FEXT は比較して著しく小さくなる可能性がある。

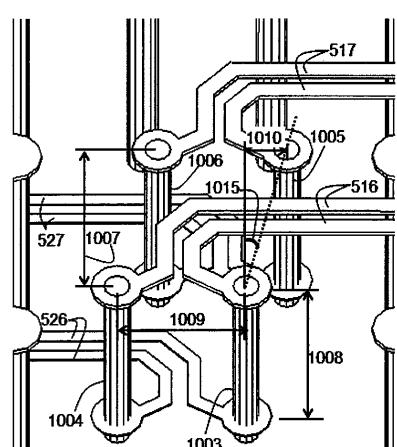

#### 【0033】

図 10 は、一実施形態による、ビアの FEXT の大きさおよび極性に影響を及ぼし得るビア構成の例示の変形例を示す。図 10 は、図 5 (b) からのブロードサイドビアのレイアウト 501 の 3D 画像を表し、隣接する 2 つの差動対を拡大表示する。ビア 1003 および 1004 は第 1 の差動対を表し、また、ビア 1005 および 1006 は第 2 の差動対を表す。第 1 の差動対は、マイクロストリップ 516 を使用して PCB の上に引き回され、コネクタパッド (図示せず) に接続し、ストリップ線路 526 を使用して PCB を通して引き回される。第 2 の差動対は、マイクロストリップ 517 を使用して PCB の上に引き回され、コネクタパッド (図示せず) に接続し、ストリップ線路 527 を使用して PCB を通して引き回される。

#### 【0034】

第 1 の差動対のビアと第 2 の差動対のビアとの間の間隔 1007 により、負の FEXT の大きさを制御する。間隔を大きくすると生じる大きさはより小さくなり、また、間隔を小さくすると生じる大きさはより大きくなる。ビア 1008 の深さもまた負の FEXT の大きさを制御する。ビアが深いほど生じる大きさはより大きくなり、また、ビアが浅ければ生じる大きさはより小さくなる。差動対の 2 つの信号ビアの間の間隔 1009 は対の中の結合を制御し、このことは隣接する差動対の間の結合強度に影響を与える。対の中での緊密なビア結合では、隣接する対とのクロストークはより小さく現れ、また、対の中での結合の緩やかなビアでは、隣接する対とのクロストークはより大きく現れる。第 1 および第 2 の差動対の間のオフセット 1010 またはオフセット角 1015 は、ビアの FEXT の大きさおよび極性を制御する。オフセット角 1015 が 0° から 90° に広げられると、FEXT は負の値から正の値に移る。0° のオフセットが最大の負の FEXT を生み、90° のオフセットが最大の正の FEXT を生じさせることに留意されたい。何らかの角度 1015 で、極性は負から正に移行し、また、その移行角度では、隣接する対の間のビアの FEXT は極端に小さい。

#### 【0035】

上述の変形は、利用可能な唯一のものではないが、FEXT を変化させることが分かれている。これらの変形は、コネクタの FEXT を相殺するために必要とされるビアの FEXT の大きさの制御において有用であり得る。たとえば、コネクタが大きな正極性の FEXT を示しており、かつ、コネクタピンのピッチによって決定され得る第 1 および第 2 の対の間のビア間隔 1007 がコネクタの FEXT を相殺するために必要とされる負の値を生じさせるのに十分なほど近接していないと仮定する。より長いビア 1008 を使用することによって PCB の中のより深い層に引き回すこと、対の中のビア同士の間の間隔 1009 を大きくすること、またはさらには可能であれば対同士の間のビア間隔 1007 を小さくすることを検討することができる他方で、ビアの FEXT が強すぎる場合は、対の中のビア間隔 1009 を小さくすること、またはオフセット 1010 を追加することを検討することができる。

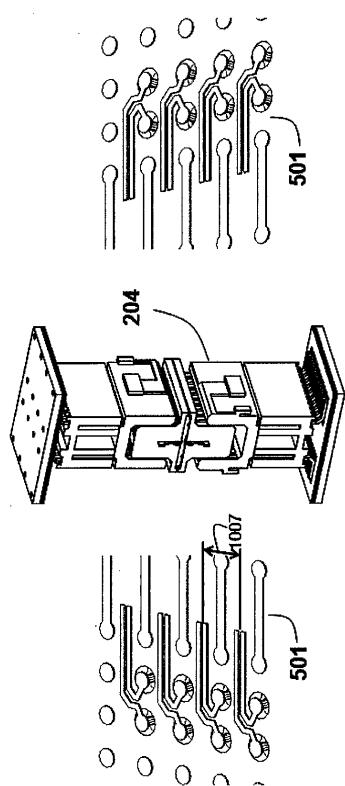

#### 【0036】

図 11 は、高速で、積層高さの低い、表面実装 (SMT) 型のコネクタ 204 に適用されるような、ビア設計の一実施形態を示す。モデル 501 はブロードサイド結合型のビアを組み込み、この場合隣接するチャネルの間の間隔 1007 は、0.5 mm のコネクタピンのピッチおよび接地 - 信号 - 信号 - 接地 (GSSG) 構成から導かれる 1.5 mm であり、また、引き回し層は PCB の頂面から 0.3 mm 下方にある。モデル 501 のデータは、コネクタ 204 のモデルと各端部でカスケード接続される。

#### 【0037】

10

20

30

40

50

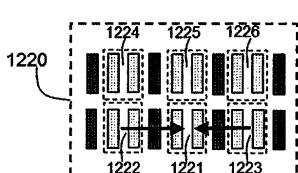

図12(a)は一実施形態によるPCBのパッドのレイアウトを示す。図12(b)および12(c)は、一実施形態による、コネクタのみのモデル、ビアのみのモデル、およびビア-コネクタ-ビアのカスケード接続型のモデルに関する、周波数領域および時間領域における差動FEXTのグラフを示す。図12(a)のPCBパッドのレイアウト1220は、コネクタピンの割り当てを示し、この場合、差動信号の第1の列は対1221、1222、および1223を含み接地パッドが2つの連続する対の間に割り当てられ、また、差動信号の第2の列は対1224、1225、および1226を備え接地パッドが2つの連続する対の間に割り当てられる。対1221をピクティムとして割り当てる際、最大のクロストークは、ほとんどの場合、隣接する対1222および1223からもたらされる。この理由により、実施形態におけるこのビア設計は、隣接する対から現れるコネクタのクロストークを相殺するために、隣接する対のビアのクロストークを制御することを目標とする。ほとんどの場合、コネクタのクロストークの方が大きい。図12(b)のグラフ1200は、コネクタ1201のモデル、ブロードサイド結合型のビア1202のモデル、およびカスケード接続されたブロードサイドビア-コネクタ-ブロードサイドビア1203のモデルの、周波数領域におけるFEXTを示す。改良されたビアを有するコネクタの合計FEXTは、コネクタのみのデータから目立って低減され得る。図12(c)のグラフ1210は、コネクタ1211のモデル、ブロードサイド結合型のビア1212のモデル、およびカスケード接続されたブロードサイドビア-コネクタ-ブロードサイドビア1213のモデルの、時間領域におけるFEXTを示す。コネクタ1211およびブロードサイドビア1212は反対の極性のFEXTを有し、したがって、加算後にキャンセレーションが発生する。

#### 【0038】

図13(a)は一実施形態による対を示す。図13(b)は一実施形態によるSMT型のコネクタを示す。図13(c)は、ビアモデルがカスケード接続されたおよびカスケード接続されていないコネクタの、挿入損失対クロストーク比(IRC)のグラフを示す。図13(a)の最も近い5つのFEXTアグレッサ対1224、1225、1226、1222、および1223が考慮される。ピクティム対1221は第1の列の中央部で選択された。図13(c)のグラフ1300は、コネクタのみのもの1301、コネクタとカスケード接続されたブロードサイド結合型のビア1302、およびコネクタとカスケード接続された従来のビア5001303、ならびにIEEE802.3ap10GBASE-KR仕様を外挿したものの、IRC曲線をプロットする。より大きいIRCを有することが望ましく、したがって垂直軸に沿ったより高い値が好ましい。この例において最適化される関連技術のビア1303では、IRCはコネクタのみの場合1301よりも僅かに悪い。しかし、SI以外の制約のためビアのクロストークが完全に最適化されない場合があるので、実際の実装ではIRCは目立ってさらに悪くなる傾向がある。ブロードサイドビア1302の実施では、IRCはコネクタのみの1301の場合に対して改善し、このことはブロードサイド結合型のビアのモデルをコネクタのモデルにカスケード接続することによってFEXTが低減されたことを示す。

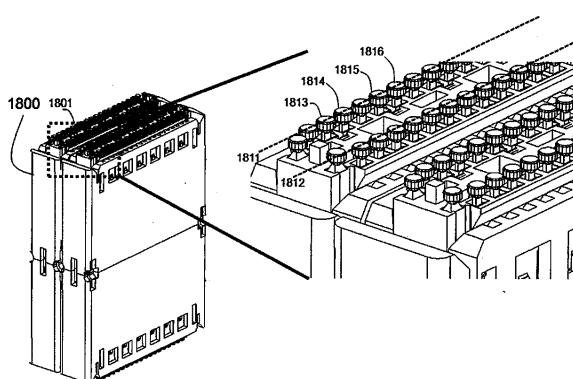

#### 【0039】

図14は、高速で、積層高さの高い、表面実装(SMT)型のコネクタに適用されるような、ビア設計の一実施形態を示す。モデル501はブロードサイド結合型のビアを組み込み、この場合隣接するチャネルの間の間隔1007は1.3mmであり、これは0.5mmのコネクタピンのピッチおよびGSSG構成を使用する従来の間隔から僅かに小さくされており、また、引き回し層はPCBの頂面から0.65mm下方にある。モデル501のデータは図示のようにコネクタ1400のモデルと各端部でカスケード接続される。

#### 【0040】

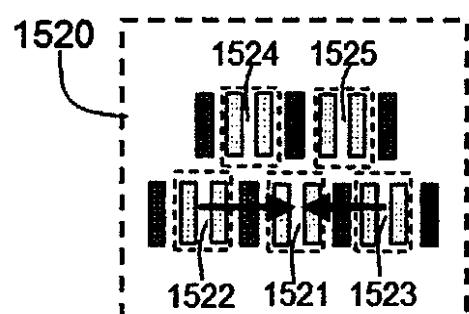

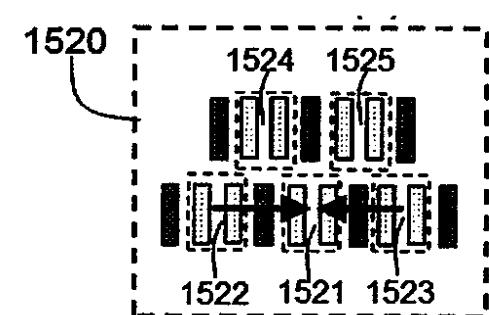

図15(a)は一実施形態による対を示す。図15(b)および15(c)は、一実施形態による、コネクタのみのモデル、ビアのみのモデル、およびビア-コネクタ-ビアのカスケード型のモデルに関する、周波数領域および時間領域における差動FEXTを示す。図15(a)のPCBのパッドのレイアウト1520は、コネクタピンの割り当てを示

し、この場合、差動信号の第1の列は対1521、1522、および1523を含み接地パッドが2つの連続する対の間に割り当てられ、また、差動信号の第2の列は対1524および1525を含み接地パッドが2つの連続する対の間に割り当てられる。対1521をピクティムとして割り当てる際、最大のクロストークは、ほとんどの場合、隣接する対1522および1523からもたらされる。この理由により、先の例で述べたように、実施形態におけるこのビア設計は、隣接する対から現れるコネクタのクロストークを相殺するために、隣接する対のビアのクロストークを制御することを目標とする。図15(b)のグラフ1500は、コネクタ1501のモデル、ブロードサイド結合型のビア1502のモデル、およびカスケード接続されたブロードサイドビア-コネクタ-ブロードサイドビア1503のモデルの、周波数領域におけるFEXTを示す。改良されたビアを有するコネクタの合計FEXTは、コネクタのみのデータから著しく低減され得る。図15(c)のグラフ1510は、コネクタ1511のモデル、ブロードサイド結合型のビア1512のモデル、およびカスケード接続されたブロードサイドビア-コネクタ-ブロードサイドビア1513のモデルの、時間領域におけるFEXTを示す。コネクタ1511およびブロードサイドビア1512は反対の極性のFEXTを有し、したがって、加算後にキャンセレーションが発生する。

#### 【0041】

図16(a)は一実施形態による対を示す。図16(b)は、一実施形態による、ビアモデルがカスケード接続されたおよびカスケード接続されていないコネクタの、挿入損失対クロストーク比(IRC)のグラフを示す。図16(a)に示されるような最も近い4つのFEXTアグレッサ対1524、1525、1522、および1523が考慮される。この例では、ピクティム対1521は第1の列の中央部で選択される。図16(b)のグラフ1600は、コネクタのみのもの1601、コネクタとカスケード接続されたブロードサイド結合型のビア1602、およびコネクタとカスケード接続された従来のビア5001603、ならびにIEEE802.3ap10GBASE-KR仕様を外挿したものの、IRC曲線をプロットする。この例において最適化される関連技術のビア1603では、IRCはコネクタのみの場合1601よりも僅かに悪い。ブロードサイドビア1602の実施では、IRCはコネクタのみの1601の場合に対して著しく改善し、このことはブロードサイド結合型のビアのモデルをコネクタのモデルにカスケード接続することによってFEXTキャンセレーションが発生したことを示す。

#### 【0042】

図17(a)～17(d)は、負極性のFEXTを有する電気コネクタおよび正のFEXTを有するビア設計に適用されるような、一実施形態を示す。図17(a)のコネクタ1700は、端面図1701とともに図17(b)で示すように、信号導体1710の2つの列を収容する。第1の列1711上に位置する第1の差動対および第2の列1712上に位置する第2の差動対は、1715によって示すようにブロードサイド結合型の構成であり、負極性のFEXTを生じさせる。図17(c)のPCBレイアウト1720は、関連技術のビアのレイアウトを示し、この場合引き回しのため、コネクタからの対1711はパッド1727上に取り付けられ、コネクタからの対1712はパッド1728の上に取り付ける。ビア1725および1726はそれぞれ離間され、累積クロストークの大きな低下は期待されない。図17(d)のPCBレイアウト1730は、本開示の一実施形態を示し、この場合引き回しのため、コネクタからの対1711はパッド1737上に取り付けられ、コネクタからの対1712はパッド1738の上に取り付ける。ビア1735および1736はそれぞれ、第1の差動対1711および第2の差動対1712がエッジ結合構成に従うように位置付けられ、正のFEXTを生みコネクタ内で生み出された負のFEXTを相殺する。

#### 【0043】

図18(a)および18(b)は、ボールグリッドアレイ(BGA)コネクタおよびその引き回しのビア設計に適用されるような、一実施形態を示す。図18(a)のBGAコネクタ1800は、信号導体の複数の列1811、1812、などを有する。1801の

拡大画像から見られるように、第1の列1811は、第1の差動対信号導体1813および1814、第2の差動対信号導体1815および1816、などを含む。各列の差動対はエッジ結合される。図18(b)のPCBレイアウト1820は、ビアの引き回しでブロードサイド結合を形成する信号のコネクタ列のそれぞれを示す。第1の列1811は、コネクタ導体1813および1814と嵌まり合う第1の差動対BGA接点パッド1821および1822、コネクタ導体1815および1816に接合する第2の差動対BGA接点パッド1825および1826を含む。列1811の第1の差動対は列1811の第2の差動対とのブロードサイド構成を形成するが、このことは、各差動対の第1のBGAパッド1821および1825に関してビア-イン-パッド(via-in-pad)を使用し、かつ、各差動対の第2のBGAパッド1822および1826をビアパッド1823および1827へと外へ引き回すためにドッグ-ボーンパッドを使用することによって行われる。列1811の第1の差動対のビアは1821および1823に位置し、また、列1811の第2の差動対のビアは1825および1827に位置し、故に、FEXTキャンセレーションを促進するブロードサイド結合を形成する。この図示は例として機能し、ブロードサイドビア構成の正確な構成に従う必要はない。

10

#### 【0044】

図19(a)～19(b)は電気コネクタに適用されるような、関連技術の構成を示し、図19(c)～19(d)は電気コネクタに適用されるような、実施形態を示す。図19(a)の関連技術の構成1900は、エッジ結合型のコネクタ信号導体1905の構成を示す。レセプタクル側1906とプラグ側1907は、示すように1904で嵌め合わされる。関連技術では、嵌合部分の幾何学形状は標準化委員会によって規定され、修正を行うことはできない。プラグ側1907の信号導体は、ケーブル終端部1902でケーブル1903と接合する。図19(b)のコネクタの側面図1910のインサート成形物1912は、コネクタ導体を覆って成形され、また、コネクタシェル1917はこの成形体を密閉する。コネクタシェル1916はコネクタのレセプタクル側1906を密閉する。隣接するアグレッサからピクティム対1901への差動FEXTは、正の極性を有すると予測される。

20

#### 【0045】

図19(c)の実施形態の構成1950は、エッジ結合1955およびブロードサイド結合1965の両方を信号導体に適用することによる、コネクタ内の実施を示す。レセプタクル側1956とプラグ側1957は、示すように1954で嵌め合わされる。プラグ側1957の信号導体は、ケーブル終端部1952でケーブル1953と接合する。図19(d)のコネクタの側面図1960のインサート成形物1962は、コネクタ導体を覆って成形され、また、コネクタシェル1967はこの成形体を密閉する。隣接するアグレッサからピクティム対1951への差動FEXTは、エッジ結合1955の構成およびブロードサイド結合1965の構成が連続しているため、大きさが小さいと予測される。各構成の最適な結合長さでは、両方の極性の大きさは同様になり、コネクタの累積FEXTは低減されることになる。

30

#### 【0046】

本出願の他の実施は、本明細書を考慮しつつ本明細書に開示された実施形態を実施することによって当業者には明らかとなろう。記載された実施形態の様々な態様および/または構成要素が、単独でまたは任意の組み合わせで使用され得る。本明細書および実施形態が例として考えるべきであって、本出願の真の範囲および精神が以下の特許請求の範囲によって示されることが意図される。

40

#### 【符号の説明】

#### 【0047】

100 差動対

101、111、121、131 入力

102、112、122、132 出力

103 信号

|                                         |                      |    |

|-----------------------------------------|----------------------|----|

| 1 1 0                                   | チャネル                 |    |

| 1 1 4                                   | F E X T              |    |

| 1 1 5                                   | コネクタ                 |    |

| 1 1 6                                   | ビア 2                 |    |

| 1 1 7                                   | 合計クロストーク             |    |

| 1 2 0、1 3 0                             | ピクティムチャネル            |    |

| 1 2 4、1 3 4                             | ビアのF E X T           |    |

| 1 2 5、1 3 5                             | コネクタのF E X T         |    |

| 1 2 6、1 3 6                             | ビアのF E X T           |    |

| 1 2 7                                   | F E X T              | 10 |

| 1 3 7                                   | 合計F E X T            |    |

| 1 4 0                                   | チャネル概略図              |    |

| 2 0 0、2 0 1                             | 多層P C B              |    |

| 2 0 2、2 0 3                             | ビア領域                 |    |

| 2 0 4                                   | 表面実装型のコネクタ           |    |

| 2 0 6                                   | ビア                   |    |

| 2 0 7                                   | トレース                 |    |

| 3 0 0、3 0 1、3 0 2、3 0 3                 | ビア                   |    |

| 3 1 0、3 1 1、3 1 2、3 1 3                 | シングルエンドの項            |    |

| 3 2 0                                   | 差動F E X T            | 20 |

| 4 0 0、4 0 1、4 0 2、4 0 3                 | ビア                   |    |

| 4 2 0、4 2 1、4 2 2、4 2 3                 | シングルエンドの項            |    |

| 4 3 0                                   | 差動F E X T            |    |

| 5 0 0、5 0 1                             | レイアウト                |    |

| 5 1 0、5 1 1                             | 接地ビア                 |    |

| 5 1 6、5 1 7                             | マイクロストリップ            |    |

| 5 2 0、5 2 1、5 2 2、5 2 3、5 2 4、5 2 5     | 差動対                  |    |

| 5 2 6、5 2 7                             | ストリップ線路              |    |

| 5 3 0、5 3 1                             | 表面実装パッド              |    |

| 6 2 0、6 2 1                             | アンチパッド               | 30 |

| 6 4 0、6 4 1                             | 層                    |    |

| 7 1 0、7 1 1                             | アンチパッド               |    |

| 7 4 0、7 4 1                             | 電源層                  |    |

| 8 0 0                                   | P C B モデル            |    |

| 8 0 1、8 0 2、8 1 1、8 1 2、9 1 1、9 1 2     | 入力                   |    |

| 8 0 3、8 0 4、9 1 3、9 1 4                 | 出力                   |    |

| 8 1 0、9 1 0                             | ビアモデル                |    |

| 1 0 0 3、1 0 0 4、1 0 0 5、1 0 0 6、1 0 0 8 | ビア                   |    |

| 1 0 0 7、1 0 0 9                         | 間隔                   |    |

| 1 0 1 0                                 | オフセット                | 40 |

| 1 0 1 5                                 | オフセット角               |    |

| 1 4 0 0                                 | コネクタ                 |    |

| 1 7 0 0                                 | コネクタ                 |    |

| 1 7 1 0                                 | 信号導体                 |    |

| 1 7 1 1                                 | 第1の列、コネクタからの対、第1の差動対 |    |

| 1 7 1 2                                 | 第2の列、コネクタからの対、第2の差動対 |    |

| 1 7 2 0、1 7 3 0                         | P C B レイアウト          |    |

| 1 7 2 5、1 7 2 6、1 7 3 5、1 7 3 6         | ビア                   |    |

| 1 7 2 7、1 7 2 8、1 7 3 7、1 7 3 8         | パッド                  |    |

| 1 8 0 0                                 | B G A コネクタ           | 50 |

- 1 8 1 1、1 8 1 2 信号導体の列

1 8 1 3、1 8 1 4 第1の差動対信号導体

1 8 1 5、1 8 1 6 第2の差動対信号導体

1 8 2 0 P C B レイアウト

1 8 2 1、1 8 2 2 第1の差動対B G A接点パッド

1 8 2 3、1 8 2 7 ピアパッド

1 8 2 5、1 8 2 6 第2の差動対B G A接点パッド

1 9 0 0 関連技術の構成

1 9 0 1、1 9 5 1 ピクティム対

1 9 0 2、1 9 5 2 ケーブル終端部

1 9 0 3、1 9 5 3 ケーブル

1 9 0 5 コネクタ信号導体

1 9 0 6、1 9 5 6 レセプタクル側

1 9 0 7、1 9 5 7 プラグ側

1 9 1 2、1 9 6 2 インサート成形物

1 9 1 6、1 9 1 7、1 9 6 7 コネクタシェル

1 9 5 0 実施形態の構成

1 9 5 5 エッジ結合

1 9 6 5 プロードサイド結合

10

【図1】

【図2】

【図3(a)】

【図3(b)-(c)】

【図4(a)】

【図4(b)-(d)】

【図5(a) - (b)】

【図6(a) - (b)】

【図7(a) - (b)】

【図8(a) - (d)】

【図9(a)-(d)】

【図10】

9(c)

9(d)

【図11】

【図12(a)】

1220

【図 1 2 ( b ) - ( c )】

【図 1 3 ( a )】

【図 1 3 ( b )】

【図 1 3 ( c )】

【図14】

【図15(b)-(c)】

【図15(a)】

【図16(a)】

【図 1-6 (b)】

【図17(a)-(b)】

【図17(c)-(d)】

【図18(a)】

【図18(b)】

【図19(a) - (d)】

実施態

関連技術

---

フロントページの続き

(74)代理人 100120525

弁理士 近藤 直樹

(74)代理人 100167911

弁理士 豊島 匠二

(72)発明者 クニア アイハラ

アメリカ合衆国 カリフォルニア州 95122 サン ホセ ロバーツ アベニュー 1162

(72)発明者 チン - チャオ ファン

アメリカ合衆国 カリフォルニア州 95129 サン ホセ ロイヤル アン コート 142

7

審査官 原田 貴志

(56)参考文献 米国特許出願公開第2010/0323535(US, A1)

特表2012-516021(JP, A)

特開2008-091732(JP, A)

特表2008-545250(JP, A)

(58)調査した分野(Int.Cl., DB名)

H05K 3/36

H05K 1/02

H01P 3/04

H01R 12/57

H01R 13/6469