| DOMANDA DI INVENZIONE NUMERO | 102022000000179 |

|------------------------------|-----------------|

| Data Deposito                | 07/01/2022      |

| Data Pubblicazione           | 07/07/2023      |

## Classifiche IPC

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| G       | 11     | С           | 7      | 06          |

## Titolo

ARCHITETTURA DI AMPLIFICATORE DI LETTURA PER UNA MEMORIA NON VOLATILE MEMORIZZANTE INFORMAZIONI CODIFICATE

## DESCRIZIONE

del brevetto per invenzione industriale dal titolo:

"ARCHITETTURA DI AMPLIFICATORE DI LETTURA PER UNA MEMORIA

NON VOLATILE MEMORIZZANTE INFORMAZIONI CODIFICATE"

di STMICROELECTRONICS S.R.L.

di nazionalità italiana

con sede: VIA C. OLIVETTI 2

20864 AGRATE BRIANZA (MB)

Inventori: DISEGNI Fabio Enrico Carlo, CARISSIMI Marcella, TOMASONI Alessandro, LO IACONO Daniele

\* \* \* \* \*

La presente descrizione è relativa ad un'architettura di amplificatore di lettura per una memoria non volatile, in cui le informazioni sono memorizzate in modo codificato. In particolare, forme di realizzazione della presente descrizione si riferiranno a memorie non volatili in cui le informazioni memorizzate sono associate a una corrente che scorre attraverso corrispondenti celle di memoria; più in particolare, forme di realizzazione della presente descrizione faranno riferimento a memorie a cambiamento di fase ("Phase Change Memories - PCM").

Nelle memorie non volatili, come PCM ("Phase Change Memory"), ST-RAM ("Magneto Resistive Random Access Memory"), RRAM ("Resistive Random Access Memory"), informazioni memorizzate sono associate a diversi stati fisici delle celle

di memoria; tali stati possono essere dedotti/modificati operando sulla corrente che scorre attraverso le celle di memoria.

In particolare, nelle memorie PCM si sfruttano caratteristiche di materiali aventi la proprietà di commutare tra fasi con diverso comportamento elettrico per la memorizzazione di informazioni. Questi materiali possono commutare da una fase disordinata/amorfa ad una fase cristallina o policristallina ordinata; fasi diverse sono caratterizzate da diversi valori di resistività e sono di conseguenza associate a diversi valori di memorizzato. Ad esempio, gli elementi del Gruppo VI della tavola periodica, come il tellurio (Te), il selenio (Se) o l'antimonio (Sb), noti anche come calcogenuri o materiali calcogenici, possono essere utilizzati per realizzare celle di memoria a cambiamento di fase; in particolare, in tali celle di memoria è attualmente ampiamente utilizzata una lega formata da germanio (Ge), antimonio (Sb) e tellurio (Te), nota come GST (avente la composizione chimica  $Ge_2Sb_2Te_5$ ).

I cambiamenti di fase possono essere ottenuti aumentando localmente la temperatura delle celle di materiale calcogenico, tramite elettrodi resistivi (noti in generale come riscaldatori) posti a contatto con corrispondenti regioni di materiale calcogenico.

Ai riscaldatori sono collegati dispositivi di accesso (o selezione), (ad esempio transistori bipolari o MOS), che consentono selettivamente il passaggio di una corrente elettrica di programmazione (anche nota come corrente elettrica di scrittura); tale corrente elettrica, per effetto Joule, genera la temperatura necessaria per il cambio di fase, ed in particolare per commutare da uno stato di alta resistività (noto come stato di RESET) ad uno stato di bassa resistività (il cosiddetto stato di SET) o viceversa.

Durante la lettura, lo stato del materiale calcogenico viene rilevato applicando una tensione sufficientemente bassa da non provocarne un sensibile riscaldamento, e quindi leggendo il valore della corrente che scorre nella cella di memoria attraverso un circuito amplificatore di lettura. Poiché la corrente è proporzionale alla conducibilità del materiale calcogenico, è possibile determinare lo stato dello stesso materiale calcogenico e di conseguenza determinare le informazioni memorizzate nella cella di memoria.

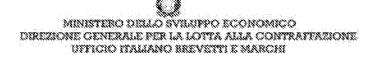

La Figura 1 mostra schematicamente un dispositivo di memorizzazione non volatile 1, comprendente una matrice di memoria 2 formata da una pluralità di celle di memoria 3, disposte in righe, o linee di parola ("wordline - WL"), e colonne, o linee di bit ("bitline"), queste ultime anche note come bitline locali LBL.

Ciascuna cella di memoria 3 è formata da un elemento di memorizzazione 3a e da un elemento di accesso 3b, collegati in serie tra una rispettiva bitline locale LBL ed un terminale di riferimento ad un potenziale di riferimento (ad esempio massa, GND). Una wordline WL è definita dall'insieme di tutti i terminali di controllo degli elementi di accesso 3b allineati lungo una stessa riga.

In modo non mostrato, per ciascun insieme di un numero di bitline locali LBL sono previste bitline principali MBL, che consentono di accedere al rispettivo insieme di bitline locali (e relative celle di memoria) per operazioni di lettura e scrittura.

L'elemento di memorizzazione 3a include un elemento di materiale a cambiamento di fase (ad esempio un calcogenuro, come GST) ed è di conseguenza in grado di memorizzare dati sotto forma di livelli di resistenza associati alle varie fasi assunte dal materiale stesso.

L'elemento di accesso 3b è, ad esempio, un transistore MOS a canale N avente il proprio terminale di porta collegato ad una rispettiva wordline WL, il proprio terminale di pozzo collegato ad un primo terminale dell'elemento di memorizzazione 3a, ed il proprio terminale di sorgente collegato al potenziale di riferimento; un secondo terminale dell'elemento di memorizzazione 3a è collegato ad una relativa bitline locale LBL. L'elemento di accesso 3b è

controllato e polarizzato in modo da consentire, quando selezionato, il passaggio di una corrente di scrittura o di una corrente di lettura (denominata, in generale, 'corrente di cella'), attraverso l'elemento di memorizzazione 3a.

Un decodificatore di colonna 4 ed un decodificatore di riga 5 consentono la selezione delle celle di memoria 3, in base a segnali di indirizzo (indicati complessivamente come AS) ricevuti in ingresso ed in base ad opportuni schemi di decodifica. I segnali di indirizzo AS possono essere generati da una logica di controllo CL, che controlla inoltre il decodificatore di colonna 4 e il decodificatore di riga 5 in modo da consentire la lettura e la scrittura (durante le cosiddette operazioni di 'SET' e 'RESET') delle celle di memoria 3 indirizzate dai segnali di indirizzo AS. La logica di controllo CL, qui non illustrata, fornisce anche segnali controllo al decodificatore di colonna di decodificatore di riga 5, al fine di controllare le suddette operazioni di lettura/scrittura.

In particolare, il decodificatore di colonna 4 e il decodificatore di riga 5 consentono la selezione delle wordline WL e delle bitline locali LBL indirizzate, e pertanto consentono la polarizzazione ad opportuni valori di tensione delle wordline WL e delle bitline locali LBL selezionate, secondo uno schema di decodifica gerarchica (che prevede anche la selezione delle relative bitline

principali).

Il decodificatore di colonna 4 è inoltre configurato per implementare internamente due distinti percorsi verso le bitline locali LBL della matrice di memoria 2 di volta in volta selezionate: un percorso di lettura, atto a creare selettivamente un percorso conduttivo tra ciascuna bitline locale LBL selezionata ed un blocco di lettura 7, che include una pluralità di amplificatori di lettura; ed un percorso di scrittura, atto a creare selettivamente un conduttivo tra ciascuna bitline locale LBL selezionata ed un blocco di scrittura 8 configurato per fornire le correnti richieste per le operazioni di scrittura, ovvero per la cosiddetta programmazione delle celle di memoria corrispondenti logici, e pertanto stati per la memorizzazione delle informazioni.

Il decodificatore di colonna 4 comprende, per ciascun percorso di lettura e programmazione, opportuni elementi di selezione (in particolare transistori controllati), collegati in modo da implementare un sistema di decodifica degli indirizzi, tipicamente gerarchico, per la selezione delle celle di memoria 3.

In modo noto, le memorie non volatili possono avere un'architettura differenziale, in cui i dati (bit logici) sono memorizzati in due celle di memoria, una cella diretta ed una complementare, aventi stati opposti (ad esempio una

cella diretta avente un valore logico alto, '1', e la relativa cella complementare avente un valore logico basso, '0', ovvero un valore negato rispetto alla cella diretta).

Questa codifica differenziale, ovvero la memorizzazione non solo dell'effettivo valore diretto (uno o zero), ma anche del suo valore negato o complementare (zero o uno) in una coppia di celle di memoria, permette di evitare problemi dovuti alla deriva (drift) dei valori memorizzati durante la vita delle celle di memoria.

Nell'architettura differenziale, le operazioni lettura consistono nel confrontare la differenza di corrente in due rami di un rispettivo amplificatore di lettura (ed esempio, nel blocco di lettura 7 sopra discusso), accoppiati alla cella diretta e, rispettivamente, alla cella l'uscita dell'amplificatore complementare, di lettura indicativa dell'informazione memorizzata essendo (bit logico). Poiché il bit logico è associato ad una differenza di corrente, il suo valore può essere letto correttamente anche se i valori fisici delle celle diretta e complementare hanno subito derive nel tempo.

L'inconveniente dell'architettura differenziale è il numero raddoppiato di celle di memoria utilizzate per memorizzare una stessa quantità di informazioni o, equivalentemente, il numero dimezzato di bit di informazioni che possono essere memorizzati utilizzando uno stesso numero

di celle di memoria.

Ad esempio, nel caso in cui la dimensione della parola dei dati memorizzati sia 32 bit, considerando anche i bit aggiuntivi richiesti per i codici di correzione di errore (ad esempio, SEC, Single Error Correction, di 6 bit + DED, Double Error Detection, di 1 bit), utilizzando un'architettura differenziale sono richieste 78 celle di memoria.

Allo stesso modo, per una dimensione della parola di 64 bit di informazioni + DEC di 14 bit + TED di 1 bit, per la codifica differenziale sono richieste 158 celle di memoria.

In generale, l'efficienza di una matrice di memoria differenziale (ad esempio di tipo PCM) non supera il 50%.

A causa del fatto che la densità dell'area è un fattore abilitante chiave, è sicuramente sentita l'esigenza di fornire una soluzione migliorata per la memorizzazione di informazioni in memorie non volatili di tipo differenziale e di fornire una relativa architettura di amplificatore di lettura migliorata in grado di leggere le informazioni memorizzate.

Scopo della presente soluzione è pertanto quello di fornire un'architettura di amplificatore di lettura che soddisfi, almeno in parte, la suddetta esigenza evidenziata dalla Richiedente.

Secondo la presente soluzione, è fornita

un'architettura di amplificatore di lettura, come definita nelle rivendicazioni allegate.

Per una migliore comprensione della presente invenzione, ne verranno ora descritte forme di realizzazione preferite, puramente a titolo di esempio non limitativo, con riferimento ai disegni allegati, in cui:

- la Figura 1 mostra uno schema a blocchi schematico e generale di un dispositivo di memoria non volatile, in particolare di tipo PCM;

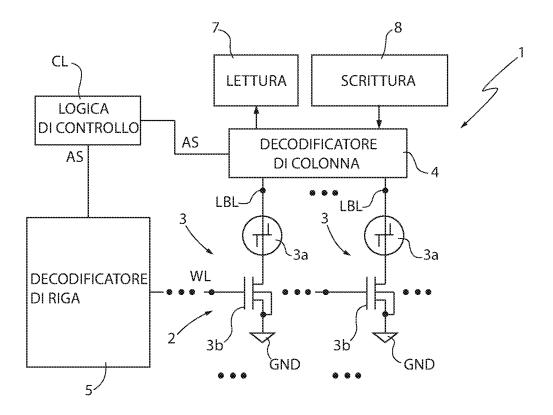

- la Figura 2 mostra uno schema a blocchi schematico di un'architettura di amplificatore di lettura secondo una forma di realizzazione della presente soluzione;

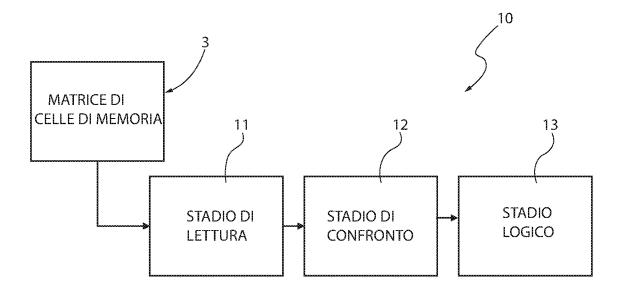

- la Figura 3 mostra uno schema circuitale di un circuito amplificatore di lettura dell'architettura di amplificatore di lettura;

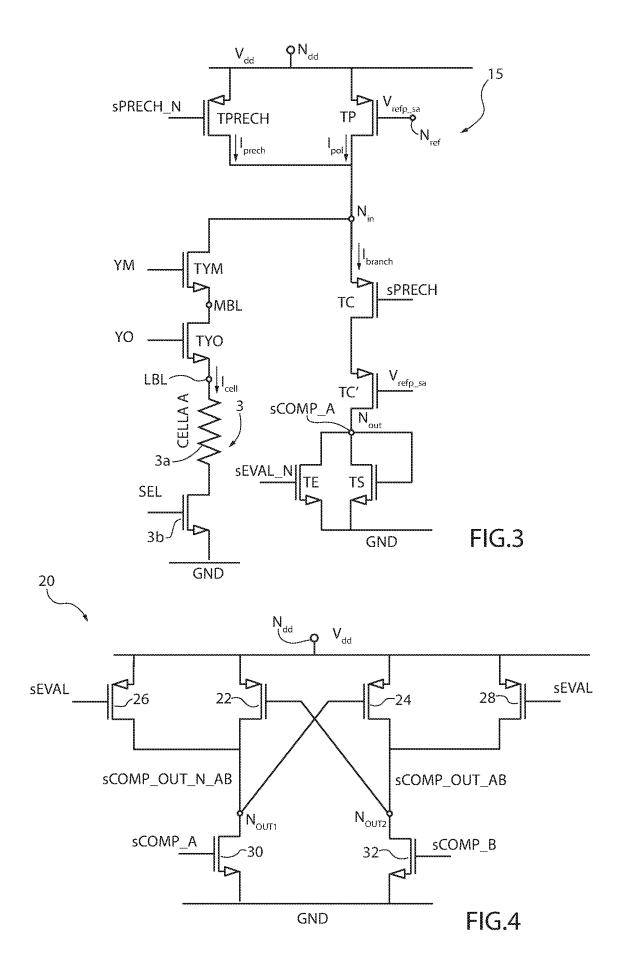

- la Figura 4 mostra uno schema circuitale di un circuito di confronto dell'architettura di amplificatore di lettura;

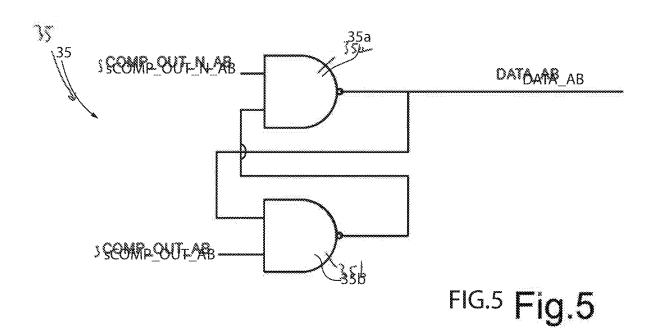

- la Figura 5 mostra uno schema circuitale di un circuito di latch dell'architettura di amplificatore di lettura:

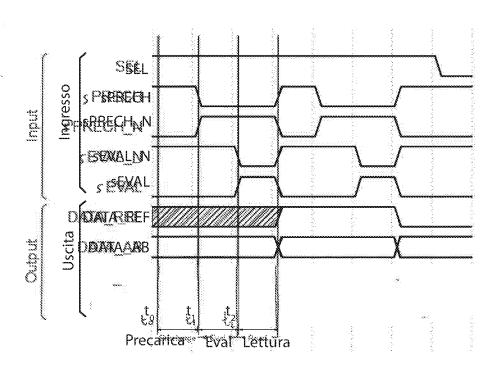

- la Figura 6 mostra diagrammi di temporizzazione di operazioni eseguite nell'architettura di amplificatore di lettura;

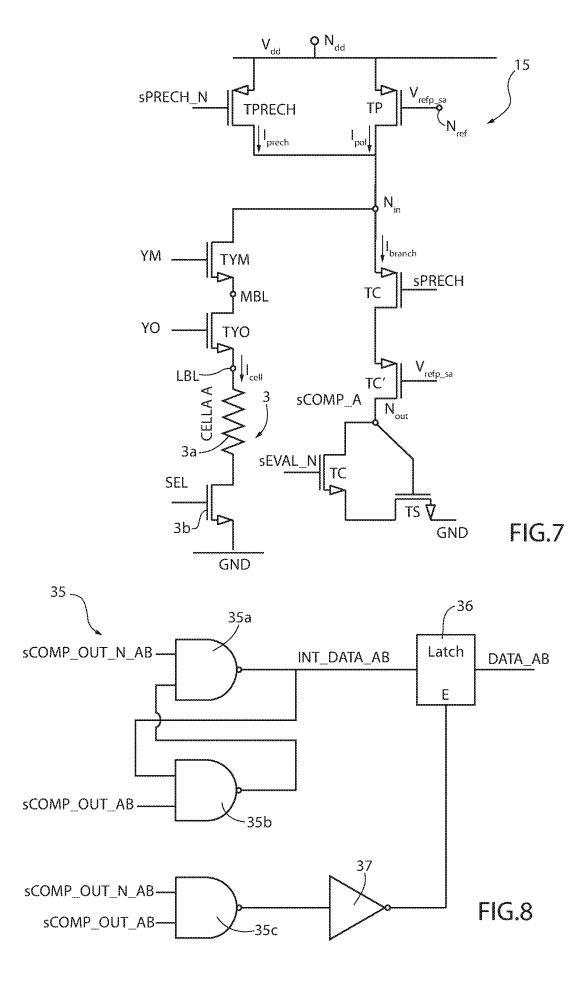

- la Figura 7 mostra uno schema circuitale di un

circuito di amplificatore di lettura dell'architettura di amplificatore di lettura, secondo una diversa forma di realizzazione;

- la Figura 8 mostra uno schema circuitale di un circuito di latch dell'architettura di amplificatore di lettura, secondo una diversa forma di realizzazione;

- le Figure 9A e 9B mostrano schemi circuitali di un circuito di definizione di sottoinsieme nell'architettura di amplificatore di lettura, secondo rispettive forme di realizzazione;

- la Figura 10 mostra uno schema circuitale di un circuito di generazione di riferimenti nell'architettura di amplificatore di lettura; e

- la Figura 11 mostra un diagramma a blocchi schematico di un apparecchio elettronico che incorpora un dispositivo di memoria che include la presente architettura di amplificatore di lettura.

La presente Richiedente ha constatato che può essere ottenuta un'occupazione di memoria più compatta ed efficiente, mantenendo allo stesso tempo i vantaggi di un'architettura di memoria differenziale, memorizzando informazioni nelle celle di memoria non volatile in modo codificato.

In particolare, un gruppo di un determinato numero (maggiore di due) di celle di memoria non volatile può

memorizzare una parola codice formata dai valori degli stati memorizzati delle celle del gruppo, presi secondo un dato ordine; le celle di memoria essendo del tipo in cui uno stato logico memorizzato, che può essere alto logico ('1') o basso logico ('0'), può essere modificato tramite l'applicazione di una corrente e lo stato nella cella di memoria viene letto leggendo una corrente che scorre attraverso la stessa cella di memoria.

Ad esempio, nel caso in cui il gruppo di celle di memoria non volatile includa un numero No di celle di memoria pari a quattro, una prima parola codice memorizzata esemplificativa può corrispondere ad una combinazione di stati [0 0 1 0], ovvero in cui una prima, una seconda e una quarta cella hanno un valore logico '0' (anche definito stato di 'RESET', nel caso di una cella di memoria PCM) e una terza cella ha un valore logico '1' (anche definito stato di 'SET', nel caso di una cella di memoria PCM); mentre una seconda parola codice esemplificativa può corrispondere a una combinazione di stati [0 0 0 1]. A ciascuna parola codice può corrispondere un simbolo, ovvero un valore o un'etichetta dati a cui è mappata la parola codice (ad esempio, i simboli '2' o '3' per la prima e la seconda parola codice esemplificativa).

Un circuito di lettura (amplificatore di lettura), configurato per implementare una decodifica delle

informazioni memorizzate in modo codificato, può ad esempio essere configurato per identificare la posizione e/o il numero degli "uno" nel gruppo di celle di memoria. Ciò può essere ottenuto confrontando, tra loro (ad esempio con confronti a coppie), le correnti delle celle di memoria nel gruppo di celle.

Un aspetto della presente soluzione prevede pertanto un'architettura di amplificatore di lettura, che, a titolo esemplificativo, può essere implementata nel blocco di lettura 7 di un dispositivo di memorizzazione non volatile 1 come quello illustrato nella Figura 1, che è configurata per consentire la lettura delle informazioni memorizzate, in modo codificato, nelle celle di memoria non volatile, implementando, in particolare, confronti tra correnti di cella di diverse celle di memoria.

Come mostrato nella Figura 2, l'architettura di amplificatore di lettura, indicata in generale con 10, comprende: uno stadio di lettura 11, accoppiato alla matrice di celle di memoria 3 di un dispositivo di memorizzazione non volatile 1 (ad esempio di tipo PCM), e includente una pluralità di rami di lettura di amplificatore di lettura, uno per ciascuna cella di memoria 3, configurati per leggere la rispettiva corrente di cella I<sub>cell</sub>; uno stadio di confronto 12, configurato per eseguire un confronto delle correnti di cella di diverse celle di memoria 3 di un gruppo, ad esempio

confrontandole a coppie ottenendo rispettivi risultati di confronto a coppie, ovvero valori binari, in particolare bit, che siano zero o uno a seconda di quale corrente delle due celle di memoria confrontate sia maggiore; e uno stadio logico 13, configurato per determinare, in base ai risultati di confronto forniti dallo stadio di confronto 12, una parola codice letta relativa al gruppo di celle di memoria 3 ed un relativo simbolo decodificato.

Più in dettaglio, la Figura 3 mostra un ramo di lettura di amplificatore di lettura, indicato con 15, dello stadio di lettura 11 dell'architettura di amplificatore di lettura 10.

Come discusso in precedenza, il ramo di lettura di amplificatore di lettura 15 è accoppiato ad una rispettiva cella di memoria 3 (qui indicata come Cell\_A), ad esempio una cella PCM formata da un elemento di memorizzazione 3a (rappresentato come un elemento resistivo) e da un elemento di accesso 3b (nell'esempio un transistore NMOS, avente un terminale di porta ricevente un segnale di selezione e polarizzazione SEL, ad esempio dal decodificatore di riga 5 della Figura 1); il ramo di lettura di amplificatore di lettura 15 è configurato per fornire un segnale di uscita sCOMP\_A, indicativo della corrente di cella I<sub>cell</sub> che scorre attraverso la stessa cella di memoria 3, in particolare essendo correlato da una relazione inversa alla stessa

corrente di cella Icell.

In dettaglio, il ramo di lettura di amplificatore di lettura 15 comprende un transistore di polarizzazione TP ed un transistore di precarica TPRECH, che sono transistori in modalità di arricchimento e canale P e presentano, ad esempio, caratteristiche simili.

Ι terminali di del sorgente transistore di polarizzazione TP e del transistore di precarica TPRECH sono collegati ad un nodo di alimentazione  $N_{dd}$ , che è posto ad una tensione di alimentazione  $V_{dd}$ , ad esempio, pari a 1 Volt. Il terminale di porta del transistore di polarizzazione TP è collegato ad un nodo di riferimento N<sub>ref</sub>, che è posto ad una tensione di riferimento V<sub>refp sa</sub>; un segnale sPRECH N è fornito al terminale di porta del transistore di precarica TPRECH (tale segnale sPRECH e la relativa negazione sPRECH N possono essere generati ad esempio dalla logica di controllo CL, si veda la Figura 1, e possono variare tra 0 V e la tensione di alimentazione  $V_{dd}$ ). Inoltre, i terminali di pozzo degli stessi transistore di polarizzazione TP e transistore di precarica TPRECH sono collegati tra loro e definiscono un nodo di ingresso Nin.

Il ramo di lettura di amplificatore di lettura 15 comprende inoltre un transistore di controllo superiore TC e un transistore di controllo inferiore TC', che sono transistori in modalità di arricchimento e canale P e

presentano, ad esempio, caratteristiche simili.

Il transistore di controllo superiore TC e il transistore di controllo inferiore TC' sono collegati insieme in serie. In particolare, il terminale di sorgente del transistore di controllo superiore TC è collegato al nodo di ingresso  $N_{in}$ , mentre il terminale di pozzo del transistore di controllo superiore TC è collegato al terminale di sorgente del transistore di controllo inferiore TC', il cui terminale di pozzo forma un nodo di uscita Nout, su cui è fornito il segnale di uscita sCOMP A. Sul terminale di porta del transistore di controllo superiore TC è presente un segnale sPRECH, che è pari alla negazione logica del segnale sPRECH N di cui sopra; la suddetta tensione di riferimento V<sub>refp sa</sub> (o una diversa tensione di riferimento con valore fisso) è presente sul terminale di porta del transistore di controllo inferiore TC'.

Il ramo di lettura di amplificatore di lettura 15 comprende inoltre un transistore di lettura TS e un transistore di valutazione TE, che sono di tipo a modalità di arricchimento e canale N, presentano caratteristiche simili e hanno i loro terminali di sorgente collegati ad un potenziale di riferimento, ad esempio a massa GND.

I terminali di pozzo del transistore di lettura TS e del transistore di valutazione TE sono collegati al nodo di uscita  $N_{\rm out}$ ; il terminale di porta del transistore di lettura

TS è collegato allo stesso nodo di uscita  $N_{\rm out}$ , lo stesso transistore di lettura TS essendo pertanto connesso a diodo. Inoltre, sul terminale di porta del transistore di valutazione TE è presente un segnale sEVAL\_N (il segnale sEVAL\_N e la relativa negazione sEVAL possono anch'essi essere generati dalla logica di controllo CL e possono variare tra 0 V e la tensione di alimentazione  $V_{\rm dd}$ ).

Il nodo di ingresso N<sub>in</sub> è accoppiato alla cella di memoria 3 tramite un transistore di decodifica di primo livello TYO ed un transistore di decodifica di secondo transistori in modalità livello TYM, che sono arricchimento canale N, presentano, е ad esempio, caratteristiche simili e sono collegati insieme in serie.

In particolare, il terminale di pozzo del transistore di decodifica di secondo livello TYM è collegato al nodo di ingresso Nin, mentre il terminale di sorgente del transistore di decodifica di secondo livello TYM è collegato al terminale di pozzo del transistore di decodifica di primo livello TYO, che è accoppiato a una bitline principale MBL. Il terminale di sorgente del transistore di primo livello TYO è accoppiato ad una bitline locale LBL e pertanto anche all'elemento di memorizzazione 3a della prima cella di memoria 3. Corrispondenti segnali di polarizzazione di decodifica di primo livello e di decodifica di secondo livello, indicati da YO e YM e generati, ad esempio, dal decodificatore di colonna 4 (si veda la Figura 1), sono forniti ai terminali di porta del transistore di primo livello TYO e, rispettivamente, del transistore di secondo livello TYM (in modo noto, per selezionare e polarizzare la relativa bitline locale ad una tensione desiderata per le operazioni di memoria).

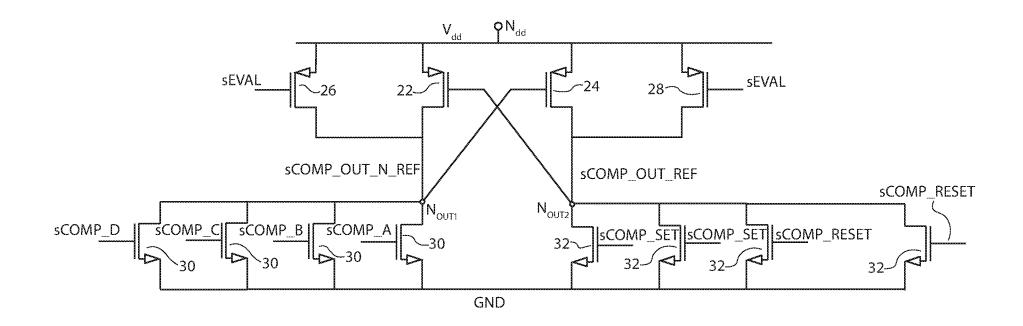

Con riferimento alla Figura 4, viene ora descritto in maggiore dettaglio un circuito di confronto, indicato con 20, dello stadio di confronto 12 dell'architettura di amplificatore di lettura 10.

Come sopra discusso, lo stadio di confronto 12 include un numero di tali circuiti di confronto 20, ciascuno configurato per implementare un rispettivo confronto tra segnali indicativi delle correnti di cella  $I_{\text{cell}}$  che scorrono attraverso rispettive diverse celle di memoria 3 del dispositivo di memoria non volatile 1 (ad esempio, un confronto a coppia tra rispettive coppie di celle di memoria 3).

Nell'esempio mostrato nella Figura 4, il circuito di confronto 20 è configurato per eseguire un confronto tra i segnali di uscita sCOMP\_A e sCOMP\_B, rispettivamente associati ad una corrente di cella I<sub>cell</sub> che scorre attraverso una prima ed una seconda cella di memoria, Cell\_A e Cell\_B (gli stessi segnali di uscita sCOMP\_A e sCOMP\_B essendo forniti da due diversi rami di lettura di amplificatore di

lettura 15 dello stadio di lettura 11 dell'architettura di amplificatore di lettura 10).

Il circuito di confronto 20 comprende un primo transistore ad accoppiamento incrociato 22 e un secondo transistore ad accoppiamento incrociato 24 e un primo transistore di abilitazione 26 e un secondo transistore di abilitazione 28, che sono transistori in modalità di arricchimento e canale P e presentano, ad esempio, caratteristiche simili.

I terminali di sorgente del primo e secondo transistore ad accoppiamento incrociato 22, 24 e del primo e secondo transistore di abilitazione 26, 28 sono collegati al nodo di alimentazione  $N_{\rm dd}$ , e sono pertanto posti alla tensione di alimentazione  $V_{\rm dd}$ . I terminali di porta del primo e secondo transistore ad accoppiamento incrociato 22, 24 sono collegati, rispettivamente, al terminale di pozzo del secondo transistore ad accoppiamento incrociato 24 e al terminale di pozzo del primo transistore ad accoppiamento incrociato 22.

I terminali di pozzo del primo e secondo transistore di abilitazione 26, 28 formano, rispettivamente, un primo nodo di uscita  $N_{\text{out1}}$  ed un secondo nodo di uscita  $N_{\text{out2}}$  del circuito di confronto 20 e sono collegati, rispettivamente, al terminale di pozzo del primo e del secondo transistore ad accoppiamento incrociato 22, 24. Inoltre, sui terminali di

porta sia del primo sia del secondo transistore di abilitazione 26, 28 è fornito un segnale sEVAL, pari alla negazione logica del segnale sEVAL\_N a cui si è fatto riferimento sopra.

Il circuito di confronto 20 comprende inoltre un primo transistore di uscita 30 e un secondo transistore di uscita 32, che sono transistori in modalità di arricchimento e canale N e presentano, ad esempio, caratteristiche simili.

I terminali di pozzo e sorgente del primo transistore di uscita 30 sono collegati, rispettivamente, al primo nodo di uscita N<sub>out1</sub> e al potenziale di riferimento (massa GND). I terminali di pozzo e sorgente del secondo transistore di uscita 32 sono collegati, rispettivamente, al secondo nodo di uscita N<sub>out2</sub> e al potenziale di riferimento. Inoltre, i terminali di pozzo del primo e del secondo transistore di uscita 30, 32 sono collegati al nodo di uscita N<sub>out</sub> di un rispettivo ramo di lettura di amplificatore di lettura 15, ricevendo pertanto, in questo esempio, il segnale di uscita scomp B.

Le tensioni presenti sul primo nodo di uscita  $N_{\text{out1}}$  e sul secondo nodo di uscita  $N_{\text{out2}}$  sono definite segnale sCOMP\_OUT\_N\_AB e, rispettivamente, segnale sCOMP\_OUT\_AB. Inoltre, le coppie di valori logici (sCOMP\_A, sCOMP\_B) e (sCOMP\_OUT\_AB, sCOMP\_OUT\_N\_AB) sono definite, rispettivamente, stato di ingresso e stato di uscita del

circuito di confronto 20.

Come illustrato nella Figura 5, lo stadio di confronto 12 dell'architettura di amplificatore di lettura 10 comprende inoltre un rispettivo circuito di latch 35 per ciascuno dei circuiti di confronto 20 sopra discussi.

Il circuito di latch 35 comprende due porte NAND 35a, 35b, aventi un rispettivo primo ingresso collegato al primo e, rispettivamente, al secondo nodo di uscita N<sub>out1</sub>, N<sub>out2</sub> del corrispondente circuito di confronto 20, in modo da ricevere, rispettivamente, il segnale sCOMP\_OUT\_N\_AB e il segnale sCOMP\_OUT\_AB (nell'esempio, riferiti al confronto tra le celle Cell\_A e Cell\_B). Il secondo ingresso di ciascuna porta NAND 35a, 35b è collegato all'uscita dell'altra porta NAND 35b, 35a.

L'uscita della porta NAND 35a costituisce inoltre qui l'uscita del circuito di latch 35, che fornisce un dato letto DATA\_AB, che ha un valore basso o alto (nell'intervallo [0 Vdd]), in funzione del confronto tra le correnti di cella I<sub>cell</sub>, nell'esempio delle celle Cell A e Cell B.

In base a quanto sopra, l'architettura di amplificatore di lettura 10 consente di eseguire un confronto tra gli stati in cui si trova una qualsiasi data coppia di celle di memoria 3, e in modo corrispondente un confronto tra le rispettive correnti di cella  $I_{\text{cell}}$ . In particolare, il confronto tra i segnali di uscita forniti dai rispettivi rami di lettura di

amplificatore di lettura 15 (ad esempio, sCOMP\_A e sCOMP\_B) determina le coppie di valori logici (ad esempio, sCOMP\_A, sCOMP\_B e sCOMP\_OUT\_AB, sCOMP\_OUT\_N\_AB) all'ingresso e all'uscita del relativo circuito di confronto 20 e pertanto i dati letti DATA\_AB risultanti dal confronto e forniti all'uscita del circuito di latch 35.

Lo stadio logico 13 viene quindi configurato per elaborare i dati letti associati ad un gruppo di un determinato numero di celle di memoria non volatile 3 e determinare così la relativa parola codice memorizzata.

Viene ora discusso in maggiore dettaglio il funzionamento del ramo di lettura di amplificatore di lettura 15 e del relativo circuito di confronto 20, facendo anche riferimento al diagramma temporale della Figura 6.

Si assume che i segnali di polarizzazione di decodifica di primo livello e di decodifica di secondo livello YO, YM siano pari a '1' e siano pertanto pari a un valore di tensione tale per cui il transistore di decodifica di primo livello TYO e i transistori di decodifica di secondo livello TYM siano in condizione di saturazione. Ad esempio, le tensioni dei segnali di polarizzazione di decodifica di primo livello e secondo livello YO, YM sono comprese in un intervallo tra 1,2 e 1,4 V, e sono pertanto superiori alla tensione di alimentazione V<sub>dd</sub>. Si assume inoltre, ancora una volta a titolo esemplificativo, che sulla bitline locale LBL sia

presente una tensione di 0,6 V. Inoltre, si assume che sul terminale di porta dell'elemento di accesso 3b sia presente un segnale SEL che abilita lo stesso elemento di accesso 3b, ovvero che consente la selezione della cella di memoria 3a.

Si assume inoltre che la tensione di riferimento  $V_{refp\_sa}$  sia tale per cui, quando il transistore di precarica TPRECH è inibito, il transistore di polarizzazione TP operi in saturazione e vi scorra attraverso una corrente di polarizzazione  $I_{pol}$  avente valore desiderato.

In modo non mostrato, il nodo di riferimento  $N_{ref}$  ed il transistore di polarizzazione TP possono far parte di specchi di corrente che possono essere controllati, ad esempio, dalla logica di controllo CL, in modo da imporre il valore  $I_{pol}$  di cui sopra. Senza che ciò implichi alcuna perdita di generalità, nel seguito si assume che la tensione di riferimento  $V_{refp\_sa}$  sia tale per cui il valore  $I_{pol}$  sia approssimativamente pari a 20  $\mu$ A. In generale, la tensione di riferimento  $V_{refp\_sa}$  è compresa tra massa e la tensione di alimentazione  $V_{dd}$ ; ad esempio, è valida la relazione  $0,1V < V_{refp\_sa} < (V_{dd}-0,3V)$ .

Inizialmente, il ramo di lettura di amplificatore di lettura 15 è controllato, ad esempio dalla logica di controllo CL, in modo da effettuare una fase di precarica.

In particolare, ad un istante  $t_0$  (si veda la Figura 6), il segnale sEVAL è basso (pari a  $^{\circ}0'$ , ad esempio ha una

tensione nulla), mentre il segnale sPRECH è alto ('1', ad esempio è pari alla tensione di alimentazione  $V_{\rm dd}$ ). Inoltre, il segnale sPRECH\_N è '0'; pertanto, il transistore di precarica TPRECH opera in regione lineare e vi scorre una corrente di precarica  $I_{\rm prech}$ . La corrente di precarica  $I_{\rm prech}$  è, ad esempio, dell'ordine di 100  $\mu$ A ed è comunque superiore al valore  $I_{\rm pol}$ .

Nel nodo di ingresso  $N_{\text{in}}$  viene pertanto iniettata una corrente  $I_{\text{i}}$ , che è pari alla somma della corrente di polarizzazione  $I_{\text{pol}}$  e della corrente di precarica  $I_{\text{prech}}$ .

Nello stesso istante  $t_0$ , il transistore di controllo superiore TC è inibito e anche il transistore di controllo inferiore TC' è inibito.

Tutta la corrente  $I_i$  scorre nella cella di memoria 3a e carica una capacità formata dalla bitline principale MBL. In pratica, la bitline principale MBL, che è associata a una capacità molto superiore a quelle associate alle bitline locali, viene caricata.

Inoltre, all'istante to, il segnale sEVAL\_N è pari a '1', quindi il transistore di valutazione TE opera in regione lineare, e di conseguenza scarica, ovvero forza a massa, il nodo di uscita Nout. Di conseguenza, il segnale sCOMP\_A (e analogamente il segnale sCOMP\_B del relativo ramo di lettura di amplificatore di lettura 15) è pari a '0'; questo significa che il transistore di lettura TS è spento.

Anche i transistori di uscita 30, 32 del circuito di confronto 30 sono inibiti.

Inoltre, poiché sEVAL è pari a '0', il primo ed il secondo transistore di abilitazione 26, 28 sono al di sopra della soglia e forzano i valori logici dei segnali sCOMP\_OUT\_AB e sCOMP\_OUT\_N\_AB a '1'. Di conseguenza, il primo ed il secondo transistore ad accoppiamento incrociato 22, 24 sono al di sotto della soglia.

Si noti che in questa fase il circuito di latch 35 opera in una condizione di memorizzazione; ovvero, i dati letti DATA AB mantengono l'ultimo valore assunto.

Ad un successivo istante  $t_1$ , i segnali sPRECH e sPRECH\_N commutano i loro valori, facendo sì che la fase di precarica termini ed inizi una fase di valutazione.

In particolare, il segnale sPRECH\_N va a '1', e questo porta allo spegnimento del transistore di precarica TPRECH, e pertanto anche della relativa corrente di precarica I<sub>prech</sub>. I segnali sEVAL e sEVAL\_N rimangono invece, rispettivamente, pari a '0' e a '1'. Di conseguenza, il nodo di uscita N<sub>out</sub> rimane a massa, e pertanto il segnale sCOMP\_A rimane pari a '0', mentre i segnali sCOMP\_OUT\_AB e sCOMP\_OUT\_N\_AB rimangono pari a '1'.

Il fatto che, all'istante  $t_1$ , il segnale sPRECH diventi pari a '0' significa che il transistore di controllo superiore TC si accende ed inizia a operare in saturazione;

anche il transistore di controllo inferiore TC' si accende ed inizia a operare in saturazione.

Nelle suddette condizioni, le correnti di cella  $I_{\text{cell}}$  che scorrono nelle celle di memoria (Cell\_A e Cell\_B) dipendono dai valori di resistenza dei rispettivi elementi di memorizzazione 3a, e pertanto dai dati memorizzati.

In particolare, una corrente di ramo  $I_{\text{branch}}$  pari a  $I_{\text{pol}}$ -  $I_{\text{cell}}$  scorre ora attraverso il transistore di controllo superiore TC e il transistore di controllo inferiore TC' verso il transistore di lettura TS.

Ad un istante successivo  $t_2$ , i segnali sEVAL e sEVAL\_N commutano il loro valore, facendo sì che la fase di valutazione termini ed inizi una fase di lettura.

In particolare, all'istante  $t_2$ , il segnale sEVAL\_N diventa '0', e questo conduce allo spegnimento del transistore di valutazione TE, che manteneva a massa il nodo di uscita  $N_{\rm out}$ , la tensione (ovvero, i segnali sCOMP\_A e sCOMP\_B) del quale diventa pertanto libera di variare.

Pertanto, i segnali sCOMP\_A e sCOMP\_B (corrispondenti alla tensione tra i terminali di porta e di sorgente del transistore di lettura TS) iniziano a salire dal valore zero iniziale, con una velocità e una temporizzazione dipendenti dal valore della corrente di cella  $I_{\text{cell}}$  (in particolare in funzione della corrente di ramo  $I_{\text{branch}}$  di cui sopra).

Ad esempio, nel caso in cui Cell A memorizzi un valore

logico '1' e Cell\_B memorizzi un valore logico '0', il segnale di tensione sCOMP\_B aumenterà più rapidamente del segnale di tensione sCOMP\_A (poiché la corrente di ramo  $I_{branch}$  sarà superiore per la cella Cell B).

Inoltre, poiché il segnale sEVAL ha assunto il valore '1', il primo ed il secondo transistore di abilitazione 26, 28 del circuito di confronto 20 scendono al di sotto della soglia, lasciando quindi i nodi di uscita N<sub>out1</sub>, N<sub>out2</sub> liberi di evolvere, in particolare in base al valore dei segnali sCOMP\_A e sCOMP\_B ai terminali di porta del primo e del secondo transistore di uscita 30, 32.

Il più veloce tra i segnali sCOMP\_A e sCOMP\_B fornisce la direzione di inversione al circuito di confronto 30, che il seguente circuito di latch 35 definisce quindi nell'intervallo [GND Vdd], fornendo i dati letti DATA\_AB (che, nell'esempio, avranno un valore basso, '0').

La Figura 7 mostra una possibile variante di realizzazione per il ramo di lettura di amplificatore di lettura 15, che differisce da quanto discusso con riferimento alla Figura 3 solo per una diversa configurazione del transistore di lettura TS, che è nuovamente di tipo NMOS, ma qui non è collegato a diodo.

In questo caso, il terminale di porta del transistore di lettura TS è collegato al nodo di uscita  $N_{\rm out}$  ed i terminali di pozzo e sorgente sono collegati al potenziale di

riferimento (massa, GND), così come il terminale di sorgente del transistore di valutazione TE.

Si noti che, invece del transistore di rilevamento TS, un elemento capacitivo di lettura potrebbe essere collegato tra il nodo di uscita  $N_{\text{out}}$  ed il potenziale di riferimento (GND).

In questa forma di realizzazione, la corrente di ramo  $I_{branch}$  (pari a  $I_{pol}-I_{cell}$ ) carica pertanto un nodo capacitivo (ovvero il terminale di porta del transistore di lettura TS), provocando così l'aumento del segnale di uscita (in questo caso, sCOMP\_A) in corrispondenza del nodo di uscita  $N_{out}$ , nuovamente con una velocità che è funzione del valore della stessa corrente di ramo  $I_{branch}$  ma in questo caso senza saturazione ad un valore definito dalla tensione tra i terminali di porta e di sorgente dello stesso transistore di lettura TS.

Un'altra differenza di questa forma di realizzazione è relativa alla configurazione del circuito di latch 35 per ciascuno dei circuiti di confronto 20 (i quali circuiti di confronto 20 invece non differiscono rispetto a quanto sopra discusso).

Come mostrato nella Figura 8, il circuito di latch 35 qui comprende inoltre un latch di uscita 36, che fornisce in corrispondenza di un'uscita di latch i dati letti (ad esempio DATA\_AB in caso di confronto tra le celle di memoria Cell\_A

e Cell\_B) ed ha un ingresso di latch accoppiato all'uscita della porta NAND 35a; il latch di uscita 36 ha inoltre un ingresso di abilitazione, che riceve un segnale di abilitazione E definente una temporizzazione di finestra di lettura per il latch dei dati letti DATA AB.

Il circuito di latch 35 comprende un'ulteriore porta NAND 35c che riceve al suo ingresso entrambi i segnali sCOMP\_OUT\_AB e sCOMP\_OUT\_N\_AB e fornisce, tramite un buffer 37, il segnale di abilitazione E di cui sopra per il latch di uscita 36.

La temporizzazione della finestra di lettura è pertanto definita dall'evoluzione dei segnali sCOMP\_OUT\_AB e sCOMP\_OUT\_N\_AB (ai nodi di uscita Nout1, Nout2 del circuito di confronto 20), che sono entrambi alti quando la fase di lettura inizia ed evolvono verso il basso; una volta che il segnale di abilitazione E è alto, la lettura è conclusa e i dati letti DATA\_AB vengono bloccati ("latched") dal latch di uscita 36.

Viene ora discusso un ulteriore aspetto della presente soluzione, riguardante una possibile codifica dei dati memorizzati nella matrice di memoria (e una relativa configurazione dello stadio logico 13).

Secondo tale codifica, dato un insieme di parole codice ottenibili dai valori memorizzati di un determinato numero  $N_{\text{c}}$  di celle di memoria non volatile in un gruppo, le

informazioni possono essere memorizzate in almeno due sottoinsiemi di tale insieme di parole codice comprendenti ciascuno almeno una parola codice, ciascuna parola codice in uno stesso sottoinsieme avendo uno stesso peso di Hamming e ciascuna parola codice appartenente ad un sottoinsieme avendo una distanza di Hamming pari a o maggiore di due rispetto a ciascuna parola codice appartenente ad un altro sottoinsieme.

Ad esempio, il numero  $N_c$  di celle di memoria 3 in un gruppo può essere tre, come mostrato nella Tabella 1 di seguito. Con tre celle (Cell\_A, Cell\_B, Cell\_C) e due sottoinsiemi (SB1, SB2), possono essere definite quattro parole codice: {000, 011, 101, 110}; in tal modo, possono essere ottenuti quattro simboli (o mappe di bit) per la codifica dei dati memorizzati.

| Cell_A | Cell_B | Cell_C | Sottoinsieme | Simbolo | Марра  |

|--------|--------|--------|--------------|---------|--------|

|        |        |        |              |         | di bit |

| 1      | 1      | 0      | SB1          | 0       | 00     |

| 1      | 0      | 1      | SB1          | 1       | 01     |

| 0      | 1      | 1      | SB1          | 2       | 10     |

| 0      | 0      | 0      | SB2          | 3       | 11     |

Tabella 1

In un altro esempio, il numero  $N_{\rm c}$  può essere quattro, come mostrato nella Tabella 2 di seguito. Con quattro celle

(Cell\_A, Cell\_B, Cell\_C, Cell\_D) e due sottoinsiemi (SB1, SB2), possono essere definite otto parole codice e otto simboli per la codifica dei dati memorizzati.

| Cell_A | Cell_B | Cell_C | Cell_D | Sottoinsieme | Simbolo | Марра |

|--------|--------|--------|--------|--------------|---------|-------|

|        |        |        |        |              |         | di    |

|        |        |        |        |              |         | bit   |

| 1      | 0      | 0      | 0      | SB1          | 0       | 000   |

| 0      | 1      | 0      | 0      | SB1          | 1       | 001   |

| 0      | 0      | 1      | 0      | SB1          | 2       | 010   |

| 0      | 0      | 0      | 1      | SB1          | 3       | 011   |

| 0      | 1      | 1      | 1      | SB2          | 4       | 100   |

| 1      | 0      | 1      | 1      | SB2          | 5       | 101   |

| 1      | 1      | 0      | 1      | SB2          | 6       | 110   |

| 1      | 1      | 1      | 0      | SB2          | 7       | 111   |

Tabella 2

In questa forma di realizzazione, durante la lettura (o la decodifica) dei dati memorizzati nel modo codificato, è prima richiesto di determinare il sottoinsieme a cui appartengono i dati.

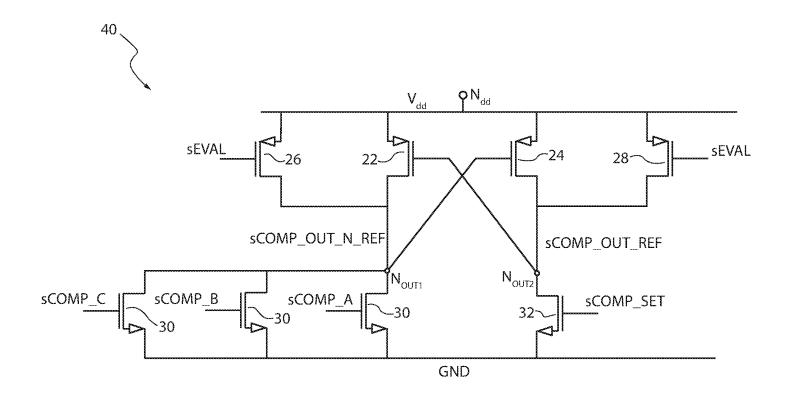

Lo stadio di lettura 11 dell'architettura di amplificatore di lettura 10 comprende pertanto inoltre un circuito di definizione di sottoinsieme 40 (per ciascun gruppo di celle di memoria 3 definenti una parola codice), configurato per consentire la determinazione del

sottoinsieme a cui appartiene una parola codice da leggere.

Questo circuito di definizione di sottoinsieme 40 è implementato come un comparatore, configurato per confrontare un segnale indicativo della somma delle correnti di cella  $I_{cell}$  di tutte le celle di memoria 3 del gruppo (definente la parola codice da leggere) con almeno un segnale di soglia, indicativo di una corrente di riferimento o fissa  $I_{ref}$ , avente un valore opportuno che consente una corretta discriminazione tra i sottoinsiemi.

Come discusso in precedenza, la somma effettivamente implementata è tra ciascuna corrente di ramo  $I_{branch}$ , ovvero la corrente di cella  $I_{cell}$  riferita alla corrente di polarizzazione  $I_{pol}$ , ovvero:  $(I_{pol}-I_{cellA})$  +  $(I_{pol}-I_{cellB})$  +  $(I_{pol}-I_{cellC})$ . Analogamente, il segnale di soglia è riferito alla stessa corrente di polarizzazione  $I_{pol}$  (in realtà, a tre volte la stessa corrente di polarizzazione  $I_{pol}$ ), al fine di implementare il corretto confronto e la discriminazione di sottoinsieme.

Nell'esempio della Tabella 1, in cui una parola codice è definita da tre celle di memoria, le parole codice nel primo sottoinsieme hanno due celle di memoria nello stato di 'SET' (o '1') e una nello stato di 'RESET' (o '0'), mentre le parole codice nel secondo sottoinsieme non hanno celle di memoria nello stato di 'SET' e tre nello stato di 'RESET'. In questo esempio, il segnale di soglia può essere indicativo

di un riferimento o di una corrente fissa  $I_{ref}$  il cui valore corrisponde a quello di una singola cella di memoria di riferimento nello stato di 'SET':  $I_{ref}=I_{ref}$  SET.

Ad esempio, la corrente  $I_{\rm ref}$  può essere ricavata come media della corrente di un certo numero di celle di memoria non volatile 3 programmate nello stesso stato (in questo caso, lo stato di SET); in alternativa, la corrente  $I_{\rm ref}$  può essere ricavata da una cella tipica scelta nello stato di SET o da un'altra corrente fissa di valore opportuno.

In maggiore dettaglio, e come mostrato nella Figura 9A, il circuito di definizione di sottoinsieme 40 in questo caso comprende, analogamente ai circuiti di confronto 20 sopra discussi: un primo transistore ad accoppiamento incrociato, nuovamente indicato con 22, ed un secondo transistore ad accoppiamento incrociato 24 e un primo transistore di abilitazione 26 ed un secondo transistore di abilitazione 28, di una modalità di arricchimento e canale P.

I terminali di sorgente del primo e secondo transistore ad accoppiamento incrociato 22, 24 e del primo e secondo transistore di abilitazione 26, 28 sono collegati al nodo di alimentazione  $N_{\rm dd}$ , e sono pertanto posti alla tensione di alimentazione  $V_{\rm dd}$ . I terminali di porta del primo e secondo transistore ad accoppiamento incrociato 22, 24 sono collegati, rispettivamente, al terminale di pozzo del secondo transistore ad accoppiamento incrociato 24 e al

terminale di pozzo del primo transistore ad accoppiamento incrociato 22.

I terminali di pozzo del primo e secondo transistore di abilitazione 26, 28 formano, rispettivamente, un primo nodo di uscita N<sub>out1</sub> ed un secondo nodo di uscita N<sub>out2</sub> e sono collegati, rispettivamente, ai terminali di pozzo del primo e del secondo transistore ad accoppiamento incrociato 22, 24. Inoltre, sui terminali di porta del primo e del secondo transistore di abilitazione 26, 28 è fornito un segnale sEVAL, pari alla negazione logica del segnale di riferimento sEVAL N di cui sopra.

Il circuito di definizione di sottoinsieme 40 comprende inoltre un numero  $N_c$  di primi transistori di uscita 30 (corrispondenti al numero di celle di memoria 3 nella parola codice), accoppiati in parallelo, tra il primo nodo di uscita  $N_{\rm out1}$  ed il potenziale di riferimento (GND), riceventi ad un rispettivo terminale di porta il segnale di uscita (nell'esempio, sCOMP\_A, sCOMP\_B, sCOMP\_C) fornito da un rispettivo ramo di lettura di amplificatore di lettura 15 dell'architettura di amplificatore di lettura 10.

Il circuito di definizione di sottoinsieme 40 comprende inoltre, in questo esempio (che è riferito alla codifica della Tabella 1), un unico secondo transistore di uscita 32, che è un transistore in modalità di arricchimento e canale N, collegato tra il secondo nodo di uscita  $N_{\text{out2}}$  e il

potenziale di riferimento (GND) e ricevente in corrispondenza di un terminale di porta un segnale di confronto sCOMP\_SET indicativo della corrente di riferimento o fissa  $I_{\text{ref}}$  (il cui valore corrisponde in questo caso a  $I_{\text{ref}}$  set).

Al primo ed al secondo nodo di uscita N<sub>out1</sub>, N<sub>out2</sub> è presente un rispettivo segnale di uscita sCOMP\_OUT\_N\_REF e sCOMP\_OUT\_REF, indicativo del determinato sottoinsieme. Nell'esempio, il segnale sCOMP\_OUT\_REF è '0' per il sottoinsieme SB1 e il segnale sCOMP\_OUT\_N\_REF è '0' per il sottoinsieme SB2.

Lo stadio di lettura 11 dell'architettura di amplificatore di lettura 10 comprende inoltre un rispettivo circuito di latch per ciascuno dei circuiti di definizione di sottoinsieme 40 sopra discussi.

Il circuito di latch (in modo corrispondente al circuito mostrato nella Figura 5) comprende due porte NAND, aventi un rispettivo primo ingresso collegato al primo e, rispettivamente, al secondo nodo di uscita del relativo circuito di definizione di sottoinsieme 40, in modo da ricevere, rispettivamente, il segnale sCOMP\_OUT\_N\_REF e il segnale sCOMP\_OUT\_REF. Il secondo ingresso di ciascuna porta NAND è collegato all'uscita dell'altra porta NAND.

L'uscita della porta NAND costituisce inoltre qui l'uscita del circuito di latch, che fornisce un dato di

sottoinsieme DATA\_REF, che ha un valore basso o alto, indicativo del sottoinsieme determinato. Nell'esempio, DATA\_REF è '0' per il sottoinsieme SB1 e '1' per il sottoinsieme SB2.

Nel caso in cui sia implementata la codifica della Tabella 2, come mostrato nella Figura 9B, il circuito di definizione di sottoinsieme 40 comprende un certo numero di secondi transistori di uscita 32, che sono transistori in modalità di arricchimento e canale N, collegati tra il secondo nodo di uscita N<sub>out2</sub> e il potenziale di riferimento (GND) e riceventi ad un terminale di porta un rispettivo segnale di confronto sCOMP\_SET o sCOMP\_RESET indicativo di una rispettiva corrente di riferimento o fissa I<sub>ref</sub> (il cui valore può corrispondere in questo caso a I<sub>ref\_SET</sub> o I<sub>ref\_RESET</sub>, ovvero una corrente di riferimento o fissa il cui valore corrisponde a quello di una singola cella di memoria di riferimento nello stato di 'RESET').

Infatti, nel caso in cui la parola codice sia definita da quattro celle di memoria, le parole codice nel primo sottoinsieme SB1 hanno una cella di memoria nello stato di 'SET' e tre celle di memoria nello stato di 'RESET'; mentre le parole codice nel secondo sottoinsieme SB2 hanno tre celle di memoria nello stato di 'SET' e una nello stato di 'RESET'.

In questo esempio, il segnale di soglia può quindi essere indicativo di una corrente di riferimento o fissa  $I_{\text{ref}}$

il cui valore corrisponde a qualsiasi combinazione idonea di celle di memoria di riferimento nello stato di 'SET' o 'RESET', ad esempio:  $I_{ref}=2 \cdot I_{ref}$  SET+ $2 \cdot I_{ref}$  SET.

Anche in questo esempio, il segnale sCOMP\_OUT\_REF è '0' per il sottoinsieme SB1 e il segnale sCOMP\_OUT\_N\_REF è '0' per il sottoinsieme SB2.

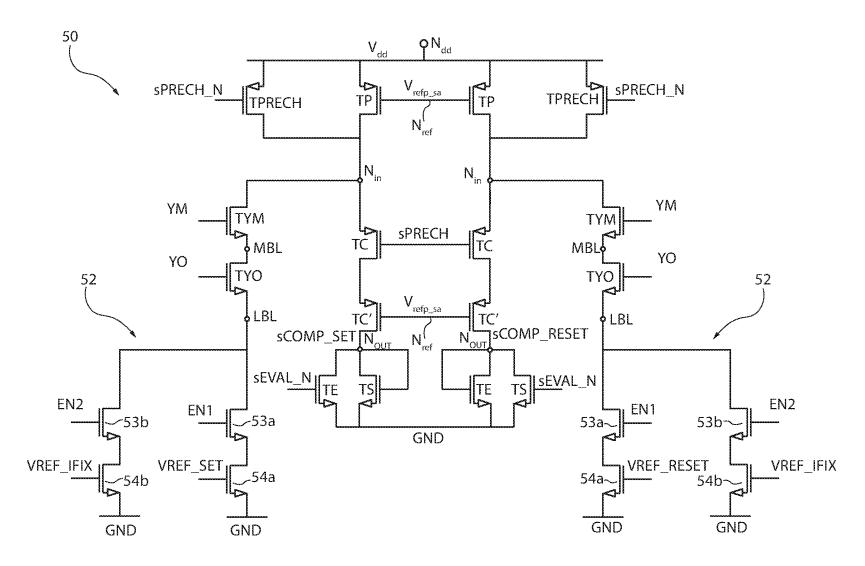

La Figura 10 mostra una possibile implementazione di un circuito di generazione di riferimenti 50 nell'architettura di amplificatore di lettura 10, configurato per generare i segnali sCOMP\_SET e, rispettivamente, sCOMP\_RESET di cui sopra per il circuito di definizione di sottoinsieme 40.

Questo circuito corrisponde in gran parte ad un ramo di lettura di amplificatore di lettura 15 dello stadio di lettura 11 dell'architettura di amplificatore di lettura 10 (mostrato nella Figura 3), per cui elementi simili saranno indicati con gli stessi numeri di riferimento e non verranno discussi nuovamente nel dettaglio.

Diversamente dal ramo di lettura di amplificatore di lettura 15, in questo circuito di generazione di riferimento 50 la bitline locale (in questo caso "fittizia", "dummy", non essendo collegata ad una cella di memoria) è accoppiata ad un generatore di riferimento 52 configurato per generare la corrente di riferimento o fissa  $I_{\rm ref}$ .

Il generatore di riferimento 52 comprende un primo transistore di abilitazione 53a ed un primo transistore di

riferimento 54a, entrambi di tipo NMOS, collegati in serie tra la bitline locale LBL (fittizia) ed il potenziale di riferimento (GND), il primo transistore di abilitazione 53a avendo un terminale di porta ricevente un primo segnale di abilitazione EN1 ed il primo transistore di riferimento 54a avendo un terminale di porta ricevente una prima tensione di riferimento VREF\_SET (o VREF\_RESET), essendo indicativi della corrente I<sub>ref\_SET</sub> di una cella di memoria di riferimento nello stato di 'SET' (o analogamente della corrente I<sub>ref\_RESET</sub> di una cella di memoria nello stato di 'RESET').

Il generatore di riferimento 52 comprende inoltre un secondo transistore di abilitazione 53b ed un secondo transistore di riferimento 54b, entrambi di tipo NMOS, collegati in serie tra la bitline locale LBL (fittizia) ed il potenziale di riferimento (GND), il secondo transistore di abilitazione 53b avendo un terminale di porta ricevente un secondo segnale di abilitazione EN2 ed il secondo transistore di riferimento 54b avendo un terminale di porta ricevente ricevente una seconda tensione di riferimento VREF\_IFIX, indicativa di un valore fisso per la corrente Iref\_SET o Iref\_RESET, simulando la corrente circolante in una cella di memoria 3 nello stato di SET o RESET.

A seconda dei valori del primo e del secondo segnale di abilitazione EN1, EN2, il circuito di generazione di

riferimenti 50 genera quindi i segnali sCOMP\_SET, sCOMP\_RESET di cui sopra, indicativi di una corrente di riferimento o fissa  $I_{ref}$  (il cui valore corrisponde a  $I_{ref\_SET}$ , rispettivamente a  $I_{ref\_RESET}$ ).

Viene ora fornita una descrizione esemplificativa relativa al funzionamento dello stadio logico 13 dell'architettura di amplificatore di lettura 10, configurato per elaborare i dati letti associati a un gruppo di celle di memoria non volatile 3 e determinare così la relativa parola codice memorizzata (come discusso in precedenza, può essere implementata una logica a maggioranza per identificare la parola codice memorizzata).

Si fa dapprima riferimento alla codifica esemplificativa della Tabella 1 di cui sopra, assumendo, a titolo esemplificativo, che sia stata memorizzata una parola codice [0 1 1], con Cell\_A='0', Cell\_B='1' e Cell\_C='1'.

La tabella seguente, Tabella 3, riassume i risultati previsti all'uscita dei circuiti di confronto 20 (considerando che DATA\_REF è '1'):

| Confronto       | Risultato                |

|-----------------|--------------------------|

| DATA_AB, A vs B | B vince                  |

| DATA_AC, A vs C | C vince                  |

| DATA_BC, B vs C | Possono vincere B o C, X |

## Tabella 3

Si noti che solo cell\_A con valore '0' perde i tre confronti con le altre due celle (Cell\_B e Cell\_C); lo stadio logico 13 determina quindi che la parola codice memorizzata è [0 1 1].

In questo esempio, se DATA\_REF è '0', allora la parola codice memorizzata è [0 0 0], indipendentemente dai risultati del confronto.

Si fa ora riferimento alla codifica esemplificativa della Tabella 2 di cui sopra, assumendo, a titolo esemplificativo, che sia stata memorizzata una parola codice [0 0 0 1], con Cell\_A='0', Cell\_B='0', Cell\_C='0' e Cell\_D='1'.

Anche in questo caso, può essere implementata dallo stadio logico 13 una logica a maggioranza per identificare la parola codice memorizzata.

La tabella seguente, Tabella 4, riassume in questo caso i risultati previsti all'uscita dei circuiti di confronto 20 (considerando che DATA REF è '1'):

| Confronto       | Risultato                |

|-----------------|--------------------------|

| DATA_AB, A vs B | Possono vincere A o B, X |

| DATA_AC, A vs C | Possono vincere A o C, X |

| DATA_AD, A vs D | D                        |

| DATA_BC, B vs C | Possono vincere B o C, X |

|-----------------|--------------------------|

| DATA_BD, B vs D | D                        |

| DATA_CD, C vs D | D                        |

## Tabella 4

Si noti che solo cell\_D con valore 1 vince i tre confronti con le altre tre celle di memoria 3; lo stadio logico 13 determina quindi che la parola codice memorizzata è [0 0 0 1]; in altre parole è sufficiente identificare la posizione di corrente massima, per le parole codice nel Sottoinsieme SB1 (è analogamente sufficiente identificare la posizione di corrente minima, nel caso del Sottoinsieme SB2).

I vantaggi che la presente soluzione permette di ottenere risultano chiari dalla precedente descrizione.

In generale, l'architettura di amplificatore di lettura 10 consente di confrontare i dati memorizzati in qualsiasi cella di memoria 3 del dispositivo di memoria non volatile 1 con qualsiasi numero opportuno di altre celle di memoria 3, in modo da decodificare le parole codice utilizzate per la memorizzazione di informazioni.

Di conseguenza, la soluzione qui descritta consente di ottenere un'occupazione di memoria più compatta ed efficiente.

Inoltre, la soluzione qui descritta necessita di meno celle di memoria 3 per comporre la matrice, determinando un

possibile miglioramento della resa.

Inoltre, la soluzione descritta fornisce un tempo di accesso simile alle soluzioni note, senza aggravio di tempi.

Il risultante dispositivo di memorizzazione non volatile 1 può pertanto trovare impiego in numerosi contesti.

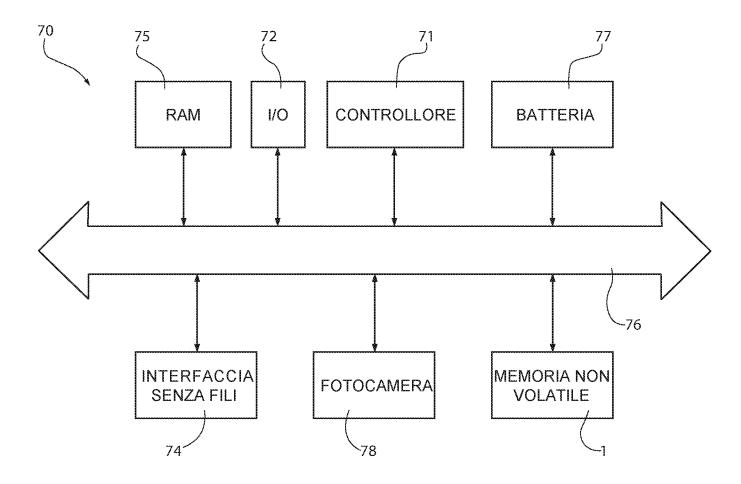

Ad esempio, la Figura 11 illustra una porzione di un apparecchio elettronico 70, che può essere, ad esempio: un PDA ("Personal Digital Assistant - Assistente Digitale Personale"); un computer portatile o fisso, possibilmente con capacità di trasferimento dati in modo wireless; un telefono mobile; un lettore audio digitale; una macchina fotografica o una telecamera; o ulteriori dispositivi in grado di elaborare, memorizzare, trasmettere e ricevere informazioni.

L'apparecchio elettronico 70 comprende: un controllore 71 (ad esempio, dotato di un microprocessore, un DSP o un microcontrollore); un dispositivo di ingresso/uscita 72 (ad esempio, dotato di un tastierino numerico e di un display), per l'immissione in ingresso e la visualizzazione di dati; memorizzazione il dispositivo di non volatile un'interfaccia senza fili 74, ad esempio un'antenna, per trasmettere e ricevere dati attraverso una rete comunicazione senza fili a radiofrequenza; ed una memoria RAM 75. Tutti i componenti dell'apparecchio elettronico 70 sono accoppiati tramite un bus 76. Una batteria 77 può essere

utilizzata come sorgente di alimentazione di energia elettrica nell'apparecchio elettronico 70, che può inoltre essere dotato di fotocamera, o videocamera o telecamera 68. Inoltre, il controllore 71 può controllare il dispositivo di memorizzazione non volatile 1, ad esempio cooperando con la logica di controllo CL.

Inoltre, risulta chiaro che a quanto qui descritto ed illustrato possono essere apportate modifiche e variazioni, senza per questo allontanarsi dall'ambito di protezione della presente invenzione, come definita nelle rivendicazioni allegate.

Ad esempio, si sottolinea ancora una volta che la presente architettura di amplificatore di lettura 10 può essere utilizzata per celle di memoria 3, che possono essere diverse dalle celle di memoria di tipo PCM, ad esempio per celle di memoria ST-RAM o RRAM.

## <u>RIVENDI</u>CAZIONI

1. Architettura di amplificatore di lettura (10) per un dispositivo di memoria non volatile (1) comprendente una pluralità di celle di memoria (3), in cui gruppi di celle di memoria memorizzano rispettive parole codice formate da stati logici, alto logico ('1') o basso logico ('0'), memorizzati dalle celle di memoria del gruppo; detta architettura di amplificatore di lettura (10) comprendendo:

una pluralità di rami di lettura di amplificatore di lettura (15), ciascun ramo di lettura di amplificatore di lettura (15) accoppiato ad una rispettiva cella di memoria (3) e configurato per fornire un segnale di uscita (sCOMP\_A), che è indicativo di una corrente di cella (I<sub>cell</sub>) che scorre attraverso la stessa cella di memoria (3);

uno stadio di confronto (12), configurato per eseguire un confronto tra le correnti di cella ( $I_{cell}$ ) di celle di memoria (3) di un gruppo; e

uno stadio logico (13), configurato per determinare, in base ai risultati di confronto forniti dallo stadio di confronto (12), una parola codice letta relativa al gruppo di celle di memoria (3).

2. Architettura di amplificatore di lettura secondo la rivendicazione 1, in cui il segnale di uscita (sCOMP\_A) del ramo di lettura di amplificatore di lettura (15) è correlato da una relazione inversa alla rispettiva corrente di cella

$(I_{cell})$ .

3. Architettura di amplificatore di lettura secondo la rivendicazione 1 o 2, in cui il segnale di uscita (sCOMP\_A) del ramo di lettura di amplificatore di lettura (15) è funzione di una corrente di ramo ( $I_{branch}$ ) che scorre attraverso il ramo di lettura di amplificatore di lettura (15), data da:

$I_{branch} = I_{pol} - I_{cell}$

in cui  $I_{\text{pol}}$  è una corrente di polarizzazione fornita al ramo di lettura di amplificatore di lettura (15) e  $I_{\text{cell}}$  è detta corrente di cella.

4. Architettura di amplificatore di lettura secondo una qualsiasi delle rivendicazioni precedenti, in cui il ramo di lettura di amplificatore di lettura (15) comprende un transistore di polarizzazione (TP) accoppiato tra un nodo di alimentazione  $(N_{dd})$  e un nodo di ingresso  $(N_{in})$  e avente un terminale di porta ricevente una tensione di riferimento  $(V_{refp sa})$ , in modo che una corrente di polarizzazione  $(I_{pol})$ vi scorra attraverso e verso il nodo di ingresso; in cui la cella di memoria (3) è accoppiata al nodo di ingresso (Nin) tramite almeno un transistore di selezione (TYM, TYO) che consente la selezione della cella di memoria (3); il ramo di di amplificatore di lettura (15) comprendendo lettura inoltre un elemento di lettura di corrente (TS) accoppiato al nodo di ingresso (Nin) e configurato per fornire il segnale

di uscita (sCOMP\_A) in funzione di una corrente di ramo ( $I_{branch}$ ), che è una differenza tra la corrente di polarizzazione ( $I_{pol}$ ) e la corrente di cella ( $I_{cell}$ ) che scorre attraverso la cella di memoria selezionata.

- 5. Architettura di amplificatore di lettura secondo la rivendicazione 4, in cui l'elemento di lettura di corrente (TS) è un transistore di lettura, collegato a diodo tra un nodo di uscita ( $N_{out}$ ) su cui è fornito il segnale di uscita ( $SCOMP_A$ ) ed un terminale di riferimento (GND); in cui il nodo di uscita ( $N_{out}$ ) è accoppiato al nodo di ingresso ( $N_{in}$ ) tramite un elemento di commutazione (TC).

- 6. Architettura di amplificatore di lettura secondo la rivendicazione 4, in cui il ramo di lettura di amplificatore di lettura (15) comprende inoltre un transistore di forzatura (TE) avente un terminale di pozzo accoppiato a un nodo di uscita (Nout) su cui è fornito il segnale di uscita (SCOMP\_A), un terminale di sorgente accoppiato ad un terminale di riferimento (GND) e un terminale di porta ricevente un segnale di abilitazione (sEVAL\_N) tale da, in alternativa, accoppiare il nodo di uscita (Nout) al terminale di riferimento (GND) o consentire un'evoluzione della tensione sul nodo di uscita (Nout) in funzione della corrente di ramo (Ibranch); in cui l'elemento di lettura di corrente (TS) è un transistore di lettura, accoppiato tra il terminale di sorgente del transistore di forzatura (TE) ed il terminale

di riferimento (GND) e avente un terminale di porta accoppiato al nodo di uscita ( $N_{\text{out}}$ ); in cui il nodo di uscita ( $N_{\text{out}}$ ) è accoppiato al nodo di ingresso tramite un elemento di commutazione (TC).

- 7. Architettura di amplificatore di lettura secondo una qualsiasi delle rivendicazioni precedenti, in cui lo stadio di confronto (12) è configurato per eseguire confronti a coppie tra i segnali di uscita (sCOMP\_A, SCOMP\_B) dei rami di lettura di amplificatore di lettura (15) accoppiati a rispettive celle di memoria (3) del gruppo, ottenendo rispettivi risultati di confronto a coppie, a seconda di quale corrente di cella delle celle di memoria (3) confrontate è superiore; in cui lo stadio logico (13) è configurato per determinare la parola codice letta in base ai risultati di confronto a coppie.

- 8. Architettura di amplificatore di lettura secondo la rivendicazione 7, in cui lo stadio logico (13) è configurato per determinare la parola codice letta in base ad una logica a maggioranza.

- 9. Architettura di amplificatore di lettura secondo una qualsiasi delle rivendicazioni precedenti, in cui, dato un insieme di parole codice ottenibile dai valori memorizzati nelle celle di memoria (3) di un gruppo, informazioni sono memorizzate in almeno due sottoinsiemi (SB1, SB2) di detto insieme di parole codice, comprendenti ciascuno almeno una

parola codice, ciascuna parola codice in uno stesso sottoinsieme avendo uno stesso peso di Hamming e ciascuna parola codice appartenente ad un sottoinsieme (SB1) avendo una distanza di Hamming pari a o maggiore di due rispetto a ciascuna parola codice appartenente a un altro sottoinsieme (SB2); in cui l'architettura di amplificatore di lettura (10) comprende inoltre un circuito di definizione di sottoinsieme (40) per ciascun gruppo di celle di memoria (3), configurato per consentire la determinazione del sottoinsieme a cui appartiene una parola codice da leggere.

- 10. Architettura di amplificatore di lettura secondo la rivendicazione 9, in cui lo stadio logico (13) è configurato per determinare la parola codice letta corrispondente al gruppo di celle di memoria (3) anche in base alla determinazione di sottoinsieme da parte del circuito di definizione di sottoinsieme (40).

- 11. Architettura di amplificatore di lettura secondo la rivendicazione 9 o 10, in cui il circuito di definizione di sottoinsieme (40) include un circuito comparatore, configurato per confrontare un segnale indicativo di una somma delle correnti di cella ( $I_{cell}$ ) di tutte le celle di memoria (3) del gruppo con un segnale di soglia, il cui valore consente una discriminazione tra i sottoinsiemi (SB1, SB2).

- 12. Architettura di amplificatore di lettura secondo la

rivendicazione 11, in cui il segnale di soglia è indicativo di una corrente di riferimento o fissa  $(I_{ref})$ , essendo una combinazione di una o più correnti di cella in celle di memoria (3) in un primo stato logico e/o di una o più correnti di cella in celle di memoria (3) in un secondo stato logico.

13. Architettura di amplificatore di lettura secondo la rivendicazione 12, in cui il circuito di definizione di sottoinsieme (40) comprende: un primo transistore accoppiamento incrociato (22) e un secondo transistore ad accoppiamento incrociato (24) collegati tra un nodo di alimentazione  $(N_{dd})$  e una prima  $(N_{out1})$ , rispettivamente una seconda (N<sub>out2</sub>), uscita ed aventi terminali di collegati, rispettivamente, al secondo e primo nodo di uscita; un numero di primi transistori di uscita (30), il numero corrispondendo al numero di celle di memoria (3) nella parola codice, accoppiati in parallelo, tra il primo nodo di uscita (N<sub>out1</sub>) ed un potenziale di riferimento riceventi ad un rispettivo terminale di porta il segnale di uscita (sCOMP A, sCOMP B, sCOMP C) fornito da un rispettivo ramo di lettura di amplificatore di lettura (15); ed almeno un transistore di uscita (32), accoppiato tra il secondo nodo di uscita (Nout2) ed il potenziale di riferimento (GND) e ricevente ad un terminale di porta un segnale di confronto (sCOMP SET, sCOMP RESET) indicativo della corrente riferimento o fissa (Iref); in cui, al primo ed al secondo

nodo di uscita ( $N_{\text{out1}}$ ,  $N_{\text{out2}}$ ) è presente un rispettivo segnale di uscita ( $\text{sCOMP\_OUT\_N\_REF}$ ,  $\text{sCOMP\_OUT\_REF}$ ), indicativo del determinato sottoinsieme.

- 14. Dispositivo di memoria (1) comprendente almeno un'architettura di amplificatore di lettura (10) secondo una qualsiasi delle rivendicazioni precedenti, il dispositivo di memoria (1) comprendendo inoltre dette celle di memoria (3), le celle di memoria (3) essendo del tipo in cui lo stato logico memorizzato viene modificato tramite applicazione di una corrente e lo stato logico memorizzato nella cella di memoria viene letto leggendo una corrente che vi scorre attraverso.

- 15. Dispositivo di memoria (1) secondo la rivendicazione 14, in cui le celle di memoria (3) sono celle PCM Phase Change Memory.

FIG.1

FIG.2

FIG.6 Fig.6

FIG.9A

FIG.9B

FIG.10

FIG.11