# ITALIAN PATENT OFFICE

Document No.

102012902101191A1

**Publication Date**

20140514

**Applicant**

STMICROELECTRONICS S.R.L.

Title

CIRCUITO ELETTRONICO DIGITALE DI INTERFACCIA PER UN TRASDUTTORE ACUSTICO, E RELATIVO SISTEMA DI TRASDUZIONE ACUSTICO

#### DESCRIZIONE

del brevetto per invenzione industriale dal titolo:

"CIRCUITO ELETTRONICO DIGITALE DI INTERFACCIA PER UN TRASDUTTORE ACUSTICO, E RELATIVO SISTEMA DI TRASDUZIONE ACUSTICO"

di STMICROELECTRONICS S.R.L.

di nazionalità italiana

con sede: VIA C. OLIVETTI, 2

AGRATE BRIANZA (MB)

Inventori: ZERBINI Martino, MOLINARI Luca

\* \* \*

La presente invenzione si riferisce ad un circuito elettronico digitale di interfaccia per un trasduttore acustico, e ad un relativo sistema di trasduzione acustico.

Sono noti trasduttori acustici, ad esempio microfoni MEMS (Micro-Electro-Mechanical System), comprendenti una struttura sensibile micromeccanica, atta a trasdurre onde di pressione acustica in una grandezza elettrica (ad esempio una variazione capacitiva), ed un'elettronica di lettura, atta ad effettuare opportune operazioni di elaborazione (tra cui operazioni di amplificazione e filtraggio) di tale grandezza elettrica in modo da fornire un segnale elettrico di uscita, analogico (ad esempio una tensione elettrica), o digitale (ad esempio un segnale PDM, Pulse Density Modulation, in modulazione a densità di

# impulsi).

Tale segnale elettrico, eventualmente elaborato ulteriormente da un circuito elettronico di interfaccia, viene quindi reso disponibile per un sistema elettronico esterno, ad esempio un circuito di controllo a microprocessore di un apparecchio elettronico incorporante il trasduttore acustico.

La struttura sensibile micromeccanica comprende in generale un elettrodo mobile, realizzato come diaframma o membrana, disposto affacciato ad un elettrodo fisso, per realizzare i piatti di un condensatore di rilevamento a capacità variabile. L'elettrodo mobile è generalmente ancorato, mediante una sua porzione perimetrale, ad un substrato, mentre una sua porzione centrale è libera di muoversi o flettersi in risposta alla pressione esercitata da onde di pressione acustica incidenti. L'elettrodo mobile e l'elettrodo fisso realizzano un condensatore, e la flessione della membrana che costituisce l'elettrodo mobile causa una variazione di capacità, in funzione del segnale acustico da rilevare.

In generale, le prestazioni elettriche del trasduttore acustico dipendono dalle caratteristiche meccaniche della struttura sensibile di rilevamento, ed inoltre dalla configurazione delle associate camere acustiche, anteriore e posteriore, ovvero delle camere affacciate ad una

rispettiva faccia, anteriore o posteriore, della membrana, ed attraversate in uso dalle onde di pressione incidenti la membrana, e che si allontanano dalla stessa.

Sono numerose le applicazioni in cui è richiesto il rilevamento di onde di pressione acustica con un ampio intervallo dinamico (cosiddetto "dynamic range"), ovvero la possibilità di rilevare segnali con livelli di pressione acustica (SPL - Sound Pressure Level) elevati, al contempo mantenendo alti valori del rapporto segnale rumore (SNR - Signal to Noise Ratio), e segnali con ridotti livelli di pressione acustica con elevata sensibilità.

In sostanza, è spesso una importante richiesta di ottimizzare il compromesso progetto quella l'ottenimento di ampio intervallo dinamico un nel delle onde di rilevamento pressione acustica е l'ottenimento di un basso rapporto tra segnale e rumore.

Il brevetto statunitense US 6,271,780 B1 descrive a tal proposito una soluzione per incrementare l'intervallo dinamico in un sistema acustico, comprendente un convertitore analogico/digitale (ADC - Analog to Digital Converter), atto a ricevere un segnale di rilevamento analogico da un trasduttore acustico. Tale soluzione prevede di sottoporre il segnale analogico di ingresso, in parallelo, a due percorsi di elaborazione di segnale, aventi una prima porzione analogica ed una seconda porzione

digitale, ciascuno rispettivo fattore di е un amplificazione e guadagno, in modo da adattarsi rispettivamente a segnali con basso, o alto, livello di pressione acustica. I due segnali digitali all'uscita dei percorsi di elaborazione vengono ricombinati per fornire risultante di uscita. un segnale Prima dell'operazione di ricombinazione, i due segnali devono essere sottoposti ad una operazione di equalizzazione, per tenere conto di differenze di quadagno, offset e fase generate dalle precedenti operazioni di elaborazione del segnale, in parte di tipo analogico, ed evitare così distorsioni del segnale risultante di uscita.

Tale soluzione non è esente da problematiche, legate principalmente alla complessità della catena di elaborazione, ad una non trascurabile sensibilità a rumori e oscillazioni del segnale di ingresso, e ad una ridotta configurabilità.

In generale, è dunque sicuramente sentita l'esigenza di realizzare una soluzione perfezionata per estendere l'intervallo dinamico nel rilevamento di onde di pressione acustica tramite un trasduttore acustico.

Lo scopo della presente invenzione è quello di soddisfare, almeno in parte, tale esigenza.

Secondo la presente invenzione, vengono pertanto forniti un circuito elettronico digitale di interfaccia per

un trasduttore acustico, ed un relativo sistema di trasduzione acustico, come definiti nelle rivendicazioni allegate.

Per una migliore comprensione della presente invenzione, ne vengono ora descritte forme di realizzazione preferite, puramente a titolo di esempio non limitativo e con riferimento ai disegni allegati, nei quali:

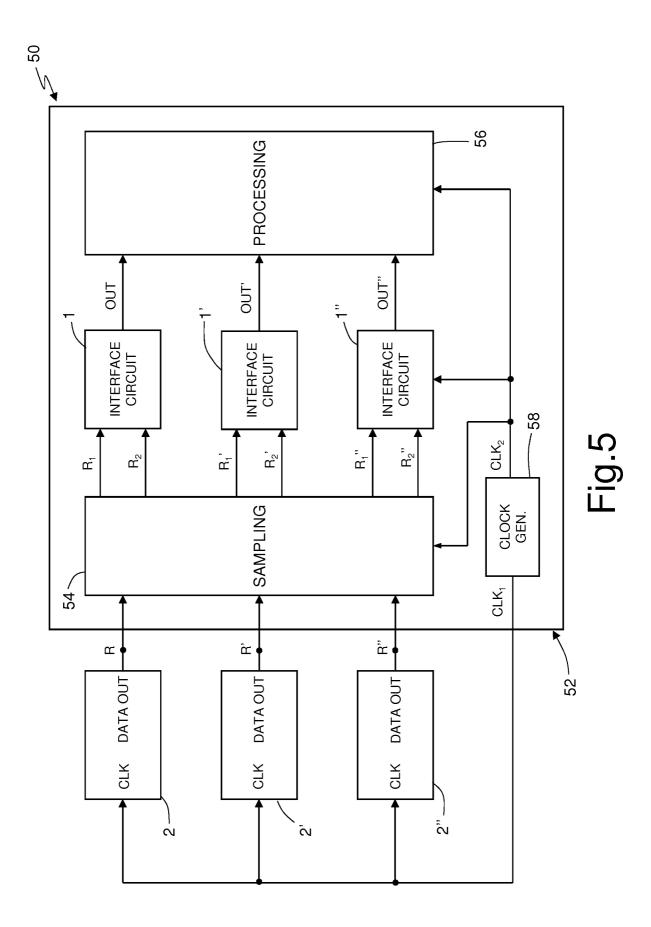

- la figura 1 è uno schema a blocchi di un circuito elettronico digitale di interfaccia, accoppiato ad un trasduttore acustico, secondo un aspetto della presente soluzione;

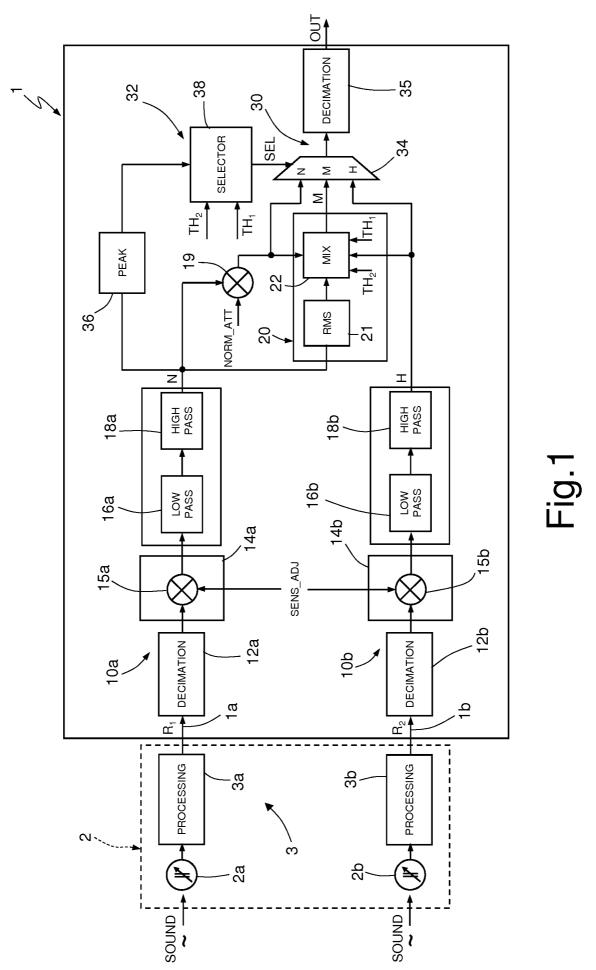

- la figura 2 mostra grafici relativi a grandezze acustiche associate al trasduttore acustico di figura 1;

- la figura 3 è uno schema a blocchi di un primo misuratore di livello nel circuito di interfaccia di figura 1;

- la figura 4 è uno schema a blocchi di un secondo misuratore di livello nel circuito di interfaccia di figura 1; e

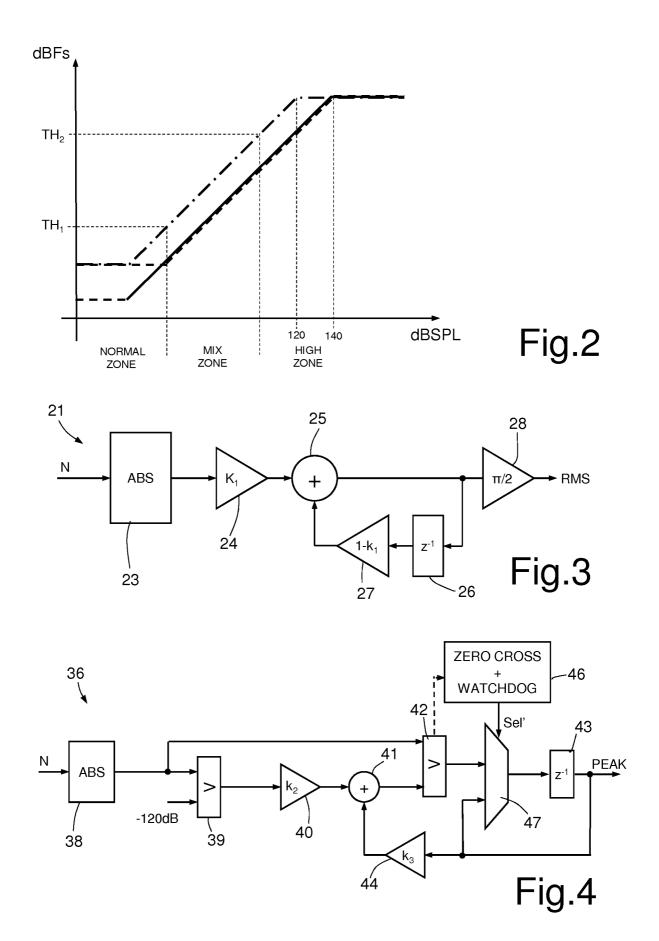

- la figura 5 è uno schema a blocchi di un sistema di trasduzione acustico, secondo un ulteriore aspetto della presente soluzione.

In figura 1 è indicato in generale con 1 un circuito elettronico digitale di interfaccia per un trasduttore acustico, indicato con 2.

Il trasduttore acustico 2, mostrato qui schematicamente, comprende una prima struttura sensibile micromeccanica 2a ed una seconda struttura sensibile micromeccanica 2b, distinta dalla prima, essendo ad esempio realizzata in una distinta piastrina (die) di materiale semiconduttore, o in una porzione distinta di una stessa piastrina di materiale semiconduttore.

Le strutture sensibili micromeccaniche 2a, 2b sono schematizzate in figura 1 mediante un rispettivo condensatore, con capacità variabile in funzione delle onde di pressione acustica incidenti.

Ciascuna struttura sensibile micromeccanica 2a, 2b può comprendere una rispettiva membrana, atta a deformarsi in funzione delle onde di pressione acustica incidenti; le strutture sensibili micromeccaniche 2a, 2b presentano differenti caratteristiche meccaniche, ad esempio in termini di una differente rigidità alle deformazioni, che determinano differenti caratteristiche elettriche nel rilevamento delle onde di pressione acustica.

In particolare, la prima struttura sensibile micromeccanica 2a è configurata per il rilevamento di segnali aventi un primo livello (massimo) di pressione acustica, ad esempio con AOP (Acoustic Overload Point) pari a 120 dBSPL; mentre la seconda struttura sensibile micromeccanica 2b è configurata per il rilevamento di

segnali aventi un secondo livello di pressione acustica, maggiore rispetto al primo livello, ad esempio con AOP (Acoustic Overload Point) pari a 140 dBSPL.

Il trasduttore acustico 2 può essere ad esempio realizzato come descritto nella domanda di brevetto WO2012093598.

In tal caso, la prima e la seconda struttura sensibile micromeccanica 2a, 2b sono realizzate mediante una stessa membrana mobile, che viene opportunamente separata in due porzioni elettricamente isolate, affacciate ad un rispettivo elettrodo fisso, in modo da formare due condensatori di rilevamento: una prima porzione periferica, atta a rilevare elevati livelli di pressione acustica con una ridotta sensibilità, ed una porzione centrale, che subisce maggiori deformazioni elastiche, atta a rilevare livelli di pressione acustica inferiori, ma con una maggiore sensibilità.

Il trasduttore acustico 2 comprende inoltre un circuito elettronico ASIC 3, avente un primo canale 3a, accoppiato alla prima struttura sensibile micromeccanica 2a, e fornente su una prima uscita, un primo segnale di rilevamento R<sub>1</sub>, di tipo digitale, in funzione dei segnali elettrici trasdotti dalla stessa prima struttura sensibile micromeccanica 2a; ed un secondo canale 3b, accoppiato alla seconda struttura sensibile micromeccanica 2b, e fornente

su una seconda uscita, un secondo segnale di rilevamento  $R_2$ , di tipo digitale, in funzione dei segnali elettrici trasdotti dalla stessa seconda struttura sensibile micromeccanica 2b.

A parità di segnale (ovvero, in presenza di uno stesso valore di SPL) il primo canale 3a presenta dunque un segnale elettrico di valore maggiore rispetto al secondo canale 3b.

Il primo ed il secondo segnale di rilevamento sono ad esempio segnali PDM, in modulazione a densità di impulsi, ed il primo ed il secondo canale 3a, 3b includono un rispettivo modulatore sigma-delta (di tipo per sé noto, qui non descritto in dettaglio).

In alternativa, come ad esempio descritto nella domanda di brevetto WO2012093598, il circuito elettronico ASIC 3 può avere un'unica uscita, su cui sono combinati in maniera opportuna (ad esempio con una tecnica di interlacciamento), i segnali di rilevamento; in tal caso, è richiesto uno stadio di ricostruzione dei segnali di rilevamento a partire dal flusso di dati interlacciato, per la loro successiva elaborazione.

Il circuito elettronico digitale di interfaccia 1 presenta un primo ed un secondo ingresso 1a, 1b, destinati a ricevere rispettivamente il primo ed il secondo segnale di rilevamento  $R_1$ ,  $R_2$ , direttamente dal trasduttore

acustico 2, o, in alternativa, dall'opportuno stadio di ricostruzione degli stessi segnali a partire dal flusso di dati presente sull'eventuale unica uscita dello stesso trasduttore acustico 2.

Secondo un aspetto della presente soluzione, il circuito elettronico digitale di interfaccia 1 esegue, come descritto in dettaglio in seguito, una operazione di ricombinazione del primo e del secondo segnale di rilevamento  $R_1$ ,  $R_2$ , per la generazione di un segnale risultante di uscita, al fine di ampliare l'intervallo dinamico e ottenere un compromesso ottimizzato con il rapporto tra segnale e rumore.

In generale, tale operazione di ricombinazione, illustrata schematicamente in figura 2, si basa su misure di livello del primo segnale di rilevamento  $R_1$  e sul confronto dei livelli misurati con una soglia inferiore e con una soglia superiore, indicate con  $TH_1$  e  $Th_2$  nella stessa figura 2:

in cui il livello del nel caso segnale di rilevamento sia superiore alla soglia superiore  $Th_2$ , segnale risultante di uscita (la cui curva caratteristica è in linea continua) fornito mostrata è а partire dall'elaborazione del secondo segnale di rilevamento R2 in uscita dal secondo canale 3b (la cui caratteristica è mostrata in linea tratteggiata);

livello in cui il del nel caso segnale di rilevamento sia minore della soglia inferiore Th<sub>1</sub>, il di uscita è fornito segnale risultante а partire dall'elaborazione del primo segnale di rilevamento  $R_1$  in uscita dal primo canale 3a (la cui caratteristica mostrata in linea a tratto-punto); e

- nel caso in cui il livello del segnale di rilevamento sia compreso tra la soglia inferiore  $Th_1$  e la soglia superiore  $Th_2$ , il segnale risultante di uscita è fornito a partire da una combinazione opportuna del primo e del secondo segnale di rilevamento  $R_1$ ,  $R_2$ .

In dettaglio, e tornando alla figura 1, il circuito di interfaccia 1 comprende un primo ramo di elaborazione 10a, collegato al primo ingresso 1a e destinato all'elaborazione digitale del primo segnale di rilevamento  $R_1$ , ed un secondo ramo di elaborazione 10b, collegato al secondo ingresso 1b e destinato all'elaborazione digitale del secondo segnale di rilevamento  $R_2$ .

Ciascun ramo di elaborazione 10a, 10b comprende: un rispettivo primo blocco di decimazione 12a, 12b, che riceve in ingresso il primo o, rispettivamente, secondo segnale di rilevamento  $R_1$ ,  $R_2$  ed esegue un'operazione di decimazione sui campioni dello stesso segnale (il processo di decimazione comprendendo anche un filtraggio FIR passa basso), ed un rispettivo blocco di regolazione 14a, 14b,

includente un rispettivo primo moltiplicatore 15a, 15b, per la moltiplicazione del segnale all'uscita del primo stadio di decimazione 12a, 12b per un fattore di regolazione Sens\_Adj, di valore configurabile e tale da compensare eventuali differenze tra un valore teorico ed un valore effettivo della sensibilità di rilevamento delle strutture sensibili micromeccaniche 2a, 2b del trasduttore acustico 2.

Ciascun ramo di elaborazione 10a, 10b comprende inoltre, collegati in cascata all'uscita del rispettivo blocco di regolazione 14a, 14b: un blocco di filtro passa basso 16a, 16b; ed un blocco di filtro passa alto 18a, 18b.

In particolare, il blocco di filtro passa basso 16a, 16b implementa un filtro digitale, ad esempio di tipo IIR del secondo ordine con frequenza di taglio di 20 kHz, per eliminare eventuale rumore presente al di fuori della banda audio nel primo o nel secondo segnale di rilevamento  $R_1$ ,  $R_2$ .

Il blocco di filtro passa alto 18a, 18b implementa anch'esso un filtro digitale di tipo IIR, al fine di eliminare eventuale offset in continua (cosiddetto "DC offset") e rumore ambientale, ad esempio disturbi dovuti al vento, cosiddetto "wind noise".

Il primo ramo di elaborazione 10a comprende inoltre un secondo moltiplicatore 19, che riceve il segnale filtrato

all'uscita del blocco di filtro passa alto 18a, indicato con N (corrispondente all'elaborazione del primo segnale di rilevamento  $R_1$ , per questo definito nel seguito come primo segnale di rilevamento filtrato) e lo moltiplica per un fattore di attenuazione Norm\_Att, di valore configurabile e tale da compensare le differenze di sensibilità e guadagno tra la prima e la seconda struttura sensibile micromeccanica 2a, 2b e tra il primo ed il secondo canale 3a, 3b del circuito ASIC 3 del trasduttore acustico 2.

Il circuito di interfaccia 1 comprende inoltre uno stadio di ricombinazione 20, includente un primo blocco di misurazione di livello 21 ed un blocco di miscelazione 22 (mixing).

Il primo blocco di misurazione di livello 21 presenta un ingresso collegato all'uscita del blocco di filtro passa alto 18a del primo ramo di elaborazione 10a, ed è configurato, come illustrato in figura 3, in modo da misurare il valore efficace (RMS - Root Mean Square) del primo segnale di rilevamento filtrato N.

In dettaglio, il primo blocco di misurazione di livello 21 comprende: un'unità di calcolo del valore assoluto 23, che riceve in ingresso il primo segnale di rilevamento filtrato N e ne calcola il valore assoluto; una prima unità di moltiplicazione 24, con fattore moltiplicativo  $K_1$  e collegata all'uscita dell'unità di

calcolo del valore assoluto 23; un'unità sommatore 25, avente un primo ingresso di somma, collegato all'uscita della prima unità di moltiplicazione 24, un secondo ingresso di somma, ed un'uscita; un percorso di retroazione collegato tra l'uscita ed il secondo ingresso dell'unità di somma 25, ed includente un'unità di ritardo unitario 26 e, in cascata, una seconda unità di moltiplicazione 27, con fattore moltiplicativo (1- $K_1$ ); ed una terza unità di moltiplicazione 28, con fattore moltiplicativo pari a  $\pi/2$ , avente ingresso collegato all'uscita dell'unità di somma 25 ed uscita fornente il valore efficace RMS.

Tornando alla figura 1, il blocco di miscelazione 22 dello stadio di ricombinazione 20 presenta: un primo ingresso ricevente il valore efficace RMS dal primo blocco di misurazione di livello 21; un secondo ingresso collegato all'uscita del secondo moltiplicatore 19 e ricevente dunque il primo segnale di rilevamento filtrato N, attenuato del Norm Att; un attenuazione fattore di terzo ingresso collegato all'uscita del blocco di filtro passa alto 18b del secondo ramo di elaborazione 10b e ricevente dunque il secondo segnale di rilevamento filtrato (indicato con H); ed un quarto ed un quinto ingresso riceventi rispettivamente la soglia inferiore  $\mathrm{Th}_1$ la superiore Th2, aventi valori configurabili.

Il blocco di miscelazione 22 è configurato in modo da

fornire in uscita un segnale di miscelazione, indicato con M, che è dato dalla seguente espressione:

$$M = H \left[ 1 - \frac{Th_2 - RMS}{Th_2 - Th_1} \right] + N \left[ \frac{Th_2 - RMS}{Th_2 - Th_1} \right]$$

In sostanza, il segnale di miscelazione M è ottenuto mediante la combinazione pesata del primo e del secondo segnale di rilevamento filtrati N, H (il primo segnale di rilevamento filtrato N essendo anche opportunamente attenuato), con un peso che è funzione della distanza del livello del segnale acustico rilevato dalla soglia, in particolare la soglia superiore Th2, impostata.

In maniera evidente, nel caso limite in cui il livello del segnale acustico rilevato, in particolare il valore efficace RMS del primo segnale di rilevamento filtrato N, è pari alla soglia superiore  $Th_2$ , il segnale di miscelazione corrisponde al secondo segnale di rilevamento filtrato H; mentre nel caso limite in cui il livello del segnale acustico rilevato è pari alla soglia inferiore  $Th_1$ , il segnale di miscelazione corrisponde al primo segnale di rilevamento filtrato N.

Il circuito di interfaccia 1 comprende inoltre uno stadio di uscita 30 ed uno stadio di selezione 32.

Lo stadio di uscita 30 comprende a sua volta un'unità multiplexer 34, avente: un primo ingresso collegato all'uscita del secondo moltiplicatore 19 e ricevente dunque

il primo segnale di rilevamento filtrato N, attenuato del fattore di attenuazione Norm Att; un secondo ingresso collegato all'uscita del blocco di filtro passa alto 18b del secondo ramo di elaborazione 10b e ricevente dunque il segnale di rilevamento filtrato H; secondo un all'uscita dello stadio di ingresso collegato ricombinazione 20 e ricevente il segnale di miscelazione M; ed un'uscita, che viene selettivamente collegata alternativamente al primo, secondo o terzo ingresso, in funzione di un segnale di selezione Sel, che viene ricevuto dallo stadio di selezione 32, come meglio definito in seguito.

Lo stadio di uscita 30 comprende inoltre un secondo blocco di decimazione 35, che presenta ingresso collegato all'uscita dell'unità multiplexer 34 e uscita su cui fornisce, dopo opportuna operazione di decimazione sui campioni del segnale ricevuto in ingresso (nuovamente includente anche un filtraggio FIR passa basso), il segnale di uscita Out dal circuito di interfaccia 1, rendendolo disponibile ad un sistema elettronico esterno.

Lo stadio di selezione 32 comprende un secondo blocco di misurazione di livello 36, ed un blocco selettore 38.

Il secondo blocco di misurazione di livello 36 presenta un ingresso collegato all'uscita del blocco di filtro passa alto 18a del primo ramo di elaborazione 10a,

ed è configurato, come illustrato in figura 4, in modo da misurare il valore di picco (peak level) del primo segnale di rilevamento filtrato N.

In dettaglio, il secondo blocco di misurazione di livello 36 comprende: una rispettiva unità di calcolo del valore assoluto 38, che riceve in ingresso il primo segnale di rilevamento filtrato N e ne calcola il valore assoluto; una prima unità comparatore 39, che confronta il valore assoluto precedentemente calcolato con valore un riferimento di rumore, ad esempio pari a -120 indicativo di una soglia di rumore, al fine di filtrare il contributo di rumore eventualmente presente (operando dunque come una sorta di "noise gate"); una rispettiva prima unità moltiplicazione 40, con di fattore collegata all'uscita dell'unità moltiplicativo  $K_2$ е comparatore 39; ed una rispettiva unità sommatore 41, avente un primo ingresso di somma, collegato all'uscita della prima unità di moltiplicazione 40, un ingresso di somma, ed un'uscita.

Il secondo blocco di misurazione di livello 36 comprende inoltre: una seconda unità comparatore 42, che riceve in ingresso i campioni del valore assoluto del primo segnale di rilevamento filtrato N ed i campioni del segnale di uscita dall'unità sommatore 41, e ne determina di volta in volta il maggiore; ed un percorso di retroazione

collegato tra l'uscita della seconda unità comparatore 42 ed il secondo ingresso dell'unità sommatore 41, ed includente una rispettiva unità di ritardo unitario 43 e, in cascata, una rispettiva seconda unità di moltiplicazione 44, con fattore moltiplicativo  $K_3$ .

In maniera di per sé evidente, l'unità sommatore 41, la seconda unità comparatore 42 ed il percorso di retroazione implementano uno stadio di decadimento, e consentono di inseguire i picchi del segnale di ingresso e di mantenerli con un certo fattore di decadimento, determinato, tra l'altro, dai valori dei fattori moltiplicativi  $K_2$  e  $K_3$  (ad esempio, tale fattore di decadimento è pari a 3,7 db/ms).

Il secondo blocco di misurazione di livello 36 comprende inoltre un'unità di controllo 46 ed un'unità multiplexer 47.

L'unità multiplexer 47 presenta un primo ingresso collegato all'uscita della seconda unità comparatore 42 ed un secondo ingresso collegato all'ingresso della seconda unità di moltiplicazione 44, ed un'uscita collegata all'uscita del secondo blocco di misurazione di livello 36, e fornente dunque il segnale di picco Peak, in funzione di un segnale di controllo Sel'.

L'unità di controllo 46 ha funzioni di "zero crossing" e "watch dog", ed è configurata in modo da monitorare,

campione dopo campione dei segnali digitali, il risultato del confronto eseguito dalla seconda unità comparatore 42, ed in modo da generare il segnale di controllo Sel' per l'unità multiplexer 47.

In particolare, l'unità di controllo 42 analizza gli attraversamenti dello zero, cosiddetti "zero crossing", del segnale risultato del confronto eseguito nella seconda unità comparatore 42 ed abilita la fase di decadimento del di picco Peak (chiudendo il segnale percorso retroazione, ovvero collegando l'uscita del multiplexer 47 all'uscita della seconda unità comparatore 42) determina un attraversamento dello zero, a meno che non sia ancora stato raggiunto un certo numero prefissato campioni dei segnali (la funzione di "watchdog" essendo appunto quella di contare i campioni e sbloccare percorso di retroazione, solo se un limite massimo è stato raggiunto). In tal modo, risulta ad esempio possibile filtrare oscillazioni anomale dei segnali elaborati, almeno all'interno di un certo numero predeterminato di campioni.

Tornando ora al circuito elettronico digitale di interfaccia di figura 1, il blocco selettore 38 riceve in ingresso il segnale di picco Peak ed i valori configurabili della soglia inferiore  $Th_1$  e della soglia superiore  $Th_2$ , ed in funzione di tali valori genera il segnale di selezione Sel per determinare il segnale da inviare all'uscita

dell'unità multiplexer 34, secondo l'algoritmo di ricombinazione discusso in precedenza.

In particolare, nel caso in cui il valore del segnale di picco Peak sia compreso tra la soglia inferiore Th<sub>1</sub> e la soglia superiore Th<sub>2</sub>, il segnale di selezione Sel seleziona il segnale di miscelazione M per l'uscita dell'unità multiplexer 34; nel caso in cui il segnale di picco Peak sia minore della soglia inferiore Th<sub>1</sub>, il segnale di selezione Sel seleziona il primo segnale di rilevamento filtrato N (opportunamente attenuato) per l'uscita dell'unità multiplexer 34; mentre nel caso in cui il segnale di picco Peak sia maggiore della soglia superiore Th<sub>2</sub>, il segnale di selezione Sel seleziona il secondo segnale di rilevamento filtrato H per l'uscita della stessa unità multiplexer 34.

In figura 5 viene ora mostrato un esempio di applicazione di quanto precedentemente descritto, riferito ad un sistema microfonico, indicato in generale con 50, comprendente tre trasduttori acustici, indicati con 2, 2' e 2", ciascuno dotato di una coppia di strutture sensibili micromeccaniche (qui non illustrate) e ciascuno avente una sola uscita digitale (qui indicata come DataOut), su cui vengono forniti in maniera interlacciata i segnali di rilevamento associati alle stesse strutture sensibili micromeccaniche, qui indicati con R, R' e R".

sistema microfonico 50 comprende un circuito a microprocessore 52, che realizza: uno stadio campionamento 54, ricevente i segnali digitali R, R' e R" forniti dai trasduttori acustici 2, 2' e 2" e generante, per ciascuno di essi, i due distinti segnali di rilevamento  $R_1', R_2'; R_1'', R_2''$  (con operazioni note di  $R_1$ ,  $R_2$ ; interlacciamento); un circuito di interfaccia 1, 1' e 1", per ciascuno dei trasduttori acustici 2, 2' e 2", ricevente la rispettiva coppia di segnali di rilevamento e fornente in uscita un rispettivo segnale di uscita Out, Out' e Out", come descritto in dettaglio in precedenza; ed uno stadio di elaborazione digitale 56, che riceve i segnali di uscita Out, Out' e Out", riferiti a ciascuno dei trasduttori acustici 2, 2' e 2", ed esegue opportune elaborazioni degli stessi segnali (ad esempio per implementare algoritmi di cancellazione del rumore).

Il circuito a microprocessore 52 può inoltre generare internamente, mediante un generatore di clock 58, un primo segnale di orologio  $CLK_1$ , che viene fornito ai trasduttori acustici 2, 2' e 2", su un rispettivo ingresso di clock CLK, in modo tale da temporizzare le operazioni di rilevamento dei segnali di pressione acustica; ed un secondo segnale di orologio  $CLK_2$ , avente una prefissata relazione con il primo segnale di orologio  $CLK_1$  (ad esempio essendo sfasato di un angolo opportuno rispetto ad esso),

che viene utilizzato internamente allo stesso circuito a microprocessore 52, per le operazioni di campionamento e di elaborazione dei segnali di rilevamento acquisiti.

In particolare, le operazioni di ricombinazione e di elaborazione sono effettuate ad una frequenza di campionamento maggiore, ad esempio 16 volte maggiore, rispetto ad una frequenza base, in tal modo riducendo la latenza delle stesse operazioni di elaborazione.

Da quanto è stato descritto ed illustrato precedentemente, i vantaggi che la presente soluzione consente di ottenere sono evidenti.

particolare, la presenza nel circuito interfaccia 1 dei due distinti rami di elaborazione 10a, 10b, ciascuno accoppiato operativamente ad una distinta struttura sensibile micromeccanica di rilevamento ricevente il relativo segnale digitale di rilevamento, consente di migliorare le prestazioni elettriche, termini dell'intervallo dinamico, della sensibilità e del rapporto segnale/rumore, rispetto ad esempio a soluzioni la generazione di due che prevedano percorsi elaborazione a partire da un unico segnale di rilevamento, di tipo analogico.

L'utilizzo, nel circuito di interfaccia 1 di due distinti misuratori di livello (di picco e di valore efficace) consente di ottenere specifici vantaggi

nell'elaborazione dei segnali: in particolare, il misuratore del livello di picco consente di ottenere una risposta rapida ai cambiamenti del segnale ed al contempo una buona stabilità di misura rispetto alle fluttuazioni alla caratteristica del segnale stesso, grazie decadimento selettivamente implementata, in tal assicurando tempestive commutazioni nella selezione del segnale di uscita, evitando errori e possibili saturazioni; il misuratore del livello RMS consente di ottenere una misura stabile rispetto alle fluttuazioni ed ai disturbi (ad esempio i cosiddetti "glitch"), garantendo una corretta miscelazione dei segnali di rilevamento. Il segnale in uscita risulta privo di modulazioni di ampiezza percepibili dall'orecchio (una volta che queste vengono riprodotte acusticamente).

La realizzazione stessa del misuratore di livello di picco presenta specifici vantaggi, nell'utilizzo di una funzionalità "noise gate" per il filtraggio del rumore, di un filtro di decadimento, per migliorare la misurazione del segnale per le basse frequenze, e di una funzione di "watch dog" con "zero crossing", per ridurre le fluttuazioni e migliorare la misurazione del segnale per le alte frequenze.

La presenza dello stadio di filtraggio passa-basso 16a, 16b in ciascun ramo di elaborazione 10a, 10b consente

di evitare errate stime del livello di segnale (solitamente stime più alte del valore effettivo), o comunque stime non correlate a tale valore effettivo, e di evitare saturazioni nelle operazioni di ricombinazione.

Il circuito di interfaccia 1 risulta inoltre ampiamente configurabile, ad esempio per quanto riguarda la scelta dei valori di soglia inferiore e superiore  $Th_1$ ,  $Th_2$ , la regolazione di sensibilità dei rami di elaborazione mediante il fattore di regolazione Sens Adj regolazione del fattore di attenuazione Norm Att, in tal modo consentendo un facile adattamento a caratteristiche di vari tipi di microfoni (come mostrato ad esempio in figura 5, in cui vengono infatti utilizzati vantaggiosamente tre trasduttori acustici 2, 2', 2", con caratteristiche di sensibilità anche molto differenti tra loro).

In conclusione, è chiaro che modifiche e varianti possono essere apportate a quanto è stato descritto ed illustrato sin qui, senza tuttavia scostarsi dall'ambito di tutela della presente invenzione come definito nelle rivendicazioni allegate.

In particolare, è evidente che il circuito di interfaccia 1 precedentemente descritto può vantaggiosamente essere integrato nello stesso chip (o nella stessa piastrina) in cui è realizzato il circuito elettronico ASIC 3 del trasduttore acustico 2, che in tal

caso può fornire in uscita un segnale già opportunamente ricombinato ed ottimizzato rispetto all'intervallo dinamico, in funzione dei segnali di rilevamento associati ad entrambe le strutture sensibili micromeccaniche di cui lo stesso trasduttore acustico 2 è internamente dotato.

## RIVENDICAZIONI

1. Circuito di interfaccia digitale (1), per un trasduttore acustico (2) dotato di una prima (2a) e di una seconda (2b) struttura di rilevamento, detto circuito di interfaccia digitale (1) avendo un primo (1a) ed un secondo (1b) ingresso e comprendendo:

un primo (10a) ed un secondo (10b) percorso di elaborazione digitale accoppiati rispettivamente al primo (1a) ed al secondo (1b) ingresso e fornenti un primo (N) ed un secondo (H) segnale digitale elaborato; ed

uno stadio di ricombinazione (20) configurato in modo da fornire un segnale miscelato (M), tramite la combinazione di detti primo (N) e secondo (H) segnale elaborato con un rispettivo peso che è funzione di un primo valore di livello (RMS) di detto primo segnale elaborato (N),

caratterizzato dal fatto che detti primo (1a) ingresso destinati a secondo (1b)sono ricevere rispettivamente un primo (R1) ed un secondo (R2) segnale di rilevamento, associati rispettivamente alla prima (2a) ed alla seconda (3b) struttura di rilevamento di detto trasduttore acustico (2); e dal fatto di comprendere uno stadio di uscita (30, 32) configurato in modo da fornire selettivamente in uscita alternativamente detto primo segnale digitale elaborato (N), detto secondo segnale digitale elaborato (H) o detto segnale miscelato (M).

- 2. Circuito secondo la rivendicazione 1, in cui detto stadio di uscita (30, 32) comprende uno stadio selettore (38), configurato in modo da selezionare in uscita alternativamente detto primo segnale digitale elaborato (N), detto secondo segnale digitale elaborato (H) o detto segnale miscelato (M), sulla base di un secondo valore di livello (Peak) di detto primo segnale elaborato (N), differente da detto primo valore di livello (RMS).

- 3. Circuito secondo la rivendicazione 2, in cui detto stadio di ricombinazione (20) comprende un primo misuratore di livello (21) configurato in modo da misurare detto primo valore di livello (RMS), come valore efficace, RMS Root Mean Square, di detto primo segnale elaborato (N); ed in cui detto stadio di uscita (30, 32) comprende un secondo misuratore di livello (36) configurato in modo da misurare detto secondo valore di livello (Peak), come valore di picco di detto primo segnale elaborato (N).

- 4. Circuito secondo la rivendicazione 3, in cui detto secondo misuratore di livello (36) comprende: uno stadio di decadimento (41-44) per generare una versione di detto valore di picco (Peak) decrementata di un fattore desiderato, per il confronto con un campione attuale di detto primo segnale elaborato (N); ed un blocco di filtraggio di rumore (39), configurato in modo da ricevere

campioni di detto primo segnale elaborato (N) e da renderli disponibili per il confronto nel caso in cui soddisfino una determinata relazione con una prefissata soglia di rumore.

- 5. Circuito secondo la rivendicazione 4, in cui detto secondo misuratore di livello (36) comprende inoltre un blocco di controllo (46), configurato in modo da abilitare selettivamente detto stadio di decadimento (41-44).

- 6. Circuito secondo la rivendicazione 5, in cui detto secondo misuratore di livello (36) comprende: un'unità comparatore (42) configurata in modo da confrontare detto campione attuale di detto primo segnale elaborato (N) con detto valore di picco (Peak) decrementato, generando, campione dopo campione, un segnale di confronto; ed in cui detto blocco di controllo (46) è configurato in modo da abilitare det.t.o stadio decadimento (41-44), di al rilevamento di un attraversamento dello zero del segnale di confronto e dopo aver atteso un prefissato numero di campioni.

- 7. Circuito secondo la rivendicazione 5 o 6, in cui detto blocco di filtraggio di rumore (39) implementa una funzionalità di "noise gate", e detto blocco di controllo (42) implementa una funzionalità di "watch dog" con "zero crossing".

- 8. Circuito secondo una qualsiasi delle rivendicazioni 2-7, in cui detto stadio selettore (32) è configurato in

modo da ricevere detto secondo valore di livello (Peak), un valore di soglia inferiore ( $Th_1$ ) ed un valore di soglia superiore ( $Th_2$ ), ed in modo da generare un segnale di selezione (Sel) in funzione del confronto tra detto secondo valore di livello (Peak) e detti valore di soglia inferiore ( $Th_1$ ) e superiore ( $Th_2$ ); ed in cui detto stadio di uscita comprende uno stadio multiplatore (34), configurato in modo da ricevere detto segnale di selezione (Sel) e fornire in uscita alternativamente detto primo segnale digitale elaborato ( $Th_1$ ), detto secondo segnale digitale elaborato ( $Th_1$ ) o detto segnale miscelato ( $Th_1$ ), sulla base di detto segnale di selezione (Sel).

- 9. Circuito secondo una qualsiasi delle rivendicazioni precedenti, in cui detto stadio di ricombinazione (20) è configurato in modo da ricevere detto primo valore di livello (RMS), un valore di soglia inferiore ( $Th_1$ ) ed un valore di soglia superiore ( $Th_2$ ), ed in modo da generare detto segnale miscelato ( $Th_1$ ) in funzione di detti primo ( $Th_1$ ) e secondo ( $Th_1$ ) segnale elaborato, associando a detti primo ( $Th_1$ ) e secondo ( $Th_1$ ) segnale elaborato un rispettivo peso che è funzione di detto primo valore di livello ( $Th_1$ ), di detto valore di soglia inferiore ( $Th_1$ ) e di detto valore di soglia superiore ( $Th_2$ ).

- 10. Circuito secondo la rivendicazione 8 o 9, in cui detto valore di soglia inferiore  $(Th_1)$  e detto valore di

soglia superiore (Th2) sono configurabili.

- 11. Circuito secondo una qualsiasi delle rivendicazioni precedenti, in cui detti primo (10a) e (10b) percorso di elaborazione digitale destinati a ricevere detti segnali di rilevamento (R1, R2) associati a dette prima (2a) e seconda (3b) struttura di rilevamento di detto trasduttore acustico (2), aventi differenti sensibilità nel rilevamento di onde di pressione acustica; ed in cui a detto primo segnale di rilevamento  $(R_1)$  è associata una maggiore sensibilità nel rilevamento di dette onde di pressione acustica.

- 12. Circuito la secondo rivendicazione 11. stadio comprendente inoltre uno di regolazione sensibilità (14a, 14b), configurato in modo da apportare un fattore correttivo (Sens adj), di valore configurabile, al valore di detti segnali di rilevamento  $(R_1, R_2)$  per tenere conto di una variazione del valore di dette sensibilità rispetto ad un valore teorico.

- 13. Circuito secondo una qualsiasi delle rivendicazioni precedenti, in cui ciascuno di detti primo (10a) e secondo (10b) percorso di elaborazione comprende in cascata un filtro passa basso (16a, 16b) ed un filtro passa alto (18a, 18b), per rimuovere contributi di rumore al di fuori di una prefissata banda di frequenze.

- 14. Circuito secondo una qualsiasi delle

rivendicazioni precedenti, in cui detti segnali di rilevamento  $(R_1,\ R_2)$  sono segnali digitali in modulazione PDM.

- 15. Sistema di trasduzione acustico, comprendente: una prima (2a) ed una seconda (2b) struttura di rilevamento, tra loro separate e distinte ed aventi differenti caratteristiche di rilevamento di onde di pressione acustica; ed un circuito di interfaccia digitale (1), secondo una qualsiasi delle rivendicazioni precedenti, accoppiato a dette prima (2a) e seconda (2b) struttura di rilevamento.

- 16. Sistema secondo la rivendicazione 15, comprendente inoltre un circuito ASIC (3), collegato elettricamente a dette prima (2a) e seconda (2b) struttura di rilevamento; in cui detto circuito di interfaccia digitale (1) e detto circuito ASIC (3) sono integrati in uno stesso chip.

- 17. Sistema secondo la rivendicazione 15, comprendente inoltre un circuito ASIC (3), collegato elettricamente a dette prima (2a) e seconda (2b) struttura di rilevamento, e configurato in modo da ricevere ed elaborare rispettivi segnali elettrici e generare un segnale di rilevamento interlacciato (R) includente informazioni associate ad entrambi i segnali elettrici; comprendente uno stadio di campionamento (54) configurato in modo da ricevere detto segnale di rilevamento interlacciato (R) e generare detto

primo  $(R_1)$  e secondo  $(R_2)$  segnale di rilevamento per detto circuito di interfaccia digitale (1), ciascuno associato ad una rispettiva di dette prima (2a) e seconda (2b) struttura di rilevamento.

p.i.: STMICROELECTRONICS S.R.L.

Lorenzo NANNUCCI

## CLAIMS

1. A digital interface circuit (1), for an acoustic transducer (2) provided with a first detection structure (2a) and a second detection structure (2b), said digital interface circuit (1) having a first input (1a) and a second input (1b) and comprising:

5

10

15

20

25

- a first digital processing path (10a) and a second digital processing path (10b), which are coupled, respectively, to the first input (1a) and the second input (1b) and supply a first digital processed signal (N) and a second digital processed signal (H); and

- a recombination stage (20) configured to supply a mixed signal (M), via combination of said first processed signal (N) and second processed signal (H) with a respective weight that is a function of a first level value (RMS) of said first processed signal (N),

- characterized in that said first and second inputs (1a, 1b) are designed to receive, respectively, a first detection signal  $(R_1)$  and a second detection signal  $(R_2)$ , associated, respectively, to the first detection structure (2a) and to the second detection structure (3b) of said acoustic transducer (2); and in that it comprises an output stage (30, 32) configured to selectively supply at output alternatively said first digital processed signal (N), said second digital processed signal (H), or said mixed signal (M).

- 2. The circuit according to claim 1, wherein said output stage (30, 32) comprises a selector stage (38), configured to select at output alternatively said first digital processed signal (N), said second digital processed signal (H), or said mixed signal (M), on the basis of a second level value (Peak) of said first processed signal (N) different from said first level value (RMS).

3. The circuit according to claim 2, wherein said recombination stage (20) comprises a first level meter (21) configured to measure said first level value (RMS), as root-mean-square value of said first processed signal (N); and wherein said output stage (30, 32) comprises a second level meter (36) configured to measure said second level value (Peak) as peak value of said first processed signal (N).

5

- 4. The circuit according to claim 3, wherein said second level meter (36) comprises: a decay stage (41-44) for generating a version of said peak level (Peak) decremented by a desired factor, for the comparison with a current sample of said first processed signal (N); and a noise-filtering block (39), configured to receive samples of said first processed signal (N) and make them available for the comparison in the case where they satisfy a given relation with a pre-set noise threshold.

- 5. The circuit according to claim 4, wherein said second level meter (36) further comprises a control block (46), configured to selectively enable said decay stage (41-44).

- 6. The circuit according to claim 5, wherein said second level meter (36) comprises: a comparator unit (42) configured to compare said current sample of said first processed signal (N) with the decremented peak level (Peak), generating, sample after sample, a comparison signal; and wherein said control block (46) is configured to enable said decay stage (41-44), upon detection of a zero-crossing of the comparison signal and after waiting a pre-set number of samples.

- 7. The circuit according to claim 5 or 6, wherein said noise-filtering block (39) implements a noise-gate function, and

said control block (42) implements a watchdog function with zero crossing.

- 8. The circuit according to any one of claims 2-7, wherein said selector stage (32) is configured to receive said second level value (Peak), a lower threshold value (Th<sub>1</sub>) and an upper threshold value (Th<sub>2</sub>), and to generate a selection signal (Sel) as a function of the comparison between said second level value (Peak) and said lower (Th<sub>1</sub>) and upper (Th<sub>2</sub>) threshold values; and wherein said output stage comprises a multiplexer stage (34), configured to receive said selection signal (Sel) and supply at output alternatively said first processed digital signal (N), said second processed digital signal (H), or said mixed signal (M), on the basis of said selection signal (Sel).

- 9. The circuit according to any one of the preceding claims, wherein said recombination stage (20) is configured to receive said first level value (RMS), a lower threshold value ( $Th_1$ ), and an upper threshold value ( $Th_2$ ), and to generate said mixed signal (M) as a function of said first processed signal (N) and second processed signal (H), associating to said first processed signal (N) and second processed signal (H) a respective weight that is a function of said first level value (RMS), of said lower threshold value ( $Th_1$ ), and of said upper threshold value ( $Th_2$ ).

- 10. The circuit according to claim 8 or 9, wherein said lower threshold value ( $Th_1$ ) and said upper threshold value ( $Th_2$ ) are 30 configurable.

- 11. The circuit according to any one of the preceding claims, wherein said first digital processing path (10a) and second digital processing path (10b) are designed to receive said

detection signals  $(R_1, R_2)$  associated to said first detection structure (2a) and second detection structure (3b) of said acoustic transducer (2), which have different sensitivities in the detection of acoustic-pressure waves; and wherein associated to said first detection signal  $(R_1)$  is a higher sensitivity in the detection of said acoustic-pressure waves.

5

10

25

30

- 12. The circuit according to claim 11, further comprising a sensitivity-adjustment stage (14a, 14b), configured to apply a corrective factor (Sens\_adj), of configurable value, to the value of said detection signals ( $R_1$ ,  $R_2$ ) to take into account a variation of the value of said sensitivities with respect to a theoretical value.

- 13. The circuit according to any one of the preceding claims, wherein each of said first processing path (10a) and second processing path (10b) comprises, cascaded to one another, a low-pass filter (16a, 16b) and a high-pass filter (18a, 18b), for removing contributions of noise outside a pre-set frequency band.

- 14. The circuit according to any one of the preceding claims, wherein said detection signals  $(R_1,\ R_2)$  are PDM digital signals.

- 15. An acoustic transducer system, comprising: a first detection structure (2a) and a second detection structure (2b), which are separate and distinct from one another and have different characteristics of detection of acoustic-pressure waves; and a digital interface circuit (1), according to any one of the preceding claims, coupled to said first detection structure (2a) and second detection structure (2b).

- 16. The system according to claim 15, further comprising an

ASIC circuit (3), electrically connected to said first detection structure (2a) and said second detection structure (2b); wherein said digital interface circuit (1) and said ASIC circuit (3) are integrated in one and the same chip.

5

10

15

17. The system according to claim 15, further comprising an ASIC circuit (3), electrically connected to said first detection structure (2a) and said second detection structure (2b) and configured to receive and process respective electrical signals and generate an interlaced detection signal (R) including information associated to both of the electrical signals; said system comprising a sampling stage (54) configured to receive said interlaced detection signal (R) and generate said first detection signal (R<sub>1</sub>) and said second detection signal (R<sub>2</sub>) for said digital interface circuit (1), each associated to a respective one of said first detection structure (2a) and said second detection structure (2b).

Lorenzo NANNUCCI (Iscrizione Albo nr. 1214/B)

Lorenzo NANNUCCI (Iscrizione Albo nr. 1214/B)