# (10) **DE 10 2005 058 214 A1** 2006.06.14

(12)

# Offenlegungsschrift

(21) Aktenzeichen: 10 2005 058 214.1

(22) Anmeldetag: **06.12.2005** (43) Offenlegungstag: **14.06.2006**

(51) Int Cl.8: *G11C 5/06* (2006.01)

**G11C 5/02** (2006.01)

(30) Unionspriorität:

11/010,942 10.12.2004 US

(74) Vertreter:

PAe Reinhard, Skuhra, Weise & Partner GbR, 80801 München

(71) Anmelder:

Infineon Technologies AG, 81669 München, DE

(72) Erfinder:

Raghuram, Siva, 82110 Germering, DE

Prüfungsantrag gemäß § 44 PatG ist gestellt.

#### Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

- (54) Bezeichnung: Stapel-DRAM-Speicherchip für ein Doppelreihen-Speichermodul (DIMM)

- (57) Zusammenfassung: Die Erfindung bezieht sich auf einen DRAM-Speicherchip für ein Doppelreihen-Speichermodul (DIMM), welches besitzt:

- (a) eine vorher festgelegte Anzahl (M) von gestapelten DRAM-Speicherchips;

- (b) wobei jeder DRAM-Speicherchip durch ein entsprechendes Speicherrangsignal (r) auswählbar ist;

- (c) wobei jeder DRAM-Speicherchip ein Feld von Speicherzellen aufweist;

- (d) wobei ein gewöhnlicher interner Adressbus, welcher aus Adressleitungen besteht, zum Adressieren der Speicherzellen vorgesehen ist und mit allen M gestapelten DRAM-Speicherchips verbunden ist;

- (e) wobei M interne Datenbusse, welche aus internen Datenleitungen bestehen, vorgesehen sind, um Daten in die Speicherzellen zu schreiben und Daten aus den Speicherzellen der gestapelten DRAM-Speicherchips zu lesen; wobei

- (f) eine integrierte Rücktreibereinheit vorgesehen ist, welche aufweist:

- (f1) Puffer für alle internen Adressleitungen, welche für das Treiben externer Adresssignale vorgesehen sind, welche an Adresslötstellen des DRAM-Speicherchips angelegt sind: und

- (f2) einen Multiplexer/Demultiplexer, welcher die internen Datenleitungen des ausgewählten DRAM-Speicherchips an Datenlötstellen des DRAM-Speicherchips schaltet.

## **Beschreibung**

Hintergrund der Erfindung

Bereich der Erfindung

**[0001]** Die Erfindung bezieht sich im Allgemeinen auf einen DRAM-Chip für ein DRAM Dual Inline Memory Module bzw. DRAM-Doppelreihen Speichermodul (DIMM), und speziell auf einen DRAM-Speicherchip für ein registrierten Doppelreihen-Speichermodul (DIMM).

#### Stand der Technik

[0002] Speichermodule sind zum Erhöhen der Speicherkapazität eines Computersystems vorgesehen. Ursprünglich wurden einzelne Einreihen-Speichermodule in Personal Computern benutzt, um die Größe des Speichers zu erhöhen. Ein einzelnes Einreihen-Speichermodul weist DRAM-Chips auf seiner Leiterplatine (PCB) nur auf einer Seite auf. Die Kontakte zum Verbinden der Leiterplatine des Einreihen-Speichermoduls (SIMM) sind redundant auf beiden Seiten des Moduls. Eine erste Variante von SIMMs hat dreißig Pins und liefert 8 Bits an Daten (9 Bits in Paritätsversionen). Eine zweite Variante von SIMMs, welche PS/2 genannt werden, weisen 72 Pins auf und liefern 32 Bits an Daten (36 Bits in Paritätsversionen).

[0003] Aufgrund der unterschiedlichen Datenbusbreite des Speichermoduls in einigen Prozessoren werden manchmal mehrere SIMM-Module in Paaren installiert, um eine Speicherbank zu füllen. Beispielsweise werden in 80386- oder 80486-Systeme, welche eine Datenbusbreite von 32 Bits besitzen, entweder vier 30-Pin-SIMMs oder ein 72-Pin-SIMM für eine Speicherbank benötigt. Für Pentiumsysteme, welche eine Datenbusbreite von 64 Bits besitzen, werden 72-Pin-SIMMs benötigt. Um einen einzelnes Einreihen-Speichermodul (SIMM) zu installieren, wird das Modul auf einem Sockel platziert. RAM-Technologien, welche bei Einreihen-Speichermodulen benutzt werden, beinhalten EDO und FPM.

**[0004]** Doppelreihen-Speichermodule (DIMM) begannen Einreihen-Speichermodule (SIMM) als den vorherrschenden Typ von Speichermodulen zu ersetzen, sobald die Pentiumprozessoren von Intel große Verbreitung am Markt bekamen.

[0005] Während einzelne Einreihen-Speichermodule (SIMMS) Speichereinheiten oder DRAM-Chips besitzen, welche nur auf einer Seite ihrer Leiterplatinen (PCB) montiert sind, weisen Doppelreihen-Speichermodule (DIMMS) Speichereinheiten auf, welche auf beiden Seiten der Leiterplatine der Module montiert sind.

[0006] Es gibt unterschiedliche Typen von Doppelreihen-Speichermodulen (DIMM). Ein ungepuffertes Doppelreihen-Speichermodul enthält keine Puffer oder Register, welche auf dem Modul platziert sind. Diese ungepufferten Doppelreihen-Speichermodule werden typischerweise in Desktop-PC-Systemen und Workstations benutzt. Die Anzahl von Pins ist typischerweise 168 in Einzeldatenraten-(SDR-)Speichermodulen, 184 Pins in Doppelreihenrate-Modulen und in DDR-2-Modulen. DDR-2-DRAMs sind eine natürliche Erweiterung der bestehenden DDR-DRAMs. DDR-2 wurde bei einer Betriebsfrequenz von 200 MHz eingeführt und wird gerade auf 266 MHz (DDR-2 533) erweitert, 333 MHz (DDR-2 667) für den Hauptspeicher und sogar 400 MHz (DDR-2 800) für spezielle Applikationen. DDR-SDRAM chron-DRAMs) erhöhen die Geschwindigkeit durch das Lesen von Daten sowohl an der ansteigenden Flanke als auch der abfallenden Flanke eines Taktpulses, wobei im Wesentlichen die Datenbandbreite verdoppelt wird, ohne die Taktfrequenz eines Taktsignals zu erhöhen.

[0007] Eine weitere Art von Doppelreihen-Speichermodulen (DIMM) ist ein registriertes Doppelreihen-Speichermodul. Ein registriertes Doppelreihen-Speichermodul weist mehrere zusätzliche Schaltungen auf dem Modul, speziell eine Rücktreiberpufferkomponente ähnlich einem Register auf, um die Befehlsadresssignale rückzutreiben. Ferner wird ein Phasenregelkreis (PLL) für Zeitjustierungen der Rücktreibertaktsignale vorgesehen. Registrierte Doppelreihen-Speichermodule werden typischerweise in hochmodernen Servern und hochmodernen Workstations benutzt.

[0008] ECC-Doppelreihen-Speichermodule weisen Fehlerkorrekturbits oder ECC-Bits auf. Diese Art von Doppelreihen-Speichermodulen besitzt insgesamt 64 Datenbits plus 8 ECC-Bits und wird meistens für Server-Computer benutzt. Registrierte Doppelreihen-Speichermodule werden entweder mit ECC oder ohne ECC für SDR, DDR und DDR-2 benutzt.

**[0009]** Eine weitere Art von Doppelreihen-Speichermodulen werden so genannte kleine außerreihige DIMM (SO-DIMM) genannt. Sie sind eine verbesserte Version von Standard-Doppelreihen-Speichermodulen und werden in Laptops und in einigen speziellen Servern benutzt.

**[0010]** Ein Doppelreihen-Speichermodul weist eine vorher festgelegte Anzahl N von Speicherchips (DRAMs) auf seiner Leiterplatine auf, Die Datenbreite jedes Speicherchips beträgt typischerweise 4 Bits, 8 Bits oder 16 Bits. Heutzutage nutzen Personal Computer meistens ein ungepuffertes Doppelreihen-Speichermodul, wenn ein DIMM als Hauptspeicher ausgewählt ist. Jedoch für ein Computersystem mit höheren Hauptspeicher-Volumenerfordernissen,

## DE 10 2005 058 214 A1 2006.06.14

speziell für einen Server, werden gewöhnlich Doppelreihen-Speichermodule gewählt.

**[0011]** Da sich die Speicheranforderungen in einem Computersystem von Tag zu Tag erhöhen, d.h. sowohl bezüglich der Speichergröße als auch der Speichergeschwindigkeit, ist es wünschenswert, eine maximale Anzahl von Speicherchips (DRAMs) auf jedem Speichermodul (DIMM) zu platzieren.

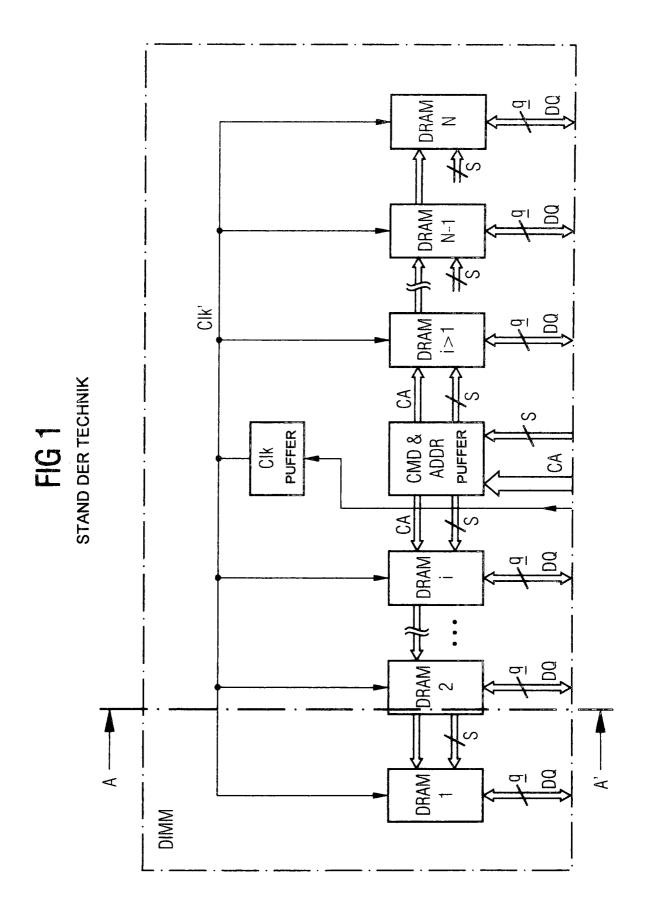

[0012] Fig. 1 zeigt ein Doppelreihen-Speichermodul entsprechend dem Stand der Technik. Das Doppelreihen-Speichermodul weist N DRAM-Chips auf, welche auf der oberen Seite der Leiterplatine (PCB) montiert sind. Das registrierte Doppelreihen-Speichermodul, wie es in Fig. 1 gezeigt wird, weist einen Befehls- und Adresspuffer auf, welcher Befehls- und Adresssignale puffert, welche an das Doppelreihen-Speichermodul mit Hilfe einer Hauptplatine angelegt werden und welche diese Signale über einen Befehls- und Adressbus (CA) an die DRAM-Chips abgeben, welche auf der Leiterplatine montiert sind. Ein Chipauswahlsignal S wird auch durch den Befehls- und Adresspuffer gepuffert und wird für das Auswählen des gewünschten DRAM-Chips, welcher auf der DIMM-Leiterplatine montiert ist, geliefert. Alle DRAM-Chips werden über ein Taktsignal CLK getaktet, welches durch einen Taktsignalpuffer gepuffert ist, welcher auch auf das Doppelreihen-Speichermodul (DIMM) montiert ist. Jeder DRAM-Chip ist mit der Hauptplatine über einen getrennte Datenbus (DQ) verbunden, welcher q Datenleitungen besitzt. Der Datenbus jedes DRAM-Chips weist typischerweise 4 bis 16 Bits auf.

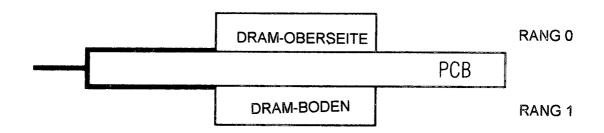

[0013] Fig. 2 zeigt einen Querschnitt des Doppelreihen-Speichermoduls (DIMM), wie er in Fig. 1, entlang der Linie A-A' gezeigt wird. Um die Speicherkapazität des DIMMs zu erhöhen, besitzt der DIMM DRAM-Chips, welche auf beiden Seiten der Leiterplatine (PCB) montiert sind. Es gibt einen DRAM-Chip auf der oberen Seite des DIMM-Moduls und einen DRAM-Chip an der unteren Seite des DIMM-Moduls. Entsprechend weist das DRAM-Doppelreihen-Speichermodul, wie es in Fig. 2 gezeigt wird, zwei Speicherränge oder Speicherniveaus auf, d.h. Speicherrang 0 und Speicherrang 1.

**[0014]** Um die Speicherkapazität eines Doppelreihen-Speichermoduls (DIMM) zu erhöhen, wurden weitere gestapelte DRAM-Chips entwickelt.

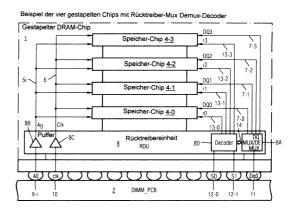

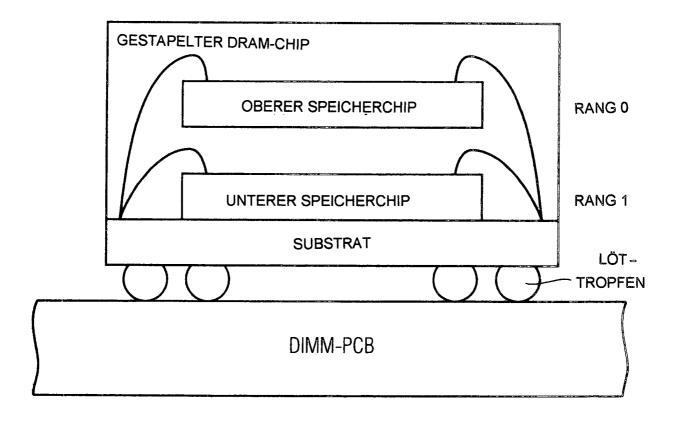

**[0015] Fig.** 3 zeigt einen gestapelten DRAM-Chip, welcher einen oberen Speicherchip und einen unteren Speicherchip besitzt, so dass er damit zwei Speicherränge innerhalb eines gestapelten DRAM-Chips liefert. Die zwei Speicherchips sind innerhalb eines Chips auf einem Substrat gepackt. Der gestapelte DRAM-Chip ist mit der Leiterplatine über Lötstellen bzw. Lötpunkte, wie z.B. Löttropfen, verbunden. Dop-

pelreihen-Speichermodule, welche gestapelte DRAM-Chips auf beiden Seiten der Leiterplatine besitzen, wie in **Fig.** 3 gezeigt, besitzen vier Speicherränge, d.h. zwei Speicherränge auf der oberen Seite und zwei Speicherränge auf der unteren Seite.

[0016] Bei gegenwärtigen Computer-Doppelreihen-Speichermodulen ist es erlaubt, dass sie zwei Speicherränge besitzen. Wenn man die Anzahl der Speicherränge innerhalb der Speichersysteme auf vier Speicherränge oder sogar acht Speicherränge erhöht, wird die Belastung auf dem DQ-Bus und dem CA-Bus erhöht, wie in Fig. 1 gezeigt wird. Für den CA-Bus ist das Erhöhen der Last nicht dramatisch, da der Befehls- und Adressbus (CA) bei halber Geschwindigkeit im Vergleich zum Datenbus läuft und der Befehls- und Adresspuffer die Adress- und Befehlssignale, welche durch den Prozessor an der Hauptplatine des Doppelreihen-Speichermoduls angelegt werden, zurücktreibt. Das Erhöhen der Speicherränge auf dem Doppelreihen-Speichermodul ruft jedoch ein Erhöhen der Belastung des DQ-Datenbusses hervor, welcher durch das Steuergerät auf der Hauptplatine betrieben wird. Die Datenrate auf den DQ-Bussen ist sehr hoch, speziell wenn sie bei einer DDR-2-Datenrate laufen. Folglich verschlechtert ein Erhöhen der Belastung, welche mit jedem Datenbus verbunden ist, die Rate der Datensignale weiter, so dass Datenfehler nicht ausgeschlossen werden können. Entsprechend gibt es eine Begrenzung der Anzahl M von Speicherrängen innerhalb eines DRAM-Chips, welcher mit dem DQ-Bus des Chips verbunden sind. Durch das Begrenzen der Anzahl Speicherrängen, welcher innerhalb eines DRAM-Chips erlaubt sind, ist auch die Speicherkapazität eines Zweireihenspeichers begrenzt.

#### Zusammenfassung der Erfindung

## Aufgabenstellung

**[0017]** Entsprechend ist es eine Aufgabe der vorliegenden Erfindung, einen gestapelten DRAM-Speicherchip für ein Doppelreihen-Speichermodul zu liefern, welcher es gestattet, für eine vorher festgelegte Betriebsfrequenz eine erhöhte Anzahl von Speicherrängen auf dem Zweireihenspeicher anzubringen.

**[0018]** Diese Aufgabe wird durch einen gestapelten DRAM-Speicherchip erreicht, welcher die Merkmale des Anspruchs 1 aufweist.

**[0019]** Die vorliegende Erfindung liefert einen gestapelten DRAM-Speicherchip für ein Doppelreihen-Speichermodul (DIMM), welches besitzt:

- (a) eine vorher festgelegte Anzahl (M) von gestapelten DRAM-Speicherchips;

- (b) wobei jeder DRAM-Speicherchip durch ein entsprechendes Speicherrangsignal (r) auswählbar ist;

- (c) wobei jeder DRAM-Speicherchip ein Feld von Speicherzellen aufweist;

- (d) wobei ein gewöhnlicher interner Adressbus, welcher aus Adressleitungen besteht, für das Adressieren der Speicherzellen vorgesehen ist und mit allen M gestapelten DRAM-Speicherchips verbunden ist:

- (e) wobei M interne Datenbusse, welche aus internen Datenleitungen bestehen, für das Schreiben von Daten in die Speicherzellen und das Lesen der Daten aus den Speicherzellen der gestapelten DRAM-Speicherchips vorgesehen sind; wobei

- (f) eine integrierte Rücktreibereinheit vorgesehen ist, welche aufweist:

- (f1) Puffer für alle internen Adressleitungen, welche vorgesehen sind, externe Adresssignale zu treiben, welche an den Adresslötstellen des DRAM-Speicherchips angelegt sind, und;

- (f2) einen Multiplexer/Demultiplexer, welcher die internen Datenleitungen des ausgewählten DRAM-Speicherchips auf Datenlötstellen des DRAM-Speicherchips schaltet.

**[0020]** In einem bevorzugten Speicherchip weist die Rücktreibereinheit ferner einen Speicherrang-Decodierer zum Erzeugen des internen Speicherrangsignals auf, in Antwort auf externe Auswahlsignale, welche an den Steueranschlüssen des DRAM-Speicherchips angelegt sind.

[0021] Dies hat den Vorteil, dass durch das Integrieren des Speicherrang-Decoders innerhalb des DRAM-Speicherchips die Anzahl der Auswahlsignale, welche durch den Befehls- und Adresspuffer für jeden DRAM-Chip geliefert werden müssen, reduziert ist. Folglich ist die Anzahl der Auswahlsignalleitungen auf dem Doppelreihen-Speichermodul reduziert, so dass die Größe der Leiterplatine erniedrigt wird und die Komplexität der Leitungsführung herabgesetzt ist.

**[0022]** In einer weiteren Ausführungsform steuert der Speicherrang-Decodierer den Multiplexer/Demultiplexer.

**[0023]** In einer weiteren Ausführungsform weist der Multiplexer/Demultiplexer Puffer zum Puffern der Datensignale auf, welche über die geschalteten Datenleitungen übertragen werden.

**[0024]** In einer bevorzugten Ausführungsform des gestapelten DRAM-Speicherchips entsprechend der vorliegenden Erfindung sind alle DRAM-Speicherchips durch ein gewöhnliches internes Taktsignal getaktet.

**[0025]** In einer bevorzugten Ausführungsform des gestapelten DRAM-Chips entsprechend der vorliegenden Erfindung weist die Rücktreibereinheit ferner einen Puffer zum Treiben eines externen Taktsignals

auf, welches an einem Taktlötanschluss des DRAM-Speicherchips angelegt ist, um das interne Taktsignal zu erzeugen.

**[0026]** In einer bevorzugten Ausführungsform des gestapelten DRAM-Speicherchips entsprechend der vorliegenden Erfindung sind der Stapel an DRAM-Chips und die Rücktreibereinheit in dem DRAM-Speicherchip integriert.

**[0027]** In einer bevorzugten Ausführungsform des DRAM-Speicherchips entsprechend der vorliegenden Erfindung wird die Rücktreibereinheit über Spannungsversorgungs-Lötanschlüsse des DRAM-Speicherchips versorgt.

**[0028]** Die Erfindung liefert ferner ein Doppelreihen-Speichermodul, welches eine Vielzahl von gestapelten DRAM-Speicherchips aufweist, wobei jeder gestapelte DRAM-Speicherchip besitzt:

- (a) eine vorher festgelegte Anzahl (M) von gestapelten DRAM-Speicherchips;

- (b) wobei jeder DRAM-Speicherchip aus dem jeweiligen Speicherrangsignal (r) auswählbar ist;

- (c) wobei jeder DRAM-Speicherchip ein Feld von Speicherzellen aufweist;

- (d) wobei ein gewöhnlicher interner Adressbus, welcher aus Adressleitungen besteht, für das Adressieren der Speicherzellen vorgesehen ist und mit allen M gestapelten DRAM-Speicherchips verbunden ist;

- (e) wobei M interne Datenbusse, welche aus internen Datenleitungen bestehen, für das Schreiben von Daten in die Speicherzellen und das Lesen von Daten aus den Speicherzellen der gestapelten DRAM-Speicherchips vorgesehen sind;

- (f) wobei unterhalb der gestapelten DRAM-Speicherchips eine Rücktreibereinheit vorgesehen ist, wobei die Rücktreibereinheit aufweist:

- (f1) Puffer für alle internen Adressleitungen, welche für das Treiben von externen Adresssignalen vorgesehen sind, welche an den Adresslötstellen des DRAM-Speicherchips angelegt sind, und;

- (f2) einen Multiplexer/Demultiplexer, welcher die internen Datenleitungen des ausgewählten DRAM-Speicherchips an Datenlötstellen des DRAM-Speicherchips schaltet.

**[0029]** In einer bevorzugten Ausführungsform weist das Doppelreihen-Speichermodul einen Befehls- und Adresspufferchip zum Puffern von Befehls- und Adresssignalen auf, welche von der Hauptleiterplatine empfangen werden.

[0030] In einer bevorzugten Ausführungsform des Doppelreihen-Speichermoduls entsprechend der vorliegenden Erfindung ist der Befehls- und Adresspuffer über einen Befehls- und Adressbus an alle gestapelten DRAM-Speicherchips angeschlossen, welche auf einer Leiterplatine des Doppelreihen-Spei-

chermoduls montiert sind.

#### Ausführungsbeispiel

Kurze Beschreibung der Zeichnungen

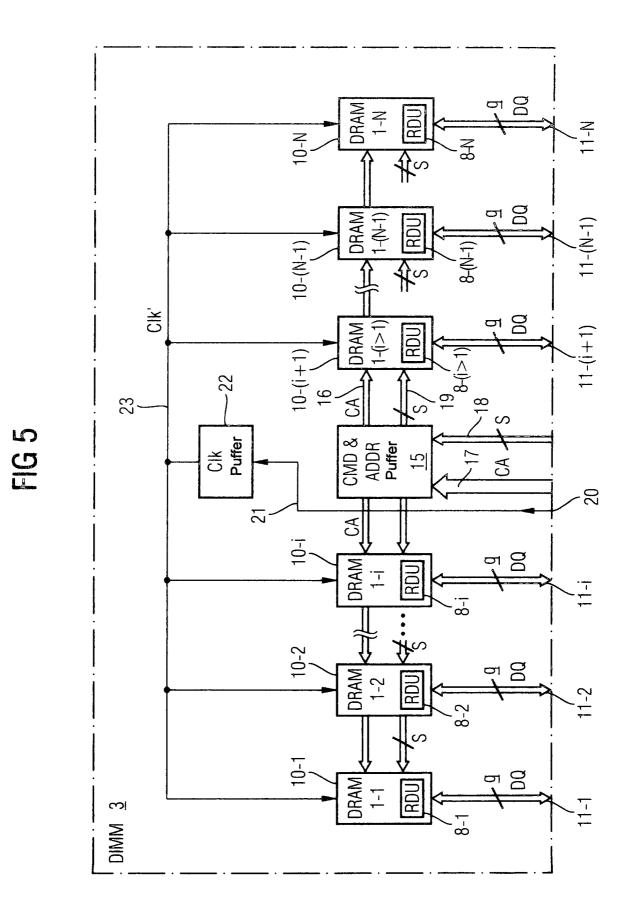

**[0031]** Fig. 1 zeigt ein Doppelreihen-Speichermodul (DIMM) entsprechend dem Stand der Technik von oben;

**[0032]** Fig. 2 ist eine Querschnittsansicht des Doppelreihen-Speichermoduls entsprechend dem Stand der Technik, wie es in Fig. 1 gezeigt wird;

**[0033]** Fig. 3 zeigt einen Querschnitt eines gestapelten DRAM-Chips entsprechend dem Stand der Technik;

**[0034]** Fig. 4 zeigt eine Querschnittsansicht einer bevorzugten Ausführungsform eines gestapelten DRAM-Chips entsprechend der vorliegenden Erfindung;

**[0035]** Fig. 5 zeigt eine Draufsicht auf ein Doppelreihen-Speichermodul, welches gestapelte DRAM-Chips aufweist, entsprechend der vorliegenden Erfindung.

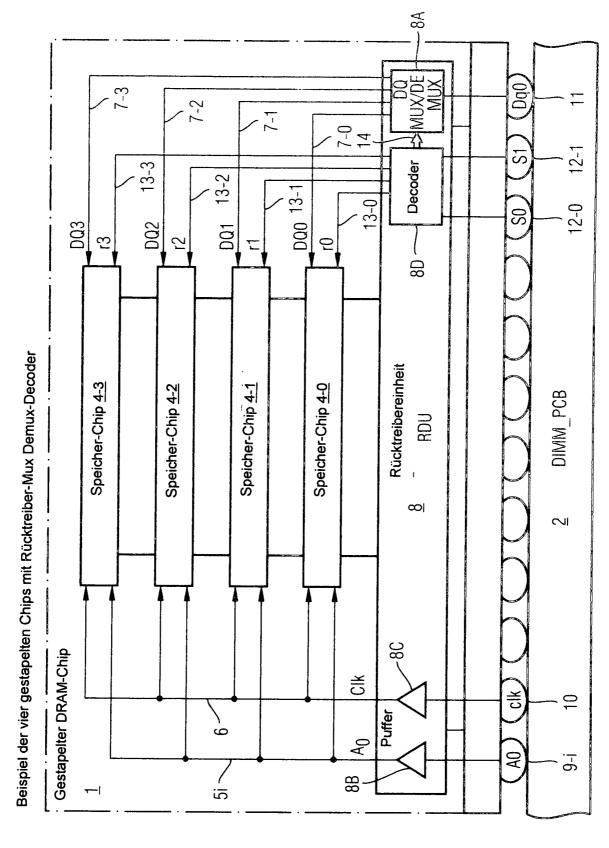

[0036] Mit Bezug auf Fig. 4 wird ein Querschnitt eines gestapelten DRAM-Speicherchips 1 gezeigt, welcher auf einer Leiterplatine (PCB) 2 eines Doppelreihen-Speichermoduls 3 montiert ist. Der gestapelte DRAM-Chip 1, wie er in Fig. 4 gezeigt wird, weist in der gezeigten Ausführungsform vier gestapelte Speicherchips 4-0, 4-1, 4-2, 4-5 auf. Jeder Speicherchip 4-i ist über ein entsprechendes Speicherrangsignal r-i auswählbar. Die DRAM-Speicherchips 4-i beinhalten ein Feld von Speicherzellen, welche über Adressleitungen adressierbar sind. Ein gewöhnlicher interner Adressbus 5 weist eine vorher festgelegte Anzahl von internen Adressleitungen 5-i auf, welche für das Adressieren der Speicherzellen der Speicherchips 4-i vorgesehen sind. Fig. 4 zeigt als ein Beispiel einen Adresslötanschluss Ao auf, welcher über eine Adressleitung 5-i an alle Speicherchips 4-i angeschlossen ist. Alle Adressleitungen des internen Adressbusses sind parallel zu allen vier DRAM-Speicherchips des gestapelten DRAM-Chips 1 angeschlossen. Die Speicherchips 4-i sind über ein Taktsignal CLK, welches an allen Speicherchips angelegt ist, über eine interne Taktleitung 6 getaktet, wie dies in Fig. 4 gezeigt wird. Jeder Speicherchip 4-i ist über einen entsprechenden internen Datenbus 7-i an einen DQ-Multiplexer/Demultiplexer 8A angeschlossen. Jeder interne Datenbus 7-i weist eine vorher festgelegte Anzahl von Datenleitungen für das Anschließen des jeweiligen Speicherchips 4-i an den DQ-Multiplexer/Demultiplexer 8A auf, Jeder DQ-Datenbus 7-i weist z.B. 4 bis 16 Bitleitungen auf. Die internen Datenbusse DQ-Busse 7-i sind für das Schreiben von Daten in die Speicherzellen und für das Lesen der Daten aus den Speicherzellen der gestapelten DRAM-Speicherchips **4-i** vorgesehen.

[0037] Der gestapelte DRAM-Chip 1 entsprechend der vorliegenden Erfindung, wie sie in Fig. 4 gezeigt wird, weist unterhalb der gestapelten DRAM-Speicherchips 4-i eine Rücktreibereinheit 8 auf. Die Rücktreibereinheit 8 weist die DQ-Multiplexer/Demultiplexer-Einheit 8A und Puffer 8B für alle internen Adressleitungen 5-i auf, welche für das Treiben von externen Adresssignalen bereitgestellt sind, welche an den Adresslötstellen 9-i des DRAM-Speicherchips 1 angelegt sind. In der bevorzugten Ausführungsform, wie sie in Fig. 4 gezeigt wird, weist die Rücktreibereinheit 8 ferner einen Puffer 8C zum Treiben eines Taktsignals CLK auf, welches an dem DRAM-Chip 1 mit Hilfe einer Taktsignallötstelle 10 angelegt ist. Die Rücktreibereinheit 8 weist in allen Ausführungsformen den Multiplexer/Demultiplexer 8A auf, welcher die internen Datenleitungen oder den Datenbus 7-i eines ausgewählten DRAM-Speicherchips an die Datenlötstellen 11 des DRAM-Speicherchips 1 schaltet. Die Lötstellen 9, 10, 11 sind durch Kugeln bzw. Tropfen oder Stifte gebildet. Die Anzahl q der DQ-Leitungen durch den DRAM-Chip 1 ist in einer bevorzugten Ausführungsform entweder vier oder acht.

**[0038]** In der bevorzugten Ausführungsform, wie sie in <u>Fig. 4</u> gezeigt wird, weist die Rücktreibereinheit **8** ferner einen Speicherrang-Decoder **8D** zum Erzeugen interner Speicherrang-Auswahlsignale r-i in Antwort auf externe ausgewählte Signale  $S_i$  auf, welche angelegt sind, um die Lötstellen **12-0**, **12-1** des DRAM-Speicherchips **1**, wie er in <u>Fig. 4</u> gezeigt wird, zu steuern. Der Speicherrang-Decoder **8D** empfängt in der gezeigten Ausführungsform zwei externe Auswahlsignale  $S_0$ ,  $S_1$  und decodiert sie, um vier Speicherrangsignale  $r_i$  zu erzeugen, welche an die Speicherchips **4-i** über Steuerleitungen **13-i** angelegt sind.

[0039] In der bevorzugten Ausführungsform der Fig. 4 ist der Speicherrang-Decoder 8D innerhalb der Rücktreibereinheit 8 des gestapelten DRAM 1 integriert. In einer alternativen Ausführungsform ist der Decoder 8D in den zentralen Befehls- und Adresspuffer des Doppelreihen-Speichermoduls 3 integriert. Die Integration des Speicherrang-Decoders 8D innerhalb der Rücktreibereinheit 8 hat den Vorteil, dass die Anzahl der Auswahlsignale und die Auswahlleitungen auf dem Doppelreihen-Speichermodul 3 minimiert werden kann. In der bevorzugten Ausführungsform der Fig. 4 steuert der Speicherrang-Decoder 8D den DQ-Multiplexer/Demultiplexer 8A über interne Steuerleitungen 14. Der Multiplexer/Demultiplexer 8A weist in einer bevorzugten Ausführungsform Puffer zum Treiben der Datensignale auf, welche über die geschalteten Datenleitungen übertragen werden. Der Multiplexer/Demultiplexer 8a wird von dem Multiplexmodus (Lesemodus) zu dem Demultiplexmodus (Schreibemodus) in Antwort auf ein Schreibefreigabe-(WE-)Steuersignal geschaltet.

[0040] Der Stapel der DRAM-Speicherchips 4-i und die Rücktreibereinheit 8 sind in dem DRAM-Speicherchip 1 integriert. Um die Speicherdichte pro Doppelreihen-Speichermodul 3 zu erhöhen, sind die Speicherchips in einer bevorzugten Ausführungsform in ein FBGA (Fine Pitch Ball Grid bzw. feingeteiltes Kugelgitter) integriert. Das Vorsehen einer Rücktreibereinheit 8 innerhalb des gestapelten DRAM-Chips 1, welches in der FBGA-Packung integriert sein kann, gestattet es, die Anzahl der Speicherchips 4-i zu erhöhen, ohne die Belastung für den Befehls- und Adresspuffer 15 und, noch bedeutender, für die Belastung des Frozessors auf dem Hauptboard zu erhöhen. Dies gestattet eine wesentlich höhere Betriebsfrequenz für das Betreiben des Doppelreihen-Speichermoduls 3. In der bevorzugten Ausführungsform, wie sie in Fig. 4 gezeigt wird, ist die Rücktreibereinheit 8 unterhalb des Speicherchipstapels auf der unteren Seite des gestapelten DRAM-Chips 1 vorgesehen.

[0041] Fig. 5 zeigt ein Doppelreihen-Speichermodul 3, welches eine vorher festgelegte Anzahl N von gestapelten DRAM-Chips 1 aufweist, wie sie in Fig. 4 gezeigt werden. Die Anzahl N der DRAMs ist typischerweise 9 oder 18, abhängig von der Anzahl M der Speicherränge. Jeder gestapelte DRAM-Chip 1 weist M gestapelte DRAM-Speicherchips auf. Die Anzahl M der gestapelten DRAM-Speicherchips kann 1, 2, 4, 8, 16 ... DRAM-Speicherchips sein. Das Doppelreihen-Speichermodul 3 weist ferner wenigstens einen zentralen Befehls- und Adresspuffer 15 auf, welcher in der Mitte der Leiterplatine 2 des Doppelreihen-Speichermoduls 3 platziert ist. Der Befehls- und Adresspuffer 15 ist über einen Befehlsund Adressbus 16 an alle DRAM-Speicherchips 1 auf dem Doppelreihen-Speichermodul 3 angeschlossen. Der Befehls- und Adresspuffer 15 empfängt Befehlsund Adresssignale von der Hauptleiterplatine über Befehls- und Adressleitungen 17 und treibt sie über den Befehls- und Adressbus 16 an alle DRAM-Chips 1. Der Befehls- und Adresspuffer 15 empfängt ferner Auswahlsignale über einen Auswahlsteuerbus 18 und treibt sie über einen Auswahlsignalbus 19 an alle DRAM-Chips 1. Die Selektionssignale, welche an die DRAM-Chips 1 über den Auswahlbus 19 angelegt sind, wählen den DRAM-Chip und den Speicherchip 4-i innerhalb des DRAM-Chips 1 aus.

**[0042]** Im Falle, dass der lokale Speicherrang-Decoder **8D** innerhalb der Rücktreibereinheit **8** jedes gestapelten DRAM-Speicherchips **1** integriert ist, wird die Busbreite S des Auswahlsignalbusses **19** gegeben durch:

$2^{S} = N + M$

wobei N die Anzahl der DRAM-Chips auf dem Doppelreihen-Speichermodul 3 ist und

**[0043]** M die Anzahl der gestapelten Speicherchips oder Ränge innerhalb jedes DRAM-Chips 1 ist.

[0044] In einer anderen Ausführungsform, in welcher der Speicherrang-Decoder 8D in den Befehlsund Adresspuffer 15 integriert ist und nicht innerhalb des DRAM-Chips 1, ist die Busbreite S des Auswahlsteuerbusses 19 gegeben durch

S = IdN + M

**[0045]** In beiden Ausführungsformen wird die Anzahl der Kontaktlötstellen, um das Doppelreihen-Speichermodul **3** an der Hauptplatine über Auswahlleitungen **18** zu kontaktieren, minimiert.

[0046] Das Doppelreihen-Speichermodul 3 entsprechend der vorliegenden Erfindung, wie es in Fig. 5 gezeigt wird, weist ferner wenigstens eine Kontaktlötstelle 20 auf, welche über eine Taktleitung 21 an einen Taktsignalpuffer 22 angeschlossen ist. Das externe Taktsignal, welches von der Hauptplatine empfangen wird, wird durch den Taktsignalpuffer 21 gepuffert und an alle DRAM-Speicherchips 1 über eine interne Taktleitung 23 angelegt. Jeder DRAM-Chip 1 weist eine Rücktreibereinheit 8 mit einem Puffer 8C zum Puffern des empfangenen internen Taktsignals auf.

[0047] Mit dem gestapelten DRAM-Speicherchip 1. entsprechend der vorliegenden Erfindung, kann ein Doppelreihen-Speichermodul 3 mit einer sehr hohen Speicherdichte erreicht werden, ohne die Belastung für den Prozessor auf der Hauptplatine zu erhöhen. Entsprechend erlaubt das Doppelreihen-Speichermodul 3, welches die gestapelten DRAM-Speicherchips 1 entsprechend der vorliegenden Erfindung aufweist, höhere Betriebsfrequenzen des Prozessors. Das Stapeln der Speicherchips liefert eine vorher nicht da gewesene Speicherdichte über die Platinenfläche und bietet zur gleichen Zeit höhere elektrische Eigenschaften der resultierenden Doppelreihen-Speicherkomponente. Ein Doppelreihen-Speichermodul 3 entsprechend der vorliegenden Erfindung ist voll mit existierenden Einbauplätzen für Doppelreihenspeicher kompatibel. Da die gleiche Verbindungstechnologie für die gestapelten Speicherchips 4-1 benutzt wird, besitzen die Chips ähnliche elektrische Parameter. In einer bevorzugten Ausführungsform sind die DRAM-Speicherchips 1 in feingeteilten Kugelgitterpackungen (FPBG) auf BOC-Platine in Chip-Technologie integriert.

### Patentansprüche

1. Gestapelter DRAM-Speicherchip für Doppelreihen-Speichermodul (DIMM), welcher besitzt:

- (a) eine vorher festgelegte Anzahl (M) von gestapelten DRAM-Speicherchips;

- (b) wobei jeder DRAM-Speicherchip durch ein entsprechendes Speicherrangsignal (r) auswählbar ist;

- (c) wobei jeder DRAM-Speicherchip ein Feld von Speicherzellen aufweist;

- (d) wobei ein allgemeiner interner Adressbus, welcher aus Adressleitungen besteht, zum Adressieren der Speicherzellen vorgesehen ist und welcher mit allen M gestapelten DRAM-Speicherchips verbunden ist:

- (e) wobei M interne Datenbusse, welche aus internen Datenleitungen bestehen, zum Schreiben von Daten in die Speicherzellen und zum Lesen von Daten aus den Speicherzellen der gestapelten DRAM-Speicherchips vorgesehen sind; wobei

- (f) eine integrierte Rücktreibereinheit vorgesehen ist, welche aufweist:

- (f1) Puffer für alle internen Adressleitungen, welche zum Treiben externer Adresssignale vorgesehen sind, welche an Adresslötstellen des DRAM-Speicherchips angelegt sind, und;

- (f2) einen Multiplexer/Demultiplexer, welcher die internen Datenleitungen des ausgewählten DRAM-Speicherchips an Datenlötstellen des DRAM-Speicherchips schaltet,

- 2. Gestapelter DRAM-Speicherchip nach Anspruch 1, wobei die Rücktreibereinheit ferner einen Speicherrang-Decoder zum Erzeugen des internen Speicherrangsignals in Antwort auf interne Auswahlsignale aufweist, welche angelegt sind, um die Lötstellen des DRAM-Speicherchips zu steuern,

- 3. Gestapelter DRAM-Speicherchip nach Anspruch 3, wobei der Speicherrang-Decoder den Multiplexer/Demultiplexer steuert.

- 4. Gestapelter DRAM-Speicherchip nach Anspruch 1, wobei der Multiplexer/Demultiplexer zwischen einem Multiplexmodus und einem Demultiplexmodus in Antwort auf ein Schreibefreigabe-Steuersignal geschaltet wird.

- 5. Gestapelter DRAM-Speicherchip nach Anspruch 1, wobei der Multiplexer/Demultiplexer Puffer zum Treiben der Datensignale aufweist, welche über die geschalteten Datenleitungen übertragen werden.

- 6. Gestapelter DRAM-Speicherchip nach Anspruch 1, wobei alle DRAM-Speicherchips durch ein gewöhnliches internes Taktsignal getaktet werden,

- 7. Gestapelter DRAM-Speicherchip nach Anspruch 6, wobei die Rücktreibereinheit ferner einen Puffer zum Treiben eines externen Taktsignals aufweist, welches an eine Taktlötstelle des DRAM-Speicherchips angelegt ist, um das interne Taktsignal zu erzeugen.

- 8. Gestapelter DRAM-Speicherchip nach Anspruch 1, wobei der Stapel von DRAM-Speicherchips und die Rücktreibereinheit in dem DRAM-Speicherchip integriert sind.

- 9. Gestapelter DRAM-Speicherchip nach Anspruch 1, wobei die Rücktreibereinheit über Spannungsversorgungs-Lötstellen des DRAM-Speicherchips versorgt wird.

- 10. Doppelreihen-Speichermodul (DIMM), welches eine Vielzahl von gestapelten DRAM-Speicherchips aufweist, wobei jeder gestapelte DRAM-Speicherchip besitzt:

- (a) eine vorher festgelegte Anzahl (M) von gestapelten DRAM-Speicherchips;

- (b) wobei jeder DRAM-Speicherchip durch ein entsprechendes Speicherrangsignal (3) auswählbar ist;

- (c) wobei jeder DRAM-Speicherchip ein Feld von Speicherzellen aufweist;

- (d) wobei ein gewöhnlicher interner Adressbus, welcher aus Adressleitungen besteht, zum Adressieren der Speicherzellen vorgesehen ist und welcher an alle M gestapelten DRAM-Speicherchips angeschlossen ist;

- (e) wobei M interne Datenbusse, welche aus internen Datenleitungen bestehen, vorgesehen sind, um Daten in die Speicherzellen zu schreiben und Daten aus den Speicherzellen der gestapelten DRAM-Speicherchips zu lesen;

- (f) wobei eine integrierte Rücktreibereinheit vorgesehen ist, welche aufweist:

- (f1) Puffer für alle internen Adressleitungen, welche für das Treiben externer Adresssignale vorgesehen sind, welche an den Adresslötstellen des DRAM-Speicherchips angelegt sind; und

- (f2) einen Multiplexer/Demultiplexer, welcher die internen Datenleitungen des ausgewählten DRAM-Speicherchips an Datenlötstellen des DRAM-Speicherchips schaltet,

- 11. Doppelreihen-Speichermodul (DIMM) nach Anspruch 10, wobei das Doppelreihen-Speichermodul ferner einen Befehls- und Adresspufferchip zum Puffern von Befehls- und Adresssignalen aufweist, welche von einer Hauptleiterplatine empfangen werden.

- 12. Doppelreihen-Speichermodul (DIMM) nach Anspruch 11, wobei der Befehls- und Adresspuffer über einen Befehls- und Adressbus mit allen gestapelten DRAM-Speicherchips verbunden ist, welche auf einer Leiterplatine des Doppelreihen-Speichermoduls montiert sind.

Es folgen 4 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG 2 STAND DER TECHNIK

FIG 3

STAND DER TECHNIK

FIG 4