(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6127872号

(P6127872)

(45) 発行日 平成29年5月17日(2017.5.17)

(24) 登録日 平成29年4月21日(2017.4.21)

(51) Int.Cl.

F 1

G06F 12/00 (2006.01)

G06F 13/38 (2006.01)G06F 12/00

G06F 13/38571A

310C

請求項の数 7 (全 10 頁)

(21) 出願番号 特願2013-201878 (P2013-201878)

(22) 出願日 平成25年9月27日 (2013.9.27)

(65) 公開番号 特開2015-69326 (P2015-69326A)

(43) 公開日 平成27年4月13日 (2015.4.13)

審査請求日 平成28年6月6日 (2016.6.6)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100090273

弁理士 國分 孝悦

豊田 雄太

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 細江 広治

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 常世田 明夫

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

最終頁に続く

(54) 【発明の名称】演算処理装置及び演算処理装置の制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリに対して複数の長さのアクセス要求を発行するメモリ制御部を有する演算処理装置であって、

前記メモリ制御部は、

前記アクセス要求の長さ毎に前記アクセス要求を保持する複数のキュー保持部と、

前記メモリの資源の残数に応じて、前記複数のキュー保持部に保持されているアクセス要求のいずれかを選択して前記メモリに発行する調停部と

を有することを特徴とする演算処理装置。

## 【請求項 2】

前記複数の長さのアクセス要求は、複数の長さの書き込みデータを含む書き込み要求であることを特徴とする請求項1記載の演算処理装置。

## 【請求項 3】

前記複数の長さのアクセス要求は、読み出し要求及び書き込み要求であることを特徴とする請求項1又は2記載の演算処理装置。

## 【請求項 4】

前記メモリの資源の残数は、前記メモリ内のクロック乗り換え回路が前記アクセス要求を記憶する複数のフロップフロップ回路のうちの未使用のフリップフロップ回路の数であることを特徴とする請求項1～3のいずれか1項に記載の演算処理装置。

## 【請求項 5】

10

20

前記メモリは、前記アクセス要求の長さが長いほど多くの資源を必要とし、前記調停部は、前記メモリの資源の残数以下の資源を必要とする長さのアクセス要求を選択して前記メモリに発行することを特徴とする請求項1～4のいずれか1項に記載の演算処理装置。

#### 【請求項6】

前記調停部は、前記アクセス要求の長さ毎の発行数をカウントするカウンタを有し、前記アクセス要求の長さ毎の発行数に応じて、前記複数のキュー保持部に保持されているアクセス要求のいずれかを選択して前記メモリに発行することを特徴とする請求項1～5のいずれか1項に記載の演算処理装置。

#### 【請求項7】

メモリに対して複数の長さのアクセス要求を発行するメモリ制御部を有する演算処理装置の制御方法であって、

前記メモリ制御部が有する複数のキュー保持部が、前記アクセス要求の長さ毎に前記アクセス要求を保持し、

前記メモリ制御部が有する調停部が、前記メモリの資源の残数に応じて、前記複数のキュー保持部に保持されているアクセス要求のいずれかを選択して前記メモリに発行することを特徴とする演算処理装置の制御方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、演算処理装置及び演算処理装置の制御方法に関する。

#### 【背景技術】

#### 【0002】

パケットのアドレスフィールドからリンクを特定でき、情報フレームが確認情報として送受信され、扱うパケット長に統計的な偏りを有するパケット通信方式が知られている（例えば、特許文献1参照）。バッファをパケット長に応じて複数種類設けてなるバッファプールと、受信パケットをパケット長に応じてバッファプールの各バッファに振分けるデータ受信部が設けられる。優先的に送受信を行ないたいパケットに応じたバッファの数を多くし、パケット受信時にデータ受信可能なバッファが無い場合、アドレスフィールドからリンクを特定しそのリンクに対してのみ自局ビジーとする。空バッファの総数が規定数以下になると、全リンクに対して自局ビジーとする機能と、空バッファの総数が一定数を越えると、自局レディとする機能とを有するフロー制御部が設けられる。

#### 【0003】

また、可変長のパケットにより通信するネットワークを相互に接続するパケット通信網接続装置が知られている（例えば、特許文献2参照）。判定手段は、受信したパケットを、そのパケット長が所定の値以下であれば短パケット、そうでなければ長パケットと判定する。優先送信手段は、短パケットを長パケットに優先して送信する。

#### 【0004】

また、単一の出力待ち行列を用いた優先制御方式が知られている（例えば、特許文献3参照）。この優先制御方式は、輻輳を受けているまたは受け得るパケットと輻輳を受けていないパケットの順序を交換することにより、輻輳を受けていないパケットの出力優先度を向上させる。

#### 【先行技術文献】

#### 【特許文献】

#### 【0005】

【特許文献1】特開平1-146445号公報

【特許文献2】特開平10-271163号公報

【特許文献3】特開2001-177575号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

10

20

30

40

50

**【0006】**

メモリに対するアクセス要求のパケット長は、アクセス要求の種別に依り異なり、固定長では無い。一方で、メモリは、受信処理の資源に限りがあるため、常時、アクセス要求を処理できない場合が多い。この場合、メモリは、資源の空きを待って、アクセス要求の処理を行うことになる。演算処理装置は、メモリの資源の残数が足りず、アクセス要求の送信が待たされることにより、スループットが低下してしまう。

**【0007】**

1つの側面では、本発明の目的は、メモリに対するアクセス要求発行のスループットを向上させることができる演算処理装置及び演算処理装置の制御方法を提供することである。

10

**【課題を解決するための手段】****【0008】**

演算処理装置は、メモリに対して複数の長さのアクセス要求を発行するメモリ制御部を有する演算処理装置であって、前記メモリ制御部は、前記アクセス要求の長さ毎に前記アクセス要求を保持する複数のキュー保持部と、前記メモリの資源の残数に応じて、前記複数のキュー保持部に保持されているアクセス要求のいずれかを選択して前記メモリに発行する調停部とを有する。

**【発明の効果】****【0009】**

調停部を設けることにより、メモリに対するアクセス要求発行のスループットを向上させることができる。

20

**【図面の簡単な説明】****【0010】**

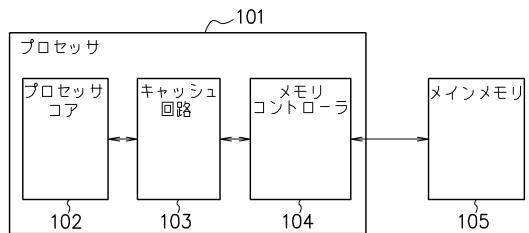

【図1】図1は、本実施形態による演算処理システムの構成例を示す図である。

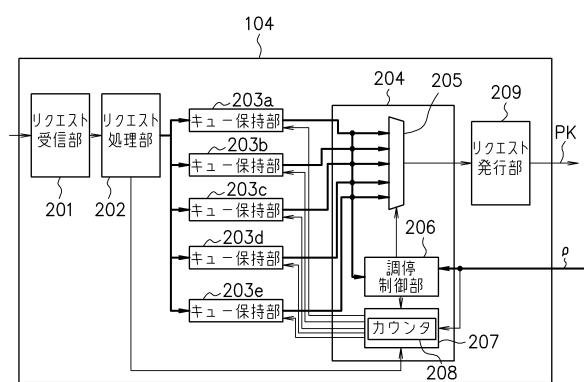

【図2】図2は、図1のメモリコントローラの構成例を示す図である。

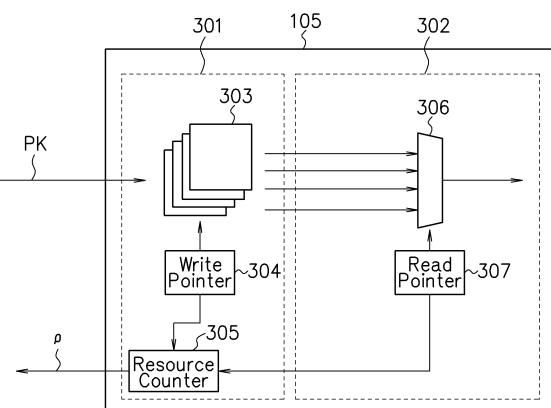

【図3】図3は、図1のメインメモリの構成例を示す図である。

**【発明を実施するための形態】****【0011】**

図1は、本実施形態による演算処理システムの構成例を示す図である。演算処理システムは、プロセッサ101及びメインメモリ105を有する。プロセッサ101は、演算処理装置であり、プロセッサコア102、キャッシュ回路103及びメモリコントローラ104を有する。プロセッサコア102は、フェッチ及びストア命令をキャッシュ回路103に発行する。キャッシュ回路103は、キャッシュメモリ及びキャッシュコントローラを有する。キャッシュコントローラは、アクセス要求（読み出し要求又は書き込み要求）のパケットをメモリコントローラ104に発行する。メモリコントローラ104は、メモリ制御部であり、アクセス要求の調停を行い、アクセス要求のパケットをメインメモリ105に発行する。メインメモリ105は、読み出し要求を入力すると、指定アドレスのデータを読み出し、読み出したデータを、メモリコントローラ104及びキャッシュ回路103を介して、プロセッサコア102に出力する。また、メインメモリ105は、書き込み要求を入力すると、書き込み要求内の書き込みデータを指定アドレスに書き込む。

30

**【0012】**

メモリコントローラ104が発行するアクセス要求のパケット長は、アクセス要求の種別に依り異なり、可変長である。メモリコントローラ104は、メインメモリ105に対して複数の長さのアクセス要求を発行する。例えば、アクセス要求は、異なる長さの書き込みデータを含む書き込み要求によりパケット長が異なる。また、アクセス要求は、読み出し要求と書き込み要求とではパケット長が異なる。

**【0013】**

図2は、図1のメモリコントローラ（ホスト回路）104の構成例を示す図である。メモリコントローラ104は、リクエスト受信部201、リクエスト処理部202、複数のキュー保持部203a～203e、リクエスト調停部204、及びリクエスト発行部20

50

9を有する。リクエスト調停部 204は、リクエスト選択部 205、調停制御部 206及びリクエスト抑止制御部 207を有する。リクエスト抑止制御部 207は、カウンタ 208を有する。メモリコントローラ 104は、キャッシュ回路 103からアクセス要求のパケットを受信し、受信したパケットの調停を行い、アクセス要求のパケットPKをメインメモリ 105に送信する。その際、メモリコントローラ 104は、メインメモリ 105の資源の残数 をメインメモリ 105から受信し、アクセス要求の調停を行う。

#### 【0014】

図3は、図1のメインメモリ(リモート回路) 105の構成例を示す図である。メインメモリ 105は、アクセス要求のパケットPKの受信処理の資源に限りがあるため、資源の空きを待って、アクセス要求のパケットPKの受信処理を行う。プロセッサ 101は、

10 メインメモリ 105の資源の残数が足りない場合には、アクセス要求の送信が待たされることにより、スループットが低下してしまう。

#### 【0015】

メインメモリ 105は、受信パケットクロックドメイン 301及びメモリクロックドメイン 302を有する。受信パケットクロックドメイン 301及びメモリクロックドメイン 302は、クロック乗り換え回路を構成する。受信パケットクロックドメイン 301は、複数のフリップフロップ回路 303、書き込みポインタ記憶部 304及び資源カウンタ回路 305を有し、受信パケットPKの周波数と同じ第1のクロック信号に同期して動作する。メモリクロックドメイン 302は、読み出し回路 306及び読み出しポインタ記憶部 307を有し、メインメモリ 105の動作クロック信号である第2のクロック信号に同期して動作する。第2のクロック信号は、第1のクロック信号とは異なる周波数のクロック信号である。すなわち、受信パケットPKのクロック周波数と、メインメモリ 105の内部のクロック周波数とが異なる。クロック乗り換え回路は、第1のクロック信号に同期するパケットPKを第2のクロック信号に同期するパケットに変換する。

20

#### 【0016】

複数のフリップフロップ回路 303は、ファーストイントファーストアウト(FIFO)のバッファを構成し、受信したアクセス要求のパケットPKを保持する。アクセス要求のパケットPKの長さにより、保持に必要なフリップフロップ回路 303の数が異なる。パケットPKの長さが長いほど、多くのフリップフロップ回路 303を必要とする。パケットPKは、第1のクロック信号に同期して、複数のフリップフロップ回路 303内において、書き込みポインタ記憶部 304に記憶されている書き込みポインタが示すアドレスに書き込まれる。書き込み後、書き込みポインタ記憶部 304内の書き込みポインタはインクリメントされる。フリップフロップ回路 303に保持されているパケットPKは、メインメモリ 105内で処理するために読み出される。具体的には、読み出し回路 306は、複数のフリップフロップ回路 303において、読み出しポインタ記憶部 307に記憶されている読み出しポインタが示すアドレスのデータを第2のクロック信号に同期して読み出す。読み出し後、読み出しポインタ記憶部 307内の読み出しポインタはインクリメントされる。

#### 【0017】

以上の動作により、クロック乗り換え回路は、パケットPKの周波数で受信したデータをメインメモリ 105の内部のクロック周波数のデータに変換することができる。ここで、もし第1のクロック信号が第2のクロック信号よりも高速な周波数である場合、書き込む速度が読み出す速度よりも速いため、データを保持しているフリップフロップ回路 303が足りなくなり、いずれデータが上書きされてしまう。これを防ぐため、資源カウンタ回路 305は、書き込みポインタ記憶部 304内の書き込みポインタと読み出しポインタ記憶部 307内の読み出しポインタとの差を、未使用的フリップフロップ回路(資源) 303の残数 としてメモリコントローラ 104に送信する。すなわち、メインメモリ 105の資源の残数 は、メインメモリ 105内のクロック乗り換え回路がアクセス要求のパケットPKを記憶する複数のフリップフロップ回路 303のうちの未使用的フリップフロップ回路 303の数である。メインメモリ 105は、資源の残数 をパケットPKの送受

40

50

信に合わせて送信しても良いし、定期的に送信してもよい。なお、メインメモリ 104 の資源は、クロック乗り換え回路のフリップフロップ回路 303 である例を説明したが、これに限定されない。

#### 【0018】

次に、図 2 を参照しながら、メモリコントローラ 104 の制御方法を説明する。リクエスト受信部 201 は、キャッシュ回路 103 からアクセス要求のパケットを受信してリクエスト処理部 202 に出力する。リクエスト処理部 202 は、入力したパケットのパケット長毎に異なるキューホルダ部 203a ~ 203e にパケットを振り分けて保持させ、パケット長毎のパケット受信情報をリクエスト抑止制御部 207 に出力する。キューホルダ部 203a、203b、203c、203d、203e の順で、保持するパケットのパケット長が長くなっている。なお、5 個のキューホルダ部 203a ~ 203e を設ける例を示すが、5 個に限定されない。

10

#### 【0019】

キューホルダ部 203a は、最もパケット長が長い第 1 のパケット長のパケットを保持する。メインメモリ 105 が第 1 のパケット長のパケットを受信処理するには、最も多い第 1 の資源数  $\mu_1$  を必要とする。すなわち、資源の残数  $\mu_1$  が第 1 の資源数  $\mu_1$  以上である場合には、キューホルダ部 203a に保持されている第 1 のパケット長のアクセス要求のパケットをメインメモリ 105 に発行可能である。

#### 【0020】

キューホルダ部 203b は、2 番目にパケット長が長い第 2 のパケット長のパケットを保持する。メインメモリ 105 が第 2 のパケット長のパケットを受信処理するには、2 番目に多い第 2 の資源数  $\mu_2$  を必要とする。すなわち、資源の残数  $\mu_2$  が第 2 の資源数  $\mu_2$  以上である場合には、キューホルダ部 203b に保持されている第 2 のパケット長のアクセス要求のパケットをメインメモリ 105 に発行可能である。

20

#### 【0021】

キューホルダ部 203c は、3 番目にパケット長が長い第 3 のパケット長のパケットを保持する。メインメモリ 105 が第 3 のパケット長のパケットを受信処理するには、3 番目に多い第 3 の資源数  $\mu_3$  を必要とする。すなわち、資源の残数  $\mu_3$  が第 3 の資源数  $\mu_3$  以上である場合には、キューホルダ部 203c に保持されている第 3 のパケット長のアクセス要求のパケットをメインメモリ 105 に発行可能である。

30

#### 【0022】

キューホルダ部 203d は、4 番目にパケット長が長い第 4 のパケット長のパケットを保持する。メインメモリ 105 が第 4 のパケット長のパケットを受信処理するには、4 番目に多い第 4 の資源数  $\mu_4$  を必要とする。すなわち、資源の残数  $\mu_4$  が第 4 の資源数  $\mu_4$  以上である場合には、キューホルダ部 203d に保持されている第 4 のパケット長のアクセス要求のパケットをメインメモリ 105 に発行可能である。

#### 【0023】

キューホルダ部 203e は、5 番目にパケット長が長い第 5 のパケット長のパケットを保持する。メインメモリ 105 が第 5 のパケット長のパケットを受信処理するには、5 番目に多い第 5 の資源数  $\mu_5$  を必要とする。すなわち、資源の残数  $\mu_5$  が第 5 の資源数  $\mu_5$  以上である場合には、キューホルダ部 203e に保持されている第 5 のパケット長のアクセス要求のパケットをメインメモリ 105 に発行可能である。以上より、 $\mu_1 > \mu_2 > \mu_3 > \mu_4 > \mu_5$  の関係を有する。

40

#### 【0024】

リクエスト抑止制御部 207 は、リクエスト処理部 202 から入力するパケット長毎のパケット受信情報を基に、パケット長毎の単位時間当たりの受信数 1 ~ 5 を演算する。受信数 1 は、キューホルダ部 203a に保持される第 1 のパケット長のパケットの単位時間当たりの受信数である。受信数 2 は、キューホルダ部 203b に保持される第 2 のパケット長のパケットの単位時間当たりの受信数である。受信数 3 は、キューホルダ部 203c に保持される第 3 のパケット長のパケットの単位時間当たりの受信数である。受信数 50

4は、キュー保持部203dに保持される第4のパケット長のパケットの単位時間当たりの受信数である。受信数5は、キュー保持部203eに保持される第5のパケット長のパケットの単位時間当たりの受信数である。なお、受信数1～5は、レジスタ等により、ユーザが自由に設定できるようにしてもよい。

#### 【0025】

また、リクエスト抑止制御部207は、パケット長毎の発行限度数L1～L5を演算する。第1の発行限度数L1は、キュー保持部203aに保持されている第1のパケット長のパケットの発行限度数であり、次式により演算される。ここで、Taは、定数である。

$$L_1 = (Ta \times 1) / (1 + 2 + 3 + 4 + 5)$$

#### 【0026】

第2の発行限度数L2は、キュー保持部203bに保持されている第2のパケット長のパケットの発行限度数であり、次式により演算される。

$$L_2 = (Ta \times 2) / (1 + 2 + 3 + 4 + 5)$$

#### 【0027】

第3の発行限度数L3は、キュー保持部203cに保持されている第3のパケット長のパケットの発行限度数であり、次式により演算される。

$$L_3 = (Ta \times 3) / (1 + 2 + 3 + 4 + 5)$$

#### 【0028】

第4の発行限度数L4は、キュー保持部203dに保持されている第4のパケット長のパケットの発行限度数であり、次式により演算される。

$$L_4 = (Ta \times 4) / (1 + 2 + 3 + 4 + 5)$$

#### 【0029】

第5の発行限度数L5は、キュー保持部203eに保持されている第5のパケット長のパケットの発行限度数であり、次式により演算される。

$$L_5 = (Ta \times 5) / (1 + 2 + 3 + 4 + 5)$$

ここで、発行限度数L1～L5は、それぞれ、1より小さい場合は1に設定される。

#### 【0030】

初期時、メインメモリ105のフリップフロップ回路303は使用されていないので、資源の残数は最大値になる。この場合、 $\mu_1$ であるので、調停制御部206は、キュー保持部203a～203eが出力するパケットのヘッダ内の時間情報を基に、各キュー保持部203a～203eの先頭のパケットの中で最も古いアクセス要求のパケットの選択信号をリクエスト選択部205に出力し、リクエスト発行情報をリクエスト抑止制御部207に出力する。リクエスト選択部205は、選択信号を基に、各キュー保持部203a～203eの先頭のパケットの中で最も古いアクセス要求のパケットを選択してリクエスト発行部209に出力する。リクエスト発行部209は、選択されたアクセス要求のパケットPKをメインメモリ105に発行する。選択されたパケットは、キュー保持部から削除され、次のパケットについて、上記の処理が繰り返される。

#### 【0031】

次に、 $\mu_1$ になると、カウンタ208は、調停制御部206から入力したリクエスト発行情報を基に、パケット長毎の発行数C1～C5のカウントを開始する。第1の発行数C1は、リクエスト選択部204及びリクエスト発行部209により発行されたキュー保持部203aのアクセス要求のパケットの数である。第2の発行数C2は、リクエスト選択部204及びリクエスト発行部209により発行されたキュー保持部203bのアクセス要求のパケットの数である。第3の発行数C3は、リクエスト選択部204及びリクエスト発行部209により発行されたキュー保持部203cのアクセス要求のパケットの数である。第4の発行数C4は、リクエスト選択部204及びリクエスト発行部209により発行されたキュー保持部203dのアクセス要求のパケットの数である。第5の発行アクセス要求数C5は、リクエスト選択部204及びリクエスト発行部209により発行されたキュー保持部203eのアクセス要求のパケットの数である。

#### 【0032】

10

20

30

40

50

リクエスト抑止制御部 207 は、第1の発行数 C1 が第1の限度数 L1 より大きくなつた場合には、キュー保持部 203a に発行抑止信号を出力する。キュー保持部 203a は、発行抑止信号を入力すると、内部のアクセス要求のパケットの発行を抑止する。

#### 【0033】

また、リクエスト抑止制御部 207 は、第2の発行数 C2 が第2の限度数 L2 より大きくなつた場合には、キュー保持部 203b に発行抑止信号を出力する。キュー保持部 203b は、発行抑止信号を入力すると、内部のアクセス要求のパケットの発行を抑止する。

#### 【0034】

また、リクエスト抑止制御部 207 は、第3の発行数 C3 が第3の限度数 L3 より大きくなつた場合には、キュー保持部 203c に発行抑止信号を出力する。キュー保持部 203c は、発行抑止信号を入力すると、内部のアクセス要求のパケットの発行を抑止する。

#### 【0035】

また、リクエスト抑止制御部 207 は、第4の発行数 C4 が第4の限度数 L4 より大きくなつた場合には、キュー保持部 203d に発行抑止信号を出力する。キュー保持部 203d は、発行抑止信号を入力すると、内部のアクセス要求のパケットの発行を抑止する。

#### 【0036】

また、リクエスト抑止制御部 207 は、第5の発行数 C5 が第5の限度数 L5 より大きくなつた場合には、キュー保持部 203e に発行抑止信号を出力する。キュー保持部 203e は、発行抑止信号を入力すると、内部のアクセス要求のパケットの発行を抑止する。

#### 【0037】

カウンタ 208 は、 $\mu_1$  になると、発行数 C1 ~ C5 をそれぞれ「0」にリセットする。

#### 【0038】

調停制御部 206 は、 $\mu_1$  である場合、発行が抑止されていないキュー保持部 203a ~ 203e であり、かつ 以下の資源数  $\mu_1$  ~  $\mu_5$  を持つキュー保持部 203a ~ 203e の中で、最も古いアクセス要求のパケットの選択信号をリクエスト選択部 205 に出力し、リクエスト発行情報をリクエスト抑止制御部 207 に出力する。リクエスト選択部 205 は、選択信号を基に、上記の最も古いアクセス要求のパケットを選択してリクエスト発行部 209 に出力する。リクエスト発行部 209 は、選択されたアクセス要求のパケット PK をメインメモリ 105 に発行する。選択されたパケットは、キュー保持部から削除され、次のパケットについて、上記の処理が繰り返される。上記のように、発行数 C1 ~ C5 がそれぞれ限度数 L1 ~ L5 より大きくなつた場合には、それぞれの発行抑止信号を出力することにより、各パケット長のパケットの発行数を平均化することができる。

#### 【0039】

なお、すべてのキュー保持部 203a ~ 203e の中で発行可能なアクセス要求のパケットがない場合は、アクセス要求のパケットの発行が行われない。この待機時間により、メインメモリ 105 の資源の空きが発生し、資源の残数 が徐々に増加していく。

#### 【0040】

また、リクエスト抑止制御部 207 は、パケット長毎に、一定時間パケットが選択されなかつた場合には、優先度を上げることができる。この場合、調停制御部 206 は、一定時間パケットが選択されず、優先度を上げたパケット長のパケットの属するキュー保持部 203a ~ 203e を優先して選択する。また、調停制御部 206 は、資源の残数 により、そのキュー保持部 203a ~ 203e のパケットが選択できない場合は、資源の残数 が資源数  $\mu_1$  ~  $\mu_5$  以上になるまで、パケットの発行を抑止する。

#### 【0041】

上記の定数 Ta は、レジスタ等でユーザにより自由に設定できる。定数 Ta が大きければ、アクセス要求のパケットの発行の空き時間が最短となり、スループットが最大となる。ただし、長時間発行されないアクセス要求のパケットが存在する恐れがあり、最大レイテンシが大きくなってしまう。これに対し、定数 Ta が小さければ、短期的に全てのキュー保持部 203a ~ 203e のアクセス要求のパケットを発行しようとするため、最大レ

10

20

30

40

50

イテンシは小さくなるが、アクセス要求のパケット発行を待たせる時間が多くなるため、スループットは小さくなる。

#### 【0042】

以上のように、複数のキュー保持部 203a～203e は、アクセス要求のパケットの長さ毎にアクセス要求のパケットを保持する。調停部 204 は、メインメモリ 105 の資源の残数 に応じて、複数のキュー保持部 203a～203e に保持されているアクセス要求のパケットのいずれかを選択してメインメモリ 105 に発行する。

#### 【0043】

メインメモリ 105 は、アクセス要求のパケット P K の長さが長いほど多くの資源を必要とする。調停部 204 は、メインメモリ 105 の資源の残数 以下の資源を必要とする長さのアクセス要求のパケットを選択してメインメモリ 105 に発行する。

10

#### 【0044】

カウンタ 208 は、アクセス要求のパケットの長さ毎の発行数 C1～C5 をカウントする。調停部 204 は、アクセス要求のパケットの長さ毎の発行数 C1～C5 に応じて、複数のキュー保持部 203a～203e に保持されているアクセス要求のパケットのいずれかを選択してメインメモリ 105 に発行する。

#### 【0045】

仮に、メモリコントローラ 104 が、一律にアクセス要求のパケットを受信した順番でパケットを発行すると、メインメモリ 105 の資源不足により、パケット発行が待たされ、スループットが小さくなってしまう。本実施形態によれば、メインメモリ 105 の資源不足の場合には、後続の発行可能なアクセス要求のパケットを先に発行するため、全体的に、スループットを向上させることができる。

20

#### 【0046】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されなければならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【符号の説明】

#### 【0047】

|           |                |    |

|-----------|----------------|----|

| 101       | プロセッサ          | 30 |

| 102       | プロセッサコア        |    |

| 103       | キャッシュ回路        |    |

| 104       | メモリコントローラ      |    |

| 105       | メインメモリ         |    |

| 201       | リクエスト受信部       |    |

| 202       | リクエスト処理部       |    |

| 203a～203e | キュー保持部         |    |

| 204       | リクエスト調停部       |    |

| 205       | リクエスト選択部       |    |

| 206       | 調停制御部          | 40 |

| 207       | リクエスト抑止制御部     |    |

| 208       | カウンタ           |    |

| 209       | リクエスト発行部       |    |

| 301       | 受信パケットクロックドメイン |    |

| 302       | メモリクロックドメイン    |    |

| 303       | フリップフロップ回路     |    |

| 304       | 書き込みポインタ記憶部    |    |

| 305       | 資源カウンタ回路       |    |

| 306       | 読み出し回路         |    |

| 307       | 読み出しポインタ記憶部    | 50 |

【 図 1 】

【図2】

【 図 3 】

---

フロントページの続き

(72)発明者 相原 正寿

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 須賀 誠

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

審査官 後藤 彰

(56)参考文献 特表2015-508546(JP,A)

国際公開第2013/107393(WO,A1)

特開2003-337741(JP,A)

特開平10-307747(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 00

G 06 F 13 / 38