US 20160351576A1

(19) **United States**

(12) **Patent Application Publication**

**YAMAZAKI et al.**

(10) **Pub. No.: US 2016/0351576 A1**

(43) **Pub. Date: Dec. 1, 2016**

(54) **SEMICONDUCTOR DEVICE**

(71) Applicant: **Semiconductor Energy Laboratory Co., Ltd.**, Atsugi-shi (JP)

(72) Inventors: **Shunpei YAMAZAKI**, Setagaya (JP); **Tomoaki ATSUMI**, Hadano (JP); **Yuta ENDO**, Atsugi (JP)

(21) Appl. No.: **15/159,021**

(22) Filed: **May 19, 2016**

(30) **Foreign Application Priority Data**

May 26, 2015 (JP) ..... 2015-106145

**Publication Classification**

(51) **Int. Cl.**

**H01L 27/115** (2006.01)

**H01L 29/24** (2006.01)

**H01L 29/10** (2006.01)

(52) **U.S. Cl.**

CPC ..... **H01L 27/1157** (2013.01); **H01L 27/11582** (2013.01); **H01L 27/11573** (2013.01); **H01L 29/1037** (2013.01); **H01L 29/24** (2013.01)

(57)

**ABSTRACT**

A highly integrated semiconductor device is provided. The semiconductor device includes a substrate, a prism-like insulator, a memory cell string including a plurality of transistors connected in series. The prism-like insulator is provided over the substrate. The memory cell string is provided on the side surface of the prism-like insulator. The plurality of transistors each include a gate insulator and a gate electrode. The gate insulator includes a first insulator, a second insulator, and a charge accumulation layer. The charge accumulation layer is positioned between the first insulator and the second insulator.

FIG. 1A

FIG. 2A

FIG. 2B

FIG. 3A

Block storing data to be deleted

(data "1" written)

BGL=V<sub>E</sub>

FIG. 3B

Block from which data is not deleted

BGL=V<sub>E</sub>

FIG. 4

Writing operation 1

FIG. 5

Writing operation 2

FIG. 6

## Writing operation 2n

FIG. 7

Reading operation 1

FIG. 8

Reading operation 2

FIG. 9

Reading operation 2n

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14A

FIG. 14B

FIG. 14C

FIG. 14D

FIG. 14E

FIG. 15A

FIG. 15B

FIG. 15C

FIG. 15D

FIG. 15E

FIG. 16A

FIG. 16B

FIG. 16C

FIG. 16D

FIG. 17A

FIG. 17B

FIG. 18

## SEMICONDUCTOR DEVICE

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The present invention relates to, for example, a semiconductor, a transistor, and a semiconductor device. The present invention relates to, for example, a method for manufacturing a semiconductor, a transistor, and a semiconductor device. The present invention relates to, for example, a semiconductor, a display device, a light-emitting device, a lighting device, a power storage device, a memory device, a processor, and an electronic device. The present invention relates to a method for manufacturing a semiconductor, a display device, a liquid crystal display device, a light-emitting device, a memory device, and an electronic device. The present invention relates to a driving method of a semiconductor device, a display device, a liquid crystal display device, a light-emitting device, a memory device, and an electronic device.

[0003] Note that one embodiment of the present invention is not limited to the above technical field. The technical field of one embodiment of the invention disclosed in this specification and the like relates to an object, a method, or a manufacturing method. In addition, one embodiment of the present invention relates to a process, a machine, manufacture, or a composition of matter.

[0004] In this specification and the like, a semiconductor device generally means a device that can function by utilizing semiconductor characteristics. A display device, a light-emitting device, a lighting device, an electro-optical device, a semiconductor circuit, and an electronic device include a semiconductor device in some cases.

[0005] 2. Description of the Related Art

[0006] A memory device including a semiconductor has attracted attention as a high capacity memory device included in a computer and the like. In particular, it has been known that the integration degree of a NAND flash memory is easily heightened because the NAND flash memory has a small number of wirings or electrodes per memory cell. Storage capacity has been increased year by year because of realization of technology such as multivalued memory. In recent years, two-dimensional memory cell arrangement has approached limits on higher integration and is being replaced with technology of three-dimensional memory cell arrangement (see Patent Document 1).

### REFERENCE

#### Patent Document

[Patent Document 1] Japanese Published Patent Application No. 2011-96340

### SUMMARY OF THE INVENTION

[0007] An object is to provide a highly integrated semiconductor device. Another object is to provide a semiconductor device with three-dimensional memory cell arrangement. Another object is to provide a semiconductor device with large storage capacity. Another object is to provide a semiconductor device with a long retention period.

[0008] Another object is to provide a module including any of the above semiconductor devices. Another object is to provide an electronic device including any of the above semiconductor devices or the module. Another object is to

provide a novel semiconductor device. Another object is to provide a novel module. Another object is to provide a novel electronic device.

[0009] Another object is to provide a transistor having normally-off electrical characteristics. Another object is to provide a transistor having a low leakage current in an off state. Another object is to provide a transistor having a small subthreshold swing value. Another object is to provide a transistor having a small short-channel effect. Another object is to provide a transistor having excellent electrical characteristics. Another object is to provide a transistor having high reliability. Another object is to provide a transistor with high frequency characteristics.

[0010] Note that the descriptions of these objects do not disturb the existence of other objects. In one embodiment of the present invention, there is no need to achieve all the objects. Other objects will be apparent from and can be derived from the description of the specification, the drawings, the claims, and the like.

(1)

[0011] One embodiment of the present invention is a semiconductor device that includes a substrate, a prism-like insulator, a memory cell string including a plurality of transistors connected in series. The prism-like insulator is provided over the substrate, and the memory cell string is provided on the side surface of the prism-like insulator.

(2)

[0012] One embodiment of the present invention is a semiconductor device that includes a substrate, a prism-like insulator, a plurality of memory cell strings. The plurality of memory cell strings each comprise a plurality of transistors connected in series. The prism-like insulator is provided over the substrate, and the plurality of memory cell strings each are provided on a side surface of the prism-like insulator.

(3)

[0013] One embodiment of the present invention is the semiconductor device according to (1) or (2), in which the plurality of transistors each include a gate insulator and a gate electrode, the gate insulator includes a first insulator, a second insulator, and a charge accumulation layer, and the charge accumulation layer is positioned between the first insulator and the second insulator.

(4)

[0014] One embodiment of the present invention is the semiconductor device according to any one of (1) to (3), in which the plurality of transistors include an oxide semiconductor.

(5)

[0015] One embodiment of the present invention is the semiconductor device according to (4), in which the oxide semiconductor contains indium, an element M (aluminum, gallium, yttrium, or tin), and zinc.

(6)

[0016] One embodiment of the present invention is the semiconductor device according to any one of (1) to (5) which further includes a first transistor and a second transistor provided over the substrate. A source terminal of the first transistor is electrically connected to a first terminal of the memory cell string and a drain terminal of the second transistor is electrically connected to a second terminal of the memory cell string.

(7)

[0017] One embodiment of the present invention is the semiconductor device according to (6), in which the first transistor and the second transistor include single crystal silicon.

[0018] A highly integrated semiconductor device can be provided. A semiconductor device with three-dimensional memory cell arrangement can be provided. A semiconductor device with large storage capacity can be provided. A semiconductor device with a long retention period can be provided.

[0019] A module including any of the above semiconductor devices can be provided. An electronic device including any of the above semiconductor devices or the module can be provided. A novel semiconductor device can be provided. A novel module can be provided. A novel electronic device can be provided.

[0020] A transistor having normally-off electrical characteristics can be provided. A transistor having a low leakage current in an off state can be provided. A transistor having a small subthreshold swing value can be provided. A transistor having a small short-channel effect can be provided. A transistor having excellent electrical characteristics can be provided. A transistor having high reliability can be provided. A transistor with high frequency characteristics can be provided.

[0021] Note that the description of these effects does not disturb the existence of other effects. One embodiment of the present invention does not necessarily achieve all the effects listed above. Other effects will be apparent from and can be derived from the description of the specification, the drawings, the claims, and the like.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0022] In the accompanying drawings:

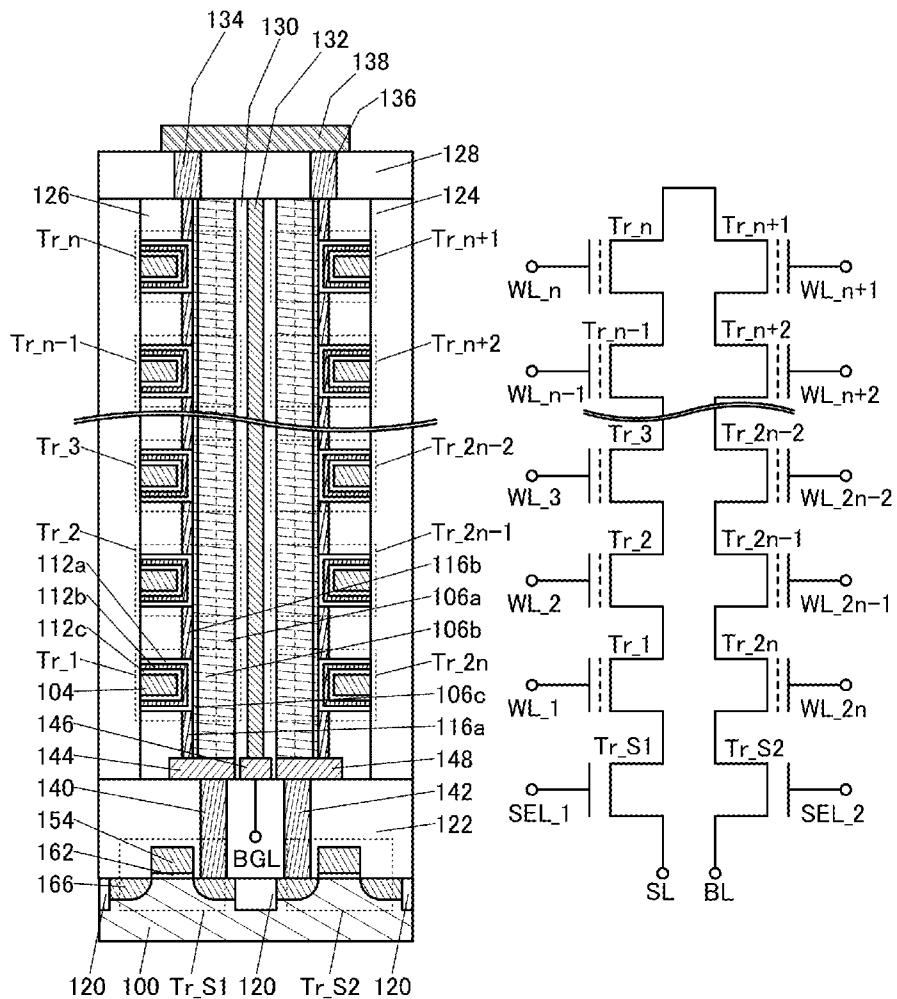

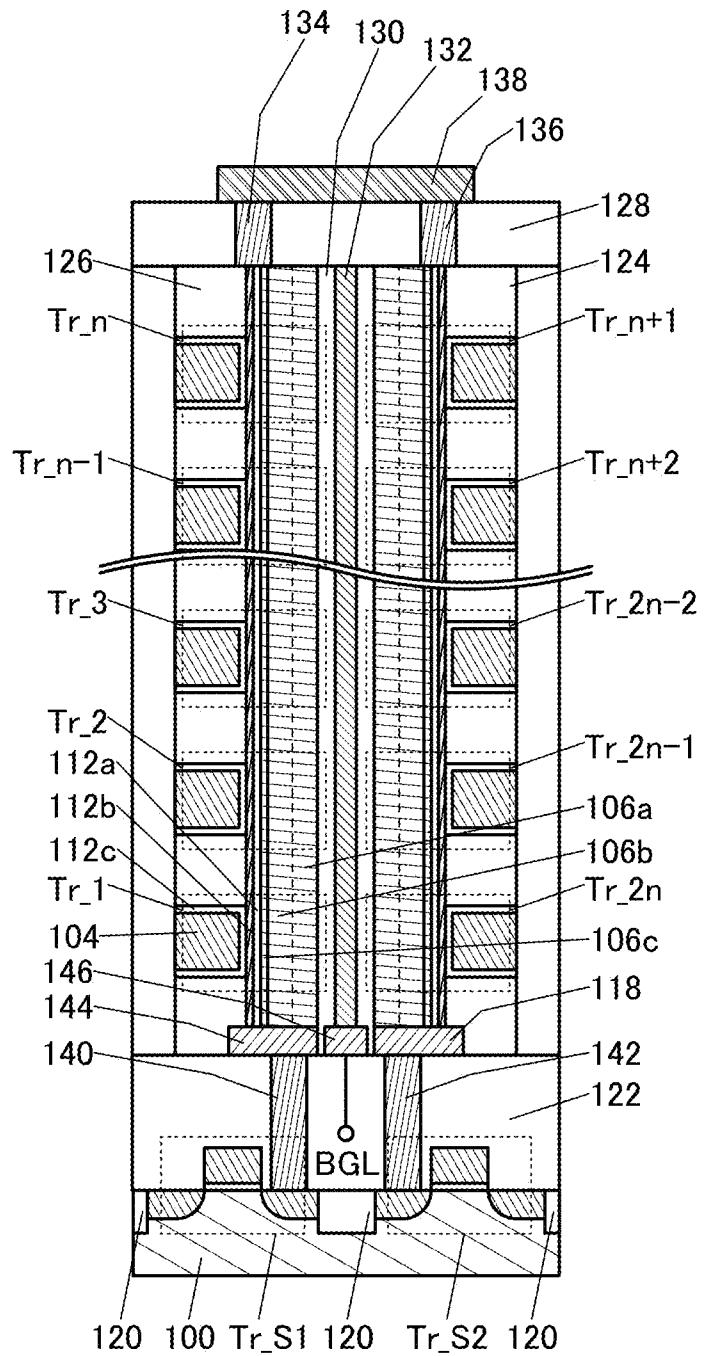

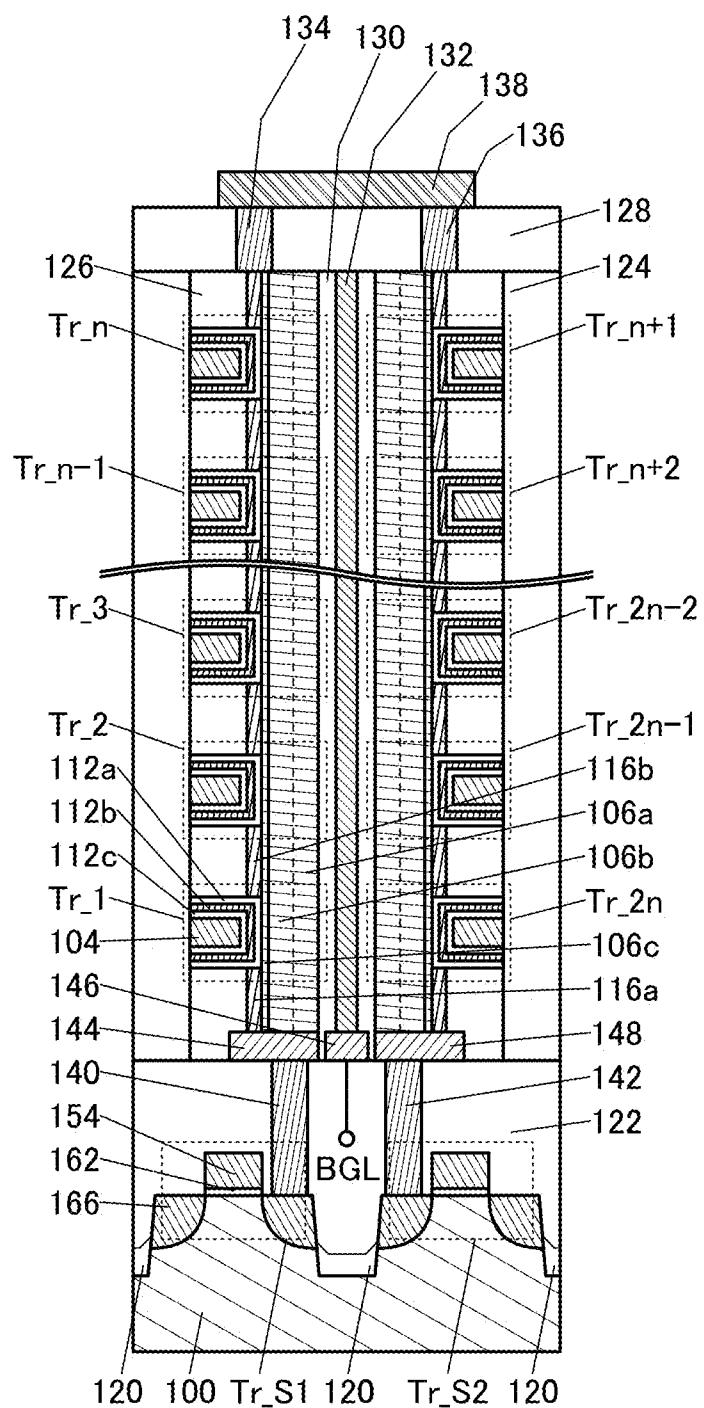

[0023] FIGS. 1A and 1B are a cross-sectional view and a circuit diagram of a semiconductor device of one embodiment of the present invention;

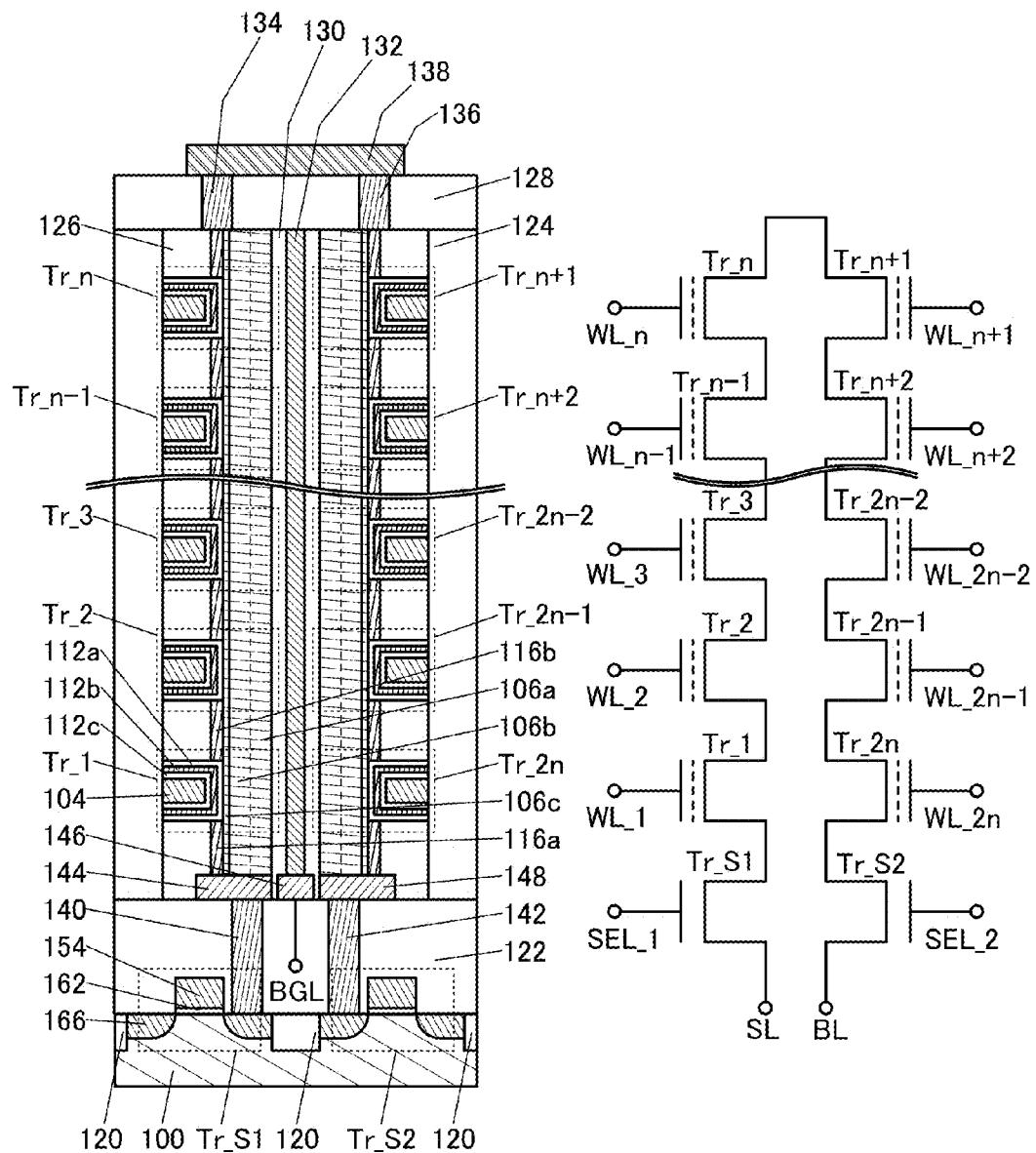

[0024] FIGS. 2A and 2B are a schematic view and a cross-sectional view illustrating operation of a semiconductor device of one embodiment of the present invention;

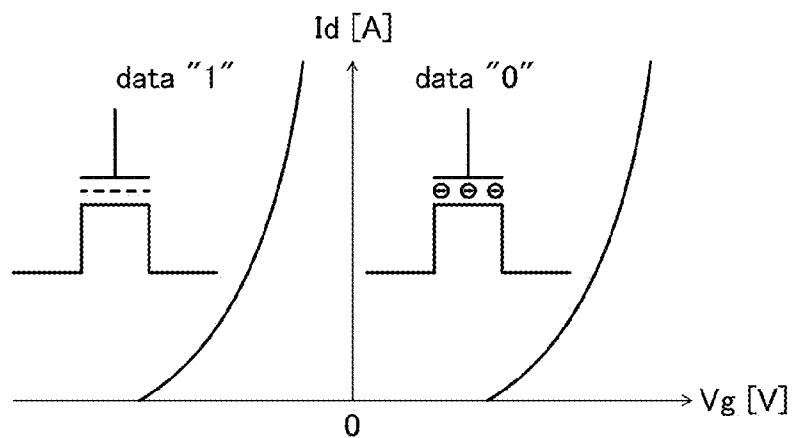

[0025] FIGS. 3A and 3B are circuit diagrams illustrating operation of a semiconductor device of one embodiment of the present invention;

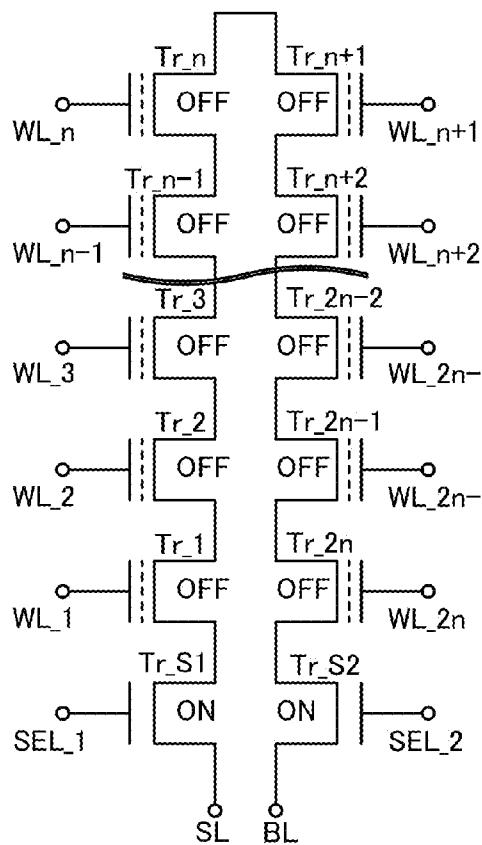

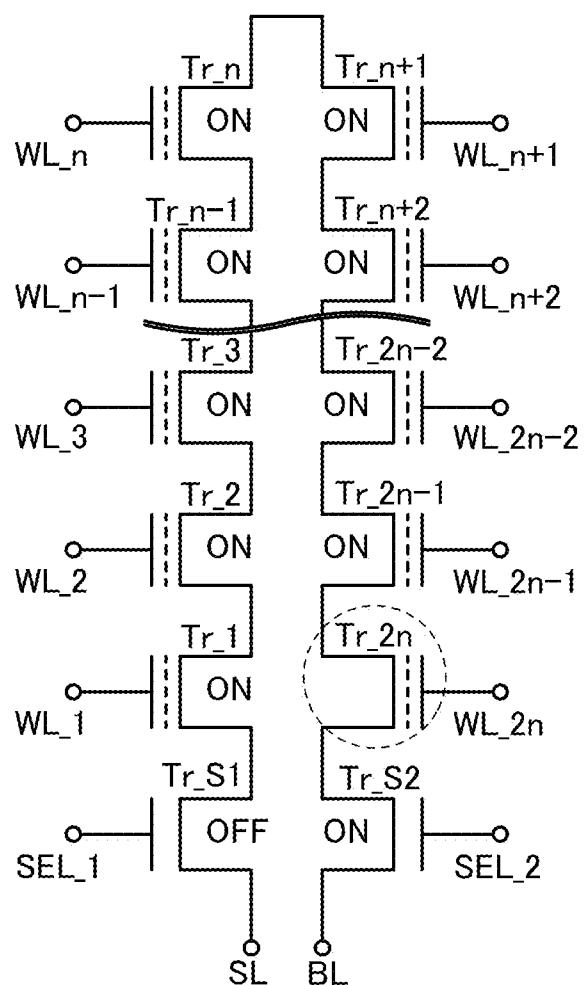

[0026] FIG. 4 is a circuit diagram illustrating operation of a semiconductor device of one embodiment of the present invention;

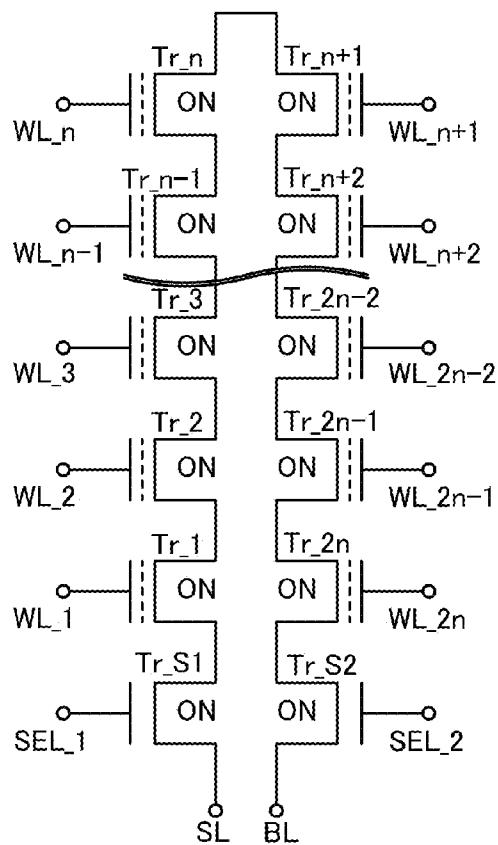

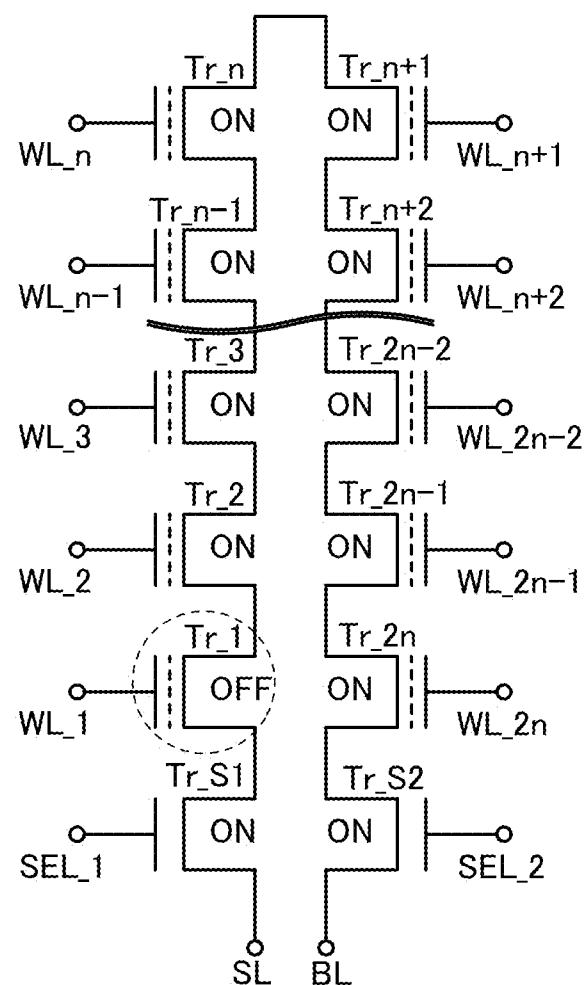

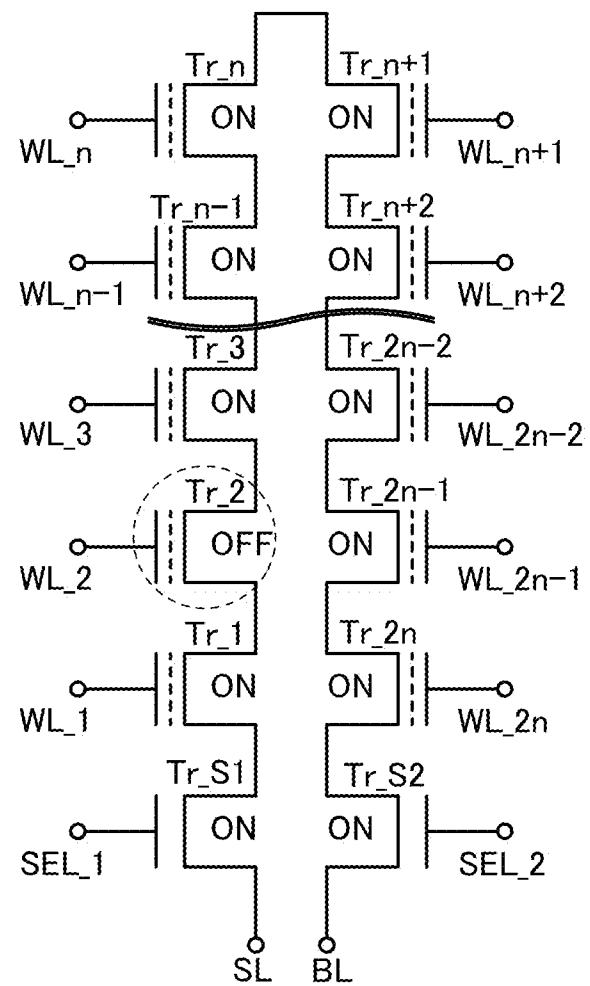

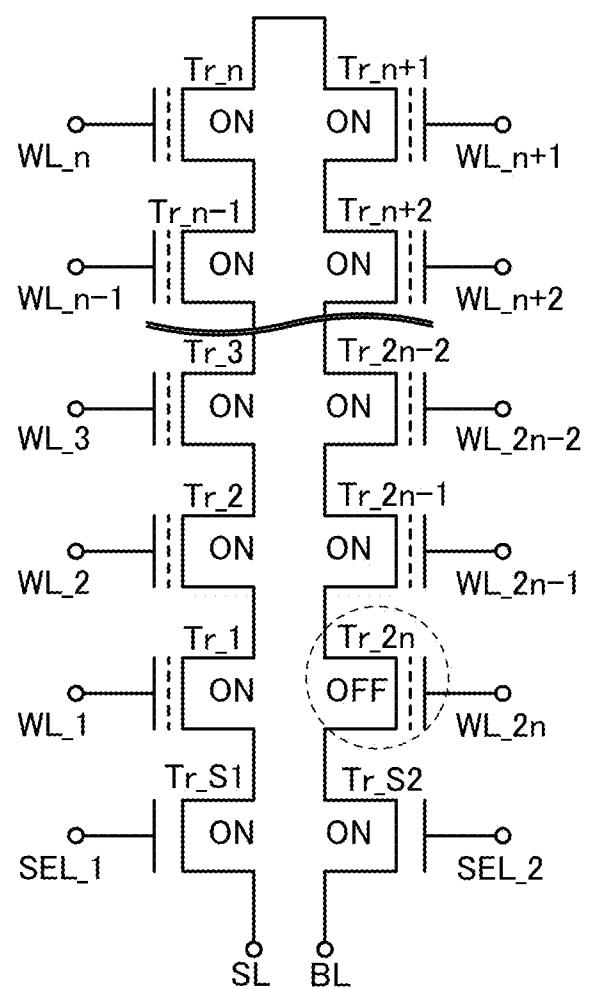

[0027] FIG. 5 is a circuit diagram illustrating operation of a semiconductor device of one embodiment of the present invention;

[0028] FIG. 6 is a circuit diagram illustrating operation of a semiconductor device of one embodiment of the present invention;

[0029] FIG. 7 is a circuit diagram illustrating operation of a semiconductor device of one embodiment of the present invention;

[0030] FIG. 8 is a circuit diagram illustrating operation of a semiconductor device of one embodiment of the present invention;

[0031] FIG. 9 is a circuit diagram illustrating operation of a semiconductor device of one embodiment of the present invention;

[0032] FIG. 10 is a cross-sectional view of a semiconductor device of one embodiment of the present invention;

[0033] FIG. 11 is a cross-sectional view of a semiconductor device of one embodiment of the present invention;

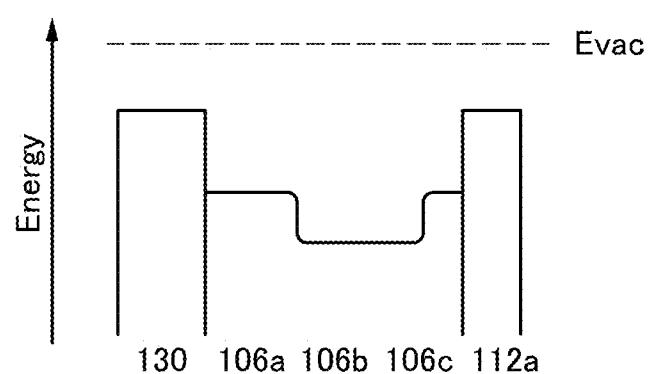

[0034] FIG. 12 is a band diagram of a channel formation region in a transistor of one embodiment of the present invention and its vicinity thereof;

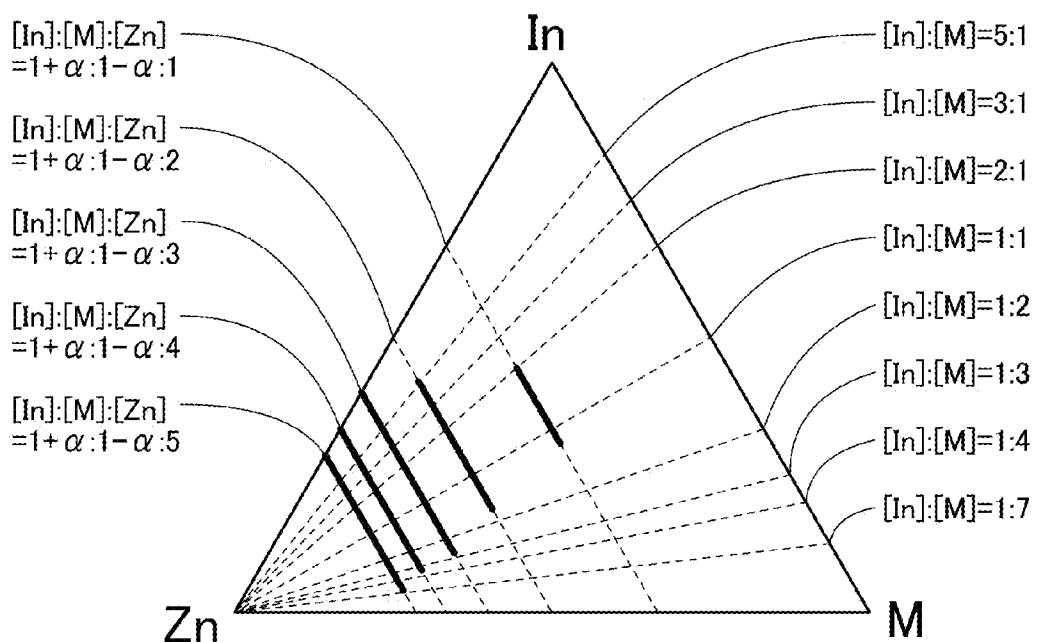

[0035] FIG. 13 is a triangular diagram for explaining composition of an In-M-Zn oxide;

[0036] FIGS. 14A to 14E show structural analysis of a CAAC-OS and a single crystal oxide semiconductor by XRD and selected-area electron diffraction patterns of a CAAC-OS;

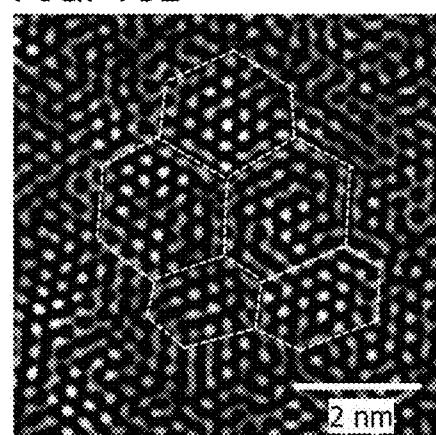

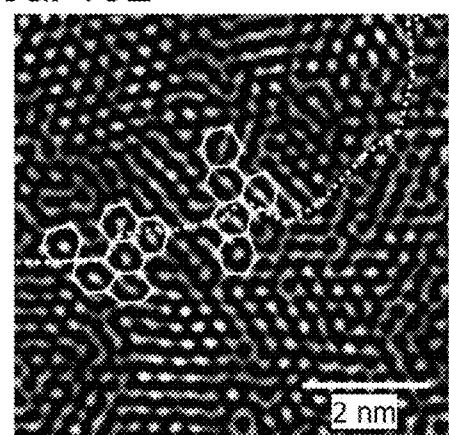

[0037] FIGS. 15A to 15E show a cross-sectional TEM image and plan-view TEM images of a CAAC-OS and images obtained through analysis thereof;

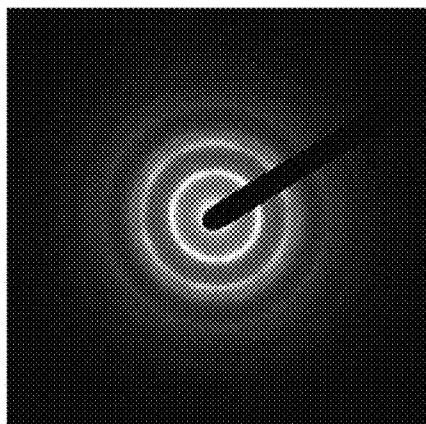

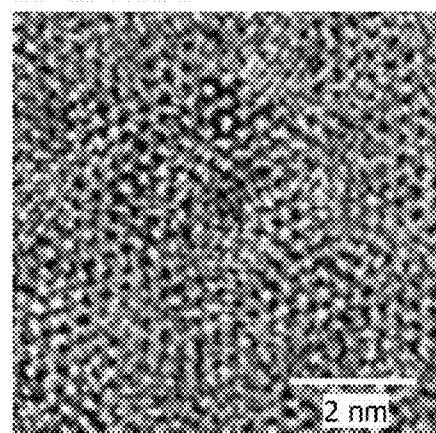

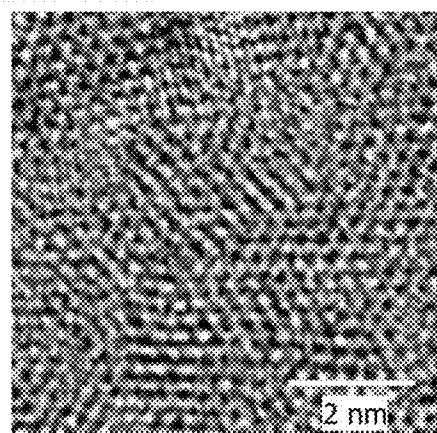

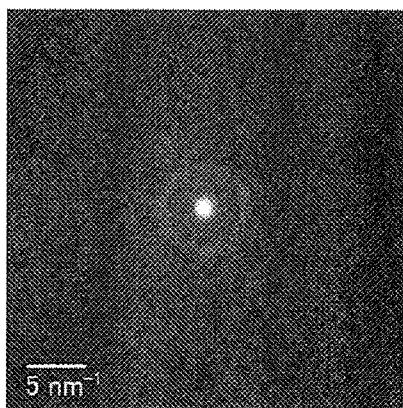

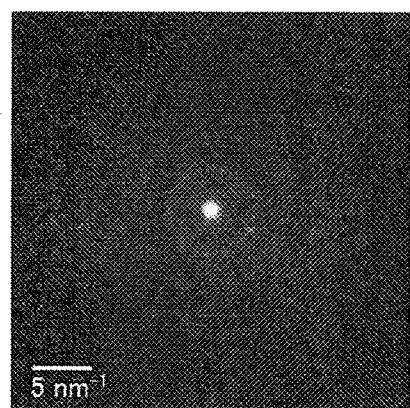

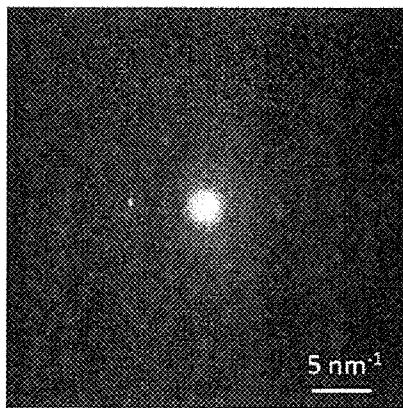

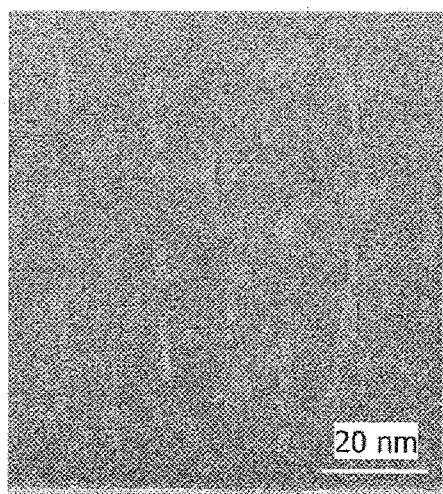

[0038] FIGS. 16A to 16D show electron diffraction patterns and a cross-sectional TEM image of an nc-OS;

[0039] FIGS. 17A and 17B show cross-sectional TEM images of an a-like OS; and

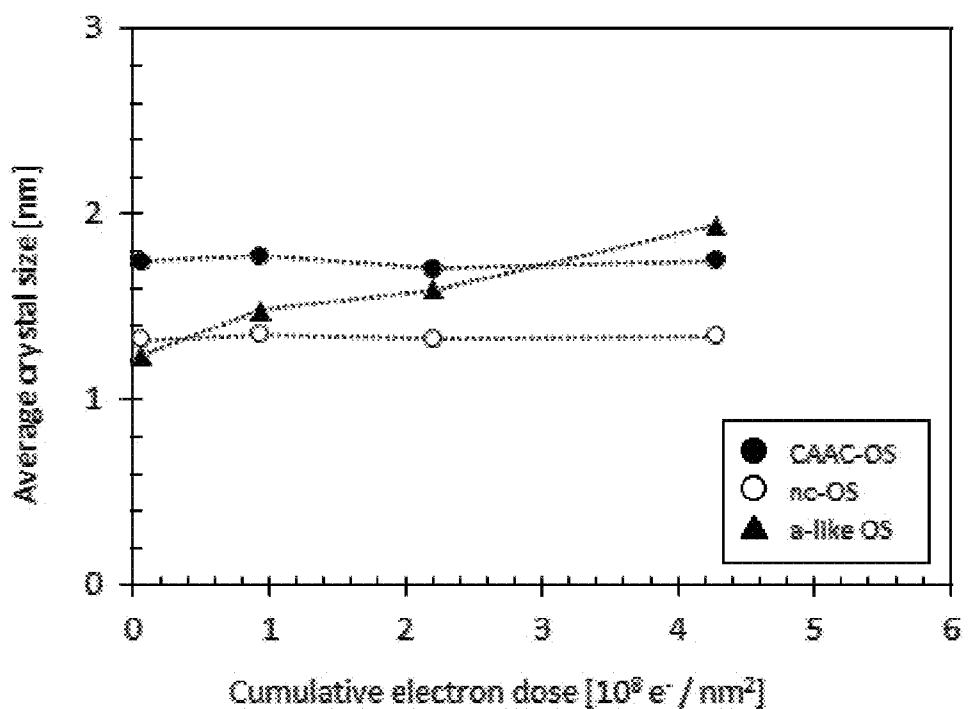

[0040] FIG. 18 shows a change of crystal parts of an In—Ga—Zn oxide owing to electron irradiation.

#### DETAILED DESCRIPTION OF THE INVENTION

[0041] Embodiments of the present invention will be described in detail with reference to the drawings. However, the present invention is not limited to the description below, and it is easily understood by those skilled in the art that modes and details disclosed herein can be modified in various ways. Furthermore, the present invention is not construed as being limited to description of the embodiments. In describing structures of the invention with reference to the drawings, common reference numerals are used for the same portions in different drawings. Note that the same hatched pattern is applied to similar parts, and the similar parts are not especially denoted by reference numerals in some cases.

[0042] Note that the size, the thickness of films (layers), or regions in drawings is sometimes exaggerated for simplicity.

[0043] In this specification, the terms "film" and "layer" can be interchanged with each other.

[0044] A voltage usually refers to a potential difference between a given potential and a reference potential (e.g., a source potential or a ground potential (GND)). A voltage can be referred to as a potential and vice versa. In general, a potential (a voltage) is relative and is determined depending on the difference relative to a reference potential. Therefore, even a "ground potential," for example, is not necessarily 0 V. For example, in some cases, a "ground potential" is the lowest potential in a circuit. In other cases, a "ground potential" is a moderate potential in a circuit. In those cases, a positive potential and a negative potential are set using the potential as a reference.

[0045] Note that the ordinal numbers such as "first" and "second" are used for convenience and do not denote the order of steps or the stacking order of layers. Therefore, for example, the term "first" can be replaced with the term "second," "third," or the like as appropriate. In addition, the ordinal numbers in this specification and the like do not correspond to the ordinal numbers which specify one embodiment of the present invention in some cases.

[0046] Note that an impurity in a semiconductor refers to, for example, elements other than the main components of the semiconductor. For example, an element with a concentration of lower than 0.1 atomic % is an impurity. When an

impurity is contained, the density of states (DOS) may be formed in a semiconductor, the carrier mobility may be decreased, or the crystallinity may be decreased, for example. In the case where the semiconductor is an oxide semiconductor, examples of an impurity which changes characteristics of the semiconductor include Group 1 elements, Group 2 elements, Group 14 elements, Group 15 elements, and transition metals other than the main components; specifically, there are hydrogen (hydrogen is included in water), lithium, sodium, silicon, boron, phosphorus, carbon, and nitrogen, for example. In the case of an oxide semiconductor, oxygen vacancy may be formed by entry of impurities such as hydrogen. Furthermore, in the case where the semiconductor is silicon, examples of an impurity which changes characteristics of the semiconductor include oxygen, Group 1 elements except hydrogen, Group 2 elements, Group 13 elements, and Group 15 elements.

[0047] Note that in this specification, the description “A has a shape such that an end portion extends beyond an end portion of B” may indicate, for example, the case where at least one of end portions of A is positioned on an outer side than at least one of end portions of B in a top view or a cross-sectional view. Thus, the description “A has a shape such that an end portion extends beyond an end portion of B” can be alternately referred to as the description “one of end portions of A is positioned on an outer side than one of end portions of B in a top view,” for example.

[0048] In this specification, the term “parallel” indicates that the angle formed between two straight lines is greater than or equal to  $-10^\circ$  and less than or equal to  $10^\circ$ , and accordingly also includes the case where the angle is greater than or equal to  $-5^\circ$  and less than or equal to  $5^\circ$ . A term “substantially parallel” indicates that the angle formed between two straight lines is greater than or equal to  $-30^\circ$  and less than or equal 15 to  $30^\circ$ . In addition, the term “perpendicular” indicates that the angle formed between two straight lines is greater than or equal to  $80^\circ$  and less than or equal to  $100^\circ$ , and accordingly also indicates that the angle formed between two straight lines is greater than or equal to  $85^\circ$  and less than or equal to  $95^\circ$ . A term “substantially perpendicular” indicates that the angle formed between two straight lines is greater than or equal to  $60^\circ$  and less than or equal to  $120^\circ$ .

[0049] In this specification, trigonal and rhombohedral crystal systems are included in a hexagonal crystal system.

#### <Semiconductor Device>

[0050] A semiconductor device of one embodiment of the present invention will be described below.

[0051] Note that the transistor is assumed to be of an n-channel type below. However, a term, a reference numeral, or the like may be replaced with an appropriate one in the following description when a p-channel transistor is used.

#### <Structure of Semiconductor Device>

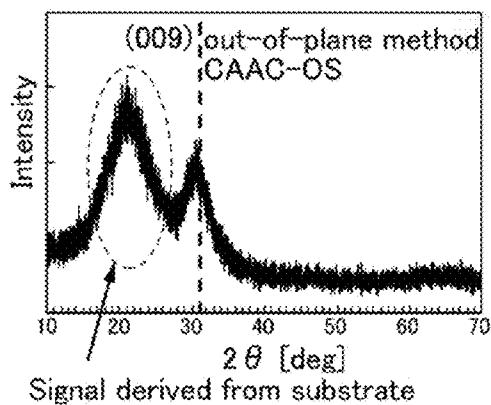

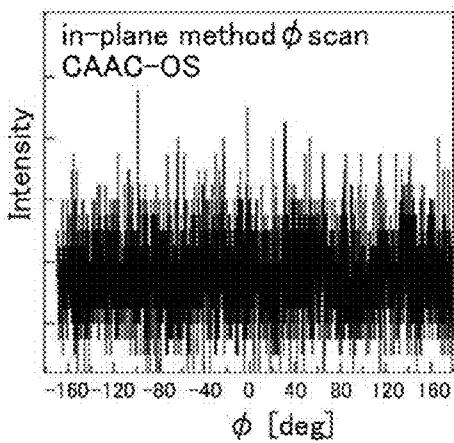

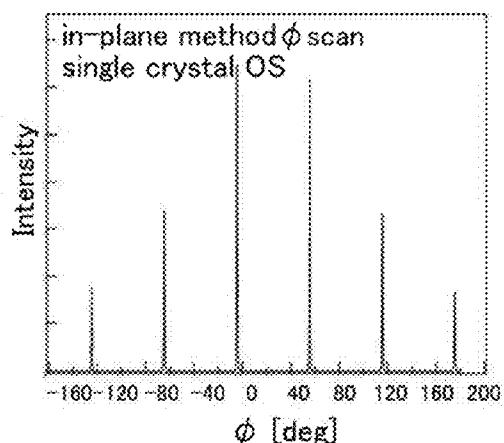

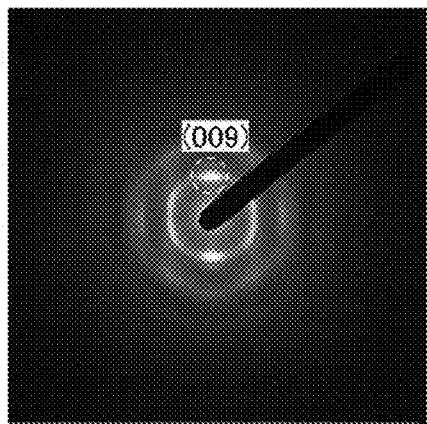

[0052] An example of a structure of a semiconductor device of one embodiment of the present invention is shown below.

[0053] FIG. 1A is a cross-sectional view of a semiconductor device of one embodiment of the present invention. FIG. 1B is a circuit diagram of the semiconductor device in FIG. 1A.

[0054] The semiconductor device in FIG. 1A includes a substrate 100, an insulator 120, an insulator 122, an insulator 124, an insulator 126, an insulator 128, an insulator 130, a conductor 140, a conductor 142, a conductor 144, a conductor 146, a conductor 148, a conductor 132, a conductor 134, a conductor 136, a conductor 138, a transistor Tr\_S1, a transistor Tr\_S2, and transistors Tr\_to Tr\_2n (n is an integer of 2 or more).

[0055] The transistors Tr\_S1 and Tr\_S2 are provided to the substrate 100. Specifically, the transistor Tr\_S includes a pair of impurity regions 166 provided in the substrate 100, a channel formation region placed between the impurity regions 166, a conductor 154 including a region overlapping with the channel formation region, and an insulator 162 placed between the channel formation region and the conductor 154. The conductor 154 has a function as a gate electrode and the insulator 162 has a function as a gate insulator. The conductor 154, which serves as a gate electrode of the transistor Tr\_S1, is electrically connected to a wiring SEL\_1. The conductor 154, which serves as a gate electrode of the transistor Tr\_S2, is electrically connected to a wiring SEL\_2. The transistor Tr\_S2 has the same structure as that of the transistor Tr\_S1, and the description of its structure is omitted; however, the transistor Tr\_S2 may have a different structure. The transistors Tr\_S1 and Tr\_S2 are isolated by the insulator 120. As the element isolation method, a shallow trench isolation (STI) method, a local oxidation of silicon (LOCOS) method, or the like can be used. Note that the structures of the transistors Tr\_S1 and Tr\_S2 are not limited to the structures illustrated in FIG. 1A. For example, a transistor provided over a silicon on insulator (SOI) substrate or a FIN-type transistor may be used.

[0056] The insulator 122 is provided over the transistors Tr\_S1 and Tr\_S2. The insulator 130, and the conductors 144, 146, and 148 are provided over the insulator 122. The insulator 130 has a prism-like shape or a wall-like shape and is provided with the transistors Tr\_1 to Tr\_2n (n is an integer of 2 or more) on the sides thereof. Note that the channel length direction of each of the transistors Tr\_1 to Tr\_n is parallel to the direction perpendicular to a top surface of the substrate and the channel length direction of each of the transistors Tr\_n+1 to Tr\_2n is parallel to the direction perpendicular to the top surface of the substrate. Note that the insulator 130 does not necessarily have a prism-like shape or a wall-like shape, and may be a cylinder shape, for example. One side of the insulator 130 is provided with the transistors Tr\_1 to Tr\_n, and the other side is provided with the transistors Tr\_n+1 to Tr\_2n. The larger n is, the more highly integrated the semiconductor device is. For example, n may be 2, 4, 8, 16, 32, 64, or 128.

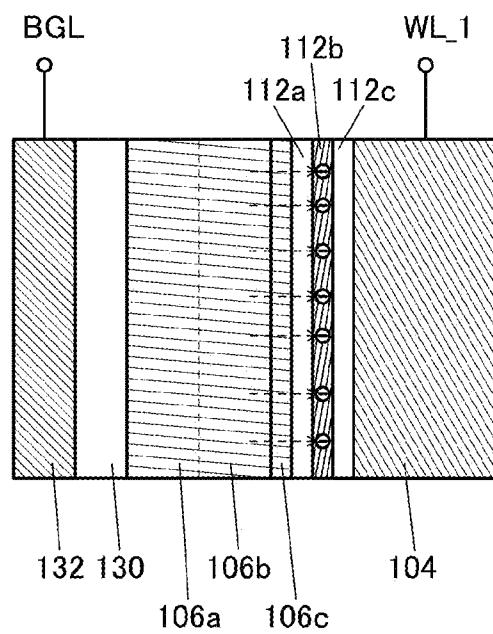

[0057] Note that the conductor 132 has a region facing the transistors Tr\_1 to Tr\_2n with the insulator 130 therebetween. The conductor 132 has a function as a back gate electrode of the transistors Tr\_1 to Tr\_2n (also referred to as a second gate electrode) and is electrically connected to a wiring BGL.

[0058] For example, the transistor Tr\_1 includes an insulator 106a, a semiconductor 106b, an insulator 106c, a conductor 116a, a conductor 116b, an insulator 112a, a charge accumulation layer 112b, an insulator 112c, and a conductor 104. The insulator 106a is provided along the side of the insulator 130. The semiconductor 106b is provided along the side of the insulator 130 with the insulator 106a therebetween. The insulator 106c is provided along the side

of the insulator 130 with the semiconductor 106b and the insulator 106a therebetween. The insulator 112a, the conductor 116a, and the conductor 116b each include a region facing the insulator 130 with the insulator 106c, the semiconductor 106b, and the insulator 106a therebetween. Note that the insulator 112a is placed between the conductor 116a and the conductor 116b. The charge accumulation layer 112b has a region facing the insulator 130 with the insulator 112a, the insulator 106c, the semiconductor 106b, and the insulator 106a therebetween. The insulator 112c has a region facing the insulator 130 with the charge accumulation layer 112b, the insulator 112a, the insulator 106c, the semiconductor 106b, and the insulator 106a therebetween. The conductor 104 has a region facing the insulator 130 with the insulator 112c, the charge accumulation layer 112b, the insulator 112a, the insulator 106c, the semiconductor 106b, and the insulator 106a therebetween.

[0059] Thus, in the transistor Tr\_1, the semiconductor 106b has a function as a channel formation region, the conductor 104 has a function as a gate electrode, the insulator 112a, the charge accumulation layer 112b, and the insulator 112c each have a function as a gate insulator, the conductor 116a has a function as a source electrode, and the conductor 116b has a function as a drain electrode. The insulator 106a and the insulator 106c have functions of reducing the density of defect states at the interfaces between the semiconductor 106b and the insulator 106a and between the semiconductor 106b and the insulator 106c. Combination of materials used for the insulator 106a, the semiconductor 106b, and the insulator 106c will be described later. The conductor 104, which serves as the gate electrode of the transistor Tr\_1, is electrically connected to a wiring WL\_1. Note that the wiring WL\_1 has a function as a word line. Note that the transistor Tr\_1 is not limited to the structure illustrated in FIG. 1A. For example, some components such as the insulators 106a and 106c are not necessarily provided.

[0060] The transistor Tr\_1 includes the charge accumulation layer 112b between the conductor 104 and the semiconductor 106b. Thus, the threshold voltage of the transistor Tr\_1 corresponds to the polarity and amount of charge included in the charge accumulation layer 112b. The threshold voltage of the transistor Tr\_1 can be controlled by the charge accumulation layer 112b; therefore, the transistor Tr\_1 can serve as a memory cell (also referred to as a memory element) which stores data corresponding to the threshold voltage.

[0061] As shown in the left of FIG. 2A, the threshold voltage of the transistor Tr\_1 is negative when electrons are not accumulated in the charge accumulation layer 112b. When electrons are accumulated in the charge accumulation layer 112b as shown in FIG. 2B, the threshold voltage changes to cancel an electric field generated by the electrons, and then the threshold voltage becomes positive as shown in the right of FIG. 2A. That is, the transistor Tr\_1 takes data "1" because it is on when electrons are not accumulated in the charge accumulation layer 112b, and takes data "0" because of non-conduction when electrons are accumulated in the charge accumulation layer 112b. Although the description is about a two-valued memory cell here, a multivalued memory cell of three values or more (such as a four-valued, eight-valued, sixteen-valued, or thirty-two-valued memory cell) may be used. Note that electron injection into the charge accumulation layer 112b will be described later.

[0062] The transistors Tr\_2 to Tr\_2n have the same structures as that of the transistor Tr\_1. Each of the gate electrodes of the transistors Tr\_2 to Tr\_2n is electrically connected to corresponding wirings WL\_2 to WL\_2n. The wirings WL\_2 to WL\_2n each have a function as a word line.

[0063] As described above, the transistors Tr\_1 to Tr\_2n each have a function as a memory cell. The transistors Tr\_1 to Tr\_2n are connected in series; thus, they can be collectively called one memory cell string. Memory cell strings can be arranged in matrix over the substrate 100, for example. Each of the memory cell strings is electrically connected to a selection transistor. Specifically, the memory cell strings are arranged over points of intersection of a plurality of straight lines extending in a first direction and a plurality of straight lines extending in a second direction over the substrate 100. The angle between the first direction and the second direction may be typically 45° or 90°. However, the angle may be in the range of greater than or equal to 10° and less than or equal to 90°, greater than or equal to 30° and less than or equal to 90°, greater than or equal to 45° and less than or equal to 90°, or greater than or equal to 60° and less than or equal to 90°, for example. The arrangement of the memory cell strings is preferably dense, and it depends on the shape of the memory cell strings. A wiring SL and a wiring BL provided along the first direction, for example, can be shared between the memory cell strings formed along the first direction. Note that the arrangement of the memory cell strings is not limited to a matrix arrangement. The wiring SL has a function as a source line. The wiring BL has a function as a bit line.

[0064] The plurality of memory cell strings are collectively called a block. One block is supposed to include  $a \times b$  memory cell strings,  $a$  is the number of memory cell strings in the first direction ( $a$  is a natural number) and  $b$  is the number of memory cell strings in the second direction ( $b$  is a natural number). Note that the blocks may have different numbers of memory cell strings. A rule of how to form the blocks may be determined as appropriate. In a block, the wiring BGL is electrically connected to the conductor 132, for example. The conductors 132 are electrically isolated from the wirings BGL between the blocks. In one block, wirings WL\_1 to WL\_2n provided along the second direction, for example, can be shared between the memory cell strings formed along the second direction. The wirings WL\_1 to WL\_2n may be provided for each of the blocks or may be shared between the blocks arranged along the second direction. Memory cells sharing the wirings WL\_1 to WL\_2n are collectively called a page. Note that the wirings BL and SL can be shared between blocks arranged along the first direction.

[0065] A source terminal of the transistor Tr\_S1 is electrically connected to the wiring SL, and its drain terminal of the transistor Tr\_S1 is electrically connected to a first terminal of the memory cell string. A drain terminal of the transistor Tr\_S2 is electrically connected to the wiring BL, and its source terminal of the transistor Tr\_S2 is electrically connected to a second terminal of the memory cell string. The transistors Tr\_S1 and Tr\_S2 can be called selection transistors because the transistors control conduction or non-conduction between the memory cell string and the wirings.

**[0066]** The operations of writing and reading data to/from the semiconductor device shown in FIGS. 1A and 1B will be described below.

<Reset Operation>

**[0067]** When data is written to each of the memory cells, data is preferably deleted (data “1” is preferably written) in advance of the writing operation. The operation of deleting data is also referred to as a reset operation. The reset operation is performed in each block. For example, a reset operation can be performed in the following manner: a block storing data to be deleted is selected, an erasing potential  $V_E$  (e.g., 15 V) is applied to the wiring BGL electrically connected to the conductor 132, a low potential (a potential such as 0 V, at which the transistors Tr\_1 to Tr\_2n are turned off) is applied to the wirings WL\_1 to WL\_2n, and the transistors Tr\_S1 and Tr\_S2 are turned on as shown in FIG. 3A. Note that when the conductor 132 is not provided, a reset operation can also be performed by an erasing potential  $V_E$  applied to the wirings SL and BL. Electrons stored in the charge accumulation layer 112b of each of the transistors Tr\_1 to Tr\_2n can be extracted through the reset operation.

**[0068]** In a block from which data is not deleted, the electrical connection between the conductor 132 and the wiring BGL is cut off so that an erasing potential  $V_E$  is not to be applied to the conductor 132. Alternatively, as shown in FIG. 3B, a potential such as an erasing potential  $V_E$ , at which the transistors Tr\_1 to Tr\_2n are turned on, may be applied to the wirings WL\_1 to WL\_2n electrically connected to a block from which data is not deleted. That is, the charge accumulation layer 112b is not applied with a difference in potential which leads electron extraction.

**[0069]** Note that data in a memory cell which is not subjected to rewriting is preferably stored in a different region in advance of the reset operation of the block.

<Writing Operation>

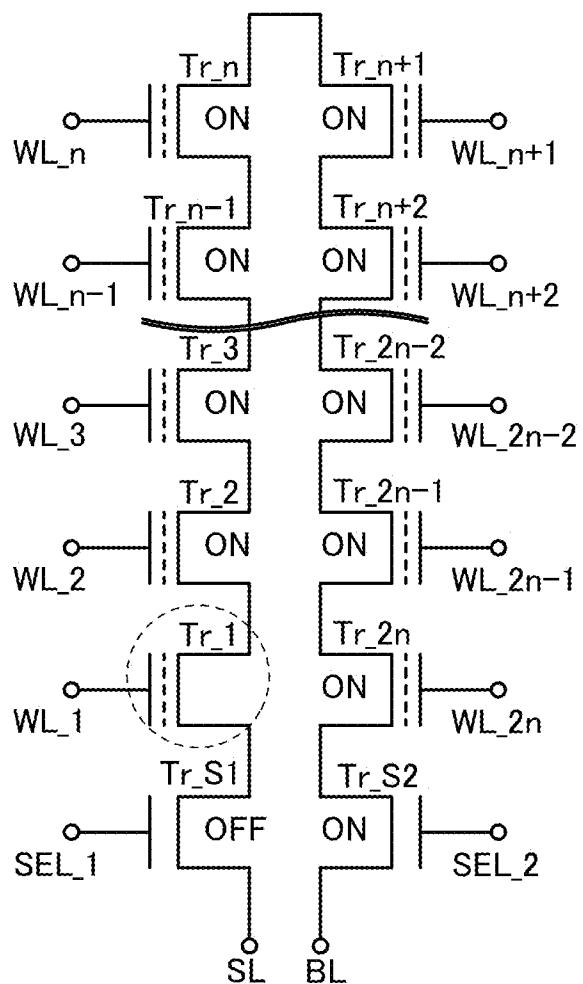

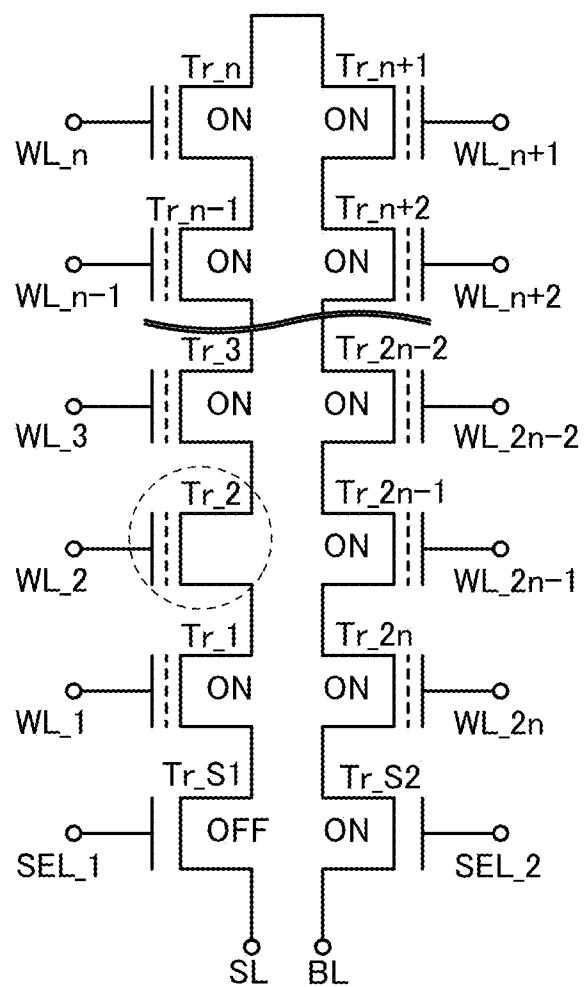

**[0070]** Next, a writing operation of data to each memory cell will be described with reference to FIGS. 4 to 6.

**[0071]** A writing operation of data can be performed for each of the above pages. First, a writing potential (e.g., 15 V) is applied to a word line of a page subjected to writing, and then a positive potential (a potential such as 3 V, at which a transistor is turned on) is applied to a word line of a page which is not subjected to writing. As shown in FIG. 4, a writing potential is applied to the wiring WL\_1 first, and then positive potentials are applied to the wirings WL\_2 to WL\_2n. In addition, the transistor Tr\_S1 electrically connected to the wiring SL is off, and the transistor Tr\_S2 electrically connected to the wiring BL is on. Accordingly, a potential of the wiring BL is applied to the memory cell of the page subjected to writing. Data corresponding to the potential of the wiring BL is written to the memory cell. Specifically, when a potential of the wiring BL is a low potential such as 0 V, electrons are injected into the charge accumulation layer 112b because a difference between the potential of the wiring BL and the writing potential applied to the wiring WL\_1 is increased. When the potential of the wiring BL is a positive potential, electrons are not injected into the charge accumulation layer 112b because a difference between the potential of the wiring BL and the writing potential applied to the wiring WL\_1 is decreased. That is, data “0” is written to the memory cell when a low potential

is applied to the wiring BL, and the memory cell keeps data “1” when a positive potential is applied.

**[0072]** Data writing can be performed page by page in such a manner that each of the wirings BL is applied with a potential required in the corresponding memory cell string. As shown in FIGS. 5 and 6, the same data writing is performed also for the wirings WL\_2 to WL\_2n, so that data writing can be performed for the block or the whole of the semiconductor device.

**[0073]** Note that data other than the data “0” or data “1” can also be written to the memory cell. For example, the amount of electrons injected into the charge accumulation layer 112b can be controlled on the basis of a potential of the wiring BL or the like or a potential applying period.

<Reading Operation>

**[0074]** Next, a reading operation of data written in each memory cell will be described with reference to FIGS. 7 to 9.

**[0075]** A reading operation of data can also be performed for each of the pages. First, a low potential such as 0 V is applied to a word line of a page subjected to reading, and then a positive potential (a potential such as 3 V, at which a transistor is turned on) is applied to a word line of a page which is not subjected to reading. As shown in FIG. 7, a low potential is applied to the wiring WL\_1 first, and then positive potentials are applied to the wirings WL\_2 to WL\_2n. In addition, the transistor Tr\_S1 electrically connected to the wiring SL and the transistor Tr\_S2 electrically connected to the wiring BL are on. A reading potential such as 1 V is applied to the wiring BL, and a low potential such as 0 V is applied to the wiring SL. At this time, a current is supplied to the memory cell string if the memory cell has data “1,” and a current is not supplied to the memory cell string if the memory cell has data “0.” Accordingly, data of the memory cell can be read by detection of the current value at that time or by detection of a potential drop of the wiring BL.

**[0076]** Data in each of the memory cell strings is output to the wiring BL; thus, data per page can be read. As shown in FIGS. 8 and 9, the same data reading is performed for the wirings WL\_2 to WL\_2n, so that data reading subjected to the block or the whole of the semiconductor device can be performed.

**[0077]** As described above, the semiconductor device of one embodiment of the present invention has high integration due to the three-dimensional arrangement of the memory cells. Thus, the semiconductor device has a large storage capacity per footprint. For example, the semiconductor device has a storage capacity of 1 Tbyte or more, 3 Tbyte or more, or 10 Tbyte or more. The semiconductor device can also be called a semiconductor device including a nonvolatile or substantially nonvolatile memory element because it can store data for a long period.

**[0078]** The semiconductor device of one embodiment of the present invention is suited for a storage device for computers because the semiconductor device is capable of rewriting and storing data for a long period, and has a large storage capacity. For example, the semiconductor device can be used in a main storage device (also referred to as a main memory or a memory) that stores data inside a computer, an external storage device (also referred to as a storage or a second storage device) that stores data outside a computer,

or the like. Examples of the external storage device include a memory card and a solid state drive (SSD).

<Modification Example of Semiconductor Device>

[0079] The structure of the semiconductor device of one embodiment of the present invention is not limited to the structure in FIG. 1A. For example, the insulator **106c** may be provided to have a shape along the insulator **130** with the semiconductor **106b** and the insulator **106a** therebetween as shown in FIG. 10. The insulator **112a** may be provided to have a shape along the insulator **130** with the insulator **106c**, the semiconductor **106b**, and the insulator **106a** therebetween. In addition, the charge accumulation layer **112b** may be provided to have a shape along the insulator **130** with the insulator **112a**, the insulator **106c**, the semiconductor **106b**, and the insulator **106a** therebetween. The conductors **116a** and **116b** in FIG. 1A can be omitted.

[0080] The transistors **Tr\_S1** and **Tr\_S2** may be FIN-type transistors as shown in FIG. 11.

<Components of Semiconductor Device>

[0081] The components of the semiconductor device will be described below.

[0082] The insulators **120**, **122**, **124**, **126**, **128**, and **130** may each be formed to have a single-layer structure or a stacked-layer structure including an insulator containing, for example, boron, carbon, nitrogen, oxygen, fluorine, magnesium, aluminum, silicon, phosphorus, chlorine, argon, gallium, germanium, yttrium, zirconium, lanthanum, neodymium, hafnium, or tantalum. For example, aluminum oxide, magnesium oxide, silicon oxide, silicon oxynitride, silicon nitride oxide, silicon nitride, gallium oxide, germanium oxide, yttrium oxide, zirconium oxide, lanthanum oxide, neodymium oxide, hafnium oxide, or tantalum oxide may be used. Note that a “silicon oxynitride film” refers to a film that includes oxygen at a higher proportion than nitrogen, and a “silicon nitride oxide film” refers to a film that includes nitrogen at a higher proportion than oxygen.

[0083] Note that the insulators **120**, **122**, **124**, **126**, **128**, and **130** have functions of isolating adjacent elements, wirings, and the like in some cases; thus, an insulator with a low dielectric constant is preferably used. For example, an insulator with a dielectric constant of 5 or lower, preferably 4 or lower, or further preferably 3 or lower is used. Specifically, an insulator containing silicon and oxygen or an insulator containing fluorine in addition to silicon and oxygen, or the like is preferably used. At least one of the insulators **120**, **122**, **124**, **126**, **128**, and **130** may be a space.

[0084] At least one of the insulators **120**, **122**, **124**, **126**, **128**, and **130** preferably contains an insulator having a function of blocking oxygen and impurities such as hydrogen (a function of not transmitting oxygen or impurities such as hydrogen). When an insulator that has a function of blocking oxygen and impurities such as hydrogen is placed near the transistors **Tr\_1** to **Tr\_2n**, the electrical characteristics of the transistors **Tr\_1** to **Tr\_2n** can be stable.

[0085] When the transistors **Tr\_1** to **Tr\_2n** are transistors including an oxide semiconductor, it is preferable that the adjacent insulator **130** or/and insulator **126** be an insulator including excess oxygen. The excess oxygen can be used to reduce oxygen vacancy in the oxide semiconductor. Note that excess oxygen means oxygen in an insulator or the like

which does not bond with (which is liberated from) the insulator or the like or has low bonding energy with the insulator or the like.

[0086] An insulator including excess oxygen may release oxygen, the amount of which is higher than or equal to  $1 \times 10^{18}$  atoms/cm<sup>3</sup>, higher than or equal to  $1 \times 10^{19}$  atoms/cm<sup>3</sup>, or higher than or equal to  $1 \times 10^{20}$  atoms/cm<sup>3</sup> (converted into the number of oxygen atoms) in thermal desorption spectroscopy (TDS) analysis in the range of a surface temperature of 100° C. to 700° C. inclusive or 100° C. to 500° C. inclusive.

[0087] The method for measuring the amount of released oxygen using TDS analysis will be described below.

[0088] The total amount of gas released from a measurement sample in TDS analysis is proportional to the integral value of the ion intensity of the released gas. Then, comparison with a reference sample is made, whereby the total amount of released gas can be calculated.

[0089] For example, the number of oxygen molecules ( $N_{O2}$ ) released from a measurement sample can be calculated according to the following formula using the TDS results of a silicon substrate containing hydrogen at a predetermined density, which is a reference sample, and the TDS results of the measurement sample. Here, all gases having a mass-to-charge ratio of 32 which are obtained in the TDS analysis are assumed to originate from an oxygen molecule. Note that  $CH_3OH$ , which is a gas having the mass-to-charge ratio of 32, is not taken into consideration because it is unlikely to be present. Furthermore, an oxygen molecule including an oxygen atom having a mass number of 17 or 18 which is an isotope of an oxygen atom is not taken into consideration either because the proportion of such a molecule in the natural world is negligible.

$$N_{O2} = N_{H2} / S_{H2} \times S_{O2} \times a$$

[0090] The value  $N_{H2}$  is obtained by conversion of the number of hydrogen molecules desorbed from the reference sample into densities. The value  $S_{H2}$  is the integral value of ion intensity when the reference sample is subjected to the TDS analysis. Here, the reference value of the reference sample is set to  $N_{H2}/S_{H2}$ . The value  $S_{O2}$  is the integral value of ion intensity when the measurement sample is analyzed by TDS. The value  $a$  is a coefficient affecting the ion intensity in the TDS analysis. Refer to Japanese Published Patent Application No. H6-275697 for details of the above formula. The amount of released oxygen was measured with a thermal desorption spectroscopy apparatus produced by ESCO Ltd., EMD-WA1000S/W, using a silicon substrate containing a certain amount of hydrogen atoms as the reference sample.

[0091] Furthermore, in the TDS analysis, oxygen is partly detected as an oxygen atom. The ratio between oxygen molecules and oxygen atoms can be calculated from the ionization rate of the oxygen molecules. Note that, since the above  $a$  includes the ionization rate of the oxygen molecules, the number of the released oxygen atoms can also be estimated through the measurement of the number of the released oxygen molecules.

[0092] Note that  $N_{O2}$  is the number of the released oxygen molecules. The number of released oxygen in the case of being converted into oxygen atoms is twice the number of the released oxygen molecules.

[0093] Furthermore, an insulator from which oxygen is released by heat treatment may contain a peroxide radical.

Specifically, the spin density attributed to the peroxide radical is greater than or equal to  $5 \times 10^{17}$  spins/cm<sup>3</sup>. Note that the insulator containing a peroxide radical may have an asymmetric signal with a g factor of approximately 2.01 in electron spin resonance (ESR).

[0094] In the case where the transistors Tr\_S1 and Tr\_S2 are silicon transistors including single crystal silicon, polycrystalline silicon, or the like, excess oxygen might be a factor in degrading the electrical characteristics. Accordingly, the insulator 122 preferably includes an insulator having a low oxygen-transmitting property so that the excess oxygen does not enter the transistors Tr\_S1 or Tr\_S2.

[0095] On the contrary, hydrogen can be used to terminate dangling bonds of silicon. Consequently, electrical characteristics of the transistors Tr\_S1 and Tr\_S2 can be improved. Note that hydrogen becomes a factor in degrading the electrical characteristics of the transistors Tr\_1 to Tr\_2n in some cases, so that the insulator 122 preferably includes an insulator having a low hydrogen-transmitting property.

[0096] Because of its small atomic radius or the like, hydrogen is likely to be diffused in an insulator (i.e., the diffusion coefficient of hydrogen is large). For example, a low-density insulator has a high hydrogen-transmitting property. In other words, a high-density insulator has a low hydrogen-transmitting property. The density of a low-density insulator is not always low throughout the insulator; an insulator including a low-density part is also referred to as a low-density insulator. This is because the low-density part serves as a hydrogen path. Although a density that allows hydrogen to be transmitted is not limited, it is typically lower than 2.6 g/cm<sup>3</sup>. Examples of a low-density insulator include an inorganic insulator such as silicon oxide or silicon oxynitride and an organic insulator such as polyester, polyolefin, polyamide (e.g., nylon or aramid), polyimide, polycarbonate, or acrylic. Examples of a high-density insulator include magnesium oxide, aluminum oxide, germanium oxide, gallium oxide, yttrium oxide, zirconium oxide, lanthanum oxide, neodymium oxide, hafnium oxide, and tantalum oxide. Note that a low-density insulator and a high-density insulator are not limited to these insulators. For example, the insulators may contain one or more of boron, nitrogen, fluorine, neon, phosphorus, chlorine, and argon.

[0097] An insulator having crystal grain boundaries can have a high hydrogen-transmitting property. In other words, hydrogen is less likely to be transmitted through an insulator having no grain boundaries or few grain boundaries. For example, a non-polycrystalline insulator (e.g., an amorphous insulator) has a lower hydrogen-transmitting property than that of a polycrystalline insulator.

[0098] An insulator having a high hydrogen-bonding energy has a low hydrogen-transmitting property in some cases. For example, when an insulator which forms a hydrogen compound by bonding with hydrogen has bonding energy at which hydrogen is not released at temperatures in fabrication and operation of a device, the insulator can be in the category of an insulator having a low hydrogen-transmitting property. For example, an insulator which forms a hydrogen compound at higher than or equal to 200° C. and lower than or equal to 1000° C., higher than or equal to 300° C. and lower than or equal to 1000° C., or higher than or equal to 400° C. and lower than or equal to 1000° C. has a low hydrogen-transmitting property in some cases. An insulator which forms a hydrogen compound and which releases hydrogen at higher than or equal to 200° C. and lower than

or equal to 1000° C., higher than or equal to 300° C. and lower than or equal to 1000° C., or higher than or equal to 400° C. and lower than or equal to 1000° C. has a low hydrogen-transmitting property in some cases. An insulator which forms a hydrogen compound and which releases hydrogen at higher than or equal to 20° C. and lower than or equal to 400° C., higher than or equal to 20° C. and lower than or equal to 300° C., or higher than or equal to 20° C. and lower than or equal to 200° C. has a high hydrogen-transmitting property in some cases. Hydrogen which is released easily and liberated can be referred to as excess hydrogen.

[0099] The charge accumulation layer 112b may be formed to have a single-layer structure or a stacked-layer structure including an insulator containing, for example, boron, carbon, nitrogen, oxygen, fluorine, magnesium, aluminum, silicon, phosphorus, chlorine, argon, gallium, germanium, yttrium, zirconium, lanthanum, neodymium, hafnium, or tantalum. For example, aluminum oxide, magnesium oxide, silicon oxide, silicon oxynitride, silicon nitride oxide, gallium oxide, germanium oxide, yttrium oxide, zirconium oxide, lanthanum oxide, neodymium oxide, hafnium oxide, or tantalum oxide may be used.

[0100] The insulators 112a and 112c may each be formed to have a single-layer structure or a stacked-layer structure including an insulator containing, for example, boron, carbon, nitrogen, oxygen, fluorine, magnesium, aluminum, silicon, phosphorus, chlorine, argon, gallium, germanium, yttrium, zirconium, lanthanum, neodymium, hafnium, or tantalum. For example, aluminum oxide, magnesium oxide, silicon oxide, silicon oxynitride, silicon nitride oxide, silicon nitride, gallium oxide, germanium oxide, yttrium oxide, zirconium oxide, lanthanum oxide, neodymium oxide, hafnium oxide, or tantalum oxide may be used.

[0101] The charge accumulation layer 112b is provided between the insulators 112a and 112c. The charge accumulation layer 112b has a function of accumulating electrons. For example, an insulator including an electron trap is suitable for the charge accumulation layer 112b. The electron trap can be formed by addition of impurities, application of damages, or the like. The electron trap may be formed at an interface between the charge accumulation layer 112b and the insulator 112a or at an interface between the charge accumulation layer 112b and the insulator 112c. In that case, junction of different kinds of materials is preferably formed between the charge accumulation layer 112b and the insulator 112a and between the charge accumulation layer 112b and the insulator 112c. When the interface between the charge accumulation layer 112b and the insulator 112a includes an electron trap, the insulator 112c is not necessarily provided in some cases. Alternatively, when the interface between the charge accumulation layer 112b and the insulator 112c includes an electron trap, the insulator 112a is not necessarily provided in some cases. Note that electrons are preferably less likely to move in the charge accumulation layer 112b because the charge accumulation layer 112b is shared with the adjacent memory cells. Note that when the adjacent memory cells and the charge accumulation layer 112b are separated, electrons can move in the charge accumulation layer 112b. That is, the charge accumulation layer 112b may be a semiconductor or a conductor.

[0102] The insulators 112a and 112c each preferably have a thickness which leads to electron tunneling by the gate

voltage or the back gate voltage so that electrons are injected to the charge accumulation layer **112b**. Note that, in order to prevent electron leakage during a time when the memory cell stores data, the thickness is preferably such a thickness that electron tunneling does not occur when the gate voltage or the back gate voltage is not applied. Note that it is difficult to totally eliminate electron tunneling; therefore, the insulators **112a** and **112c** may have a thickness at which data can be stored and electron tunneling does not occur. The thickness of the insulators **112a** and **112c** may be greater than or equal to 3 nm and less than or equal to 15 nm, preferably greater than or equal to 4 nm and less than or equal to 10 nm. An insulator with a large energy gap is preferably used so that electron leakage is prevented. The energy gaps of the insulators **112a** and **112c** are, for example, larger than or equal to 6 eV and smaller than or equal to 10 eV, preferably larger than or equal to 7 eV and smaller than or equal to 10 eV, further preferably larger than or equal to 8 eV and smaller than or equal to 10 eV.

[0103] Specifically, silicon nitride, silicon nitride oxide, or hafnium oxide that has high density of defect states is preferably used for the charge accumulation layer **112b**. Silicon oxide or silicon oxynitride is preferably used for the insulators **112a** and **112c**.

[0104] The conductors **154**, **140**, **142**, **144**, **146**, **148**, **104**, **116a**, **116b**, **132**, **134**, **136**, and **138** each may be formed to have a single-layer structure or a stacked-layer structure including a conductor containing one or more kinds of, for example, boron, nitrogen, oxygen, fluorine, silicon, phosphorus, aluminum, titanium, chromium, manganese, cobalt, nickel, copper, zinc, gallium, yttrium, zirconium, molybdenum, ruthenium, silver, indium, tin, tantalum, and tungsten. An alloy or a compound of the above element may be used, for example, and a conductor containing aluminum, a conductor containing copper and titanium, a conductor containing copper and manganese, a conductor containing indium, tin, and oxygen, a conductor containing titanium and nitrogen, or the like may be used.

[0105] The insulator **106a**, the semiconductor **106b**, and the insulator **106c** will be described below.

[0106] Placing the insulator **106a** under the semiconductor **106b** and placing the insulator **106c** over the semiconductor **106b** can improve electrical characteristics of the transistor in some cases.

[0107] The insulator **106a**, the semiconductor **106b**, and the insulator **106c** each preferably include a CAAC-OS.

[0108] The semiconductor **106b** is an oxide containing indium, for example. The semiconductor **106b** can have high carrier mobility (electron mobility) by containing indium, for example. The semiconductor **106b** preferably contains an element M. The element M is preferably aluminum, gallium, yttrium, tin, or the like. Other elements which can be used as the element M are boron, silicon, titanium, iron, nickel, germanium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, and the like. Note that two or more of the above elements may be used in combination as the element M in some cases. The element M is an element having a high bonding energy with oxygen, for example. The element M is an element whose bonding energy with oxygen is higher than that of indium. The element M is an element that can increase the energy gap of the oxide, for example. Furthermore, the semiconductor **106b** preferably contains zinc. When containing zinc, the oxide is easily crystallized in some cases.

[0109] Note that the semiconductor **106b** is not limited to the oxide containing indium. The semiconductor **106b** may be, for example, an oxide which does not contain indium and contains zinc, gallium, tin, or the like such as a zinc tin oxide or a gallium tin oxide.

[0110] The semiconductor **106b** is formed using, for example, an oxide with a wide energy gap. For example, the energy gap of the semiconductor **106b** is greater than or equal to 2.5 eV and less than or equal to 4.2 eV, preferably greater than or equal to 2.8 eV and less than or equal to 3.8 eV, further preferably greater than or equal to 3 eV and less than or equal to 3.5 eV.

[0111] The insulators **106a** and **106c** are each an oxide containing one or more or two or more elements contained in the semiconductor **106b** other than oxygen, for example. Since the insulators **106a** and **106c** each contain one or more or two or more elements contained in the semiconductor **106b** other than oxygen, a defect state is less likely to be formed at the interface between the insulator **106a** and the semiconductor **106b** and the interface between the semiconductor **106b** and the insulator **106c**.

[0112] The insulator **106a**, the semiconductor **106b**, and the insulator **106c** preferably contain at least indium. In the case of using an In-M-Zn oxide as the insulator **106a**, when the total proportion of In and M is assumed to be 100 atomic %, the proportions of In and M are preferably set to be less than 50 atomic % and greater than 50 atomic %, respectively, and further preferably less than 25 atomic % and greater than 75 atomic %, respectively. In the case of using an In-M-Zn oxide as the semiconductor **106b**, when the total proportion of In and M is assumed to be 100 atomic %, the proportions of In and M are preferably set to be greater than 25 atomic % and less than 75 atomic %, respectively, and further preferably greater than 34 atomic % and less than 66 atomic %, respectively. In the case of using an In-M-Zn oxide as the insulator **106c**, when the total proportion of In and M is assumed to be 100 atomic %, the proportions of In and M are preferably set to be less than 50 atomic % and greater than 50 atomic %, respectively, and further preferably less than 25 atomic % and greater than 75 atomic %, respectively. Note that the insulator **106c** may be an oxide that is of the same type as the oxide of the insulator **106a**. Note that the insulator **106a** and/or the insulator **106c** do/does not necessarily contain indium in some cases. For example, the insulator **106a** and/or the insulator **106c** may be gallium oxide. Note that the atomic ratio between the elements contained in the insulator **106a**, the semiconductor **106b**, and the insulator **106c** is not necessarily a simple integer ratio.

[0113] As the semiconductor **106b**, an oxide having an electron affinity higher than those of the insulators **106a** and **106c** is used. For example, as the semiconductor **106b**, an oxide having an electron affinity higher than those of the insulators **106a** and **106c** by 0.07 eV or higher and 1.3 eV or lower, preferably 0.1 eV or higher and 0.7 eV or lower, and further preferably 0.15 eV or higher and 0.4 eV or lower is used. Note that the electron affinity refers to an energy difference between the vacuum level and the bottom of the conduction band.

[0114] An indium gallium oxide has a low electron affinity and a high oxygen-blocking property. Therefore, the insulator **106c** preferably includes an indium gallium oxide. The gallium atomic ratio  $[Ga/(In+Ga)]$  is, for example, higher

than or equal to 70%, preferably higher than or equal to 80%, further preferably higher than or equal to 90%.

[0115] At this time, when gate voltage is applied, a channel is formed in the semiconductor **106b** whose electron affinity is the highest among the insulator **106a**, the semiconductor **106b**, and the insulator **106c**.

[0116] Here, in some cases, there is a mixed region of the insulator **106a** and the semiconductor **106b** between the insulator **106a** and the semiconductor **106b**. Furthermore, in some cases, there is a mixed region of the semiconductor **106b** and the insulator **106c** between the semiconductor **106b** and the insulator **106c**. The mixed region has a low density of defect states. For that reason, the stack including the insulator **106a**, the semiconductor **106b**, and the insulator **106c** has a band structure where energy is changed continuously at each interface and in the vicinity of the interface (continuous junction) (see FIG. 12). Note that boundaries of the insulator **106a**, the semiconductor **106b**, and the insulator **106c** are not clear in some cases.

[0117] At this time, electrons move mainly in the semiconductor **106b**, but neither in the insulator **106a** nor in the insulator **106c**. Note that the insulator **106a** and the insulator **106c** can exhibit a property of any of a conductor, a semiconductor, and an insulator when existing alone. When the transistor operates, they each, however, have a region where a channel is not formed. Specifically, a channel is formed only in a region near the interface between the insulator **106a** and the semiconductor **106b** and a region near the interface between the insulator **106c** and the semiconductor **106b**, whereas a channel is not formed in the other region. Therefore, the insulator **106a** and the insulator **106c** can be called insulators when the transistor operates, and are thus referred to as, not semiconductors or conductors, but insulators in this specification. The insulator **106a**, the semiconductor **106b**, and the insulator **106c** are separately called semiconductor or insulator only because of the relative difference in physical property. Therefore, for example, an insulator that can be used as the insulator **106a** or the insulator **106c** can be used as the semiconductor **106b** in some cases. As described above, when the density of defect states at the interface between the insulator **106a** and the semiconductor **106b** and the density of defect states at the interface between the semiconductor **106b** and the insulator **106c** are decreased, electron movement in the semiconductor **106b** is less likely to be inhibited and the on-state current of the transistor can be increased.

[0118] As factors in inhibiting electron movement are decreased, the on-state current of the transistor can be increased. For example, in the case where there is no factor in inhibiting electron movement, electrons are assumed to be moved efficiently. Electron movement is also inhibited, for example, in the case where physical unevenness in a channel formation region is large.

[0119] To increase the on-state current of the transistor, for example, root mean square (RMS) roughness with a measurement area of  $1 \mu\text{m} \times 1 \mu\text{m}$  of the top or bottom surface of the semiconductor **106b** (a formation surface; here, the top surface of the insulator **106a**) is less than 1 nm, preferably less than 0.6 nm, further preferably less than 0.5 nm, still further preferably less than 0.4 nm. The average surface roughness (also referred to as Ra) with the measurement area of  $1 \mu\text{m} \times 1 \mu\text{m}$  is less than 1 nm, preferably less than 0.6 nm, further preferably less than 0.5 nm, still further preferably less than 0.4 nm. The maximum difference (also

referred to as P-V) with the measurement area of  $1 \mu\text{m} \times 1 \mu\text{m}$  is less than 10 nm, preferably less than 9 nm, further preferably less than 8 nm, still further preferably less than 7 nm. RMS roughness, Ra, and P-V can be measured using, for example, a scanning probe microscope SPA-500 manufactured by SII Nano Technology Inc.

[0120] Moreover, the thickness of the insulator **106c** is preferably as small as possible to increase the on-state current of the transistor. For example, the insulator **106c** is formed to include a region having a thickness of less than 10 nm, preferably less than or equal to 5 nm, further preferably less than or equal to 3 nm. Meanwhile, the insulator **106c** has a function of blocking entry of elements other than oxygen (such as hydrogen and silicon) included in the adjacent insulator into the semiconductor **106b** where a channel is formed. For this reason, it is preferable that the insulator **106c** have a certain thickness. For example, the insulator **106c** is formed to include a region having a thickness of greater than or equal to 0.3 nm, preferably greater than or equal to 1 nm, further preferably greater than or equal to 2 nm. The insulator **106c** preferably has an oxygen blocking property to suppress outward diffusion of oxygen released from the other insulators.

[0121] To improve reliability, the insulator **106a** is preferably thick and the insulator **106c** is preferably thin. For example, the insulator **106a** includes a region with a thickness of, for example, greater than or equal to 10 nm, preferably greater than or equal to 20 nm, further preferably greater than or equal to 40 nm, still further preferably greater than or equal to 60 nm. When the thickness of the insulator **106a** is made large, a distance from an interface between the adjacent insulator and the insulator **106a** to the semiconductor **106b** in which a channel is formed can be large. Since the productivity of the semiconductor device might be decreased, the insulator **106a** has a region with a thickness of, for example, less than or equal to 200 nm, preferably less than or equal to 120 nm, further preferably less than or equal to 80 nm.

[0122] For example, a region with a silicon concentration measured by secondary ion mass spectrometry (SIMS) of higher than or equal to  $1 \times 10^{16}$  atoms/cm $^3$  and lower than or equal to  $1 \times 10^{19}$  atoms/cm $^3$ , preferably higher than or equal to  $1 \times 10^{16}$  atoms/cm $^3$  and lower than or equal to  $5 \times 10^{18}$  atoms/cm $^3$ , further preferably higher than or equal to  $1 \times 10^{16}$  atoms/cm $^3$  and lower than or equal to  $2 \times 10^{18}$  atoms/cm $^3$  is provided, for example, between the semiconductor **106b** and the insulator **106a**. A region with a silicon concentration measured by SIMS of higher than or equal to  $1 \times 10^{16}$  atoms/cm $^3$  and lower than or equal to  $1 \times 10^{19}$  atoms/cm $^3$ , preferably higher than or equal to  $1 \times 10^{16}$  atoms/cm $^3$  and lower than or equal to  $5 \times 10^{18}$  atoms/cm $^3$ , further preferably higher than or equal to  $1 \times 10^{16}$  atoms/cm $^3$  and lower than or equal to  $2 \times 10^{18}$  atoms/cm $^3$  is provided between the semiconductor **106b** and the insulator **106c**.

[0123] The semiconductor **106b** includes a region with a hydrogen concentration measured by SIMS of higher than or equal to  $1 \times 10^{16}$  atoms/cm $^3$  and lower than or equal to  $2 \times 10^{20}$  atoms/cm $^3$ , preferably higher than or equal to  $1 \times 10^{16}$  atoms/cm $^3$  and lower than or equal to  $5 \times 10^{19}$  atoms/cm $^3$ , further preferably higher than or equal to  $1 \times 10^{16}$  atoms/cm $^3$  and lower than or equal to  $1 \times 10^{19}$  atoms/cm $^3$ , and still further preferably higher than or equal to  $1 \times 10^{16}$  atoms/cm $^3$  and lower than or equal to  $5 \times 10^{18}$  atoms/cm $^3$ . It is preferable to reduce the hydrogen concentration in the insulator **106a** and

the insulator **106c** in order to reduce the hydrogen concentration in the semiconductor **106b**. The insulator **106a** and the insulator **106c** each include a region with a hydrogen concentration measured by SIMS of higher than or equal to  $1 \times 10^{16}$  atoms/cm<sup>3</sup> and lower than or equal to  $2 \times 10^{20}$  atoms/cm<sup>3</sup>, preferably higher than or equal to  $1 \times 10^{16}$  atoms/cm<sup>3</sup> and lower than or equal to  $5 \times 10^{19}$  atoms/cm<sup>3</sup>, further preferably higher than or equal to  $1 \times 10^{16}$  atoms/cm<sup>3</sup> and lower than or equal to  $1 \times 10^{19}$  atoms/cm<sup>3</sup>, and still further preferably higher than or equal to  $1 \times 10^{16}$  atoms/cm<sup>3</sup> and lower than or equal to  $5 \times 10^{18}$  atoms/cm<sup>3</sup>. The semiconductor **106b** includes a region with a nitrogen concentration measured by SIMS of higher than or equal to  $1 \times 10^{15}$  atoms/cm<sup>3</sup> and lower than or equal to  $5 \times 10^{19}$  atoms/cm<sup>3</sup>, preferably higher than or equal to  $1 \times 10^{15}$  atoms/cm<sup>3</sup> and lower than or equal to  $5 \times 10^{18}$  atoms/cm<sup>3</sup>, further preferably higher than or equal to  $1 \times 10^{15}$  atoms/cm<sup>3</sup> and lower than or equal to  $1 \times 10^{18}$  atoms/cm<sup>3</sup>, and still further preferably higher than or equal to  $1 \times 10^{15}$  atoms/cm<sup>3</sup> and lower than or equal to  $5 \times 10^{17}$  atoms/cm<sup>3</sup>. It is preferable to reduce the nitrogen concentration in the insulator **106a** and the insulator **106c** in order to reduce the nitrogen concentration in the semiconductor **106b**. The insulator **106a** and the insulator **106c** each include a region with a nitrogen concentration measured by SIMS of higher than or equal to  $1 \times 10^{15}$  atoms/cm<sup>3</sup> and lower than or equal to  $5 \times 10^{19}$  atoms/cm<sup>3</sup>, preferably higher than or equal to  $1 \times 10^{15}$  atoms/cm<sup>3</sup> and lower than or equal to  $5 \times 10^{18}$  atoms/cm<sup>3</sup>, further preferably higher than or equal to  $1 \times 10^{15}$  atoms/cm<sup>3</sup> and lower than or equal to  $1 \times 10^{18}$  atoms/cm<sup>3</sup>, and still further preferably higher than or equal to  $1 \times 10^{15}$  atoms/cm<sup>3</sup> and lower than or equal to  $5 \times 10^{17}$  atoms/cm<sup>3</sup>.

[0124] The above three-layer structure is an example. For example, a two-layer structure including the semiconductor **106b** and the insulator **106a** or including the semiconductor **106b** and the insulator **106c** may be employed. A four-layer structure in which any one of the semiconductors described as examples of the insulator **106a**, the semiconductor **106b**, and the insulator **106c** is provided under or over the insulator **106a** or under or over the insulator **106c** may be employed. An n-layer structure (n is an integer of 5 or more) may be employed in which one of the semiconductors described as examples of the insulator **106a**, the semiconductor **106b**, and the insulator **106c** is provided at two or more of the following positions: over the insulator **106a**, under the insulator **106a**, over the insulator **106c**, and under the insulator **106c**.

#### <Composition>

[0125] The composition of an In-M-Zn oxide will be described below. The element M is aluminum, gallium, yttrium, tin, or the like. Other elements which can be used as the element M are boron, silicon, titanium, iron, nickel, germanium, zirconium, molybdenum, lanthanum, cerium, neodymium, hafnium, tantalum, tungsten, and the like.

[0126] FIG. 13 is a triangular diagram whose vertices represent In, M, and Zn. In the diagram, [In] means the atomic concentration of In, [M] means the atomic concentration of the element M, and [Zn] means the atomic concentration of Zn.

[0127] A crystal of an In-M-Zn oxide is known to have a homologous structure and is represented by  $\text{InMO}_3(\text{ZnO})_m$  (m is a natural number). Since In and M can be interchanged, the crystal can also be represented by  $\text{In}_{1+\alpha}\text{M}_{1-\alpha}\text{O}_3(\text{ZnO})_m$  ( $-1 \leq \alpha \leq 1$ ). This composition is represented by any of the

dashed lines denoted as  $[\text{In}]:[\text{M}]:[\text{Zn}] = 1+\alpha:1-\alpha:1$ ,  $[\text{In}]:[\text{M}]:[\text{Zn}] = 1+\alpha:1-\alpha:2$ ,  $[\text{In}]:[\text{M}]:[\text{Zn}] = 1+\alpha:1-\alpha:3$ ,  $[\text{In}]:[\text{M}]:[\text{Zn}] = 1+\alpha:1-\alpha:4$ , and  $[\text{In}]:[\text{M}]:[\text{Zn}] = 1+\alpha:1-\alpha:5$ . Note that the bold lines on the dashed lines represent, for example, the compositions that each allow oxides (raw materials) to be a solid solution when the oxides are mixed and subjected to baking at 1350°C.

[0128] Thus, when an oxide has a composition close to the above composition that allows the oxide to be a solid solution, the crystallinity can be increased. When an In-M-Zn oxide is deposited by a sputtering method, the composition of a target is different from the composition of the deposited film in some cases. For example, using an In-M-Zn oxide in which an atomic ratio is 1:1:1, 1:1:1.2, 3:1:2, 4:2:4.1, 1:3:2, 1:3:4, or 1:4:5 as a target results in a film having an atomic ratio of 1:1:0.7 (approximately 1:1:0.5 to 1:1:0.9), 1:1:0.9 (approximately 1:1:0.8 to 1:1:1.1), 3:1:1.5 (approximately 3:1:1 to 3:1:1.8), 4:2:3 (approximately 4:2:2.6 to 4:2:3.6), 1:3:1.5 (approximately 1:3:1 to 1:3:1.8), 1:3:3 (approximately 1:3:2.5 to 1:3:3.5), or 1:4:4 (approximately 1:4:3.4 to 1:4:4.4). Thus, in order to obtain a film with a desired composition, a composition of a target may be selected in consideration of a change in the composition.

#### <Structure of Oxide Semiconductor>

[0129] The structure of an oxide semiconductor will be described below.

[0130] An oxide semiconductor is classified into a single crystal oxide semiconductor and the other, a non-single-crystal oxide semiconductor. Examples of a non-single-crystal oxide semiconductor include a c-axis aligned crystalline oxide semiconductor (CAAC-OS), a polycrystalline oxide semiconductor, a nanocrystalline oxide semiconductor (nc-OS), an amorphous-like oxide semiconductor (a-like OS), and an amorphous oxide semiconductor.

[0131] From another perspective, an oxide semiconductor is classified into an amorphous oxide semiconductor and the other, a crystalline oxide semiconductor. Examples of a crystalline oxide semiconductor include a single crystal oxide semiconductor, a CAAC-OS, a polycrystalline oxide semiconductor, and an nc-OS.

[0132] An amorphous structure is generally thought to be isotropic and have no non-uniform structure, to be metastable and not have fixed positions of atoms, to have a flexible bond angle, and to have a short-range order but have no long-range order, for example.

[0133] In other words, a stable oxide semiconductor cannot be regarded as a completely amorphous oxide semiconductor. Moreover, an oxide semiconductor that is not isotropic (e.g., an oxide semiconductor that has a periodic structure in a microscopic region) cannot be regarded as a completely amorphous oxide semiconductor. In contrast, an a-like OS, which is not isotropic, has an unstable structure that contains a void. Because of its instability, an a-like OS is close to an amorphous oxide semiconductor in terms of physical properties.

#### <CAAC-OS>

[0134] First, a CAAC-OS will be described.

[0135] A CAAC-OS is one of oxide semiconductors having a plurality of c-axis aligned crystal parts (also referred to as pellets).

[0136] Analysis of a CAAC-OS by X-ray diffraction (XRD) will be described. For example, when the structure of a CAAC-OS including an  $\text{InGaZnO}_4$  crystal that is classified into the space group  $\text{R}-3\text{m}$  is analyzed by an out-of-plane method, a peak appears at a diffraction angle ( $2\theta$ ) of around  $31^\circ$  as shown in FIG. 14A. This peak is derived from the (009) plane of the  $\text{InGaZnO}_4$  crystal, which indicates that crystals in the CAAC-OS have c-axis alignment, and that the c-axes are aligned in a direction substantially perpendicular to a surface over which the CAAC-OS film is formed (also referred to as a formation surface) or the top surface of the CAAC-OS film. Note that a peak sometimes appears at a  $2\theta$  of around  $36^\circ$  in addition to the peak at a  $2\theta$  of around  $31^\circ$ . The peak at a  $2\theta$  of around  $36^\circ$  is derived from a crystal structure classified into the space group  $\text{Fd}-3\text{m}$ . Therefore, it is preferable that the CAAC-OS do not show the peak.

[0137] On the other hand, in structural analysis of the CAAC-OS by an in-plane method in which an X-ray is incident on the CAAC-OS in a direction parallel to the formation surface, a peak appears at a  $2\theta$  of around  $56^\circ$ . This peak is derived from the (110) plane of the  $\text{InGaZnO}_4$  crystal. When analysis ( $\phi$  scan) is performed with  $2\theta$  fixed at around  $56^\circ$  and with the sample rotated using a normal vector to the sample surface as an axis ( $\phi$  axis), as shown in FIG. 14B, a peak is not clearly observed. In contrast, in the case where single crystal  $\text{InGaZnO}_4$  is subjected to  $\phi$  scan with  $2\theta$  fixed at around  $56^\circ$ , as shown in FIG. 14C, six peaks which are derived from crystal planes equivalent to the (110) plane are observed. Accordingly, the structural analysis by XRD shows that the directions of a-axes and b-axes are irregularly oriented in the CAAC-OS.

[0138] Next, a CAAC-OS analyzed by electron diffraction will be described. For example, when an electron beam with a probe diameter of 300 nm is incident on a CAAC-OS including an  $\text{InGaZnO}_4$  crystal in a direction parallel to the formation surface of the CAAC-OS, a diffraction pattern (also referred to as a selected-area electron diffraction pattern) shown in FIG. 14D can be obtained. In this diffraction pattern, spots derived from the (009) plane of an  $\text{InGaZnO}_4$  crystal are included. Thus, the electron diffraction also indicates that pellets included in the CAAC-OS have c-axis alignment and that the c-axes are aligned in a direction substantially perpendicular to the formation surface or the top surface of the CAAC-OS. Meanwhile, FIG. 14E shows a diffraction pattern obtained in such a manner that an electron beam with a probe diameter of 300 nm is incident on the same sample in a direction perpendicular to the sample surface. As shown in FIG. 14E, a ring-like diffraction pattern is observed. Thus, the electron diffraction using an electron beam with a probe diameter of 300 nm also indicates that the a-axes and b-axes of the pellets included in the CAAC-OS do not have regular orientation. The first ring in FIG. 14E is considered to be derived from the (010) plane, the (100) plane, and the like of the  $\text{InGaZnO}_4$  crystal. The second ring in FIG. 14E is considered to be derived from the (110) plane and the like.

[0139] In a combined analysis image (also referred to as a high-resolution TEM image) of a bright-field image and a diffraction pattern of a CAAC-OS, which is obtained using a transmission electron microscope (TEM), a plurality of pellets can be observed. However, even in the high-resolution TEM image, a boundary between pellets, that is, a grain boundary is not clearly observed in some cases. Thus, in the

CAAC-OS, a reduction in electron mobility due to the grain boundary is less likely to occur.

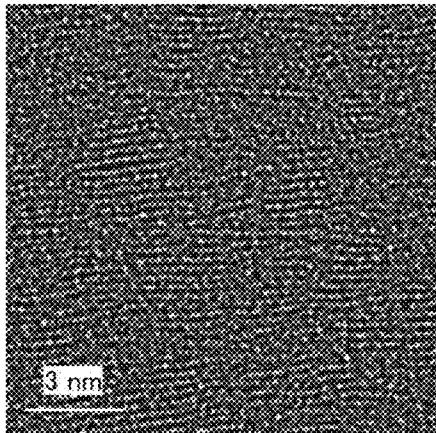

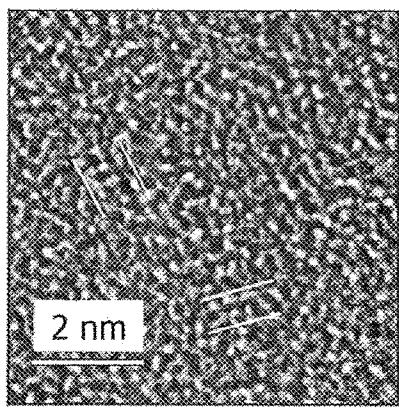

[0140] FIG. 15A shows a high-resolution TEM image of a cross section of the CAAC-OS which is observed from a direction substantially parallel to the sample surface. The high-resolution TEM image is obtained with a spherical aberration corrector function. The high-resolution TEM image obtained with a spherical aberration corrector function is particularly referred to as a Cs-corrected high-resolution TEM image. The Cs-corrected high-resolution TEM image can be observed with, for example, an atomic resolution analytical electron microscope JEM-ARM200F manufactured by JEOL Ltd.

[0141] FIG. 15A shows pellets in which metal atoms are arranged in a layered manner. FIG. 15A proves that the size of a pellet is greater than or equal to 1 nm or greater than or equal to 3 nm. Therefore, the pellet can also be referred to as a nanocrystal (nc). Furthermore, the CAAC-OS can also be referred to as an oxide semiconductor including c-axis aligned nanocrystals (CANC). A pellet reflects unevenness of a formation surface or a top surface of the CAAC-OS, and is parallel to the formation surface or the top surface of the CAAC-OS.