(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 102 41 344 B4 2007.10.25

(12)

## Patentschrift

(21) Aktenzeichen: 102 41 344.4

(22) Anmelddatum: 06.09.2002

(43) Offenlegungstag: 10.07.2003

(45) Veröffentlichungstag

der Patenterteilung: 25.10.2007

(51) Int Cl.<sup>8</sup>: H01L 21/58 (2006.01)

H01L 23/04 (2006.01)

H01L 23/10 (2006.01)

B81C 1/00 (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

(30) Unionspriorität:

10/028,058 20.12.2001 US

(73) Patentinhaber:

Avago Technologies Wireless IP (Singapore) Pte.

Ltd., Singapore, SG

(74) Vertreter:

Schoppe, Zimmermann, Stöckeler & Zinkler, 82049

Pullach

(72) Erfinder:

Geefay, Frank S., Cupertino, Calif., US; Gan, Qing,

Fremont, Calif., US; Mattos, Ann, San Jose, Calif.,

US; Figueiredo, Domingo A., Union, Calif., US

(56) Für die Beurteilung der Patentfähigkeit in Betracht

gezogene Druckschriften:

US 60 62 461 A

US 56 68 033 A

US 52 73 939 A

US 62 55 741 B1

EP 10 41 628 A2

(54) Bezeichnung: Waferebenengehäuse mit Siliziumdichtung

(57) Hauptanspruch: Verfahren zum Herstellen eines Wafe-

rebenengehäuses, das folgende Schritte umfaßt:

Liefern eines ersten Wafers (203) und eines zweiten Wa-

fers (207);

Entfernen eines Teils von dem ersten Wafer, um eine Dich-

tung (201) zu bilden;

Bilden einer Anschlußfläche (305) auf dem zweiten Wafer,

wobei die Anschlußfläche (305) im wesentlichen mit der

Dichtung übereinstimmt;

Einfügen von Verbindungsmedium (209) zwischen die

Dichtung (201) und die Anschlußfläche (305); und

Verbinden der Dichtung (201) mit der Anschlußfläche (305)

mit dem Verbindungsmedium (209), um zwischen dem ers-

ten (203) und dem zweiten Wafer (207) eine hermetisch ab-

gedichtete Umgebung (211) zu erzeugen,

wobei die Dichtung (201) nicht mehr als 20 µm breit ist.

## Beschreibung

**[0001]** Die vorliegende Erfindung bezieht sich auf Halbleiterhäusungstechniken und insbesondere auf die Herstellung von Waferebenengehäusen.

**[0002]** Viele Halbleiterbauelemente sind empfindlich gegenüber Verschmutzung, Feuchtigkeit und anderen solchen Umgebungsfaktoren. Um dieselben vor Schäden zu schützen, müssen die Bauelemente in ein hermetisch abgedichtetes Gehäuse gesetzt werden. In der Vergangenheit mußte ein Bauelement zunächst geschnitten oder anderweitig von seinem Wafer getrennt werden, bevor es in ein Gehäuse gesetzt werden konnte. Bei Waferebenengehäusen wird das Häuseln durchgeführt, während das Bauelement auf dem Wafer verbleibt. Auf diese Weise können Hunderte oder Tausende von Gehäusen gleichzeitig erzeugt werden, und dann durch Sägen oder anderweitig getrennt werden.

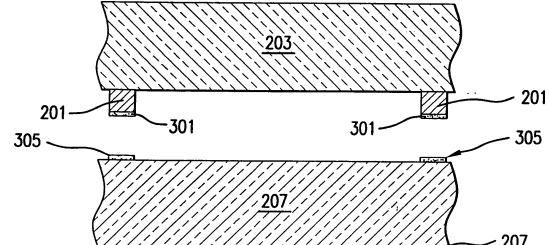

**[0003]** Fig. 1 stellt ein beispielhaftes Waferebenengehäuse **101** dar. Ein erster Wafer **102** weist eine Dichtung **103** auf, die an einem zweiten Wafer **107** befestigt ist, wodurch eine hermetisch abgedichtete Umgebung **109** zwischen den beiden Wafern gebildet wird, um ein Bauelement **111** zu schützen. Nur ein Teil des Wafers **102** und des Wafers **107** sind in der Figur gezeigt, aber es kann Hunderte oder Tausende solcher Waferebenengehäuse geben, die gleichzeitig zwischen den beiden Wafern gebildet werden. Die Dichtung **103** wird durch Aufbringen von Material, wie z. B. Metall oder einem Polyimid, auf den Wafer **102** in der gewünschten Dichtungsform erzeugt. Die beiden Wafers werden dann an der Dichtung miteinander verbunden. Dieses Verfahren ist beim Erzeugen einer hermetisch abgedichten Umgebung **109** wirkungsvoll. Das aufgebrachte Material ist jedoch nicht sehr starr und ist anfällig für Deformationen, wenn während dem Verbindungsprozeß ein Druck angelegt wird. Da ein Großteil des angelegten Drucks durch die Dichtungsdeformation aufgebraucht wird, überträgt sich nur wenig des angelegten Drucks tatsächlich auf die Verbindungsstelle selbst. Daher muß während einer längeren Zeitperiode mehr Druck angelegt werden, um die Verbindung zu erzeugen. Ferner erzeugt der Prozeß des Aufbringens von Material eine unregelmäßige Dichtungsverbindungsoberfläche, was während dem Verbinden Probleme verursacht. Schließlich ist es schwierig, die Geometrie der Dichtung genau zu steuern, da das aufgebrachte Material dazu neigt, während dem Aufbringungsprozeß zu schrumpfen oder die Form zu verändern.

**[0004]** Aus der US 5,668,033 ist ein Verfahren zum Herstellen eines Halbleiterbeschleunigungssensors bekannt, bei dem ein Sensorelement in einem Siliziumwafer gebildet ist. Das Element umgebend ist ein Verbindungsrahmen vorgesehen. Ein Abdeckwafer

hat eine erhöhte Struktur, auf der eine Verbindungsenschicht vorgesehen ist, die formmäßig an dem Verbindungsrahmen angepasst ist. Die Verbindungsenschicht wird mit dem Rahmen verbunden, um das Element abzudichten. Der Verbindungsrahmen und entsprechend die von dem Abdeckwafer vorstehende Struktur weisen eine Breite zwischen 100 und 300 µm auf.

**[0005]** Aus der US 6,062,461 ist ein Verfahren zum Verbinden von bearbeiteten Wafern bekannt. Ein erster Wafer umfasst einen lötaren Ring auf einer Oberfläche desselben. Ein Abdeckwafer weist vorstehende Abschnitte auf, auf denen eine lötbare Schicht angeordnet ist, so dass durch Löten eine Verbindung zwischen den Wafern hergestellt werden kann.

**[0006]** Die US 5,273,939 behandelt das Verbinden von mikromechanischen Elementen, wobei ein Sensorelement und ein Substrat über vorstehende Abschnitte verbunden werden können, beispielsweise durch Siliziumbonden, anodisches Bonden, Kleben oder Löten. Die Grundfläche der vorstehenden Elemente soll klein gegen die Fläche des Sensors sein.

**[0007]** Die US 6,255,741 B1 befasst sich mit einem Halbleiterelement, bei dem eine Polyimidschicht unter Verwendung eines resistiven Haftmittels auf Polyimidbasis (Silikon) mit einem Halbleiterwafer verbunden ist.

**[0008]** Die EP 1, 041, 268 A2 befasst sich mit dem Häuseln eines Bildsensorssubstrats durch Aufkleben eines transparenten Deckels auf das Substrat, wobei als optischer Kleber BCB verwendet wird.

**[0009]** Es ist die Aufgabe der vorliegenden Erfindung, ein Verfahren zum Herstellen eines Waferebenengehäuses und ein Waferebenengehäuse mit verbesserten Charakteristika zu schaffen.

**[0010]** Diese Aufgabe wird durch ein Verfahren gemäß Anspruch 1 und ein Gehäuse gemäß Anspruch 11 oder 18 gelöst.

**[0011]** Gemäß einem dargestellten bevorzugten Ausführungsbeispiel der vorliegenden Erfindung wird eine Dichtung für ein Waferebenengehäuse aus dem Wafermaterial selbst ausgeschnitten. Der Wafer ist typischerweise aus Silizium hergestellt, obwohl Materialien, wie z. B. Glas, 3-5-Verbindungen, Keramik, Kunststoff oder andere Materialien verwendet werden können. Silizium ist äußerst starr und daher ein ideales Dichtungsmaterial. Wenn während der Verbindung Druck angelegt wird, deformed sich die Siliziumdichtung nicht, und der angelegte Druck ist an der Verbindungsstelle konzentriert. Folglich wird weniger Kraft und/oder Zeit benötigt, um das Waferebenengehäuse zu verbinden. Ferner ist die Originalwaferoberfläche so hergestellt, daß sie äußerst flach ist.

Da die Dichtungsüberfläche die Originalwaferoberfläche ist, hat die Dichtung ebenfalls eine äußerst flache Oberfläche, was eine einheitliche feste Verbindung ermöglicht.

**[0012]** Die vorliegende Erfindung verwendet außerdem eine bestehende Siliziumätztechnologie, die sowohl bei der Ätztiefe als auch der Dichtungsbreite eine hohe Präzision liefert, wenn die gewünschte Form ausgeschnitten wird. Dies ermöglicht eine stärkere Steuerung über die Abmessungen des hermetisch abgedichteten Hohlraums. Außerdem können aufgrund der hohen Stärke des Siliziums die Dichtungen schmäler gemacht werden als in der Vergangenheit, normalerweise nicht mehr als 10 µm breit. Der Oberflächenbereich der Dichtung bestimmt die Druckmenge auf der Verbindungsstelle während dem Verbinden für eine bestimmte Verbindungskraft. Da eine schmalere Dichtung weniger Oberflächenbereich aufweist, ist dieselbe in der Lage, mehr der angelegten Verbindungskraft an der Verbindungsstelle zu konzentrieren, um eine starke Abdichtung zu erzeugen.

**[0013]** Weitere Merkmale und Vorteile der vorliegenden Erfindung und auch die Struktur und der Betrieb bevorzugter Ausführungsbeispiele der vorliegenden Erfindung sind nachfolgend mit Bezugnahme auf die beiliegenden beispielhaften Zeichnungen näher erläutert. Bei den Zeichnungen zeigen gleiche Bezugszeichen identische oder funktional ähnliche Elemente an.

**[0014]** Bevorzugte Ausführungsbeispiele der vorliegenden Erfindung werden nachfolgend bezugnehmend auf die beiliegenden Zeichnungen näher erläutert. Es zeigen:

**[0015]** [Fig. 1](#) eine Querschnittsansicht eines herkömmlichen Waferbenenengehäuses;

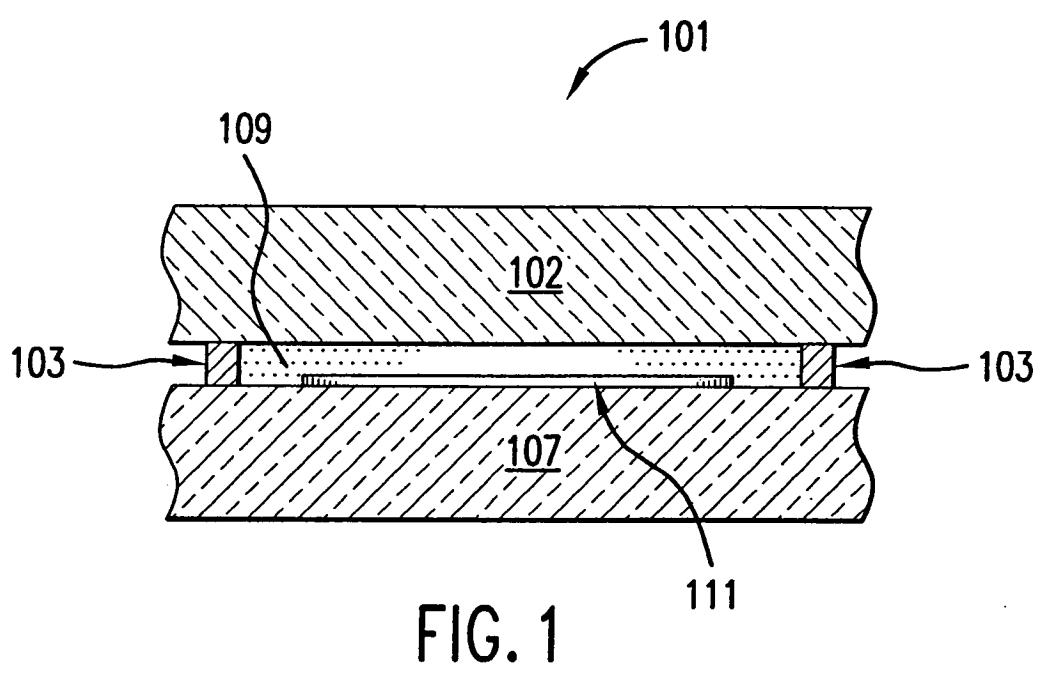

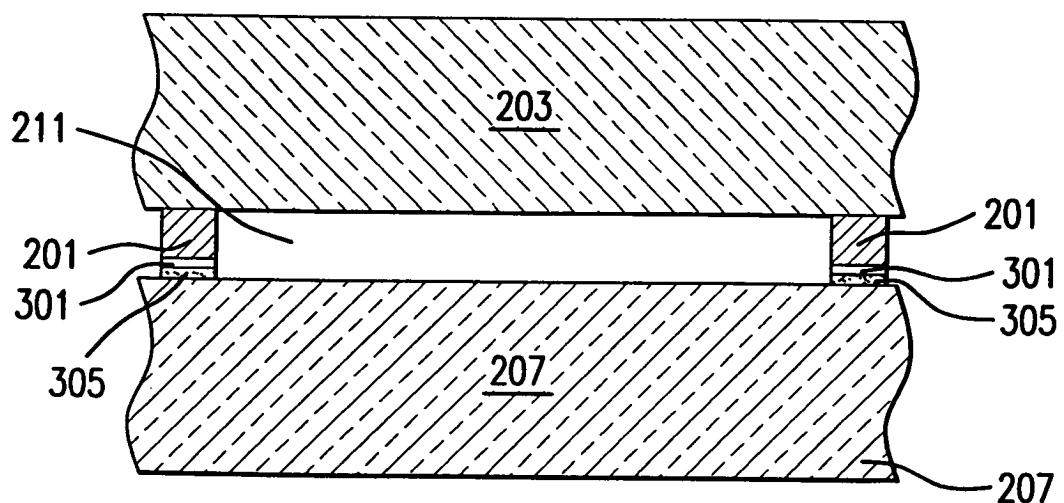

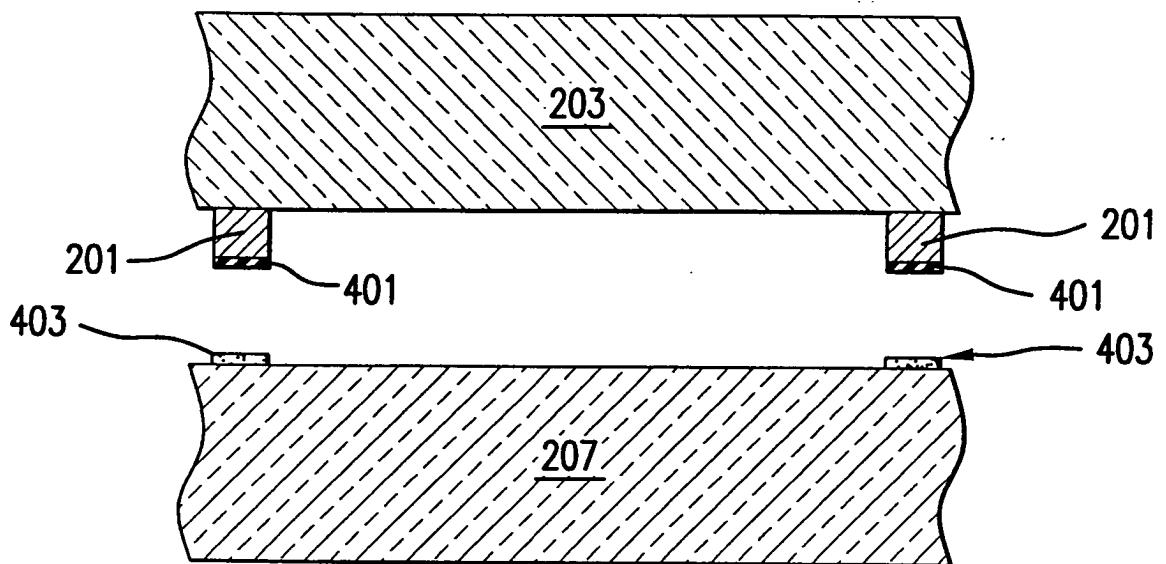

**[0016]** [Fig. 2A](#) eine Querschnittsansicht der vorliegenden Erfindung;

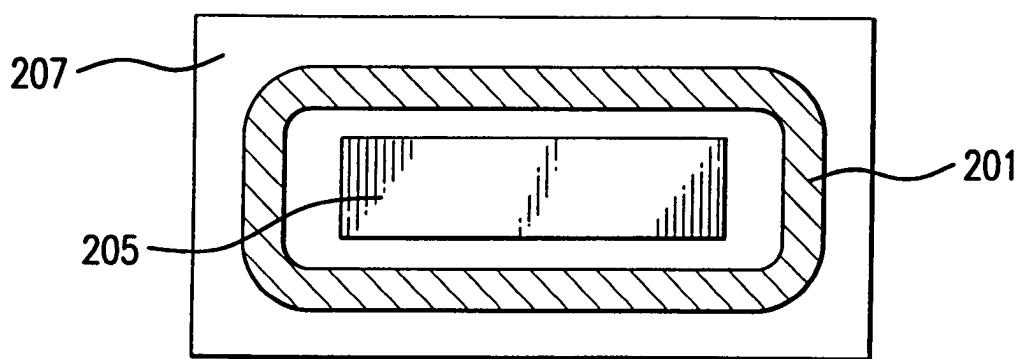

**[0017]** [Fig. 2B](#) eine Von-Oben-Nach-Unten-Ansicht der vorliegenden Erfindung entlang der Linie B-B' in [Fig. 2A](#);

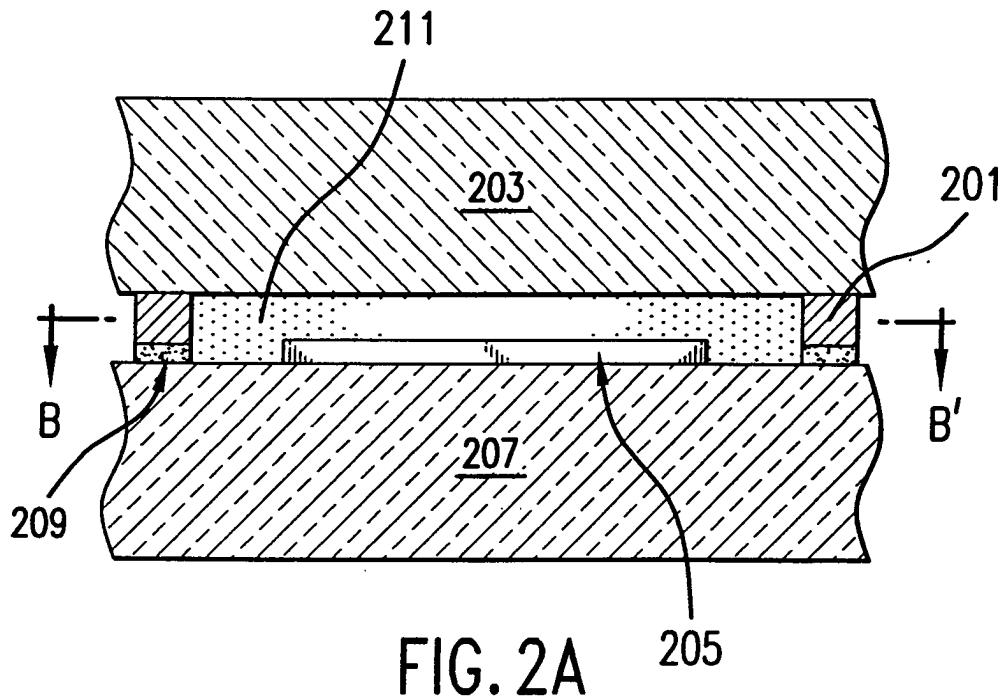

**[0018]** [Fig. 3A](#) bis [Fig. 3E](#) die Herstellung eines Waferbenenengehäuses, in dem Dichtung mit leitfähigem Verbindungsmaterial verbunden ist;

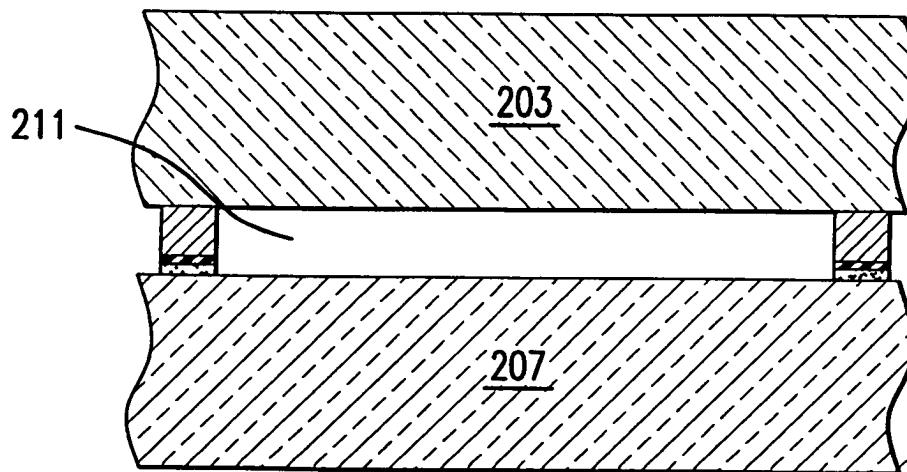

**[0019]** [Fig. 4A](#) bis [Fig. 4E](#) die Herstellung eines Waferbenenengehäuses, bei dem die Dichtung unter Verwendung von nichtleitfähigem Verbindungsmaterial verbunden ist; und

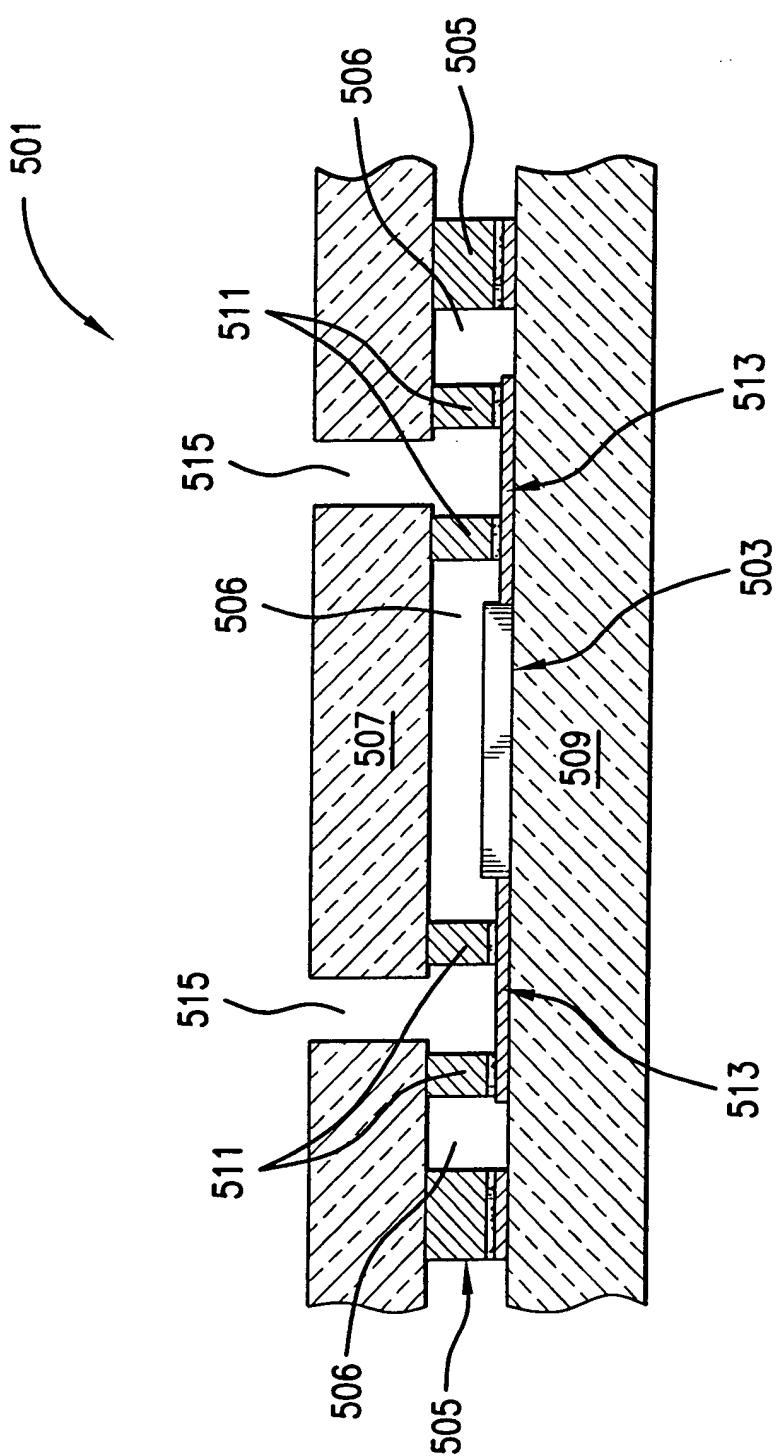

**[0020]** [Fig. 5](#) alternative Dichtungskonfigurationen in einem Waferbenenengehäuse.

**[0021]** [Fig. 2A](#) zeigt eine Querschnittsansicht eines bevorzugten Ausführungsbeispiels, das gemäß den Lehren der vorliegenden Erfindung hergestellt ist. Eine Dichtung **201** auf einem Abdeckungswafer **203** umgibt ein Bauelement **205**, das auf einem Basiswafer **107** hergestellt ist, und dichtet dasselbe ab. Das Bauelement **205** ist ein beliebiges mikroelektronisches Bauelement, wie z. B. eine mikroelektromechanische Systemstruktur (MEMS; MEMS = microelectromechanical system) oder eine elektronische Schaltung. Typischerweise sind die Wafer aus Silizium hergestellt. Die Wafer können auch aus Glas, Keramik oder einem anderen Halbleitermaterial hergestellt sein, ohne von dem Schutzbereich der vorliegenden Erfindung abzuweichen.

**[0022]** [Fig. 2B](#) zeigt eine Von-Oben-Nach-Unten-Ansicht der vorliegenden Erfindung entlang der Linie B-B' in [Fig. 2A](#). Wie es in [Fig. 2B](#) deutlicher ersichtlich ist, umgibt die Dichtung **201** das Bauelement **205** vollständig und umschließt dasselbe. Obwohl die Dichtung **201** als ein Rechteck gezeigt ist, kann die Dichtung **201** ein Quadrat, ein Kreis, ein Oval, ein Rechteck oder jede andere Form sein, die das Bauelement **205** umschließt.

**[0023]** Mit Bezugnahme auf [Fig. 2A](#) ist die Dichtung **201** aus einem Abdeckungswafer **203** geschnitten oder geätzt und mit Verbindungsmaterial **209** an dem Basiswafer **207** verbunden. Das Verbindungsmaterial **209** kann eine oder mehrere von vielen Substanzen sein, die eine annehmbare Haftung, Abdichtung, Hermetizität und andere Eigenschaften zeigen, die sicherstellen, daß das Bauelement **205** nicht durch die externe Umgebung beschädigt wird. Das Verbindungsmaterial **209** kann entweder leitfähig oder nicht leitfähig sein. Zwischen dem Abdeckungswafer **203** und dem Basiswafer **207** ist eine hermetisch abgedichtete Umgebung **211** erzeugt, um das Bauelement **205** zu schützen. Die hermetisch abgedichtete Umgebung **211** kann ein vollständiges Vakuum sein, oder mit einem Inertgas oder einer anderen Substanz gefüllt sein.

**[0024]** [Fig. 3A](#) – [Fig. 3E](#) zeigen die Herstellung eines Waferbenenengehäuses, bei dem die Dichtung mit leitfähigem Verbindungsmaterial verbunden ist.

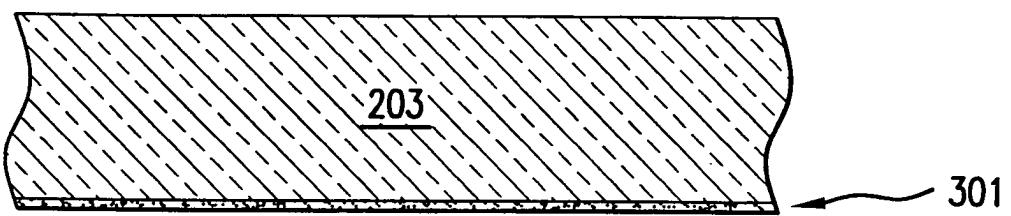

**[0025]** [Fig. 3A](#) zeigt den Abdeckungswafer **203**. Der Abdeckungswafer **203** wird typischerweise aus Schmelzzonensilizium mit einem sehr hohen spezifischen Widerstand gebildet, um HF-Kopplungsprobleme mit dem Bauelement **205** (nicht gezeigt) zu vermeiden. Leitfähiges Verbindungsmaterial **301** wird an die Oberfläche des Abdeckungswafers **203** angelegt. Mögliche leitfähige Verbindungsmaterialien sind Gold, Gold-Zinn-Legierungen, Palladium-Zinn-Legierungen, Zinn-Blei-Legierungen und andere Metalle.

**[0026]** In [Fig. 3B](#) wird leitfähiges Verbindungsmate-

rial **301** mit Photoresist **303** strukturiert, dann unter Verwendung eines herkömmlichen photolithographischen Prozesses belichtet und entwickelt, um ausgewählte Abschnitte des leitfähigen Verbindungsmaterials **301** zu entfernen.

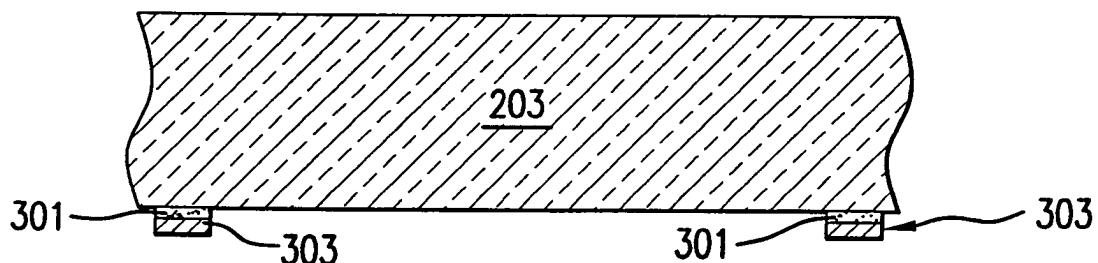

**[0027]** In [Fig. 3C](#) wird das bestehende Photoresist **303** als eine Maske verwendet, um den Abdeckungswafer **203** zu ätzen. Ausgewählte Abschnitte des Abdeckungswafermaterials werden entfernt, um die Dichtung **201** zu erzeugen. Jeder herkömmliche Ätzprozeß kann verwendet werden, wie z. B. reaktives Ionenätzen (RIE; RIE = reactive ion etching) oder tiefes reaktives Ionenätzen (DRIE; DRIE = deep reactive ion etching). Die Dichtung **201** wird aus dem gleichen Material erzeugt wie der Abdeckungswafer **203**. Normalerweise ist das Material Silizium, das eine gute Starrheit und Hermetizität aufweist. Bei tatsächlichen Arbeitsumgebungen ist die Dichtung **201** zwischen 3 – 12 µm breit und 4 – 10 µm tief. Andere Größen für die Dichtungsbreite und -tiefe können verwendet werden, um den gleichen Zweck zu erreichen. Das Photoresist **303** wird entfernt, nachdem die Dichtung **201** gebildet ist.

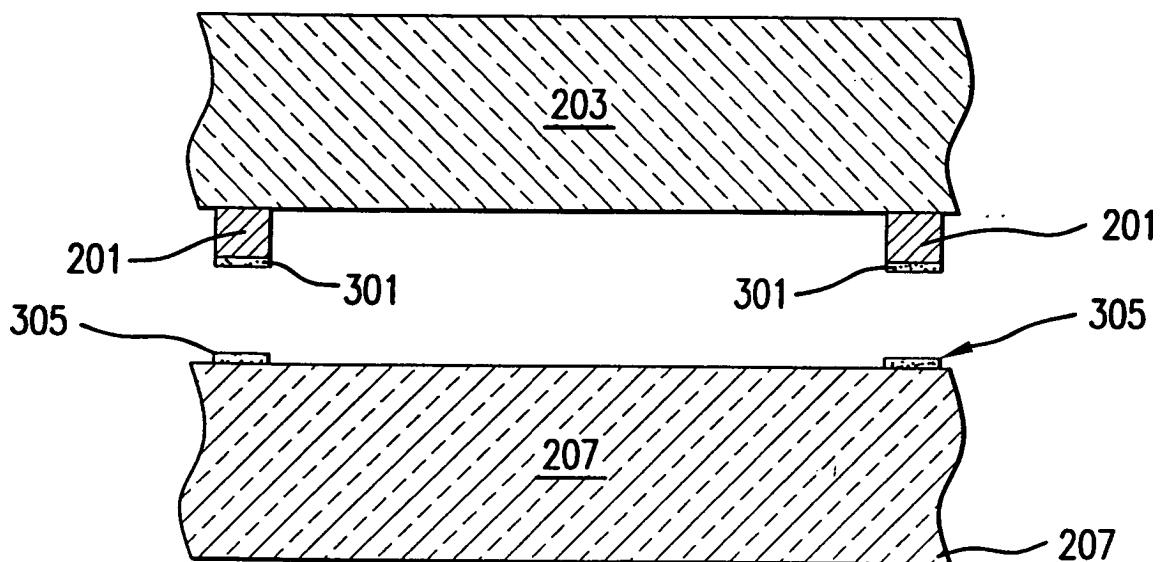

**[0028]** [Fig. 3D](#) zeigt die Ausrichtung der Dichtung **201** mit einer zusammenpassenden Anschlußfläche **305** auf dem Basiswafer **207**. Die zusammenpassende Anschlußfläche **305** kann aus jedem Material hergestellt sein, das sich mit leitfähigem Verbindungsmaterial **301** verbindet. Falls das leitfähige Verbindungsmaterial **301** beispielsweise Gold ist, kann die zusammenpassende Anschlußfläche **305** aus Gold, einer Gold-Zinn-Legierung, einer Zinn-Blei-Legierung usw. gebildet sein.

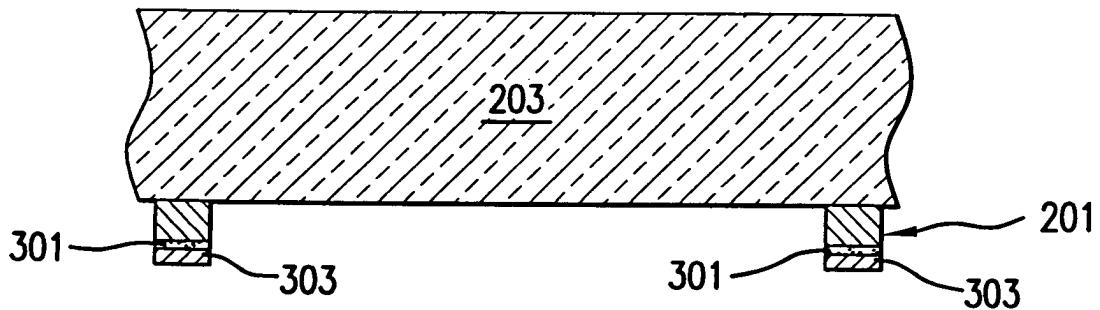

**[0029]** In [Fig. 3E](#) sind der Abdeckungswafer **203** und der Basiswafer **207** miteinander verbunden, um eine hermetisch abgedichtete Umgebung **211** zu erzeugen. Während dem Verbinden werden für das System und den Dichtungsbereich eine geeignete Kraft und Temperatur verwendet. In einem tatsächlichen Arbeitsausführungsbeispiel, bei dem das leitfähige Verbindungsmaterial **301** und die zusammenpassende Anschlußfläche **305** beide aus Gold waren, wurde eine Kraft von 20 Kilonewton bei 330°C für 5 – 10 Minuten angelegt, um eine effektive Verbindung zu erreichen. Diese Werte sind nur zu Darstellungszwecken offenbart. Es sollte klar sein, daß diese Werte variieren können, während sie trotzdem das gleiche Verbindungsergebnis erzielen. Falls die angelegte Kraft beispielsweise auf 8 Kilonewton reduziert wird, werden 20 – 40 Minuten bei 330°C benötigt, um eine effektive Verbindung zu erreichen. Die besten Ergebnisse werden erreicht, wenn die Verbindung in einer Vakuumumgebung durchgeführt wird, oder in einem Inertgas, wie z. B. Nitrogen. Die verbundenen Wafer können durch herkömmliche Einrichtungen herunter gedünnt werden, falls dies erforderlich ist.

**[0030]** Die in [Fig. 3A](#) – [Fig. 3E](#) gezeigten Schritte lehren das Aufbringen von leitfähigem Verbindungs material **301** auf die Dichtung **201**, bevor der Abdeckungswafer **203** und der Basiswafer **207** miteinander verbunden werden. Alternativ kann das leitfähige Verbindungsmaterial **301** auf die zusammenpassende Anschlußfläche **305** statt auf die Dichtung **201** aufgebracht werden, oder sowohl auf die zusammenpassende Anschlußfläche **305** als auch auf die Dichtung **201**, um die gleiche Verbindung in dem Waferebenengehäuse zu erreichen.

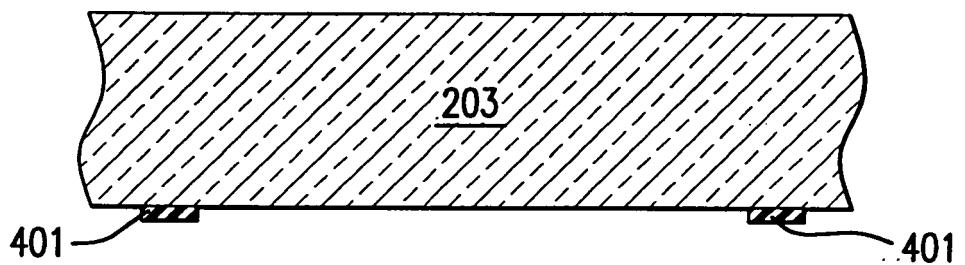

**[0031]** [Fig. 4A](#) – [Fig. 4E](#) zeigt die Herstellung eines Waferebenengehäuses mit einer Dichtung, die mit nichtleitfähigem Verbindungsmaterial verbunden ist.

**[0032]** [Fig. 4A](#) zeigt den Abdeckungswafer **203** mit nichtleitfähigem Verbindungsmaterial **401**, das bereits in der Form einer Dichtung strukturiert ist. Ein Vorteil des Verwendens von nichtleitfähigem Verbindungsmaterial **401** ist es, daß Signalleitungen sicher unter der Dichtung geführt werden können. Eine mögliche Auswahl für nichtleitfähige Materialien sind Polyimide, B-Zustand-Bisbenzocyclobutene (BCB; BCB = bisbenzocyclobutene), andere Polymere oder Glas. Diese Materialien können photoempfindlich sein oder nicht. Wenn nichtleitfähiges Verbindungsmaterial **401** photoempfindlich ist, kann es unter Verwendung von herkömmlicher Photolithographie geformt werden. Wenn nichtleitfähiges Verbindungsmaterial **401** nicht photoempfindlich ist, ist ein Maskierprozeß nötig, um nichtleitfähiges Verbindungsmaterial **401** in die gewünschte Struktur zu formen.

**[0033]** In [Fig. 4B](#) werden Abschnitte des Abdeckungswafers **203** entfernt, um die Dichtung **201** unter Verwendung eines beliebigen Standardätzprozesses, wie z. B. RIE oder DRIE, zu erzeugen. Das bestehende nichtleitfähige Material **401** wird als eine Maske zum Ätzen der Dichtung **201** verwendet.

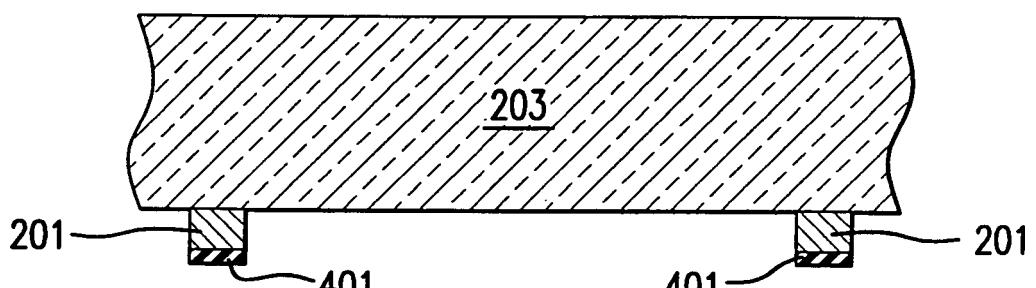

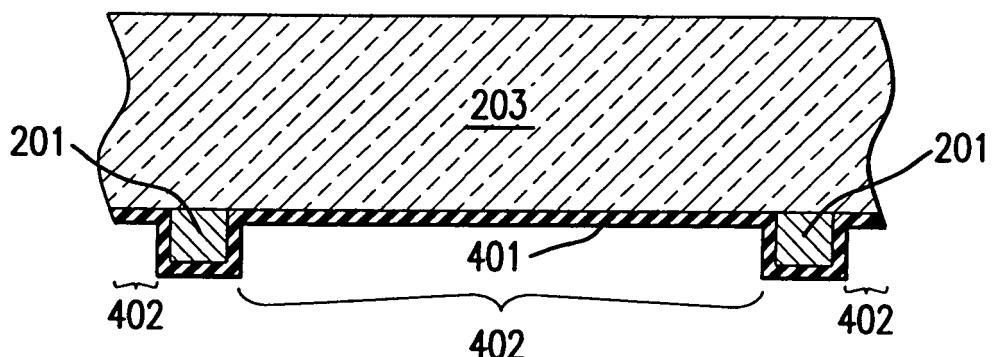

**[0034]** [Fig. 4C](#) zeigt ein alternatives Verfahren zum Aufbringen nichtleitfähigen Verbindungsmaterials **401**. Die Dichtung **201** kann zuerst erzeugt werden, bevor eine Schicht aus nichtleitfähigem Verbindungsmaterial **401** auf die gesamte Oberfläche des Abdeckungswafers **203** aufgebracht wird. Obwohl das Verbindungsmaterial auf den Bereichen **402** als auch auf der Dichtungsverbindungsoberfläche sein wird, können diese Bereiche **402** auf dem Abdeckungswafer **203** belassen werden, da das Material nicht leitfähig ist. Ein zusätzlicher Maskierschritt kann verwendet werden, um das Verbindungsmaterial in den Bereichen **402** zu entfernen, falls dies gewünscht ist.

**[0035]** [Fig. 4D](#) zeigt die Ausrichtung der Dichtung **201** mit einer zusammenpassenden Anschlußfläche **403** auf dem Basiswafer **207**. Die zusammenpassende Anschlußfläche **403** kann aus jedem Material hergestellt sein, das sich mit nichtleitfähigem Verbin-

dungsmaterial **401** verbindet. Falls das nichtleitfähige Verbindungsmaterial beispielsweise ein Polyimid ist, kann die zusammenpassende Anschlußfläche **403** auch ein Polyimid sein. Um die Verbindung zu verbessern, kann die zusammenpassende Anschlußfläche **403** mit einem Haftungspromotor behandelt werden, wie z. B. Tantalkarbid (TaC) oder Siliziumkarbid (SiC). TaC und SiC weisen beide exzellente Haftung an Silizium auf und bilden entweder chemische oder kovalente Verbindungen mit Polymer. Der Haftungspromoter kann durch chemische Dampfaufbringung (CVD) aufgebracht werden, durch Sputtern bzw. Zerstäuben oder einen anderen ähnlichen Dünnfilmaufbringungsprozeß, und dann durch Photomaskier- und Ätzprozesse strukturiert werden. Alternativ kann sich die Dichtung **201** direkt mit dem Basiswafer **207** verbinden, ohne die zusammenpassende Anschlußfläche **403**. Ein Haftungspromoter kann nach wie vor verwendet werden, um den Verbindungsprozeß zu verbessern.

**[0036]** In [Fig. 4E](#) sind der Abdeckungswafer **203** und der Basiswafer **207** miteinander verbunden, um eine hermetisch abgedichtete Umgebung **211** zu bilden. Während der Verbindung werden für das System und den Dichtungsbereich eine geeignete Kraft und Temperatur verwendet. Die besten Ergebnisse werden erreicht, wenn die Verbindung in einer Vakuumumgebung oder einem Inertgas, wie z. B. Nitrogen, durchgeführt wird. Falls notwendig, können die verbundenen Wafer durch herkömmliche Einrichtungen gedünnt werden.

**[0037]** Die in [Fig. 4A](#) – [Fig. 4E](#) gezeigten Schritte lehren das Aufbringen von nichtleitfähigem Verbindungsmaterial **401** auf die Dichtung **201**, bevor der Abdeckungswafer **203** und der Basiswafer **207** miteinander verbunden werden. Alternativ kann das nichtleitfähige Verbindungsmaterial **401** auf die zusammenpassende Anschlußfläche **403** statt auf die Dichtung **201** aufgebracht werden, oder sowohl auf die zusammenpassende Anschlußfläche **403** als auch auf die Dichtung **201**, um die gleiche Verbindung in dem Waferebenengehäuse zu erreichen. Oder, falls keine zusammenpassende Anschlußfläche **403** verwendet wird, kann das nichtleitfähige Verbindungsmaterial **401** direkt an der Verbindungsstelle auf den Basiswafer **207** aufgebracht werden.

**[0038]** [Fig. 5](#) zeigt alternative Dichtungskonfigurationen in einem Waferebenengehäuse **501**. Wenn das Bauelement **503** in Kontakt mit der externen Umgebung kommen muß, während dasselbe innerhalb einer hermetisch abgedichteten Umgebung bleibt, können mehrere Ebenen von Dichtungen verwendet werden. Eine äußere Hauptdichtung **505** erzeugt eine hermetisch abgedichtete Umgebung **506** zwischen einem Abdeckungswafer **507** und einem Basiswafer **509**. Löcher **515** in dem Abdeckungswafer **507** ermöglichen einen Zugriff auf die Anschlußflä-

chen **513**. Sekundäre innere Dichtungen **511** dichten die Löcher **515** von der hermetisch abgedichteten Umgebung ab, wodurch das Bauelement **503** geschützt bleibt.

## Patentansprüche

1. Verfahren zum Herstellen eines Waferebenengehäuses, das folgende Schritte umfaßt:

Liefern eines ersten Wafers (**203**) und eines zweiten Wafers (**207**);

Entfernen eines Teils von dem ersten Wafer, um eine Dichtung (**201**) zu bilden;

Bilden einer Anschlußfläche (**305**) auf dem zweiten Wafer, wobei die Anschlußfläche (**305**) im wesentlichen mit der Dichtung übereinstimmt;

Einfügen von Verbindungsmaterial (**209**) zwischen die Dichtung (**201**) und die Anschlußfläche (**305**); und

Verbinden der Dichtung (**201**) mit der Anschlußfläche (**305**) mit dem Verbindungsmaterial (**209**), um zwischen dem ersten (**203**) und dem zweiten Wafer (**207**) eine hermetisch abgedichtete Umgebung (**211**) zu erzeugen,

wobei die Dichtung (**201**) nicht mehr als 20 µm breit ist.

2. Verfahren gemäß Anspruch 1, bei dem der erste Wafer (**203**) aus Silizium besteht.

3. Verfahren gemäß Anspruch 1, bei dem die Dichtung (**201**) nicht mehr als 10 µm breit ist.

4. Verfahren gemäß Anspruch 1 oder 3, bei dem das Einfügen von Verbindungsmaterial (**209**) das Aufbringen von Verbindungsmaterial auf die Dichtung umfaßt.

5. Verfahren gemäß Anspruch 1 oder 3, bei dem das Einfügen von Verbindungsmaterial (**209**) das Aufbringen von Verbindungsmaterial (**209**) auf die Anschlußfläche (**305**) umfaßt.

6. Verfahren gemäß einem der Ansprüche 1 bis 5, bei dem das Verbindungsmaterial (**209**) leitfähiges Verbindungsmaterial (**301**) umfaßt.

7. Verfahren gemäß Anspruch 6, bei dem das leitfähige Verbindungsmaterial ein Metall ist, das von der Gruppe ausgewählt ist, die aus Gold, Gold-Zinn, Zinn-Blei und Palladium-Zinn besteht.

8. Verfahren gemäß einem der Ansprüche 1 bis 5, bei dem das Verbindungsmaterial (**209**) ein nichtleitfähiges Verbindungsmaterial (**401**) umfaßt.

9. Verfahren gemäß Anspruch 8, bei dem das nichtleitfähige Verbindungsmaterial ein Material ist, das von der Gruppe ausgewählt ist, die aus Polyimid, B-Zustands-Bisbenzocyclobuten (BCB) und Glas besteht.

10. Verfahren gemäß Anspruch 9, bei dem das Einfügen eines Haftungspromoters zwischen die Dichtung (201) und die Anschlußfläche (305) nach dem Einbringen von Verbindungsmaterial auftritt.

11. Waferebenengehäuse, das folgende Merkmale umfaßt:

einen ersten Wafer (203) und einen zweiten Wafer (207);

eine Dichtung (201), die aus dem ersten Wafer (203) gebildet ist;

eine Anschlußfläche (305) auf dem zweiten Wafer (207), die im wesentlichen mit der Dichtung (201) übereinstimmt; und

Verbindungsmaterial (209), das die Dichtung (201) und die Anschlußfläche (305) verbindet,

wobei die Dichtung (201) nicht mehr als 20 µm breit ist.

12. Waferebenengehäuse gemäß Anspruch 11, bei dem der erste Wafer (203) aus Silizium gebildet ist.

13. Waferebenengehäuse gemäß Anspruch 11, bei dem die Dichtung (201) nicht mehr als 10 µm breit ist.

14. Waferebenengehäuse gemäß Anspruch 11 oder 13, bei dem das Verbindungsmaterial (209) leitfähiges Verbindungsmaterial umfaßt.

15. Waferebenengehäuse gemäß Anspruch 14, bei dem das leitfähige Verbindungsmaterial ein Metall ist, das von der Gruppe ausgewählt ist, die aus Gold, Gold-Zinn, Zinn-Blei und Palladium-Zinn besteht.

16. Waferebenengehäuse gemäß Anspruch 11 oder 13, bei dem das Verbindungsmaterial (209) nichtleitfähiges Verbindungsmaterial (401) umfaßt.

17. Waferebenengehäuse gemäß Anspruch 16, bei dem das nichtleitfähige Verbindungsmaterial ein Material ist, das von der Gruppe ausgewählt ist, die aus Polyimid, B-Zustands-Bisbenzocyclobuten (BCB) und Glas besteht.

18. Waferebenengehäuse, das folgende Merkmale umfaßt:

einen ersten Wafer (203) und einen zweiten Wafer (207);

eine Dichtung (201), die aus dem ersten Wafer (203) gebildet ist; und

Verbindungsmaterial (209), das die Dichtung (201) und den zweiten Wafer (207) verbindet,

wobei die Dichtung (201) weniger als 20 µm breit ist.

19. Waferebenengehäuse gemäß Anspruch 18, bei dem die Dichtung (201) weniger als 10 µm breit ist.

20. Waferebenengehäuse gemäß Anspruch 18 oder 19, bei dem das Verbindungsmaterial nichtleitfähig ist.

21. Waferebenengehäuse gemäß Anspruch 20, bei dem das nichtleitfähige Verbindungsmaterial von der Gruppe ausgewählt ist, die aus Polyimid, B-Zustands-Bisbenzocyclobuten (BCB) und Glas besteht.

Es folgen 7 Blatt Zeichnungen

Anhängende Zeichnungen

FIG. 2B

FIG. 3A

FIG. 3B

FIG. 3C

FIG. 3D

FIG. 3E

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 4D

FIG. 4E

FIG. 5