(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7577643号**

**(P7577643)**

(45)発行日 令和6年11月5日(2024.11.5)

(24)登録日 令和6年10月25日(2024.10.25)

|                         |               |

|-------------------------|---------------|

| (51)国際特許分類              | F I           |

| H 04 N 25/60 (2023.01)  | H 04 N 25/60  |

| H 04 N 5/33 (2023.01)   | H 04 N 5/33   |

| H 04 N 25/771 (2023.01) | H 04 N 25/771 |

| H 01 L 27/146 (2006.01) | H 01 L 27/146 |

| H 01 L 27/144 (2006.01) | H 01 L 27/144 |

請求項の数 7 (全37頁)

(21)出願番号 特願2021-504891(P2021-504891)

(86)(22)出願日 令和2年2月21日(2020.2.21)

(86)国際出願番号 PCT/JP2020/007045

(87)国際公開番号 WO2020/184149

(87)国際公開日 令和2年9月17日(2020.9.17)

審査請求日 令和5年2月14日(2023.2.14)

(31)優先権主張番号 特願2019-43786(P2019-43786)

(32)優先日 平成31年3月11日(2019.3.11)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 316005926

ソニーセミコンダクタソリューションズ

株式会社

神奈川県厚木市旭町四丁目14番1号

(74)代理人 110001357

弁理士法人つばさ国際特許事務所

鈴木 三佐男

神奈川県厚木市旭町四丁目14番1号

ソニーセミコンダクタソリューションズ

株式会社内

花田 尚樹

審査官

最終頁に続く

(54)【発明の名称】 撮像素子および撮像装置

**(57)【特許請求の範囲】****【請求項1】**

各々が光電変換部と、前記光電変換部から出力された電荷に基づく画素信号を出力する読み出し回路とを含む複数のセンサ画素と、

前記画素信号に基づく制御電圧を各前記光電変換部に印加する電圧制御部と、

変換効率制御部と

を備え、

各前記センサ画素は、

前記光電変換部から転送された電荷を保持する電荷保持部と、

前記光電変換部から前記電荷保持部に電荷を転送する転送トランジスタと、

前記電荷保持部に接続されたスイッチ素子と、

前記スイッチ素子を介して前記電荷保持部の容量と並列に接続された補助容量と

を更に有し、

前記変換効率制御部は、前記画素信号に基づいて前記スイッチ素子のオンオフを制御し、

前記変換効率制御部は、前記画素信号が第1閾値を超えたときに前記スイッチ素子をオフし、前記画素信号が前記第1閾値よりも小さな第2閾値を下回ったときに前記スイッチ素子をオンする

撮像素子。

**【請求項2】**

前記電圧制御部は、前記画素信号が前記第1閾値を超えたときに前記制御電圧を、前記

第2閾値を下回ったときの前記制御電圧と比べて相対的に大きくし、前記画素信号が前記第2閾値を下回ったときに前記制御電圧を、前記画素信号が前記第1閾値を超えたときの前記制御電圧と比べて相対的に小さくする

請求項1に記載の撮像素子。

**【請求項3】**

各前記センサ画素は、前記光電変換部を挟み込む第1電極および第2電極を更に有し、前記電圧制御部は、前記第1電極に印加する第1電圧と、前記第2電極に印加する第2電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第1電圧および前記第2電圧を生成する

請求項1に記載の撮像素子。

10

**【請求項4】**

各前記センサ画素は、前記光電変換部の電荷を初期化する排出トランジスタを更に含み、前記転送トランジスタは、前記第2電極に電気的に接続され、前記排出トランジスタは、前記第2電極に電気的に接続され、前記電圧制御部は、前記排出トランジスタがオンしているときに、前記第2電極に前記第2電圧を印加する

請求項3に記載の撮像素子。

**【請求項5】**

各前記センサ画素は、前記光電変換部を挟み込む第1電極および第2電極を更に含み、前記転送トランジスタは、前記第2電極に電気的に接続され、前記読み出し回路は、前記電荷保持部の電位を初期化するリセットトランジスタを有し、前記電圧制御部は、前記第1電極に印加する第1電圧と、前記転送トランジスタがオンしているときに前記リセットトランジスタによって印加された前記第2電極の第2電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第1電圧を生成する

20

請求項1に記載の撮像素子。

**【請求項6】**

各前記センサ画素は、前記光電変換部を挟み込む第1電極および第2電極を更に含み、前記読み出し回路は、前記電荷保持部の電位を初期化するリセットトランジスタを有し、前記電圧制御部は、前記第1電極に印加する第1電圧と、前記リセットトランジスタによって印加された前記第2電極の第2電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第1電圧を生成する

30

請求項1に記載の撮像素子。

**【請求項7】**

各々が光電変換部と、前記光電変換部から出力された電荷に基づく画素信号を出力する読み出し回路とを含む複数のセンサ画素を有する撮像素子と、

前記画素信号に基づく制御電圧を各前記光電変換部に印加する画質制御回路とを備え、

各前記センサ画素は、

前記光電変換部から転送された電荷を保持する電荷保持部と

前記光電変換部から前記電荷保持部に電荷を転送する転送トランジスタと

40

前記電荷保持部に接続されたスイッチ素子と、

前記スイッチ素子を介して前記電荷保持部の容量と並列に接続された補助容量と、

前記画素信号に基づいて前記スイッチ素子のオンオフを制御する変換効率制御部とを更に有し、

前記変換効率制御部は、前記画素信号が第1閾値を超えたときに前記スイッチ素子をオフし、前記画素信号が前記第1閾値よりも小さな第2閾値を下回ったときに前記スイッチ素子をオンする

撮像装置。

**【発明の詳細な説明】**

**【技術分野】**

50

**【0001】**

本開示は、撮像素子および撮像装置に関する。

**【背景技術】****【0002】**

近年、赤外領域に感度を有する撮像素子（赤外線センサ）が商品化されている。例えば、特許文献1では、このような赤外線センサにInGaAs（インジウムガリウム砒素）等のIII-V族半導体を光電変換部として用いることが記載されている。この光電変換部において、赤外線が吸収されることで電荷が発生する。

**【先行技術文献】****【特許文献】**

10

**【0003】**

【文献】国際公開WO 2017 / 150167

**【発明の概要】****【0004】**

このような撮像素子では、画質の低下を抑えることが望まれている。従って、画質の低下を抑えることが可能な撮像素子および撮像装置を提供することが望ましい。

**【0005】**

本開示の一実施の形態に係る撮像素子は、複数のセンサ画素と、電圧制御部とを備えている。各センサ画素は、光電変換部と、光電変換部から出力された電荷に基づく画素信号を出力する読み出し回路とを含む。電圧制御部は、画素信号に基づく制御電圧を各光電変換部に印加する。

20

**【0006】**

本開示の一実施の形態に係る撮像装置は、撮像素子と、画質制御回路とを備えている。撮像素子は、複数のセンサ画素を有している。各センサ画素は、光電変換部と、光電変換部から出力された電荷に基づく画素信号を出力する読み出し回路とを含む。画質制御回路は、画素信号に基づく制御電圧を各光電変換部に印加する。

**【0007】**

本開示の一実施の形態に係る撮像素子および撮像装置では、画素信号に基づく制御電圧が各光電変換部に印加される。これにより、撮像素子で得られる画像データの画質が制御されるので、各光電変換部に固定電圧を印加した場合と比べて、画像データの輝度の大きさに応じた画質調整が行われ得る。

30

**【図面の簡単な説明】****【0008】**

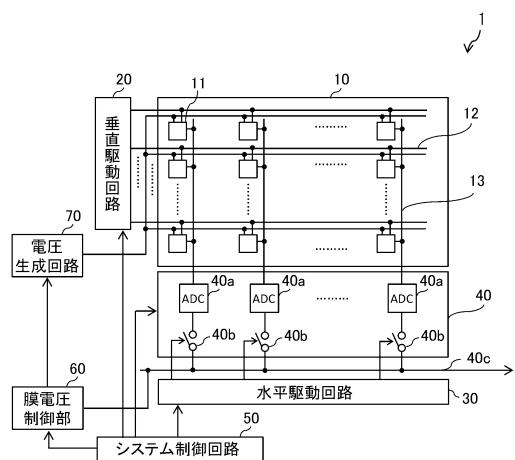

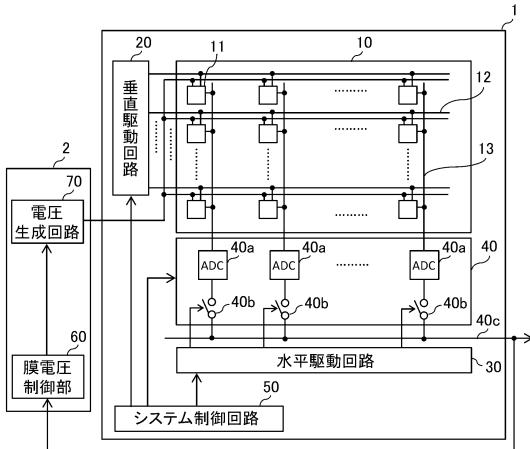

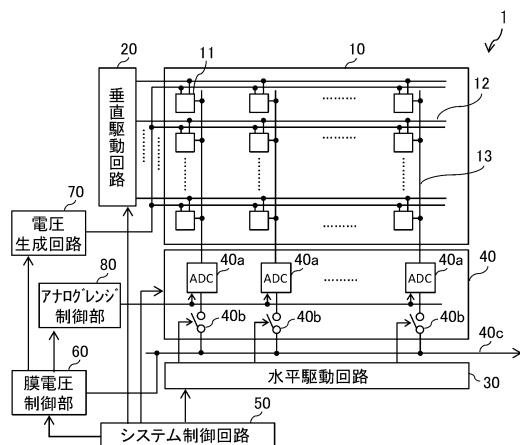

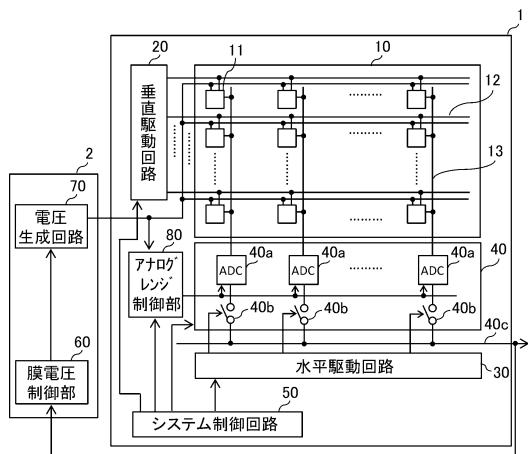

【図1】本開示の第1の実施形態に係る撮像素子の概略構成例を表す図である。

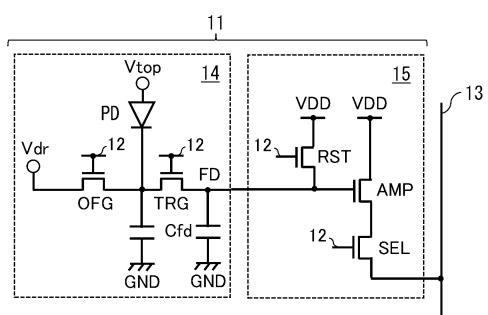

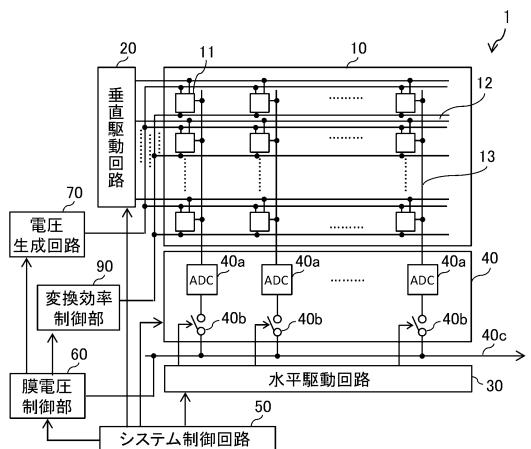

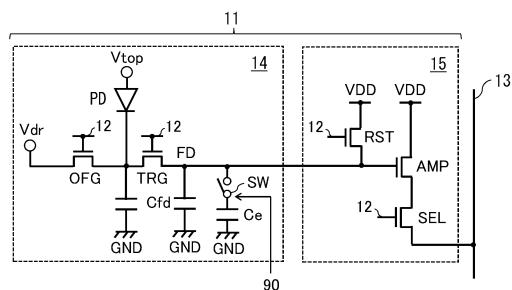

【図2】図1のセンサ画素の回路構成例を表す図である。

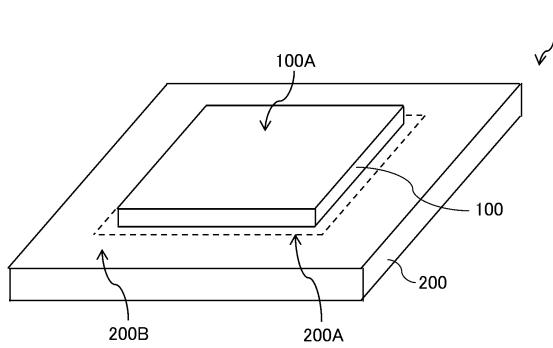

【図3】図1の撮像素子の斜視構成例を表す図である。

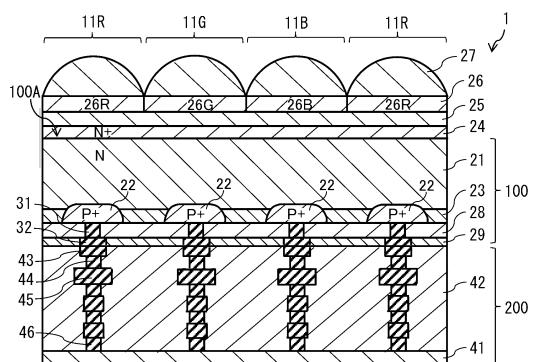

【図4】図3の撮像素子の断面構成例を表す図である。

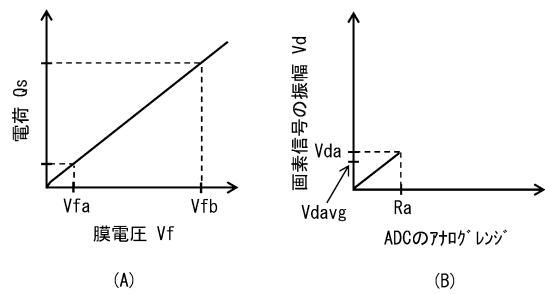

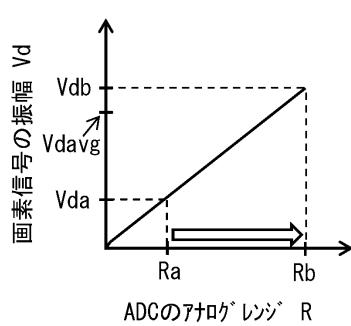

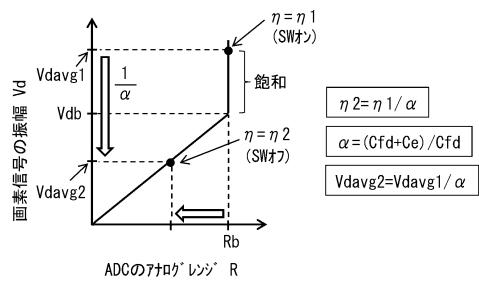

【図5】(A)図1の撮像素子の膜電圧と保持可能な電荷との関係の一例を表す図である。(B)ADCのアナログレンジと画素信号の振幅との関係の一例を表す図である。

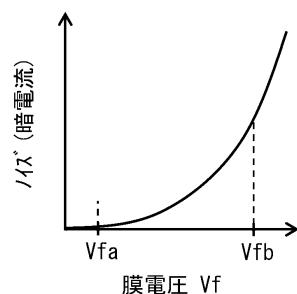

【図6】図1の撮像素子の膜電圧とノイズとの関係の一例を表す図である。

40

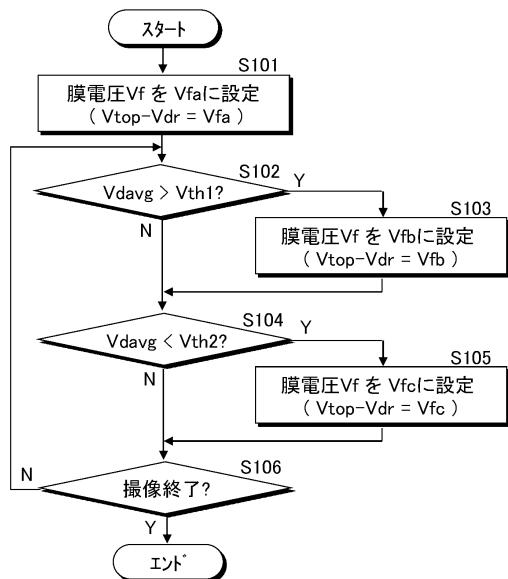

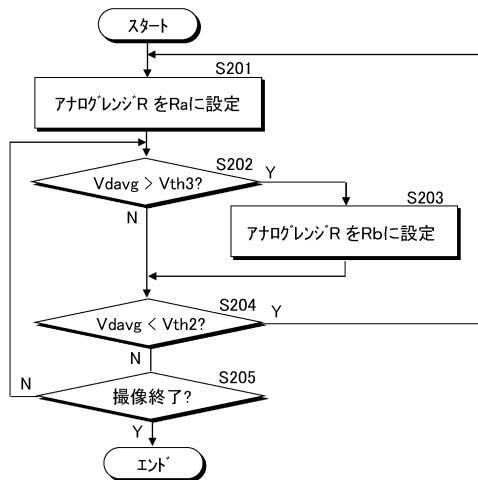

【図7】図1の撮像素子の画質調整手順の一例を表す図である。

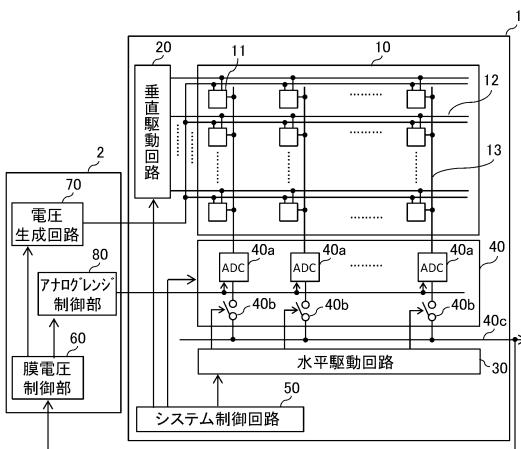

【図8】図1の撮像素子の概略構成の一変形例を表す図である。

【図9】図1の撮像素子の概略構成の一変形例を表す図である。

【図10】ADCのアナログレンジと画素信号の振幅との関係の一例を表す図である。

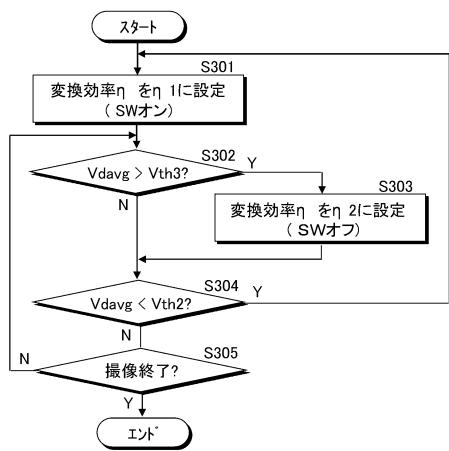

【図11】図9の撮像素子の画質調整手順の一例を表す図である。

【図12】図9の撮像素子の概略構成の一変形例を表す図である。

【図13】図9の撮像素子の概略構成の一変形例を表す図である。

【図14】図1の撮像素子の概略構成の一変形例を表す図である。

【図15】図14のセンサ画素の回路構成例を表す図である。

【図16】ADCのアナログレンジと画素信号の振幅との関係の一例を表す図である。

50

【図17】図14の撮像素子の画質調整手順の一例を表す図である。

【図18】図14の撮像素子の概略構成の一変形例を表す図である。

【図19】図14の撮像素子の概略構成の一変形例を表す図である。

【図20】図2のセンサ画素の回路構成の一変形例を表す図である。

【図21】図15のセンサ画素の回路構成の一変形例を表す図である。

【図22】図2のセンサ画素の回路構成の一変形例を表す図である。

【図23】図15のセンサ画素の回路構成の一変形例を表す図である。

【図24】図3の撮像素子の断面構成の一変形例を表す図である。

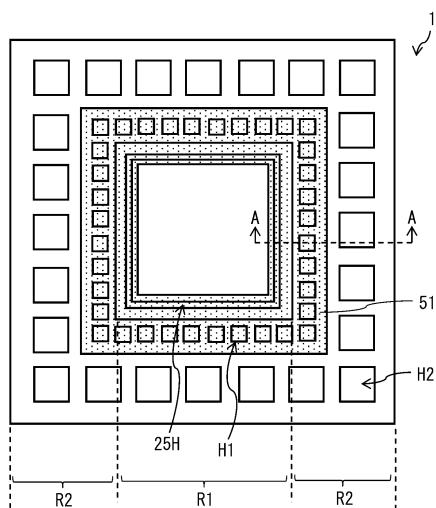

【図25】図1の撮像素子の平面構成の一例を表す図である。

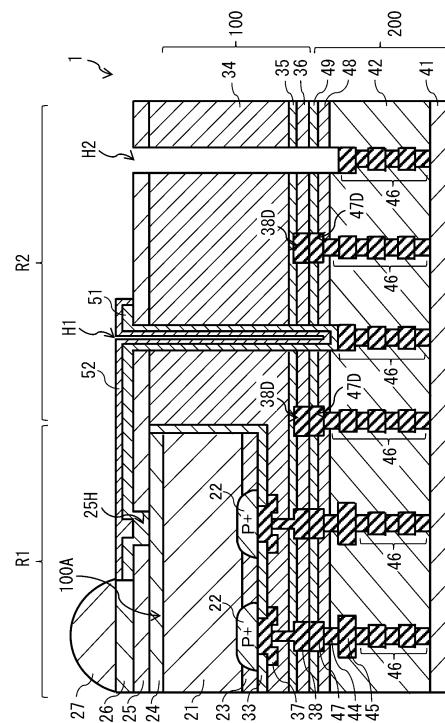

【図26】図25の撮像素子のA-A線での断面構成の一例を表す図である。

10

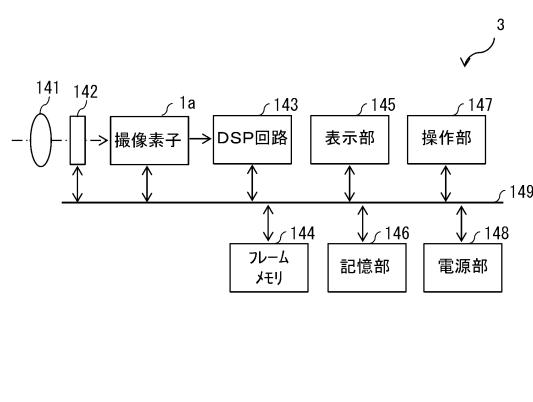

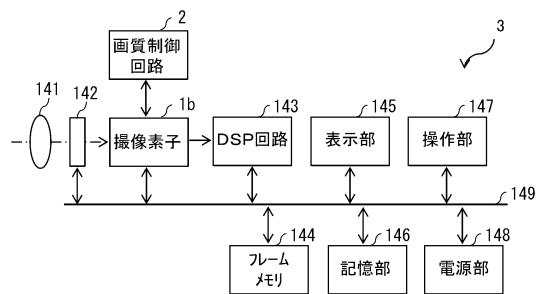

【図27】本開示の第2の実施形態に係る撮像装置の概略構成例を表す図である。

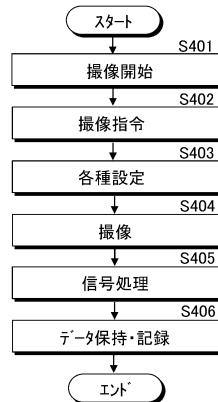

【図28】図27の撮像装置における撮像手順の一例を表す図である。

【図29】図27の撮像装置の概略構成の一変形例を表す図である。

【図30】車両制御システムの概略的な構成の一例を示すブロック図である。

【図31】車外情報検出部及び撮像部の設置位置の一例を示す説明図である。

【図32】内視鏡手術システムの概略的な構成の一例を示す図である。

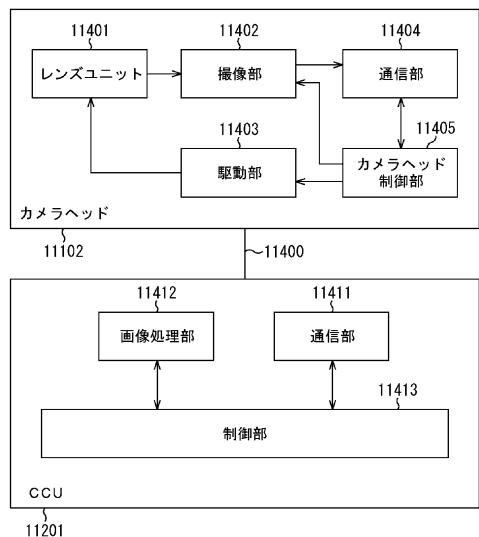

【図33】カメラヘッド及びCCUの機能構成の一例を示すブロック図である。

【発明を実施するための形態】

【0009】

以下、本開示を実施するための形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

20

1. 第1の実施の形態（撮像素子）…図1～図7

2. 第1の実施の形態の変形例（撮像素子）…図8～図26

3. 第2の実施の形態（撮像装置）…図27、図28

4. 第2の実施の形態の変形例（撮像装置）…図29

5. 応用例

応用例1（移動体）…図30、図31

応用例2（手術システム）…図32、図33

【0010】

<1. 第1の実施の形態>

30

【構成】

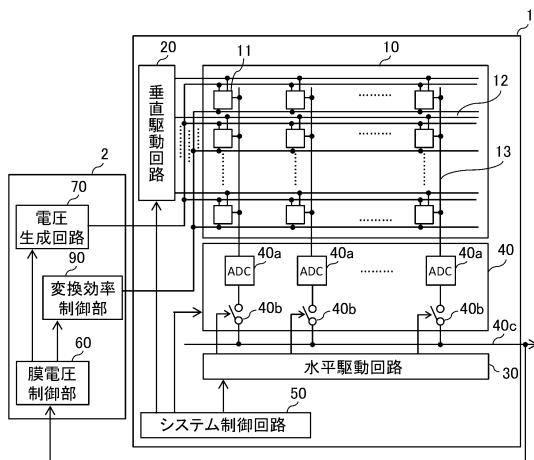

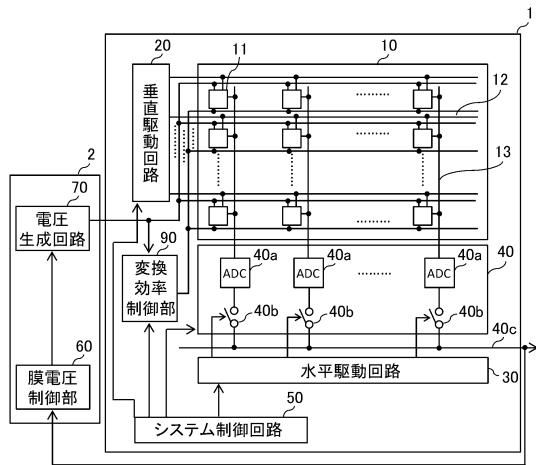

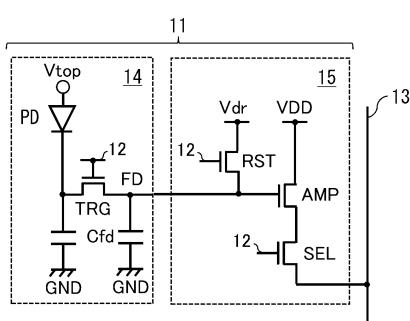

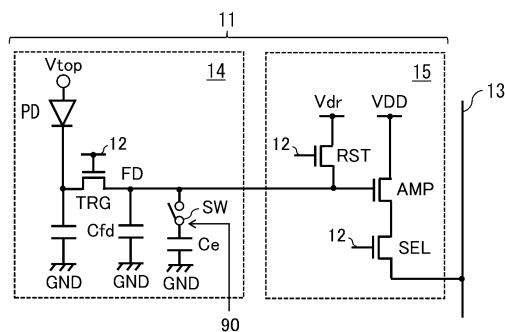

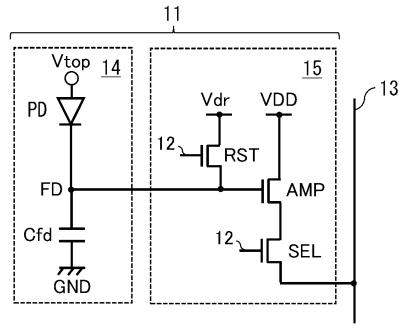

本開示の第1の実施形態に係る撮像素子1について説明する。図1は、撮像素子1の概略構成例を表したものである。撮像素子1は、例えば赤外線イメージセンサであり、例えば波長800nm以上の光に対しても感度を有している。撮像素子1は、光電変換素子を含む複数のセンサ画素11が行列状（マトリックス状）に2次元配置されてなる画素アレイ部10を備えている。センサ画素11は、例えば、図2に示したように、光電変換を行う画素回路14と、画素回路14から出力された電荷に基づく画素信号を出力する読み出し回路15とによって構成されている。

【0011】

画素回路14は、例えば、フォトダイオードPDと、転送トランジスタTRGと、フローティングディフェュージョンFDと、排出トランジスタOFGとを有している。転送トランジスタTRGおよび排出トランジスタOFGは、例えば、NMOS（Metal Oxide Semiconductor）トランジスタである。フォトダイオードPDは、本開示の「光電変換部」の一具体例に相当する。

40

【0012】

フォトダイオードPDは、所定の波長の光（例えば、波長900nm～1700nmの赤外領域の波長の光）を吸収して、信号電荷を発生する光電変換部である。フォトダイオードPDは、例えば、II-V族半導体などの化合物半導体を含んで構成されている。フォトダイオードPDに用いられるII-V族半導体としては、例えば、InGaP、InAlP、InGaAs、InAlAs、またはカルコパイライト構造の化合物半導体

50

などが挙げられる。カルコパイライト構造の化合物半導体は、高い光吸収係数と、広い波長域に渡って高い感度が得られる材料であり、光電変換用のn型半導体材料として好ましく用いられる。フォトダイオードPDは、上述した化合物半導体の他、アモルファスシリコン(Si)、ゲルマニウム(Ge)、量子ドット光電変換膜、有機光電変換膜などを含んで構成されていてもよい。

#### 【0013】

フォトダイオードPDのカソードが、転送トランジスタTRGのソースに接続されており、フォトダイオードPDのアノードが、電圧Vtopが印加される電源線に接続されている。転送トランジスタTRGのドレインがフローティングディフュージョンFDに接続され、転送トランジスタTRGのゲートは画素駆動線12に接続されている。10

#### 【0014】

転送トランジスタTRGは、フォトダイオードPDのカソードとフローティングディフュージョンFDとの間に接続されており、ゲート電極に印加される制御信号に応じて、フォトダイオードPDに保持されている電荷をフローティングディフュージョンFDに転送する。転送トランジスタTRGのドレインがフローティングディフュージョンFDに電気的に接続されており、転送トランジスタTRGのゲートは画素駆動線12に接続されている。

#### 【0015】

フローティングディフュージョンFDは、転送トランジスタTRGを介してフォトダイオードPDから転送された電荷を一時的に保持する浮遊拡散領域である。フローティングディフュージョンFDには、例えば、読み出し回路15が接続されるとともに、読み出し回路15を介して垂直信号線13が接続されている。フローティングディフュージョンFDは、読み出し回路15の入力端に接続されている。20

#### 【0016】

排出トランジスタOFGでは、ドレインが、電圧Vdrが印加される電源線に接続され、ソースがフォトダイオードPDのカソードに接続されている。排出トランジスタOFGは、ゲート電極に印加される制御信号に応じて、フォトダイオードPDの電荷を初期化(リセット)する。

#### 【0017】

読み出し回路15は、例えば、リセットトランジスタRSTと、選択トランジスタSELと、増幅トランジスタAMPとを有している。リセットトランジスタRSTのソース(読み出し回路15の入力端)がフローティングディフュージョンFDに接続されており、リセットトランジスタRSTのドレインが電源線VDDおよび増幅トランジスタAMPのドレインに接続されている。リセットトランジスタRSTのゲートは画素駆動線12に接続されている。増幅トランジスタAMPのソースが選択トランジスタSELのドレインに接続されており、増幅トランジスタAMPのゲートがリセットトランジスタRSTのソースに接続されている。選択トランジスタSELのソース(読み出し回路15の出力端)が垂直信号線13に接続されており、選択トランジスタSELのゲートが画素駆動線12に接続されている。30

#### 【0018】

リセットトランジスタRSTは、フローティングディフュージョンFDの電位を所定の電位に初期化(リセット)する。リセットトランジスタRSTがオン状態となると、フローティングディフュージョンFDの電位を電源線VDDの電位にリセットする。選択トランジスタSELは、読み出し回路15からの画素信号の出力タイミングを制御する。増幅トランジスタAMPは、画素信号として、フローティングディフュージョンFDに保持された電荷のレベルに応じた電圧の信号を生成する。つまり、増幅トランジスタAMPは、画素信号として、センサ画素11における受光量の応じた電圧の信号を生成する。増幅トランジスタAMPは、ソースフォロア型のアンプを構成しており、フォトダイオードPDで発生した電荷のレベルに応じた電圧の画素信号を出力する。増幅トランジスタAMPは、選択トランジスタSELがオン状態となると、フローティングディフュージョンFDの40

電位を増幅して、その電位に応じた電圧を、垂直信号線 13 を介して、後述の水平選択回路 40 に出力する。

#### 【0019】

なお、選択トランジスタ S E L が、電源線 V D D と増幅トランジスタ A M P との間に設けられていてもよい。この場合、リセットトランジスタ R S T のドレインが電源線 V D D および選択トランジスタ S E L のドレインに接続されている。選択トランジスタ S E L のソースが増幅トランジスタ A M P のドレインに接続されており、選択トランジスタ S E L のゲートが画素駆動線 12 に接続されている。増幅トランジスタ A M P のソース（読み出し回路 15 の出力端）が垂直信号線 13 に接続されており、増幅トランジスタ A M P のゲートがリセットトランジスタ R S T のソースに接続されている。

10

#### 【0020】

撮像素子 1 は、例えば、図 3 に示したように、2つの基板（受光基板 100 および駆動基板 200）を備えている。撮像素子 1 は、2つの基板（受光基板 100 および駆動基板 200）を貼り合わせて構成された3次元構造を備えている。

#### 【0021】

受光基板 100 は、シリコン（Si）基板上に、複数のフォトダイオード P D が行列状に形成された基板である。受光基板 100 の上面（駆動基板 200 とは反対側の表面）が受光面 100A となっている。駆動基板 200 は、Si 基板上に、画素信号生成回路領域 200A および周辺回路領域 200B が形成された基板である。画素信号生成回路領域 200A には、複数の画素信号生成回路 45 が行列状に形成されている。各画素信号生成回路 45 は、センサ画素 11 のうちフォトダイオード P D を除いた回路である。周辺回路領域 200B には、画素信号を処理するロジック回路が形成されており、例えば、垂直駆動回路 20、水平駆動回路 30、水平選択回路 40、システム制御回路 50、膜電圧制御部 60 および電圧生成回路 70 が形成されている。つまり、撮像素子 1 は、画素アレイ部 10、垂直駆動回路 20、水平駆動回路 30、水平選択回路 40、システム制御回路 50、膜電圧制御部 60 および電圧生成回路 70 を備えている。ロジック回路は、センサ画素 11 ごとの画素信号（デジタル値）を外部に出力する。

20

#### 【0022】

システム制御回路 50 は、マスタークロックに基づいて、垂直駆動回路 20、水平駆動回路 30、水平選択回路 40 および膜電圧制御部 60 などの動作の基準となるクロック信号や制御信号などを生成し、垂直駆動回路 20、水平選択回路 40 および膜電圧制御部 60 などに対して与える。

30

#### 【0023】

垂直駆動回路 20 は、例えば、シフトレジスタなどによって構成され、複数の画素駆動線 12 を介して、複数のセンサ画素 11 の行走査の制御を行う。水平選択回路 40 は、例えば、画素アレイ部 10 の画素列（または垂直信号線 13）ごとに、A D C 40a およびスイッチ素子 40b が設けられた回路である。A D C 40a は、画素信号を A D (Analog-to-Digital) 変換する。A D C 40a は、アナログレンジ R を可変させることができ、外部から入力されたレンジ設定値に基づくアナログレンジ R に設定する。なお、本実施の形態では、アナログレンジ R は R a に設定されている。

40

#### 【0024】

A D C 40a の入力端には垂直信号線 13 が接続されており、A D C 40a の出力端にはスイッチ素子 40b が接続されている。水平駆動回路 30 は、例えば、シフトレジスタなどによって構成され、水平選択回路 40 の各スイッチ素子 40b を順番に駆動する。水平駆動回路 30 によって各スイッチ素子 40b を順番に駆動することにより、垂直信号線 13 の各々を通して伝送される各画素信号が順番に水平信号線 40c に出力され、D S P 回路などに入力される。

#### 【0025】

膜電圧制御部 60 は、センサ画素 11 から得られる画素信号に基づいて、各フォトダイオード P D に印加する膜電圧 V f を制御する。膜電圧制御部 60 は、膜電圧 V f を制御す

50

るための制御信号を電圧生成回路 70 に出力する。電圧生成回路 70 は、膜電圧制御部 60 から入力された制御信号に基づいて、アナログの電圧（電圧  $V_{top}$  および  $V_{dr}$ ）を生成し、電源線を介して各フォトダイオード PD に印加する。つまり、膜電圧制御部 60 および電圧生成回路 70 は、センサ画素 11 から得られる画素信号に基づく膜電圧  $V_f$  を各フォトダイオード PD に印加することにより、画素信号から得られる画像データの画質を制御する。

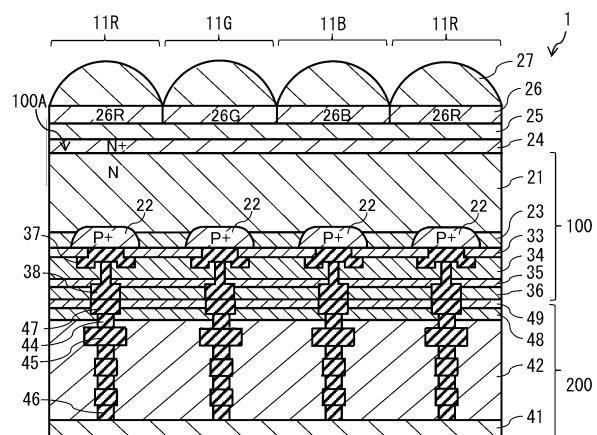

#### 【0026】

図 4 は、撮像素子 1 の断面構成例を表したものである。撮像素子 1において、受光基板 100 は、光電変換部（フォトダイオード PD）である n 型半導体膜 21 を有している。

n 型半導体膜 21 は画素アレイ部 10 の全面に形成されており、例えば、フォトダイオード PD に用いられる材料として上述した材料によって構成されている。なお、以下では、n 型半導体膜 21 が InGaAs によって構成されているものとして、他の構成についての説明を行う。

10

#### 【0027】

受光基板 100 は、さらに、n 型半導体膜 21 の、駆動基板 200 側の面に接する p 型半導体層 22 をセンサ画素 11 ごとに有している。各 p 型半導体層 22 は、高濃度の p 型半導体によって形成されており、例えば、p 型 InGaAs によって形成されている。p 型半導体層 22 は、フォトダイオード PD の電極（第 2 電極）としての機能を有している。p 型半導体層 22 には、オン状態の排出トランジスタ OFG を介して所定の電圧  $V_{dr}$  が印加されたり、オン状態の転送トランジスタ TRG およびリセットトランジスタ RST を介して電源線 VDD の電圧  $V_{dd}$  が印加されたりする。受光基板 100 は、さらに、各 p 型半導体層 22 を互いに分離する n 型半導体層 23 を有している。n 型半導体層 23 は、各 p 型半導体層 22 と同一の層内に形成されており、例えば、n 型 InP によって形成されている。

20

#### 【0028】

受光基板 100 は、さらに、n 型半導体膜 21 の、受光面 100A 側の面に接する n 型半導体層 24 を有している。n 型半導体層 24 は、n 型半導体膜 21 よりも高濃度の n 型半導体によって形成されており、例えば、n 型 InGaAs、n 型 InP または n 型 InAlAs によって形成されている。n 型半導体層 24 は、n 型半導体膜 21 で生成された電荷の逆流を防止するバリア層として機能する。受光基板 100 は、さらに、n 型半導体層 24 の、受光面 100A 側の面に接する反射防止膜 25 を有している。反射防止膜 25 は、例えば、窒化シリコン（SiN）、酸化ハフニウム（HfO<sub>2</sub>）、酸化アルミニウム（Al<sub>2</sub>O<sub>3</sub>）、酸化ジルコニア（ZrO<sub>2</sub>）、酸化タンタル（Ta<sub>2</sub>Ta<sub>5</sub>）、酸化チタン（TiO<sub>2</sub>）などによって形成されている。n 型半導体層 24 は、n 型半導体膜 21 を上下に挟む電極のうちの上側の電極（第 1 電極）としても機能する。上部電極には、所定の電圧  $V_{top}$  が印加される。

30

#### 【0029】

受光基板 100 は、さらに、反射防止膜 25 の上に、カラーフィルタ 26 およびオーナップレンズ 27 を有している。カラーフィルタ 26 は、赤色光を選択的に透過させる複数のフィルタ 26R と、緑色光を選択的に透過させる複数のフィルタ 26G と、青色光を選択的に透過させる複数のフィルタ 26B とによって構成されている。複数のフィルタ 26R、26G、26B は、センサ画素 11 ごとに 1 つずつ設けられており、例えば、受光面 100A と平行な面内にベイヤー配列で配置されている。なお、図 4 には、フィルタ 26R が設けられたセンサ画素 11 が 11R と表記されており、フィルタ 26G が設けられたセンサ画素 11 が 11G と表記されており、フィルタ 26B が設けられたセンサ画素 11 が 11B と表記されている。なお、カラーフィルタ 26 は、必要に応じて省略され得る。

40

#### 【0030】

受光基板 100 は、さらに、p 型半導体層 22 および n 型半導体層 23 の下側に、パッシベーション層 28 および絶縁層 29 を有している。受光基板 100 は、さらに、パッシベーション層 28 を貫通するとともに p 型半導体層 22 に接する接続電極 31 と、絶縁層

50

29を貫通するとともに接続電極31に接するバンプ電極32とを有している。一組の接続電極31およびバンプ電極32は、センサ画素11ごとに1つずつ設けられている。バンプ電極32は、駆動基板200の接続層43(後述)に接合されており、接続層43と電気的に接続されている。バンプ電極32は、例えば、受光基板100と駆動基板200とを互いに貼り合わせた際に、駆動基板200の接続層43に接合される。

#### 【0031】

駆動基板200は、支持基板41と層間絶縁層42とを含む。支持基板41は、例えばシリコン(Si)基板により構成されている。層間絶縁層42は、支持基板41と絶縁層29(受光基板100)との間に設けられている。層間絶縁層42には、例えば、受光基板100に近い位置から順に、複数の接続層43、複数の読み出し電極44、複数の画素信号生成回路45および複数の配線46が設けられている。複数組の接続層43、読み出し電極44、画素信号生成回路45および配線46がセンサ画素11ごとに一組ずつ設けられている。層間絶縁層42内の複数の層間絶縁層42が、例えば、各フォトダイオードPDから電荷の読み出しを行うためのROIC(Read Out IC)内に設けられている。駆動基板200は、層間絶縁層42のうち、周辺回路領域200Bに対応する箇所には、上述のロジック回路が設けられている。

10

#### 【0032】

図5(A)は、フォトダイオードPDに印加される膜電圧Vfと、フォトダイオードPDに保持可能な電荷Qsとの関係の一例を表したものである。図5(B)は、ADC40aのアナログレンジ(ダイナミックレンジ)と画素信号の振幅Vdとの関係の一例を表したものである。図5(B)には、ADC40aのアナログレンジがRaに設定されている場合が例示されている。

20

#### 【0033】

図5(A)から、フォトダイオードPD(n型半導体膜21)に対して印加する電圧(膜電圧Vf = Vtop - Vdr)を大きくするにつれて、フォトダイオードPD(n型半導体膜21)に保持可能な電荷Qsの量も大きくなることがわかる。フォトダイオードPD(n型半導体膜21)に保持される電荷Qsの量が増えるにつれて、画素信号の振幅Vdも大きくなる。ただし、これは、図5(B)に示したように、画素信号の振幅Vdの平均値Vdag(後述)がADC40aのアナログレンジRaに対応する電圧Vdaを超えないことが肝要である。画素信号の振幅Vdの平均値VdagがADC40aのアナログレンジRaに対応する電圧Vdaを超えた場合、ADC40aが飽和し、ADC40aの出力が一定値となる。

30

#### 【0034】

図6は、フォトダイオードPDに印加される膜電圧Vfと、フォトダイオードPDに生じるノイズ(暗電流)との関係の一例を表したものである。図6から、フォトダイオードPD(n型半導体膜21)に対して印加する電圧(膜電圧Vf = Vtop - Vdr)を大きくするにつれて、フォトダイオードPDに生じるノイズ(暗電流)のレベルが指数関数的に増加することがわかる。従って、高輝度のときは、光ショットノイズが支配的になるので、膜電圧Vfを高めに設定し、低輝度のときは、ノイズ(暗電流)が支配的になるので、膜電圧Vfを低めに設定することで、画質劣化が抑制され得る。

40

#### 【0035】

##### [画質調整]

次に、図7を参照して、撮像素子1の画質調整手順について説明する。図7は、撮像素子1の画質調整手順の一例を表したものである。システム制御回路50は、撮像指令を受けると、膜電圧設定指令を膜電圧制御部60に出力する。膜電圧制御部60は、膜電圧設定指令を受けると、まず、膜電圧VfをVfaに設定する(ステップS101)。具体的には、膜電圧制御部60は、Vtop(第1電圧)とVdr(第2電圧)との電位差(Vtop - Vdr)がVfaとなるように、VtopおよびVdrを設定する。例えば、膜電圧制御部60は、Vtopを+2Vに設定し、Vdrを+1Vに設定する。膜電圧制御部60は、VtopおよびVdrの設定値を電圧生成回路70に出力する。電圧生成回路

50

70は、膜電圧制御部60から入力された設定値に基づいて、フォトダイオードPDのアノードに接続された電源線に対して、 $V_{top} = +2V$ の電圧を印加し、排出トランジスタOFGのドレインに接続された電源線に対して、 $V_{dr} = +1V$ の電圧を印加する。

#### 【0036】

次に、膜電圧制御部60は、画素アレイ部10のうち対象領域の複数のセンサ画素11から得られた複数の画素信号の平均値 $V_{avg}$ が所定の閾値 $V_{th1}$ (第1閾値)を超えているか否かを判定する(ステップS102)。閾値 $V_{th1}$ は、膜電圧 $V_f$ が $V_fa$ に設定されているときに光ショットノイズが支配的か否かを判断するための閾値である。その結果、平均値 $V_{avg}$ が所定の閾値 $V_{th1}$ を超えている場合には、膜電圧制御部60は、膜電圧 $V_f$ を、 $V_{fb}$ ( $V_{fb} > V_fa$ )に設定する(ステップS103)。つまり、膜電圧制御部60は、膜電圧 $V_f$ を、 $V_fa$ よりも相対的に大きくする。具体的には、膜電圧制御部60は、 $V_{top} - V_{dr}$ が $V_{fb}$ となるように、平均値 $V_{avg}$ に基づいて、 $V_{top}$ および $V_{dr}$ を設定する。例えば、膜電圧制御部60は、 $V_{top}$ を $+3V$ に設定し、 $V_{dr}$ を $+1V$ に設定する。膜電圧制御部60は、 $V_{top}$ および $V_{dr}$ の設定値を電圧生成回路70に出力する。電圧生成回路70は、膜電圧制御部60から入力された設定値に基づいて、フォトダイオードPDのアノードに接続された電源線に対して、 $V_{top} = +3V$ の電圧を印加し、排出トランジスタOFGのドレインに接続された電源線に対して、 $V_{dr} = +1V$ の電圧を印加する。

10

#### 【0037】

平均値 $V_{avg}$ が所定の閾値 $V_{th1}$ 以下の場合と、膜電圧 $V_f$ を $V_{fb}$ ( $V_{fb} > V_fa$ )に設定した場合には、膜電圧制御部60は、平均値 $V_{avg}$ が所定の閾値 $V_{th2}$ (第2閾値)( $V_{th2} < V_{th1}$ )を下回っているか否かを判定する(ステップS104)。閾値 $V_{th2}$ は、画素信号がノイズに埋もれているか否かを判断するための閾値である。その結果、平均値 $V_{avg}$ が所定の閾値 $V_{th2}$ を下回っている場合には、膜電圧制御部60は、膜電圧 $V_f$ を $V_{fc}$ ( $V_{fc} < V_fa$ )に設定する(ステップS105)。つまり、膜電圧制御部60は、膜電圧 $V_f$ を、 $V_fa$ よりも相対的に小さくする。具体的には、膜電圧制御部60は、 $V_{top} - V_{dr}$ が $V_{fc}$ となるように、平均値 $V_{avg}$ に基づいて、 $V_{top}$ および $V_{dr}$ を設定する。一方、平均値 $V_{avg}$ が所定の閾値 $V_{th2}$ 以上となっている場合には、膜電圧制御部60は、電圧の設定値をそのままにしておく。システム制御回路50は、撮像終了指令を受けた場合には、撮像を終了するとともに、撮像素子1の画質調整も終了する(ステップS106)。システム制御回路50は、撮像終了指令を受けていない場合には、膜電圧制御部60に対して、再び、ステップS102からの実行を指示する。このようにして、撮像素子1の画質調整が行われる。

20

#### 【0038】

##### [効果]

本実施形態では、撮像素子1の出力(画素信号の振幅 $V_d$ の平均値 $V_{avg}$ )に基づく膜電圧 $V_f$ を各フォトダイオードPD( $n$ 型半導体膜21)に印加することにより、画素信号から得られる画像データの画質が制御される。具体的には、撮像素子1の出力(画素信号の振幅 $V_d$ の平均値 $V_{avg}$ )が閾値 $V_{th1}$ を超えたときに膜電圧 $V_f$ を相対的に大きくし、撮像素子1の出力(画素信号の振幅 $V_d$ の平均値 $V_{avg}$ )が閾値 $V_{th2}$ を下回ったときに膜電圧 $V_f$ を相対的に小さくする。このように、本実施形態では、高輝度のときは、膜電圧 $V_f$ を相対的に大きくして、光ショットノイズの影響を低減し、低輝度のときは、膜電圧 $V_f$ を相対的に小さくして、S/N比を高くしている。これにより、画質劣化を抑制することができる。

30

#### 【0039】

また、本実施の形態では、電圧 $V_{top}$ と電圧 $V_{dr}$ との電位差( $V_{top} - V_{dr}$ )が膜電圧 $V_f$ となるように、画素信号に基づいて電圧 $V_{top}$ および電圧 $V_{dr}$ が生成される。このようにして生成された膜電圧 $V_f$ が、各フォトダイオードPD( $n$ 型半導体膜21)に印加されることにより、画質劣化を抑制することができる。

40

#### 【0040】

50

また、本実施の形態では、各画素回路 14 には、フォトダイオード P D ( n 型半導体膜 21 )と、転送トランジスタ T R G と、排出トランジスタ O F G とが設けられている。そして、排出トランジスタがオンしているときに、p 型半導体層 22 に V d r が印加される。これにより、画素信号に基づいて、各フォトダイオード P D ( n 型半導体膜 21 )に膜電圧 V f が印加される。従って、画質劣化を抑制することができる。

#### 【 0 0 4 1 】

< 2 . 第 1 の実施の形態の変形例 >

##### [[変形例 A ]]

上記実施の形態では、膜電圧制御部 60 および電圧生成回路 70 は、撮像素子 1 内に設けられていたが、例えば、図 8 に示したように、撮像素子 1 とは別体の画質制御回路 2 内に設けられていてもよい。この場合、膜電圧制御部 60 は、例えば、図 8 に示したように、撮像素子 1 の出力に基づいて、膜電圧 V f を設定してもよい。このようにした場合であっても、上記実施の形態と同様の効果を奏する。

10

#### 【 0 0 4 2 】

##### [[変形例 B ]]

上記実施の形態において、撮像素子 1 は、例えば、図 9 に示したように、アナログレンジ制御部 80 を更に備えていてもよい。アナログレンジ制御部 80 は、膜電圧制御部 60 から入力される判定結果（つまり、撮像素子 1 の出力（画素信号の振幅 V d の平均値 V d a v g ））に基づいて、A D C 4 0 a のアナログレンジ R を制御する。具体的には、アナログレンジ制御部 80 は、膜電圧制御部 60 から入力される判定結果（つまり、撮像素子 1 の出力（画素信号の振幅 V d の平均値 V d a v g ））に基づくレンジ設定値を A D C 4 0 a に出力することにより、画素信号から得られる画像データの画質を制御する。

20

#### 【 0 0 4 3 】

図 10 は、A D C 4 0 a のアナログレンジ R ( ダイナミックレンジ ) と画素信号の振幅 V d との関係の一例を表したものである。図 10 には、A D C 4 0 a のアナログレンジ R が R a または R b に設定されている場合が例示されている。

#### 【 0 0 4 4 】

図 10 に示したように、画素信号の振幅 V d の平均値 V d a v g が A D C 4 0 a のアナログレンジ R a に対応する電圧 V d a を超えている場合、A D C 4 0 a が飽和する。しかし、A D C 4 0 a のアナログレンジ R を R a から R b に拡大することにより、画素信号の振幅 V d の平均値 V d a v g が、A D C 4 0 a のアナログレンジ R b に対応する電圧 V d b を下回り、A D C 4 0 a の飽和が解消する。従って、高輝度のときは、白飛びを防ぐために、A D C 4 0 a のダイナミックレンジ R を高めに設定し、低輝度のときは、ノイズ（暗電流）が支配的になるので、A D C 4 0 a のダイナミックレンジ R を低めに設定することで、画質劣化が抑制され得る。

30

#### 【 0 0 4 5 】

##### [画質調整]

次に、図 11 を参照して、本変形例に係る撮像素子 1 の画質調整手順について説明する。図 11 は、本変形例に係る撮像素子 1 の画質調整手順の一例を表したものである。なお、本変形例では、撮像素子 1 は、図 7 に記載の画質調整手順を実行するとともに、図 11 に記載の画質調整手順を実行する。

40

#### 【 0 0 4 6 】

アナログレンジ制御部 80 は、まず、A D C 4 0 a のアナログレンジ R を R a に設定する（ステップ S 2 0 1）。具体的には、アナログレンジ制御部 80 は、アナログレンジ R を R a にする制御信号を A D C 4 0 a に出力する。A D C 4 0 a は、アナログレンジ制御部 80 から、アナログレンジ R を R a にする制御信号が入力されると、アナログレンジ R を R a に設定する。

#### 【 0 0 4 7 】

次に、アナログレンジ制御部 80 は、膜電圧制御部 60 から入力された判定結果が “ V d a v g > V t h 3 ” である場合、アナログレンジ R を R b ( R b > R a ) に設定する（ステ

50

ップ S 2 0 2 , 2 0 3 )。つまり、アナログレンジ制御部 8 0 は、アナログレンジ R を、R a よりも相対的に大きくする。閾値 V t h 3 ( 第 1 閾値 ) は、膜電圧 V f が V f a に設定されているときに画像が白とびをするか否かを判断するための閾値である。このとき、アナログレンジ制御部 8 0 は、アナログレンジ R を R b にする制御信号を A D C 4 0 a に出力する。A D C 4 0 a は、アナログレンジ制御部 8 0 から、アナログレンジ R を R b にする制御信号が入力されると、アナログレンジ R を R b に設定する。

#### 【 0 0 4 8 】

アナログレンジ制御部 8 0 は、膜電圧制御部 6 0 から入力された判定結果が “ V d a v g V t h 3 ” である場合、または、アナログレンジ R を R b に設定した場合には、平均値 V d a v g と閾値 V t h 2 との大小関係についての判定結果が膜電圧制御部 6 0 から入力されるのを待つ。このとき、アナログレンジ制御部 8 0 は、膜電圧制御部 6 0 から入力された判定結果が “ V d a v g < V t h 2 ” ( V t h 2 < V t h 3 ) である場合、アナログレンジ R を R a に設定する ( ステップ S 2 0 4 , 2 0 1 ) 。つまり、アナログレンジ制御部 8 0 は、アナログレンジ R を、R b よりも相対的に小さくする。具体的には、アナログレンジ制御部 8 0 は、アナログレンジ R を R a にする制御信号を A D C 4 0 a に出力する。A D C 4 0 a は、アナログレンジ制御部 8 0 から、アナログレンジ R を R a にする制御信号が入力されると、アナログレンジ R を R a に設定する。

#### 【 0 0 4 9 】

アナログレンジ制御部 8 0 は、膜電圧制御部 6 0 から入力された判定結果が “ V d a v g V t h 2 ” である場合、撮像終了指令が入力されていないときには、ステップ S 2 0 2 を実行する ( ステップ S 2 0 4 , 2 0 5 ) 。アナログレンジ制御部 8 0 は、撮像終了指令が入力されたときには、アナログレンジ R の設定を終了する ( ステップ S 2 0 5 ) 。このようにして、撮像素子 1 の画質調整が行われる。

#### 【 0 0 5 0 】

##### [効果]

本変形例では、撮像素子 1 の出力 ( 画素信号の振幅 V d の平均値 V d a v g ) に基づく膜電圧 V f を各フォトダイオード P D ( n 型半導体膜 2 1 ) に印加することにより、画素信号から得られる画像データの画質が制御される。具体的には、撮像素子 1 の出力 ( 画素信号の振幅 V d の平均値 V d a v g ) が閾値 V t h 1 を超えたときに膜電圧 V f を相対的に大きくし、撮像素子 1 の出力 ( 画素信号の振幅 V d の平均値 V d a v g ) が閾値 V t h 2 を下回ったときに膜電圧 V f を相対的に小さくする。このように、本変形例では、高輝度のときは、膜電圧 V f を相対的に大きくして、光ショットノイズの影響を低減し、低輝度のときは、膜電圧 V f を相対的に小さくして、S / N 比を高くしている。これにより、画質劣化を抑制することができる。

#### 【 0 0 5 1 】

本変形例では、さらに、画素信号に基づくレンジ設定値を A D C 4 0 a に出力することにより、画素信号から得られる画像データの画質が制御される。具体的には、撮像素子 1 の出力 ( 画素信号の振幅 V d の平均値 V d a v g ) が閾値 V t h 3 を超えたときにレンジ設定値を相対的に大きくし、撮像素子 1 の出力 ( 画素信号の振幅 V d の平均値 V d a v g ) が閾値 V t h 2 を下回ったときにレンジ設定値を相対的に小さくする。このように、本変形例では、高輝度のときは、レンジ設定値を相対的に大きくして、画像が白とびするのを抑制し、低輝度のときは、レンジ設定値を相対的に小さくして、S / N 比を高くしている。これにより、画質劣化を抑制することができる。

#### 【 0 0 5 2 】

##### [[変形例 C ]]

上記変形例 B では、膜電圧制御部 6 0 、電圧生成回路 7 0 およびアナログレンジ制御部 8 0 は、撮像素子 1 内に設けられていたが、例えば、図 1 2 に示したように、撮像素子 1 とは別体の画質制御回路 2 内に設けられていてもよい。この場合、膜電圧制御部 6 0 は、例えば、図 1 2 に示したように、撮像素子 1 の出力に基づいて、膜電圧 V f を設定してもよい。このようにした場合であっても、上記実施の形態と同様の効果を奏する。

10

20

30

40

50

## 【0053】

## [[変形例D]]

上記変形例Bでは、膜電圧制御部60、電圧生成回路70およびアナログレンジ制御部80は、撮像素子1内に設けられていた。しかし、例えば、図13に示したように、膜電圧制御部60および電圧生成回路70が、撮像素子1とは別体の画質制御回路2内に設けられ、アナログレンジ制御部80が撮像素子1内に設けられていてもよい。

## 【0054】

この場合、膜電圧制御部60は、例えば、図13に示したように、撮像素子1の出力に基づいて、膜電圧 $V_f$ を設定してもよい。また、アナログレンジ制御部80は、例えば、図13に示したように、電圧生成回路70の出力電圧( $V_{top}$ 、 $V_{dr}$ )の値に基づいて、ADC40aのアナログレンジRを設定してもよい。10

## 【0055】

本変形例では、撮像素子1の出力に基づいて各フォトダイオードPD(n型半導体膜21)に印加される膜電圧 $V_f$ が設定され、各フォトダイオードPD(n型半導体膜21)に印加される電圧( $V_{top}$ 、 $V_{dr}$ )の値に基づいて、ADC40aのアナログレンジRが設定される。これにより、画質劣化を抑制することができる。

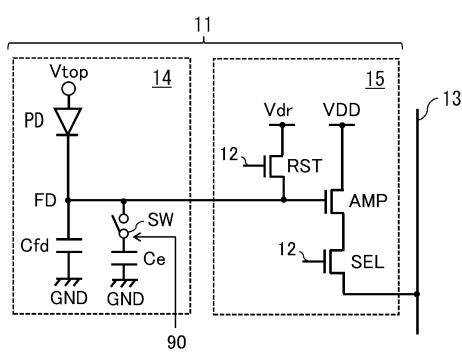

## 【0056】

## [[変形例E]]

上記実施の形態において、撮像素子1は、例えば、図14に示したように、効率変換制御部90を更に備えてもよい。効率変換制御部90は、膜電圧制御部60から入力される判定結果(つまり、撮像素子1の出力(画素信号の振幅 $V_d$ の平均値 $V_{avg}$ ))に基づいて、画素回路14の変換効率 $\eta$ を制御する。具体的には、効率変換制御部90は、膜電圧制御部60から入力される判定結果(つまり、撮像素子1の出力(画素信号の振幅 $V_d$ の平均値 $V_{avg}$ ))に基づく制御信号を後述のスイッチ素子SWに出力することにより、画素信号から得られる画像データの画質を制御する。20

## 【0057】

図15は、本変形例に係るセンサ画素11の回路構成の一例を表したものである。本変形例に係るセンサ画素11において、画素回路14は、フローティングディフュージョンFDに接続されたスイッチ素子SWと、スイッチ素子SWを介してフローティングディフュージョンFDの容量(FD容量 $C_{fd}$ )と並列に接続された補助容量 $C_e$ とを有している。効率変換制御部90は、スイッチ素子SWのオンオフを制御することにより、画素回路14の変換効率 $\eta$ を制御する。30

## 【0058】

図16は、ADC40aのアナログレンジRと画素信号の振幅 $V_d$ との関係の一例を表したものである。図16には、ADC40aのアナログレンジRがRbに設定されている場合が例示されている。

## 【0059】

効率変換制御部90の制御によってスイッチ素子SWがオンしている場合、互いに並列接続されたFD容量 $C_{fd}$ および補助容量 $C_e$ に蓄積された電荷によって生じる電圧が読み出し回路15に入力される。このときの画素回路14の変換効率 $\eta$ を1とする。効率変換制御部90の制御によってスイッチ素子SWがオフした場合、補助容量 $C_e$ は、フローティングディフュージョンFDから分離されるので、FD容量 $C_{fd}$ に蓄積された電荷によって生じる電圧が読み出し回路15に入力される。このときの画素回路14の変換効率 $\eta_2$ は、 $1 / (C_{fd} + C_e) / C_{fd}$ となる。ここで、 $\eta_2$ は、 $(C_{fd} + C_e) / C_{fd}$ である。つまり、スイッチ素子SWをオフすることにより、変換効率 $\eta$ が $1 / (C_{fd} + C_e) / C_{fd}$ だけ低くなる。例えば、補助容量 $C_e$ がFD容量 $C_{fd}$ の2倍の容量となっている場合、変換効率 $\eta_2$ は、変換効率 $\eta$ の $1 / 3$ 倍となる。変換効率 $\eta$ が低くなると、例えば、図16に示したように、変換効率 $\eta$ が低くなった分だけ、画素信号の振幅 $V_d$ が小さくなる。そこで、例えば、スイッチ素子SWがオンしているときの平均値 $V_{avg}$ がADC40aのアナログレンジRの上限(Rb)に対応する電圧値 $V_{db}$ よりも大きく、ADC40aが飽和している場40

合に、スイッチ素子SWをオフすることにより、スイッチ素子SWオフ時の平均値V<sub>d a v g 2</sub>がV<sub>d a v g 1 /</sub>となり、電圧値V<sub>d b</sub>よりも小さくすることができる。従って、高輝度のときは、白飛びを防ぐために、変換効率<sub>1</sub>を低めに設定し、低輝度のときは、ノイズ(暗電流)が支配的になるので、変換効率<sub>2</sub>を高めに設定することで、画質劣化が抑制され得る。

#### 【0060】

##### [画質調整]

次に、図17を参照して、撮像素子1の画質調整手順について説明する。図17は、撮像素子1の画質調整手順の一例を表したものである。なお、本変形例では、撮像素子1は、図7に記載の画質調整手順を実行するとともに、図17に記載の画質調整手順を実行する。

10

#### 【0061】

効率変換制御部90は、まず、画素回路14の変換効率<sub>1</sub>を1に設定する(ステップS301)。具体的には、効率変換制御部90は、画素回路14内のスイッチ素子SWに対して、スイッチ素子SWをオンさせる制御信号を出力する。スイッチ素子SWは、効率変換制御部90から、スイッチ素子SWをオンさせる制御信号が入力されると、オンする。これにより、FD容量C<sub>f d</sub>と補助容量C<sub>e</sub>とが互いに並列に接続される。

#### 【0062】

次に、効率変換制御部90は、膜電圧制御部60から入力された判定結果が“V<sub>d a v g</sub> > V<sub>t h 3</sub>”である場合、変換効率<sub>2</sub>(2 < 1)に設定する(ステップS302, 303)。このとき、効率変換制御部90は、スイッチ素子SWをオフさせる制御信号をスイッチ素子SWに出力する。スイッチ素子SWは、効率変換制御部90から、スイッチ素子SWをオフさせる制御信号が入力されると、オフする。つまり、効率変換制御部90は、平均値V<sub>d a v g</sub>がV<sub>t h 3</sub>を超えたときにスイッチ素子SWをオフする。これにより、補助容量C<sub>e</sub>がフローティングディフュージョンFDから分離される。

20

#### 【0063】

効率変換制御部90は、膜電圧制御部60から入力された判定結果が“V<sub>d a v g</sub> < V<sub>t h 3</sub>”である場合、または、スイッチ素子SWをオフに設定した場合には、平均値V<sub>d a v g</sub>と閾値V<sub>t h 2</sub>(V<sub>t h 2</sub> < V<sub>t h 3</sub>)との大小関係についての判定結果が膜電圧制御部60から入力されるのを待つ。このとき、効率変換制御部90は、膜電圧制御部60から入力された判定結果が“V<sub>d a v g</sub> < V<sub>t h 2</sub>”である場合、変換効率<sub>1</sub>に設定する(ステップS304, 301)。具体的には、効率変換制御部90は、スイッチ素子SWに対して、スイッチ素子SWをオンさせる制御信号を出力する。スイッチ素子SWは、効率変換制御部90から、スイッチ素子SWをオンさせる制御信号が入力されると、オンする。つまり、効率変換制御部90は、平均値V<sub>d a v g</sub>がV<sub>t h 3</sub>よりも小さなV<sub>t h 2</sub>を下回ったときにスイッチ素子SWをオンする。これにより、FD容量C<sub>f d</sub>と補助容量C<sub>e</sub>とが互いに並列に接続される。

30

#### 【0064】

効率変換制御部90は、膜電圧制御部60から入力された判定結果が“V<sub>d a v g</sub> = V<sub>t h 2</sub>”である場合、撮像終了指令が入力されていないときには、ステップS302を実行する(ステップS304, 302)。効率変換制御部90は、撮像終了指令が入力されたときには、変換効率<sub>1</sub>の設定を終了する(ステップS305)。このようにして、撮像素子1の画質調整が行われる。

40

#### 【0065】

##### [効果]

本変形例では、撮像素子1の出力(画素信号の振幅V<sub>d</sub>の平均値V<sub>d a v g</sub>)に基づく膜電圧V<sub>f</sub>を各フォトダイオードPD(n型半導体膜21)に印加することにより、画素信号から得られる画像データの画質が制御される。具体的には、撮像素子1の出力(画素信号の振幅V<sub>d</sub>の平均値V<sub>d a v g</sub>)が閾値V<sub>t h 1</sub>を超えたときに膜電圧V<sub>f</sub>を相対的に大きくし、撮像素子1の出力(画素信号の振幅V<sub>d</sub>の平均値V<sub>d a v g</sub>)が閾値V<sub>t h</sub>

50

2を下回ったときに膜電圧 $V_f$ を相対的に小さくする。このように、本変形例では、高輝度のときは、膜電圧 $V_f$ を相対的に大きくして、光ショットノイズの影響を低減し、低輝度のときは、膜電圧 $V_f$ を相対的に小さくして、S/N比を高くしている。これにより、画質劣化を抑制することができる。

#### 【0066】

本変形例では、さらに、画素信号に基づく制御信号をスイッチ素子SWに出力することにより、画素信号から得られる画像データの画質が制御される。具体的には、撮像素子1の出力(画素信号の振幅 $V_d$ の平均値 $V_{davg}$ )が閾値 $V_{th3}$ を超えたときにスイッチ素子SWをオフし、撮像素子1の出力(画素信号の振幅 $V_d$ の平均値 $V_{davg}$ )が閾値 $V_{th2}$ を下回ったときにスイッチ素子SWをオンする。このように、本変形例では、高輝度のときは、スイッチ素子SWをオフして、画像が白飛びするのを抑制し、低輝度のときは、スイッチ素子SWをオンして、S/N比を高くしている。これにより、画質劣化を抑制することができる。

10

#### 【0067】

##### [[変形例F]]

上記変形例Eでは、膜電圧制御部60、電圧生成回路70および効率変換制御部90は、撮像素子1内に設けられていた。しかし、例えば、図18に示したように、膜電圧制御部60、電圧生成回路70および効率変換制御部90が、撮像素子1とは別体の画質制御回路2内に設けられていてもよい。この場合、膜電圧制御部60は、例えば、図18に示したように、撮像素子1の出力に基づいて、膜電圧 $V_f$ を設定してもよい。このようにした場合であっても、上記実施の形態と同様の効果を奏する。

20

#### 【0068】

##### [[変形例G]]

上記変形例Eでは、膜電圧制御部60、電圧生成回路70および効率変換制御部90は、撮像素子1内に設けられていた。しかし、例えば、図19に示したように、膜電圧制御部60および電圧生成回路70が、撮像素子1とは別体の画質制御回路2内に設けられ、効率変換制御部90が撮像素子1内に設けられていてもよい。

30

#### 【0069】

この場合、膜電圧制御部60は、例えば、図19に示したように、撮像素子1の出力に基づいて、膜電圧 $V_f$ を設定してもよい。また、効率変換制御部90は、例えば、図19に示したように、電圧生成回路70の出力電圧( $V_{top}$ 、 $V_{dr}$ )の値に基づいて、画素回路14の変換効率を設定してもよい。

#### 【0070】

本変形例では、撮像素子1の出力に基づいてフォトダイオードPD(n型半導体膜21)に印加される膜電圧 $V_f$ が設定され、フォトダイオードPD(n型半導体膜21)に印加される電圧( $V_{top}$ 、 $V_{dr}$ )の値に基づいて、画素回路14の変換効率が設定される。これにより、画質劣化を抑制することができる。

#### 【0071】

##### [[変形例H]]

上記実施の形態およびその変形例において、画素回路14は、例えば、図20、図21に示したように、排出トランジスタOFGが省略されてもよい。このとき、膜電圧制御部60は、n型半導体層24に印加する電圧 $V_{top}$ と、転送トランジスタTRGがオンしているときにリセットトランジスタRSTによって印加されたp型半導体層22の電極 $V_{dr}$ との電位差( $V_{top} - V_{dr}$ )が膜電圧 $V_f$ となるように、画素信号に基づいて電圧 $V_{top}$ を生成してもよい。

40

#### 【0072】

また、上記実施の形態およびその変形例において、画素回路14は、例えば、図22、図23に示したように、排出トランジスタOFGおよび転送トランジスタTRGが省略されてもよい。このとき、膜電圧制御部60は、n型半導体層24に印加する電圧 $V_{top}$ と、リセットトランジスタRSTによって印加されたp型半導体層22の電極 $V_{dr}$ との

50

電位差 ( $V_{top} - V_{dr}$ ) が膜電圧  $V_f$  となるように、画素信号に基づいて電圧  $V_{top}$  を生成してもよい。

#### 【0073】

本変形例では、これらのようにした場合であっても、上記実施の形態およびその変形例に係る撮像素子1と同様の効果を奏する。

#### 【0074】

##### [[変形例I]]

上記実施の形態およびその変形例A～Hでは、受光基板100と駆動基板200とが、パンプ接合されていた。しかし、上記実施の形態およびその変形例A～Hにおいて、受光基板100と駆動基板200とが、Cu-Cu接合されていてもよい。図24は、本変形例に係る撮像素子1の断面構成の一変形例を表したものである。10

#### 【0075】

受光基板100は、パッシベーション層28、絶縁層29、複数の接続電極31および複数のパンプ電極32の代わりに、絶縁膜33、埋め込み層34、層間絶縁膜35, 36、複数の電極37および複数のコンタクト電極38を有している。

#### 【0076】

絶縁膜33は、n型半導体層23と、各p型半導体層22の一部とを覆っており、各p型半導体層22と対向する箇所に開口を有している。絶縁膜33は、例えば、酸化シリコン( $SiO_x$ )または酸化アルミニウム( $Al_2O_3$ )等の酸化物を含んで構成されている。複数の膜からなる積層構造により絶縁膜33を構成するようにしてもよい。絶縁膜33は、例えば、酸窒化シリコン( $SiON$ )、炭素含有酸化シリコン( $SiOC$ )、窒化シリコン( $SiN$ )およびシリコンカーバイド( $SiC$ )などのシリコン( $Si$ )系絶縁材料により構成するようにしてもよい。絶縁膜33の厚みは、例えば数十nm～数百nmである。20

#### 【0077】

複数の電極37は、絶縁膜33の各開口に1つずつ設けられており、p型半導体層22ごとに1つずつ設けられている。各電極37は、対応するp型半導体層22に接している。各電極37は、例えば、チタン( $Ti$ )、タングステン( $W$ )、窒化チタン( $TiN$ )、白金( $Pt$ )、金( $Au$ )、ゲルマニウム( $Ge$ )、パラジウム( $Pd$ )、亜鉛( $Zn$ )、ニッケル( $Ni$ )およびアルミニウム( $Al$ )のうちのいずれかの単体、またはそれらのうちの少なくとも1種を含む合金により構成されている。各電極37は、このような構成材料の単膜であってもよく、あるいは、2種以上を組み合わせた積層膜であってもよい。例えば、各電極37は、チタンおよびタングステンの積層膜により構成されている。各電極37の厚みは、例えば数十nm～数百nmである。30

#### 【0078】

埋め込み層34は、各電極37を埋め込んで形成されている。埋め込み層34において、駆動基板200側の面は平坦になっている。埋め込み層34は、例えば、酸化シリコン( $SiO_x$ )、窒化シリコン( $SiN$ )、酸窒化シリコン( $SiON$ )、炭素含有酸化シリコン( $SiOC$ )およびシリコンカーバイド( $SiC$ )等の無機絶縁材料により構成されている。40

#### 【0079】

層間絶縁膜35, 36は、埋め込み層34の、駆動基板200側の平坦面にこの順に積層されている。層間絶縁膜35, 36は、例えば、無機絶縁材料により構成されている。この無機絶縁材料としては、例えば、窒化シリコン( $SiN$ )、酸化アルミニウム( $Al_2O_3$ )、酸化ケイ素( $SiO_2$ )および酸化ハフニウム( $HfO_2$ )等が挙げられる。層間絶縁膜35, 36を同一の無機絶縁材料により構成するようにしてもよい。

#### 【0080】

複数のコンタクト電極38は、電極37ごとに1つずつ設けられている。各コンタクト電極38は、対応する電極37に接している。各コンタクト電極38の、駆動基板200側の面は、層間絶縁膜36から露出している。各コンタクト電極38の、駆動基板200

10

20

30

40

50

側の面と、層間絶縁膜36の、駆動基板200側の面とは、同一の面内に配置されている。

#### 【0081】

駆動基板200は、複数の接続層43の代わりに、複数のコンタクト電極47を有している。駆動基板200は、さらに、層間絶縁膜48, 49を有している。複数のコンタクト電極47は、読み出し電極44ごとに1つずつ設けられている。各コンタクト電極47は、対応する読み出し電極44に接している。

#### 【0082】

層間絶縁膜48, 49は、層間絶縁層42の、受光基板100側の面にこの順に積層されている。層間絶縁膜48, 49は、例えば、無機絶縁材料により構成されている。この無機絶縁材料としては、例えば、窒化シリコン(SiN), 酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>), 酸化ケイ素(SiO<sub>2</sub>)および酸化ハフニウム(HfO<sub>2</sub>)等が挙げられる。10

#### 【0083】

各コンタクト電極47の、受光基板100側の面は、層間絶縁膜49から露出している。各コンタクト電極47の、受光基板100側の面と、層間絶縁膜49の、受光基板100側の面とは、同一の面内に配置されている。コンタクト電極38, 47は、例えば、銅(Cu)により構成されている。コンタクト電極38とコンタクト電極47とが互いに接合されている。

#### 【0084】

図25は、本変形例に係る撮像素子1の平面構成の一例を表したものである。図26は、図25の撮像素子1のA-A線での断面構成の一例を表したものである。撮像素子1は、中央部の素子領域R1と、素子領域R1の外側に設けられ、素子領域R1を囲む周辺領域R2とを有している。素子領域R1は、撮像素子1において、n型半導体膜21(フォトダイオードPD)が設けられた箇所に対応している。撮像素子1は、素子領域R1から周辺領域R2にわたって設けられた導電膜51を有している。この導電膜51は、素子領域R1の中央部に対向する領域に開口を有している。素子領域R1のうち、導電膜51から露出された領域(導電膜51の開口に対向する領域)が、受光領域である。素子領域R1のうち、導電膜51で覆われた領域は、OPB(Optical Black)領域である。OPB領域は、受光領域を囲むように設けられている。OPB領域は、黒レベルの画素信号を得るために用いられる。20

#### 【0085】

受光基板100において、絶縁膜33は、n型半導体層23と、各p型半導体層22の一部とを覆うとともに、n型半導体膜21(フォトダイオードPD)の側面を覆っている。受光基板100において、埋め込み層34は、絶縁膜33を介してn型半導体膜21の側面を覆っており、素子領域R1から周辺領域R2にわたって設けられている。周辺領域R2には、受光基板100を貫通し、駆動基板200に達する穴H1, H2が設けられている。30

#### 【0086】

穴H1は、穴H2よりも素子領域R1に近い位置に設けられており、穴H1の側壁および底面は、導電膜51に覆われている。穴H1は、n型半導体膜21と駆動基板200の配線46とを接続するためのものであり、反射防止膜25、埋め込み層34、層間絶縁膜35および層間絶縁膜36を貫通して設けられている。40

#### 【0087】

穴H2は、例えば、穴H1よりも受光基板100の端部に近い位置に設けられている。穴H2は、反射防止膜25、埋め込み層34、層間絶縁膜35および層間絶縁膜36を貫通し、駆動基板200の配線46に達している。穴H2を介して、外部と撮像素子1との電気的な接続が行われる。穴H1, H2は、駆動基板200に達していなくてもよい。例えば、穴H1, H2が、層間絶縁膜36に設けられた配線に達しており、この配線が駆動基板200の配線46に接続されていてもよい。

#### 【0088】

受光基板100において、層間絶縁膜36、層間絶縁膜35および埋め込み層34は、50

駆動基板 200 に近い位置にからこの順に設けられている。層間絶縁膜 36、層間絶縁膜 35 および埋め込み層 34 は、素子領域 R1 から周辺領域 R2 にわたって設けられており、層間絶縁膜 36 および各コンタクト電極 38 が駆動基板 200 との接合面を構成している。受光基板 100 の接合面が素子領域 R1 および周辺領域 R2 に設けられており、素子領域 R1 の接合面と周辺領域 R2 の接合面とは、同一平面を構成している。

#### 【 0 0 8 9 】

受光基板 100 に設けられた複数のコンタクト電極 38 のうち、周辺領域 R2 に設けられた複数のコンタクト電極 38 は、n 型半導体膜 21（フォトダイオード P D）との電気的な接続が無く、受光基板 100 と駆動基板 200 との接合のために設けられたダミー電極 38D である。

10

#### 【 0 0 9 0 】

駆動基板 200 において、層間絶縁膜 49、層間絶縁膜 48 および層間絶縁層 42 は、受光基板 100 に近い位置にからこの順に設けられている。層間絶縁膜 49、層間絶縁膜 48 および層間絶縁層 42 は、素子領域 R1 から周辺領域 R2 にわたって設けられており、層間絶縁膜 49 および各コンタクト電極 47 が受光基板 100 との接合面を構成している。駆動基板 200 の接合面が素子領域 R1 および周辺領域 R2 に設けられており、素子領域 R1 の接合面と周辺領域 R2 の接合面とは、同一平面を構成している。

#### 【 0 0 9 1 】

駆動基板 200 に設けられた複数のコンタクト電極 47 のうち、周辺領域 R2 に設けられた複数のコンタクト電極 47 は、n 型半導体膜 21（フォトダイオード P D）との電気的な接続が無く、受光基板 100 と駆動基板 200 との接合のために設けられたダミー電極 47D である。ダミー電極 47D は、ダミー電極 38D と対向する位置に設けられており、対向位置に設けられたダミー電極 38D に接合されている。これにより、周辺領域 R2 の強度を向上させることが可能となる。

20

#### 【 0 0 9 2 】

導電膜 51 は、OPB 領域から周辺領域 R2 の穴 H1 にわたって設けられている。導電膜 51 は、OPB 領域に設けられた反射防止膜 25 の開口 25H において n 型半導体層 24 に接するとともに、穴 H1 を介して駆動基板 200 の配線 46 に接している。これにより、駆動基板 200 から導電膜 51 を介して n 型半導体層 24 に電圧が供給される。導電膜 51 は、n 型半導体層 24 への電圧供給経路として機能するとともに、遮光膜としての機能を有し、OPB 領域を形成する。導電膜 51 は、例えば、タンゲステン (W)、アルミニウム (Al)、チタン (Ti)、モリブデン (Mo)、タンタル (Ta) または銅 (Cu) を含む金属材料により構成されている。導電膜 51 上にパッシベーション膜 52 が設けられていてもよい。

30

#### 【 0 0 9 3 】

##### < 3 . 第 2 の実施の形態 >

図 27 は、上記実施の形態、上記変形例 B、上記変形例 E および上記変形例 H に係る撮像素子 1（以下、「撮像素子 1a」と称する。）を備えた撮像装置 3 の概略構成の一例を表したものである。

#### 【 0 0 9 4 】

撮像装置 3 は、例えば、デジタルスチルカメラやビデオカメラ等の撮像装置や、スマートフォンやタブレット型端末等の携帯端末装置などの電子機器である。撮像装置 3 は、例えば、撮像素子 1a、光学系 141、シャッタ装置 142、DSP 回路 143、フレームメモリ 144、表示部 145、記憶部 146、操作部 147 および電源部 148 を備えている。撮像装置 3 において、撮像素子 1a、シャッタ装置 142、DSP 回路 143、フレームメモリ 144、表示部 145、記憶部 146、操作部 147 および電源部 148 は、バスライン 149 を介して相互に接続されている。

40

#### 【 0 0 9 5 】

撮像素子 1a は、入射光に応じた画像データ（デジタル値）を出力する。光学系 141 は、1 枚または複数枚のレンズを有して構成され、被写体からの光（入射光）を撮像素子

50

1 a に導き、撮像素子 1 a の受光面に結像させる。シャッタ装置 142 は、光学系 141 および撮像素子 1 a の間に配置され、撮像素子 1 a への光照射期間および遮光期間を制御する。DSP 回路 143 は、撮像素子 1 a から出力される画像データ（デジタル値）を処理する信号処理回路である。フレームメモリ 144 は、DSP 回路 143 により処理された画像データを、フレーム単位で一時的に保持する。表示部 145 は、例えば、液晶パネルや有機 EL (Electro Luminescence) パネル等のパネル型表示装置からなり、撮像素子 1 a で撮像された動画又は静止画を表示する。記憶部 146 は、撮像素子 1 a で撮像された動画又は静止画の画像データを、半導体メモリやハードディスク等の記録媒体に記録する。操作部 147 は、ユーザによる操作に従い、撮像装置 3 が有する各種の機能についての操作指令を発する。電源部 148 は、撮像素子 1 a、シャッタ装置 142、DSP 回路 143、フレームメモリ 144、表示部 145、記憶部 146 および操作部 147 の動作電源となる各種の電源を、これら供給対象に対して適宜供給する。

#### 【0096】

次に、撮像装置 3 における撮像手順の一例について説明する。

#### 【0097】

図 28 は、撮像装置 3 における撮像動作のフローチャートの一例を表す。ユーザは、操作部 147 を操作することにより撮像開始を指示する（ステップ S401）。すると、操作部 147 は、撮像指令を撮像素子 1 a に送信する（ステップ S402）。撮像装置 3 において、撮像素子 1 a は、撮像指令を受けると、各種設定（例えば、上述の画質調整など）を行う（ステップ S403）。その後、撮像素子 1 a は、所定の撮像方式での撮像を実行する（ステップ S404）。なお、撮像装置 3 において、撮像素子 1 a は、必要に応じて、ステップ S403 およびステップ S404 を繰り返し実行する。

#### 【0098】

撮像素子 1 a は、撮像により得られた画像データを DSP 回路 143 に出力する。ここで、画像データとは、フローティングディフュージョン FD に一時的に保持された電荷に基づいて生成された画素信号の全画素分のデータである。DSP 回路 143 は、撮像素子 1 a から入力された画像データに基づいて所定の信号処理（例えばノイズ低減処理など）を行う（ステップ S405）。DSP 回路 143 は、所定の信号処理がなされた画像データをフレームメモリ 144 に保持させ、フレームメモリ 144 は、画像データを記憶部 146 に記憶させる（ステップ S406）。このようにして、撮像装置 3 における撮像が行われる。

#### 【0099】

本実施の形態では、撮像素子 1 a が撮像装置 3 に適用される。これにより、撮像素子 1 a の画質調整を自動的に行うことができる。

#### 【0100】

##### <4. 第 2 の実施の形態の変形例>

上記第 2 の実施の形態において、撮像装置 3 は、撮像素子 1 a の代わりに、上記変形例 A、上記変形例 C、上記変形例 D、上記変形例 F、上記変形例 G および上記変形例 H に係る撮像素子 1（以下、「撮像素子 1 b」と称する。）を備えていてもよい。この場合、撮像装置 3 は、例えば、図 29 に示したように、画質制御回路 2 を備えていてもよい。このようにした場合であっても、上記適用例と同様、撮像素子 1 b の画質調整を自動的に行うことができる。

#### 【0101】

##### <5. 応用例>

##### [応用例 1]

本開示に係る技術（本技術）は、様々な製品へ応用することができる。例えば、本開示に係る技術は、自動車、電気自動車、ハイブリッド電気自動車、自動二輪車、自転車、パーソナルモビリティ、飛行機、ドローン、船舶、ロボット等のいずれかの種類の移動体に搭載される装置として実現されてもよい。

#### 【0102】

10

20

30

40

50

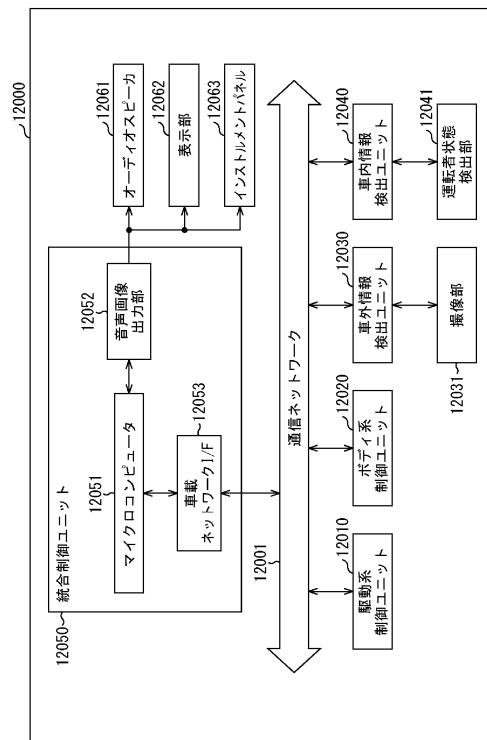

図30は、本開示に係る技術が適用され得る移動体制御システムの一例である車両制御システムの概略的な構成例を示すブロック図である。

#### 【0103】

車両制御システム12000は、通信ネットワーク12001を介して接続された複数の電子制御ユニットを備える。図30に示した例では、車両制御システム12000は、駆動系制御ユニット12010、ボディ系制御ユニット12020、車外情報検出ユニット12030、車内情報検出ユニット12040、及び統合制御ユニット12050を備える。また、統合制御ユニット12050の機能構成として、マイクロコンピュータ12051、音声画像出力部12052、及び車載ネットワークI/F(*interface*)12053が図示されている。10

#### 【0104】

駆動系制御ユニット12010は、各種プログラムにしたがって車両の駆動系に関連する装置の動作を制御する。例えば、駆動系制御ユニット12010は、内燃機関又は駆動用モータ等の車両の駆動力を発生させるための駆動力発生装置、駆動力を車輪に伝達するための駆動力伝達機構、車両の舵角を調節するステアリング機構、及び、車両の制動力を発生させる制動装置等の制御装置として機能する。

#### 【0105】

ボディ系制御ユニット12020は、各種プログラムにしたがって車体に装備された各種装置の動作を制御する。例えば、ボディ系制御ユニット12020は、キーレスエントリーシステム、スマートキーシステム、パワーウィンドウ装置、あるいは、ヘッドライト、バックランプ、ブレーキランプ、ウィンカー又はフォグランプ等の各種ランプの制御装置として機能する。この場合、ボディ系制御ユニット12020には、鍵を代替する携帯機から発信される電波又は各種スイッチの信号が入力され得る。ボディ系制御ユニット12020は、これらの電波又は信号の入力を受け付け、車両のドアロック装置、パワーウィンドウ装置、ランプ等を制御する。20

#### 【0106】

車外情報検出ユニット12030は、車両制御システム12000を搭載した車両の外部の情報を検出する。例えば、車外情報検出ユニット12030には、撮像部12031が接続される。車外情報検出ユニット12030は、撮像部12031に車外の画像を撮像させるとともに、撮像された画像を受信する。車外情報検出ユニット12030は、受信した画像に基づいて、人、車、障害物、標識又は路面上の文字等の物体検出処理又は距離検出処理を行ってもよい。30

#### 【0107】

撮像部12031は、光を受光し、その光の受光量に応じた電気信号を出力する光センサである。撮像部12031は、電気信号を画像として出力することもできるし、測距の情報として出力することもできる。また、撮像部12031が受光する光は、可視光であつても良いし、赤外線等の非可視光であつても良い。

#### 【0108】

車内情報検出ユニット12040は、車内の情報を検出する。車内情報検出ユニット12040には、例えば、運転者の状態を検出する運転者状態検出部12041が接続される。運転者状態検出部12041は、例えば運転者を撮像するカメラを含み、車内情報検出ユニット12040は、運転者状態検出部12041から入力される検出情報に基づいて、運転者の疲労度合い又は集中度合いを算出してもよいし、運転者が居眠りをしていないかを判別してもよい。40

#### 【0109】

マイクロコンピュータ12051は、車外情報検出ユニット12030又は車内情報検出ユニット12040で取得される車内外の情報に基づいて、駆動力発生装置、ステアリング機構又は制動装置の制御目標値を演算し、駆動系制御ユニット12010に対して制御指令を出力することができる。例えば、マイクロコンピュータ12051は、車両の衝突回避あるいは衝撃緩和、車間距離に基づく追従走行、車速維持走行、車両の衝突警告、50

又は車両のレーン逸脱警告等を含む A D A S ( Advanced Driver Assistance System ) の機能実現を目的とした協調制御を行うことができる。

**【 0 1 1 0 】**

また、マイクロコンピュータ 1 2 0 5 1 は、車外情報検出ユニット 1 2 0 3 0 又は車内情報検出ユニット 1 2 0 4 0 で取得される車両の周囲の情報に基づいて駆動力発生装置、ステアリング機構又は制動装置等を制御することにより、運転者の操作に拘らずに自律的に走行する自動運転等を目的とした協調制御を行うことができる。

**【 0 1 1 1 】**

また、マイクロコンピュータ 1 2 0 5 1 は、車外情報検出ユニット 1 2 0 3 0 で取得される車外の情報に基づいて、ボディ系制御ユニット 1 2 0 2 0 に対して制御指令を出力することができる。例えば、マイクロコンピュータ 1 2 0 5 1 は、車外情報検出ユニット 1 2 0 3 0 で検出した先行車又は対向車の位置に応じてヘッドライトランプを制御し、ハイビームをロービームに切り替える等の防眩を図ることを目的とした協調制御を行うことができる。

10

**【 0 1 1 2 】**

音声画像出力部 1 2 0 5 2 は、車両の搭乗者又は車外に対して、視覚的又は聴覚的に情報を通知することが可能な出力装置へ音声及び画像のうちの少なくとも一方の出力信号を送信する。図 3 0 の例では、出力装置として、オーディオスピーカ 1 2 0 6 1 、表示部 1 2 0 6 2 及びインストルメントパネル 1 2 0 6 3 が例示されている。表示部 1 2 0 6 2 は、例えば、オンボードディスプレイ及びヘッドアップディスプレイの少なくとも一つを含んでいてもよい。

20

**【 0 1 1 3 】**

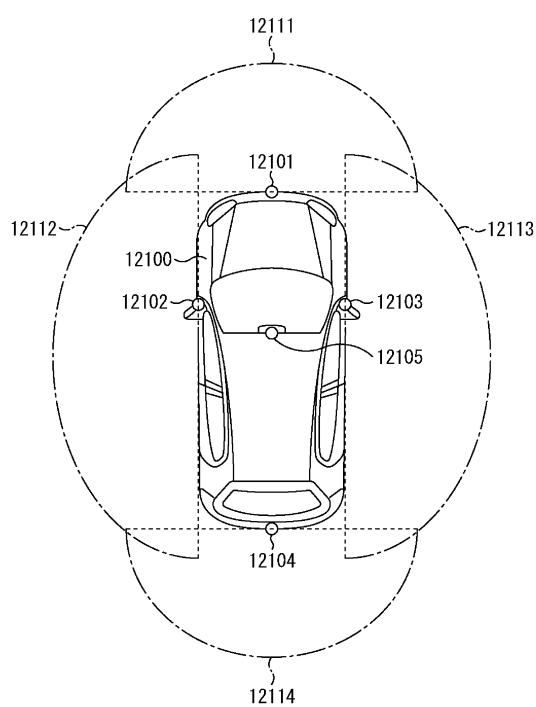

図 3 1 は、撮像部 1 2 0 3 1 の設置位置の例を示す図である。

**【 0 1 1 4 】**

図 3 1 は、車両 1 2 1 0 0 は、撮像部 1 2 0 3 1 として、撮像部 1 2 1 0 1 , 1 2 1 0 2 , 1 2 1 0 3 , 1 2 1 0 4 , 1 2 1 0 5 を有する。

**【 0 1 1 5 】**

撮像部 1 2 1 0 1 , 1 2 1 0 2 , 1 2 1 0 3 , 1 2 1 0 4 , 1 2 1 0 5 は、例えば、車両 1 2 1 0 0 のフロントノーズ、サイドミラー、リアバンパ、バックドア及び車室内のフロントガラスの上部等の位置に設けられる。フロントノーズに備えられる撮像部 1 2 1 0 1 及び車室内のフロントガラスの上部に備えられる撮像部 1 2 1 0 5 は、主として車両 1 2 1 0 0 の前方の画像を取得する。サイドミラーに備えられる撮像部 1 2 1 0 2 , 1 2 1 0 3 は、主として車両 1 2 1 0 0 の側方の画像を取得する。リアバンパ又はバックドアに備えられる撮像部 1 2 1 0 4 は、主として車両 1 2 1 0 0 の後方の画像を取得する。撮像部 1 2 1 0 1 及び 1 2 1 0 5 で取得される前方の画像は、主として先行車両又は、歩行者、障害物、信号機、交通標識又は車線等の検出に用いられる。

30

**【 0 1 1 6 】**

なお、図 3 1 には、撮像部 1 2 1 0 1 ないし 1 2 1 0 4 の撮影範囲の一例が示されている。撮像範囲 1 2 1 1 1 は、フロントノーズに設けられた撮像部 1 2 1 0 1 の撮像範囲を示し、撮像範囲 1 2 1 1 2 , 1 2 1 1 3 は、それぞれサイドミラーに設けられた撮像部 1 2 1 0 2 , 1 2 1 0 3 の撮像範囲を示し、撮像範囲 1 2 1 1 4 は、リアバンパ又はバックドアに設けられた撮像部 1 2 1 0 4 の撮像範囲を示す。例えば、撮像部 1 2 1 0 1 ないし 1 2 1 0 4 で撮像された画像データが重ね合わせられることにより、車両 1 2 1 0 0 を上方から見た俯瞰画像が得られる。

40

**【 0 1 1 7 】**

撮像部 1 2 1 0 1 ないし 1 2 1 0 4 の少なくとも 1 つは、距離情報を取得する機能を有していてもよい。例えば、撮像部 1 2 1 0 1 ないし 1 2 1 0 4 の少なくとも 1 つは、複数の撮像素子からなるステレオカメラであってもよいし、位相差検出用の画素を有する撮像素子であってもよい。

**【 0 1 1 8 】**

例えば、マイクロコンピュータ 1 2 0 5 1 は、撮像部 1 2 1 0 1 ないし 1 2 1 0 4 から

50

得られた距離情報を基に、撮像範囲 12111ないし12114内における各立体物までの距離と、この距離の時間的变化（車両 12100に対する相対速度）を求ることにより、特に車両 12100の進行路上にある最も近い立体物で、車両 12100と略同じ方向に所定の速度（例えば、0 km/h以上）で走行する立体物を先行車として抽出することができる。さらに、マイクロコンピュータ 12051は、先行車の手前に予め確保すべき車間距離を設定し、自動ブレーキ制御（追従停止制御も含む）や自動加速制御（追従発進制御も含む）等を行うことができる。このように運転者の操作に拘らずに自律的に走行する自動運転等を目的とした協調制御を行うことができる。

#### 【0119】

例えば、マイクロコンピュータ 12051は、撮像部 12101ないし12104から得られた距離情報を元に、立体物に関する立体物データを、2輪車、普通車両、大型車両、歩行者、電柱等その他の立体物に分類して抽出し、障害物の自動回避に用いることができる。例えば、マイクロコンピュータ 12051は、車両 12100の周辺の障害物を、車両 12100のドライバが視認可能な障害物と視認困難な障害物とに識別する。そして、マイクロコンピュータ 12051は、各障害物との衝突の危険度を示す衝突リスクを判断し、衝突リスクが設定値以上で衝突可能性がある状況であるときには、オーディオスピーカ 12061や表示部 12062を介してドライバに警報を出力することや、駆動系制御ユニット 12010を介して強制減速や回避操舵を行うことで、衝突回避のための運転支援を行うことができる。

#### 【0120】

撮像部 12101ないし12104の少なくとも1つは、赤外線を検出する赤外線カメラであってもよい。例えば、マイクロコンピュータ 12051は、撮像部 12101ないし12104の撮像画像中に歩行者が存在するか否かを判定することで歩行者を認識することができる。かかる歩行者の認識は、例えば赤外線カメラとしての撮像部 12101ないし12104の撮像画像における特徴点を抽出する手順と、物体の輪郭を示す一連の特徴点にパターンマッチング処理を行って歩行者か否かを判別する手順によって行われる。マイクロコンピュータ 12051が、撮像部 12101ないし12104の撮像画像中に歩行者が存在すると判定し、歩行者を認識すると、音声画像出力部 12052は、当該認識された歩行者に強調のための方形輪郭線を重畳表示するように、表示部 12062を制御する。また、音声画像出力部 12052は、歩行者を示すアイコン等を所望の位置に表示するよう表示部 12062を制御してもよい。

#### 【0121】

以上、本開示に係る技術が適用され得る移動体制御システムの一例について説明した。本開示に係る技術は、以上説明した構成のうち、撮像部 12031に適用され得る。具体的には、撮像装置 3は、撮像部 12031に適用することができる。撮像部 12031に本開示に係る技術を適用することにより、高画質な撮影画像を得ることができるので、移動体制御システムにおいて撮影画像を利用した高精度な制御を行うことができる。

#### 【0122】

##### [応用例 2]

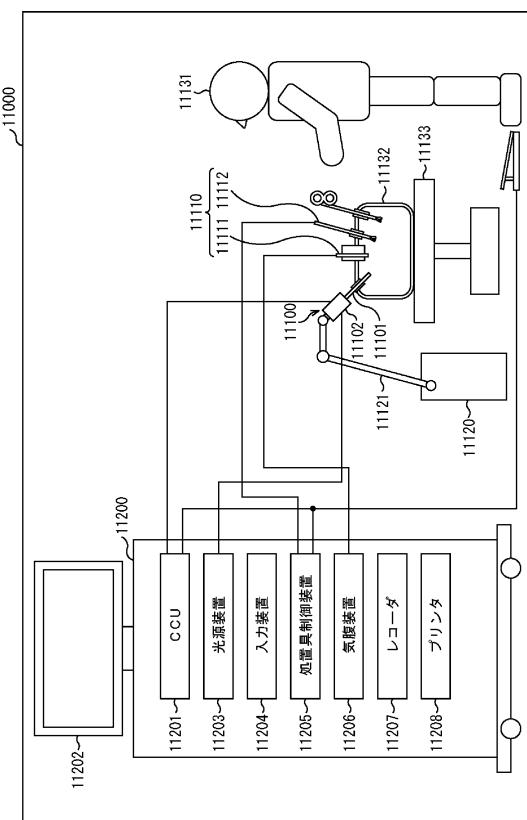

図 32 は、本開示に係る技術（本技術）が適用され得る内視鏡手術システムの概略的な構成の一例を示す図である。

#### 【0123】

図 32 では、術者（医師） 11131が、内視鏡手術システム 11000を用いて、患者ベッド 11133上の患者 11132に手術を行っている様子が図示されている。図示するように、内視鏡手術システム 11000は、内視鏡 11100と、気腹チューブ 11111やエネルギー処置具 11112等の、その他の術具 11110と、内視鏡 11100を支持する支持アーム装置 11120と、内視鏡下手術のための各種の装置が搭載されたカート 11200と、から構成される。

#### 【0124】

内視鏡 11100は、先端から所定の長さの領域が患者 11132の体腔内に挿入され

10

20

30

40

50

る鏡筒 11101 と、鏡筒 11101 の基端に接続されるカメラヘッド 11102 と、から構成される。図示する例では、硬性の鏡筒 11101 を有するいわゆる硬性鏡として構成される内視鏡 11100 を図示しているが、内視鏡 11100 は、軟性の鏡筒を有するいわゆる軟性鏡として構成されてもよい。

#### 【0125】

鏡筒 11101 の先端には、対物レンズが嵌め込まれた開口部が設けられている。内視鏡 11100 には光源装置 11203 が接続されており、当該光源装置 11203 によって生成された光が、鏡筒 11101 の内部に延設されるライトガイドによって当該鏡筒の先端まで導光され、対物レンズを介して患者 11132 の体腔内の観察対象に向かって照射される。なお、内視鏡 11100 は、直視鏡であってもよいし、斜視鏡又は側視鏡であってもよい。10

#### 【0126】

カメラヘッド 11102 の内部には光学系及び撮像素子が設けられており、観察対象からの反射光（観察光）は当該光学系によって当該撮像素子に集光される。当該撮像素子によって観察光が光電変換され、観察光に対応する電気信号、すなわち観察像に対応する画像信号が生成される。当該画像信号は、RAWデータとしてカメラコントロールユニット（CCU： Camera Control Unit）11201 に送信される。

#### 【0127】

CCU11201 は、CPU（Central Processing Unit）や GPU（Graphics Processing Unit）等によって構成され、内視鏡 11100 及び表示装置 11202 の動作を統括的に制御する。さらに、CCU11201 は、カメラヘッド 11102 から画像信号を受け取り、その画像信号に対して、例えば現像処理（デモザイク処理）等の、当該画像信号に基づく画像を表示するための各種の画像処理を施す。20

#### 【0128】

表示装置 11202 は、CCU11201 からの制御により、当該 CCU11201 によって画像処理が施された画像信号に基づく画像を表示する。

#### 【0129】

光源装置 11203 は、例えば LED（Light Emitting Diode）等の光源から構成され、術部等を撮影する際の照射光を内視鏡 11100 に供給する。30

#### 【0130】

入力装置 11204 は、内視鏡手術システム 11000 に対する入力インターフェースである。ユーザは、入力装置 11204 を介して、内視鏡手術システム 11000 に対して各種の情報の入力や指示入力を行うことができる。例えば、ユーザは、内視鏡 11100 による撮像条件（照射光の種類、倍率及び焦点距離等）を変更する旨の指示等を入力する。

#### 【0131】

処置具制御装置 11205 は、組織の焼灼、切開又は血管の封止等のためのエネルギー処置具 11112 の駆動を制御する。気腹装置 11206 は、内視鏡 11100 による視野の確保及び術者の作業空間の確保の目的で、患者 11132 の体腔を膨らめるために、気腹チューブ 11111 を介して当該体腔内にガスを送り込む。レコーダ 11207 は、手術に関する各種の情報を記録可能な装置である。プリンタ 11208 は、手術に関する各種の情報を、テキスト、画像又はグラフ等各種の形式で印刷可能な装置である。40

#### 【0132】

なお、内視鏡 11100 に術部を撮影する際の照射光を供給する光源装置 11203 は、例えば LED、レーザ光源又はこれらの組み合わせによって構成される白色光源から構成することができる。RGB レーザ光源の組み合わせにより白色光源が構成される場合には、各色（各波長）の出力強度及び出力タイミングを高精度に制御することができるため、光源装置 11203 において撮像画像のホワイトバランスの調整を行うことができる。また、この場合には、RGB レーザ光源それぞれからのレーザ光を時分割で観察対象に照射し、その照射タイミングに同期してカメラヘッド 11102 の撮像素子の駆動を制御す50

ることにより、RGBそれぞれに対応した画像を時分割で撮像することも可能である。当該方法によれば、当該撮像素子にカラーフィルタを設けなくても、カラー画像を得ることができる。

#### 【0133】

また、光源装置11203は、出力する光の強度を所定の時間ごとに変更するようにその駆動が制御されてもよい。その光の強度の変更のタイミングに同期してカメラヘッド11102の撮像素子の駆動を制御して時分割で画像を取得し、その画像を合成することにより、いわゆる黒つぶれ及び白とびのない高ダイナミックレンジの画像を生成することができる。

#### 【0134】

また、光源装置11203は、特殊光観察に対応した所定の波長帯域の光を供給可能に構成されてもよい。特殊光観察では、例えば、体組織における光の吸収の波長依存性を利用して、通常の観察時における照射光（すなわち、白色光）に比べて狭帯域の光を照射することにより、粘膜表層の血管等の所定の組織を高コントラストで撮影する、いわゆる狭帯域光観察（Narrow Band Imaging）が行われる。あるいは、特殊光観察では、励起光を照射することにより発生する蛍光により画像を得る蛍光観察が行われてもよい。蛍光観察では、体組織に励起光を照射し当該体組織からの蛍光を観察すること（自家蛍光観察）、又はインドシアニングリーン（ICG）等の試薬を体組織に局注するとともに当該体組織にその試薬の蛍光波長に対応した励起光を照射し蛍光像を得ること等を行うことができる。光源装置11203は、このような特殊光観察に対応した狭帯域光及び／又は励起光を供給可能に構成され得る。

10

#### 【0135】

図33は、図32に示すカメラヘッド11102及びCCU11201の機能構成の一例を示すブロック図である。

#### 【0136】

カメラヘッド11102は、レンズユニット11401と、撮像部11402と、駆動部11403と、通信部11404と、カメラヘッド制御部11405と、を有する。CCU11201は、通信部11411と、画像処理部11412と、制御部11413と、を有する。カメラヘッド11102とCCU11201とは、伝送ケーブル11400によって互いに通信可能に接続されている。

20

#### 【0137】

レンズユニット11401は、鏡筒11101との接続部に設けられる光学系である。鏡筒11101の先端から取り込まれた観察光は、カメラヘッド11102まで導光され、当該レンズユニット11401に入射する。レンズユニット11401は、ズームレンズ及びフォーカスレンズを含む複数のレンズが組み合わされて構成される。

#### 【0138】

撮像部11402は、撮像素子で構成される。撮像部11402を構成する撮像素子は、1つ（いわゆる単板式）であってもよいし、複数（いわゆる多板式）であってもよい。撮像部11402が多板式で構成される場合には、例えば各撮像素子によってRGBそれぞれに対応する画像信号が生成され、それらが合成されることによりカラー画像が得られてもよい。あるいは、撮像部11402は、3D（Dimensional）表示に対応する右目用及び左目用の画像信号をそれぞれ取得するための1対の撮像素子を有するように構成されてもよい。3D表示が行われることにより、術者11131は術部における生体組織の奥行きをより正確に把握することが可能になる。なお、撮像部11402が多板式で構成される場合には、各撮像素子に対応して、レンズユニット11401も複数系統設けられ得る。

30

#### 【0139】

また、撮像部11402は、必ずしもカメラヘッド11102に設けられなくてもよい。例えば、撮像部11402は、鏡筒11101の内部に、対物レンズの直後に設けられてもよい。

40

50

**【0140】**

駆動部11403は、アクチュエータによって構成され、カメラヘッド制御部11405からの制御により、レンズユニット11401のズームレンズ及びフォーカスレンズを光軸に沿って所定の距離だけ移動させる。これにより、撮像部11402による撮像画像の倍率及び焦点が適宜調整され得る。

**【0141】**

通信部11404は、CCU11201との間で各種の情報を送受信するための通信装置によって構成される。通信部11404は、撮像部11402から得た画像信号をRAWデータとして伝送ケーブル11400を介してCCU11201に送信する。

**【0142】**

また、通信部11404は、CCU11201から、カメラヘッド11102の駆動を制御するための制御信号を受信し、カメラヘッド制御部11405に供給する。当該制御信号には、例えば、撮像画像のフレームレートを指定する旨の情報、撮像時の露出値を指定する旨の情報、並びに／又は撮像画像の倍率及び焦点を指定する旨の情報等、撮像条件に関する情報が含まれる。

**【0143】**

なお、上記のフレームレートや露出値、倍率、焦点等の撮像条件は、ユーザによって適宜指定されてもよいし、取得された画像信号に基づいてCCU11201の制御部11413によって自動的に設定されてもよい。後者の場合には、いわゆるA E (Auto Exposure)機能、A F (Auto Focus)機能及びA W B (Auto White Balance)機能が内視鏡11100に搭載されていることになる。

20

**【0144】**

カメラヘッド制御部11405は、通信部11404を介して受信したCCU11201からの制御信号に基づいて、カメラヘッド11102の駆動を制御する。

**【0145】**

通信部11411は、カメラヘッド11102との間で各種の情報を送受信するための通信装置によって構成される。通信部11411は、カメラヘッド11102から、伝送ケーブル11400を介して送信される画像信号を受信する。

**【0146】**

また、通信部11411は、カメラヘッド11102に対して、カメラヘッド11102の駆動を制御するための制御信号を送信する。画像信号や制御信号は、電気通信や光通信等によって送信することができる。

30

**【0147】**

画像処理部11412は、カメラヘッド11102から送信されたRAWデータである画像信号に対して各種の画像処理を施す。

**【0148】**

制御部11413は、内視鏡11100による術部等の撮像、及び、術部等の撮像により得られる撮像画像の表示に関する各種の制御を行う。例えば、制御部11413は、カメラヘッド11102の駆動を制御するための制御信号を生成する。

**【0149】**

また、制御部11413は、画像処理部11412によって画像処理が施された画像信号に基づいて、術部等が映った撮像画像を表示装置11202に表示させる。この際、制御部11413は、各種の画像認識技術を用いて撮像画像内における各種の物体を認識してもよい。例えば、制御部11413は、撮像画像に含まれる物体のエッジの形状や色等を検出することにより、鉗子等の術具、特定の生体部位、出血、エネルギー処置具11112の使用時のミスト等を認識することができる。制御部11413は、表示装置11202に撮像画像を表示させる際に、その認識結果を用いて、各種の手術支援情報を当該術部の画像に重畠表示させてもよい。手術支援情報が重畠表示され、術者11131に提示されることにより、術者11131の負担を軽減することや、術者11131が確実に手術を進めることができる。

40

50

**【 0 1 5 0 】**

カメラヘッド 1 1 1 0 2 及び C C U 1 1 2 0 1 を接続する伝送ケーブル 1 1 4 0 0 は、電気信号の通信に対応した電気信号ケーブル、光通信に対応した光ファイバ、又はこれらの複合ケーブルである。

**【 0 1 5 1 】**

ここで、図示する例では、伝送ケーブル 1 1 4 0 0 を用いて有線で通信が行われていたが、カメラヘッド 1 1 1 0 2 と C C U 1 1 2 0 1 との間の通信は無線で行われてもよい。

**【 0 1 5 2 】**

以上、本開示に係る技術が適用され得る内視鏡手術システムの一例について説明した。本開示に係る技術は、以上説明した構成のうち、内視鏡 1 1 1 0 0 のカメラヘッド 1 1 1 0 2 に設けられた撮像部 1 1 4 0 2 に好適に適用され得る。撮像部 1 1 4 0 2 に本開示に係る技術を適用することにより、高画質な撮影画像を得ることができるので、高画質な内視鏡 1 1 1 0 0 を提供することができる。

10

**【 0 1 5 3 】**

以上、実施の形態およびその変形例、適用例および応用例を挙げて本開示を説明したが、本開示は実施の形態等に限定されるものではなく、種々変形が可能である。なお、本明細書中に記載された効果は、あくまで例示である。本開示の効果は、本明細書中に記載された効果に限定されるものではない。本開示が、本明細書中に記載された効果以外の効果を持っていてもよい。

**【 0 1 5 4 】**

20

また、例えば、本開示は以下のよう構成を取ることができる。

**( 1 )**

各々が光電変換部と、前記光電変換部から出力された電荷に基づく画素信号を出力する読み出し回路とを含む複数のセンサ画素と、

前記画素信号に基づく制御電圧を各前記光電変換部に印加する電圧制御部と

を備えた撮像素子。

**( 2 )**

前記電圧制御部は、前記画素信号が第 1 闘値を超えたときに前記制御電圧を相対的に大きくし、前記画素信号が前記第 1 闘値よりも小さな第 2 闘値を下回ったときに前記制御電圧を相対的に小さくする

30

( 1 ) に記載の撮像素子。

**( 3 )**

各前記センサ画素は、前記光電変換部を挟み込む第 1 電極および第 2 電極を更に有し、前記電圧制御部は、前記第 1 電極に印加する第 1 電圧と、前記第 2 電極に印加する第 2 電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第 1 電圧および前記第 2 電圧を生成する

( 1 ) または ( 2 ) に記載の撮像素子。

**( 4 )**

各前記センサ画素は、

前記光電変換部から転送された電荷を保持する電荷保持部と

前記第 2 電極に電気的に接続され、前記光電変換部から前記電荷保持部に電荷を転送する転送トランジスタと

前記第 2 電極に電気的に接続され、前記光電変換部の電荷を初期化する排出トランジスタと

を更に含み、

前記電圧制御部は、前記排出トランジスタがオンしているときに、前記第 2 電極に前記第 2 電圧を印加する

40

( 3 ) に記載の撮像素子。

**( 5 )**

各前記画素は、

50

前記光電変換部を挟み込む第1電極および第2電極と、

前記光電変換部から転送された電荷を保持する電荷保持部と

前記第2電極に電気的に接続され、前記光電変換部から前記電荷保持部に電荷を転送する転送トランジスタと

を更に含み、

前記読み出し回路は、前記電荷保持部の電位を初期化するリセットトランジスタを有し、

前記電圧制御部は、前記第1電極に印加する第1電圧と、前記転送トランジスタがオンしているときに前記リセットトランジスタによって印加された前記第2電極の第2電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第1電圧を生成する

(1) または (2) に記載の撮像素子。

10

(6)

各前記画素は、前記光電変換部から転送された電荷を保持する電荷保持部を更に含み、

前記読み出し回路は、前記電荷保持部の電位を初期化するリセットトランジスタを有し、

前記電圧制御部は、前記第1電極に印加する第1電圧と、前記リセットトランジスタによって印加された前記第2電極の第2電圧との電位差が前記制御電圧となるように、前記画素信号に基づいて前記第1電圧を生成する

(1) または (2) に記載の撮像素子。

(7)

前記画素信号をA D (Analog-to-Digital) 変換するA D 変換回路と、

前記画素信号に基づくレンジ設定値を前記A D 変換回路に出力するレンジ制御部と

を更に備えた

20

(1) ないし (6) のいずれか1つに記載の撮像素子。

(8)

前記レンジ制御部は、前記画素信号が第1閾値を超えたときに前記レンジ設定値を相対的に大きくし、前記画素信号が前記第1閾値よりも小さな第2閾値を下回ったときに前記レンジ設定値を相対的に小さくする

(7) に記載の撮像素子。

(9)

各前記センサ画素は、

前記光電変換部から転送された電荷を保持する電荷保持部と

前記光電変換部から前記電荷保持部に電荷を転送する転送トランジスタと

前記電荷保持部に接続されたスイッチ素子と、

前記スイッチ素子を介して前記電荷保持部の容量と並列に接続された補助容量と、

前記画素信号に基づいて前記スイッチ素子のオンオフを制御する変換効率制御部と

を更に備えた

30

(1) ないし (6) のいずれか1つに記載の撮像素子。

(10)

前記変換効率制御部は、前記画素信号が第1閾値を超えたときに前記スイッチ素子をオフし、前記画素信号が前記第1閾値よりも小さな第2閾値を下回ったときに前記前記スイッチ素子をオンする

40

(9) に記載の撮像素子。

(11)

各々が光電変換部と、前記光電変換部から出力された電荷に基づく画素信号を出力する読み出し回路とを含む複数のセンサ画素を有する撮像素子と、

前記画素信号に基づく制御電圧を各前記光電変換部に印加する画質制御回路と

を備えた

撮像装置。

【0155】

本開示の一実施の形態に係る撮像素子および撮像装置によれば、画素信号に基づく制御電圧を各光電変換部に印加するようにしたので、各光電変換部に固定電圧を印加した場合

50

と比べて、画像データの輝度の大きさに応じた画質調整を行うことができる。従って、画質の低下を抑えることができる。なお、本開示の効果は、ここに記載された効果に必ずしも限定されず、本明細書中に記載されたいずれの効果であってもよい。

【0156】

本出願は、日本国特許庁において2019年3月11日に出願された日本特許出願番号第2019-043786号を基礎として優先権を主張するものであり、この出願のすべての内容を参照によって本出願に援用する。

【0157】

当業者であれば、設計上の要件や他の要因に応じて、種々の修正、コンビネーション、サブコンビネーション、および変更を想到し得るが、それらは添付の請求の範囲やその均等物の範囲に含まれるものであることが理解される。

10

20

30

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

10

20

30

40

50

【図 5】

【図 6】

10

【図 7】

【図 8】

20

30

40

50

【図 9】

【図 10】

【図 11】

【図 12】

10

20

30

40

50

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

10

20

30

40

50

【図 17】

【図 18】

【図 19】

【図 20】

10

20

30

40

50

【図 2 1】

【図 2 2】

10

【図 2 3】

【図 2 4】

20

30

40

50

【図25】

【図26】

【図27】

【図28】

10

20

30

40

50

【図 2 9】

【図 3 0】

10

20

30

40

【図 3 1】

【図 3 2】

50

【図 3 3】

10

20

30

40

50

---

フロントページの続き

(56)参考文献 国際公開第2017/150167 (WO, A1)

特開2018-098690 (JP, A)

特開2016-134909 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H04N 5/30 - 5/33

23/11

23/20 - 23/30

25/00

25/20 - 25/61

25/615 - 25/79

H01L 27/14 - 27/148

27/30

29/76