(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-205782

(P2010-205782A)

(43) 公開日 平成22年9月16日(2010.9.16)

| (51) Int.Cl.                    | F 1                      | テーマコード (参考) |

|---------------------------------|--------------------------|-------------|

| <b>HO 1 L 21/3205 (2006.01)</b> | HO 1 L 21/88 Q 4 M 1 O 4 |             |

| <b>HO 1 L 23/52 (2006.01)</b>   | HO 1 L 21/90 A 5 F O 3 3 |             |

| <b>HO 1 L 21/768 (2006.01)</b>  | HO 1 L 21/90 C           |             |

| <b>HO 1 L 21/28 (2006.01)</b>   | HO 1 L 21/28 3 O 1 S     |             |

|                                 | HO 1 L 21/28 A           |             |

審査請求 未請求 請求項の数 15 O L (全 12 頁)

|           |                            |          |                                                      |

|-----------|----------------------------|----------|------------------------------------------------------|

| (21) 出願番号 | 特願2009-46801 (P2009-46801) | (71) 出願人 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地 |

| (22) 出願日  | 平成21年2月27日 (2009.2.27)     | (74) 代理人 | 100110928<br>弁理士 速水 進治                               |

|           |                            | (72) 発明者 | 中山 知士<br>神奈川県川崎市中原区下沼部1753番地<br>NECエレクトロニクス株式会社内     |

|           |                            | (72) 発明者 | 笠間 佳子<br>神奈川県川崎市中原区下沼部1753番地<br>NECエレクトロニクス株式会社内     |

|           |                            | (72) 発明者 | 藤倉 栄一<br>山形県鶴岡市宝田一丁目11番73号<br>NECセミコンダクターズ山形株式会社内    |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】デボ物を充分除去することを可能とし、かつシリサイド層表面を酸化することが無い洗浄工程を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置100の製造方法は、Niを含むシリサイド層104の上面に形成された絶縁層をドライエッチングして、Niを含むシリサイド層104を露出させる工程と、Niを含むシリサイド層104を還元性を有する還元水で洗浄する工程と、を含むことを特徴とする。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

Niを含むシリサイド層の上面に形成された絶縁層をドライエッチングして、前記Niを含むシリサイド層を露出させる工程と、

前記Niを含むシリサイド層を還元水で洗浄する工程と、を含む半導体装置の製造方法。

**【請求項 2】**

前記還元水は、塩基性でかつ還元性を有する水溶液である請求項1に記載の半導体装置の製造方法。

**【請求項 3】**

前記還元水は、アンモニアを0.01 ppm以上、1000 ppm以下の範囲で含有する水素水または電解還元水である請求項1または2に記載の半導体装置の製造方法。

**【請求項 4】**

前記還元水は、pHが7より大きく、ORP(酸化還元電位)が負である請求項1から3のいずれかに記載の半導体装置の製造方法。

**【請求項 5】**

前記Niを含むシリサイド層を露出させる工程後、酸化性ガスを含んだガスによる処理を施すことなく、かつpH 7である液体にさらすことなく、前記還元水で洗浄する工程と、を含む請求項1から4のいずれかに記載の半導体装置の製造方法。

**【請求項 6】**

前記絶縁層に凹部を形成する工程と、

前記凹部を還元水で洗浄する工程と、をさらに含む請求項1から5のいずれかに記載の半導体装置の製造方法。

**【請求項 7】**

前記還元水で洗浄する工程後、pH 7である液体にさらすことなく、さらに乾燥処理を施す工程と、を含む請求項1から6のいずれかに記載の半導体装置の製造方法。

**【請求項 8】**

前記乾燥処理を施す工程後、さらに前記凹部にバリアメタルおよび金属膜を形成する工程と、を含む請求項7に記載の半導体装置の製造方法。

**【請求項 9】**

前記乾燥処理を施す工程後、前記酸化性ガスを含んだガスによる処理を施すことなく、かつ前記pH 7である液体にさらすことなく、前記凹部に前記バリアメタルおよび前記金属膜を形成する工程と、を含む請求項7または8に記載の半導体装置の製造方法。

**【請求項 10】**

前記絶縁層は、少なくとも、第1の絶縁膜と、その上面に形成された第2の絶縁膜と、を含む請求項6から9のいずれかに記載の半導体装置の製造方法。

**【請求項 11】**

前記凹部を形成する工程が、レジストをマスクとして前記第2の絶縁膜を選択的にエッティングする工程と、

前記レジストを除去する工程と、

前記第2の絶縁膜をマスクとして前記第1の絶縁膜を選択的にエッティングする工程と、を含む請求項10に記載の半導体装置の製造方法。

**【請求項 12】**

前記第1の絶縁膜は、シリコン窒化膜である請求項10または11に記載の半導体装置の製造方法。

**【請求項 13】**

前記第2の絶縁膜は、シリコン酸化膜である請求項10から12のいずれかに記載の半導体装置の製造方法。

**【請求項 14】**

前記Niを含むシリサイド層は、Nisi層、Nip<sub>t</sub>Si層、およびこれらの積層か

10

20

30

40

50

ら選択される請求項 1 から 13 のいずれかに記載の半導体装置の製造方法。

【請求項 15】

前記還元水で洗浄する工程後、前記Niを含むシリサイド層が前記還元水で覆われてから、前記凹部に前記バリアメタルおよび前記金属膜を形成する工程までの間に、前記Niを含むシリサイド層は水にさらされることがない請求項 8 から 14 のいずれかに記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関する。

10

【背景技術】

【0002】

半導体装置の微細化、高集積化、高速化に伴い、ゲート電極上やソースドレイン（拡散層）上に形成されるシリサイドにはより低抵抗な材料が要求され、そのため、NiSi、NiPtSiなど、Niを含んだシリサイド膜が用いられるようになってきた。

一方、コンタクトプラグ形成時に薄膜シリサイドの突き抜け防止やサイドウォール残膜確保のためドライエッチングの高選択性が求められており、その際発生するデポ物の除去とシリサイドの酸化と溶解との両立が困難になってきている。

【0003】

シリサイド層上に形成された絶縁膜でのコンタクトホールの形成方法として、たとえば特許文献 1 には、以下のような技術が記載されている。

20

【0004】

特許文献 1 では、シリサイド層上に、エッチング阻止膜として SiN 膜を形成し、その上面に層間絶縁膜としてシリコン酸化膜を形成する。その後、コンタクトホールを形成するための開口を含む所定パターンのレジスト膜を形成し、そのレジスト膜をマスクとして、シリコン酸化膜をドライエッチングにより選択的に除去し、O<sub>2</sub> プラズマなどによるアッシングなどによってレジスト膜を剥離する。その後、シリコン酸化膜をマスクとして、エッチング阻止膜の SiN 膜を選択的に除去する。このようにして、コンタクトホールが形成される。この特許文献 1 のコンタクトホールの形成方法では、エッチング阻止膜の SiN 膜が残存した状態でアッシングを施しているため、シリサイド層が露出した状態で O<sub>2</sub> プラズマにさらされることは無い。

30

【0005】

前述のように、低抵抗化にともない、シリサイドとして NiSi など、Ni を含んだシリサイド層を用いた場合、エッチング阻止膜である SiN 膜のエッチングの際は、Ni シリサイド層との高選択性が要求されるようになった。したがって、SiN 膜のエッチングは、高選択性を得るためにデポ物が発生しやすい条件で行われることになり、その結果、コンタクトホールの底部には、デポ物が生じやすくなつた。そのため、コンタクトホール形成後、このデポ物を除去する洗浄が重要となつてくる。

【0006】

この種のデポ物の除去としては、一般には、アッシングやアンモニア水と過酸化水素水の混合液（以下、アンモニア過水）、フッ酸、硫酸と過酸化水素水の混合液（以下、硫酸過水）などが用いられている。

40

【0007】

特許文献 1 には、コンタクトホール形成後、フッ酸などの酸洗浄を施し、その後アルカリ性薬液で処理することが開示されている。また、シリサイド層表面に RF エッチングを施すことも開示されている。

【0008】

特許文献 2 には、カソード水やアノード水が、シリサイド層を露出させる開口部形成のエッチング工程後に施される洗浄工程にも適用できることが開示されている。ただし、同文献によれば、カソード水やアノード水となる電解質水溶液には 1 ~ 30 質量% の水酸化

50

アンモニウム、1～30質量%のフッ化物が溶解しているとされる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2007-234760公報

【特許文献2】特開2002-146574公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、上記文献記載の従来技術は、以下の点で課題を有していた。

上記特許文献1等の従来技術では、シリサイド層上のデポ物を除去するために、酸を含む水溶液や酸素プラズマ処理等の酸化処理を伴う。また、特許文献2では、1～30質量%の水酸化アンモニウムの電解質水溶液を用いるため、水洗工程が必須になる。

また、シリサイド層、特にNiシリサイド層は、水洗工程によっても酸化されやすい。

このため、上記従来技術により、シリサイド層上のデポ物を除去すると、シリサイド層が酸化されてしまうという問題がある。

【課題を解決するための手段】

【0011】

本発明によれば、Niを含むシリサイド層の上面に形成された絶縁層をドライエッチングして、前記Niを含むシリサイド層を露出させる工程と、

前記Niを含むシリサイド層を還元水で洗浄する工程と、を含む半導体装置の製造方法が提供される。

【0012】

Niを含むシリサイド層上のドライエッチングで生成されたデポ物を、還元水で洗浄することができる。

【発明の効果】

【0013】

本発明によれば、シリサイド層を酸化させることなくデポ物を除去することができる半導体装置の製造方法が提供される。

【図面の簡単な説明】

【0014】

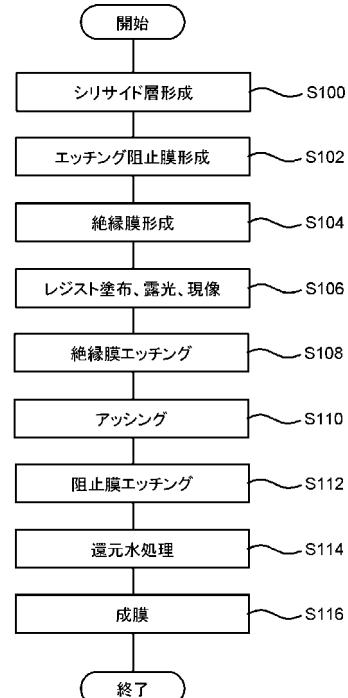

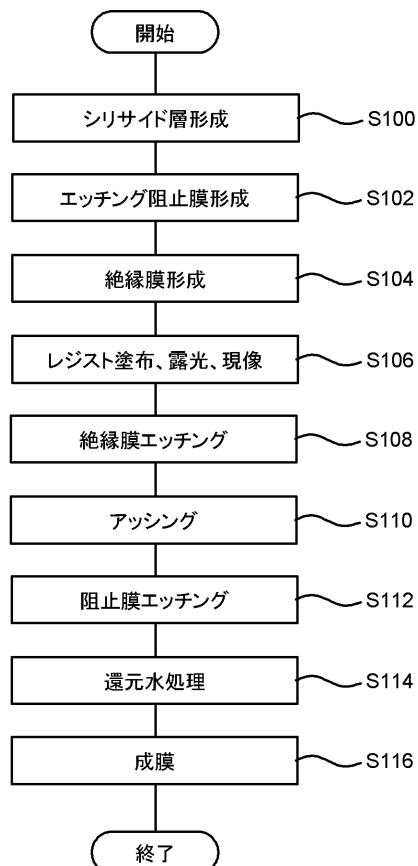

【図1】本発明の実施の形態における半導体装置の製造手順を示すフローチャートを示す図である。

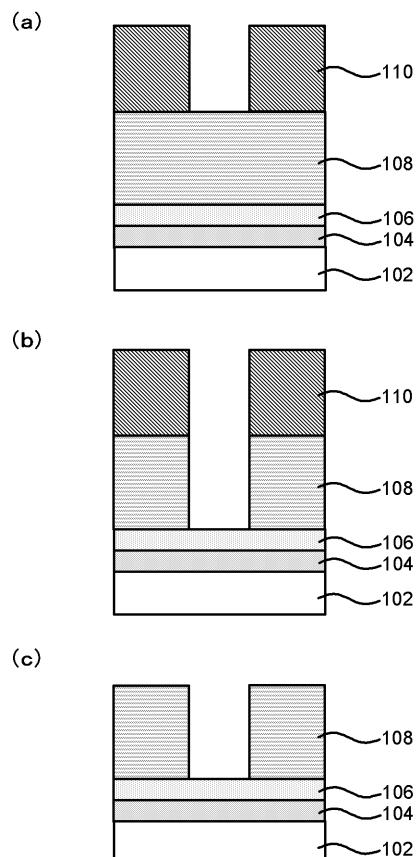

【図2】本発明の実施の形態における半導体装置の製造手順を示す工程断面図である。

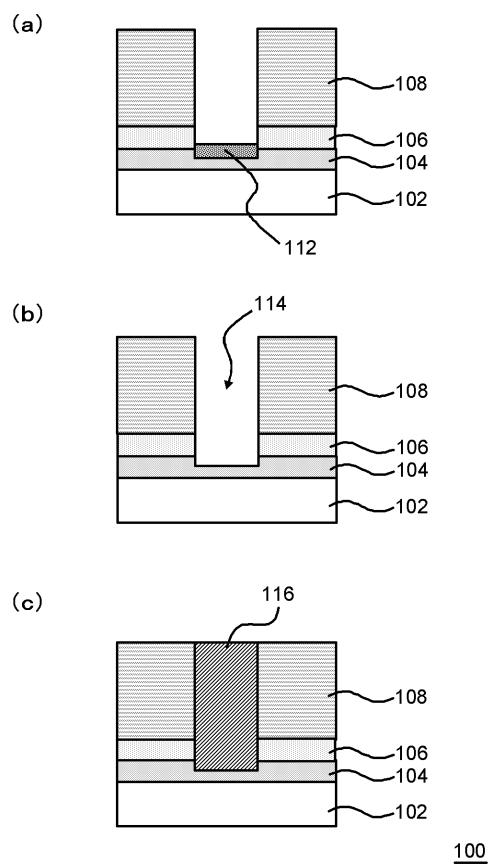

【図3】本発明の実施の形態における半導体装置の製造手順を示す工程断面図である。

【図4】本発明の実施の形態における断面SEM画像を示す図である。

【図5】本発明の実施の形態におけるコンタクトホールの底のXPSスペクトルを示す図である。

【発明を実施するための形態】

【0015】

本発明の実施の一形態を図面を参照して以下に説明する。尚、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0016】

本実施の形態の半導体装置の製造方法について、図1から図3を用いて以下説明する。

図1は、本実施の形態における半導体装置の製造手順を示すフローチャートである。図2、図3は、半導体装置の製造手順を示す工程断面図を示すものである。

本実施の形態において、まず、半導体基板102上にNiを含むシリサイド層104を形成する(S100)。つづいて、Niを含むシリサイド層104上にエッティング阻止膜106を形成する(S102)。次いで、エッティング阻止膜106上に絶縁膜108を形成する(S104)。その後、絶縁膜上に所定パターンのレジスト層110を形成し(S

10

20

30

40

50

106)、レジスト層110をマスクとして絶縁膜108をエッティングしてコンタクトホール(開口部)を形成する(S108)。つづいて、アッシングによりレジスト層110を除去する(S110)。

【0017】

次いで、絶縁膜108をマスクとしてドライエッティングにより、エッティング阻止膜106を除去する(S112)。これにより、コンタクトホールの底面にNiを含むシリサイド層104が露出する。つづいて、半導体基板102全面を還元水114で洗浄する(S114)。これにより、コンタクトホール内に堆積したデポ物112が除去され、Niを含むシリサイド層104表面が清浄化される。本実施の形態においては、還元水114は、塩基性でかつ還元性を有する水溶液とする。

10

【0018】

本実施の形態において、このようにNiを含むシリサイド層104表面を保護した状態で、半導体基板102を成膜チャンバに移動する。次いで、成膜チャンバ内でコンタクトホール内に導電膜を成膜し、金属膜116を形成する(S116)。

【0019】

次に、以上の処理を詳細に説明する。図において、本発明に直接関係しないゲート絶縁膜やゲート電極などの記載は省略し、ソース・ドレイン上のシリサイド部分のみを記載している。

【0020】

Niを含むシリサイド層104は、NiSi層、NiPtSi層、およびこれらの積層から選択されることが好ましく、以下のようにして製造することができる。ここでは、NiSi層を形成する例を説明する。まず、シリコン基板である半導体基板102上面に、Ni膜である金属膜(膜厚約50以上、200以下)をスパッタ法により形成する。つづいて、たとえば250以上、350以下で、第1の熱処理(シンター)を行う。これにより、Ni<sub>2</sub>Si層が形成される。その後、未反応の金属膜をSPM(硫酸過水、Salfaric Acid/Hydrogen Peroxide(/Water)Mixture)等を用いたエッティングにより除去する。つづいて、たとえば350以上、400以下で、第2の熱処理(シンター)を行う。これにより、NiSi層が形成される。

20

【0021】

本実施の形態の半導体装置100の製造方法において、絶縁層は、少なくとも、第1の絶縁膜(エッティング阻止膜106)と、その上面に形成された第2の絶縁膜(絶縁膜108)と、を含むことが好ましい。

30

また、コンタクトホールを形成する工程が、レジストをマスクとして絶縁膜108を選択的にエッティングする工程と、レジストを除去する工程と、絶縁膜108をマスクとしてエッティング阻止膜106を選択的にエッティングする工程と、を含むことが好ましい。

エッティング阻止膜106は、たとえばSiN膜により構成することができる。エッティング阻止膜106は、たとえばALD法により形成することができる。絶縁膜108は、たとえばシリコン酸化膜(SiO<sub>2</sub>)により構成することができる。

【0022】

つづいて、絶縁膜108上に、コンタクトホールを形成するための開口を含む所定パターンのレジスト層110を形成する(図2(a))。つづいて、レジスト層110をマスクとして、ドライエッティングにより絶縁膜108を選択的に除去する(図2(b))。つづいて、アッシングまたはSPMやAPMを用いたウェットエッティングにより、レジスト層110を除去する(図2(c))。次いで、絶縁膜108をマスクとして、ドライエッティングによりエッティング阻止膜106を選択的に除去する(図3(a))。これにより、Niを含むシリサイド層104に達する凹部(コンタクトホール)が形成される。

40

【0023】

エッティング阻止膜106のドライエッティング(S112)において、用いるガスの選択比が求められるため、例えばCH<sub>3</sub>FのようにH比率の高いガスを使用することが好ましい。さらに、たとえばCH<sub>2</sub>F<sub>2</sub>やCHF<sub>3</sub>などのフルオロカーボンガスを用いてもよい。

50

また酸素ガスなどを含めてよい。

【0024】

しかし、このとき、コンタクトホールには、ドライエッティングによるデポ物112が形成される。本実施の形態において、このようなコンタクトホール内に残っているデポ物112を還元水114で洗浄除去する(図3(b)、図1のステップS114)。これにより、デポ物112が除去されて、Niを含むシリサイド層104が清浄化される。洗浄には、単にリーンスすることも含まれる。

【0025】

本実施の形態の半導体装置100の製造方法は、Niを含むシリサイド層104の上面に形成された絶縁層をドライエッティングして、Niを含むシリサイド層104を露出させる工程と、Niを含むシリサイド層104を還元水114で洗浄する工程と、を含むことが好みしい。

さらに、絶縁層に凹部(コンタクトホール)を形成する工程と、コンタクトホールを還元水114で洗浄する工程と、を含むことが好みしい。

【0026】

ここで、還元水洗浄直前の上記還元水は、Niを含むシリサイド層104の表面をOH基で保護することでシリサイド層の酸化を防ぐため、アンモニアを0.01ppm以上で含有する水素水または電解還元水が好みしい。さらに、上記還元水は、還元水処理後に水洗が不要なように、アンモニアは1000ppm以下の範囲で含有する水素水または電解還元水であることが好みしい。

さらに、アンモニアの濃度は、0.1ppm以上、100ppm以下の範囲であることがより好みしい。この範囲にあるので、上記還元水は塩基性である。アンモニアの濃度は、還元水処理直前にpHメータを用いてpH値から計量した。pHメータは市販されているものを用いることができる。

【0027】

また、上記還元水は、pHが7よりも大きく、ORP(酸化還元電位)が負であることが好みしい。さらにpHが8よりも大きいことが好みしい。また、還元性によりデポ物を除去するためには、ORPが-100mVより小さいことが好みしい。特に、ORPは-800mV以上、-500mV以下が望ましい。この範囲にあるので、上記還元水は、還元性である。

pHは、上記還元水処理直前にpHメータを用いて測定した。酸化還元電位は、上記還元水処理直前にORPメータを用いて測定した。ORPメータは市販されているものを用いることができる。

【0028】

上記還元水の液温は、室温でもよく、適宜室温より高い温度で用いてよい。

【0029】

上記電解還元水とは、アンモニウムイオンを少量(1質量%以下)含む水を電気分解した際に、陰極側に生成される液のことをいう。上記電解還元水を得るための生成装置として、たとえば二槽式電気分解方式の装置を用いることができるが、これ以外に三槽式の装置を使用することもできる。上記水素水としては、電気分解によって陰極で発生した水素ガス、または、ボンベからの水素ガスを弱アンモニア水に溶解させた水が望ましい。

アンモニウムイオン量を調整することで、所望のpHおよび酸化還元電位を得ることができ、また溶存水素ガス量を調整することでも所望の酸化還元電位を得ることができる。

【0030】

上記還元水処理方法については枚葉洗浄およびバッチ洗浄のどちらでもよい。処理時間は30sec以上が望ましく、特に60sec以上、180sec以下が望ましい。

【0031】

また、上記還元水による洗浄後は、純水などの水によって、還元水をリーンスする工程は必要ない。

そのため、本実施の形態の半導体装置100の製造方法において、還元水で洗浄する工

10

20

30

40

50

程後、Niを含むシリサイド層104が前記還元水で覆われてから、コンタクトホールにバリアメタルおよび金属膜を形成する工程までの間に、Niを含むシリサイド層104は水にさらされることはなくてもよい。

#### 【0032】

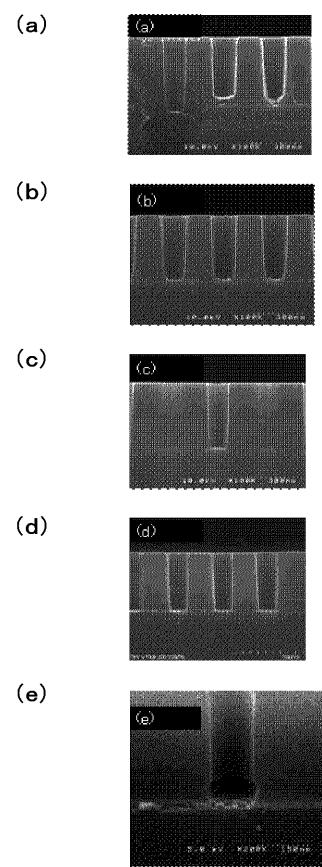

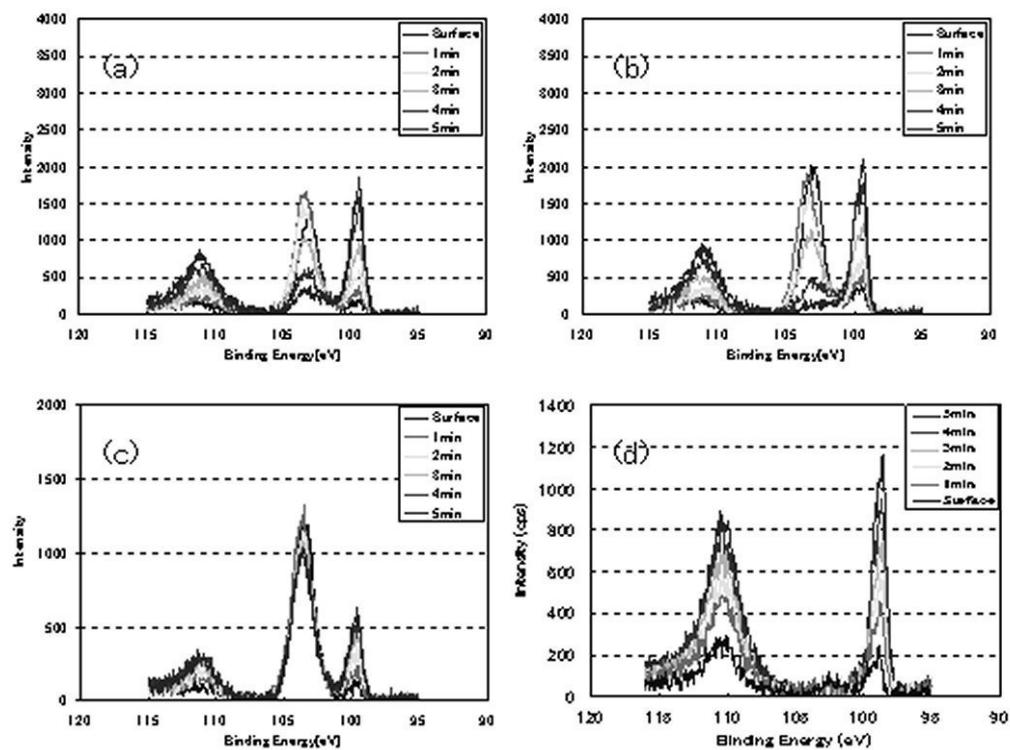

図4は、断面SEM画像を示す。この図4においては、ドライエッチング後(図4(a))、ドライエッチング後に従来洗浄したもの(アッシング図4(b)、硫酸過水洗浄図4(c)、DHF図4(e))およびドライエッチング後に本実施の形態の還元水処理した後(図4(d))の断面SEM画像を示す。さらに、図5は、1分から5分後のコンタクトホール底のXPSスペクトルを示す。この図5においては、ドライエッチング後(図5(a))、ドライエッチング後に従来洗浄したもの(アッシング図5(b)、硫酸過水洗浄図5(c))およびドライエッチング後に本実施の形態の還元水処理した後(図5(d))のXPSスペクトルを示す。

10

XPSスペクトルは、X線光電子分光法を用いて測定した。

還元水として、アンモニア濃度10ppm、pH9.5、酸化還元電位-600mVを用いた。また、本実施の形態の範囲の還元水を用いた場合にも、同様の結果が得られた。

#### 【0033】

アッシング(図4(b))や硫酸過水洗浄(図4(c))により、断面SEMからはデボ物が除去できているように見える。しかし、本実施の形態の還元水処理した後(図4(d))と比較すると、充分にコンタクトホール底のデボ物が除去されていないことが分かる。また、DHF処理(図4(e))は絶縁膜のエッチング、コンタクトホール底のエッチングが確認できる。

20

#### 【0034】

さらに、XPSスペクトルから、エッチング後(図5(a))、エッチング後に従来の洗浄をしたもの(アッシング図5(b)、硫酸過水洗浄図5(c))において、約103eVのピークが現れている。このピークは、SiO<sub>2</sub>を表していると考えられている。

#### 【0035】

これらと比較して、本実施の形態の還元水洗浄後においては、SiO<sub>2</sub>起因のピークもなく、コンタクトホール底にはNiSi膜が表面に形成されていることがわかる。

#### 【0036】

これは、上記還元水のORPがマイナスを示すことによる還元する働きにより、NiSi膜上の導通阻害物(SiO<sub>2</sub>)を還元させたためだと推測される。

30

また、上記還元水洗浄後、1分から5分後のコンタクトホール底のXPSスペクトルにおいても、SiO<sub>2</sub>起因のピークもないことが分かった。そのため、コンタクトホール底において、還元水処理後も継続してNiを含むシリサイド層104表面の酸化を防ぐことができる。

#### 【0037】

ここで、特許文献2の技術では、たとえばカソード水を用いた場合、水酸化アンモニウムの濃度が1~30質量%と高いため、その後水洗を必要とする。そのため、特許文献2では、シリサイドとしてはNiシリサイドの開示はないが、シリサイドがNiシリサイドの場合には、その水洗工程でもNiを含むシリサイド層の酸化を引き起こすという問題点がある。

40

#### 【0038】

しかし、本実施の形態の半導体装置100の製造方法は、上記還元水による処理後は純水によるリーン工程は必要ないため、Niを含むシリサイド層104を露出させる工程後、酸化性ガスを含んだガスによる処理を施すことなく、かつpH7である液体にさらすことなく、上記還元水で洗浄する工程と、を実施することができる。

また、上記還元水で洗浄する工程後、例えばSPM等のpH7の液体にさらすことなく、さらに乾燥処理を施す工程と、を実施することができる。

#### 【0039】

つづいて、半導体基板102を成膜チャンバに移動する。次いで、コンタクトホール内

50

に導電性の金属膜 116 を成膜する（図 3（c））。

【0040】

本実施の形態の半導体装置 100 の製造方法は、乾燥処理を施す工程後、さらにコンタクトホールにバリアメタルおよび金属膜 116 を形成する工程と、を実施することができる。

さらに、乾燥処理を施す工程後、酸化性ガスを含んだガスによる処理を施すことなく、かつ pH 7 である液体にさらすことなく、コンタクトホール（凹部）にバリアメタルおよび金属膜 116 を形成する工程と、を実施することができる。

金属膜 116 とバリアメタル層とは、積層構造とすることができます。

【0041】

金属膜 116 としては、たとえば Ti が好適に用いることができる。バリアメタルとしては、たとえば W、Ti、Ta、これらの窒化物または積層体が好適に用いることができる。

【0042】

以上、本発明の実施の形態について説明したが、もちろん本発明は、上記実施の形態に限定されるものではない。

たとえば、本発明の実施の形態の適用は、拡散層上のシリサイド層に限定されるものではなく、たとえばゲート電極上のシリサイド層でもよい

【0043】

また、Ni を含むシリサイド層は、自己整合的（シリサイド）に形成されてもよい。Ni シリサイドは、Ni を含有していれば、NiSi に限定されず、NiPtSi でもよく、それらの積層膜でもよい。

【0044】

また、これらの元素の化学量論的な組成比は任意であって、NiSi とは必ずしも Ni と Si の組成比が 1 : 1 に限定されるものではない。

【0045】

また、エッチング阻止膜 106 は、SiN 膜に限定されず、その上面に形成される絶縁膜 108 とエッチング選択比が得られる絶縁層であればよい。

【0046】

さらに、SiN 膜の下層に、シリサイド層と SiN 膜との間に、シリコン酸化膜の薄膜を形成してもよい。この場合、シリコン酸化膜の薄膜のエッチングが必要となり、その際に、上面の絶縁膜 108 のシリコン酸化膜もわずかにエッチングされるが、エッチング量はわずかのため問題はない。

【0047】

絶縁膜 108 は、シリコン酸化膜に限定されず、LOW-K 膜でもよい。LOW-K 膜としては、MSQ、SiOCH、HSQ、有機膜などが例示される。

【0048】

本発明の実施の形態は、Ni を含むシリサイド層が露出したコンタクトホールの洗浄において、還元水を用いるため、デポ物を充分除去することを可能とし、かつシリサイド層表面を酸化することが無いため、コンタクト抵抗を良好に保つことができる。

【0049】

また、本発明の実施の形態の還元水による洗浄では、酸化性ガスによる処理や酸化性の液体による処理を施す必要が無く、さらに還元水処理後の水洗も不要であるため、シリサイド層表面の酸化を防ぐことができ、コンタクト抵抗を良好に保つことができる。

【0050】

さらに、フッ酸処理や RF エッチングなど Ni を含むシリサイド層表面をエッチングする処理も行わないため、シリサイド層が薄膜化しても、コンタクト抵抗を良好に保ち、リークの発生も抑制できる。

【0051】

さらに、還元水洗浄によって、Ni シリサイドの表面を H 基で終端することができ、酸

10

20

30

40

50

化をさらに防ぐことができる。

【0052】

なお、当然ながら、上述した実施の形態および複数の変形例は、その内容が相反しない範囲で組み合わせることができる。また、上述した実施の形態および変形例では、各部の構造などを具体的に説明したが、その構造などは本願発明を満足する範囲で各種に変更することができる。

【符号の説明】

【0053】

|     |             |

|-----|-------------|

| 100 | 半導体装置       |

| 102 | 半導体基板       |

| 104 | Niを含むシリサイド層 |

| 106 | エッティング阻止膜   |

| 108 | 絶縁膜         |

| 110 | レジスト層       |

| 112 | デポ物         |

| 114 | 還元水         |

| 116 | 金属膜         |

10

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 菊池 敦志

山形県鶴岡市宝田一丁目11番73号 N E C セミコンダクタ - ズ山形株式会社内

F ター ム(参考) 4M104 BB14 BB17 BB18 BB21 BB30 BB32 BB33 DD08 DD16 DD17

DD22 FF22 HH15

5F033 JJ18 JJ19 JJ21 JJ32 JJ33 JJ34 KK01 KK25 NN06 NN07

PP15 QQ08 QQ11 QQ20 QQ25 QQ37 QQ70 QQ73 QQ92 RR01

RR04 RR06 RR09 RR25 WW00 WW04 XX09