(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-536599

(P2016-536599A)

(43) 公表日 平成28年11月24日(2016.11.24)

|                             |            |             |

|-----------------------------|------------|-------------|

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

| <b>G01N 27/00</b> (2006.01) | G01N 27/00 | Z 2 G 06 0  |

| <b>B82Y 40/00</b> (2011.01) | B82Y 40/00 | 4 B 02 9    |

| <b>B82Y 15/00</b> (2011.01) | B82Y 15/00 | 4 M 10 4    |

| <b>B82Y 5/00</b> (2011.01)  | B82Y 5/00  |             |

| <b>C12M 1/00</b> (2006.01)  | C12M 1/00  | A           |

審査請求 未請求 予備審査請求 未請求 (全 52 頁) 最終頁に続く

|               |                              |          |                                                                          |

|---------------|------------------------------|----------|--------------------------------------------------------------------------|

| (21) 出願番号     | 特願2016-537398 (P2016-537398) | (71) 出願人 | 513217540<br>クオンタムバイオシステムズ株式会社<br>東京都中央区日本橋本町二丁目3番11号                    |

| (86) (22) 出願日 | 平成26年8月26日 (2014.8.26)       | (72) 発明者 | 池田 修二<br>大阪市淀川区西中島7-14-35 大阪<br>屋北5号館601号室                               |

| (85) 翻訳文提出日   | 平成28年4月26日 (2016.4.26)       | (72) 発明者 | マーク オールダム<br>アメリカ合衆国 94062 カリフォル<br>ニア州 エメラルド ヒルズ グレンミア<br>ウエイ 738       |

| (86) 國際出願番号   | PCT/IB2014/002143            | (72) 発明者 | エリック ノードマン<br>アメリカ合衆国 94301-4022<br>カリフォルニア州 パロアルト ミドルフ<br>ィールド ロード 2150 |

| (87) 國際公開番号   | W02015/028886                |          |                                                                          |

| (87) 國際公開日    | 平成27年3月5日 (2015.3.5)         |          |                                                                          |

| (31) 優先権主張番号  | 特願2013-176132 (P2013-176132) |          |                                                                          |

| (32) 優先日      | 平成25年8月27日 (2013.8.27)       |          |                                                                          |

| (33) 優先権主張国   | 日本国 (JP)                     |          |                                                                          |

| (31) 優先権主張番号  | 特願2013-177051 (P2013-177051) |          |                                                                          |

| (32) 優先日      | 平成25年8月28日 (2013.8.28)       |          |                                                                          |

| (33) 優先権主張国   | 日本国 (JP)                     |          |                                                                          |

最終頁に続く

(54) 【発明の名称】ナノギャップ電極およびその製造方法

## (57) 【要約】

本開示は、ナノギャップ電極を形成するための方法を提供する。場合によっては、サイドウォールの膜厚によって調整された幅を有するナノギャップは、マスクとして第1電極形成部に接触したサイドウォールを用いて第1電極形成部と第2電極形成部との間に形成されてもよい。第1電極形成部、サイドウォール、および第2電極形成部の表面が露出される。その後、サイドウォールは取り外され、第1電極形成部と第2電極形成部の間にナノギャップを形成する。

## 【特許請求の範囲】

## 【請求項 1】

(a) 基板に隣接する第1電極形成部と、前記第1電極形成部に隣接するサイドウォールと、前記サイドウォールに隣接する第2電極形成部とを設けることと、

(b) 前記サイドウォールを除去することにより、前記第1電極形成部および前記第2電極形成部間にナノギャップを形成することと、

(c) 前記第1電極形成部および前記第2電極形成部間に標的種が配置される時ナノギャップを横切る電流を検出する電極として使用するために前記第1電極形成部および前記第2電極形成部を用意することと、

を備える、少なくとも1つのナノギャップを有するセンサを製造する方法。

10

## 【請求項 2】

前記電極として使用するために前記第1電極形成部および前記第2電極形成部を用意することは、前記電極を設けるため前記第1電極形成部および前記第2電極形成部の少なくとも一部を除去することを含む、請求項1に記載の方法。

## 【請求項 3】

前記第1電極形成部および/または前記第2電極形成部は、金属ナイトライドから形成される、請求項1に記載の方法。

## 【請求項 4】

前記第1電極形成部および/または前記第2電極形成部は、チタンナイトライドから形成される、請求項3に記載の方法。

20

## 【請求項 5】

前記基板は、半導体層に隣接する酸化半導体層を含む、請求項1に記載の方法。

## 【請求項 6】

前記半導体は、シリコンである、請求項5に記載の方法。

## 【請求項 7】

前記サイドウォールは、略2ナノメータ以下の幅を有する、請求項1に記載の方法。

## 【請求項 8】

前記幅は、略1ナノメータ以下である、請求項7に記載の方法。

## 【請求項 9】

前記幅は、略0.5ナノメータより大きい、請求項8に記載の方法。

30

## 【請求項 10】

前記標的種は、核酸分子であり、前記サイドウォールは、前記核酸分子の直径より小さい幅を有する、請求項1に記載の方法。

## 【請求項 11】

(c) の前に、前記第1電極形成部の表面と、前記サイドウォールの表面と、前記第2電極形成部の表面とを露出することをさらに含む、請求項1に記載の方法。

## 【請求項 12】

(b) の前に、前記第1電極形成部と前記第2電極形成部の間で前記サイドウォールの断面が四辺状であるように、前記サイドウォールの一部を除去することをさらに含む、請求項1に記載の方法。

40

## 【請求項 13】

前記ナノギャップと交差するチャネルを形成することをさらに含む、請求項1に記載の方法。

## 【請求項 14】

前記チャネルは、覆われたチャネルである、請求項13に記載の方法。

## 【請求項 15】

(a) 基板に隣接する電極形成部に第1幅を有する間隙を介して互いに対向する側壁を有するギャップ形成マスクを配置することと、

(b) 前記ギャップ形成マスクの前記側壁に、前記電極形成部が間に露出されるサイドウォールを形成することと、

50

(c) 前記サイドウォールの間に前記第1幅より小さい第2幅を有するナノギャップを形成するため、前記サイドウォールの間に露出される前記電極形成部の一部を除去することと、

(d) 前記ナノギャップにより分離される電極形成部の部分を露出するため前記サイドウォールを除去することと、

(e) 電極形成部間に標的種が配置される時前記ナノギャップを横切る電流を検出する電極として使用するための前記電極形成部の部分を用意することと、

を備える、少なくとも1つのナノギャップを有するセンサを形成する方法。

#### 【請求項16】

前記電極として使用するために前記電極形成部の部分を用意することは、前記電極を設けるため前記電極形成部の部分を除去することを含む、請求項15に記載の方法。 10

#### 【請求項17】

前記基板は、半導体層に隣接する酸化半導体層を含む、請求項15に記載の方法。

#### 【請求項18】

前記半導体は、シリコンである、請求項17に記載の方法。

#### 【請求項19】

前記第2幅は、略2ナノメータ以下の幅である、請求項15に記載の方法。

#### 【請求項20】

前記第2幅は、略1ナノメータ以下の幅である、請求項19に記載の方法。 20

#### 【請求項21】

前記第2幅は、略0.5ナノメータより大きいこと、請求項20に記載の方法。

#### 【請求項22】

前記標的種は、核酸分子であり、前記第2幅は、前記核酸分子の直径より小さい、請求項15に記載の方法。

#### 【請求項23】

前記ギャップ形成マスクと前記サイドウォールは、異なる材料で形成される、請求項15に記載の方法。

#### 【請求項24】

前記ナノギャップと交差するチャネルを形成することをさらに含む、請求項15に記載の方法。 30

#### 【請求項25】

前記チャネルは、覆われたチャネルである、請求項24に記載の方法。

#### 【請求項26】

(a) 基板に隣接する電極形成部に隣接して配置されたサイドウォールを含むマスクを設けることと、

(b) 前記電極形成部の一部を露出させる間隙を前記マスクに形成するため前記サイドウォールを除去することと、

(c) ナノギャップを形成するため前記電極形成部の前記一部を除去することと、

(d) 前記ナノギャップにより分離される前記電極形成部の部分を露出するために前記マスクを除去することと、 40

(e) 前記電極形成部間に標的種が配置される時前記ナノギャップを横切る電流を検出する電極として使用するために前記電極形成部の前記部分を用意することと、

を備える、少なくとも1つのナノギャップを有するセンサを形成する方法。

#### 【請求項27】

前記電極として使用するために前記電極形成部の部分を用意することは、前記電極を設けるため前記電極形成部の部分を除去することを含む、請求項26に記載の方法。

#### 【請求項28】

前記(a)は、(i)前記電極形成部に隣接して配置された第1マスクの側壁に前記サイドウォールを設けることと、(ii)前記第1マスクを除去することと、(iii)前記サイドウォールに隣接した第2マスクを形成することとを含み、前記マスクは少なくと 50

も前記第2マスクの一部を含む、請求項26に記載の方法。

【請求項29】

前記第1マスクを除去することは、前記電極形成部を露出することを含む、請求項28に記載の方法。

【請求項30】

前記第2マスクは、前記サイドウォールを覆う、請求項28に記載の方法。

【請求項31】

前記第1マスクを除去した後に、前記サイドウォールは、略2ナノメータ以下の幅を有する独立したサイドウォールである、請求項28に記載の方法。

【請求項32】

前記(a)は、(i)前記電極形成部に隣接して配置された第1マスクの側壁に前記サイドウォールを設けることと、(ii)前記サイドウォールに隣接して第2マスクを形成することと、(iii)前記第2マスクをエッチングすることとを含み、前記マスクは少なくとも前記第1マスクと前記第2マスクの一部を含む、請求項26に記載の方法。

10

【請求項33】

前記サイドウォールに隣接した前記第2マスクを形成することは、前記第1マスクと前記サイドウォールを覆う前記第2マスクを含む、請求項32に記載の方法。

【請求項34】

前記第2マスクをエッチングすることは、前記第1マスクおよび/または前記サイドウォールをエッチングすることを含む、請求項32に記載の方法。

20

【請求項35】

前記ナノギャップと交差するチャネルを形成することをさらに含む、請求項26に記載の方法。

【請求項36】

前記チャネルは、覆われたチャネルである、請求項35に記載の方法。

【請求項37】

前記基板は、半導体層に隣接する酸化半導体層を含む、請求項26に記載の方法。

【請求項38】

前記半導体は、シリコンである、請求項37に記載の方法。

30

【請求項39】

前記(a)は、サイドウォール形成層を設けることと、前記サイドウォールを形成するため前記サイドウォール形成層をエッチングすることとをさらに含む、請求項26に記載の方法。

【請求項40】

前記ナノギャップは、略2ナノメータ以下の幅を有する、請求項26に記載の方法。

【請求項41】

前記幅は、略1ナノメータ以下である、請求項40に記載の方法。

【請求項42】

前記幅は、略0.5ナノメータより大きい、請求項41に記載の方法。

40

【請求項43】

前記標的種は、核酸分子であり、前記サイドウォールは、前記核酸分子の直径より小さい、請求項26に記載の方法。

【請求項44】

前記ナノギャップと交差するチャネルを形成することをさらに含む、請求項26に記載の方法。

【請求項45】

前記チャネルは、覆われたチャネルである、請求項44に記載の方法。

【請求項46】

(a)基板に隣接し第2材料を有する電極形成部に、第1材料を有するフィルムを設けることと、

50

(b) 前記第1材料と前記第2材料を反応させるため前記フィルムを熱することにより、体積膨張して互いに対向し、いずれもサイドウォールを有する2つの電極部を形成することと、

(c) 体積膨張により互いの方へ前記電極部のサイドウォールを近づけることにより、前記電極部の間にナノギャップを形成することと、

(d) 前記電極部間に標的種が配置される時前記ナノギャップを横切る電流を検出する電極として使用するために前記電極を用意することと、

を備える、ナノギャップ電極センサを製造する方法。

**【請求項47】**

前記電極として使用するための前記電極部を用意することは、前記電極を設けるため前記電極部の少なくとも一部を除去することを含む、請求項46に記載の方法。

10

**【請求項48】**

前記(a)は、(i)前記電極形成部の幅に合わせて選択されたマスクを形成し、(ii)前記電極形成部に前記フィルムを形成する、請求項46に記載の方法。

**【請求項49】**

2つの電極部を形成する際、前記2つの電極部が前記反応から生ずる体積膨張により前記マスクを浸食することにより、前記電極部のサイドウォールを互いの方へ近づける、請求項48に記載の方法。

20

**【請求項50】**

前記マスクと、前記マスクの下部領域に残存している前記電極部の未反応部分とを除去することにより、前記電極部の間にナノギャップを形成することをさらに含む、請求項49に記載の方法。

**【請求項51】**

前記ナノギャップと交差するチャネルを形成することをさらに含む、請求項46に記載の方法。

**【請求項52】**

前記チャネルは、覆われたチャネルである、請求項51に記載の方法。

**【請求項53】**

(a) 基板に隣接し、第1幅を有する間隙を介して互いに対向して配置された2つの電極形成部を設けることと、

30

(b) 前記電極形成部に化合物生成層を成膜することと、

(c) 前記化合物生成層と少なくとも1つの前記電極形成部の間の反応を促進するため熱処理を行い、その反応により体積膨張された少なくとも1つの電極部を形成することにより、前記電極形成部のサイドウォールを体積膨張により互いに近づけて前記第1幅より小さい第2幅を有するナノギャップを形成することと、

(d) 前記電極形成部間に標的種が配置される時前記ナノギャップを横切る電流を検出する電極として使用するために前記電極形成部を用意することと、

を備える、少なくとも1つのナノギャップ電極を有するセンサを製造する方法。

**【請求項54】**

前記電極として使用するための前記電極部を用意することは、前記電極を設けるため前記電極部の部分を除去することを含む、請求項53に記載の方法。

40

**【請求項55】**

前記化合物生成層は、シリサイド生成層であり、前記(c)は、前記反応の間に前記電極形成部のシリサイド化を含み、前記電極形成部は、前記シリサイド化の間に体積膨張する、請求項53に記載の方法。

**【請求項56】**

前記第2幅は、略2ナノメータ以下の幅を有する、請求項53に記載の方法。

**【請求項57】**

前記第2幅は、略1ナノメータ以下である、請求項56に記載の方法。

**【請求項58】**

50

前記第2幅は、略0.5ナノメータより大きい、請求項57に記載の方法。

【請求項59】

前記標的種は、核酸分子であり、前記第2幅は、前記核酸分子の直径より小さい、請求項53に記載の方法。

【請求項60】

前記(c)は、前記化合物生成層と両方の前記電極形成部の間での前記反応を含む、請求項53に記載の方法。

【請求項61】

前記(c)は、前記化合物生成層と前記電極形成部の1つのみの間での前記反応を含む、請求項53に記載の方法。

【請求項62】

前記ナノギャップと交差するチャネルを形成することをさらに含む、請求項53に記載の方法。

【請求項63】

前記チャネルは、覆われたチャネルである、請求項62に記載の方法。

【請求項64】

基板にナノギャップを挟んで対向して配置された少なくとも2つの電極部を備えるナノギャップ電極センサであって、前記電極部の対向するサイドウォールは、互いが徐々に近づき、前記サイドウォール間の幅は徐々に狭くなり、前記電極は、標的種が前記電極の間に配置される時前記ナノギャップを横切る電流を検出するように適合された、ナノギャップ電極センサ。

【請求項65】

前記電極部は、金属シリサイドから形成される、請求項64に記載のナノギャップ電極センサ。

【請求項66】

前記ナノギャップは、前記ナノギャップが前記基板に近づくにつれ、前記電極部の前記サイドウォール間の距離が徐々に拡がるような後方に曲った形状に形成される、請求項64または65に記載のナノギャップ電極センサ。

【請求項67】

前記サイドウォールは、前記基板と接して外側に膨張した部分を含む、請求項64または65に記載のナノギャップ電極センサ。

【請求項68】

前記ナノギャップと交差し流体連結されているチャネルをさらに備える、請求項64に記載のナノギャップ電極センサ。

【請求項69】

前記チャネルは、覆われたチャネルである、請求項68に記載のナノギャップ電極センサ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ナノギャップ電極およびその製造方法に関し、参照することにより本願に組み込まれる2013年8月27日に出願された日本特許出願2013-176132および2013年8月28日に出願された日本特許出願2013-177051に対して、優先権を主張する。

【背景技術】

【0002】

近年、対向した電極部間にナノスケールの間隙が形成された電極構造(以下、ナノギャップ電極と呼ぶ)が注目されており、ナノギャップ電極を用いた電子デバイスや、バイオデバイス等について研究が盛んに行われている。例えば、バイオデバイスの分野では、ナノギャップ電極を利用し、DNAの塩基配列を解析する分析装置が考えられている(例え

10

20

30

40

50

ば、特許文献 1 参照)。

【0003】

実際上、この分析装置では、ナノギャップ電極の電極部間にあるナノスケールでなる中空状の間隙(以下、ナノギャップと呼ぶ)に一本鎖DNAを通過させ、当該一本鎖DNAの塩基が電極部間のナノギャップを通過したときに電極部に流れる電流を計測してゆき、その電流値を基に一本鎖DNAを構成する塩基を同定し得るようになされている。

【0004】

ところで、このような分析装置では、ナノギャップ電極の電極部間の距離が大きくなると検出できる電流値が小さくなってしまい、高感度で試料を分析することが困難になるため、電極部間のナノギャップを小さく形成し得ることが望まれている。

10

【0005】

従来、このようなナノギャップ電極の製造方法としては、金等でなる電極層上に形成されたチタン等の金属マスクを集束イオンビームの照射によりパターニングし、このパターニングされた金属マスクから露出した下層の電極層をドライエッチングし、電極層にナノギャップを形成してナノギャップ電極を製造する方法が知られている(例えば、特許文献 2 参照)。

【0006】

しかしながら、このようなナノギャップ電極の製造手法では、パターニングされた金属マスクにより覆われていない露出した電極層部分を、ドライエッチングして電極層にナノギャップとなる間隙を形成していることから、電極層に形成される間隙(マスク幅間隙)の最小幅が、金属マスクをパターニングできる幅となり、それよりもさらに小さなナノギャップを形成し難いという問題があった。そして、近年では、使用態様に応じて従来と同じ寸法の幅のナノギャップを形成し得る他、従来よりも一段と幅が小さいナノギャップをも形成し得る新たな製造方法の開発が望まれている。

20

【0007】

そこで、本発明は以上の点を考慮してなされたもので、従来と同じ寸法の幅のナノギャップを形成し得る他、従来よりも一段と幅が小さいナノギャップをも形成し得るナノギャップ電極の製造方法を提案することを目的とする。

30

【0008】

本発明は、ナノギャップ電極およびナノギャップ電極の製造方法に関する。

【0009】

集束イオンビーム、電子ビーム、ナノインプリント技術が、幅と深さが 20 ナノメートル( nm )の、可能性としては 10 ナノメートルのナノチャネルを生成するのに有用であると言われている。チャネル幅が一本鎖DNAの旋回半径より小さいシステムは知られているが、一本鎖DNAの断面回転半径より小さくなるような十分に狭い幅を備えたシステムや方法については知られていない。

40

【0010】

二次構造が生体分子の異なる部分を形成することを妨げる可能性があるが、高い割合の生体分子についての問い合わせを可能し、サンプル生体分子からナノギャップへアクセスを可能にするように十分に小さな寸法を持つナノチャネルに対する需要は存在する。

【0011】

しかし、上述のようにナノギャップ電極を製造する方法においては、パターン形成されたメタルマスクで覆われていない露出した電極層は、電極層中にナノギャップとなる溝を形成するためにドライエッチングされるかもしれない。このため、電極層に形成されたギャップ(マスクのギャップの幅に相当)の最小幅は、金属マスクをパターン形成することができる最小幅である。したがって、この方法では、金属マスクに形成することができる最小フィーチャーの幅よりも小さいナノギャップを形成することが困難であるという問題点を有している。

【発明の概要】

【0012】

50

本開示は、ナノギャップ電極用の装置、システムおよび方法およびナノチャネルシステムを提供する。本明細書に提供される方法は、現在利用可能な他の方法を用いて形成される間隙よりも小さいナノギャップを有するナノギャップ電極を形成することができる。

#### 【0013】

いくつかの実施形態では、ナノギャップ電極を製造する方法は、電極形成部に配置されたマスクとしてのサイドウォールを使用し、電極形成部分のサイドウォールの膜厚によって調整された幅を有するナノギャップを形成するステップを含む。

#### 【0014】

他の実施形態では、ナノギャップ電極を製造する方法は、基板上に形成された第1電極形成部の側壁にサイドウォールを形成し、その後サイドウォールに当接して第2電極形成部を形成する工程を含み、それにより、第1電極形成部と第2電極形成部の間にサイドウォールを配置し、第1電極形成部分、サイドウォールおよび第2電極形成部分の表面に露出してサイドウォールを除去することにより第1電極形成部と第2電極形成部間にナノギャップを形成する。

10

#### 【0015】

別の実施形態では、ナノギャップ電極を製造する方法は、電極形成部に間隙を挟んで互いに対向する側壁を有するギャップ形成マスクを設け、このギャップ形成マスクの側壁にサイドウォールを形成し、側壁間電極形成部分を露出する工程と、側壁の間に露出した電極形成部分を除去しそれらのナノギャップを形成する工程を含む。

20

#### 【0016】

さらなる態様において、ナノギャップ電極を製造する方法は、間隙の電極形成部分を露出するためギャップ形成マスクの間隙を形成するギャップ形成マスクの側壁を除去する工程と、間隙内にナノギャップを形成するための間隙の外に露出した電極形成部分を除去する工程を含む。

30

#### 【0017】

他の実施形態では、ナノギャップ電極を製造する方法は、電極形成部に配置されたサイドウォール形成マスクの側壁にサイドウォールを形成し、その後、垂直方向の側壁にサイドウォール形成マスクを除去する工程と、側壁部を取り囲むように間隙を形成するマスクを形成する工程と、側壁がギャップ形成マスクで間隙を形成するために除去し、間隙の電極形成部分を露出する工程と、間隙から露出した電極形成部分を除去し、間隙内にナノギャップを形成する工程を含む。

#### 【0018】

別の実施形態では、ナノギャップ電極を製造する方法は、側壁に接するように電極形成部に配置された第1のギャップ形成マスクの側壁にサイドウォールを形成させてから、2番目のギャップ形成マスクを形成し、これにより側壁を第1ギャップ形成マスク及び第2ギャップ形成マスクとの間に、第1ギャップ成用マスクの側壁、側壁および第2ギャップ形成マスクの表面を露出して側壁を除去して、第1ギャップ形成マスクと第2ギャップ形成用マスクとの間に間隙を形成することにより、間隙内の電極形成部分を除去し間隙内にナノギャップを形成する工程を含む。

40

#### 【0019】

本発明によれば、サイドウォールの膜厚によって調整された幅を有するナノギャップを形成することができるため、従来のナノギャップと同じ幅のナノギャップだけでなくさらに小さいナノギャップを形成することができる。

#### 【0020】

本発明の一態様によれば、ナノギャップ電極を製造する方法は、対向する電極形成部に化合物形成層を成膜してから熱処理を行う工程と、電極形成部分を化合物形成層と反応させる工程と、反応により2つの体積膨張対向電極を形成する工程と、体積膨張により互いに電極を接近させて電極間にナノギャップを形成する工程を含む。

#### 【0021】

本発明の他の態様によれば、ナノギャップ電極を製造する方法は、基板上に設けられた

50

一対の対向した電極形成部の所定の幅に適合するように選択されたマスクを形成する工程と、電極形成部に化合物形成層の膜を形成する工程と、電極形成部と化合物形成層を反応させて互いに対向する2つの電極を形成するために熱処理を行い、反応に起因する体積膨張によってマスク下を貫通することにより、体積膨張によりマスクの幅より電極のサイドウォールを互いに接近させる工程と、マスクとマスク下にあった領域のゲート電極形成部分の未反応部分を除去し電極間のナノギャップを形成する工程と、を含む。

#### 【0022】

本発明の他の態様によれば、ナノギャップ電極を製造する方法は、基板上で間隙を挟んで互いに対向して配置された2つの電極形成部を形成する工程と、電極形成部に化合物生成層を成膜する工程と、化合物生成層を電極形成部と反応を引き起こす熱処理を行い、2つの電極をその反応による体積膨張で互いに対向するように形成することにより、体積膨張で電極部を互いに接近させて間隙より小さいナノギャップを形成する工程とを含む。

10

#### 【0023】

他の実施形態では、電極間の間隙は、電極の体積膨張量と同程度まで小さくできる。したがって、標準的なリソグラフプロセスにより形成された間隙より小さいナノギャップを有するナノギャップ電極を設けることができ、ナノギャップ電極を製造する方法を提供できる。

#### 【0024】

他の実施形態では、ナノギャップ電極構造の形成について有用なものとして明細書内で記載した方法は、e ビーム(電子ビーム)、イオンビームミーリング、ナノインプリントリソグラフィなどの従来の半導体プロセスを使って形成されるものより小さいナノチャネルを形成することに利用することができる。

20

#### 【0025】

本発明の一態様によれば、少なくとも1つのナノギャップを有するセンサを製造する方法は、(a)基板に隣接する第1電極形成部と、前記第1電極形成部に隣接するサイドウォールと、前記サイドウォールに隣接する第2電極形成部とを設ける工程と、(b)前記サイドウォールを除去することにより、前記第1電極形成部および前記第2電極形成部間にナノギャップを形成する工程と、(c)前記第1電極形成部および前記第2電極形成部間に標的種が配置される時ナノギャップを横切る電流を検出する電極として使用するために前記第1電極形成部および前記第2電極形成部を用意する工程と、を備える。ある実施形態では、その電流は、トンネル電流である。

30

#### 【0026】

ある実施形態では、前記電極として使用するために前記第1電極形成部および前記第2電極形成部を用意することは、前記電極を設けるため前記第1電極形成部および前記第2電極形成部の少なくとも一部を除去することを含む。別の実施形態では、前記第1電極形成部および/または前記第2電極形成部は、金属ナイトライドから形成される。別の実施形態では、前記第1電極形成部および/または前記第2電極形成部は、チタンナイトライドから形成される。ある実施形態では、前記基板は、半導体層に隣接する酸化半導体層を含む。別の実施形態では、前記半導体は、シリコンである。

40

#### 【0027】

ある実施形態では、前記サイドウォールは、略2ナノメータ以下の幅を有する。別の実施形態では、前記幅は、略1ナノメータ以下である。別の実施形態では、前記幅は、略0.5ナノメータより大きい。

#### 【0028】

ある実施形態では、(c)の前に、前記第1電極形成部の表面と、前記サイドウォールの表面と、前記第2電極形成部の表面とを露出する工程をさらに含む。

#### 【0029】

ある実施形態では、(b)の前に、前記第1電極形成部と前記第2電極形成部の間前記サイドウォールの断面が四辺状であるように、前記サイドウォールの一部を除去する工程をさらに含む。

50

**【0030】**

ある実施形態では、前記ナノギャップと交差するチャネルを形成する工程をさらに含む。別の実施形態では、前記チャネルは、覆われたチャネルである。

**【0031】**

本発明の一態様によれば、少なくとも1つのナノギャップを有するセンサを形成する方法は、(a)基板に隣接する電極形成部に第1幅を有する間隙を介して互いに対向する側壁を有するギャップ形成マスクを配置する工程と、(b)前記ギャップ形成マスクの前記側壁に、前記電極形成部が間に露出されるサイドウォールを形成する工程と、(c)前記サイドウォールの間に前記第1幅より小さい第2幅を有するナノギャップを形成するため、前記サイドウォールの間に露出される前記電極形成部の一部を除去する工程と、(d)前記ナノギャップにより分離される電極形成部の部分を露出するため前記サイドウォールを除去する工程と、(e)電極形成部間に標的種が配置される時前記ナノギャップを横切る電流を検出する電極として使用するための前記電極形成部の部分を用意する工程と、を備える。ある実施形態では、前記電流は、トンネル電流である。

10

**【0032】**

ある実施形態では、前記電極として使用するために前記電極形成部の部分を用意することは、前記電極を設けるため前記電極形成部の部分を除去することを含む。別の実施形態では、前記基板は、半導体層に隣接する酸化半導体層を含む。別の実施形態では、前記半導体は、シリコンである。

20

**【0033】**

ある実施形態では、前記第2幅は、略2ナノメータ以下の幅である。別の実施形態では、前記第2幅は、略1ナノメータ以下の幅である。別の実施形態では、前記第2幅は、略0.5ナノメータより大きい。

**【0034】**

ある実施形態では、前記標的種は、核酸分子であり、前記第2幅は、前記核酸分子の直径より小さい。

**【0035】**

ある実施形態では、前記ナノギャップと交差するチャネルを形成する工程をさらに含む。別の実施形態では、前記チャネルは、覆われたチャネルである。

30

**【0036】**

本発明の一態様によれば、少なくとも1つのナノギャップを有するセンサを形成する方法は、(a)基板に隣接する電極形成部に隣接して配置されたサイドウォールを含むマスクを設ける工程と、(b)前記電極形成部の一部を露出させる間隙を前記マスクに形成するため前記サイドウォールを除去する工程と、(c)ナノギャップを形成するため前記電極形成部の前記一部を除去する工程と、(d)前記ナノギャップにより分離される前記電極形成部の部分を露出するために前記マスクを除去する工程と、(e)前記電極形成部間に標的種が配置される時前記ナノギャップを横切る電流を検出する電極として使用するために前記電極形成部の前記部分を用意する工程と、を備える。別の実施形態では、前記電流は、トンネル電流である。別の実施形態では、前記標的種は、核酸分子であり、前記サイドウォールは、前記核酸分子の直径より小さい。

40

**【0037】**

ある実施形態では、前記電極として使用するために前記電極形成部の部分を用意することは、前記電極を設けるため前記電極形成部の部分を除去することを含む。

**【0038】**

ある実施形態では、前記(a)の工程は、(i)前記電極形成部に隣接して配置された第1マスクの側壁に前記サイドウォールを設ける工程と、(ii)前記第1マスクを除去する工程と、(iii)前記サイドウォールに隣接した第2マスクを形成する工程とを含み、前記マスクは少なくとも前記第2マスクの一部を含む。別の実施形態では、前記第1マスクを除去することは、前記電極形成部を露出することを含む。別の実施形態では、前記第2マスクは、前記サイドウォールを覆う。別の実施形態では、前記第1マスクを除去

50

した後に、前記サイドウォールは、略10ナノメータ、5ナノメータ、4ナノメータ、3ナノメータ、2ナノメータ、1ナノメータ、0.9ナノメータ、0.8ナノメータ、0.7ナノメータ、0.6ナノメータまたは0.5ナノメータ以下の幅を有する独立した(フリースタンディングの)サイドウォールである。

【0039】

ある実施形態では、前記(a)の工程は、(i)前記電極形成部に隣接して配置された第1マスクの側壁に前記サイドウォールを設ける工程と、(ii)前記サイドウォールに隣接して第2マスクを形成する工程と、(iii)前記第2マスクをエッティングする工程とを含み、前記マスクは少なくとも前記第1マスクと前記第2マスクの一部を含む。別の実施形態では、前記サイドウォールに隣接した前記第2マスクを形成することは、前記第1マスクと前記サイドウォールを覆う前記第2マスクを含む。別の実施形態では、前記第2マスクをエッティングすることは、前記第1マスクおよび/または前記サイドウォールをエッティングすることを含む。

10

【0040】

ある実施形態では、前記ナノギャップと交差するチャネルを形成する工程をさらに含む。別の実施形態では、前記チャネルは、覆われたチャネルである。

【0041】

ある実施形態では、前記基板は、半導体層に隣接する酸化半導体層を含む。別の実施形態では、前記半導体は、シリコンである。

20

【0042】

ある実施形態では、前記(a)の工程は、サイドウォール形成層を設ける工程と前記サイドウォールを形成するため前記サイドウォール形成層をエッティングする工程をさらに含む。

【0043】

ある実施形態では、前記ナノギャップは、略2ナノメータ以下の幅を有する。別の実施形態では、前記幅は、略1ナノメータ以下である。別の実施形態では、前記幅は、略0.5ナノメータより大きい。

【0044】

ある実施形態では、前記ナノギャップと交差するチャネルを形成する工程をさらに含む。別の実施形態では、前記チャネルは、覆われたチャネルである。

30

【0045】

本発明の一態様によれば、ナノギャップ電極センサを製造する方法は、(a)基板に隣接し第2材料を有する電極形成部に、第1材料を有するフィルムを設ける工程と、(b)前記第1材料と前記第2材料を反応させるため前記フィルムを熱することにより、体積膨張して互いに対向し、いずれもサイドウォールを有する2つの電極部を形成する工程と、(c)体積膨張により互いの方へ前記電極部のサイドウォールを近づけることにより、前記電極部の間にナノギャップを形成する工程と、(d)前記電極部間に標的種が配置される時前記ナノギャップを横切る電流を検出する電極として使用するために前記電極を用意する工程と、を備える。別の実施形態では、前記電流は、トンネル電流である。

40

【0046】

ある実施形態では、前記電極として使用するための前記電極部を用意することは、前記電極を設けるため前記電極部の少なくとも一部を除去することを含む。別の実施形態では、前記(a)の工程は、(i)前記電極形成部の幅に合わせて選択されたマスクを形成し、(ii)前記電極形成部に前記フィルムを形成する。別の実施形態では、2つの電極部を形成する際、前記2つの電極部が前記反応から生ずる体積膨張により前記マスクを浸食することにより、前記電極部のサイドウォールを互いの方へ近づける。別の実施形態では、前記マスクと、前記マスクの下部領域に残存している前記電極部の未反応部分とを除去することにより、前記電極部の間にナノギャップを形成することをさらに含む。

【0047】

ある実施形態では、前記方法は、前記ナノギャップと交差するチャネルを形成する工程

50

をさらに含む。別の実施形態では、前記チャネルは、覆われたチャネルである。

【0048】

本発明の一態様によれば、少なくとも1つのナノギャップ電極を有するセンサを製造する方法は、(a)基板に隣接し、第1幅を有する間隙を介して互いに対向して配置された2つの電極形成部を設ける工程と、(b)前記電極形成部に化合物生成層を成膜する工程と、(c)前記化合物生成層と少なくとも1つの前記電極形成部の間の反応を促進するため熱処理を行い、その反応により体積膨張された少なくとも1つの電極部を形成することにより、前記電極形成部のサイドウォールを体積膨張により互いに近づけて前記第1幅より小さい第2幅を有するナノギャップを形成する工程と、(d)前記電極形成部間に標的種が配置される時前記ナノギャップを横切る電流を検出する電極として使用するために前記電極形成部を用意する工程と、を備える。別の実施形態では、前記電流は、トンネル電流である。

10

【0049】

ある実施形態では、前記電極として使用するための前記電極部を用意することは、前記電極を設けるため前記電極部の部分を除去することを含む。別の実施形態では、前記化合物生成層は、シリサイド生成層であり、前記(c)の工程は、前記反応の間に前記電極形成部のシリサイド化を含み、前記電極形成部は、前記シリサイド化の間に体積膨張する。

【0050】

ある実施形態では、前記第2幅は、略2ナノメータ以下の幅を有する。別の実施形態では、前記第2幅は、略1ナノメータ以下である。別の実施形態では、前記第2幅は、略0.5ナノメータより大きい。

20

【0051】

ある実施形態では、前記標的種は、核酸分子であり、前記第2幅は、前記核酸分子の直径より小さい。

【0052】

ある実施形態では、前記(c)の工程は、前記化合物生成層と両方の前記電極形成部の間での前記反応を含む。別の実施形態では、前記(c)の工程は、前記化合物生成層と前記電極形成部の1つのみの間での前記反応を含む。

【0053】

ある実施形態では、前記方法は、前記ナノギャップと交差するチャネルを形成する工程をさらに含む。別の実施形態では、前記チャネルは、覆われたチャネルである。

30

【0054】

本発明の一態様によれば、基板にナノギャップを挟んで対向して配置された少なくとも2つの電極部を備えるナノギャップ電極センサであって、前記電極部の対向するサイドウォールは、互いが徐々に近づき、前記サイドウォール間の幅は徐々に狭くなり、前記電極は、標的種が前記電極の間に配置される時前記ナノギャップを横切る電流を検出するように適合されたナノギャップ電極センサを提供する。別の実施形態では、前記電流は、トンネル電流である。

【0055】

ある実施形態では、前記電極部は、金属シリサイドから形成される。別の実施形態では、前記ナノギャップは、前記ナノギャップが前記基板に近づくにつれ、前記電極部の前記サイドウォール間の距離が徐々に拡がるような後方に曲った形状に形成される。別の実施形態では、前記サイドウォールは、前記基板と接して外側に膨張した部分を含む。

40

【0056】

ある実施形態では、前記ナノギャップと交差し流体連結されているチャネルをさらに備える。別の実施形態では、前記チャネルは、覆われたチャネルである。

【0057】

本開示の単なる例示実施形態が図示および説明される追加の態様及び本発明の利点は以下の詳細な説明から当業者には容易に明らかとなるであろう。理解されるように、本発明は他のおよび異なる実施形態が可能であり、そのいくつかの詳細は、本開示から逸脱する

50

ことなく、種々の明白な点において変更が可能である。したがって、図面および説明は、本質的に例示であり、限定としてではないと見なされるべきである。

【0058】

(参照による援用)

各個々の刊行物、特許、または特許出願が具体的かつ個別に参照により組み込まれることが示されたかのように本明細書で言及される全ての刊行物、特許、および特許出願は、本明細書と同程度に、参考として援用される。

【0059】

本発明の新規な特徴は、添付の特許請求の範囲に詳細に記載される。本発明の特徴および利点のより良い理解は、本発明の原理を利用する例示的な実施形態及び添付図面により以下の詳細な説明を参照することによって得られるであろう。

10

【図面の簡単な説明】

【0060】

【図1】本発明の一実施形態による製造方法により製造したナノギャップ電極の構成を示す概略図である。

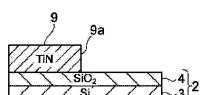

【図2A】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図2B】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

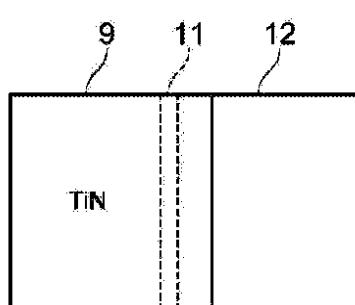

【図2C】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

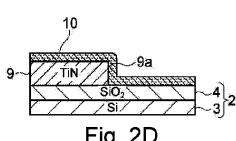

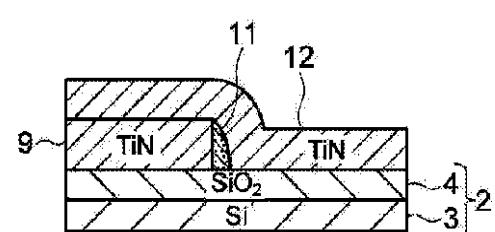

【図2D】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図2E】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図2F】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

20

【図3A】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図3B】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図3C】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図3D】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図3E】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図3F】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図4】本発明の一実施形態による製造方法により製造したナノギャップ電極の構成を示す概略図である。

【図5】図4に示すナノギャップ電極の製造方法の説明に供する概略図である。

30

【図6A】図4に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図6B】図4に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図6C】図4に示すナノギャップ電極の製造方法の説明に供する概略図である。

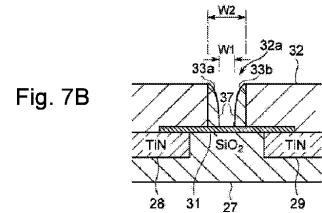

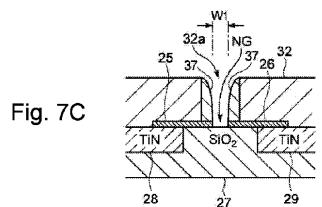

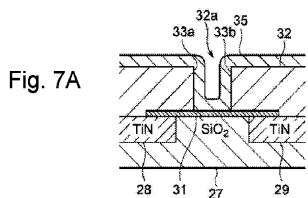

【図7A】図4に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図7B】図4に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図7C】図4に示すナノギャップ電極の製造方法の説明に供する概略図である。

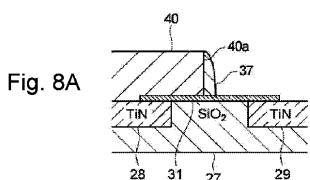

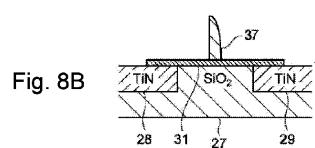

【図8A】ナノギャップ電極の製造方法の説明に供する概略図である。

【図8B】ナノギャップ電極の製造方法の説明に供する概略図である。

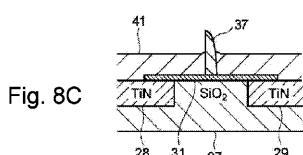

【図8C】ナノギャップ電極の製造方法の説明に供する概略図である。

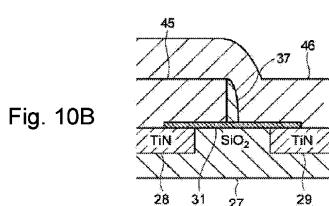

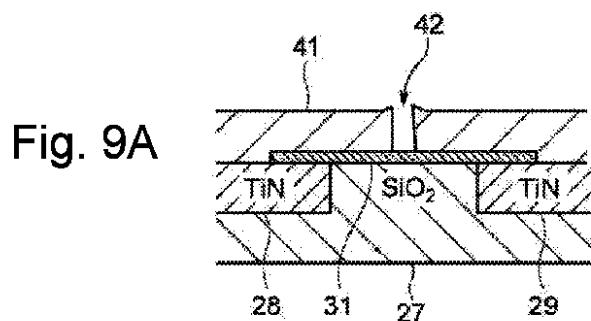

【図9A】図8に示すナノギャップ電極の製造方法の説明に供する概略図である。

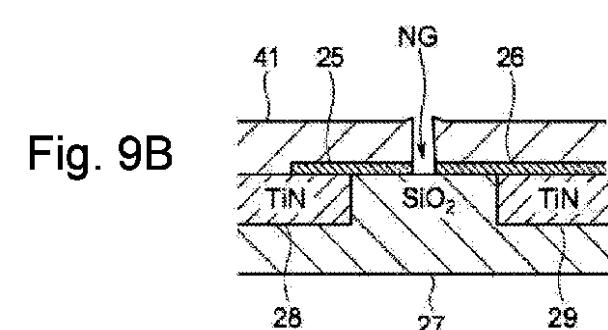

【図9B】図8に示すナノギャップ電極の製造方法の説明に供する概略図である。

40

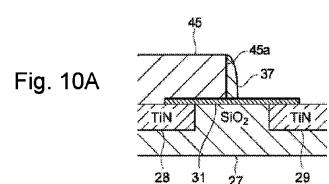

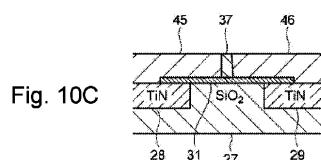

【図10A】ナノギャップ電極の製造方法の説明に供する概略図である。

【図10B】ナノギャップ電極の製造方法の説明に供する概略図である。

【図10C】ナノギャップ電極の製造方法の説明に供する概略図である。

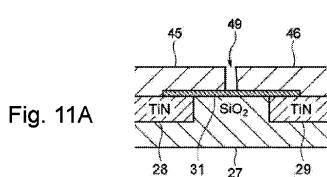

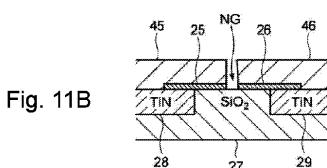

【図11A】図10に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図11B】図10に示すナノギャップ電極の製造方法の説明に供する概略図である。

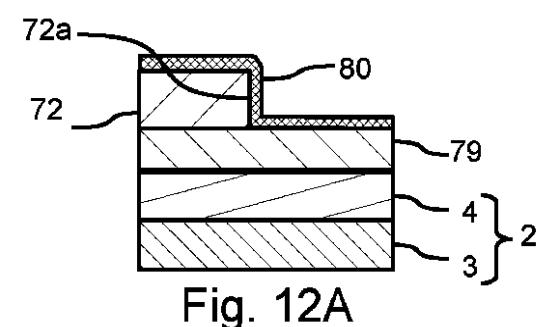

【図12A】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

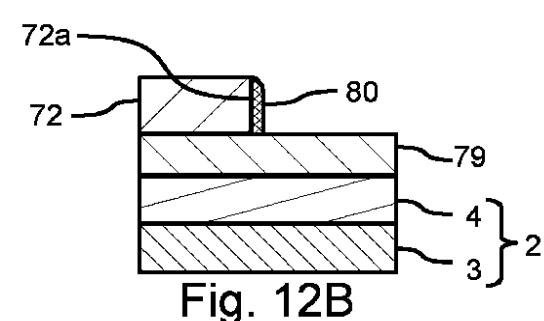

【図12B】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

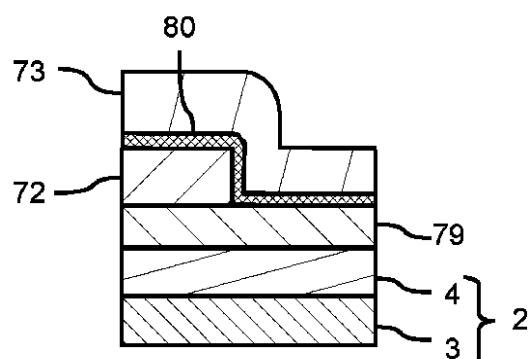

【図12C】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図12D】図1に示すナノギャップ電極の製造方法の説明に供する概略図である。

50

【図13A】図12に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図13B】図12に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図13C】図12に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図13D】図12に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図13E】図12に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図13F】図12に示すナノギャップ電極の製造方法の説明に供する概略図である。

【図14】ナノギャップ電極を示す概略図である。

【図15】電極形成部とマスクが基板上形成される構成を示す概略図である。

【図16】ナノギャップ電極の製造方法の説明に供する概略図である。

【図17】ナノギャップ電極の製造方法の説明に供する別の概略図である。

10

【図18】別の実施形態によって、ナノギャップ電極の構成を示す概略図である。

【図19】ナノギャップ電極の製造方法の説明に供する概略図である。

【図20】ナノギャップ電極の製造方法の説明に供する別の概略図である。

【図21A】いくつかの異なる電極の形を示す概略上面図である。

【図21B】いくつかの異なる電極の形を示す概略上面図である。

【図21C】いくつかの異なる電極の形を示す概略上面図である。

【図22A】ナノギャップ電極にDNAを供給するための統合チャネルでナノギャップ電極を製造する方法を説明する概略断面図である。

【図22B】ナノギャップ電極にDNAを供給するための統合チャネルでナノギャップ電極を製造する方法を説明する概略断面図である。

20

【図22C】ナノギャップ電極にDNAを供給するための統合チャネルでナノギャップ電極を製造する方法を説明する概略断面図である。

【図22D】ナノギャップ電極にDNAを供給するための統合チャネルでナノギャップ電極を製造する方法を説明する概略断面図である。

【図22E】ナノギャップ電極にDNAを供給するための統合チャネルでナノギャップ電極を製造する方法を説明する概略断面図である。

【図22F】ナノギャップ電極にDNAを供給するための統合チャネルでナノギャップ電極を製造する方法を説明する概略断面図である。

【図23】1以上のナノギャップ電極にDNAを供給するための統合チャネルの構成を示す概略上面図である。

30

【図24A】単一側膨張法を使用してナノギャップ電極を製造する方法を説明する概略図である。

【図24B】単一側膨張法を使用してナノギャップ電極を製造する方法を説明する概略図である。

【図24C】単一側膨張法を使用してナノギャップ電極を製造する方法を説明する概略図である。

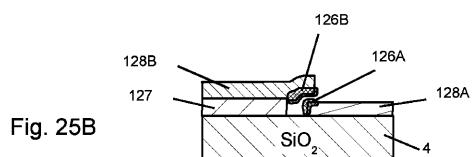

【図25A】垂直電極方向を使用してナノギャップ電極を製造する方法を説明する概略図である。

【図25B】垂直電極方向を使用してナノギャップ電極を製造する方法を説明する概略図である。

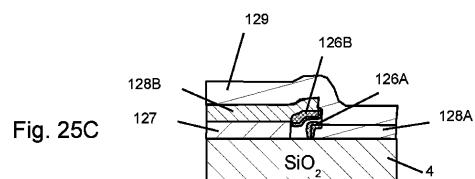

【図25C】垂直電極方向を使用してナノギャップ電極を製造する方法を説明する概略図である。

40

【発明を実施するための形態】

【0061】

【0062】

【0063】

【0064】

【0065】

【0066】

【0067】

50

【 0 0 6 8 】

【 0 0 6 9 】

【 0 0 7 0 】

【 0 0 7 1 】

【 0 0 7 2 】

【 0 0 7 3 】

【 0 0 7 4 】

【 0 0 7 5 】

【 0 0 7 6 】

【 0 0 7 7 】

【 0 0 7 8 】

【 0 0 7 9 】

【 0 0 8 0 】

【 0 0 8 1 】

【 0 0 8 2 】

【 0 0 8 3 】

【 0 0 8 4 】

【 0 0 8 5 】

10

本発明の種々の実施形態を本明細書で示し説明してきたが、そのような実施形態は、例示の手段としてのみ提供されることが、当業者には明らかであろう。多数のバリエーション、変化および置換が、本発明から逸脱することなく、当業者に起こる。これは、本明細書で説明する本発明の実施形態に対する数々の代替手段を使用してもよいことを理解すべきである。

20

【 0 0 8 6 】

本明細書中で用いられる用語「ギャップまたは間隙」は、形成されるかまたは他の材料内に設けられた孔、溝（チャネル）または通路を一般的には指す。材料とは、基板のような固体材料であってもよい。ギャップは、センシング回路またはセンシング回路に接続された電極に隣接してまたは近くに配置することができる。例としては、ギャップは、0.1ナノメートル（nm）から約1000nmのオーダーで特徴的な幅と直径を有している。ナノメータオーダーの幅を有するギャップは、「ナノギャップ」と呼ばれることがある。

30

【 0 0 8 7 】

本明細書中用いられる用語「電極形成部」は、一般に、電極を生成するために使用される部品または部材を指す。電極形成部は、電極または電極の一部となる場合がある。たとえば、電極形成部は、第2の導電体と電気的に連通する第1の導電体である。別の例において、電極形成部は電極である。

【 0 0 8 8 】

本明細書中で用いられる用語「核酸」は、一般に、1以上の核酸のサブユニットからなる分子を指す。核酸は、リン酸（A）、シトシン（C）、グアニン（G）、チミン（T）、ウラシル（U）、またはその変異体から選ばれる1種または2種以上のサブユニットを含むことができる。ヌクレオチドはA、C、G、T、U、または変異体が含まれる。ヌクレオチドは、核酸鎖に組み入れることが可能なすべてのサブユニットを含めることができる。このようなサブユニットは、A、C、G、T、Uであり、または、1以上の相補的A、C、G、T、Uに、またはプリン（AまたはG、またはその変異体）またはピリミジン塩基（すなわち、C、T、U、またはその変異体）と相補的なA、C、G、T、Uに特有なその他のサブユニットであってもよい。サブユニットは、塩基の個々の核酸塩基または基（例えば、AA、TA、AT、GC、CG、CT、TC、GT、TG、AC、CA、またはこれらのウラシルカウンターパート）を解決することができる。いくつかの例において、核酸は、デオキシリボ核酸（DNA）またはリボ核酸（RNA）、またはその誘導体である。核酸が一本鎖または二本鎖の場合もある。

40

50

## 【0089】

本開示は、ナノギャップ電極でセンサを形成するための方法を提供し、そのセンサは、種々の用途、生体分子（例えば、核酸分子）の検出などに使われる。本明細書で提供される方法に従って形成したナノギャップ電極は、核酸分子、デオキシリボ核酸（DNA）、リボ核酸（RNA）、または変異体の配列決定にも使用することができる。

## 【0090】

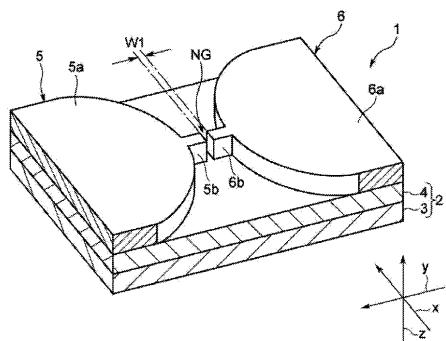

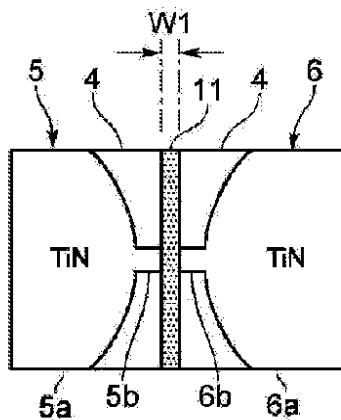

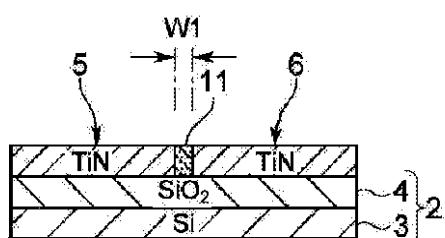

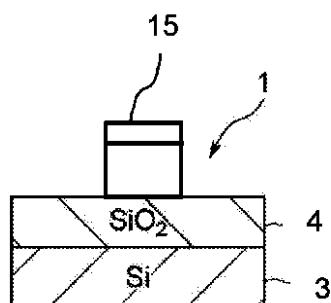

図1は、本発明の製造方法によって製造したナノギャップ電極1を示し、このナノギャップ電極1には、対向した電極部5,6が基板2上に設けられており、これら電極部5,6間に幅W1がナノスケール（例えば1000[nm]以下）でなる中空状のナノギャップNGが形成されている。本発明による製造方法によって製造したナノギャップ電極1は、例えばナノギャップNGの幅W1を0.1~30[nm]、さらには使用態様に応じて2[nm]以下、1[nm]以下、0.9[nm]以下、0.8[nm]以下、0.7[nm]以下、0.6[nm]以下、或いは0.5[nm]以下にまで形成し得るようになされている。場合によっては、W1は、生体分子（たとえば、DNAまたはRNA）でありうる標的種の直径より小さい。

10

## 【0091】

ここで、基板2は、例えばシリコン基板3と、当該シリコン基板3上に形成された酸化シリコン層4とから構成されてもよい。あるいは、基板2は、ゲルマニウムやガリウムひ素などのIV族またはV族半導体を含む他の半導体材料を含んで構成されてもよい。基板2は、当該酸化シリコン層4上に対となる2つの電極部5,6が形成された構成を有してもよい。これら電極部5,6は、いずれも例えばチタンナイトライド（TiN）等の金属部材からなり、基板2上にてナノギャップNGを中心にはほぼ左右対称に形成されている。いくつかの実施形態の場合、電極部5,6は、実質的に同一の構成を有しており、ナノギャップNGを形成する電極先端部5b,6bと、当該電極先端部5b,6bの根元部分に一体形成された基体部5a,6aとから構成されている。電極先端部5b,6bは、例えば長手方向がy方向に延びた直方体状からなり、先端面同士が対向するように配置され、先端部5b,6bは、湾曲していてもよい。

20

## 【0092】

基体部5a,6aは、電極先端部5b,6bが設けられた中央先端部分に膨らみを有し、この中央先端部分を中心にして両側部に向けてなだらかな曲面が形成されており、電極先端部5b,6bを頂点とした湾曲状に形成されている。なお、電極部5,6は、電極部5,6の長手方向たるy方向と、このy方向と直交する電極部5,6の高さ方向たるz方向とに直交するx方向から、例えば一本鎖DNAを含んだ溶液が供給されると、当該溶液を基体部5a,6aの曲面に沿って電極先端部5b,6b側に誘導し、当該溶液が確実にナノギャップNGを通過し得るように構成されている。

30

## 【0093】

因みに、このような構成を有したナノギャップ電極1は、例えば図示しない電源から電極部5,6に電流が供給され得るようになされており、電極部5,6間の電流値が図示しない電流計により計測され得る。ナノギャップ電極1は、x方向から電極部5,6間のナノギャップNGに一本鎖DNAを通過させ、当該一本鎖DNAの塩基が電極部5,6間のナノギャップNGを通過したときに電極部5,6間に流れる電流値を電流計にて計測させてゆき、その電流値を基に一本鎖DNAを構成する塩基を同定させ得る。

40

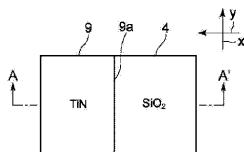

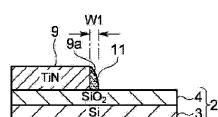

## 【0094】

次に、電極部5,6間にナノギャップNGを有するナノギャップ電極1の本発明による製造方法について説明する。この場合、先ず始めに、図2Aと、図2AのA-A部分の側断面構成を示す図2Bのように、シリコン基板3上に酸化シリコン層4が形成された基板2を用意し、例えばチタンナイトライド（TiN）からなり、側壁9aを有した四辺状の第1電極形成部9を、酸化シリコン層4上の所定領域にフォトリソグラフィ技術を利用して形成する。

## 【0095】

50

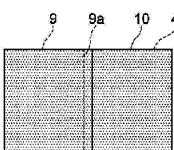

次いで、図 2 Aとの対応部分に同一符号を付して示す図 2 Cと、図 2 Bとの対応部分に同一符号を付して示す図 2 Dのように、例えば CVD (Chemical Vapor Deposition) 法等によって、基板 2 の表面 (この場合、酸化シリコン層 4) の部材と異なるチタン (Ti) やシリコンナイトライド (SiN) 等の部材でなるサイドウォール形成層 10を、第 1 電極形成部 9 上および露出した基板 2 上に成膜する。この際、第 1 電極形成部 9 には、側壁 9a に沿ってサイドウォール形成層 10 が形成されるが、この側壁 9a に形成されるサイドウォール形成層 10 の膜厚を、所望するナノギャップ NG の幅 W1 に応じて選定する。すなわち、幅 W1 が小さいナノギャップ NG を形成する場合には、サイドウォール形成層 10 の膜厚を薄く形成し、一方、幅 W1 が大きいナノギャップ NG を形成する場合には、サイドウォール形成層 10 の膜厚を厚く形成する。

10

## 【0096】

次いで、第 1 電極形成部 9 上および露出した基板 2 上に成膜したサイドウォール形成層 10を、例えばドライエッティングによりエッチバックし、第 1 電極形成部 9 の側壁 9a に沿ってサイドウォール形成層 10 を残存させ、図 2 C の対応部分に同一符号を付して示す図 2 Eと、図 2 Dとの対応部分に同一符号を付して示す図 2 Fのように、第 1 電極形成部 9 の側壁 9a に沿ってサイドウォール 11 を形成する。なお、このようにして形成されたサイドウォール 11 は、第 1 電極形成部 9 の側壁 9a の頂点から基板 2 に向けて次第に幅広に形成されており、当該サイドウォール 11 の幅の最大の厚みが最終的に形成されるナノギャップ NG の幅 W1 となり得る。

20

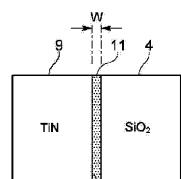

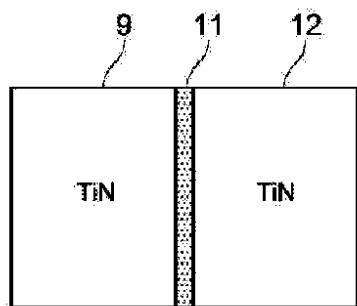

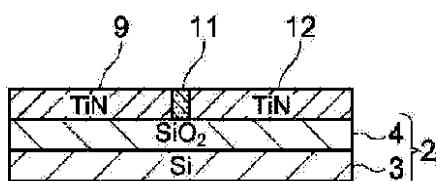

## 【0097】

次いで、図 2 Eとの対応部分に同一符号を付して示す図 3 Aと、図 2 Fとの対応部分と同一符号を付して示す図 3 Bのように、第 1 電極形成部 9 上、サイドウォール 11 上、および露出した基板 2 上に、例えばスパッタ法等によってチタンナイトライド (TiN) 等の金属部材でなる第 2 電極形成部 12 を形成する。次いで、第 1 電極形成部 9 およびサイドウォール 11 を覆っている領域の第 2 電極形成部 12 や、さらには第 1 電極形成部 9 およびサイドウォール 11 を、例えば CMP (Chemical and Mechanical Polishing) 等の平坦化処理によってオーバー研磨してゆき、図 3 Aとの対応部分に同一符号を付して示す図 3 Cと、図 3 Bとの対応部分に同一符号を付して示す図 3 Dのように、第 1 電極形成部 9 、サイドウォール 11 、および第 2 電極形成部 12 の各表面を全て外部に露出させる。

30

## 【0098】

いくつかの実施形態の場合、平坦化処理は、サイドウォール 11 の側面において上部の傾斜が大きい領域を研磨し、第 1 電極形成部 9 と第 2 電極形成部 12 との間ににおけるサイドウォール 11 の断面がほぼ四辺状となるまで、第 1 電極形成部 9 、サイドウォール 11 および第 2 電極形成部 12 をオーバー研磨している。なお、平坦化処理を行う際、第 1 電極形成部 9 、サイドウォール 11 、および第 2 電極形成部 12 の各表面を全て外部に露出させることができれば、第 1 電極形成部 9 およびサイドウォール 11 を覆っている領域の第 2 電極形成部 12 だけを研磨するようにしてもよい。

## 【0099】

次いで、これら外部に露出した第 1 電極形成部 9 、サイドウォール 11 、および第 2 電極形成部 12 の表面に層状のレジストマスクを形成した後、フォトリソグラフィ技術を利用して第 1 電極形成部 9 および第 2 電極形成部 12 をそれぞれパターニングする。ある場合には、レジストマスクでは、高分子材料は、ポリ (メタクリル酸メチル) (PMMA) 、ポリ (イミド) (PMGI) 、フェノール ホルムアルデヒド樹脂、SU 8 (Liuら、全体が参照により本明細書に組み込まれている「Process research of high aspect ratio microstructure using SU 8 resist」Microsystem Technologies 2004, V10, (4), 265 参照) などが含まれる。マスクは、基体部 5a 、6a の緩やかな曲線、および引き出し電極先端部 5b 、6b の突出部を形成することができる。図 3 Cとの対応部分に同一符号を付して示す図 3 Eと、図 3 Dとの対応部分に

40

50

同一符号を付して示す図3Fのように、第1電極形成部9を所定形状とした電極部5と、第2電極形成部12を所定形状とした電極部6とを形成して、基板2上にて電極先端部5b, 6bがサイドウォール11を介して対向配置された構成を形成する。最後に、例えばウェットエッキングによって電極先端部5b, 6b間にサイドウォール11を除去することにより、サイドウォール11の幅W1と同じ幅W1のナノギャップNGを電極先端部5b, 6b間に形成し得、図1に示すようなナノギャップ電極1を製造し得る。この際、サイドウォール11は、例えば基板2の表面にある酸化シリコン層4と異なるナイトライド(N)やシリコンナイトライド(SiN)等の部材により形成されていることから、サイドウォール11のみを除去し得、基板2上に電極部5, 6を確実に残存させることができる。

10

## 【0100】

ある場合には、第1電極形成部9及び第2電極形成部12の間に配置される標的種(例えば、ビオモリュレDNAまたはRNAなど)と、ナノギャップを横切る電流を検出する電極として使用するために用意されています。現在は、トンネル電流であり得る。このような電流は、ナノギャップを介して標的種の流れによって検出することができます。場合によっては、電極に結合された検出回路は電流を発生させるための電極間に印加される電圧が用意されています。別 の方法として、または、加えて、電極は標的種(例えば、核酸分子の塩基)と関連付けられた電気伝導度の測定、および/または同定することができる。この場合においては、トンネル電流は、電気伝導率と関係づけることができる。

20

## 【0101】

以上の構成において、基板2上に形成された第1電極形成部9の側壁9aにサイドウォール11を形成し、第1電極形成部9上、サイドウォール11上、および露出した基板2上に第2電極形成部12を形成した後、第2電極形成部12に覆われた第1電極形成部9およびサイドウォール11が外部に露出するように第2電極形成部12を除去して、外部に露出した第1電極形成部9、サイドウォール11、および第2電極形成部12を基板2上に形成する。そして、第1電極形成部9および第2電極形成部12間にサイドウォール11を除去し、第1電極形成部9および第2電極形成部12間にナノギャップNGを形成し、その後、第1電極形成部9および第2電極形成部12をパターニングして電極先端部5b, 6b間にナノギャップNGが設けられた電極部5, 6を形成する。

30

## 【0102】

このような本発明の製造方法では、サイドウォール11の膜厚を調整することで、所望の幅W1でなるナノギャップNGを形成し得、また、当該サイドウォール11の膜厚については極めて薄く形成し得ることから、サイドウォール11の幅W1に対応した極めて小さい幅W1のナノギャップNGをも形成し得る。

40

## 【0103】

以上の構成によれば、第1電極形成部9に対して配置されたサイドウォール11をマスクとして用い、サイドウォール11の膜厚により調整された幅W1のナノギャップNGを第1電極形成部9および第2電極形成部12間に形成するようにしたことにより、従来と同じ寸法の幅W1のナノギャップNGを形成し得る他、従来よりも一段と幅W1が小さいナノギャップNGをも形成し得る。

## 【0104】

なお、上述した実施形態においては、図3Bに示すように、製造過程で第1電極形成部9上に第2電極形成部12を直接形成する場合について述べたが、本発明はこれに限らず、例えば表面にハードマスクが形成された第1電極形成部9を用い、当該第1電極形成部9上に第2電極形成部12を直接形成しなくてもよい。この場合でも、サイドウォール11と隣接するように第2電極形成部12を形成し、第1電極形成部9および第2電極形成部12間にサイドウォール11を配置でき、かくして、当該サイドウォール11を除去することで第1電極形成部9および第2電極形成部12間にナノギャップNGを形成し得る。

## 【0105】

50

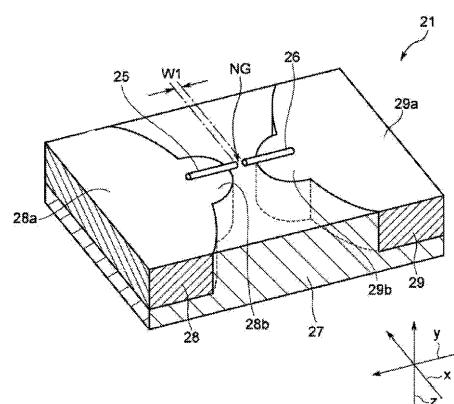

図4に示すように別の実施形態で、ナノギャップ電極21を示し、先端面が対向した円柱状の電極部25,26が基板22上に設けられており、これら電極部25,26間に幅W1がナノスケール（例えば1000[nm]以下）でなる中空状のナノギャップNGが形成されている。本発明による製造方法によって製造したナノギャップ電極21でも、例えばナノギャップNGの幅W1を0.1~30[nm]、さらには使用様に応じて2[nm]以下、1[nm]以下、0.9[nm]、0.8[nm]、0.7[nm]、0.6[nm]、0.5[nm]、またこれら以外の幅以下にまで形成し得るようになされている。

#### 【0106】

ここで、基板22は、例えば図示しないシリコン基板上に酸化シリコン層27が形成されており、この酸化シリコン層27内に電極支持部28,29が対向配置された構成を有する。また、この基板22の表面には、一方の電極支持部28上に一方の電極部25が配置され、他方の電極支持部29上に当該電極部25と対をなす他方の電極部26が配置されている。

10

#### 【0107】

なお、電極支持部28,29は、いずれも例えばチタンナイトライド(TiN)等の金属部材からなり、基板22内にて所定の間隙を隔ててほぼ左右対称に形成され、その表面が酸化シリコン層27の表面と面一に形成されている。いくつかの実施形態の場合、電極支持部28,29は、同一の構成を有しており、電極部25,26が表面に固着された電極膨出部28b,29bと、当該電極膨出部28b,29bの根元部分に一体形成された基体部28a,29aとから構成され、基体部28a,29aから電極膨出部28b,28bが突出した構成を有する。いくつかの実施形態の場合、電極支持部28,29は、電極膨出部28b,29bが略半円状に形成され、基体部28a,29aが電極膨出部28b,29bのある中央先端部分を中心に両側部に向けてなだらかに傾斜しており、全体として電極膨出部28b,29bを頂点とした凸状に形成されている。

20

#### 【0108】

かかる構成に加えて、円柱状の電極部25,26は、例えばカーボンナノチューブ等の導電性部材により形成されており、外周面が電極膨出部28b,29bにそれぞれ固着され、長手方向がy方向に延び、先端面同士が対向するように配置されている。

30

#### 【0109】

因みに、このような構成を有したナノギャップ電極21は、例えば図示しない電源から電極部25,26に電流が供給され得るようになされており、電極部25,26間の電流値が図示しない電流計により計測され得る。ナノギャップ電極21は、図示しない誘導手段によってx方向から電極部25,26間のナノギャップNGに一本鎖DNAを通過させ、当該一本鎖DNAの塩基が電極部25,26間のナノギャップNGを通過したときに電極部25,26間に流れる電流値を電流計にて計測させてゆき、その電流値を基に一本鎖DNAを構成する塩基を同定させ得る。

#### 【0110】

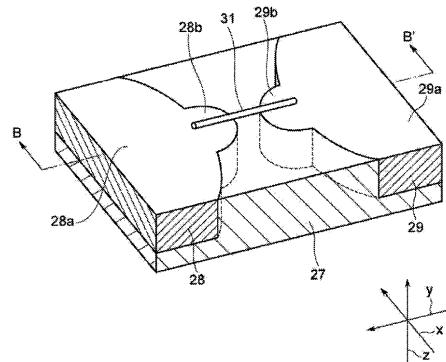

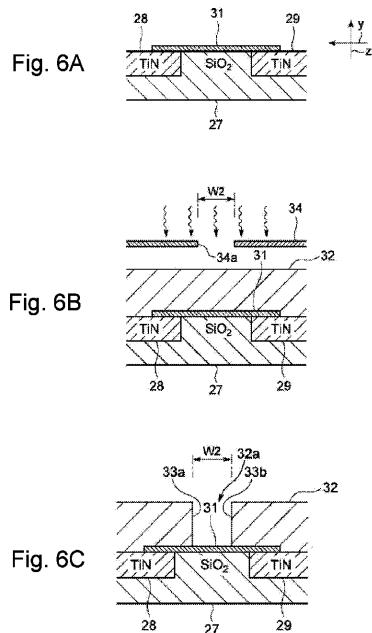

次に、電極部25,26間にナノギャップNGを有するナノギャップ電極21の本発明による製造方法について説明する。この場合、先ず始めに、図4との対応部分に同一符号を付して示す図5と、図5のB-B部分の側断面構成を示す図6Aのように、酸化シリコン層27内に所定形状の電極支持部28,29を形成した基板22を用意し、当該電極支持部28,29の電極膨出部28b,29b(図5)を架け渡すようにして、一方の電極支持部28の表面から基板22の表面を介して他方の電極支持部29の表面に亘って円柱状の電極形成部31を形成する。

40

#### 【0111】

次いで、図6Aとの対応部分に同一符号を付して示す図6Bのように、電極形成部31上および基板22上に層状のレジストマスク32を成膜した後、ナノギャップNG(図4)の幅W1よりも大きい幅W2の開口部34aが形成されたフォトマスク34を用い、露光・現像によりレジストマスク32をパターニングする。なお、ギャップ形成マスクとし

50

てのレジストマスク 3 2 をパターニングする際、フォトマスク 3 4 は、電極形成部 3 1 のナノギャップ NG を形成する領域に開口部 3 4 a を配置する。

【 0 1 1 2 】

これにより、レジストマスク 3 2 には、図 6 B との対応部分に同一符号を付して示す図 6 C のように、ナノギャップ NG ( 図 4 ) が形成される領域に対応した領域に、側壁 3 3 a , 3 3 b が幅 W 2 を介して対向配置した間隙 3 2 a が形成され、当該間隙 3 2 a から電極形成部 3 1 を外部に露出させ得る。次いで、図 6 C との対応部分に同一符号を付して示す図 7 A のように、例えば CVD 法等によって、基板 2 2 の表面 ( この場合、酸化シリコン層 2 7 および電極支持部 2 8 , 2 9 ) の部材と異なるチタン ( Ti ) やシリコンナイトライド ( SiN ) 等の部材でなるサイドウォール形成層 3 5 を、レジストマスク 3 2 上や、レジストマスク 3 2 の間隙 3 2 a 内に露出した電極形成部 3 1 の部分および酸化シリコン層上に成膜する。この際、レジストマスク 3 2 には、間隙 3 2 a 内の側壁 3 3 a , 3 3 b にも所定膜厚のサイドウォール形成層 3 5 が、たとえば、気相成長法、化学気相成長法 ( CVD ) といった方法により形成され得る。サイドウォール形成用層 3 5 は、所定の膜厚を有し、これもまた間隙 3 2 a 内にレジストマスク 3 2 の側壁 3 3 a , 3 3 b 上に形成されてもよい。

10

【 0 1 1 3 】

次いで、間隙 3 2 a 内の電極形成部 3 1 および酸化シリコン層 2 7 上や、レジストマスク 3 2 上に成膜したサイドウォール形成層 3 5 を、例えばドライエッチングによりエッチバックし、レジストマスク 3 2 の側壁 3 3 a , 3 3 b に沿ってサイドウォール形成層 3 5 を残存させ、図 7 A の対応部分に同一符号を付して示す図 7 B のように、レジストマスク 3 2 の側壁 3 3 a , 3 3 b に沿ってサイドウォール 3 7 を形成する。なお、このようにして形成されたサイドウォール 3 7 は、レジストマスク 3 2 の側壁 3 3 a , 3 3 b の頂点から電極形成部 3 1 や酸化シリコン層 2 7 に向けて次第に幅が広くなるように形成されており、この幅の厚み分だけ間隙 3 2 a の幅 W 2 を狭くし得る。このように厚くすることは、標的種の検出などの様々な用途での使用に対するナノギャップ幅を選択するために使用できる。

20

【 0 1 1 4 】

かくして、レジストマスク 3 2 の間隙 3 2 a では、当該間隙 3 2 a 内で電極形成部 3 1 が露出する幅 W 1 が、レジストマスク 3 2 の間隙 3 2 a の幅 W 2 よりもサイドウォール 3 7 の膜厚分だけ小さくなり得る。次いで、対向配置されたサイドウォール 3 7 間の幅 W 1 の間隙に露出している電極形成部 3 1 を、例えばドライエッチングにより除去し、図 7 B との対応部分に同一符号を付して示す図 7 C のように、サイドウォール 3 7 間に幅 W 1 のナノギャップ NG を形成するとともに、当該ナノギャップ NG を介して対向配置された 2 つの電極部 2 5 , 2 6 を形成する。

30

【 0 1 1 5 】

このようにレジストマスク 3 2 の間隙 3 2 a 内にて電極形成部 3 1 が露出する幅 W 1 は最終的に形成されるナノギャップ NG の幅 W 1 となる。このため、レジストマスク 3 2 の側壁 3 2 a , 3 2 b にサイドウォール形成層 3 5 を形成する工程では、当該サイドウォール形成層 3 5 の膜厚を、所望するナノギャップ NG の幅 W 1 に応じて選定する。すなわち、幅 W 1 が小さいナノギャップ NG を形成する場合には、サイドウォール形成層 3 5 の膜厚を厚く形成して、レジストマスク 3 2 の間隙 3 2 a 内に露出させる電極形成部 3 1 の幅 W 1 を小さくする。一方、幅 W 1 が大きいナノギャップ NG を形成する場合には、サイドウォール形成層 3 5 の膜厚を薄く形成して、レジストマスク 3 2 の間隙 3 2 a 内に露出させる電極形成部 3 1 の幅 W 1 を大きくする。

40

【 0 1 1 6 】

そして、最後に、電極部 2 5 , 2 6 上および酸化シリコン層 2 7 上にあるサイドウォール 3 7 を例えばウェットエッチングにより除去した後、電極部 2 5 , 2 6 上および酸化シリコン層 2 7 上にあるレジストマスク 3 2 をアッシングにより除去することにより、図 4 に示したように、電極部 2 5 , 2 6 間にナノギャップ NG を有したナノギャップ電極 2 1

50

を形成し得る。なお、この場合、サイドウォール37を最初に除去した後、レジストマスク32を除去しているが、本発明はこれに限らず、レジストマスク32を最初に除去した後、サイドウォール37を除去するようにしてもよい。

【0117】

以上の構成において、間隙を隔てて対向した側壁33a, 33bを有するレジストマスク32を電極形成部31上に形成し、レジストマスク32の両側壁33a, 33bにそれぞれサイドウォール37を形成し、サイドウォール37間に電極形成部31を露出させた後、サイドウォール37間に露出した電極形成部31を除去してナノギャップNGを形成する。

【0118】

このような本発明の製造方法では、レジストマスク32の間隙32aの幅W2に加えて、サイドウォール37の膜厚を調整することで、所望の幅W1でなるナノギャップNGを形成し得る。また、この製造方法では、レジストマスク32の側壁33a, 33bにサイドウォール37を形成し、当該サイドウォール37の膜厚分だけレジストマスク32の間隙32aの幅W2を小さくし得ることから、パターニングしたレジストマスク32に形成した間隙32aの幅W2よりも、さらに一段と小さい幅W1のナノギャップNGを形成できる。

10

【0119】

以上の構成によれば、電極形成部31に対して配置されたサイドウォール37をマスクとして用い、サイドウォール37の膜厚により調整された幅W1のナノギャップNGを電極形成部31に形成するようにしたことにより、従来と同じ寸法の幅W1のナノギャップNGを形成し得る他、従来のリソグラフ技術を使用して形成された従来のナノギャップよりも一段と幅W1が小さいナノギャップNGをも形成し得る。

20

【0120】

なお、上述した実施の形成においては、間隙32aを有するレジストマスク32を、電極形成部31上に直接形成するようにしたが、本発明はこれに限らず、例えば、表面にハードマスクが形成された電極形成部を用い、間隙を有するギャップ形成マスクをハードマスク上に形成し、当該ハードマスクを介して電極形成部に対しギャップ形成マスクを配置してもよい。

30

【0121】

この場合には、レジストマスク32の両側壁33a, 33bに形成されたサイドウォール37間に露出したハードマスクだけを除去して当該ハードマスクに間隙を形成する。次いで、サイドウォール37間にあるハードマスクの間隙から露出した電極形成部31を、ドライエッチングにより除去し、サイドウォール37間にナノギャップNGを形成する。

【0122】

上述のように、マスクとして、レジストマスク32が適用されても良い。他の実施形態では、間隙を形成し得、この間隙の側壁にサイドウォールを形成することができれば、レジスト以外の各種部材でなるマスクを適用してもよい。なお、最終的に製造されるナノギャップ電極としては、図7Cに示すサイドウォール37を、そのまま残存させたナノギャップ電極としてもよい。また、サイドウォール37は、後の工程で除去されてもよいし、レジストマスク32は、残存されてもよいし、除去されてもよい。

40

【0123】

次に、図4に示すナノギャップ電極21について、別の実施形態による製造方法について以下説明する。なお、図4に示すナノギャップ電極21の構成の説明については、重複するため省略する。この場合、先ず始めに図5に示すように、酸化シリコン層27内に所定形状の電極支持部28, 29を形成した酸化シリコン層27を用意し、当該電極支持部28, 29の電極膨出部28b, 29bを架け渡すようにして、一方の電極支持部28の表面から酸化シリコン層27の表面を介して他方の電極支持部29の表面に亘ってカーボンナノチューブでなる電極形成部31を形成する。

【0124】

50

また、電極形成部31は、金、プラチナなどの他の金属または合金ナノワイヤを含んでいてもよいし、半導体ナノワイヤを含んでいてもよい。ナノワイヤは、ナノメータの直径を有してもよいし、数ナノメータ以上の直径であってもよい。

#### 【0125】

また、電極形成部31は、金属、合金または半導体の薄い層（たとえば、単分子層）を含んでもよい。次いで、たとえば抵抗材料から作製されるサイドウォール形成マスク40は、電極形成部31および酸化シリコン層27上にフィルムとして形成されてもよい。次いで、電極形成部31上および酸化シリコン層27上に、例えばレジスト部材からなる層状のサイドウォール形成マスクを成膜した後、フォトリソグラフィ技術によって、サイドウォール形成マスク40をパターニングする。これにより、図5におけるB-B部分に着目した側断面構成を示す図8Aのように、電極形成部31上および酸化シリコン層27上には、電極形成部31のナノギャップNG（図4）を形成する領域に合わせてサイドウォール形成マスク40の側壁40aが形成され得る。

10

#### 【0126】

次いで、サイドウォール形成マスク40、露出した電極形成部31上および酸化シリコン層27上に、例えば電極形成部31の部材と異なるチタン（Ti）やシリコンナイトライド（SiN）等の部材でサイドウォール形成層（図示せず）を成膜した後、ドライエッティングによりエッチバックし、サイドウォール形成マスク40の側壁40aに沿ってサイドウォール形成層を残存させ、図8Aに示すように、サイドウォール形成マスク40の側壁40aに沿ってサイドウォール37を形成する。なお、このようにして形成されたサイドウォール37は、サイドウォール形成マスク40の側壁40aの頂点から電極形成部31や酸化シリコン層27に向けて次第に幅広に形成されており、当該サイドウォール37の幅の最大の厚みが最終的に形成されるナノギャップNGの幅W1となり得る。

20

#### 【0127】

次いで、図8Aとの対応部分に同一符号を付して示す図8Bのように、サイドウォール形成マスク40を除去して電極形成部31上に立設したサイドウォール37を残存させる。この場合のサイドウォールは、独立したサイドウォールである。この独立したサイドウォールは、約10ナノメータ（nm）、5nm, 4nm, 3nm, 2nm, 1nm, 0.9nm, 0.8nm, 0.7nm, 0.6nm or 0.5nm以下の幅を有することができる。次いで、図8Bとの対応部分に同一符号を付して示す図8Cのように、電極形成部31上および酸化シリコン層27上に、ギャップ形成マスクとしてのレジストマスク41を形成する。

30

このようなレジストマスク41は、露出した電極形成部31上および酸化シリコン層27上にレジスト塗布材を塗布し、これを硬化させることにより形成され得る。ここで、レジストマスク41となるレジスト塗布材は、その粘性が低く選定されており、例えば電極形成部31上および酸化シリコン層27上に塗布された際、サイドウォール37の上部に付着しても、遠心力を用いて均一な膜状に形成されるときに、自重や遠心力等でサイドウォール37の上部から落下し、当該サイドウォール37の上部がレジスト塗布材に埋もれることなく外部に露出した状態となり得る。これによりサイドウォール37は、その上部がレジストマスク41の表面から外部に露出され得る。

40

#### 【0128】

なお、レジスト塗布材の粘度が高く、サイドウォール37の上部に付着したレジスト塗布材がそのまま硬化してサイドウォール37全体がレジストマスク41に覆われたり、あるいは、レジストマスク41の膜厚が厚く、サイドウォール37全体がレジストマスクに覆われた場合には、レジストマスク41をエッチバックすることで、図8Cに示すように、レジストマスク41の表面からサイドウォール37の上部を外部に露出させる。

#### 【0129】

次いで、図8Cの対応部分に同一符号を付して示す図9Aのように、上部が露出したサイドウォール37を、例えばウェットエッティングによって除去し、当該レジストマスク41のサイドウォール37があった領域に間隙42を形成して、当該間隙42から電極形成

50

部31を露出させる。次いで、図9Aとの対応部分に同一符号を付して示す図9Bのように、レジストマスク41の間隙42から露出している電極形成部31を、例えばドライエッティングによって除去し、電極形成部31にナノギャップNGを形成するとともに、当該ナノギャップNGを介して対向配置された電極部25, 26を形成する。

【0130】

このようにレジストマスク41の間隙42内にて電極形成部31が露出する幅は最終的に形成されるナノギャップNGの幅W1(図4)となる。このため、サイドウォール形成マスク40の側壁40aにサイドウォール形成層を形成する工程では、当該サイドウォール形成層の膜厚を、所望するナノギャップNGの幅W1に応じて選定する。すなわち、幅W1が小さいナノギャップNGを形成する場合には、サイドウォール形成層の膜厚を薄く形成して、レジストマスク41の間隙42内で露出させる電極形成部31の幅を小さくする。一方、幅W1が大きいナノギャップNGを形成する場合には、サイドウォール形成層の膜厚を厚く形成して、レジストマスク41の間隙42内で露出させる電極形成部31の幅を大きくする。

【0131】

そして、最後に、電極部25, 26上および酸化シリコン層27上にあるレジストマスク41を、例えばアッシングにより除去することにより、図4に示したように、電極部25, 26間、酸化シリコン層27上にナノギャップNGを有したナノギャップ電極21を形成し得る。また、レジストマスク41は、残存させてもよいし、また、たとえば、DNAが電極部25, 26と相互作用するように動くチャネルとして使用されてもよい。

【0132】

以上の構成において、電極形成部31に対して配置したサイドウォール形成マスク40の側壁40aにサイドウォール37を形成した後、当該サイドウォール形成マスク40を除去してサイドウォール37を立設させ、このサイドウォール37を囲むようにレジストマスク41を形成する。そして、レジストマスク41に囲まれたサイドウォール37を除去してレジストマスク41に間隙42を形成し、当該間隙42から電極形成部31を露出させた後、当該間隙42から露出した電極形成部31を除去して間隙42内にナノギャップNGを形成する。

【0133】

このような本発明の製造方法では、サイドウォール37の膜厚を調整することで、レジストマスク41に形成される間隙42の幅を調整し得、かくして、間隙42内に形成されるナノギャップNGを所望の幅W1に形成し得る。また、サイドウォール37の膜厚については極めて薄く形成し得ることから、サイドウォール37の幅に対応した極めて小さい幅W1のナノギャップNGをも形成し得る。

【0134】

以上の構成によれば、電極形成部31に対して配置されたサイドウォール37をマスクとして用い、サイドウォール37の膜厚により調整された幅W1のナノギャップNGを電極形成部31に形成するようにしたことにより、従来と同じ寸法の幅W1のナノギャップNGを形成し得る他、従来よりも一段と幅W1が小さいナノギャップNGをも形成し得る。

【0135】

なお、サイドウォール形成マスク40の側壁40aに沿ってサイドウォール形成層を残存させ、壁状に立設したサイドウォール37を形成した場合について述べたが、本発明はこれに限らず、サイドウォール形成マスク40上のサイドウォール形成膜だけを除去し、サイドウォール形成マスク40の側壁40aに沿ってサイドウォール形成層を残存させるとともに、サイドウォール形成マスク40のない酸化シリコン層27上および電極形成部31にもサイドウォール形成層を残存させ、断面L字状とした底面部を有するサイドウォールを形成するようにしてもよい。

【0136】

また、サイドウォール形成マスク40や、ギャップ形成マスクとしてのレジストマスク

10

20

30

40

50

41をレジスト部材により形成した場合について述べたが、本発明はこれに限らず、サイドウォール形成マスクやギャップ形成マスクを、その他種々の部材により形成するようにしてもよい。

【0137】

次に、図4に示すナノギャップ電極21について、別の実施形態による製造方法について以下説明する。なお、図4に示すナノギャップ電極21の構成の説明については、重複するため省略する。この場合、先ず始めに図5に示すように、酸化シリコン層27内に所定形状の電極支持部28, 29を形成した基板22を用意し、当該電極支持部28, 29の電極膨出部28b, 29bを架け渡すようにして、一方の電極支持部28の表面から酸化シリコン層27の表面を介して他方の電極支持部29の表面に亘ってカーボンナノチューブでなる電極形成部31を形成する。

10

【0138】

これに加えて、後述するウェットエッチングによるサイドウォール除去の製造過程で、カーボンナノチューブでなる電極形成部31がエッチングされてしまうことを防止するために、例えばシリコンナイトライド(SiN)でなるエッチングストップ膜(図示せず)が電極形成部31上および酸化シリコン層27上に形成されてもよい。

【0139】

次いで、電極形成部31上および酸化シリコン層27上のエッチングストップ膜上に、例えばポリシリコンまたはアモルファスシリコンでなる層状の第1ギャップ形成マスクを、CVD法等によって成膜した後、フォトリソグラフィ技術によって、第1ギャップ形成マスクをパターニングする。これにより、図5におけるB-B部分に着目した側断面構成を示す図10Aのように、電極形成部31上および酸化シリコン層27上にあるエッチングストップ膜(図示せず)には、電極形成部31のナノギャップNG(図4)を形成する領域に合わせて第1ギャップ形成マスク45の側壁45aが形成され得る。

20

【0140】

次いで、電極形成部31上および基板22上のエッチングストップ膜や、第1ギャップ形成マスク45に、例えば電極形成部31の部材と異なる酸化シリコンでなるサイドウォール形成層(図示せず)を成膜した後、ドライエッチングによりエッチバックし、第1ギャップ形成マスク45の側壁45aに沿ってサイドウォール形成層を残存させ、図10Aに示すように、第1ギャップ形成マスク45の側壁45aに沿ってサイドウォール37を形成する。なお、このようにして形成されたサイドウォール37は、第1ギャップ形成マスク45の側壁45aの頂点から電極形成部31、酸化シリコン層27やエッチングストップ膜に向けて次第に幅広に形成されており、当該サイドウォール37の幅の最大の厚みが最終的に形成されるナノギャップNGの幅W1となり得る。

30

【0141】

次いで、図10Aとの対応部分に同一符号を付して示す図10Bのように、電極形成部31上および酸化シリコン層27上の図示しないエッチングストップ膜上や、サイドウォール37上、第1ギャップ形成マスク45上に、例えばポリシリコンやアモルファスシリコンでなる第2ギャップ形成マスク46を、CVD法等によって成膜する。

40

【0142】

次いで、第1ギャップ形成マスク45およびサイドウォール37を覆っている領域の第2ギャップ形成マスク46や、さらには第1ギャップ形成マスク45およびサイドウォール37を、例えばCMP等の平坦化処理によってオーバー研磨してゆき、図10Bとの対応部分に同一符号を付して示す図10Cのように、第1ギャップ形成マスク45、サイドウォール37、および第2ギャップ形成マスク46の各表面を全て外部に露出させる。

【0143】

いくつかの実施形態の場合、平坦化処理は、サイドウォール37の側面において上部の傾斜が大きい領域を研磨し、第1ギャップ形成マスク45と第2ギャップ形成マスク46との間ににおけるサイドウォール37の断面がほぼ四辺状となるまで、第1ギャップ形成マスク45、サイドウォール37および第2ギャップ形成マスク46をオーバー研磨している

50

。なお、平坦化処理を行う際、第1ギャップ形成マスク45、サイドウォール37、および第2ギャップ形成マスク46の各表面を全て外部に露出させることができれば、第1ギャップ形成マスク45およびサイドウォール37を覆っている領域の第2ギャップ形成マスク46だけを研磨するようにしてもよい。

【0144】

次いで、図10Cとの対応部分に同一符号を付して示す図11Aのように、例えばウェットエッチングによって第1ギャップ形成マスク45および第2ギャップ形成マスク46間にあるサイドウォール37を除去することにより、サイドウォール37の幅と同じ幅の間隙49を形成し、当該間隙49から電極形成部31上のエッチングストップ膜を露出させる。

10

【0145】

次いで、図11Aとの対応部分に同一符号を付して示す図11Bのように、第1ギャップ形成マスクおよび第2ギャップ形成マスク46間の間隙49から露出しているエッチングストップ膜および電極形成部31を、例えばドライエッチングによって順次除去してゆき、電極形成部31にナノギャップNGを形成するとともに、当該ナノギャップNGを介して対向配置された電極部25, 26を形成する。

【0146】

このように第1ギャップ形成マスク45および第2ギャップ形成マスク46間にある間隙49内の電極形成部31の幅は最終的に形成されるナノギャップNGの幅W1(図4)となる。このため、第1ギャップ形成マスク45の側壁45aにサイドウォール形成層を形成する工程では、当該サイドウォール形成層の膜厚を、所望するナノギャップNGの幅W1に応じて選定する。すなわち、幅W1が小さいナノギャップNGを形成する場合には、サイドウォール形成層の膜厚を薄く形成して、第1ギャップ形成マスク45および第2ギャップ形成マスク46間の間隙49内に露出する電極形成部31の幅を小さくする。一方、幅W1が大きいナノギャップNGを形成する場合には、サイドウォール形成層の膜厚を厚く形成して、第1ギャップ形成マスク45および第2ギャップ形成マスク46間の間隙49内に露出する電極形成部31の幅を大きくする。

20

【0147】

そして、最後に、電極部25, 26上および酸化シリコン層27上にある第1ギャップ形成マスク45および第2ギャップ形成マスク46を、例えばウェットエッチングにより除去することにより、図4に示したように、電極部25, 26間にナノギャップNGを有したナノギャップ電極21を形成し得る。

30

【0148】

以上の構成において、電極形成部31に対して配置した第1ギャップ形成マスク45の側壁45aにサイドウォール37を形成した後、サイドウォール37と隣接するように第2ギャップ形成マスク46を形成し、第1ギャップ形成マスク45および第2ギャップ形成マスク46間にサイドウォール37を配置する。そして、第1ギャップ形成マスク45、サイドウォール37、および第2ギャップ形成マスク46の各表面を外部に露出させ、サイドウォール37を除去することにより、第1ギャップ形成マスク45および第2ギャップ形成マスク46間に間隙49を形成し、当該間隙49内の電極形成部31を除去してナノギャップNGを形成する。

40

【0149】

このような本発明の製造方法では、サイドウォール37の膜厚を調整することで、所望の幅W1でなるナノギャップNGを形成し得、また、当該サイドウォール37の膜厚については極めて薄く形成し得ることから、サイドウォール37の幅に対応した極めて小さい幅W1のナノギャップNGをも形成し得る。また、この製造方法では、ナノギャップNGを形成する際、従来のように金属マスクをパターニングする必要もないため、その分手間もかからずナノギャップNGを形成し得る。

【0150】

以上の構成によれば、電極形成部31に対して配置されたサイドウォール37をマスク

50

として用い、サイドウォール37の膜厚により調整された幅W1のナノギャップNGを電極形成部31に形成するようにしたことにより、従来と同じ寸法の幅W1のナノギャップNGを形成し得る他、従来よりも一段と幅W1が小さいナノギャップNGをも形成し得る。

【0151】

なお、いくつかの実施形態では、図10Bに示すように、第1ギャップ形成マスク45上に第2ギャップ形成マスク46を直接形成するようにしもよい。本発明はこれに限らず、他の実施形態では、例えば、表面にハードマスクが形成された第1ギャップ形成マスク45を用い、第1ギャップ形成マスク45上に第2ギャップ形成マスク46を直接形成しなくてもよい。この場合でも、第1ギャップ形成マスク45および第2ギャップ形成マスク46間にサイドウォール37を配置でき、かくして、サイドウォール37を除去することで第1ギャップ形成マスク45および第2ギャップ形成マスク46間に間隙49を形成し得る。

10

【0152】

なお、本発明は、本実施形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形実施が可能である。例えば、電極部5,6(25,26)や、酸化シリコン層4(27)、サイドウォール11(37)等の部材については種々の部材を適用してもよい。また、第1電極形成部9や、第2電極形成部12、電極部5,6の形状については種々の形状としてもよく、電極形成部31や、電極部25,26の形状についても種々の形状としてもよい。

20

【0153】

例えば、カーボンナノチューブでなる電極形成部31を適用したが、本発明はこれに限らず、例えば単なる直方体状、円柱状等その他種々の形成でなる金属部材で電極形成部を形成してもよい。

【0154】

図6,7に関連した実施形態の製造方法について説明すると、電極形成部として、例えば直方体状の金属部材でなる電極形成部を適用した場合には、直方体状の電極形成部上に、開口部32aを有したレジストマスク32を設け、当該レジストマスク32の両側壁33a,33bに沿ってサイドウォール37を形成し、サイドウォール37間に露出した電極形成部を除去してサイドウォール37間にナノギャップNGを形成するとともに、当該ナノギャップNGを介して対向配置された直方体状の電極部を形成することができる。

30

【0155】

なお、図6~11を参照したように、酸化シリコン層27に隣接して電極支持部28,29を形成し、これら電極支持部28,29の表面に電極形成部31を設けるようにした場合について述べたが、本発明はこれに限らず、基板22内に電極支持部28,29が設けられていない、単なる酸化シリコン層の基板や、シリコン基板だけでなる基板上に、各種形状でなる電極形成部を設けるようにしてもよい。また、基板上に電極形成部を設け、当該電極形成部の両端側上部に電極支持部を突出形成し、基板上にて、対向するように配置された2つの電極支持部間に電極形成部を設けた構成としてもよい。

【0156】

さらに、上述した実施形態においては、電極部5,6(25,26)間のナノギャップNGに一本鎖DNAを通過させ、当該一本鎖DNAの塩基が電極部5,6(25,26)間のナノギャップNGを通過したときに電極部5,6(25,26)間に流れる電流値を電流計にて計測させるナノギャップ電極1(21)について述べたが、本発明はこれに限らず、その他種々の用途にナノギャップ電極を適用してもよい。本発明はこれらの実施例に限定されるものではない。ナノギャップ電極は、さまざまな他の用途にも用いることができるいくつかの態様において、ナノギャップは二本鎖DNAに対しても使用可能であり、従って、二重鎖DNAの測定に対しより適切とすることができる異なるディメンションを持つように製造される。他の実施形態では、ナノギャップは、他の生体分子は、アミノ酸、脂質または炭水化物などに利用することができるので、生体分子の種類ごとに、適切

40

50

な幅に加工されてもよい。

【0157】

また、図6～11を参照して、サイドウォールとして、頂点から酸化シリコン層27に向けて次第に幅広に形成されたサイドウォール11,37を適用した場合について述べたが、本発明はこれに限らず、例えば成膜条件（温度や、圧力、使用するガス、流量比等）を変えることで、コンフォーマルに成膜せずに場所により膜厚を変えたサイドウォール形成層を形成し、頂点から基板に向けて次第に幅狭に形成されたサイドウォールや、頂点および基板間の中間箇所等その他種々の箇所の幅が最大幅となるサイドウォールを適用してもよい。このように、次第に頂点から薄シリコン酸化膜に向かって形成されて側壁の幅を広くするには、一つの頂点とシリコン酸化膜との中間の位置、またはその他のさまざまな位置での最大幅を有してもよく、側壁に適用される膜であってもよい。

10

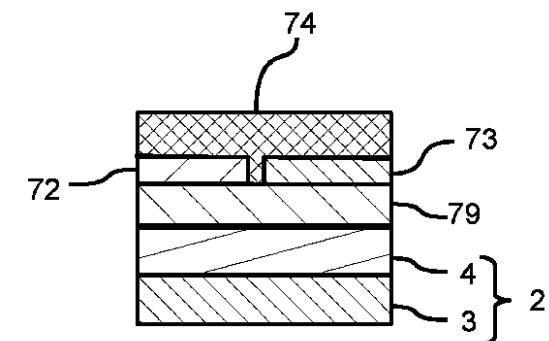

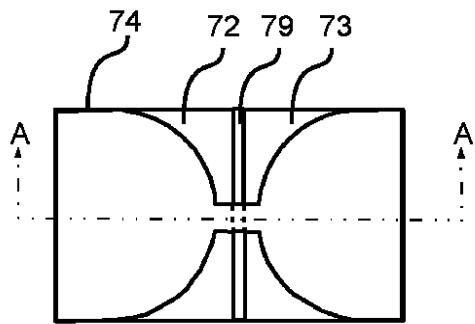

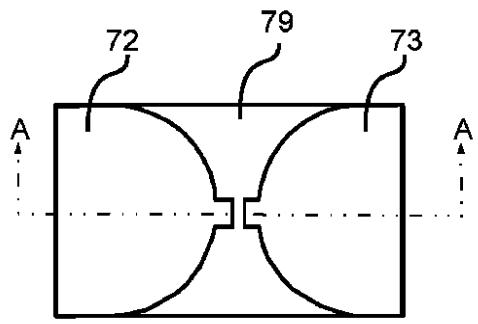

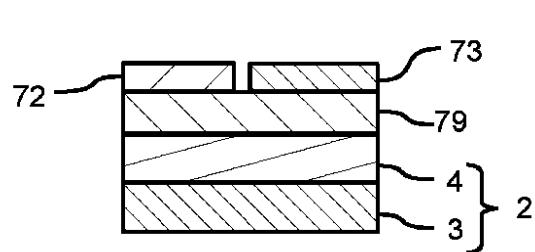

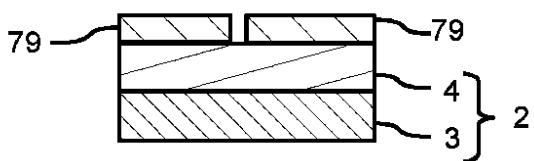

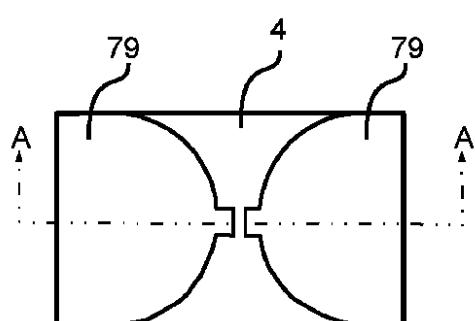

【0158】

本開示は、電極部5,6との間のナノギャップNGを有するナノギャップ電極1の製造方法について説明する。酸化シリコン層4をシリコン基板3上に形成することができる基板2に最初に用意することができる。その後電極形成層79を用いることができるが、例えばシリコンナイトライド(SiN)から成り、側壁72aを有する第1マスク72は、フォトリソグラフィ技術を用いて電極形成層79の所定領域上に形成することができる。

20

【0159】

次に、図12(a)に示すように、電極形成層79の表面（窒化チタンを含んでよい）の材料とは異なるチタン(Ti)など材料から作られたサイドウォール形成用層80は、電極形成部79と基板2の露出された部分上に、例えば化学的気相成長(CVD)法で膜として形成することができる。このとき、サイドウォール形成用層80は、第1マスク72の側壁72aに沿って形成されてもよい。側壁72a上に形成されるサイドウォール形成層80の膜厚は、ナノギャップNGの所望幅W1に応じて適宜選択することができる。つまり、小さい幅W1を有するナノギャップNGを形成する際に、サイドウォール形成用層80は薄い膜厚で形成される。逆に、大きな幅W1を有するナノギャップNGを形成する際に、サイドウォール形成用層80は大きな膜厚で形成されてもよい。

20

【0160】

次に、図12(b)に示すように、第1マスク72と電極形成層79の露出された部分上に成膜形成したサイドウォール形成用層80は、例えば、ドライエッチングによりエッチングし、第1マスク72の側壁72aに沿ってサイドウォール形成用層80の一部を残すことができる。エッチング工程は、基板2に対して垂直となるように構成されてもよいし、サイドウォール形成層80の部分は、第1のマスク72の側壁72aによるエッチングから少なくとも部分的に保護することができるような角度であってもよい。

30

【0161】

次に、図12(c)に示すように、第2マスク73を、例えばスパッタリング法によって堆積してもよい。

【0162】

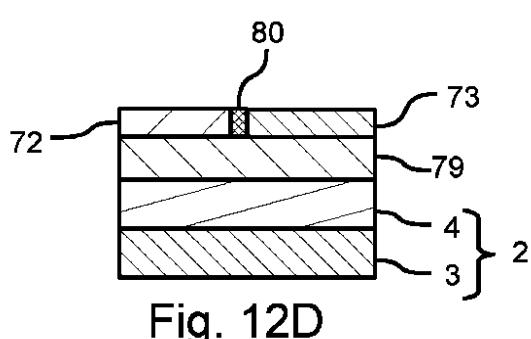

続いて、図12(d)に示すように、第1マスク72をサイドウォール形成用層80、及び第2のマスク73の領域が、CMP(化学機械研磨)法のような平坦化処理で研磨または過研磨してもよい。

40

【0163】

続いて、図13(断面図)及び図13(上面図)に示すようにレジストの層を塗布し、パターニングしてもよい。パターニングされたレジスト74により露出されて残された第1マスク72と第2マスク73の一部は、エッチング除去されてもよい。パタンドレジスト74は、図13C(断面図)及び図13D(平面図)に示すように、残りのマスク層を除去することができる。残った第1マスク72と残った第2マスク73は、電極形成層79をエッチングするのに使用してもよく、図1に示すような構造の作成する図13E(断面図)及び図13F(上面図)に示すように、後に取り除かれる。

40

【0164】

50

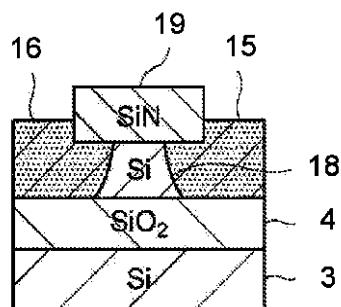

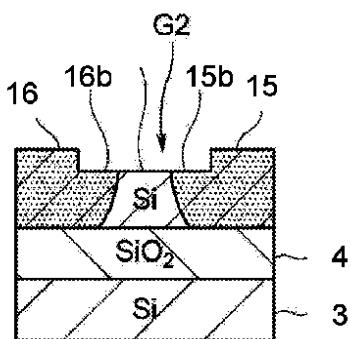

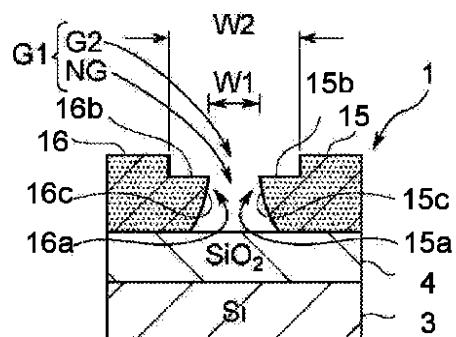

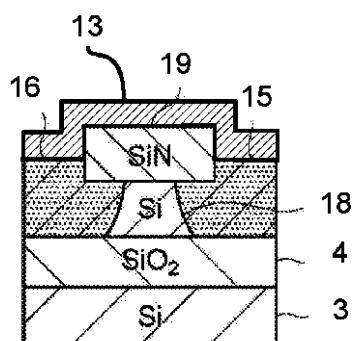

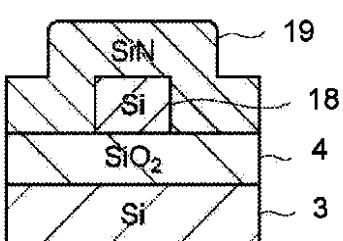

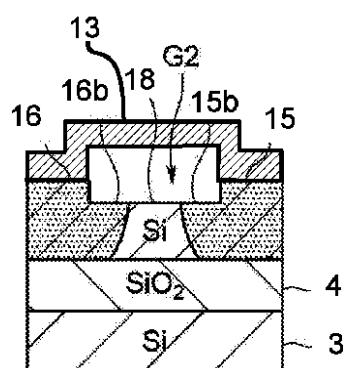

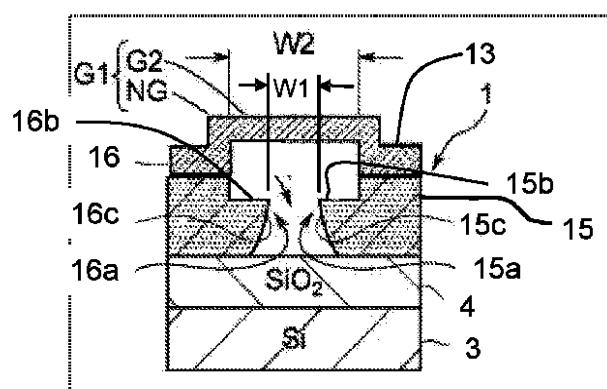

図14において、1は一実施形態による本発明のナノギャップ電極を示し、このナノギャップ電極1には、対向した電極部15,16が基板2上に設けられており、これら電極部15,16間に最小幅W1がナノスケール(1000[nm]以下)でなる中空状の間隙G1が形成されている。基板2は、例えばシリコン基板3と、当該シリコン基板3上に形成された酸化シリコン層4とから構成されており、当該酸化シリコン層4上に対となる2つの電極部15,16が形成された構成を有する。

#### 【0165】

いくつかの実施形態では、電極部15,16間に形成される間隙G1は、マスク幅間隙G2と、このマスク幅間隙G2の幅W2よりも幅狭なナノギャップNGとから構成されている。本発明のナノギャップ電極1は、製造過程で用いたマスク(後述する)により形成されるマスク幅間隙G2の幅W2よりも幅狭なナノギャップNGを形成し得る点に特徴を有しており、当該ナノギャップNGでの最小幅W1を0.1~30[nm]、10[nm]以下、5[nm]以下、2[nm]以下、1[nm]以下、0.5[nm]以下で、また、1.5~0.3[nm]、1.5~0.3[nm]、1.2~0.5[nm]、0.9~0.65[nm]、1.2~0.9[nm]、1.0~0.8[nm]、0.8~0.7[nm]で形成し得るようになされている。これらの幅は、ここで記載されたナノギャップのいずれに対してもギャップスペーシングに利用できる。

10

#### 【0166】

実際上、これら電極部15,16は、いずれもチタンシリサイド、モリブデンシリサイド、プラチナシリサイド、ニッケルシリサイド、コバルトシリサイド、パラジウムシリサイド、またはニオブシリサイド等その他種々の金属シリサイドにより形成されている。これら電極部15,16は、同一の構成を有しており、基板2上にナノギャップNGを中心に左右対称に形成され、一端の側壁15a,16aがナノギャップNGを介して対向配置されている。ある実施形態では、電極部15,16は、縦断面が四辺状で長手方向がy方向に伸びた直方体状からなり、電極部15,16の長手方向の中心軸が、y方向の同一直線上に配置され、側壁15a,16aの全面同士が対向するように配置されている。

20

#### 【0167】

また、電極部15,16の側壁15a,16aは、上方角部にL字状に凹んだ段部15b,16bが形成され、この段部15b,16bの底面部から下方へゆくに従ってなだらかに凹んだ裾引き状の曲面15c,16cが形成されている。これにより電極部15,16間に、四辺状のマスク幅間隙G2が段部15b,16b間に形成され、当該マスク幅間隙G2から基板2へゆくに従って両側の距離が次第に広がった裾引き状のナノギャップNGが曲面15c,16c間に形成され得る。

30

#### 【0168】

なお、他の実施形態では、マスク幅間隙G2とナノギャップNGとからなる間隙G1を電極部15,16間に形成するようにした場合について述べたが、本発明はこれに限らず、マスク幅間隙G2を形成している段部15b,16bを、例えばCMP(Chemic al Mechanical Polishing)で研磨し、ナノギャップNGのみを電極部15,16間に形成するようにしてもよい。

40

#### 【0169】

因みに、このような構成を有したナノギャップ電極1は、例えば図示しない電源から電極部15,16に電流が供給され得るようになされており、電極部15,16間の電流値が図示しない電流計により計測され得る。ナノギャップ電極1は、電極部15,16の長手方向たるy方向と、このy方向と直交する電極部15,16の高さ方向たるz方向とに直交するx方向から電極部15,16間のナノギャップNGに一本鎖DNAを通過させ、当該一本鎖DNAの塩基が電極部15,16間のナノギャップNGを通過したときに電極部15,16間に流れる電流値を電流計にて計測させてゆき、その電流値を基に一本鎖DNAを構成する塩基を同定させ得る。

#### 【0170】

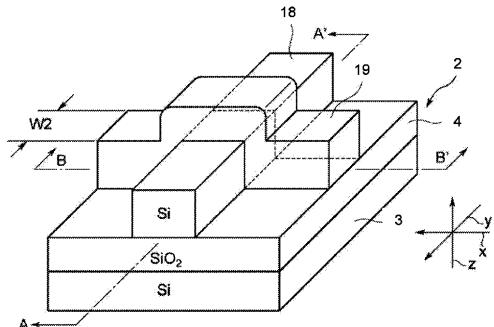

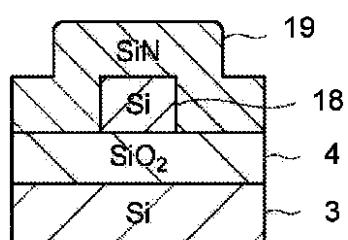

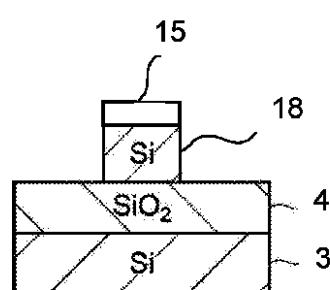

次にこのようなナノギャップ電極1の製造方法について説明する。いくつかの実施形態

50

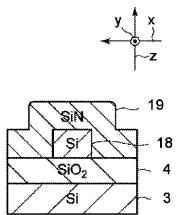

では、先ず始めに、図15に示すように、シリコン基板2上に酸化シリコン層4が形成された基板2を用意し、シリコンからなり、y方向に延びる長手方向を有した直方体状の電極形成部8を、フォトリソグラフィ技術を利用して酸化シリコン層3上に形成する。次いで、基板2上および電極形成部18上にシリコンナイトライド(SiN)でなるマスク層19(図示せず)を成膜した後、露光・現像によりパターニングしたレジストマスクを用いて当該マスク層19をパターニングしてマスクを形成する。

【0171】

これにより、電極形成部18の長手方向たるy方向と直交するx方向に向けて当該電極形成部18を跨ぐようにしてシリコンナイトライド(SiN)でなる直方体状のマスク層19を形成する。なお、マスク層19の幅W2は、後に電極部15,16を形成した際、これら電極部15,16間に形成されるマスク幅間隙G2となるため、使用態様に応じて、レジストマスクのパターニングを変えてマスク層19の幅W2を選定することが望ましい。

10

【0172】

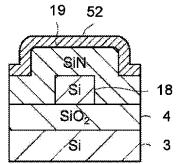

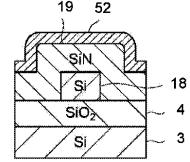

ここで、図15におけるA-A'部分の断面構成と、B-B'部分の断面構成とに着目してゆき、以下、ナノギヤップ電極1を製造する工程について説明する。この場合、図16Aは図15のA-A'部分の断面構成を示し、図16Bは図15のB-B'部分の断面構成を示す。図16Aとの対応部分に同一符号を付して示す図16Cと、図16Bとの対応部分に同一符号を付して示す図16Dのように、例えばスパッタリング等により、チタンや、モリブデン、プラチナ、ニッケル、コバルト、パラジウム、ニオブ等の金属元素でなるシリサイド生成層52をマスク層19および電極形成部18上に成膜する。なお、この際、マスク層19および電極形成部18以外の領域に露出している基板2上にもシリサイド生成層52が成膜され得る。

20

【0173】

次いで、熱処理を行うことにより、電極形成部18とシリサイド生成層52とを反応させ、図16Cとの対応部分に同一符号を付して示す図16Eと、図16Dとの対応部分に同一符号を付して示す図16Fとのように、シリサイド生成層52と接触している電極形成部18をシリサイド化させることにより金属シリサイドでなる電極部15,16(図16E)を形成する。

30

【0174】

ある場合には、電極形成部18では、図16Eに示すように、シリサイド生成層52が成膜されていないマスク層19との対向領域でシリサイド化し難いものの、マスク層19の両側部側からマスク層19の下部領域に向けてシリサイド生成層52の金属元素が拡散してゆき、シリサイド生成層52と直接接触していないマスク層19の両側部付近の下部領域でもシリサイド化が進み、マスク層19の両側部側から下部領域に向けて入り込んだ電極部15,16が形成され得る。この場合、電極部5,6は、シリサイド生成層52の金属元素がマスク層19の両側部付近から下部領域に向けて拡散してシリサイド化することでマスク層19の下部領域に形成されるとともに、当該シリサイド化する際に、シリサイド生成層52の金属元素が電極形成部18内で拡散した領域部分の体積よりも膨張(体積膨張)することから、その分、マスク層19の下部領域において電極部15,16の側壁15a,16a(具体的には、曲面15c,16c)同士がマスク層19の幅W2よりも近接した状態となり得る。

40

【0175】

また、この場合、電極形成部18は、酸化シリコン層4まで到達するまでシリサイド化が進み、当該酸化シリコン層4に接触した電極部15,16が形成され得る。このような電極部15,16は、電極形成部18の膜厚や、シリサイド生成層52の膜厚、熱処理時における温度や加熱時間等を適宜選定することにより、マスク層19の下部領域での電極部15,16の側壁15a,16a(曲面15c,16c)位置を制御でき、側壁15a,16a間の最小幅W1を、例えば0.1~30[nm]、或いはここで記載された如何なる幅でもに形成し得るとともに、曲面15c,16cの裾引きの程度を制御し得る。

50

## 【0176】

次いで、図16Eとの対応部分に同一符号を付して示す図17Aと、図16Fとの対応部分に同一符号を付して示す図17Bどのように、マスク層19や酸化シリコン層4上に残存した未反応のシリサイド生成層52を、エッティングにより除去した後、図17Aとの対応部分に同一符号を付して示す図17Cと、図17Bとの対応部分に同一符号を付して示す図17Dどのように、エッティングによりマスク層19を除去して電極部15, 16の段部15b, 16b間にマスク幅間隙G2を形成する。

## 【0177】

なお、例えばシリサイド生成層52をコバルトにより形成した場合には、電極部15, 16はコバルトシリサイド(CoSi)となり、その後、硫酸(H<sub>2</sub>SO<sub>4</sub>)と過酸化水素(H<sub>2</sub>O<sub>2</sub>)の混合液を用いたウェットエッティングによって、マスク層19上および酸化シリコン層4上に残存した未反応のシリサイド生成層52を除去し得る。

10

## 【0178】

いくつかの実施形態では、図17Cとの対応部分に同一符号を付して示す図17Eと、図17Dとの対応部分に同一符号を付して示す図17Fどのように、酸化シリコン層4上の電極部15, 16間に残存した未反応の電極形成部18をエッティング等により除去し、電極部15, 16の裾引き状の曲面15c, 16cを外部に露出させて曲面15c, 16c間に中空状のナノギャップNGを形成することにより、図14に示すようなナノギャップ電極1を製造し得る。

20

## 【0179】

以上の構成において、基板2上にある電極形成部18上に、ある幅に選定されたマスク層19を形成し、電極形成部18上にシリサイド生成層52を成膜した後、熱処理を行うことにより、シリサイド生成層52と電極形成部18とを反応させ、反応により生じる体積膨張によってマスク層19の下部領域まで入り込んだ対向する2つの電極部15, 16を形成し、電極部15, 16の側壁15a, 16a同士を体積膨張によってマスク層19の幅よりも近接させる。そして、マスク層19を除去するとともに、マスク層19の下部領域に残存した未反応の電極形成部18を除去することにより電極部15, 16間にナノギャップNGを形成し得、かくして、パターニングしたマスク層19で形成されるマスク幅間隙G2よりも、さらに一段と小さいナノギャップNGを有するナノギャップ電極1を製造できる。

30

## 【0180】

また、このようなナノギャップ電極1では、製造過程において、電極形成部18の膜厚およびシリサイド生成層52の膜厚を適宜選定するとともに、電極形成部18をシリサイド化させる熱処理時間および加熱温度を適宜選定するだけで、電極部15, 16がマスク層19の両側部から下部領域に入り込む程度を制御でき、マスク層19のマスク幅間隙G2よりもさらに幅狭なナノギャップNGを容易に形成し得る。また、このような製造方法では、マスク層19を使用した際に技術的に形成可能な最小幅のマスク幅間隙G2よりも幅狭なナノギャップNGを電極部15, 16間に形成することができる。

## 【0181】

例えば、あるナノギャップ電極の製造方法としては、露光・現像によりパターニングしたレジストマスクを用いて電極層を直接エッティングして、対向した2つの電極部間にナノギャップを形成してもよい。この場合、露光・現像によってレジストマスクに形成し得る最小幅は、一般的に10[nm]程度であることから、これよりも小さい幅のナノギャップを形成することが困難であった。

40

## 【0182】

これに対して、本発明のいくつかの実施形態に係るナノギャップ電極の製造方法では、製造過程において、仮に従来と同様に露光・現像によってレジストマスクに形成し得る最小幅W2が10[nm]であり、これに伴いマスク層19の最小幅W2が5~10[nm]となつたとしても、その後の製造工程により、マスク層19の下部領域で体積膨張によって電極部15, 16の側壁15a, 16a同士が近接してゆくことから、5~10[nm]

50

m] の最小幅 W 2 よりも小さい 2 [nm] 以下や、 1 [nm] 以下、 0.9 [nm] 以下、 0.8 [nm] 以下、 0.7 [nm] 以下、 0.6 [nm] 以下、 0.5 [nm] 以下、 またはここで述べた如何なるギャップスペーシングのナノギャップ NG を形成し得る。

【0183】

以上の構成によれば、電極形成部 18 にシリサイド生成層 52 を成膜した後に熱処理を行い、電極形成部 18 とシリサイド生成層 52 とを反応させ、体積膨張した対向する 2 つの電極部 15, 16 を生成し、体積膨張によって電極部 15, 16 の側壁 15a, 16a 同士を近接させて、電極部 15, 16 間にナノギャップ NG を形成するようにしたことにより、シリサイド化した分だけ電極部 15, 16 間のマスク幅間隙 G2 を小さくでき、かくして、加工により形成された間隙よりも、さらに一段と小さいナノギャップ NG を有するナノギャップ電極 1 を製造できる。

10

【0184】

また、このような製造方法では、電極部 15, 16 の対向する側壁 15a, 16a 同士が次第に近接してゆく曲面 15c, 16c を形成し得、当該曲面 15c, 16c によって側壁 15a, 16a 間の幅が徐々に幅狭になっているナノギャップ電極 1 を製造できる。

【0185】

なお、いくつかの実施形態においては、酸化シリコン層 4 と接するように電極部 15, 16 を形成した場合について述べたが、本発明はこれに限らず、酸化シリコン層 4 と接するように電極部 15, 16 を形成する必要はなく、酸化シリコン層 4 と電極部 15, 16 との間に未反応の電極形成部 18 が形成されていてもよい。この場合、電極形成部 18 やシリサイド生成層 52 の膜厚、電極形成部 18 をシリサイド化させる際の熱処理時間および温度を適宜選定することにより、酸化シリコン層 4 と電極部 15, 16 との間に未反応の電極形成部 8 を残存させることができる。

20

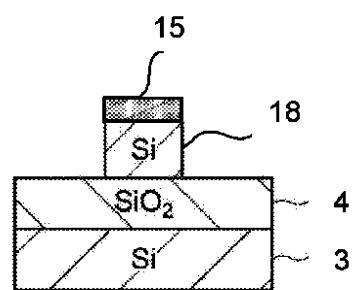

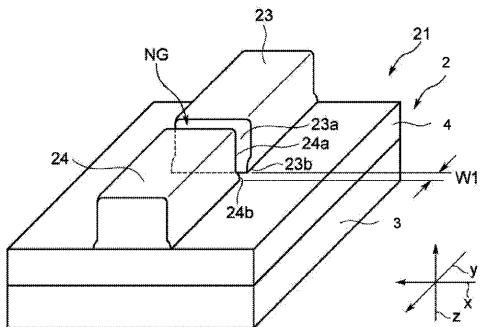

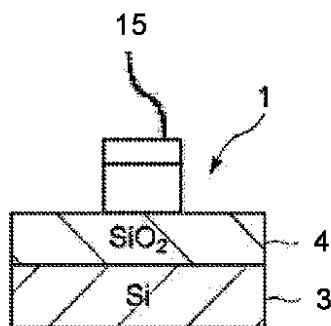

【0186】

図 14 との対応部分に同一符号を付して示す図 18 に示される実施形態では、ナノギャップ電極 21 が示されている。最小幅 W1 がナノスケール (1000 [nm] 以下) でなるナノギャップ NG が電極部 23, 24 間に形成された構成を有する。この実施形態によるナノギャップ電極 21 でも、製造過程においてマスクにより形成されるマスク幅間隙の幅よりも幅狭なナノギャップ NG を形成し得る点に特徴を有しており、当該ナノギャップ NG での最小幅 W1 を 0.1 ~ 30 [nm]、さらには使用態様に応じて 2 [nm] 以下、1 [nm] 以下、0.9 [nm] 以下、0.8 [nm] 以下、0.7 [nm] 以下、0.6 [nm] 以下、0.5 [nm] 以下、或いはここで述べた如何なる幅で形成し得るようになされている。

30

【0187】

電極部 23, 24 は、いずれもチタンシリサイド、モリブデンシリサイド、プラチナシリサイド、ニッケルシリサイド、コバルトシリサイド、パラジウムシリサイド、またはニオブシリサイド等その他種々の金属シリサイドにより形成されてもよい。電極部 23, 24 は、同一の構成を有しており、基板 2 上にナノギャップ NG を中心に左右対称に形成され、一端の側壁 23a, 24a がナノギャップ NG を介して対向配置されている。いくつかの実施形態では、電極部 23, 24 は、縦断面が四辺状で長手方向が y 方向に延びた直方体状からなり、電極部 23, 24 の長手方向の中心軸が、y 方向の同一直線上に配置され、側壁 23a, 24a の全面同士が対向するように配置されている。

40

【0188】

いくつかの実施形態では、電極部 23, 24 の側壁 23a, 24a には、基板 2 と接する領域に、外部に向けて膨らんだ膨出部が形成されている。これにより、電極部 23, 24 は、膨出部 23b, 24b の対向領域で、これら電極部 23, 24 間に形成されるナノギャップ NG の幅を、更に一段と幅狭に形成し得、最小幅 W1 とし得る。

【0189】

いくつかの実施形態では、ナノギャップ電極 21 でも、例えば図示しない電源から電極部 23, 24 に電流が供給され得るようになされており、電極部 23, 24 間の電流値が

50

図示しない電流計により計測させ得る。ナノギャップ電極 21 は、電極部 23, 24 の長手方向たる y 方向と、この y 方向と直交する電極部 23, 24 の高さ方向たる z 方向とに直交する x 方向から電極部 23, 24 間のナノギャップ NG に一本鎖 DNA を通過させ、当該一本鎖 DNA の塩基が電極部 23, 24 間のナノギャップ NG を通過したときに電極部 23, 24 間に流れる電流値を電流計にて計測させてゆき、その電流値を基に一本鎖 DNA を構成する塩基を同定させ得る。

#### 【0190】

いくつかの実施形態によるナノギャップ電極 21 の製造方法について説明する。先ず始めに、シリコン基板 4 上に酸化シリコン層 3 が形成された基板 2 を用意し、当該酸化シリコン層 3 上にシリコン層を形成する。次いで、このシリコン層上にレジスト層を成膜した後、露光・現像によりレジスト層をパターニングしてマスク（レジストマスク）を形成する。

10

#### 【0191】

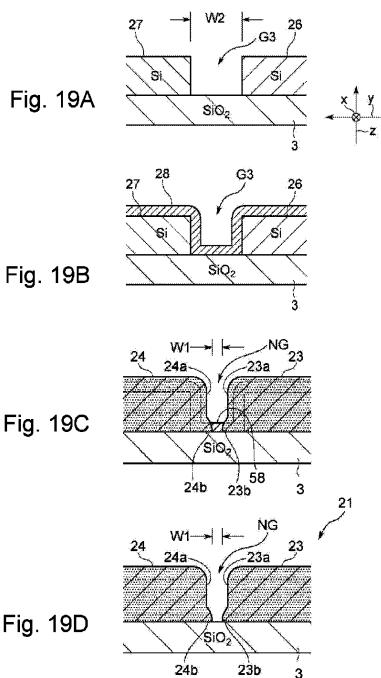

次いで、マスクによってシリコン層をパターニングし、図 19 A に示すように、マスク幅間隙 G3 を介して対向した 2 つの電極形成部 26, 27 をシリコン層から形成する。なお、この場合、電極形成部 56, 57 は、y 方向に延びる長手方向を有した直方体状に形成され、長手方向の中心軸が同一直線上に位置し、マスク幅間隙 G3 を介して側壁同士が対向配置された構成を有する。さらに、電極形成部 56, 57 は、長手方向の中心軸が同一直線上に配置され、電極形成部 56, 57 の側壁の全面同士がマスク幅間隙 G3 を介して対向するように配置されている。

20

#### 【0192】

いくつかの実施形態では、図 19 A との対応部分に同一符号を付して示す図 19 B のように、例えばスパッタリング等により、チタンや、モリブデン、プラチナ、ニッケル、コバルト、パラジウム、ニオブ等の金属元素でなるシリサイド生成層 58 を電極形成部 56, 57、および露出した酸化シリコン層 4 上に成膜してもよい。次いで、熱処理を行うことにより、電極形成部 56, 57 とシリサイド生成層 58 とを反応させ、図 19 B との対応部分に同一符号を付して示す図 19 C のように、シリサイド生成層 58 と接触していた電極形成部 56, 57 をシリサイド化することにより金属シリサイドでなる電極部 23, 24 を形成する。

30

#### 【0193】

ここで、電極部 23, 24 は、シリサイド化した際に体積膨張して側壁 23a, 24a 同士が近接してゆき、その分、マスクにより形成したマスク幅間隙 G3 よりも幅狭のナノギャップ NG を形成し得る。また、この際、電極形成部 56, 57 の基板 2 と接した領域では、他の領域と比べて過剰なシリサイド生成膜 58 があることから、当該シリサイド生成膜 58 との間でシリサイド化が進み、その結果、電極部 23, 24 が生成される際、より体積膨張した膨出部 23b, 24b が形成され得る。かくして、電極部 23, 24 は、基板 2 と接した領域に対向配置された膨出部 23b, 24b により、ナノギャップ NG の幅を更に一段と幅狭に形成し得る。

#### 【0194】

このようにして形成される電極部 23, 24 は、電極形成部 56, 57 の膜厚や、シリサイド生成層 58 の膜厚、熱処理時における温度や加熱時間等を適宜選定することにより、電極部 23, 24 の側壁 23a, 24a 位置や、膨出部 23b, 24b の膨出程度を制御でき、側壁 23a, 24a 間の幅や、膨出部 23b, 24b 間の最小幅 W1 を、例えば 0.1 ~ 30 [nm]、或いは 2 [nm] 以下、1 [nm] 以下、0.9 [nm] 以下、0.8 [nm] 以下、0.7 [nm] 以下、0.6 [nm] 以下、0.5 [nm] 以下、或いは、ここで記載された如何なるギャップスペーシングに形成し得る。

40

#### 【0195】

次いで、図 19 C との対応部分に同一符号を付して示す図 19 D のように、ナノギャップ NG 内や他の領域において酸化シリコン層 4 上に残存した未反応のシリサイド生成層 58 を、エッティングにより除去し、図 18 に示すように、電極部 23, 24 間にナノギャップ

50

PGN を有したナノギャップ電極 21 を製造し得る。

【0196】

以上の構成において、間隙（マスク幅間隙 G3）を介して対向配置された 2 つの電極形成部 56, 57 を基板 2 上に形成し、これら電極形成部 56, 57 上にシリサイド生成層 58 を成膜した後、熱処理を行うことにより、シリサイド生成層 58 と電極形成部 56, 57 とを反応させ、反応によって体積膨張した対向する 2 つの電極部 23, 24 を形成する。これにより、電極部 23, 24 の側壁 23a, 24a 同士を体積膨張によって近接させ、製造過程で形成したマスク幅間隙 G3 よりも小さいナノギャップ NG を電極部 23, 24 間に形成し得、かくして、パターニングしたマスクで形成されるマスク幅間隙 G3 よりも、さらに一段と小さいナノギャップ NG を有するナノギャップ電極 21 を製造できる。

10

【0197】

いくつかの実施形態では、ナノギャップ電極 21 は、製造過程において、電極形成部 56, 57 の膜厚およびシリサイド生成層 58 の膜厚を適宜選定するとともに、電極形成部 56, 57 をシリサイド化させる熱処理時間および加熱温度を適宜選定するだけで、電極部 23, 24 の体積膨張する程度を制御でき、マスクのマスク幅間隙 G3 よりもさらに幅狭なナノギャップ NG を容易に形成し得る。また、このような製造方法では、マスクを使用した際に技術的に形成可能な最小幅のマスク幅間隙 G3 よりも幅狭なナノギャップ NG を電極部 23, 24 間に形成することができる。

20

【0198】

いくつかの実施形態では、電極形成部 56, 57 にシリサイド生成層 58 を成膜した後に熱処理を行い、電極形成部 56, 57 とシリサイド生成層 58 とを反応させ、体積膨張させた対向する 2 つの電極部 23, 24 を生成し、当該体積膨張によって電極部 23, 24 の側壁 23a, 24a 同士を近接させて、電極部 23, 24 間にナノギャップ NG を形成するようにしたことにより、体積膨張した分だけ電極部 23, 24 間のマスク幅間隙 G3 を小さくでき、かくして、製造過程において加工により形成された間隙よりも、さらに一段と小さいナノギャップ NG を有するナノギャップ電極 21 を製造できる。

20

【0199】

いくつかの実施形態では、電極部 23, 24 の対向する側壁 23a, 24a 同士が次第に近接してゆく膨出部 23b, 24b を形成し得、当該膨出部 23b, 24b によって側壁 23a, 24a 間の幅が徐々に幅狭になっているナノギャップ電極 21 を製造できる。

30

【0200】

なお、本発明は、本実施形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形実施が可能であり、例えば電極部 15, 16 (23, 24) の形状は種々の形状としてもよい。また、上述した実施形態においては、シリコンでなる電極形成部 18 (26, 57) を設け、チタンや、モリブデン、プラチナ、ニッケル、コバルト、パラジウム、ニオブ等の金属元素のシリサイド生成層 52 (28) を当該電極形成部 18 (56, 57) に成膜した後に熱処理を行い、電極形成部 18 (56, 57) とシリサイド生成層 52 (28) とを反応させ、金属シリサイドからなる体積膨張した 2 つの電極部 15, 16 (23, 24) を生成するようにした場合について述べたが、本発明はこれに限らず、チタンでなる電極形成部を設け、タンゲステンでなる化合物生成層を当該電極形成部に成膜した後に熱処理を行い、電極形成部と化合物生成層とを反応させ、チタンタンゲステンからなる体積膨張した 2 つの電極部を生成し、体積膨張させた分だけ側壁同士を近接させて電極部間にナノギャップを形成するようにしてもよい。チタンやタンゲステン以外の材料も使用することができる。

40

【0201】

また、上述した実施形態においては、電極部 15, 16 (23, 24) 間のナノギャップ NG に一本鎖 DNA を通過させ、当該一本鎖 DNA の塩基が電極部 15, 16 (23, 24) 間のナノギャップ NG を通過したときに電極部 15, 16 (23, 24) 間に流れ电流値を電流計にて計測させるナノギャップ電極 1 (21) について述べたが、本発明

50

はこれに限らず、その他種々の用途にナノギャップ電極を適用してもよい。

【0202】

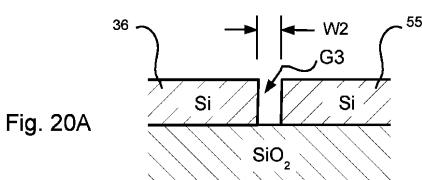

いくつかの実施形態によるナノギャップ電極21の製造方法について説明する。先ず始めに、シリコン基板4上に酸化シリコン層3が形成された基板2を用意し、当該酸化シリコン層3上にシリコン層を形成する。次いで、このシリコン層上にレジスト層を成膜した後、露光・現像によりレジスト層をパターニングしてマスク（レジストマスク）を形成する。

【0203】

次いで、シリコン層は、マスクを用いてパターニングしてもよい。図20(a)に示すように、マスク幅間隙G3を介して相互に対向する2つの電極形成部55および36は、シリコン層から形成することができる。この場合においては、電極形成部55および36は、矩形のまたはy軸に平行に延びる長軸方向を有するソリッド形状に形成されてもよい。

また、電極形成部55および36は、それらの長辺の中心軸が同一直線上に配置するように、かつ電極形成部55および36のサイドウォールがマスク幅間隙G3を挟んで対向するように、配置されてもよい。

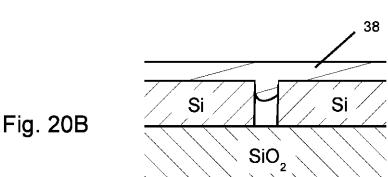

【0204】

次いで、図20(a)の対応部分に同一の符号を付した図20(b)に示すように、シリサイド生成層38は、チタン、モリブデン、プラチナ、ニッケル、コバルト、パラジウム、ニオブ、または任意の他の遷移金属や、これらの組合せ又はこれらの合金などの金属元素から形成されてよく、たとえばスパッタリングにより電極形成部55及び36上に成膜される。いくつかの実施態様において、スパッタリングは角度を付けて実施されることがある。マスク幅間隙G3の狭さのためシリサイド生成層38が底に達しない可能性がある。

【0205】

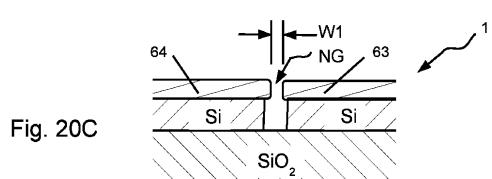

次いで、シリサイドまたはポリサイドプロセス中であってもよいが、シリサイド生成層38と電極形成部分55および36を反応させるために、熱処理を行ってもよい。次いで、ナノギャップNGおよび他の領域内の酸化シリコン層4上の残りのシリサイド生成層38の未反応部分は、エッティングにより除去することができる。そのため、図20Bの対応部分に同一の符号を付している図20Cが示すように、シリサイド生成層38と接触するようになっている電極形成部55および36は、金属シリサイド等から作られるシリサイド電極63および64を形成する。

【0206】

したがって、電極63および64のサイドウォールは、体積膨張によって互いに近接し、それにより、電極63と64の間のナノギャップNGを形成する。したがって、体積膨張量により電極23及び24の間のマスク幅間隙G3を小さくすることができる、通常のリソグラフィで形成される間隙よりも小さいナノギャップNGを有するナノギャップ電極1を製造することが可能である。

【0207】

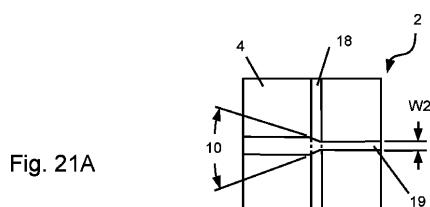

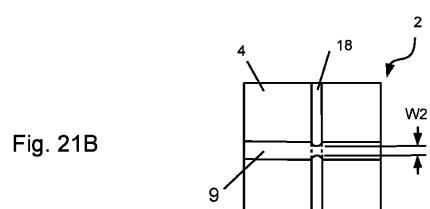

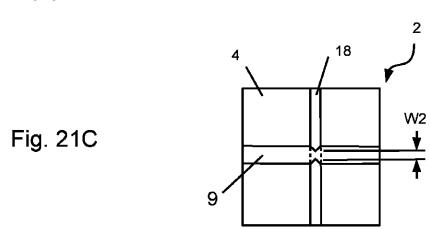

いくつかの実施態様において、非矩形形状のマスク層19を用いることが望ましい場合がある。これは、ナノギャップNGの点または垂直方向のエッジを作成するので単一ベース測定を容易にする。図21A-21Cは、最小マスク寸法がマスク幅間隙G2に対応する幅W2である、3の異なるマスクのバリエーションの上面図を示す。図21Aに示すように一実施形態では、そのマスクは、電極形成部18に台形状のギャップ膜を作成する。いくつかの実施形態において、台形角10は、10度以上、30度以上、60度以上となり得る。いくつかの実施形態において、シリコンへの金属の拡散により形成されたシリサイドは、平面状のエッジと言うより曲線状エッジを有する電極になるが、それでも最小ギャップ距離G2を有することができる。本発明は図21A-21Cに示されているマスクのバリエーションに限られない。

【0208】

10

20

30

40

50

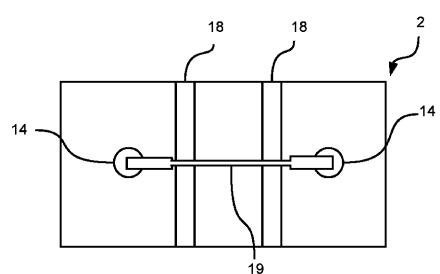

図 20 A - 20 F の対応部分に同一の符号を付した図 22 A - 22 F に示されるいくつかの実施形態では、ナノギャップ電極に標的種（例えば、DNA または RNA のような生体分子）をもたらすため小さなチャネルを形成することが望ましい場合がある。マスク層 19 は、このチャネルを形成するように設計することができるので、処理中にエッティングすることができる。図 22 A, 22 C および 22 E は、チャネルトップ層 13 の追加を示している。チャネルトップ層 13 は、わかりやすいように図 22 B, 22 D, 22 E に示されていません。いくつかの実施形態においては、チャネルトップ層は、SiO<sub>2</sub> のような製造方法と互換性のある非導電性材料であってもよいし、ポリジメチルシロキサンまたは SU8 などのポリマーであってもよい。

## 【0209】

10

図 23 に示すようにいくつかの実施形態では、マスク層 19 のエッティングを可能にするために、チャネルトップ層 13 は、少なくとも 1 つのチャネルアクセスポート 14 を堆積させることができる。図 23 において、2 つのチャンネルアクセスポート 14 の上面図が示される。いくつかの実施形態では、マスク層 19 の幅と厚さは、除去する際一つまたは複数のチャネルを形成することができるマスク軸の軸によって可変にすることができる。いくつかの実施形態において、複数の電極対は、チャンネル毎に配置してもよい。

## 【0210】

20

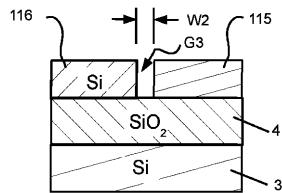

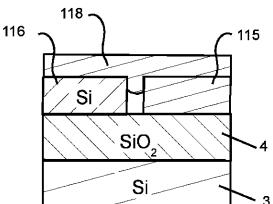

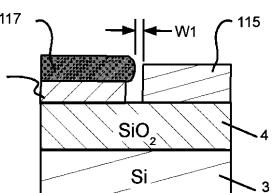

図 24 A - 24 B に示すようにいくつかの実施形態において、シリサイド膨張が片側からのみ行われることがある。いくつかの実施形態において、電極形成部 116 と金属電極 115 を製作することができる。次いで、シリサイド生成層 118 は、スパッタリング法などを用いて成膜することができる。図 24 A に示すように、間隙 W2 は、シリサイド生成層 118 が間隙 W2 の底を伝わらないような十分に狭くてもよい。金属電極 115 の金属は、シリサイド生成層 118 に対して選択することができ、シリサイド生成層 118 は金属電極 115 に影響を与えずにエッティングされうる。

## 【0211】

次いで、シリサイド層 118 と電極形成部 116 を反応させて電極 117 を形成するため、熱処理を行ってもよい。ナノギャップ NG 内および他の領域の酸化シリコン膜 4 上に残存するシリサイド生成層 118 の未反応部分は、エッティングにより除去することができる。図 24 B に示すように、シリサイドの膨張は、マスク幅 W2 よりも狭い幅 W1 の間隙を作成することができる。

30

## 【0212】

いくつかの実施形態では、得られたシリサイドは、導電性であってもよい。形成されたシリサイドを、サリサイドプロセスまたはポリサイドプロセスのような自己整合プロセスで形成することができる。複数のシリサイドの生成プロセスは、同じ電極形成要素が、例えば、電極や電極先端部を形成するために、電流により、配線電極の先端を通過可能に接続し、オペアンプや測定装置を通過するように相互接続するために利用してもよい。相互接続は、バイアス電位を適用することにも利用でき、バイアス供給源に由来する相互接続によって運ばれ、サリサイドプロセスを用いて形成されたシリサイド材料で形成される電極に適用することができる。

## 【0213】

40

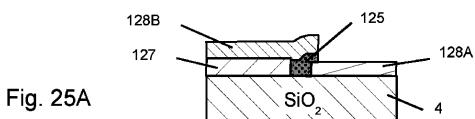

いくつかの実施形態では、シリサイド膨張は、垂直ナノギャップを作成することができる。電極形成部 125 と第 1 シリサイド発生電極 128 a は、図 25 A に示すように SiO<sub>2</sub> で被覆されたウェハ上に最初に製造されてもよい。これは、SiO<sub>2</sub> 等の誘電体層 127 に続いても良く、次いで第 2 シリサイド発生電極 128 b を堆積させることができる。これは、図 25 B に示す。

## 【0214】

50

次いで、図 25 C に示すように熱処理することにより、シリサイドの生成層 128 a, 128 b と電極形成部 125 を反応させててもよい。電極形成部 125 の未反応部分は、エッティング除去され得る。これは、電極形成部 125 の残渣の除去により作り出された流体チャネルを提供した誘電性カバー 129 によって 1 つまたは複数の軸孔（図示せず）が含

まれる。完成した断面が図 25D に示されている。

#### 【0215】

場合によっては、パターン化されたマスクを用いて形成されたマスク幅ギャップ G2、G3 は、ナノギャップ NG を形成する際の処理によって以前に形成された間隙を適用することができる。本発明はこれらの実施例に限定されるものではない。一実施形態では、間隙がパターニングされたマスク層 19 をマスク幅間隙 G2 を形成することによって形成してもよく、その後マスク層 19 の間隙を制御するためのマスクパターンをトリミングする。別の実施形態では、間隙は、例えば、電極形成部分 56 及び 57 の間に間隙を蒸着により狭めることにより、又は種々の他のタイプのプロセスによって形成することができる。本発明では、その間隙は、電極部の体積膨張量を小さくすることができる。そのため、通常のリソグラフィで形成される間隙よりもさらに小さいナノギャップ NG を有するナノギャップ電極を製造することができる。

10

#### 【0216】

いくつかの実施態様において、ナノチャネルはより小型にすることができる、小型化は、チャネルの幅又は溝深さの減少であってもよいし、幅と溝の深さ両方の減少であってもよい。いくつかの実施形態において、いくつかの実施例では、チャネルの幅および深さの一方又は双方を限定するために利用され得る。

#### 【0217】

いくつかの実施形態において、チャネルの幅及び深さは、ナノギャップを形成するのに使用されるのと同じかまたは類似したプロセスにより減少する場合がある。場合によっては、別のプロセスの操作は、チャネルの幅および深さを減らすのに用いられている。いくつかの実施形態において、チャネルの幅及び深さを減少させるために利用される材料は、非伝導性とみなすことができ、材料は露出され、チャネルの壁を形成することができる。

20

#### 【0218】

他の実施形態において、チャネルの幅及び深さを減少させるために利用される材料が導体とみなすことができるが、チャネルの通常の使用によってチャネルを通過する生体分子の電気泳動輸送の利用が含まれる可能性がある干渉を防止するように、非導電性材料が、導電性材料の上に重ね合わせられてもよい。チャネルを利用される導電性材料を被覆する絶縁体として用いることができる材料は、SiO<sub>2</sub>、または半導体プロセスにおいて典型的に用いられる他の酸化物を含むことができる。

30

#### 【0219】

他の実施例では、導体とみなすことができる材料はチャネルの幅および深さを減少するために利用され得るが、チャネルの異なる部分が、チャネルの幅を小さくして使わないままになる場合があり、それによって、タンパク質移行のための電気泳動による干渉を防ぐ導電性材料を分割する。

#### 【0220】

他の実施形態において、チャネルの幅及び深さを減少させるために利用される材料は、チャネルの一部区間などで利用されることがある。たとえば、チャネルの幅及び深さを減少させるために利用される材料は、ナノギャップ電極の近くでのチャネルの幅および深さを減少させるためにも使用可能である。チャネルを通じて転位する分子とチャネルと通して尋問するように配置することができるナノギャップ電極との間に通過して輸送される生体分子間相互作用の確率を高めるためである。チャネルの幅及び深さを減少させるために利用される材料は、ナノギャップ電極に隣接する二次構造の形成を防止するために、ナノギャップに十分近い位置でチャネルの幅および深さを低減するために利用することができる。

40

#### 【0221】

いくつかの実施形態において、特にナノチャネルの幅および深さを減少させるために利用される材料が非導体である場合には、チャネルの幅及び深さを減らすために用いられる材料は、ナノギャップ電極を形成するために用いられる材料を並置する。他の実施形態では、ナノギャップの幅や深さを減少させるために利用される材料が導体とみなすことができ

50

きるが、スペーサ要素は電極とチャネルの幅及び深さを狭くするために使用された材料をの間にあることが好ましい。

【0222】

電極とチャネルの幅及び／又は奥行きを狭くするために利用される導電性材料を使用するスペーサ要素は、少なくとも部分的には、チャネル構造の中に配置する非導電性材料を含んでもよく、あるいは、チャネルの幅及び深さの減少後に除去可能な導電性または非導電性材料を含んでもよい。

【0223】

いくつかの実施形態において、チャネルの両側を狭めることが可能であるが、他の実施形態において、チャネルの片側で狭くすることができる。

10

【0224】

いくつかの実施形態では、図3Eに示すように、サイドウォール11が形成され、電極5、6を形成したTiNの各層は、サイドウォール11の側壁をエッチバックしてもよいし、側壁（サイドウォール）は、本明細書に記載した任意の技術を使用して拡大されてもよい。非導電体を適用することができ、これは、側壁11、電極5と6との間、およびナノチャネル壁（図示せず）で埋めることができる。非導電体は、SiO<sub>2</sub>、低圧CVD（LPCVD）または超低真空CVD（ULPCVD）を含むCVD、マイクロ波CVDあるいはプラズマ強化CVD、原子層CVD、原子層蒸着（ALD）あるいはプラズマALDなどのプラズマ法、気相エピタキシ、または他の任意の適切な製作法のような標準的な半導体プロセスを利用することで発生するものを含んでもよい。構造は、研磨（例えば、CMPを使用することにより）し、オーバーポリッシュをして、チャネルに対して希望の深さを設定してもよい。

20

【0225】

図8Aに示すように、他の実施形態では、サイドウォール37は半導体製造フィーチャーの寸法に対応する幅で形成され得、レジストマスクをマスクレイヤは、サイドウォール形成用マスク40、サイドウォール37、電極支持部29と、電極形成部31の上に配置することができる。付加的な層は、サイドウォール37に加えても、チャネルの幅に相当する厚さを増大することができる。

30

【0226】

狭ナノギャップ作製を描いた図17A～17Fに示されるものに類似したいくつかの実施形態では、膨張された電極部15および16は、電極形成部18と同様に、チャネルの長さを延長すると、電極部との間及び隣接するチャネルの断面で資料を利用してチャネル狭め材料に接触するのを防止することができる。電極形成部のシリサイド化の方法とチャネルを狭くするために使用する類似した材料はそれぞれ電極ギャップを狭める。マスク層19は、第2の導電性材料との間に電気的絶縁バリアを提供し、チャネルに沿った種々の位置に配置され得る異なる電極との短絡を防止する流路と電極との間の隙間に堆積することができる。

【0227】

いくつかの実施形態では、マスク層19は、マスク層19の幅を大きくすることによりチャネル幅を増大させるためにも使用可能であり、その後シリサイドを形成するが、そのさらに離れた位置から始まり、大きくなるスペーシングになる。

40

【0228】

いくつかの実施形態において、チャネルの幅や深さは、その全長に一致する場合がある。他方、他の実施形態では、流路の幅や深さは異なるかもしれません、チャネルの幅や深さは、電極構造の近傍で狭くなり、他の所では拡大する。単一のナノチャネルに沿って配置される実施形態では、複数の電極構造は、チャネルの幅および深さは、電極構造の近傍に電極のギャップ間隔と照合することができ、電極構造の間に広がることがある。

【0229】

いくつかの実施形態では、電極の間隔が、標的分子、生体分子（例えば、DNAまたはRNA）の直径よりも狭くすることができるいくつかの実施形態では、電極のギャップ間

50

隔と一致させるには、チャネルは電極の隙間の幅よりも大きくなるかもしれない。場合によつては、チャネルは電極のギャップより広い0.1nmから電極間隔よりも広い0.3nm、または電極間隙よりも大きく0.1nmから1nm、または電極間距離よりも広く、0.1nm以上3nm以下である。同様に、チャネルの深さは、生体分子が電極ギャップの間隔よりも大きく、幅と同様に寸法を記入することができると、電極ギャップの幅よりも大きくすることができる。

#### 【0230】

他の実施形態では、溝の幅は、溝の深さよりも大きくなる場合と、小さくなる場合がある。いくつかの実施形態において、チャネルの深さは、生体分子の直径より小さくなる可能性があり、直径では例えば二本鎖DNAの直径の1/2がナノギャップ近傍の少なくとも部分的な距離とを考えることができるが、生体分子は電極ギャップの電極と相互作用をすると考えられ得るように向けることもできるようになっている。

10

#### 【0231】

他の実施形態において、チャネルの幅及び深さにバラツキがあり、チャンネルはチャネル、例えばナノチャネルに沿つて離間され得る電極ナノギャップ間にナノチャネルの一部の部分に狭くならない場合がある。

#### 【0232】

本発明の好ましい実施形態をここに開示／説明してきたが、そのような実施形態は、例示の手段としてのみ提供されることが、当業者には明らかであろう。これは発明が明細書内に記載された特定の実施例により限定されるものではない。本発明は前述の仕様を参照して記述したが、本発明の複数の実施形態の説明および例示は、限定的な意味で解釈されることを意図していない。多数のバリエーション、変化および置換が、本発明から逸脱することなく当業者に想起される。さらに、本発明のすべての態様は、さまざまな条件や変数に依存する本明細書の特定の描写は、構成や組成比に限定されるものではないことを理解しなければならない。これは、本明細書で説明する本発明の実施形態の様々な代替物を採用して本発明を実施できることは、理解されるべきであり、本発明はそのような代替、変更、変形または等価物をカバーすることが意図され、請求の範囲は、本発明の範囲を規定し、これらの請求項の範囲およびその同等物内の方法および構造がこれに包含されることが意図される。

20

#### 【先行技術文献】

30

#### 【特許文献】

#### 【0233】

【特許文献1】 国際公開公報 2011/108540号

【特許文献2】 特開2004-247203号公報

【図1】

Fig. 1

【図2A.2C.2E】

Fig. 2A

Fig. 2C

Fig. 2E

【図2B.2D.2F】

Fig. 2B

【図3A】

Fig. 3A

Fig. 2D

【図3B】

Fig. 3B

Fig. 2F

【図 3 C】

Fig. 3C

【図 3 D】

Fig. 3D

【図 3 E】

Fig. 3E

【図 3 F】

Fig. 3F

【図 4】

Fig. 4

【図 5】

Fig. 5

【図 6 A - 6 C】

【図 7 B】

【図 7 C】

【図 7 A】

【図 8 A】

【図 8 B】

【図 9 B】

【図 8 C】

【図 10 A】

【図 10 B】

【図 9 A】

【図 10C】

【図 11A】

【図 11B】

【図 12A】

【図 12B】

【図 12C】

【図 13A】

【図 12D】

【図 13 B】

Fig. 13B

【図 13 D】

Fig. 13D

【図 13 C】

Fig. 13C

【図 13 E】

Fig. 13E

【図 13 F】

Fig. 13F

【図 15】

Fig. 15

【図 14】

Fig. 14

【図 16A . 16C . 16E】

Fig. 16A

Fig. 16C

Fig. 16E

【図 16B . 16D . 16F】

Fig. 16B

Fig. 16D

Fig. 16F

【図 17A】

Fig. 17A

【図 17C】

Fig. 17C

【図 17B】

Fig. 17B

【図 17D】

Fig. 17D

【図 17 E】

Fig. 17E

【図 17 F】

Fig. 17F

【図 19 A - 19 D】

【図 18】

Fig. 18

【図 20 A】

Fig. 20A

【図 20 B】

Fig. 20B

【図 20 C】

Fig. 20C

【図 2 1 A】

【図 2 1 B】

【図 2 1 C】

【図 2 2 A】

Fig. 22A

【図 2 2 B】

Fig. 22B

【図 2 2 C】

Fig. 22C

【図 2 2 E】

Fig. 22E

【図 2 2 D】

Fig. 22D

【図 2 2 F】

Fig. 22F

【図 2 3】

Fig. 23

【図 2 4 A】

Fig. 24A

【図 2 4 B】

Fig. 24B

【図 2 4 C】

Fig. 24C

【図 2 5 A】

Fig. 25A

【図 2 5 B】

Fig. 25B

【図 2 5 C】

Fig. 25C

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                            | International application No.<br>PCT/IB2014/002143                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>Int.Cl. G01N27/00 (2006.01)i, H01L21/28 (2006.01)i, H01L29/41 (2006.01)i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                            |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                            |                                                                                |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>Int.Cl. G01N27/00-27/49, H01L21/28, H01L29/41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                            |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched<br>Published examined utility model applications of Japan 1922-1996<br>Published unexamined utility model applications of Japan 1971-2015<br>Registered utility model specifications of Japan 1996-2015<br>Published registered utility model applications of Japan 1994-2015                                                                                                                                                                                                                                                                              |                                                                                                                                                            |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>JSTPlus/JMEDPlus/JST/580 (JDreamIII)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                            |                                                                                |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                            |                                                                                |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Citation of document, with indication, where appropriate, of the relevant passages                                                                         | Relevant to claim No.                                                          |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Xiaogan Liang et al., Nanogap Detector Inside Nanofluidic Channel for Fast Real-Time Label-Free DNA Analysis, NANO LETTERS, 2008, Vol.8 No.5, pp.1472-1476 | 64, 66-69                                                                      |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | JP 2007-272212 A (Victor Company of Japan, Limited) 2007.10.18, [0034] - [0036], Fig.3-Fig.4 (No Family)                                                   | 1-63, 65                                                                       |