(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6317365号

(P6317365)

(45) 発行日 平成30年4月25日(2018.4.25)

(24) 登録日 平成30年4月6日(2018.4.6)

(51) Int.Cl.

F 1

G06F 15/173 (2006.01)

G06F 15/173 660D

G06F 9/52 (2006.01)

G06F 15/173 683C

G06F 9/46 475A

請求項の数 15 (全 28 頁)

(21) 出願番号 特願2015-546462 (P2015-546462)

(86) (22) 出願日 平成25年10月10日 (2013.10.10)

(65) 公表番号 特表2016-501414 (P2016-501414A)

(43) 公表日 平成28年1月18日 (2016.1.18)

(86) 国際出願番号 PCT/US2013/064366

(87) 国際公開番号 WO2014/088698

(87) 国際公開日 平成26年6月12日 (2014.6.12)

審査請求日 平成28年9月27日 (2016.9.27)

(31) 優先権主張番号 61/734,190

(32) 優先日 平成24年12月6日 (2012.12.6)

(33) 優先権主張国 米国(US)

(73) 特許権者 505000815

コーヒレント・ロジックス・インコーポレーテッド

アメリカ合衆国・78746・テキサス州

・オースティン・サウス キャピタル オブ テキサス ハイウェイ・1120・ビルディング 3, スイート 310

(74) 代理人 100064621

弁理士 山川 政樹

(74) 代理人 100098394

弁理士 山川 茂樹

(72) 発明者 ドブス, カール・エス

アメリカ合衆国・78737・テキサス州

・オースティン・ジム ブリッジャー ドライブ・12010

最終頁に続く

(54) 【発明の名称】同期命令を含む処理システム

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のプロセッサであって、前記複数のプロセッサの各プロセッサは、複数のプロセッサポートおよび1つの同期アダプタを備え、前記同期アダプタが複数のアダプタポートを備える、プロセッサと；

複数のコントローラであって、前記複数のコントローラの各コントローラは、複数のコントローラポートを備え、前記複数のコントローラポートの各コントローラポートは、前記複数のプロセッサのうちの隣接するプロセッサのアダプタポートに接続している、コントローラと；

を備えるシステムであって、

10

前記複数のプロセッサの各プロセッサは、

選択的に、1つ以上のアダプタポートを介して同期信号を前記複数のコントローラのそれぞれの1つ以上のコントローラに送信し；

1つ以上のコントローラからの応答に応じてプログラム命令の実行を停止する；

ように設定され、

前記複数のコントローラの各コントローラは、

前記複数のプロセッサのそれぞれの1つ以上のプロセッサから1つ以上の同期信号を受信し；

前記受信した1つ以上の同期信号に応じて前記複数のプロセッサの前記それぞれの1つ以上のプロセッサの各々に応答を送信するように設定される、システム。

20

**【請求項 2】**

前記複数のコントローラの各コントローラは、1つ以上の設定データビットを受信する

ように設定された設定ポートを備える、請求項1に記載のシステム。

**【請求項 3】**

前記それぞれの1つ以上のプロセッサの各々に前記応答を送信するために、前記複数の

コントローラの各コントローラは、さらに、前記1つ以上の設定データビットに応じて前

記それぞれの1つ以上のプロセッサに前記応答を送信するように設定される、請求項2に

記載のシステム。

**【請求項 4】**

前記複数のコントローラの各コントローラは、レジスタを備える、請求項1に記載のシ

ステム。 10

**【請求項 5】**

前記複数のコントローラの各コントローラに対する前記1つ以上の設定ビットは、各コ

ントローラの前記レジスタに格納される、請求項4に記載のシステム。

**【請求項 6】**

マルチプロセッサシステムを動作させるための方法であって、前記マルチプロセッサシ

ステムは、複数のプロセッサおよび複数の同期コントローラを備え、前記複数のプロセッ

サの各プロセッサは、同期アダプタを備え、

1つ以上のグループのプロセッサの各グループは、前記複数のプロセッサのサブセット

を備え、 20

前記方法は：

前記1つ以上のグループのプロセッサの所与のグループを特定し、前記所与のグル

ープの各プロセッサのソフトウェア内に少なくとも1つの場所を特定して、同期バリアを挿

入すること；

前記所与のグループの各プロセッサの各同期アダプタに接続している、前記複数の同

期コントローラのうちの1つの同期コントローラを特定すること；

前記特定した同期コントローラに接続している各同期アダプタに向かう方向に応じて

、前記特定した同期コントローラに対する設定データを決定し、前記設定データは、前記

特定した同期コントローラと、前記所与のグループの選択されたプロセッサの前記同期ア

ダプタとの間で複数の同期信号を伝送することを可能にすること；および 30

前記所与のグループの各プロセッサに対して、前記ソフトウェア内で前記特定した場

所の各々に同期バリアを挿入し、各同期バリアは一連の1つ以上の同期命令を含み、各同

期命令は1つ以上の引数を含み、前記1つ以上の引数の各引数は、前記所与のグループの

各プロセッサの前記同期アダプタから、前記特定した同期コントローラの1つ以上の方

向のうちの所与の1つを指定すること；

前記挿入した同期命令の所与の1つを実行している前記所与のグループの各プロセッサ

に応答して、前記所与のグループの各プロセッサの実行を停止することと；

前記所与のグループが前記挿入した同期命令の1つ1つを全プロセッサが実行したかど

うかという判断に応答して、前記所与のグループの各プロセッサの実行を再開することと

を含む、方法。 40

**【請求項 7】**

前記判断した設定データは、複数の設定データビットを備え、前記複数の設定データビ

ットのそれぞれの組み合わせに対応する各データパターンは、前記特定した同期コントロ

ーラに接続しているプロセッサの前記所与のグループの所与のプロセッサの前記同期ア

ダプタへ向かう方向に一致する、請求項6に記載の方法。

**【請求項 8】**

設定データを前記マルチプロセッサシステムにロードすることは、前記複数の設定データ

ビットを前記特定した同期コントローラのレジスタに格納することを含む、請求項7に

記載の方法。

**【請求項 9】**

50

前記所与のグループの各プロセッサの実行を再開することは、前記特定した同期コントローラによって停止信号をデアサートすることを含む、請求項 6 に記載の方法。

【請求項 10】

前記所与のグループの各プロセッサの実行を停止することは、前記所与のグループの各プロセッサの前記同期アダプタによって同期リクエスト信号をアサートすることを含む、請求項 6 に記載の方法。

【請求項 11】

同期コントローラであって：

複数の設定ビットを格納するように設定されたレジスタであって、前記複数の設定ビットは、複数のデータパターンを符号化し、前記複数のデータパターンの各データパターンは、接続した方向の複数のサブセットのうちの所与の 1 つに一致する、レジスタと；

1 つ以上の論理回路であって、前記 1 つ以上の論理回路の各論理回路は：

1 つ以上の同期リクエスト信号を受信し；

前記受信した 1 つ以上の同期リクエストおよび前記複数のデータパターンの対応するデータパターンに応じて、少なくとも 1 つのプロセッサに対する停止信号を生成し、前記少なくとも 1 つのプロセッサは、前記接続した方向の複数のサブセットのうちの対応する 1 つの所与の方向で同期コントローラに接続される

ように設定される、論理回路とを備える、同期コントローラ。

【請求項 12】

1 つ以上の入力の各入力は、ラッチを含む、請求項 1 1 に記載の同期コントローラ。

【請求項 13】

前記受信した 1 つ以上の同期リクエストおよび前記複数のデータパターンの前記対応するデータパターンに応じて前記停止信号を生成するために、各論理回路は、さらに、接続した方向の前記複数のサブセットのうちの対応する 1 つの方向に対応する 1 つ以上の停止信号を生成するように設定される、請求項 1 1 に記載の同期コントローラ。

【請求項 14】

前記受信した同期リクエストおよび前記複数のデータパターンの前記対応するデータパターンに応じて前記停止信号を生成するために、各論理回路は、さらに、前記受信した同期信号のうちの選択した 1 つのアサートに応答して前記停止信号を生成するように設定され、前記受信した同期信号のうちの前記選択した 1 つは、前記複数のデータパターンの前記対応するデータパターンの方向に対応する、請求項 1 1 に記載の同期コントローラ。

【請求項 15】

前記受信した同期リクエストおよび前記複数のデータパターンの前記対応するデータパターンに応じて前記停止信号を生成するために、各論理回路は、さらに、前記受信した同期信号のうちの残りの同期信号がアサートされていないという判断に応答して前記停止信号を生成するように設定される、請求項 1 4 に記載の同期コントローラ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コンピュータシステムおよびデジタル信号プロセッサ (DSP) に関し、さらに詳細には、マルチプロセッサシステムに関する。

【背景技術】

【0002】

本明細書は、電子システム、特に、コンピュータ、デジタル信号プロセッサ (DSP) などのデジタル電子システム、およびさらに大きいシステムに組み込まれたこれらのシステムに関する。さらに詳細には、本概念は、デジタル電子システム内の信号ネットワークに関し、特にマルチプロセッサアレイ (MPA) 内の同期信号ネットワークに関する。MPA は、処理要素 (PE) のグループと、支持メモリ (SM) と、PE とメモリとの間で帯域幅の広いデータ通信を支持する第一相互接続ネットワーク (PIN) とで設定される。

10

20

30

40

50

## 【0003】

上記P Eは、入力データおよび出力データをバッファリングするためのレジスタ、命令処理ユニット(I P U)、およびデータに対して算術関数および論理関数を実施するための論理回路/回路のほか、システムの他の部分と通信するための多数のスイッチおよびポートを有する。I P Uは、メモリから命令を取得し、それを復号化し、適切な制御信号を設定してデータをプロセッサから出し入れして算術関数および論理関数を実施する。

## 【0004】

コンピュータのメモリおよびD S Pは、最上部に高速メモリがある階層で、階層が一段下がるにつれて低速になるが容量が多くなっていく階層内に組織される。M P Aでは、階層の最上部にある支持メモリが各P Eに隣接して設置される。各支持メモリは、命令のみまたはデータのみを保持するように特殊化されてよい。特定のP Eに対する支持メモリがそのP Eに専用のものであってもよいし、他のP Eと共有されてもよい。

10

## 【0005】

M P Aが最初に回路基板上でデジタル集積回路(I C)のアレイとして作製され、各I Cが1つのプロセッサを備え、回路基板がプロセッサどうしを相互接続するデータ通信リンクを提供していた。製造寸法がさらに小さい相補型金属酸化膜半導体(C M O S)トランジスタ回路に基づいた超大規模集積(V L S I)技術が進化し続け、シリコンI Cチップ1つあたりの論理回路とメモリ回路との密度が大幅に増大した。今日、1つのI Cチップ上でM P Aは、100個以上のプロセッサおよびその支持メモリおよび相互接続ネットワークを備えて作製されている。これらのM P Aチップを回路基板上でさらに相互接続させてさらに大きいシステムを作製できる。

20

## 【0006】

M P Aに適したP Eは、単にM P Aチップ1つあたりのP E数が多いために汎用プロセッサ(G P P)よりもエネルギー効率が高いことがあり、余分なエネルギーは余分な廃熱になり、その熱を取り除くにはチップのパッケージ費用および操作費用が加算される。

## 【先行技術文献】

## 【特許文献】

## 【0007】

【特許文献1】米国特許第7,415,594号

【特許文献2】米国特許出願第13/274,138号

30

## 【発明の概要】

## 【0008】

マルチプロセッサアレイの様々な実施形態を開示する。広義には、複数のプロセッサおよび複数のコントローラが散在するように一緒に接続している回路および方法が構想される。各プロセッサは、複数のプロセッサポートおよび1つの同期アダプタを備え、同期アダプタは、複数のアダプタポートを備えている。各アダプタポートは、複数のコントローラのうちの1つのコントローラポートに接続され、各コントローラは、複数のコントローラポート、および1つの設定ポートを備えている。各プロセッサは、1つ以上のアダプタポートを介して同期信号をそれぞれの1つ以上のコントローラに送信するように設定され、さらに、1つ以上のコントローラから受信する応答に応じてプログラム命令の実行を停止するように設定される。

40

## 【0009】

さらに別の実施形態では、各コントローラは、設定ポートを備えていてよい。設定ポートは、1つ以上の設定データビットを受信するように設定されてよい。

## 【0010】

もう1つの非限定的な実施形態では、各コントローラは、さらに、1つ以上の設定ビットに応じて応答を送信するように設定されてよい。

## 【図面の簡単な説明】

## 【0011】

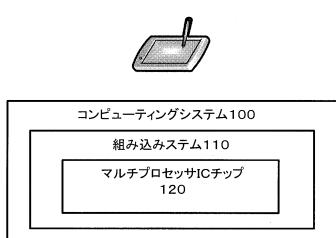

【図1】コンピューティングシステムの一実施形態を示すブロック図である。

50

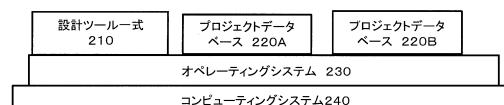

【図2A】一実施形態のコンピューティングシステムのソフトウェアとハードウェアとの階層を示すブロック図である。

【図2B】テストおよび開発システムを示すブロック図である。

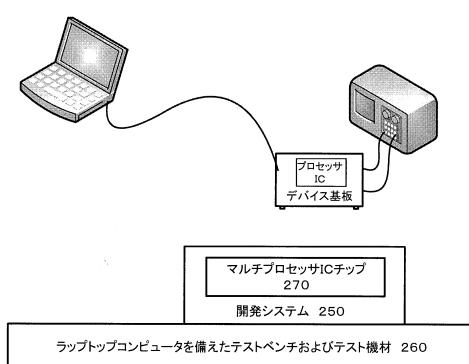

【図3】マルチプロセッサ集積回路の一実施形態を示すブロック図である。

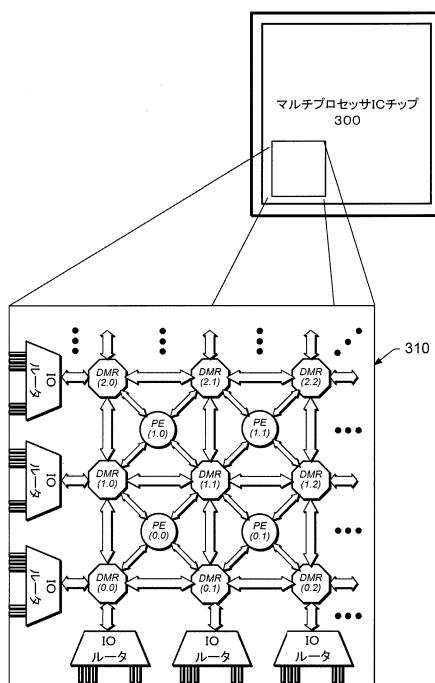

【図4】マルチプロセッサアレイの一実施形態を示すブロック図である。

【図5】同期コントローラの一実施形態を示すブロック図である。

【図6】同期ネットワークのもう1つの実施形態を示すブロック図である。

【図7】同期アダプタの一実施形態を示すブロック図である。

【図8】同期コントローラの一実施形態を示すブロック図である。

【図9】同期の連鎖を示すブロック図である。

【図10】マルチプロセッサアレイを動作させる方法の一実施形態を描いたフローチャートである。

【図11】マルチプロセッサアレイを動作させるもう1つの方法の一実施形態を描いたフローチャートである。

【図12】マルチプロセッサアレイの2つの処理要素の間の同期を示すブロック図である。

【図13】マルチプロセッサシステムの処理要素を同期させる方法の一実施形態を描いたフローチャートである。

【図14】マルチプロセッサシステムの3つの処理要素の間の同期を示すブロック図である。

【図15】マルチプロセッサシステム内の同期コントローラを動作させる方法の一実施形態を描いたフローチャートである。

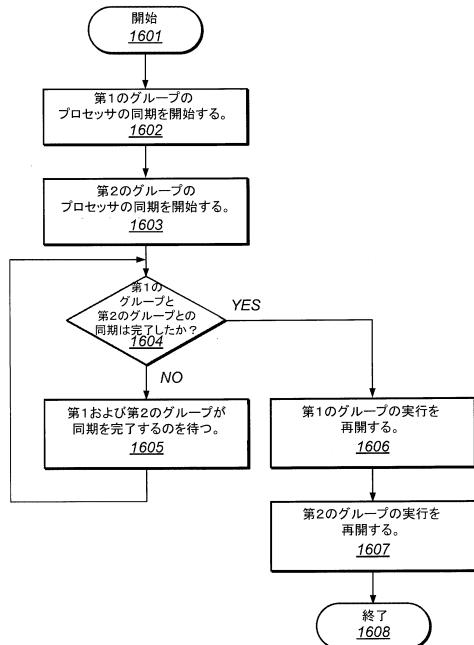

【図16】マルチプロセッサシステム内の2つのプロセッサ群を同期させる方法の一実施形態を描いたフローチャートである。

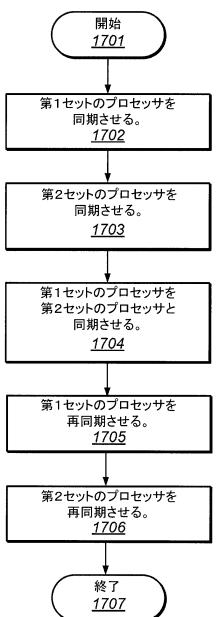

【図17】マルチプロセッサシステム内の2セットのプロセッサ同期させる方法の一実施形態を描いたフローチャートである。

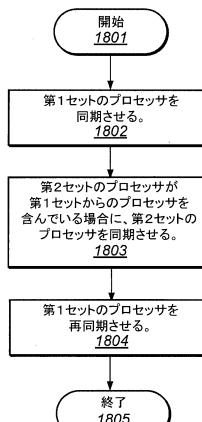

【図18】マルチプロセッサシステム内の2セットのプロセッサ同期させる方法の一実施形態を描いたフローチャートである。

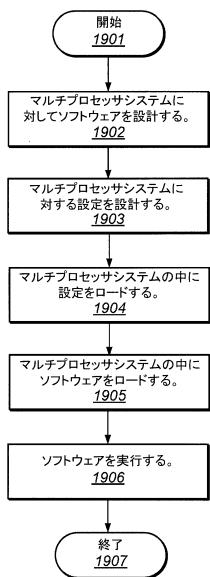

【図19】マルチプロセッサシステム用のソフトウェアを設計する方法の一実施形態を描いたフローチャートである。

【0012】

本開示は、様々な修正および代替形態が可能であるが、本開示の特定の実施形態を例として図面に示し、本明細書ではこれについて詳述していく。しかしながら、図面およびそれに対する詳細な説明は、図示した特定の形態に本開示を限定する意図はなく、逆にその意図は、付属の特許請求の範囲に規定される本開示の精神および範囲内に収まるあらゆる修正、均等物、代替物を含むことである点を理解すべきである。本明細書で使用する見出しへ、編成のみを目的とし、本明細書の範囲を限定するために使用しているのではない。本明細書全体にわたって使用しているように、「may (~であってよい)」という単語は、強制の意味（すなわち、must (~しなければならない)の意味）ではなく、容認の意味（すなわち、その可能性があるという意味）で使用している。同じように、「include (含む)」、「including (含む)」および「includes (含む)」という単語は、それを含んでいるという意味であって、限定するものではない。

【0013】

様々なユニット、回路、またはその他のコンポーネントが、1つまたは複数のタスクを実行する「ように設定された(configured to)」と記載されていることがある。このような文脈では、「~するように設定された(configured to)」というのは、動作中にその1つまたは複数のタスクを実行する「回路を有する」ことを全体的に意味する構造の広義の詳述である。このように、ユニット/回路/コンポーネントは、そのユニット/回路/コンポーネントがその時点でオンになっていないとしても、タスクを実行するように設定できるものである。一般に、「~するように設定された(c

10

20

30

40

50

on f i g u r e d t o ) 」に対応する構造を形成する回路は、ハードウェア回路を含んでいてよい。同じように、様々なユニット／回路／コンポーネントが1つまたは複数のタスクを実行すると便宜上明細書内に記載していることがある。このような記載は、「～するように設定された ( c o n f i g u r e d t o ) 」という句を含むものと解釈すべきである。1つ以上のタスクを実行するように設定されたユニット／回路／コンポーネントの詳述は、米国特許法第112条第6段落にあるそのようなユニット／回路／コンポーネントに対する解釈を採用しないことを明確に意図している。さらに全体的には、どの要素の詳述も、「means for (～を意味する)」または「step for (～のステップである)」という言葉が明記されていない限り、米国特許法第112条第6段落にあるそのような要素に対する解釈を採用しないことを明確に意図している。

10

【発明を実施するための形態】

【0014】

「P r o c e s s i n g S y s t e m W i t h I n t e r s p e r s e d S t a l l P r o p a g a t i n g P r o c e s s o r s A n d C o m m u n i c a t i o n E l e m e n t s 」と題し、発明者がMichael B. Doerr、William H. Halliday、およびDavid A. Gibson、Craig M. Chaseである米国特許第7,415,594号を参照することにより、本明細書に完全に記載されているかのようにその全容を本明細書に援用する。

【0015】

2011年10月14日に出願され、「D i s a b l i n g C o m m u n i c a t i o n i n a M u l t i p r o c e s s o r S y s t e m 」と題し、発明者がMichael B. Doerr、Carl S. Dobbs、Michael B. Solka、Michael R. Trocino、およびDavid A. Gibsonである米国特許出願第13/274,138号を参照することにより、本明細書に完全に記載されているかのようにその全容を本明細書に援用する。

20

【0016】

用語

ハードウェア設定プログラム - 例えば集積回路などのハードウェアをプログラムするか設定するために使用できるバイナリイメージにコンパイルできるソーステキストからなるプログラム。

30

【0017】

コンピュータシステム - 様々な種類のコンピューティングシステムまたは処理システムのうちのいずれかであり、パーソナルコンピュータシステム ( P C ) 、メインフレームコンピュータシステム、ワークステーション、ネットワーク機器、インターネット機器、携帯情報端末 ( P D A ) 、グリッドコンピューティングシステム、もしくはその他のデバイス、あるいはデバイスを組み合わせたものなどである。一般に、「コンピュータシステム」という用語は、記憶媒体からの命令を実行する少なくとも1つのプロセッサを有する任意のデバイス（またはデバイスを組み合わせたもの）を含ませるために広義に規定できる。

【0018】

自動的 - コンピュータシステム（例えばコンピュータシステムが実行するソフトウェア）またはデバイス（例えば回路、プログラム可能なハードウェア要素、A S I Cなど）によって実施されるアクションまたは動作のことであり、そのアクションまたは動作を直接指定したり実施したりするユーザ入力がないこと。そのため、「自動的」という用語は、ユーザが手動で実施または指定する動作で、ユーザが動作を直接実施するための入力を提供するものとは対照的である。自動的な手順であれば、ユーザが提供する入力で開始できるが、「手動で」実施されるその後のアクションはユーザが指定するものではなく、すなわち「手動で」実施されず、ユーザは実施するための各アクションを指定する。例えば、各フィールドを選択して電子フォームに書き込み、（例えば情報をタイピングしたり、チェックボックスを選択したり、無線選択をしたりして）入力して情報を指定しているユー

40

50

ザは、コンピュータシステムがユーザの行為に応答して更新しなければならないとしても、手動でフォームに書き込んでいる。フォームは、コンピュータシステムによって自動的に書き込まれてよく、この場合、コンピュータシステム（例えばコンピュータシステムで実行するソフトウェア）は、フォームのフィールドを分析し、フィールドへの回答を指定する何らかのユーザ入力なしにフォームに書き込む。前述したように、ユーザは、フォームの自動書き込みを呼び出すことができるが、その時点のフォームの書き込みに関わってはいない（例えばユーザは、フィールドへの回答を手動で指定してはおらず、むしろフィールドは自動的に完成されている）。本明細書では、ユーザが取った行為に応答して自動的に実施された動作の様々な例を提供する。

## 【0019】

10

## 概要

並列処理が可能なコンピュータシステムは、複数のデータ処理要素（P E）、支持メモリ（S M）ユニット、および帯域幅の広い相互接続ネットワーク（I N）で設定されて、個々のP E、S M、およびI / Oポートシステムどうしの間でデータを移動させることができる。そのようなシステムの第一I N（またはP I N）は、帯域幅が広く平均配信時間（待ち時間）が短くなるように最適化されてよい。しかしながら、P I Nは、確実に配信するようには最適化できない（メッセージは、「ビジー」信号になる他のメッセージをブロックできる）。その結果、P I Nは、P Eのグループに対してタスクを同期させるとには適していないことがある。いくつかの実施形態では、同期化のためにコンピュータシステムに追加のネットワークを追加することができる。このようなネットワークにより、メッセージを確実に配信できるが、このネットワークにより、コンピュータシステムに対して複雑さ、電力消費、または物理的なサイズが加わることがある。図面に示し、以下に説明した実施形態は、並列処理要素をコンピュータシステム内で同期させると同時に、コンピュータシステムの複雑さ、電力消費、または物理的なサイズに対する影響を最小にする技術を提供できる。

20

## 【0020】

## 並列処理

旧式のマイクロプロセッサおよびデジタル信号プロセッサ（D S P）は、一度に1つのタスクを実行でき、これは一般に、以下のように実行スレッドと呼ばれる。プロセッサのI P Uユニットからわかるように、実行スレッドは命令ストリームである。いくつかの実施形態では、命令ストリームに応答して結果の単一のストリームが生成される。この実行方式は一般に、S i n g l e I n s t r u c t i o n S i n g l e D a t a（単一命令單一データ、S I S D）と呼ばれる。他の実施形態では、複数の算術論理ユニット（A L U）を用いて、結果の複数のストリームを可能にすることができます。この実行方式は通常、S i n g l e I n s t r u c t i o n M u l t i p l e D a t a（単一命令複数データ、S I M D）と呼ばれる。さらに大きいマイクロプロセッサおよびD S Pは、S I M Dの能力を有することがあり、様々な実施形態では、そのような並列処理を利用して性能を高めるために、ソフトウェアを用いてよい。例えば、S I M Dを使用することによって、映像圧縮およびトランスコーディング、コンピュータビジョン、音声認識、および暗号化を加速できる。

30

## 【0021】

40

S I M D命令によって、命令の効果的な処理が可能になることがある。しかしながら、その効果は、データがA L Uに供給される速度によって異なることがある。通常、1つのS I M D命令から生じるデータ数は、2から8までの範囲であり、S I M Dごとに生じるデータ数は増大するため、各データ項目に含まれるビット数は通常減少する。S I M D命令ごとのデータ項目数を増大させる努力をすると、次のような様々な問題が生じことがある：複数のデータ項目が共通のメモリから同時にA L Uに供給され、A L Uの結果を格納すると同時にメモリに戻り、動作中に余分な電力消費が起こり、余分なA L Uはアイドル状態だが電源が入って準備が整っているときに余計な漏れ電力を消費するなどだが、これに限定されない。

50

## 【0022】

より最近のマイクロプロセッサおよびDSPは、複数のIPUならびにALUを用いて複数のスレッドを同時に実行できる。何を反復するかや特殊化されるかどうかは、それぞれのマイクロプロセッサ/DSPの設計タイプによって大きく異なる。それぞれのスレッドには独立した命令ストリームがあってよいため、この並列動作方式は、multi-instruction multi-data (マルチ命令マルチデータ、MIMD) と呼ばれる。プロセッサごとの通常のスレッド数は2~4だが、プロセッサは16スレッド以上の能力があるように設計されている。プロセッサごとのスレッド数を増大させる努力をすると、命令ストリームが共通のメモリから複数のIPUへ同時に流れ、余分なレジスタに対して余分な漏れ電力を消費するという問題が起こるが、これらは、複数のデータストリームが対応するALUに供給される問題に加えて起こることである。

10

## 【0023】

## マルチプロセッシング

マルチプロセッサシステムによってプログラマは、大型のタスクを、並列に実行できる複数の小さなタスクに分割できる。並列実行を利用して、時間を短縮して大型のタスクを完了するか、あるいは（プロセッサのクロック周波数を低減して）電力消費を削減することができる。クロック周波数が低減すれば、電源の電圧も低下してエネルギーを節約できる。

## 【0024】

マルチプロセッサシステムは、様々なコンピュータシステムのうちの1つに用いることができる。コンピューティングシステムの一実施形態を図1に示している。図示した実施形態では、コンピューティングシステム100は、デスクトップコンピュータ、ラップトップコンピュータ、タブレットコンピュータ、スマートフォン、またはその他の任意の適切なシステムであってよい。コンピューティングシステム100は、様々な実施形態では、例えば組み込みシステム110のような1つ以上の組み込みシステムを備えていてよい。いくつかの実施形態では、組み込みシステム100は、例えばマルチプロセッサIC120のような1つ以上の集積回路（IC）を備えていてよい。組み込みシステム110には1つのICしか描かれていないが、他の実施形態では、異なる数のICを用いてよく、そのそれが異なる機能を実施するように設定されてよい。

20

## 【0025】

図2Aには、一実施形態のソフトウェアとハードウェアとの階層を描いたブロック図を示している。この階層の下はコンピューティングシステム240である。いくつかの実施形態では、コンピューティングシステム240は、コンピューティングシステム100に相当するものであってよい。コンピューティングシステム240は、様々な実施形態では、デスクトップワークステーションであってよく、他の実施形態では、コンピューティングシステム240は、ラップトップコンピュータまたはその他のモバイルデバイスであってよく、ディスプレイ、ハードディスクドライブ、ネットワークインターフェースデバイスのようなコンポーネント、およびその他の任意の適切なコンポーネントを備えていてよい。

30

## 【0026】

階層の次のレベルは、オペレーティングシステム250である。様々な実施形態では、オペレーティングシステム250は、例えばWindows（登録商標）、Linux（登録商標）、Unix（登録商標）などの様々なタイプのオペレーティングシステムのうちの1つであってよい。オペレーティングシステム250のようなオペレーティングシステムは、様々な実施形態では、コンピューティングシステム240のハードウェアにアクセスするためのアプリケーションまたはユーザプログラムに必要なコマンドおよびプログラム命令を提供できる。

40

## 【0027】

上記のように、オペレーティングシステム250は、他のプログラムのためにハードウェアリソースへのアクセスを提供できる。図示した実施形態では、このようなプログラム

50

は、設計ツールー式 210、ならびにプロジェクトデータベース 220A および 220B を備えている。いくつかの実施形態では、設計ツールー式 210 は、ユーザがハードウェアリソースをコンピューティングシステム 240 内で設定できるように設定されていてよい。以下にさらに詳細に説明するように、このような設定は、制御ビットをマルチプロセッサ内の 1 つ以上の制御レジスタに格納することを含んでいてよい。制御ビットは、様々な実施形態では、マルチプロセッサの処理要素どうしの間の情報のルーティングを制御できる。いくつかの実施形態では、制御ビットは、マルチプロセッサの処理要素どうしの間の同期も制御できる。

#### 【0028】

テストおよび開発システムの一実施形態を図 2B に示している。図示した実施形態では、マルチプロセッサ I C 270 は、開発システム 250 に含まれている。開発システム 250 は、テストベンチ 260 と接続している。様々な実施形態では、テストベンチ 260 は、テスト機材、ラップトップコンピュータ、およびマルチプロセッサ I C 270 のテストおよび開発を補佐するその他の任意の適切な機材を備えていてよい。

#### 【0029】

動作中、開発システム 250 を使用して、所与のソフトウェアアプリケーションと一緒に使用するためにどのようにマルチプロセッサ 270 を設定するかを決定できる。いくつかの実施形態では、設定は、1 つ以上の処理要素をどのようにマルチプロセッサ 270 内で同期させて、並列処理中に個々の処理要素にデータを交換させるかを決定することを含んでよい。

#### 【0030】

図 2B に示した実施形態は単なる一例であることに注意されたい。他の実施形態では、異なる数のマルチプロセッサ I C および異なるテスト機材を用いてよい。

#### 【0031】

マルチプロセッサ I C の一実施形態を図 3 に示している。図示した実施形態では、マルチプロセッサ I C 300 は、プロセッサアレイ 310 を備えている。マルチプロセッサ I C 300 は、他の実施形態では、他の回路および機能ブロック（図示せず）も備えていてよい。例えば、マルチプロセッサ I C 300 は、発振器、位相ロックループ（PLL）、内部で電源を生成し調節する回路などを備えていてよいアナログ / 混合信号ブロックを備えていてよい。

#### 【0032】

動作中、メモリまたはハードディスクドライブまたはその他の適切な媒体に格納されたプログラム命令をプロセッサアレイ 310 で実行できる。いくつかの実施形態では、プロセッサアレイ 310 内の個々の処理要素（PE）を、特定のプログラム命令を実行するように設定できる。以下にさらに詳細に説明するように、プログラム命令の実行は、様々な実施形態では、同期を利用して PE どうしの間で調整できる。

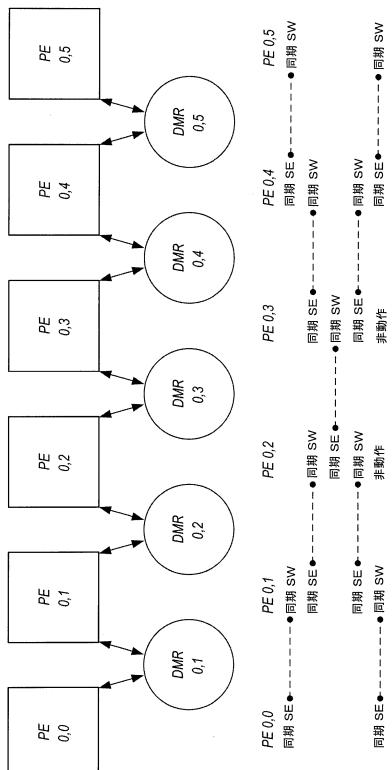

#### 【0033】

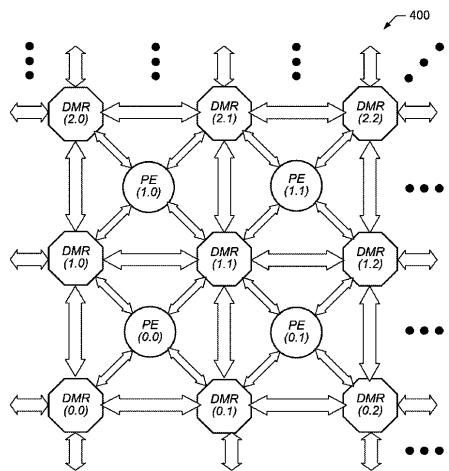

図 4 には、マルチプロセッサアレイ（MPA）の一例を示している。いくつかの実施形態では、MPA 400 は、図 3 に示したマルチプロセッサ I C 300 のプロセッサアレイ 310 に相当するものであってよい。図示した実施形態では、MPA 400 は、複数の処理要素（PE）および複数の支持メモリ（SM）および 1 つの相互接続ネットワーク（IN）を備えている。IN は、スイッチノードとリンクとで設定される。ルータとも呼ばれるスイッチノードをリンクと共に使用して、PE どうしの間および PE と MPA の I/O ポートとの間に通信経路を形成できる。しかしながら、各 PE では、通信されるどのような情報も SM にバッファリングされてよい。図示した実施形態では、SM は、データメモリルータ（DMR）と呼ばれる通信経路ルータと組み合わされている。本明細書で使用しているように、PE を PE ノードと呼ぶこともあり、DMR を DMR ノードと呼ぶこともある。本明細書では DMR を「設定可能な通信素子（configurable communication element）、または CCE」と呼ぶこともある。

#### 【0034】

10

20

30

40

50

図4に示したようなD M Rどうしの間のリンクは、直線のメッシュを形成する。しかしながら、他の実施形態では、他の多くの接続図式が可能であり、構想される。図4に示したM P A接続図式では、各P Eは4つの隣接するD M Rに接続しているのに対し、各D M Rは4つの隣接するP Eに接続するとともに4つの隣接するD M Rにも接続している。D M R 1つあたりにD M RとD M Rとの6つのリンクを使用して3次元の直線メッシュを支持するか、あるいはD M R 1つあたりに8つのリンクを使用して東西南北方向に加えて4つの対角線方向を支持するなど、より高次元のI Nを支持するために他の接続図式も検討される。リンクは、物理的に最も近くにある隣接対象物に限定されない。

#### 【0035】

M P Aとアプリケーションソフトウェアとを組み合わせたものは、様々な実施形態では、並列処理システム（P P S）と呼ぶことがある。例えば、M P Aをプログラムして、カメラからの生の映像データをバッファリングして分析してから、バッファコンテンツに対して映像データの圧縮を実施し、圧縮したデータを無線リンク上に伝送することができる。このアプリケーションソフトウェアとM P Aとを組み合わせたものを、例えば並列映像信号プロセッサと呼ぶことがある。

#### 【0036】

I / Oセルチップを含むM P A 4 0 0を、汎用マイクロプロセッサ、D S P、F P G A、またはA S I Cが現在使用されている様々なシステムおよびアプリケーションのいずれかに使用できる。例えば、図4に示した処理システムは、様々なタイプのコンピュータシステム、デジタル信号プロセッサ（D S P）または計算を必要とする他のデバイスのいずれかで使用できる。

#### 【0037】

図4に示したM P Aは単なる一例であることに注意されたい。他の実施形態では、異なる数のP EおよびP Eどうしの間の異なる接続機構を用いてよい。

#### 【0038】

##### 同期

マルチプロセッシングにより、さらに多くのプログラム命令を同時に実行できる可能性があるが、マルチプロセッシングにより、効果的な通信および調整のために、小さいタスクを特定の境界で時間と空間の面で同期させる必要性が生じる可能性がある。タスクがシステムクロック（クロックサイクルまたは省略して単に「サイクル」とも呼ばれる）の最小ティックで始まる場合、2つ以上のタスクが同期される。タスクの同期は、様々な実施形態では、サイクル数が少ない同期を実施するには困難なことがある。

#### 【0039】

上記に注意したように、P I Nはメッセージの配信を確実にするものではない。そのため、P I NはP Eの同期には適していない。代替策が、各P Eおよび共有メモリロケーションでソフトウェアバリアを用いることである。P Eがそのバリアに到達すると、P Eはロケーション値を上げた後、そのロケーション値が調整すべき予想P E数と一致するまでの値を定期的にポーリングする。しかしながら、このような技術を用いると、ほとんどのP Eのアーキテクチャは、一連のP Eがすべてバリアを超えて同じクロックサイクル内で他のP Eと同期し続けるのを確実にすることはない。

#### 【0040】

様々な実施形態では、P Eのアーキテクチャは、例えば1から20サイクルまでのよう広いサイクル範囲内でタスクを同期させることができる可能性があるが、特定の瞬間の現在のサイクル数は、プログラマの正常な制御を超えたいくつかの要因、例えば、他のアクティブスレッドの状態、S Mで現在処理されているデータのロケーション、キャッシング、割り込み処理などによって異なる。

#### 【0041】

いくつかの実施形態では、同期ネットワーク（s y n c h r o n i z a t i o n n e t w o r k）（本明細書では「同期ネットワーク（s y n c n e t w o r k）」とも呼ぶ）を用いて、M P Aの1つ以上のP Eどうしの間でタスクを同期させることができる。

10

20

30

40

50

マルチプロセッサシステムの第一相互接続ネットワーク（PIN）は、リンクとノードとで設定されてよく、その場合のノードは、リンクならびに点在する処理要素（PE）および支持メモリ（SM）に接続するためのポートを有するが、同期ネットワークを、一連の同期コントローラと、一連のPEアダプタおよびその間の接続部と、各PEにおける新たな命令とで設定してよい。

【0042】

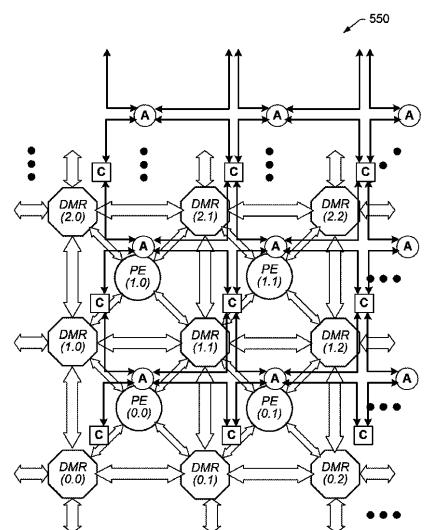

同期ネットワークを備えたMPAの一実施形態を図5に示している。図示した実施形態では、単一の同期コントローラ（C）をPINの各ノードに対して使用する。1つのシステムにある同期コントローラはすべて同じであってよい。各同期コントローラは、複数のポートを有してよく、その各々が隣接するPEに結合し、1つのポートが設定のためのものであってよい。いくつかの実施形態では、同期コントローラに結合している一連の隣接するPEは、最も近いPINノードが結合している一連のPEと同じであってよい。設定ポートは、SMロケーション、PEレジスタ、プログラミング/デバッグするための第二ネットワーク、または設定ポートに設定データを供給するその他の任意の手段に結合していてよい。同期コントローラにあるPEポートは、インバウンド用の同期信号およびアウトバウンド用の同期停止信号を有する。

10

【0043】

いくつかの実施形態では、各PEは、複数のポートを有する同期アダプタ（A）を用いることができ、各ポートは、同期コントローラに結合するほか、それ自身のPEにも結合する。いくつかの実施形態では、同期アダプタをPEに組み込むことができ、他の実施形態では、同期アダプタは別のエンティティであってよい。同期コントローラに結合している様々なポートは、PEから見た方向、例えば結合が4つの場合はNE、SE、SW、およびNWというコンパスの方向で区別することができる。アダプタにある各ポートは、アウトバウンド用の同期信号およびインバウンド用の同期停止信号を有する。さらに高次元のINを支持するために、同期コントローラとアダプタとの間の他の接続図式も検討される。同期コントローラと同期アダプタとの間のリンクは、物理的に最も近い隣接物に限定される必要はない。

20

【0044】

図5に示した同期ネットワークは単なる一例であることに注意されたい。他の実施形態では、異なる数の同期コントローラおよびアダプタ、ならびに同期コントローラとアダプタとの間の異なる接続が可能であり、構想される。

30

【0045】

いくつかの実施形態では、PEどうしの間の同期のソフトウェアによる制御を用いてよい。このような場合、専用の「同期」命令をPE命令セットに含めてよい。様々な実施形態では、このような命令に対するアセンブリ言語形式は、

同期<direction list>

であってよい。

【0046】

<direction list>フィールドは、信号を送信（アサート）し、その後同期停止信号をデアサートするのを待つための同期コントローラ方向のリスト（すなわち1つ以上）を指摘できる。APEは、次の命令を実行する前にリストに一致するすべての同期停止信号がデアサートされるまで待つことができる。

40

【0047】

いくつかの実施形態では、同期コントローラがこのPEを1つ以上の他のPEと同期させるように設定されていない場合、同期停止信号はデアサートされたままになり、PEは同期停止信号を待つことができない。同期コントローラは、同期設定レジスタ内に「マスクされて」いるPEからの同期を無視できるとともに、同期停止をこのPEにアサートできない。様々な実施形態では、同期設定レジスタは、MPAが実行する所与のアプリケーションに特有の設定情報を格納できる。

【0048】

50

同期コントローラが所与の P E を 1 つ以上の他のマスクされていない P E と同期するように設定され、かつそのマスクされていない P E がそのそれぞれの同期信号をまだアサートしていない場合は、同期コントローラは、同期停止信号をアサートし返すことで応答できる。その場合、所与の P E は、同期コントローラがマスクされていない P E の同期信号をすべて受信し、マスクされていない同期停止信号をすべてデアサートするまで待つことができる。

#### 【 0 0 4 9 】

様々な実施形態では、同期コントローラを D M R の一部として備えてよく、他の実施形態では、各同期コントローラを M P A 内のスタンドアローン型ユニットとして実施してよいことに注意されたい。

10

#### 【 0 0 5 0 】

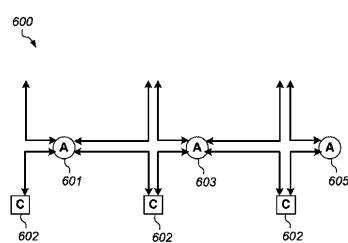

図 6 には、同期ネットワークの一部の一実施形態を示している。図示した実施形態では、同期ネットワーク 6 0 0 は、同期アダプタ 6 0 1、6 0 3、および 6 0 5、ならびに同期コントローラ 6 0 2、6 0 4、および 6 0 6 を備えている。それぞれの同期コントローラと同期アダプタとの間の接続部は、2 つのワイヤを備えている。1 つのワイヤは、同期リクエスト ( sync\_request、S R ) 信号の通信に使用されてよく、もう 1 つのワイヤは、同期停止 ( sync\_stall、S S ) 信号の通信に使用されてよい。いくつかの実施形態では、S R 信号は同期アダプタから同期コントローラに送信されてよく、S S は同期コントローラから同期アダプタに送信されてよい。

#### 【 0 0 5 1 】

所与の同期コントローラと所与の同期アダプタとの間の接続部に備わる 2 つのワイヤは、4 つの状態を符号化できる。第 1 の状態では、S R と S S 信号の両方が、非アクティブを指す論理 0 レベルであってよい。S R 信号は論理 0 レベルであってよく、S S 信号は第 2 の状態で論理 1 レベルであってよく、これは同期バリアがアクティブであるが、まだリクエストされていないことを指す。第 3 の状態では、S R 信号および S S 信号は両方とも論理 1 値であってよく、これは同期バリアがアクティブでリクエストされているがまだ完了していないことを指す。第 4 の状態では、S R リクエスト信号は論理 1 値であってよく、S S 信号は、同期バリアが完了したこと指す論理 0 値であってよい。

20

#### 【 0 0 5 2 】

図 6 に示した実施形態は単なる一例であることに注意されたい。他の実施形態では、異なる数の同期アダプタおよび同期コントローラ、ならびに異なる設定の同期コントローラおよび同期アダプタを用いてよい。

30

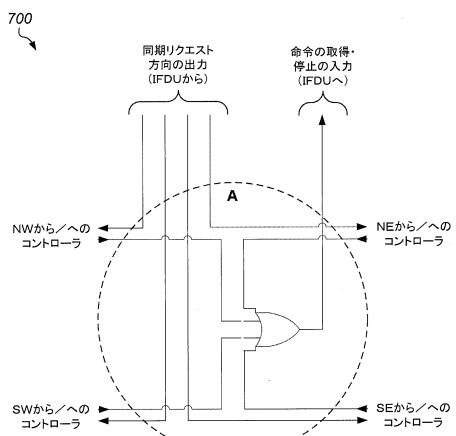

#### 【 0 0 5 3 】

同期アダプタの一実施形態を図 7 に示している。図示した実施形態では、同期アダプタ 7 0 0 は、接続した O R ゲート 7 1 0 を備えている。同期アダプタ 7 0 0 は、様々な実施形態では、P E 内に含まれていてよく、他の実施形態では、同期アダプタは、M P A 内の別のエンティティであってよい。同期アダプタ 7 0 0 は O R ゲートを備えているが、他の実施形態では、他の論理ゲートおよび論理ゲートの他の設定を用いてよい。

#### 【 0 0 5 4 】

動作中、同期アダプタ 7 0 0 は、P E の命令を取得し復号化するユニットと隣接する同期コントローラとの間の通信を仲介できる。P E の命令を取得し復号化するユニットから受信した S R 信号は、同期アダプタ 7 0 0 を介して隣接する同期コントローラまで移動できる。いくつかの実施形態では、S R 信号は、前述した命令のようなソフトウェア命令の関数であってよい。S S 信号はそれぞれの同期コントローラから戻り、O R ゲート 7 1 0 によって論理的に組み合わされる。その結果生じる信号は、P E の命令を取得し復号化するユニットを停止するために使用されてよい。いくつかの実施形態では、次の P E クロックサイクルに対する命令の取得を遅らせるには、隣接する同期コントローラのうちの 1 つから送信される单一のアクティブな S S 信号で十分である可能性がある。

40

#### 【 0 0 5 5 】

図 7 に示した同期アダプタは単なる一例であることに注意されたい。他の実施形態では

50

、異なる数の論理ゲートならびに異なる数の S R 信号および S S 信号が可能であり、構想される。

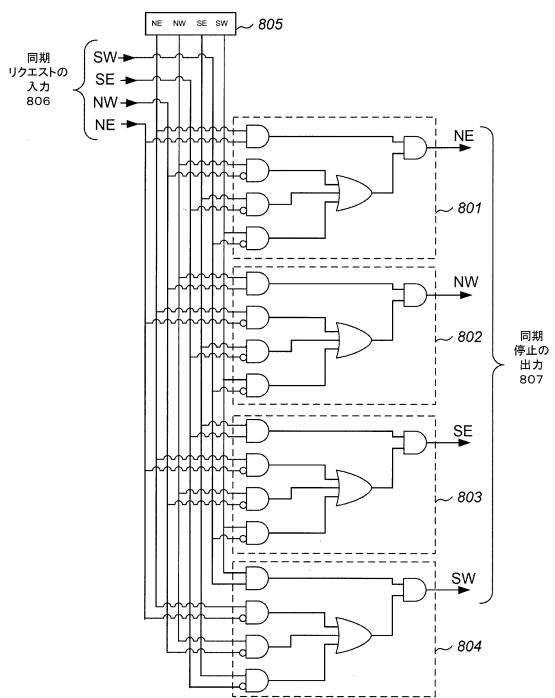

【 0 0 5 6 】

図 8 には、同期コントローラの一実施形態を示している。図示した実施形態では、同期コントローラ 8 0 0 は、論理ゲート 8 0 1 から 8 0 4 、マスクレジスタ 8 0 5 を備えている。いくつかの実施形態では、マスクレジスタは、同期コントローラ 8 0 0 の外部に位置していてもよいし、メモリ内にマッピングされた場所であってもよい。本明細書に記載したようなレジスタは、1 つ以上のデータビットを格納するように設定された格納回路の特定の実施形態であってよい。いくつかの実施形態では、レジスタは、ラッチ、フリップフロップなどの1 つ以上のデータ格納セルを備えていてよい。レジスタ 8 0 5 は、対応する P E の各「方向」に対応するマスクビットを備えていてよい。マスクレジスタ 8 0 5 には 4 方向しか描かれていないが、他の実施形態では、異なる数の「方向」が可能であり、構想される点に注意されたい。

【 0 0 5 7 】

動作中、同期コントローラ 8 0 0 は、例えば図 7 に示した同期アダプタ 7 0 0 のような隣接する同期アダプタから S R 信号 8 0 6 を受信する。すると、論理ゲート 8 0 1 から 8 0 4 は、受信した S R 信号を組み合わせて S S 信号 8 0 7 を生成することができる。いくつかの実施形態では、S S 信号 8 0 7 の生成にマスクレジスタ 8 0 5 からの設定ビットを用いてよい。例えば、マスクビットが論理 0 であれば、対応する方向からの入力は無視してもよく、その方向に対応する S S 信号は、対応する P E が停止していないことを指す論理 0 レベルに設定されてよい。

【 0 0 5 8 】

マスクビットが論理 1 レベルの場合、対応する方向に対する S S 信号の状態は、その方向からの S R 信号および対応する論理ゲート内の対応する O R ゲートの出力によって異なっていてよい。マスクビットが論理 0 レベルの場合、対応する S S 信号および対応する S R 信号の状態は、S S 信号の状態に影響を及ぼさない。

【 0 0 5 9 】

2 つ以上のマスクビットが論理 1 レベルの場合、対応する S S 信号は論理 0 レベルになり、これは、様々な実施形態では、S R 信号が論理 0 レベルの場合に「停止しない」条件を指すことがある。S S 信号に対応する S R 信号が論理 1 レベルであり、少なくとも 1 つの他の S R 信号が論理 1 レベルであれば、S S 信号は、「停止」条件を指してよい論理 1 レベルになる。

【 0 0 6 0 】

「低い」、「低い論理レベル」または「論理 0 レベル」とは、アースでの電圧またはアース近くの電圧のことであり、「高い」、「高い論理レベル」または「論理 1 レベル」とは、n チャネル型 M O S F E T をオンにし、p チャネル型 M O S F E T をオフにするのに十分な大きさの電圧レベルのことである点に注意されたい。他の実施形態では、異なる技術では「低い」および「高い」に対して異なる電圧レベルになることがある。図 8 に描いた同期コントローラの実施形態は単なる一例であることにさらに注意されたい。他の実施形態では、異なる論理ゲートおよび論理ゲートの異なる設定を用いてよい。

【 0 0 6 1 】

どのような実際のプロセッサアレイであっても、D M R に接続される P E には有限数 n があり、これは 1 クロックサイクルで D M R が同期できる P E の最大数である点に注意されたい。いくつかの実施形態では、この数は 4 であってよいが、他の実施形態では、異なる数を用いてよい。P E 1 つあたりに t 個の実行スレッドがある場合、各同期コントローラポートおよび各アダプタポートで同期信号の数および同期停止信号の数に t を乗算することによって、t × n 個のスレッドを单一の D M R と同期させるとができる。n 個よりも多い P E を同期させるためには、異なる技術を用いてよい。

【 0 0 6 2 】

大規模な P E グループ全体に対して慎重に構築した一連の同期コマンドをプログラミン

10

20

30

40

50

グすることで、どのような数の P E でも同期させることができるが、1つのクロックサイクルで即座に同期させることはできない。このプログラミング技術は、グループ内の最も外側にある P E から、そのグループの中心にあるいくつかの D M R まで停止バリアが行き渡るように調整し、その後、中心の D M R から最も外側の P E までリリース波が伝播するように調整する技術である。いくつかの実施形態では、同期を微調整するために非動作命令（一般に「n o p s」と呼ばれる）を追加してよい。

#### 【0063】

図9には、1つのラインに配置された6つのP Eの同期を示す一例を示している。P Eはどのような形状に配置されてもよいが、明瞭化のために例として1つのラインを選択した点に注意されたい。

10

#### 【0064】

P Eのラインに対して、D M Rを使用して図9に示したP Eの対を同期させることができる。D M RのN EポートおよびN Wポートにある両方のP Eが同期信号をD M Rに発信した場合に限り、同期停止から一対のP Eを解放するように所与のD M Rを設定できる。他のP Eが割り込むのを防ぐため、5つのD M RすべてをそのS W方向およびS E方向で同期ポートをマスクする（無視する）ように設定する（これは、S W、S E方向で他のP EへのD M Rの接続がないこと以外は図示していない）。D M Rのこの設定は、各D M Rにある同期設定レジスタに設定ビットを格納することによって、同期命令よりも前に行われる。

#### 【0065】

図9に描いた6つのP Eを同期させるのに必要な同期プログラミングも図9に示している。各P Eの下に一連の命令を列挙している。各P Eは、対応する命令を上から下に向かって実行する。破線で示したコネクタラインは、異なるP Eに対してどの同期命令が対になって共通のD M R（対になっている両P Eに接続しているD M R）を介して一緒に動作するのかを示している。各P Eは、異なるクロックサイクルで第1の同期命令に到達してよいが、対になっているP Eと同じクロックサイクルでその同期命令を終了するようハードウェアによって強制される。この特定の連鎖の例ではP Eが対になっているが、前述したD M Rの制約に従って、必要に応じて3つ以上のP Eを単一のサイクルで同期させることができる。

20

#### 【0066】

図9に示したP Eのプログラミングを検証した上で、中心で交差している2つのチェーンに注意されたい。第1のチェーンは、P E 0 0 およびP E 0 1に対する第1の対の同期命令からなる第1のリンク、P E 0 1とP E 0 2との間の第1の対の同期命令からなる第2のリンク、P E 0 2とP E 0 3との間の唯一の対の同期命令からなる第3のリンク、P E 0 3とP E 0 4との間の第2の対の同期命令からなる第4のリンク、およびP E 0 4とP E 0 5との間の第2の対の同期命令からなる第5のリンクを有する。第2のチェーンは、同様に形成されるが、第1のチェーンに対するミラー像のように形成される。つまり、P E 0 5との間の第1の対の同期命令からなるリンクで始まり、P E 0 0とP E 0 1との間の第2の対の同期命令からなる第5のリンクで終わる。

30

#### 【0067】

そのため、P E 0 1は第1の同期S W命令で停止から解放されると、第1の同期S E命令に捕捉され、これは、P E 0 2の第1の同期S W命令と対になることによってチェーンの次のリンクになる。P E 0 2の列についても同様に、P E 0 2は第1の同期S W命令から解放されると、第1の同期S E命令に捕捉され、これは、P E 0 2の第1の同期S W命令と対になることによってチェーンの次のリンクになる。これ以降も同じように続く。

40

#### 【0068】

各P Eがプログラムされたタスクを有し、そのそれぞれのタスクが別々に、かつ場合によっては任意の時間をかけてよいと仮定すると、P Eは、もう1つの反復に向けて準備するためにデータを交換することになる。このデータ交換に対して準備するために、P Eは図9の同期プログラミングと同期されてよい。

50

## 【0069】

各P Eはそのタスクを終了すると、図9にあるそのP Eの対応する列で第1の同期命令を実行する。チェーン内の同期命令にヒットするのが第1のP Eであれば、待機する。さらに多くのP Eが各チェーンの上半分に到達してリンクを解放した場合、各P Eは、下半分のチェーンにある次の同期命令に進み、待機する。最終的に両チェーンの上半分が解放され、中央のD M R 0 3の端から端までのリンクが解放される。この時点で全P Eが下半分のチェーンで待機しているため、これらのチェーンは、1サイクルあたり1リンクの割合で高速に連続してP Eを解放する。

## 【0070】

図示したように、同期終了の波が外側へ向かう間、内側のP Eが、最も外側のP Eが解放されるのを待つようにする必要があることがある。これは、終了が起こる同期命令の後にn o p sを追加することによってプログラムできる。P Eがn o p命令を1つ実行すると、1クロックサイクル分を待機する。各P Eに対してプログラム内で使用するn o p sの数は、外側へ向かう同期の実行がそれぞれ正確に1クロックサイクル分かかるなどを把握した上で計算される。外側へ向かう同期の実行はそれぞれ1サイクルかかり、n o p sはいずれも1サイクルかかり、停止する可能性のあるコードを実行しているP Eはないため、すべてのP Eを同期させる形で解放できる。図示したプログラミングは、すべてのP Eが命令の連続を正確に同じクロックサイクルで終了するようとする。

10

## 【0071】

この技術は、数千のP Eを含むM P Aにもスケーラブルである。例えば、2 0 2 5個のP Eからなる正方向のアレイであれば、エッジの長さはP E 4 5個分、つまりP EからP Eまでの中継点が4 4個であり、対角線のマンハッタン（階段状の）距離の中継点は8 8個である。同期チェーンは、領域全体を覆うように放射状のファン模様に設定できる。角から角まで通っているチェーンは、中継点8 8個分の長さであり、これらの中継点が2 0 2 5個のP Eすべてを同期するための最悪の場合の時間間隔を決定し、この場合は8 8クロックサイクルである。P Eが停止する動作中は、同期命令に遭遇すると、最終的にこれはアレイの中央まで通信される。停止は中央から波の形で解放され、この波は放射状に外側に向かって伝播する。N o - o p s（非動作）は、中央により近いP Eを波が角に到達するまで遅らせるために必要になることがある。その場合、全P Eは、連続する命令を同じクロックサイクルで開始できる。

20

## 【0072】

同期命令は、配信された支持メモリを含むプロセッサグループを調整して並列プログラムを実行するために使用できる。並列プログラムには多くの様々な種類がある。

## 【0073】

この命令によりプログラマは、大規模なM P Aにある複数のプロセッサをロックステップの実行に組み入れることができる可能性がある。これによって、このようなアレイの並列処理の利便性を、特にリアルタイムで処理するタスクや、収縮モードでの動作で大いに高めることができる。収縮モードとは、鼓動サイクルの長さが1以上であってよい鼓動を有するようにM P Aがプログラムされるプログラミング方法である。各鼓動においていくつかのデータ項目が各P Eに受信され、いくつかの動作が実施され、その結果が隣接するP Eに出力される。収縮モードは、P E 1つあたりにほとんどメモリを必要とせず、いくつか例を挙げると、行列数学、フィルタリング、および画像処理アプリケーションに適用されてきた。一次元の収縮モードは、通常バイオペラインと呼ばれる。これらおよびその他の並列プログラミング方法によりプログラマは、大規模な単一タスクの計算力を多くの小さなタスクに分割しやすくなる。

30

## 【0074】

単一命令複数データ（S I M D）の能力を含む従来のコンピュータ/D S Pシステムでは、並列処理は、1つのP EサイクルにあるA L Uに対して利用可能にできるデータ項目数によって制限される。通常この数には一定の最大値があり、マイクロプロセッサの場合は通常2～8であり、スーパーコンピュータでは最大おそらく1 2 8である。M I M D

40

50

の並列処理が可能な従来のマルチプロセッサシステムは、その複数の命令ストリーム中の同じ命令を用いてプログラムできる；しかしながら、これ単独では、関連する P E が始動したりロックステップの実行に残ったりすることは確実にはならない。

#### 【 0 0 7 5 】

同期命令の連鎖を用いることによって、大規模な P E グループの開始を、いくつかの実施形態では、同じサイクルで開始でき、同じ命令を同時に実行する A L U の数に対する S I M D の制限を克服する。同じタスクの複数のコピーを実行することで、複数の P E がロックステップにとどまることができるが、確実ではない。P E は、データ値、データメモリまたは通信リソースに対する干渉が原因で起こる待機状態、割り込み、ブレークポイントなどに対してサイクルのカウントが依存していない場合に限り、ロックステップにとどまることができる。長期間にわたってロックステップの実行を達成するには慎重なプログラミングが必要になることがある。しかしながら、これがうまくいかない場合は、上記の方法によって複数のスレッドを定期的に再度同期させることができる。

#### 【 0 0 7 6 】

ハードウェア（およびそれに伴い電力）の影響は、追加された同期命令の能力に対しては極めて低い。必要でない P E は閉じてよい。そのため、電力は、アルゴリズムが必要な時のみに使用され、S I M D 命令を実施させるのに必要だが常時使用するわけではないオーバーヘッド電力の一部ではない。

#### 【 0 0 7 7 】

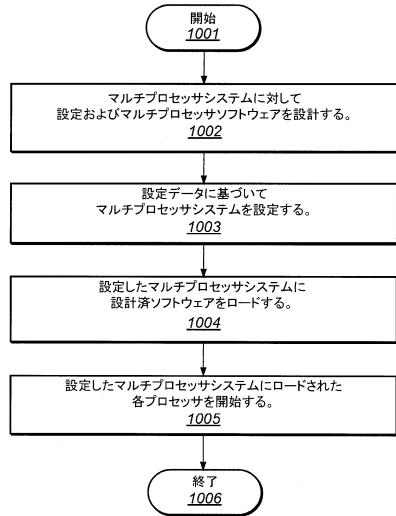

図 10 には、図 5 に描いたアレイ M P A 5 0 0 のようなマルチプロセッサアレイを動作させる方法の一実施形態を示している。この方法はブロック 1 0 0 1 から始まる。次に、マルチプロセッサシステムに対して設定およびソフトウェアを設計できる（ブロック 1 0 0 2）。いくつかの実施形態では、ソフトウェアは、様々なアプリケーションプログラムのうちのいずれか 1 つであってよく、その個々のプログラム命令は、M P A 内にある個々の P E で作動可能なものであってよい。設定は、いくつかの実施形態では、P E の時間面での共通点でデータ交換を可能にするための同期の命令およびセッティングを含んでいてよい。

#### 【 0 0 7 8 】

ソフトウェアおよび設定の設計が完了すると、マルチプロセッサシステムを設定できる（ブロック 1 0 0 3）。いくつかの実施形態では、マルチプロセッサシステムの設定は、例えば図 8 に示したレジスタ 8 0 5 のような設定レジスタに情報を格納することを含んでよい。他の実施形態では、設定データは、マルチプロセッサシステム内に備わっている 1 つ以上のメモリに格納されてよい。

#### 【 0 0 7 9 】

マルチプロセッサアレイの設定が完了した状態で、事前に設計したソフトウェアをマルチプロセッサシステムにロードできる（ブロック 1 0 0 4）。いくつかの実施形態では、ソフトウェアは、マルチプロセッサシステム内に備わっている 1 つ以上のメモリにロードされてよい。ソフトウェアは、他の実施形態では、例えばハードディスクドライブ、C D などのコンピュータアクセス可能媒体、またはその他の任意の適切な記憶媒体に格納されてよい。

#### 【 0 0 8 0 】

ソフトウェアがマルチプロセッサシステムにロードされると、マルチプロセッサの個々の P E が開始される（ブロック 1 0 0 5）。いくつかの実施形態では、各 P E は、ロードされたソフトウェア内に含まれる特定の命令セットを実行できる。各 P E は、様々な実施形態では、命令の実行を停止して、マルチプロセッサシステム内の他の P E によって実行されている命令の完了を保留できる。P E が命令を実行している状態で、本方法はブロック 1 0 0 6 で終了できる。

#### 【 0 0 8 1 】

図 10 に描いた方法は単なる一例であることに注意されたい。他の実施形態では、異なる動作および異なる順序の動作を用いてよい。

10

20

30

40

50

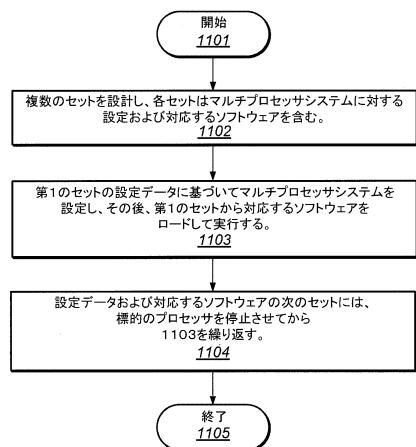

## 【0082】

マルチプロセッサシステムを動作させる方法のもう1つの実施形態を図11に示している。本方法はブロック1101から始まる。次に、マルチプロセッサシステムを動作させる複数のセットを設計できる（ブロック1102）。いくつかの実施形態では、各セットは、設定データおよびソフトウェアアプリケーションを含んでいてよい。設定データは、様々な実施形態では、そのセットに含まれる特定のソフトウェアアプリケーションに唯一のものであってよい。

## 【0083】

複数のセットを規定した状態で、複数のセットの第1のセットの設定データに基づいてマルチプロセッサシステムを設定でき、その後、対応するソフトウェアアプリケーションを実行できる（ブロック1103）。いくつかの実施形態では、マルチプロセッサシステム内の様々なPEが、ソフトウェアアプリケーションの一部である様々な命令を実行してよい。

10

## 【0084】

第1のセットからソフトウェアアプリケーションが実行されると、複数のセットの次のセットから得たデータでマルチプロセッサシステムを設定できる（ブロック1104）。新たに設定したマルチプロセッサシステムを用いて対応するソフトウェアアプリケーションを作動できる。いくつかの実施形態では、対応するソフトウェアアプリケーションのタスクを実行しているプロセッサは、停止させられてよく、本方法を前述したブロック1103から進めてよい。本方法は、ブロック1105で終了できる。

20

## 【0085】

図11に示した方法は単なる一例であることに注意されたい。他の実施形態では、異なる動作および異なる順序の動作が可能であり、構想される。

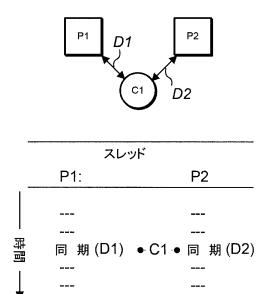

## 【0086】

図12には、マルチプロセッサシステムの2つのPEを同期させる一実施形態を描いたブロック図を示している。図示した実施形態では、処理要素P1およびP2は、それぞれ方向D1およびD2を介して同期コントローラC1に接続している。PEのP1およびP2によって処理されている各スレッドは、同期命令を含んでいる。いくつかの実施形態では、同期命令は、上記にさらに詳細に記載したような方法を含んでいてよい。

30

## 【0087】

動作中、マルチプロセッサシステムを設定し、ソフトウェアアプリケーションをロードして実行できる。PEのP1およびP2がそれぞれの指定タスクを実行している際に、同期命令に遭遇することがある。同期命令に遭遇する第1のPEは、他のPEがそのそれぞれの同期命令に遭遇するまで実行を停止できる。その時、2つのPEはデータを交換でき、その後そのPEのそれぞれのスレッドの実行を再開できる。

## 【0088】

図12に示した実施形態は単なる一例であることに注意されたい。他の実施形態では、異なる数のPEおよび異なる数の同期コントローラを用いてよい。

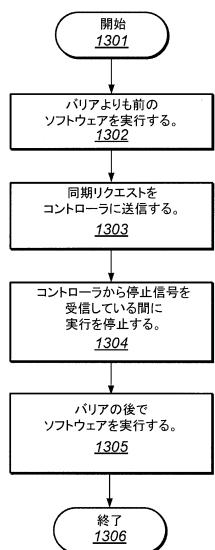

## 【0089】

マルチプロセッサシステム内でPEを同期させる方法の一実施形態を示すフローチャートを図13に描いている。図12のブロック図および図13のフローチャートを合わせて参照すると、本方法はブロック1301から始まる。次に、同期バリアよりも前にあるソフトウェア命令をプロセッサP1およびP2によって実行できる（ブロック1302）。

40

## 【0090】

次に、プロセッサP1は、同期命令に遭遇でき、その同期命令に応答して、同期リクエストをコントローラC1に送信できる（ブロック1303）。いくつかの実施形態では、マルチプロセッサシステム内の様々なプロセッサが実行する命令スレッドどうしの間の同期をそれぞれが要求する場所をソフトウェア内で特定できる。

## 【0091】

プロセッサP1が同期命令を送信すると、プロセッサP1は、コントローラC1が生成

50

した停止信号に応答する実行を停止できる（ブロック1304）。図12には単一のコントローラを示しているが、他の実施形態では、1つのプロセッサを複数のコントローラに接続してよく、複数のコントローラのいずれか1つから得た停止信号で、さらに他のプログラム命令の実行を停止できる。様々な実施形態では、停止信号は、コントローラC1がプロセッサP1とプロセッサP2との両方から同期リクエストを受信した時点でデアセットされてよい。コントローラC1が両方のプロセッサから同期リクエストを受信したとき、両プロセッサは同期バリアに到達していて、「同期している」と通知される。コントローラC1は、様々な実施形態では、図15に関して以下に記載する方法と同様に、停止信号をいつデアサーントするかを決定できる。

## 【0092】

10

停止信号のデアサーントによって、プロセッサP1は、同期バリアの後にソフトウェアの実行を再開できる（ブロック1305）。その時点で、本方法はブロック1306で終了できる。図13に示した方法には同期リクエストのみを描いているが、他の実施形態では、所与のプロセッサの命令スレッドに複数の同期命令を挿入してよい。追加の同期命令によって、いくつかの実施形態では、マルチプロセッサシステム内のさらに多数のプロセッサを同期させることができる。

## 【0093】

図13に示した方法は単なる一例であることに注意されたい。他の実施形態では、異なる動作および異なる順序の動作を用いてよい。

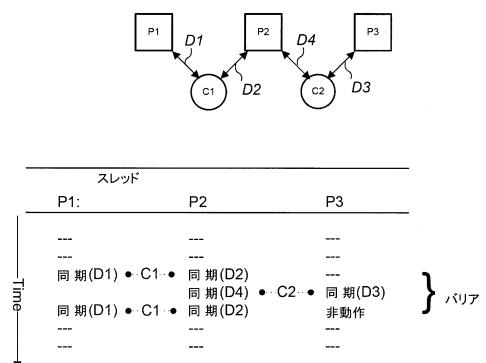

## 【0094】

20

図14には、マルチプロセッサシステムの3つのPEを同期させる一実施形態を描いたブロック図を示している。図示した実施形態では、処理要素P1は、方向D1を通じて同期コントローラC1に接続し、処理要素は、方向D2およびD4を通じて同期コントローラC1およびC2にそれぞれ接続し、処理要素P3は、方向D3を通じて同期コントローラC2に接続している。

## 【0095】

設計段階では、3つのPEを動作させるための設定が設計される。いくつかの実施形態では、この設定は、同期コントローラC1およびC2内のマスクレジスタにロードされるデータビットを含んでいてよい。データビットは、前述した方向D1からD4に応じて決定されてよい。例えば、方向D1およびD2以外の全方向をマスクするようにC1のレジスタを設定できる。設計は、関連ソフトウェアの命令スレッドのどこに同期命令を挿入するかを決定することを含んでいてもよい。データビットおよび同期命令は、一緒にバリアを形成する、すなわち、全スレッドがその地点に到達するまで3つの処理要素の各々が待機する時間に1つの場所を形成することができる。

30

## 【0096】

次に、設定データおよび関連ソフトウェアは、マルチプロセッサシステムにロードされてよい。ロードされると、P1、P2、およびP3の各々に対して標的となった命令（スレッドとも呼ばれる）を実行できる。P1が同期命令に遭遇したとき、P1は、P2がD2方向で同期命令に遭遇するまでそのスレッドの実行を停止できる。同じように、P3が同期命令に遭遇したとき、P3は、P2がD4方向で同期命令に遭遇するまでそのスレッドの実行を停止できる。

40

## 【0097】

P1およびP3に対する同期命令がP2に対する同期命令よりも先に到着した場合、同期命令がD2方向で到着することによって、P1を次のクロックサイクルのD1方向でその第2の同期命令まで進めることができる。次のクロックサイクルでも、P2がD4方向で同期命令に遭遇すると、これによってP3をD3方向でその第2の同期命令まで進めることができる。第3のクロックサイクルでは、P2がD2方向で同期命令に到達することによって、1つのサイクルでP1と再度同期させることができる。いくつかの実施形態では、P3に対してはno-op命令が望ましいことがある。

## 【0098】

50

P 1 が P 2 の後にバリアに到達した場合、P 2 は、P 1 が到達するまでその同期 (D 2) 命令で待機する。P 3 が P 2 の後にバリアに到達すれば、P 2 は、P 3 がバリアに到達するまでその同期 (D 4) 命令で待機する。

#### 【0099】

図 14 に示した実施形態は単なる一例であることに注意されたい。他の実施形態では、異なる数の P E およびコントローラを用いてよい。

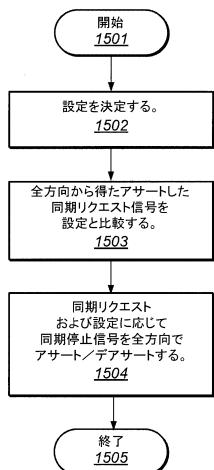

#### 【0100】

図 15 には、例えば図 8 の同期コントローラのような同期コントローラを動作させる方法の一実施形態を描いたフローチャートを示している。本方法はブロック 1501 から始まる。次に、設定を決定できる (ブロック 1502)。いくつかの実施形態では、設定データは、例えば図 8 に示したレジスタ 805 のようなレジスタに含まれていてよい。このようなレジスタに格納されている設定データビットは、様々な実施形態では、同期情報の受信をどの方向から許可するのかを決定するために復号化されてよい。それぞれの方向は、隣接するプロセッサのうちの対応する 1 つに一致していてよい。

10

#### 【0101】

次に、全方向からアサートされた同期リクエストを設定と比較することができる (ブロック 1503)。いくつかの実施形態では、この比較は、例えば図 8 に示した論理回路 801 のような論理回路を用いて実施できる。次に同期停止信号は、受信した同期リクエストおよび設定に応じてアサートされるかデアサートされてよい (ブロック 1504)。いくつかの実施形態では、図 8 の論理回路 801 のような論理回路が、1 つ以上の同期リクエストと設定情報を論理的に合わせて、所与の停止信号をいつアサートまたはデアサートすべきかを判断できる。いくつかの実施形態では、2 つ以上の同期停止信号を任意の所与の時間にアサートしデアサートできる点に注意されたい。次に本方法はブロック 1505 で終了できる。図 15 に示したフローチャートには、そこに描いた動作の単一の適用例を示しているが、様々な実施形態では、図 15 の方法をマルチプロセッサシステムの動作中に常時実施してよい。

20

#### 【0102】

図 15 に示した方法は単なる一例であることに注意されたい。他の実施形態では、異なる数の同期リクエストおよび設定データビットが可能であり、構想される。

#### 【0103】

30

マルチプロセッサシステム内の 2 つのグループのプロセッサを同期させる方法の一実施形態を描いたフローチャートを図 16 に示している。本方法はブロック 1601 から始まる。次に、マルチプロセッサシステムの第 1 のグループのプロセッサの同期を開始できる (ブロック 1602)。いくつかの実施形態では、第 1 のグループのプロセッサの同期は、図 13 および図 15 に記載した方法に関して前述した同期に似た動作を含んでいてよい。第 1 のグループは、様々な実施形態では、マルチプロセッサシステムの 1 つ以上のプロセッサを備えていてよい。いくつかの実施形態では、マルチプロセッサシステムのプロセッサの第 1 のグループの同期は、複数のクロックサイクルを完了するよう要求できる。

#### 【0104】

40

プロセッサの第 2 のグループの同期も開始できる (ブロック 1603)。第 1 のグループの同期と同じく、プロセッサの第 2 のグループの同期は、図 13 および図 15 に記載した方法に関して前述した同期に似た動作を含んでいてよい。第 2 のグループは、様々な実施形態では、第 1 のグループに含まれるプロセッサを排除するマルチプロセッサシステムの 1 つ以上のプロセッサを含んでいてよい。いくつかの実施形態では、1 つ以上のプロセッサは、第 1 のグループと第 2 のグループとの間で共有されてよい。第 1 のグループが同期していると、第 2 のグループの同期は、複数のクロックサイクルが完了することを要求できる。

#### 【0105】

次に本方法は、第 1 のグループおよび第 2 のグループの同期動作の状態に依存してよい (ブロック 1604)。同期動作の一方または両方ともが完了していないとき、2 つのグ

50

ループのプロセッサによるその先の実行が停止したままになる（ブロック 1605）。両方の同期動作が完了すると、第1のグループのプロセッサは、プログラム命令の実行を再開できる（ブロック 1606）。第2のグループのプロセッサは、プログラム命令の実行も再開できる（ブロック 1607）。両グループのプロセッサが実行を再開すると、本方法はブロック 1608 を終了できる。実行を再開する2つの動作は、連続する形で実施されるように描かれている点に注意されたい。他の実施形態では、これらの動作は、並列または逆の順序で実施されてもよい。代替実施形態でその他の動作およびその他の順序の動作を用いてもよい。

#### 【0106】

図17には、マルチプロセッサシステムにある2セットのプロセッサを同期させる方法の一実施形態を描いたフローチャートを示している。本方法はブロック 1701 から始まる。次に、マルチプロセッサシステムの第1セットのプロセッサを同期させることができる（ブロック 1702）。いくつかの実施形態では、同期は、図13および図15に記載した方法に関して前述した同期に似た動作を含んでいてよい。第1セットのプロセッサに含まれる各プロセッサは、様々な実施形態では、例えば図8に示した同期コントローラのような共通の同期コントローラに接続されてよい。

10

#### 【0107】

マルチプロセッサシステムの第1セットのプロセッサが同期すると、次にマルチプロセッサシステムの第2セットのプロセッサを同期させることができる（ブロック 1703）。様々な実施形態では、第2セットの各プロセッサは、共通の同期コントローラに接続されてよい。第1セットのプロセッサを同期させた状態で、第2セットのプロセッサの同期は、図13および図15に記載した方法に関して前述した同期に似た動作を含んでいてよい。

20

#### 【0108】

第2セットのプロセッサの同期が完了すると、第1セットのプロセッサから1つのプロセッサを第2セットのプロセッサの1つのプロセッサと同期させることができる（ブロック 1704）。いくつかの実施形態では、第1セットのプロセッサからのプロセッサ、および第2セットのプロセッサからのプロセッサは、共通の同期コントローラに接続されてよい。

#### 【0109】

30

第1セットからのプロセッサおよび第2セットからのプロセッサが同期すると、第1セットのプロセッサを再同期させることができる（ブロック 1705）。次に第2セットのプロセッサを再同期させることができる（ブロック 1706）。2つの再同期動作は、連続する形で実施するように示しているが、他の実施形態では、動作は並列または逆の順序で実施してよい点に注意されたい。本方法はブロック 1707 で終了できる。図17に描いた方法を用いることによって、様々な実施形態では、マルチプロセッサシステムのどのような数のプロセッサも同期させることができる。

#### 【0110】

図17のフローチャートに描いた方法は単なる一例であることに注意されたい。他の実施形態では、異なる動作および異なる順序の動作が可能であり、構想される。

40

#### 【0111】

マルチプロセッサシステムの2セットのプロセッサを同期させる方法のもう1つの実施形態を図18のフローチャートに示している。本方法はブロック 1801 から始まる。次に、第1セットのプロセッサのマルチプロセッサシステムを同期させることができる（ブロック 1802）。いくつかの実施形態では、同期は、図13および図15に記載した方法に関して前述した同期に似た動作を含んでいてよい。第1セットのプロセッサに含まれる各プロセッサは、様々な実施形態では、例えば図8に示した同期コントローラのような共通の同期コントローラに接続されてよい。

#### 【0112】

マルチプロセッサシステムの第1セットのプロセッサが同期すると、次にマルチプロセ

50

ツサシステムの第2セットのプロセッサを同期させることができる（ブロック1803）。様々な実施形態では、第2セットの各プロセッサは、共通の同期コントローラに接続されてよく、第2セットのプロセッサに含まれる少なくとも1つのプロセッサも第1セットのプロセッサに含まれる。第1セットのプロセッサを同期させた状態で、第2セットのプロセッサの同期は、図13および図15に記載した方法に関して前述した同期に似た動作を含んでいてよい。

#### 【0113】

マルチプロセッサシステムの第2セットのプロセッサの同期が完了すると、次に第1セットのプロセッサを再同期させることができる（ブロック1804）。いくつかの実施形態では、第1セットおよび第2セットのプロセッサに少なくとも1つのプロセッサを含むことによって、第1と第2の両方のセットにある全プロセッサを同期させることができ可能になる。第1セットのプロセッサの再同期が完了すると、本方法はブロック1805で終了できる。図18に描いた方法を用いることによって、様々な実施形態では、マルチプロセッサシステムのどのような数のプロセッサも同期させることができる。

10

#### 【0114】

図18に示したフローチャートは単なる一例であることに注意されたい。他の実施形態では、代替動作を用いてよい。

#### 【0115】

マルチプロセッサシステムに対してソフトウェアを設計する方法の一実施形態を描いたフローチャートを図19に示している。本方法はブロック1901から始まる。次にソフトウェアを、例えば図3に示したマルチプロセッサIC300のようなマルチプロセッサシステムに対して設計できる（ブロック1902）。ソフトウェアは、様々な実施形態では、プロセッサのアレイ上にマッピングできるグラフィックスや映像データ、またはその他の任意の適切なアプリケーションを処理するためのアプリケーションを含んでいてよい。いくつかの実施形態では、他の命令スレッドとの同期を要求する個々のプロセッサの命令スレッド内での場所を特定できる。前述したもののような同期命令は、命令スレッドに挿入して同期バリアを形成できるとともに、マルチプロセッサシステム内にある1つ以上のプロセッサの間での同期を可能にすることができます。

20

#### 【0116】

同期命令が挿入されると、設定データを設計できる（ブロック1903）。いくつかの実施形態では、設定データは、同期コントローラが、この同期コントローラに接続している1つ以上のプロセッサから同期リクエストを受け入れることができる設定データビットを含んでいてよい。所与の1セットの設定ビットの各ビットは、いくつかの実施形態では、接続しているプロセッサへ向かう対応する方向を表していてよいが、他の実施形態では、所与の1セットの設定ビットは、同期を入力するために許された方向を決定するために復号化されてよい。

30

#### 【0117】

次に、設定データをマルチプロセッサシステムにロードできる（ブロック1905）。いくつかの実施形態では、設定データの一部を、例えば図8に示したレジスタ805のようなコントローラ内のレジスタにロードできる。設定データは、他の実施形態では、マルチプロセッサシステム内の1つ以上のメモリにロードできる。

40

#### 【0118】

次に、設計したソフトウェアをマルチプロセッサシステムにロードできる（ブロック1905）。いくつかの実施形態では、ソフトウェアをマルチプロセッサシステム内にある1つ以上の共有メモリにロードできる。ソフトウェアは、他の実施形態では、小分けでき、ソフトウェアの個々のパートをマルチプロセッサシステム内のローカルメモリにロードできる。このようなローカルメモリそれぞれをマルチプロセッサシステム内の対応するプロセッサに接続できる。

#### 【0119】

設定データおよびソフトウェアがマルチプロセッサシステムにロードされると、ソフト

50

ウェアを実行できる（ブロック 1906）。実行中、各プロセッサは、挿入された同期命令を実行して、命令スレッド内に前もって特定された場所で、プロセッサの様々なサブセット、または様々なプロセッサにそれ自体の動作を同期させることができる。ソフトウェアの実行が完了すると、本方法はブロック 1907 で終了できる。

【0120】

図 19 のフローチャートに示した動作のいくつかは、連続する形で実施されているように描かれている点に注意されたい。他の実施形態では、1 つ以上の動作を並列に実施できる。

【0121】

本発明のシステムおよび方法を好適な実施形態に結びつけて記載してきたが、本発明は本明細書に記載した特定の形態に限定されることを意図しているわけではなく、逆にそのような代替案、修正、および均等物は、付属の特許請求の範囲に規定した本発明の精神および範囲内に正当に含まれてよいため、これを範囲に含めることを意図している。 10

【図 1】

FIG. 1

【図 2 A】

FIG. 2A

【図 2 B】

FIG. 2B

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG. 10

【図 1 1】

【図 1 2】

FIG. 11

FIG. 12

【図 1 3】

【図 1 4】

FIG. 13

FIG. 14

【図15】

FIG. 15

【図16】

FIG. 16

【図17】

FIG. 17

【図18】

FIG. 18

【図19】

FIG. 19

---

フロントページの続き

(72)発明者 マリク , アフザル・エム

アメリカ合衆国・78726・テキサス州・オースティン・ピークストン ドライブ・10205

(72)発明者 フォークナー , ケネス・アール

アメリカ合衆国・78739・テキサス州・オースティン・ロスト カヴァーン コーヴ・380

9

(72)発明者 ソルカ ,マイケル・ビイ

アメリカ合衆国・78731・テキサス州・オースティン・キャット マウンテン コーヴ・62

09

審査官 漆原 孝治

(56)参考文献 米国特許出願公開第2012/0137119(US, A1)

特表2005-531089(JP, A)

特開平02-238553(JP, A)

特開平02-264352(JP, A)

特開平07-200486(JP, A)

(58)調査した分野(Int.Cl. , DB名)

G06F 15/173

G06F 9/52