(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5259755号

(P5259755)

(45) 発行日 平成25年8月7日(2013.8.7)

(24) 登録日 平成25年5月2日(2013.5.2)

(51) Int.Cl.

F 1

**G06F 12/16 (2006.01)**G06F 12/16 320K

G06F 12/00 571A

G06F 12/00 597U

G06F 12/16 310C

G06F 12/16 310A**G06F 12/00 (2006.01)**

請求項の数 11 (全 19 頁)

(21) 出願番号

特願2011-40470 (P2011-40470)

(22) 出願日

平成23年2月25日(2011.2.25)

(65) 公開番号

特開2012-178039 (P2012-178039A)

(43) 公開日

平成24年9月13日(2012.9.13)

審査請求日

平成25年2月25日(2013.2.25)

早期審査対象出願

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100159651

弁理士 高倉 成男

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100075672

弁理士 峰 隆司

最終頁に続く

(54) 【発明の名称】 マルチチャネルを有するメモリ装置及び同装置におけるメモリアクセス方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のチャネルを介してアクセスされるメモリと、

複数のアクセスコマンドに従って前記メモリに前記複数のチャネルを介して並行してアクセスするメモリインタフェースと、

前記メモリにブロック単位でアクセスするための所定のアクセス処理において、チャネル別のアクセスコマンドの群を前記メモリインタフェースに逐次投機的に投入するコマンド生成手段と、

前記メモリインタフェースによる前記複数のチャネルを介してのメモリアクセスのいずれかでエラーが発生した場合、既に投入されている未実行のアクセスコマンドの系列を、10

バージレスポンスにより返却するバージ手段と、

前記所定の処理におけるアクセスコマンドのコマンド進捗情報をによりチャネル別に管理するコマンド進捗管理手段であって、各チャネルにおけるコマンド進捗が、前記返却された未実行のアクセスコマンドの系列のうちの最も古い未実行のアクセスコマンドの指定する位置に戻されるように、前記コマンド進捗情報を更新するコマンド進捗管理手段とを具備し、

前記コマンド生成手段は、前記更新されたコマンド進捗情報を基づいて、前記返却された最も古い未実行のアクセスコマンドを含むチャネル別のアクセスコマンドの群を前記メモリインタフェースに投入する

メモリ装置。

**【請求項 2】**

前記複数のチャネルにおけるアクセスコマンドの進捲を統括的に管理することにより、

ロックの区切りを検出する進捲統括管理手段を更に具備する請求項 1 記載のメモリ装置。

。

**【請求項 3】**

前記コマンド生成手段は、次に投入されるべきアクセスコマンドが、対応するチャネル

における最終アクセスコマンドであるならば、前記最終アクセスコマンドに、当該最終ア

クセスコマンドの実行に成功した場合に対応するコマンドレスポンスを返すことを指定す

る特定の指定情報を設定する請求項 2 記載のメモリ装置。

**【請求項 4】**

前記進捲統括管理手段は、前記複数のチャネルにそれぞれ対応する最終アクセスコマン

ドの群が投入された状態で、前記最終アクセスコマンドの群に対応するコマンドレスポン

スの群が返却されているかを判定することにより、前記ロックの区切りを検出する請求

項 3 記載のメモリ装置。

**【請求項 5】**

前記複数のチャネルのうちの第 1 のチャネルを介してのメモリアクセスでエラー訂正符

号に基づく訂正が不能なエラーが発生した場合、前記ロックのエラーページ内のエラー

箇所を、チャネル間誤り訂正によって訂正するチャネル間誤り訂正手段と、

前記チャネル間誤り訂正の結果に基づいて、前記ロックのページ毎にチャネル間誤り

訂正状態を管理するチャネル間誤り訂正状態管理手段とを更に具備し、

。

前記コマンド進捲管理手段は、少なくとも前記第 1 のチャネルにおけるコマンド進捲位

置が、前記エラーページの次のページの先頭位置にスキップされるように、前記コマン

ド進捲情報を更新する請求項 1 記載のメモリ装置。

**【請求項 6】**

前記コマンド進捲管理手段は、前記複数のチャネルのうち前記エラーページをコマンド

進捲位置とする前記第 1 のチャネルとは異なる第 2 のチャネルにおける次のコマンド進捲

位置も、前記エラーページの次のページの先頭位置にスキップされるように、前記コマン

ド進捲情報を更新する請求項 5 記載のメモリ装置。

**【請求項 7】**

複数のチャネルを介してアクセスされるメモリと、複数のアクセスコマンドに従って前

記メモリに前記複数のチャネルを介して並行してアクセスするメモリインタフェースとを

備えたメモリ装置において、所定のアクセス処理により前記メモリにロック単位でア

クセスするためのメモリアクセス方法であって、

。

チャネル別のアクセスコマンドの群を前記メモリインタフェースに逐次投機的に投入し

、

前記メモリインタフェースによる前記複数のチャネルを介してのメモリアクセスのいづ

れかでエラーが発生した場合、既に投入されている未実行のアクセスコマンドの系列を、

ページレスポンスにより返却し、

各チャネルにおけるコマンド進捲が、前記返却された未実行のアクセスコマンドの系列

のうちの最も古い未実行のアクセスコマンドの指定する位置に戻されるように、前記所定

の処理におけるアクセスコマンドの進捲を管理するためのコマンド進捲情報を更新し、

。

前記更新されたコマンド進捲情報に基づいて、前記返却された最も古い未実行のア

クセスコマンドを含むチャネル別のアクセスコマンドの群を前記メモリインタフェースに投入

する

メモリアクセス方法。

**【請求項 8】**

次に投入されるべきアクセスコマンドが、対応するチャネルにおける最終アクセスコマ

ンドであるならば、前記最終アクセスコマンドに、当該最終アクセスコマンドの実行に成

功した場合に対応するコマンドレスポンスを返すことを指定する特定の指定情報を設定す

る請求項 7 記載のメモリアクセス方法。

。

10

20

30

40

50

**【請求項 9】**

前記複数のチャネルにそれぞれ対応する最終アクセスコマンドの群が投入された状態で、前記最終アクセスコマンドの群に対応するコマンドレスポンスの群が返却されているかを判定することにより、前記ブロックの区切りを検出する請求項 8 記載のメモリアクセス方法。

**【請求項 10】**

前記複数のチャネルのうちの第 1 のチャネルを介してのメモリアクセスでエラー訂正符号に基づく訂正が不能なエラーが発生した場合、前記ブロックのエラーページ内のエラー箇所を、チャネル間誤り訂正によって訂正し、

前記チャネル間誤り訂正の結果に基づいて、前記ブロックのページ毎にチャネル間誤り訂正状態を管理し、

少なくとも前記第 1 のチャネルにおけるコマンド進捗位置が、前記エラーページの次のページの先頭位置にスキップされるように、前記コマンド進捗情報を更新する

請求項 7 記載のメモリアクセス方法。

**【請求項 11】**

前記複数のチャネルのうち前記エラーページをコマンド進捗位置とする前記第 1 のチャネルとは異なる第 2 のチャネルにおける次のコマンド進捗位置も、前記エラーページの次のページの先頭位置にスキップされるように、前記コマンド進捗情報を更新する請求項 10 記載のメモリアクセス方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明の実施形態は、マルチチャネルを有するメモリ装置及び同装置におけるメモリアクセス方法に関する。

**【背景技術】****【0002】**

従来から、NAND フラッシュメモリに代表されるメモリを備え、複数のアクセスコマンドを並行して実行するマルチチャネルを有するメモリ装置が知られている。一方、NAND フラッシュメモリのようなフラッシュメモリのデータ保持力 (data retention) は比較的弱いことが知られている。そのため、フラッシュメモリに格納されたデータの品質は、例えば時間の経過に応じて低下する可能性がある。

**【0003】**

そこで、フラッシュメモリを備えた従来のメモリ装置では、当該フラッシュメモリに格納されたデータが長時間放置されることに起因するデータ化けを適宜検査するためのパトロール処理が実行される。このパトロール処理は、リードアクセスを伴い、メモリコントローラによって例えばブロック単位に行われる。データ化け（品質の低下）が検出された場合、対応するブロックのデータはフラッシュメモリ内の別のブロックに書き換えられる。これにより、品質の低下が検出されたブロックのデータがリフレッシュされる。

**【0004】**

パトロール処理では、検査（パトロール）されるべきブロックの全領域に効率的にリードアクセスするために、複数のアクセスコマンド（リードコマンド）が投機的に発行される。つまり、先行するアクセスコマンド群の実行完了を待たずに、後続のアクセスコマンド群が発行される。そこでメモリコントローラは、アクセスコマンド群に従うリードアクセスでエラーが発生した場合に対処するために、発行された全アクセスコマンドを記録するように構成されている。このことは、パトロール処理に限らない。例えば、ホストからの要求により、フラッシュメモリに格納されているデータ（ユーザデータ）をメモリ装置自身が診断する自己診断処理においても同様である。また、繰り返しリードに起因する周辺ページのデータ化けを検出して、当該周辺ページをリフレッシュするためのリフレッシュ処理においても同様である。

**【0005】**

10

20

30

40

50

ところで、フラッシュメモリ内のブロックのデータを書き換えている最中に、当該フラッシュメモリを備えたメモリ装置の電源が遮断する可能性がある。この場合、データ書き換えは正常に終了しなかった可能性がある。そこで、フラッシュメモリ内のブロックのデータ書き換えが発生した場合に、当該データ書き換えの進捗状態を示す情報（データ書き換え進捗情報）を記録するように構成されたメモリ装置も知られている。このメモリ装置は、電源が再度投入された際に、電源遮断時におけるデータ書き換え進捗状態を示す情報に基づいて、データ書き換えが正常に終了しなかったブロックのデータを復旧する。

【先行技術文献】

【特許文献】

【0006】

10

【特許文献1】特開2005-56144号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

20

上記したように、フラッシュメモリを備えた従来のメモリ装置は、ブロックの全領域を対象とするリード／ライト処理（つまりメモリアクセス処理）において、投機的に発行される全てのアクセスコマンドを記録するように構成されている。このため従来のメモリ装置は、全アクセスコマンドを記録するためのメモリ領域（つまり管理領域）を必要とする。このことは、フラッシュメモリ以外のメモリを備えたメモリ装置でも、投機的に発行される複数のアクセスコマンドを並行して実行するメモリ装置であれば同様である。

【0008】

20

本発明の目的は、ブロック単位のメモリアクセス処理を、小容量のメモリ領域を用いた管理で高速に実行できる、マルチチャネルを有するメモリ装置及び同装置におけるメモリアクセス方法を提供することである。

【課題を解決するための手段】

【0009】

30

実施形態によれば、メモリ装置は、メモリと、メモリインターフェースと、コマンド生成手段と、ページ手段と、コマンド進捗管理手段とを具備する。前記メモリは、複数のチャネルを介してアクセスされる。前記メモリインターフェースは、複数のアクセスコマンドに従って前記メモリに前記複数のチャネルを介して並行してアクセスする。前記コマンド生成手段は、前記メモリにブロック単位でアクセスするための所定のアクセス処理において、チャネル別のアクセスコマンドの群を前記メモリインターフェースに逐次投機的に投入する。前記ページ手段は、前記メモリインターフェースによる前記複数のチャネルを介してのメモリアクセスのいずれかでエラーが発生した場合、既に投入されている未実行のアクセスコマンドの系列を、ページレスポンスにより返却する。前記コマンド進捗管理手段は、前記所定の処理におけるアクセスコマンドのコマンド進捗をコマンド進捗情報によりチャネル別に管理するコマンド進捗管理手段であって、各チャネルにおけるコマンド進捗が、前記返却された未実行のアクセスコマンドの系列のうちの最も古い未実行のアクセスコマンドの指定する位置に戻されるように、前記コマンド進捗情報を更新する。前記コマンド生成手段は、前記更新されたコマンド進捗情報に基づいて、前記返却された最も古い未実行のアクセスコマンドを含むチャネル別のアクセスコマンドの群を前記メモリインターフェースに投入する。

40

【図面の簡単な説明】

【0010】

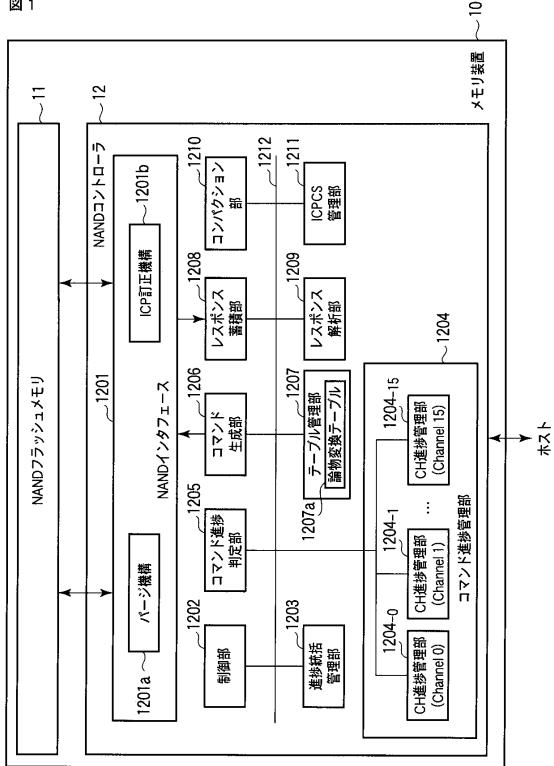

【図1】一つの実施形態に係るマルチチャネルを有するメモリ装置の典型的な構成を示すブロック図。

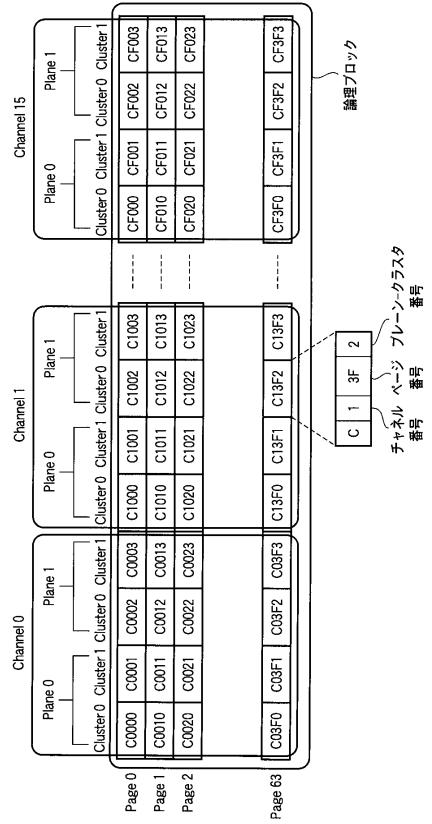

【図2】同実施形態において、1論理ブロックを対象に自己診断処理が実行される場合に生成される4,096のアクセスコマンドの例を、ページ、チャネル、ブレーン及びクラスタと対応付けて示す図。

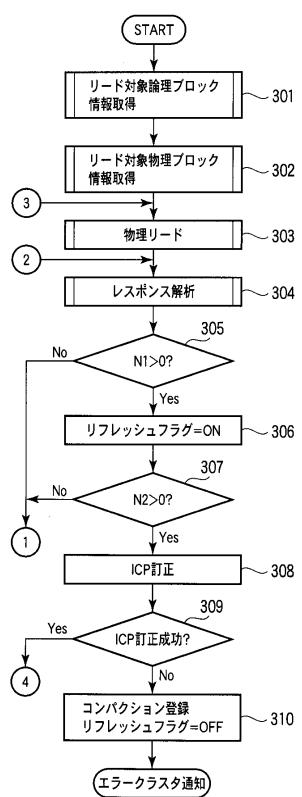

【図3】同実施形態で適用される自己診断処理の手順を説明するためのフローチャートの

50

一部を示す図。

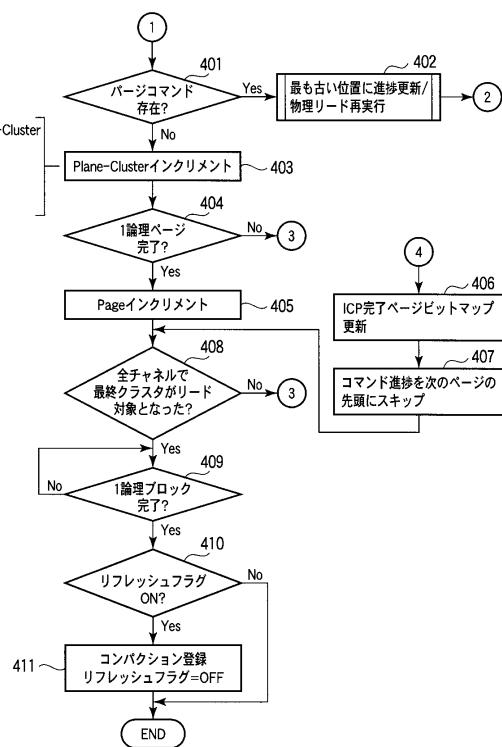

【図4】同実施形態で適用される自己診断処理の手順を説明するためのフローチャートの残りを示す図。

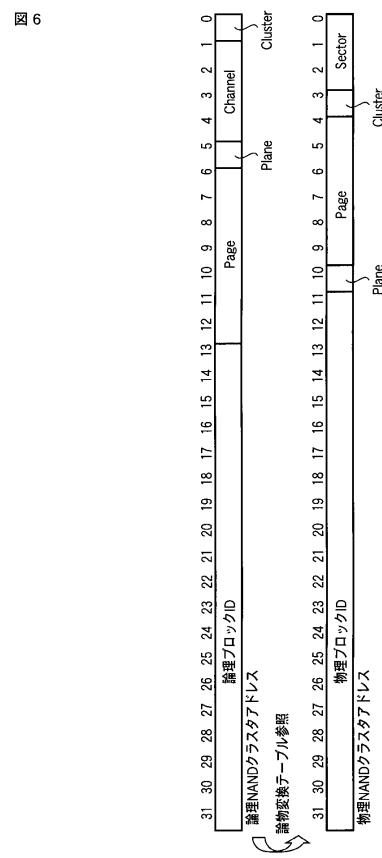

【図5】同実施形態で適用される論理アドレス及び物理アドレスのフォーマットの例を示す。

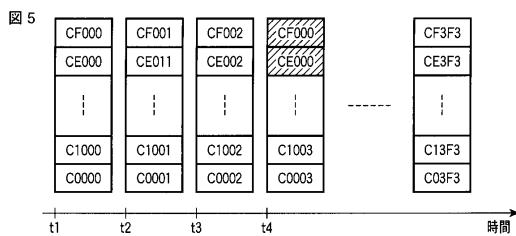

【図6】同実施形態においてコマンド生成部によって逐次投入されるリードコマンド群の時系列の一例を示す図。

**【発明を実施するための形態】**

**【0011】**

以下、実施の形態につき図面を参照して説明する。

10

図1は一つの実施形態に係るマルチチャネルを有するメモリ装置の典型的な構成を示すプロック図である。本実施形態において、図1に示すメモリ装置10は、例えばホスト(図示せず)と接続されている。ホストは、メモリ装置10を自身の記憶装置として利用する。

**【0012】**

メモリ装置10は、NANDフラッシュメモリ11とNANDコントローラ12とを備えている。NANDフラッシュメモリ11は、ユーザデータを記憶するための記憶媒体である。NANDフラッシュメモリ11は、複数のNANDフラッシュメモリチップを備えており、複数のアクセスコマンドに応じてNANDコントローラ12によって並行してアクセス可能なように構成されている。なお、複数のアクセスコマンドに応じて並行してアクセス可能であれば、NANDフラッシュメモリ11に代えて、NANDフラッシュメモリ以外のメモリを用いても構わない。

20

**【0013】**

NANDコントローラ12は、ホストからの要求に応じてNANDフラッシュメモリ11にアクセスする。NANDコントローラ12はまた、例えば自己診断処理、パトロール処理、或いはリフレッシュ処理のような、プロック単位でのメモリアクセス処理のために、NANDフラッシュメモリ11にアクセスする。ここでは、自己診断処理が行われることを前提とする。

**【0014】**

NANDコントローラー12は、NANDインターフェース1201と、制御部1202と、進捗統括管理部1203と、コマンド進捗管理部1204と、コマンド進捗判定部1205と、コマンド生成部1206と、テーブル管理部1207と、レスポンス蓄積部1208と、レスポンス解析部1209と、コンパクション部1210と、チャネル間誤り訂正状態管理部(以下、ICPCS管理部と称する)1211とを備えている。制御部1202、進捗統括管理部1203、コマンド進捗管理部1204、コマンド進捗判定部1205、コマンド生成部1206、テーブル管理部1207、レスポンス蓄積部1208、レスポンス解析部1209、コンパクション部1210、及びICPCS管理部1211の各部(モジュール)は、内部バス1212によって相互接続されている。

30

**【0015】**

NANDインターフェース1201は、NANDフラッシュメモリ11とコマンド生成部1206及びレスポンス蓄積部1208との間で情報を授受する。NANDインターフェース1201はページ機構1201a及びチャネル間誤り訂正機構(以下、ICP訂正機構と称する)1201bを備えている。

40

**【0016】**

ページ機構1201aは、投入されたアクセスコマンドの実行でエラーが発生した場合に、未実行の全てのアクセスコマンドを、特別のコマンドレスポンス(以下、ページレスポンスと称する)によってレスポンス蓄積部1208に戻す。ICP訂正機構1201bは、エラー訂正符号(ECC)で訂正不能なエラーが発生した場合に、エラー箇所をチャネル間のデータに基づいて訂正する。この訂正を、チャネル間誤り訂正(ICP訂正)と呼ぶ。

50

**【0017】**

制御部1202は内部バス1211を介して接続された、上記各モジュールの動作を制御する。進捲統括管理部1203は、処理単位（自己診断処理単位）のコマンド進捲を管理する。進捲統括管理部1203は、コマンド進捲管理部1204によって管理されるチャネル別のコマンド進捲状態を統括的に管理し、処理単位の区切り（例えば、1論理ブロックの完了）を判定する。

**【0018】**

コマンド進捲管理部1204は、論理ブロック単位で且つチャネル別に実行されるアクセス処理（ここでは、自己診断処理のためのアクセス処理）において、1論理ブロックを処理するためにNANDインターフェース1201にチャネル別に投機的に発行されるアクセスコマンドの進捲（つまりアクセスコマンド投入の進捲）を管理する。コマンド進捲管理部1204は、このチャネル別のアクセスコマンド投入の進捲（以下、コマンド進捲と称する）を管理するためのコマンド進捲情報を保持する。チャネル別のコマンド進捲情報は、DRAMのようなメモリの領域に格納される。

10

**【0019】**

チャネル別のコマンド進捲情報は、（ページ番号、プレーン番号、クラスタ番号）から構成される。より詳細には、チャネル別のコマンド進捲情報は、（ページ番号、プレーン-クラスタ番号）から構成される。チャネル別のコマンド進捲情報は、対応するチャネルに次に投入されるべき（または最も最近に投入された）アクセスコマンドによって指定される物理ブロック内の相対位置（ページ、プレーン、クラスタ）、つまりコマンド進捲位置を示す。このチャネル別のコマンド進捲情報は、上記指定される物理ブロックが割り当てられる論理ブロック内のチャネル別の相対位置（以下、単に位置と称する）をも示す。ページ番号、プレーン番号、クラスタ番号及びプレーン-クラスタ番号と、ページ、プレーン及びクラスタとについては後述する。

20

**【0020】**

本実施形態では、NANDインターフェース1201は、詳細を後述するように16のチャネル0, 1, ..., 14, 15を有している。そこで、コマンド進捲管理部1204は、16のチャネル0, 1, ..., 14, 15に対応するチャネル別コマンド進捲管理部（以下、CH進捲管理部と称する）1204-0, 1204-1, ..., 1204-14, 1204-15から構成される。CH進捲管理部1204-i（i = 0, 1, ..., 14, 15）は、チャネルiに発行されるアクセスコマンドの進捲を管理し、当該チャネルiに対応するコマンド進捲情報（ページ番号、プレーン-クラスタ番号）を保持する。

30

**【0021】**

コマンド進捲判定部1205は、後述するコマンドレスポンスに基づいてチャネル別に最も古い位置（ページ、プレーン及びクラスタ）を特定し、特定された位置に基づいてコマンド進捲の更新が必要かを判定する。最も古い位置とは、対応するチャネルに投入された未実行のアクセスコマンドの系列のうち最も古いアクセスコマンドの指定する位置を指す。

**【0022】**

コマンド生成部1206は、NANDフラッシュメモリ11にアクセスするための複数のアクセスコマンドを、NANDインターフェース1201に対してチャネル別に投機的に発行する。コマンド生成部1206は、チャネル別のアクセスコマンドの発行を、コマンド進捲管理部1204によって管理されているチャネル別のコマンド進捲情報に基づいて実行する。

40

**【0023】**

テーブル管理部1207は、論理アドレスを物理アドレスに変換するための論理-物理アドレス変換テーブル（以下、論物変換テーブルと称する）1207aを備えている。本実施形態において、論物変換テーブル1207aは、DRAMのようなメモリの領域に構築されている。テーブル管理部1207は、例えば自己診断処理を行う際に、処理対象となる論理ブロックのアドレス（論理アドレス）を、論物変換テーブル1207aに基づい

50

て対応する物理ブロックのアドレス（物理アドレス）に変換する。処理対象となる論理ブロックの論理アドレスは、当該論理ブロックを識別するための論理ブロックIDとコマンド進捲情報（ページ番号、ブレーン・クラスタ番号）とから特定できる。テーブル管理部1207はまた、論理ブロック（論理ブロックID）毎に、対応する論理ブロックの状態を示す情報（以下、論理ブロック情報と称する）を保持している。論理ブロック情報は、対応する論理ブロックが、使われている論理ブロック（つまりアクティブ論理ブロック）であるかを示す情報を含む。

#### 【0024】

レスポンス蓄積部1208は、コマンド生成部1206によってNANDインターフェース1201に投入されたアクセスコマンドに対する当該NANDインターフェース1201からのレスポンス（以下、コマンドレスポンスと称する）を蓄積する。コマンドレスポンスのうち、エラーを通知するコマンドレスポンスを、エラーレスポンスと呼ぶこともある。レスポンス蓄積部1208はまた、上述のバージレスポンスもコマンドレスポンスとして蓄積する。

#### 【0025】

レスポンス蓄積部1208は、例えば先入れ先出しバッファを用いて構成される FIFO構造を有する。レスポンス蓄積部1208はライトポインタ及びリードポインタによって管理される。ライトポインタは、次にNANDインターフェース1201から返却されるコマンドレスポンスが蓄積されるべきレスポンス蓄積部1208内の位置を示す。リードポインタは、レスポンス解析部1209によって次に解析されるべきコマンドレスponsが蓄積されているレスポンス蓄積部1208内の位置を示す。

#### 【0026】

レスポンス解析部1209は、NANDインターフェース1201によって返却されて、レスポンス蓄積部1208に蓄積されたコマンドレスポンスのうち、リードポインタの指示するコマンドレスポンスを解析する。レスポンス解析部1209は、リードポインタの指示するコマンドレスポンスを解析し終えると、当該リードポインタをレスポンス蓄積部1208内の次の位置を指示するように進める。

#### 【0027】

コンパクション部1210は、自己診断処理において論理ブロックのデータの別ブロックへの移動が必要と判定された場合、コンパクション処理を実行する。つまりコンパクション部1210は、コンパクション処理の対象となる論理ブロックの論理ブロックIDが登録された場合、コンパクション処理を実行する。このコンパクション処理により、論理ブロックIDによって示される論理ブロックに現在割り当てられているNANDフラッシュメモリ11内の第1の物理ブロック群のデータが当該NANDフラッシュメモリ11内の別の第2の物理ブロック群に書き換えられる。このデータの書き換えの後、論理ブロックIDによって示される論理ブロックに割り当てられる物理ブロック群が、第1の物理ブロック群から第2の物理ブロック群に変更される。

#### 【0028】

ICPCS管理部1211は、論理ブロックIDによって示される論理ブロック内のICP訂正が実行された論理ページ（ここでは論理ページ0乃至63のいずれか）を管理する。本実施形態において、ICPCS管理部1211は、論理ページ0乃至63のICP訂正の完了の有無を、64ビット長のビットマップ（以下、ICP完了ページビットマップと称する）で管理する。ICP完了ページビットマップは、DRAMのようなメモリの領域に格納される。

#### 【0029】

次に、本実施形態におけるメモリ装置10の動作について、自己診断処理を例に説明する。

まず本実施形態では、以下の前提条件（1）乃至（6）の下で、メモリ装置10が稼動しているものとする。

（1）コマンド生成部1206は、NANDインターフェース1201に同時に複数のア

10

20

30

40

50

クセスコマンドを投入できる。コマンド生成部 1206 から NAND インタフェース 1201 に同時に投入可能な最大アクセスコマンド数は、メモリ装置 10 の起動時に設定される。本実施形態では、NAND インタフェース 1201 は、16 のチャネル 0, 1, ..., 15 を有しており、コマンド生成部 1206 は最大 16 チャネル分のアクセスコマンドを同時に発行できる。チャネル 0, 1, ..., 15 のチャネル番号は、それぞれ、0, 1, ..., 15 (10 進数表現) である。

#### 【0030】

(2) 1論理ブロックは 64 のページ (論理ページ) 0, 1, ..., 63 で構成され、アクセス (ここではリードアクセス) は 1 ページの半分のクラスタ単位で行われるものとする。つまりアクセスはクラスタ 0, 1 に分けて行われるものとする。ページ 0, 1, ..., 63 のページ番号は、それぞれ、0, 1, ..., 63 (10 進数表現) である。クラスタ 0, 1 のクラスタ番号は、それぞれ 0, 1 (10 進数表現) である。10

#### 【0031】

(3) チャネル 0, 1, ..., 15 の各々は、2 つのプレーン 0, 1 に接続されている。各チャネルを介してのアクセス処理 (ここではリード処理) は、1 ページあたり 2 (プレーン) × 2 (クラスタ) の 4 回に分けて実行される。

#### 【0032】

(4) アクセスコマンド (ここではリードコマンド) は、チャネル毎に投入された順番で実行オーダーが保証されている。

(5) あるチャネル  $i$  でエラーが発生した場合、未実行のコマンドは全てページされる20。

(6) ECC で訂正不能なエラーが、I C P 訂正機構 1201b を用いて訂正される。

#### 【0033】

図 2 は、上記の前提条件の下で、1 論理ブロックを対象に自己診断処理が実行される場合に生成される 4, 096 (64 × 16 × 4) のアクセスコマンド C0000, C0001, C0002, C0003, C1000, C1001, C1002, C1003, ..., CF3F0, CF3F1, CF3F2, CF3F3 を、ページ 0, 1, ..., 63、チャネル 0, 1, ..., 15、プレーン 0, 1 及びクラスタ 0, 1 と対応付けて示す。図 2 の例では、1 論理ブロックに 32 の物理ブロックが割り当てられる。32 の物理ブロックは、16 のチャネル 0, 1, ..., 15 のそれぞれプレーン 0, 1 に対応する。30

#### 【0034】

アクセスコマンド  $C_{pqr}$  のうち、 $C$  はアクセスコマンドを示し、 $p$  (0, 1, ..., F) はアクセスコマンド  $C_{pqr}$  が投入されるチャネルのチャネル番号を示す 1 枠の 16 進数である。アクセスコマンド  $C_{pqr}$  のうちの  $qr$  (00, 01, ..., 3F) は、アクセスされるページのページ番号を示す 2 枠の 16 進数である。

#### 【0035】

アクセスコマンド  $C_{pqr}$  のうちの  $s$  (0, 1, 2, 3) は、当該アクセスコマンド  $C_{pqr}$  が発行されるチャネル内のプレーン及びクラスタの組み合わせを特定するためのプレーン - クラスタ番号を示す 1 枠の 16 進数である。 $s = 0$  はプレーン 0 とクラスタ 0との組み合わせを、 $s = 1$  はプレーン 0 とクラスタ 1 との組み合わせを、それぞれ示す。 $s = 2$  はプレーン 1 とクラスタ 0 との組み合わせを、 $s = 3$  はプレーン 1 とクラスタ 1 との組み合わせを、それぞれ示す。このため、 $s$  (0, 1, 2, 3)、つまりプレーン - クラスタ番号は、プレーンのプレーン番号 (0, 1) 及びクラスタのクラスタ番号 (0, 1) を示していることと等価である。40

#### 【0036】

本実施形態において、論理ブロック内のページは、チャネル別に、ページ 0, 1, ..., 63 の順にアクセスされる。但し、アクセスされるページの進捗はチャネル毎に異なる。また、NAND フラッシュメモリ 11 のチャネル  $p$  ( $p$  は 16 進数表現) を介してページ  $qr$  ( $qr$  は 2 枠の 16 進数表現) にアクセスすることを指示する 4 つのアクセスコマンド  $C_{pqrs}0, C_{pqrs}1, C_{pqrs}2, C_{pqrs}3$  は、この並びの順に実行される。50

**【0037】**

具体的には、NANDフラッシュメモリ11の例えはチャネル0（0は10進数表現）を介してページ0（0は10進数表現）にアクセスすることを指示する4つのアクセスコマンドC0000, C0001, C0002, C0003は、この並びの順に実行される。また、NANDフラッシュメモリ11の例えはチャネル15（16進表現でF）を介してページ0にアクセスすることを指示する4つのアクセスコマンドCF000, CF001, CF002, CF003は、この並びの順に実行される。同様に、NANDフラッシュユメモリ11の例えはチャネル0を介してページ63（16進表現で3F）にアクセスすることを指示する4つのアクセスコマンドC03F0, C03F1, C03F2, C03F3は、この並びの順に実行される。同様に、NANDフラッシュメモリ11の例えはチャネル15（16進表現でF）を介してページ63（16進表現で3F）にアクセスすることを指示する4つのアクセスコマンドCF3F0, CF3F1, CF3F2, CF3F3は、この並びの順に実行される。

10

**【0038】**

以下、本実施形態で適用される自己診断処理の手順の概略について、1つの論理ブロックを対象とする自己診断処理を例に説明する。自己診断処理の対象となる論理ブロックは、リードアクセスの対象となる。そこで以下の説明では、自己診断処理の対象となる論理ブロックをリード対象論理ブロックと称することもある。

**【0039】**

1) NANDコントローラ12は、リード対象論理ブロック内の全クラスタの読み出しをチャネル毎に実行し、対応するクラスタのデータが正常であるかを判定する。

20

2) NANDコントローラ12は、エラー訂正不能な有効クラスタを検出した場合、ICP訂正可能か否かを判定する。訂正不可であれば、NANDコントローラ12は、リード対象論理ブロックの自己診断処理を終了し、エラークラスタを自己診断処理の要求元に通知する。

**【0040】**

3) 上記2)でICP訂正可能であれば、NANDコントローラ12は、上記1)に戻って、後続のクラスタの読み出しを行う。

4) リード対象論理ブロックの処理が終了した時点で、1つ以上のエラー訂正不能なクラスタが検出されていた場合、NANDコントローラ12は、当該リード対象論理ブロックを、コンパクション処理の対象となる論理ブロックとして登録する。

30

**【0041】**

次に上述の自己診断処理の手順の詳細について、図3及び図4のフローチャートを参照して説明する。

今、ホストから、図1のメモリ装置10のNANDコントローラ12に自己診断処理が要求されたものとする。本実施形態において自己診断処理は、ホストによって要求されたアクセス処理に対するバックグラウンド処理として行われる。つまり自己診断処理は、ホストによって要求されたアクセス処理の空き時間を利用して行われる。なお、図3及び図4のフローチャートで示される自己診断処理は、1論理ブロックを対象としている。このため、複数の論理ブロックを自己診断する場合、図3及び図4のフローチャートで示される自己診断処理は、診断されるべき論理ブロックの数だけ繰り返される。

40

**【0042】**

NANDコントローラ12の制御部1202は、自己診断処理の対象とすべき論理ブロック（つまりリード対象ブロック）をコマンド進捗管理部1204に対して指定する。この指定には、例えばリード対象論理ブロックの論理ブロックIDが用いられる。なお、図3及び図4のフローチャートでは省略されているが、自己診断処理の開始時には、コマンド進捗管理部1204に保持されるチャネル0, 1, ..., 14, 15のコマンド進捗情報は、それぞれ初期位置（ページ0, プレーン0、クラスタ0）を示すように「000」に初期化される。

**【0043】**

コマンド進捲管理部 1204 は、制御部 1202 によってリード対象論理ブロックが指定された場合、当該指定されたリード対象論理ブロックの論理ブロック情報をテーブル管理部 1207 から取得する（ステップ 301）。もし、取得された論理ブロック情報によって、リード対象論理ブロックがアクティブ論理ブロックでないことが示されている場合、当該リード対象論理ブロックの読み出し（より詳細には自己診断処理）は不要である。この場合、図 3 及び図 4 のフローチャートでは省略されているが、制御部 1202 は、現在のリード対象論理ブロックのための自己診断処理を終了する。

#### 【0044】

これに対し、取得された論理ブロック情報によって、リード対象論理ブロックがアクティブ論理ブロックであることが示されている場合、コマンド進捲管理部 1204 は、当該リード対象論理ブロックの論理ブロック ID に基づいて論物変換テーブル 1207a を参照する。これによりコマンド進捲管理部 1204 は、リード対象論理ブロックに割り当てられているリード対象物理ブロック群の情報（物理ブロック情報と称する）を取得する（ステップ 302）。物理ブロック情報は、対応する物理ブロック群（リード対象物理ブロック群）のそれぞれの ID（物理ブロック ID）を含む。

#### 【0045】

次にコマンド進捲管理部 1204 は、ステップ 302 で取得した物理ブロック情報中の物理ブロック ID と、自身が保持する現在のチャネル別のコマンド進捲情報（ページ番号、プレーン - クラスタ番号）とに基づいて、NAND フラッシュメモリ 11 内のチャネル別にアクセスされるべき物理位置を示す物理アドレスを取得する（ステップ 303）。なお、ステップ 302 で取得した物理ブロック情報により、対応する物理ブロックが NUL ブロックであることが示されている場合、コマンド進捲管理部 1204 は、対応するチャネルの現在のコマンド進捲情報を次の位置を示すように更新する。つまりコマンド進捲管理部 1204 は、対応するチャネルのコマンド進捲（ページ、プレーン、クラスタ）を次に進める。そしてコマンド進捲管理部 1204 は、上述と同様の手順で、対応するチャネルを介してアクセスされるべき物理ブロック（リード対象物理ブロック）における物理アドレスを取得する。

#### 【0046】

図 5 は、本実施形態で適用される論理アドレス及び物理アドレスのフォーマットの例を示す。論理アドレスは、対応する論理ブロックの論理ブロック ID、ページ番号、プレーン番号、チャネル番号及びクラスタ番号から構成される。論理アドレスは、メモリ装置 10 に NAND フラッシュメモリ 11 が用いられている本実施形態では、論理 NAND クラスタアドレスとも呼ばれる。物理アドレスは、対応する物理ブロックを識別するための物理ブロック ID と、プレーン番号、ページ番号、クラスタ番号及びセクタ番号から構成される。この物理アドレスは、物理 NAND クラスタアドレスとも呼ばれる。

#### 【0047】

一方、ステップ 303 において進捲統括管理部 1203 は、コマンド進捲管理部 1204 によって管理されるチャネル別のコマンド進捲状態に基づいて、コマンド進捲がリード対象論理ブロック内の最終クラスタ（より詳細には、最終ページの最終クラスタ）まで進んだかをチャネル別に判定する。進捲統括管理部 1203 は、上記チャネル別の判定結果を保持する。ステップ 303 においてコマンド生成部 1206 は、コマンド進捲管理部 1204 によって取得された物理アドレス（つまり物理 NAND クラスタアドレス）に基づいて、チャネル別に、対応する物理位置（ページ、プレーン、クラスタ）へのリードアクセスを指定したアクセスコマンド（以下、リードコマンドと称する）を生成する。生成されたリードコマンドは、図 5 に示す形式の NAND クラスタアドレス含む。

#### 【0048】

コマンド生成部 1206 は更に、チャネル別に生成されたリードコマンドのうち、所定の条件を満たしたリードコマンドに特定の指定情報を設定する。所定の条件を満たしたリードコマンドとは、進捲統括管理部 1203 によって最終クラスタ処理中であると判定された物理 NAND クラスタアドレスに対応するリードコマンド（つまり最終リードコマン

10

20

30

40

50

ド)を指す。特定の指定情報は、対応する最終リードコマンドの実行に成功した場合にコマンドレスポンス(成功レスポンス)を返却することを指定する。つまり、特定の指定情報が設定されたリードコマンドは、当該リードコマンドの実行に成功した場合にコマンドレスポンスを返却することを指定する。一方、特定の指定情報が設定されていないリードコマンド(つまり、非最終リードコマンド)は、当該リードコマンドの実行に成功した場合にコマンドレスポンスを返却しないことを暗黙に指定する。またリードコマンドは、当該リードコマンドの実行に失敗した場合、特定の指定情報が設定されているかに無関係にコマンドレスポンス(エラーレスpons)を返却することを暗黙に指定する。なお、所定の条件を満たさないリードコマンド(非最終リードコマンド)に、コマンド実行に成功した場合にコマンドレスポンスを返却しないことを明示的に指定する指定情報が設定されても構わない。

10

#### 【0049】

ステップ303において、コマンド生成部1206は、生成されたリードコマンドの群をNANDインターフェース1201に対して最大16個同時に発行する。この例のように、図3及び図4のフローチャートに従う最初のステップ303では、16のチャネル0, 1, ..., 14, 15にそれぞれ対応する16のリードコマンドC0000, C1000, ..., CE000, CF000が同時に発行される。図6はコマンド生成部1206によって逐次投入されるリードコマンド群の時系列の一例を示す。図6の例では、16のリードコマンドC0000, C1000, ..., CE000, CF000が時刻t1に発行されたことが示されている。

20

#### 【0050】

コマンド生成部1206によってNANDインターフェース1201に同時に投入されたリードコマンドC0000, C1000, ..., CE000, CF000は当該NANDインターフェース1201内のコマンドキュー(図示せず)に蓄えられる。

#### 【0051】

もし、コマンドキューが満杯でなければ、コマンド生成部1206は、後続の物理リードコマンド群をNANDインターフェース1201に投機的に投入することができる。本実施形態では、図6に示すように、時刻t1より後の時刻t2に、16のリードコマンドC0001, C1001, ..., CE001, CF001が投入され、その後の時刻t3に、16のリードコマンドC0002, C1002, ..., CE002, CF002が投入されたものとする。このように、コマンド生成部1206は、コマンドキューが満杯になるまで、後続のリードコマンド群を投機的に投入することができる。

30

#### 【0052】

NANDインターフェース1201は、自己診断処理の開始時には、コマンドキューに最初に蓄えられた16のリードコマンドC0000, C1000, ..., CE000, CF000を取り出す。そしてNANDインターフェース1201は、取り出されたリードコマンドC0000, C1000, ..., CE000, CF000に基づき、対応するチャネル0, 1, ..., 14, 15にそれぞれ接続されたブレーン0を介してNANDフラッシュメモリ11に並行してアクセスする。

40

#### 【0053】

ここで、投機的に投入されたリードコマンド群に基づくリードアクセスのいずれかでエラーが発生したものとする。本実施形態において、このエラーは、リードされたデータに付加されているECCに基づいて検出されるため、ECCエラーと呼ばれる。

#### 【0054】

ECCエラーが発生した場合、NANDインターフェース1201は、当該ECCエラーが発生したリードアクセスを指定したリードコマンドに対するコマンドレスポンスとして、エラーレスponsをレスポンス蓄積部1208に返却する。レスポンス蓄積部1208に返却されたエラーレスpons(コマンドレスpons)は、当該レスポンス蓄積部1208に蓄積される。

#### 【0055】

50

またECCエラーが発生した場合、NANDインターフェース1201のページ機構1201aは、ECCエラーが発生したチャネルに対応するコマンドキューに蓄積されている全てのコマンド（つまり、ECCエラーが発生したチャネルに投入された未実行の全てのリードコマンド）を、ページレスポンスによってレスポンス蓄積部1208に返却する。レスポンス蓄積部1208に返却されたページレスポンス（コマンドレスポンス）は、当該レスポンス蓄積部1208に蓄積される。

#### 【0056】

前述したように、自己診断処理はシステムのバックグラウンドで実行される。このため、チャネルによっては、ホストによって要求されたアクセスのためのアクセスマップが、自己診断のためのリードコマンドの実行に優先して実行されることもある。本実施形態においてNANDインターフェース1201のページ機構1201aは、ホストによって要求されたアクセスでECCエラーが発生しても、全ての未実行のコマンドを、ページレスポンスによりレスポンス蓄積部1208に返却する。10

#### 【0057】

さて、NANDインターフェース1201によってコマンドレスポンスが返却されて、当該返却されたコマンドレスポンスがレスポンス蓄積部1208に蓄積されたものとする。レスポンス解析部1209は、リードポインタによって指示されるレスポンス蓄積部1208内の位置から始まる領域に蓄積された全てのコマンドレスポンスを解析する（ステップ304）。

#### 【0058】

レスポンス解析部1209は、コマンドレスポンスの解析結果に基づき、当該解析結果にECCエラーを通知する1つ以上のエラーレスポンス（ECCエラーレスポンス）が含まれているかを判定する（ステップ305）。もし、1つ以上のエラーレスponsが含まれていた場合、つまりECCエラー数N1がゼロを超えて（ $N1 > 0$ ）場合（ステップ305のYes）、レスポンス解析部1209はリフレッシュフラグをON状態に設定する（ステップ306）。リフレッシュフラグは、論理ブロックのための自己診断処理の終了時に、当該論理ブロックをコンパクション処理の対象として登録することを指示するのに用いられる。20

#### 【0059】

次にレスポンス解析部1209は、ステップ305でECCエラーが判定されたクラスタが有効クラスタであるか否かをテーブル管理部1207に問い合わせる。有効クラスタとは、有効なデータが格納されているクラスタを指す。有効クラスタに格納されていたデータが別のクラスタに移動された場合、当該有効クラスタは無効クラスタとなる。クラスタの有効／無効はテーブル管理部1207によって管理される。30

#### 【0060】

レスポンス解析部1209は、テーブル管理部1207に問い合わせた結果に基づいて、ECCエラーが判定された有効クラスタの数（つまり有効クラスタのECCエラー数）N2がゼロを超えているかを判定する（ステップ307）。もし、有効クラスタのECCエラー数N2がゼロを超えて（ $N2 > 0$ ）ならば（ステップ307のYes）、自己診断処理はステップ308に進む。ステップ308において制御部1202は、ECCエラーが判定された有効クラスタ（つまりECC訂正不能な有効クラスタ）を含むページ（論理ページ）について、ICP訂正機構1201bによるICP訂正を行わせる。40

#### 【0061】

本実施形態では、論理ブロック内の論理ページ毎に、対応するページのICP訂正を可能するために、16チャネルのうちの1チャネルを、ICP訂正のための誤り訂正データの格納に割り当てている。この誤り訂正データの格納に割り当てられるチャネルは、論理ページ毎に変更されるものとするが、特定のチャネルであっても構わない。ICP訂正のための誤り訂正データは、他の15チャネルに格納される対応する論理ページのデータに基づいて生成される、例えばパリティデータ（チャネル間パリティデータ）である。ICP訂正機構1201bは、このパリティデータを用いて、ECC訂正不能な有効クラス50

タを含む論理ページ j ( j = q r ) のエラー箇所を修復するための ICP 訂正を行う。つまり ICP 訂正機構 1201b は、パリティデータと、他の 15 チャンネルのうち ECC 訂正不能な有効クラスタを持つチャンネル（第 1 のチャンネル）を除くチャンネル群（第 2 のチャンネル群）に対応する論理ページ j のデータとに基づいて、ICP 訂正を行う。

#### 【0062】

制御部 1202 は、ICP 訂正機構 1201b による ICP 訂正の結果に基づき、論理ページ j の ICP 訂正に成功したかを判定する（ステップ 309）。もし、論理ページ j の ICP 訂正に失敗したならば、つまり ICP 訂正不能であったなら（ステップ 309 の N o）、制御部 1202 は、リード対象論理ブロックの論理ブロック ID を、コンパクション処理の対象となる論理ブロックとしてコンパクション部 1210 に登録する（ステップ 310）。このステップ 310において、制御部 1202 は、リフレッシュフラグを OFF 状態から ON 状態に切り替える。10

#### 【0063】

次に制御部 1202 は、自己診断処理の要求元（ここではホスト）に ICP 訂正不能クラスタを通知して、1 論理ブロックのための自己診断処理を終了する。この場合、コンパクション部 1210 は、ステップ 310 で登録された論理ブロック ID によって示される論理ブロックのデータを別ブロックに移動するためのコンパクション処理を行う。

#### 【0064】

一方、レスポンス解析部 1209 による解析結果に 1 つのエラーレスpons も含まれていない場合、つまり ECC エラー数 N1 がゼロの場合（ステップ 305 の N o）、自己診断処理はステップ 401 に進む。また、有効クラスタの ECC エラー数 N2 がゼロの場合にも（ステップ 307 の N o）、自己診断処理はステップ 401 に進む。20

#### 【0065】

ステップ 401において、コマンド進捲判定部 1205 は、レスポンス解析部 1209 によって解析されたコマンドレスポンス中にページレスポンスが含まれている（存在する）かを判定する。つまりコマンド進捲判定部 1205 は、解析されたコマンドレスポンス中にページレスポンスによって返されたコマンド（以下、ページコマンドと称する）が含まれているかを判定する。

#### 【0066】

ここで、チャンネル 14, 15 では、ホストから要求されたアクセス処理が優先して行われたために、時刻 t1 でチャンネル 0, 1, ..., 14, 15 に同時に投入されたリードコマンド C0000, C1000, ..., CE000, CF000 のうちのリードコマンド CE000, CF000 が、時刻 t2 の後も未実行であったものとする。また、ホストから要求されたチャンネル 14, 15 を介してのアクセス処理でエラーが発生したために、ページレスポンスが返却されたものとする。この返却されたページレスポンスには、リードコマンド CE000, CE001, CE002, CF000, CF001, CF002 がページコマンドとして含まれている（ステップ 401 の Yes）。

#### 【0067】

この場合、リードコマンド CE000, CE001, CE002 が投入されたチャンネル 14 に対応するコマンド進捲管理部 1204 の CH 進捲管理部 1204-14、及びリードコマンド CF000, CF001, CF002 が投入されたチャンネル 15 に対応するコマンド進捲管理部 1204 の CH 進捲管理部 1204-15 は、それぞれ自身が保持するチャンネル 14, 15 のコマンド進捲情報を次のように更新する。即ち CH 進捲管理部 1204-14, 1204-15 は、チャンネル 14, 15 のチャンネルのコマンド進捲情報（ページ番号、プレーン - クラスタ番号）を、最も古い位置が示されるように更新する（ステップ 402）。チャンネル 14, 15 に対応する最も古い位置は、最も古いページコマンド（未実行のリードコマンド）CE000, CF000 に対応する位置（ページ 0、プレーン 0、クラスタ 0）である。この場合、チャンネル 14, 15 のコマンド進捲情報は、いずれも「000」に更新される。40

#### 【0068】

10

30

40

50

またステップ402において、コマンド進捲管理部1204内のCH進捲管理部1204-14, 1204-15以外のCH進捲管理部（他のCH進捲管理部）は、自身が保持するコマンド進捲情報を、次の位置が示されるように更新する。ここでは、上記他のCH進捲管理部は、コマンド進捲情報を、図6から明らかのように、（ページ0、プレーン1、クラスタ1）が示されるように「003」に更新する。またステップ402において、コマンド進捲管理部1204は、上記ステップ303と同様にして、ステップ302で取得した物理ブロックIDと現在のチャネル別のコマンド進捲情報とに基づいて、チャネル別に物理NANDクラスタアドレスを取得する。

#### 【0069】

ステップ402においてコマンド生成部1206は、上記ステップ303と同様にして、コマンド進捲管理部1204によってチャネル別に取得された物理NANDクラスタアドレスの示す位置（ページ、プレーン、クラスタ）へのリードアクセスを指定した最大16個のリードコマンドを生成する。ステップ402においてコマンド生成部1206は、生成された最大16個のリードコマンドをNANDインターフェース1201に対して同時に発行する。図6の例では、16のリードコマンドC0003, C1003, …, CE00, CF000が時刻t4に発行されたことが示されている。ステップ402が終了すると、自己診断処理は上記ステップ304に戻る。

#### 【0070】

次に、解析されたコマンドレスポンス中にページコマンドが含まれていないものとする（ステップ401のNo）。この場合、コマンド進捲管理部1204は、自身が保持するチャネル0～15のコマンド進捲情報のプレーン・クラスタ番号sをインクリメントする（ステップ403）。つまりコマンド進捲管理部1204は、コマンド進捲を次の位置に進める。ステップS403において、更新前のプレーン・クラスタ番号sが3の場合、プレーン・クラスタ番号sは0に設定される。プレーン・クラスタ番号sは、0 1 2 3 0のように更新される。

#### 【0071】

次にコマンド進捲管理部1204は、更新されたチャネル0～15のコマンド進捲情報に基づいて、チャネル別に、1論理ページが完了したかを判定する（ステップ404）。ここでは、例えばチャネルiのコマンド進捲情報のプレーン・クラスタ番号sが0の場合、チャネルiについて1論理ページ（より詳細には、1論理ページ内のチャネルiに対応する全クラスタ）が完了したと判定される。

#### 【0072】

もし、いずれのチャネルにおいても、1論理ページが完了していないならば（ステップ404のNo）、自己診断処理はステップ303に戻る。このステップ303では、ステップ403の実行の結果、チャネル別のコマンド進捲情報の示す位置が、最終ページの最終クラスタを示しているかが進捲統括管理部1203によって判定される。進捲統括管理部1203は、チャネル別の判定結果を保持する。

#### 【0073】

これに対し、いずれかのチャネル、例えばチャネルiにおいて1論理ページが完了したならば（ステップ404のYes）、自己診断処理はステップ405に進む。ステップ405においてコマンド進捲管理部1204は、1論理ページが完了したチャネルiのコマンド進捲情報のページ番号をインクリメントする。つまりコマンド進捲管理部1204は、チャネルiのコマンド進捲を次の論理ページに進める。ここでは、直近のステップ403でプレーン・クラスタ番号sが0に設定されていることから、ステップ405で更新されたチャネルiのコマンド進捲は、次の論理ページの先頭クラスタを示す。ステップ405が終了すると、自己診断処理はステップ408に進む。

#### 【0074】

次に、論理ページjのICP訂正に成功した場合（ステップ309のYes）について説明する。このICP訂正が、チャネルiに投入されたリードコマンドに従うアクセスでECCエラーが発生したために行われたものとする。この場合、ICPCS管理部121

10

20

30

40

50

1は、ICP完了ページビットマップを、論理ページjのICP訂正の完了が示されるように更新する(ステップ406)。ここでは、64ビット長のICP完了ページビットマップの論理ページjに対応するビットjが、“1”(ON状態)に設定される。論理ページjのICP訂正に成功したことは、論理ページjの自己診断処理が全てのチャネル0～15について正常に終了したことと等価である。

#### 【0075】

そこで、コマンド進捲管理部1204は、ICP完了ページビットマップが更新された場合(ステップ406)、少なくともチャネルiのコマンド進捲を、ICP訂正に成功した論理ページjの次の論理ページj+1の先頭クラスタに進める(ステップ407)。つまりコマンド進捲管理部1204は、少なくともチャネルiのコマンド進捲に関し、論理ページjをスキップする。ステップ407においてコマンド進捲管理部1204は、残りのチャネルのコマンド進捲のうち、論理ページjの処理中を示すコマンド進捲についても、論理ページj+1の先頭クラスタに進める。ステップ407が終了すると、ステップS405が終了した場合と同様に、自己診断処理はステップ408に進む。

10

#### 【0076】

ステップ408において進捲統括管理部1203は、自身がチャネル別に保持している情報に基づき、全てのチャネル0～15でコマンド進捲がリード対象論理ブロック内の最終クラスタまで進んでいるかを判定する。つまり進捲統括管理部1203は、全てのチャネル0～15でリード対象論理ブロック内の対応する最終クラスタがリード対象となっているかを判定する。もし、最終クラスタがリード対象となっていないチャネルがあるならば(ステップ408のNo)、自己診断処理はステップ303に戻る。

20

#### 【0077】

これに対し、全てのチャネル0～15でリード対象論理ブロック内の対応する最終クラスタがリード対象となっているならば(ステップ408のYes)、自己診断処理はステップ409に進む。ステップ409において進捲統括管理部1203は、リード対象論理ブロックの処理が完了したかを判定する(ステップ409)。この判定のために進捲統括管理部1203は、全てのチャネル0～15から、リード対象論理ブロック内の対応する最終クラスタへのアクセスに応じてコマンドレスポンス(以下、最終コマンドレスポンスと称する)が返却されているかをレスポンス解析部1209に問い合わせる。

#### 【0078】

30

もし、少なくとも1つのチャネルから最終コマンドレスポンス(成功レスポンスまたはエラーレスpons)が返却されていないならば、進捲統括管理部1203はリード対象論理ブロックの処理の未完了を判定する(ステップ409のNo)。この場合、進捲統括管理部1203は、例えば所定時間後に再びステップ409を実行する。

#### 【0079】

一方、全てのチャネル0～15から最終コマンドレスポンスが返却されているならば、進捲統括管理部1203はリード対象論理ブロックの処理の完了を判定する(ステップ409のYes)。この場合、制御部1202は、リフレッシュフラグがON状態にあるかを判定する(ステップ410)。もし、リフレッシュフラグがON状態にあるならば(ステップ410のYes)、制御部1202は、リード対象論理ブロックの論理ブロックIDを、コンパクション処理の対象となる論理ブロックとしてコンパクション部1210に登録する(ステップ411)。このステップ411において、制御部1202は、リフレッシュフラグをON状態からOFF状態に切り替える。これにより制御部1202は、1論理ブロックのための自己診断処理を終了する。これに対し、リフレッシュフラグがOFF状態にあるならば(ステップ410のNo)、制御部1202はステップ411をスキップして、1論理ブロックのための自己診断処理を終了する。

40

#### 【0080】

以上、本実施形態で適用される自己診断処理の手順の詳細について説明した。なお、図1に示すメモリ装置10のNANDコントローラ2によって自律的に行われる、パトロール処理、或いはリフレッシュ処理も自己診断処理と同様に実施することが可能である。

50

**【 0 0 8 1 】**

上述したように、図1に示すメモリ装置10のNANDコントローラ2では、コマンド進捲管理部1204によってチャネル別のコマンド進捲状態が管理される。また、ICPCS管理部1211によって、論理ブロックの論理ページ毎にICP訂正完了状態が管理される。このようなコマンド進捲管理部1204及びICPCS管理部1211を備えた、本実施形態のメモリ装置10によれば、従来よりも、論理ブロック単位の大容量リード処理を無駄なく、高速に実行することが可能となる。

**【 0 0 8 2 】**

また本実施形態によれば、NANDフラッシュメモリ11を備えたメモリ装置10の信頼性確保に必要不可欠な、自己診断処理、パトロール処理、或いはリフレッシュ処理の性能向上を実現できる。また本実施形態によれば、チャネル毎の利用負荷にばらつきが生じている場合でも、ページ発生時、或いはICP訂正発生時において再投入されるコマンドの冗長度を削減することができる。10

**【 0 0 8 3 】**

以上説明した少なくとも1つの実施形態によれば、ブロック単位のメモリアクセス処理を、小容量のメモリ領域を用いた管理で高速に実行できる、マルチチャネルを有するメモリ装置及び同装置におけるメモリアクセス方法を提供することができる。

**【 0 0 8 4 】**

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。20

**【 符号の説明 】****【 0 0 8 5 】**

10...メモリ装置、11...NANDフラッシュメモリ(メモリ)、12...NANDコントローラ、1201...NANDインターフェース(メモリインターフェース)、1201a...ページ機構、1201b...チャネル間誤り訂正機構(ICP訂正機構)、1202...制御部、1203...進捲統括管理部、1204...コマンド進捲管理部、1204-0~1204-15...チャネル別コマンド進捲管理部(CH進捲管理部)、1205...コマンド進捲判定部、1206...コマンド生成部、1207...テーブル管理部、1207a...論物変換テーブル、1208...レスポンス蓄積部、1209...レスポンス解析部、1210...コンパクション部、1211...チャネル間誤り訂正状態管理部(ICPCS管理部)。30

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

【図6】

---

フロントページの続き

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(72)発明者 増尾 容子

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 山中 太市郎

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 宮本 博暢

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 渡部 博樹

(56)参考文献 特開2011-013835(JP,A)

特開平2-186464(JP,A)

国際公開第2010/122607(WO,A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 00 - G 06 F 12 / 06

G 06 F 12 / 16

G 06 F 13 / 16 - G 06 F 13 / 18