(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第3935943号

(P3935943)

(45) 発行日 平成19年6月27日(2007.6.27)

(24) 登録日 平成19年3月30日(2007.3.30)

(51) Int.C1.

F 1

A 6 1 B 5/06 (2006.01)

A 6 1 M 25/00 (2006.01)A 6 1 B 5/06

A 6 1 M 25/00 312

請求項の数 12 (全 20 頁)

|               |                              |           |                                                                            |

|---------------|------------------------------|-----------|----------------------------------------------------------------------------|

| (21) 出願番号     | 特願平9-529164                  | (73) 特許権者 | バイオセンス・インコーポレイテッド<br>アメリカ合衆国、33173 フロリダ州<br>、マイアミ、スイート 283、サンセント・ドライブ 9360 |

| (86) (22) 出願日 | 平成9年2月14日(1997.2.14)         | (74) 代理人  | 弁理士 田澤 博昭                                                                  |

| (65) 公表番号     | 特表2000-506027(P2000-506027A) | (74) 代理人  | 弁理士 加藤 公延                                                                  |

| (43) 公表日      | 平成12年5月23日(2000.5.23)        | (72) 発明者  | オサドチャイ, ダニエル<br>イスラエル国、34731 ハイファ、オレン・ストリート 18                             |

| (86) 國際出願番号   | PCT/IL1997/000060            | (72) 発明者  | フライド, シュロモ<br>イスラエル国、30900 ジクロン・ヤコフ、タシヤック・ストリート 10                         |

| (87) 國際公開番号   | W01997/029678                |           | 最終頁に続く                                                                     |

| (87) 國際公開日    | 平成9年8月21日(1997.8.21)         |           |                                                                            |

| 審査請求日         | 平成16年2月12日(2004.2.12)        |           |                                                                            |

| (31) 優先権主張番号  | 60/011,723                   |           |                                                                            |

| (32) 優先日      | 平成8年2月15日(1996.2.15)         |           |                                                                            |

| (33) 優先権主張国   | 米国(US)                       |           |                                                                            |

| (31) 優先権主張番号  | 60/017,635                   |           |                                                                            |

| (32) 優先日      | 平成8年5月17日(1996.5.17)         |           |                                                                            |

| (33) 優先権主張国   | 米国(US)                       |           |                                                                            |

(54) 【発明の名称】カテーテル較正システム及び使用状況モニタリングシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

被験者の体内挿入用プローブを較正する方法であって、書き込み可能なマイクロ回路と遠位端とを有するプローブであって、前記遠位端が、前記遠位端の遠位側先端に隣接する、診断及び/又は治療の役割を果たす機能部と、前記被験者の体内における前記プローブの位置を決めるために使用される信号を発生させる位置信号発生素子とを含むプローブを用意する工程と、前記プローブの前記遠位先端を基準とした前記位置信号発生素子の角方位及び位置変位の少なくとも一つに関するデータを含んだ、前記プローブの前記遠位先端に関する前記位置信号発生素子の較正データを決定する工程と、

前記マイクロ回路に前記較正データを記録するように前記マイクロ回路に書き込む工程とを備えた方法。

## 【請求項 2】

較正コードを暗号化する工程と、それを前記マイクロ回路に書き込む工程とを備えた請求項1に記載の方法。

## 【請求項 3】

前記暗号化されたコードを読み取る工程と、前記暗号化されたコードが予め決められたコードと一致していないとき、前記プローブの使用者に知らせる工程とを備えた請求項2に記載の方法。

## 【請求項 4】

前記暗号化されたコードを読み取る工程と、前記暗号化されたコードが予め決められたコードと一致していないとき、前記プローブの動作を止める工程とを備えた請求項3に記載の方法。

**【請求項5】**

前記マイクロ回路に書き込む工程が使用状況記録を設定する工程を含む請求項1に記載の方法。

**【請求項6】**

前記使用状況記録が前記プローブの許容使用期日を示す請求項5に記載の方法。

**【請求項7】**

前記使用状況記録が前記プローブの再使用可能回数を示す請求項5に記載の方法。

10

**【請求項8】**

前記使用状況記録が前記プローブの使用可能継続時間を示す請求項5に記載の方法。

**【請求項9】**

前記マイクロ回路に書き込む工程が前記使用状況記録へのアクセスを制限する工程を含む請求項5に記載の方法。

**【請求項10】**

前記使用状況記録へのアクセスを制限する工程が前記使用状況記録の1個以上のビットを第1の値から第2の値に変更することができるが前記第2の値から前記第1の値に変更することができない工程を備えた請求項9に記載の方法。

**【請求項11】**

前記使用状況記録へのアクセスを制限する工程がパスワードを設定する工程を含む請求項9に記載の方法。

20

**【請求項12】**

前記位置信号発生素子がゲインを有し、前記較正データが前記位置信号発生素子の前記ゲインに関するデータを含む請求項1に記載の方法。

**【発明の詳細な説明】**

**関連出願**

この出願は1996年2月15日に「カテーテル較正システム」という名称で出願された米国暫定特許出願第60/011,723号及び1996年5月17日に「カテーテル較正システム」という名称で出願された米国暫定特許出願第60/017,635号の特典を主張している。両出願の開示内容がこの明細書中に組み入れられている。この出願は、また、Biosense Inc.により、公正な日に、「体内プローブを使う医療処置及び医療装置」という名称で、米国受理官庁に特に米国を指定して出願されたPCT出願に関連している。

30

**発明の分野**

この発明は概して医療診断及び医療処置のためのシステムに関し、特にその配置が検出される医療カテーテルに関する。

**発明の背景**

さまざまな方法や素子が、電磁場を使って体内に位置するプローブやカテーテルの先端(Tip)の位置を決定するために説明されている。例えば、米国特許第5,042,486号及び国際特許出願第WO94/0938号などに説明され、それらの開示内容がこの明細書中に組み入れられている。必ずしも医療用ではないが、他の電磁場追跡システムが、米国特許第3,644,825号、第3,868,565号、第4,017,858号、第4,054,881号及び第4,849,692号に説明され、同様に、それらの開示内容がこの明細書中に組み入れられている。

40

1993年7月20日に出願された米国特許第5,391,199号は、カテーテルの位置を3次元で決定することができるがその方位を決定することができないカテーテルを組み入れているシステムを開示している。米国特許第5,391,199号はこの特許出願の譲受人に譲渡され、その開示内容がこの明細書中に組み入れられている。

国際特許出願第PCT/US95/01103号は、カテーテルの遠位側先端(distal tip)に

50

tip) の位置及び方位を 6 次元で決定するための手段を含むカテーテルシステムを開示している。国際特許出願第 P C T / U S 9 5 / 0 1 1 0 3 号は、同様に、この特許出願の譲受人に譲渡され、その開示内容がこの明細書中に組み入れられている。このシステムは、カテーテル内の位置決め可能箇所に隣接する、例えば遠位側先端の近くの、位置にある複数の非同心形コイルを使う。3つの直交コイルを使うのが好ましい。これらのコイルは、位置座標及び方位座標からなる 6 個の座標を計算することを考慮して外部に加えられた磁場に応答して信号を発生させる。その結果、カテーテルの位置及び方位がカテーテルを映像化する必要なく明らかにされる。

米国特許出願第 5 , 3 8 3 , 8 7 4 号 ( Jackson 外 ) は、カテーテルを識別しモニタリングするシステムを説明している。このシステムは、カテーテル本体のハンドル内に保持されている識別手段を含んでいる。この特許の 1 つの実施例では、ハンドルは、カテーテルの識別コード並びにカテーテルの作動及び機能特性を表すデジタル値が予め書き込まれた半導体マイクロチップを含んでいる。ハンドルは、ケーブルによりコントロールコンソールに接続されている。コントロールコンソールは、マイクロチップからデータを読み取る。1 つの開示された実施例では、マイクロチップは、カテーテルが使われた回数を記録することができる。カテーテルのハンドルにあるデジタルデータ記憶装置が、多種多様なデジタル信号線をカテーテルに付け加えている。10

#### 発明の要約

国際特許出願第 P C T / U S 9 5 / 0 1 1 0 3 号のコイルやカテーテルの位置及び方位を電磁検出するための他のシステムは、概して、カテーテル内におけるカテーテルの遠位側先端からわずかに離れた所に位置づけられている。これは、遠位側先端が一般的に電極及び他の機能部品により占められているためである。従って、位置及び方位検出システムを、コイルの配置を基準とした、カテーテル、の遠位側先端の変位を考慮して較正しなければならない。製造のばらつきにより、この変位は一般にカテーテルにより変る。20

さらに、位置信号を発生させるために使うコイルは、正確に直交していないかもしれない。カテーテルの位置及び方位を計算するために、コイルの軸が、カテーテル先端に固定される座標系のそれぞれの軸を規定する。これらの軸の方向は、カテーテルの方向を基準として明らかにされなければならない。これらの軸が直交性から外れるならば、それぞれのずれの程度を明らかにし、位置及び方位を計算するに当たって較正しなければならない。加えて、コイルの相対的なゲインが、コイルが外部に加えられた場に応答して発生させるそれぞれの位置信号の強度を決定する。これらの信号の強度は、カテーテルの位置及び方位を計算する際に使われる所以、それらの期待値からのゲインのずれにより、計算して得られる位置及び方位が不正確となる。従って、それぞれのコイルのゲインを明らかにし、位置及び方位を計算するに当たって較正しなければならない。30

従って、位置信号を発生させるために使うコイルの位置、方位及びゲインのばらつきを調整し補償するように、カテーテルを予め、好ましくは製造時に、較正することが望ましい。

好ましくは、各使用前に再較正したり、較正データを手入力したりする必要を軽減するような方法により、較正データは記録されるべきである。

従って、この発明は、較正情報が内部に保持されているカテーテルの位置及び方位を決定するために使う素子の較正方法を提供することを目的とする。40

さらにこの発明は、カテーテルに関する較正情報を簡便に電子的に格納したり呼び戻したりする手段を提供することを目的とする。

この発明の 1 つの態様では、この較正情報を、信号処理回路や計算装置に容易にアクセス可能な位置に位置づけられているマイクロ回路にデジタル形式で格納している。その結果、カテーテルはデジタル信号線を含む必要がなく、マイクロ回路から信号処理回路及び計算装置に送信されるデジタル電子信号が、電線によりカテーテルの遠位端 ( distal tip ) から信号処理回路に伝達される低レベルアナログ信号と干渉しない。

この発明の好適実施例では、体内に位置するカテーテルの位置及び方位を決定するために使う素子が、カテーテルの遠位端に隣接する位置にある複数のコイルを有している。カテーテル

1020304050

ーテルは、さらに、カテーテルの遠位端に隣接する位置にある電子マイクロ回路を有している。マイクロ回路は、素子の較正に関する情報を格納している。

マイクロ回路は、例えば、EEPROM, EPROM, PROM, フラッシュROMあるいは不揮発性RAMなどの読み取り書き込みメモリ部品を有しており、情報をデジタル形式で格納しているのが好ましい。

この発明の好適実施例では、この較正情報が、カテーテルの遠位端のコイルからの相対的な変位に関するデータを含んでいる。この発明のいくつかの他の好適実施例では、また、較正情報は、直交性からのコイルのずれに関する情報、あるいはコイルのそれぞれのゲインに関する情報、あるいはこれらの情報の組み合わせを含んでいる。

カテーテルを信号処理装置及び計算装置から電気的に絶縁する、この発明のいくつかの好適実施例では、較正情報はカテーテルにある絶縁回路に関するデータを含んでいる。カテーテルは、カテーテルの遠位端に隣接する位置あるいはカテーテルに付いているハンドル内にある少なくとも1個の誘電部品、例えば絶縁形トランスなどによって絶縁するのが好ましい。このような誘電部品に代えて、カテーテルを1個以上の光アイソレータあるいは従来から知られている他のタイプの絶縁回路により絶縁しても良い。そのような誘電部品及び他の絶縁回路により、一般的にそれらにより伝達される信号に非線形性が生じる。そのような非線形性により、電線によりカテーテルの遠位端から信号処理回路に伝達されるアナログ信号に特にかなりのひずみが生じる。従って、較正情報は誘電部品及び/又は他の絶縁回路により生じる、信号の非線形性に関するデータを含んでいるのが好ましい。

この発明の好適実施例では、カテーテルは信号処理装置及び/又は計算装置に物理的に接続されていないワイヤレスカテーテルである。正しくは、送受信機をカテーテルの近位端(proximal end)に取り付けている。送受信機は、例えば、IR(赤外線)送信、RF送信あるいは音響送信などの無線通信方法を使って、信号処理装置及び/又は計算装置と通信する。このように構成する1つの利点は、(電気に敏感な)心臓に挿入されるカテーテルを、容易に電気的にフローティングな状態にすることができるということである。別の利点は、多くのオペレータのうちの1人が巻き込まれたり及び/又は間違って身体から引き出すかもしれないケーブル及び電線の引き回し量が減少するということである。また、別の利点はカテーテル全体を1個のユニットとして殺菌することができるので、殺菌及びそのようなカテーテルを無菌状態に維持することが容易であるということである。この発明の好適実施例では、送受信機を収容するカテーテルの遠位端を、オペレータのベルトに取り付けている。カテーテルを制御するためのハンドルを、カテーテルの遠位端から数フィート離れたカテーテル上に配置するのが好ましい。理解できるように、そのようなカテーテルを体内への物質の注入及び切除に使うとき、少しの間、RF発生機のような外部の装置に接続するのが好ましい。

この発明の好適実施例では、マイクロ回路を、カテーテルの近位端に位置するコネクターに収容している。このコネクターは、カテーテルから信号処理回路及び計算装置への電子信号を連結するのが好ましい。

この発明の他の好適実施例では、コネクターに連結される電子信号は、アナログ信号及びデジタル信号の両方を含んでいる。さらに、この発明のいくつかの好適実施例では、アナログ信号は、カテーテル内にある電極が受信する電気生理学的な信号及びコイルが発生させる位置及び方位信号の両方を含んでいる。位置及び方位信号をより合わせ電線対あるいはシールドされた電線により伝達し、またコネクターがノイズやこれらの信号の干渉を減らすためにシールドしてあるのが好ましい。

この発明の他の好適実施例では、カテーテルは1個以上のアナログ-デジタル(A/D)変換器を含んでいる。アナログ-デジタル(A/D)変換器は電気生理学的な信号並びに位置及び方位信号をアナログ形式からデジタル形式に変換する。これらの実施例では、コネクターは、カテーテルから信号処理回路及び計算装置へのデジタル信号のみを連結する。そのような1つの好適実施例では、A/D変換器は、カテーテルの遠位側先端に隣接している。そのような他の好適実施例では、A/D変換器は、カテーテルの近位端に隣接し、例えばカテーテルに取り付けられているハンドル、あるいはコネクターにある。

10

20

30

40

50

この発明の好適実施例は、さらに、較正情報が内部に格納されているカテーテルの遠位側先端の位置及び方位を検出するために使う素子を較正する方法を提供する。素子の動作前に、コンピュータは格納されている較正情報を読み取り、この情報を使って、体内に位置するカテーテルの位置及び方位を決定する。

位置及び方位を決定するために使う素子が、カテーテルの遠位端に隣接する位置にあるコイルを有している、この発明の好適実施例では、コイルのゲイン及び方位それぞれに関する較正情報を、カテーテルの遠位端を既知の予め決められた位置及び方位に置き、それを既知の磁場にかけることにより発生させる。コイルは磁場に応答して信号を発生させる。この信号を検出し較正データを計算するために正常な信号値と比較する。そのとき、正常値からのコイルのゲイン及び方位のずれを考慮して、これらの較正データを、次に行われる正しい位置及び方位を決定するために使う。

さらに、この発明の好適実施例では、コイルを基準としたカテーテルの遠位側先端の変位に関する較正情報を、カテーテルの遠位側先端を1以上の予め決められた位置及び方位に置き、カテーテルに既知の磁場を加えることにより発生させる。磁場に応答してコイルが発生させる信号を検出し、その信号を使って補正関数を計算する。補正関数は、次に、カテーテルの遠位側先端の位置及び方位を決定するに当たって使うことができる。

この発明の好適実施例では、機械治具により、較正中、カテーテルを複数の予め決められた位置及び方位に保持する。ラジエータは既知の実質的に均一の磁場をこの治具の周辺に発生させる。コイルが発生させる信号を解析し、その信号を使ってコイルのゲイン及び直交性からのコイルのずれに関する較正データを生成する。

この発明の他の好適実施例では、機械治具により、較正中、カテーテルを複数の予め決められた位置及び方位に保持する。ラジエータは予め決められた不均一の磁場をこの治具の周辺に発生させる。磁場の強度及び方向は、治具内での位置の関数として明らかにされている。コイルが発生させる信号を解析し、その信号を使ってカテーテルの先端を基準としたそれぞれのコイルの変位に関する較正データを生成する。

この発明のいくつかの好適実施例では、カテーテルの位置及び方位を検出するための素子を較正する際に使用する装置が、ヒータ及び温度センサを含んでいる。これらは、較正中、カテーテルの遠位側先端を予め決められた既知の温度に維持する。先端は、カテーテルが挿入される身体の温度、例えば37に維持するのが好ましい。このようにして、較正における温度に関連した誤差、例えばカテーテル内にあるコイルのインダクタンスの温度に関連した変化を避けることができる。

上述した好適実施例のいずれかにより生成される較正データは、参照用テーブル、多項係数あるいは従来から知られている他の形式で記録できる。そのときカテーテルにあるマイクロ回路に格納する。

この発明の好適実施例では、較正データを製造時に生成し記録し、マイクロ回路を、使用者によるその後の較正データの記録を防ぐように構成している。そのようなこの発明のいくつかの好適実施例では、マイクロ回路はE PROM素子あるいはPROM素子を有しており、これらの素子をカテーテルの近位端でコネクターに収容し、EPROMあるいはPROMの入出力接続をコネクターのピンに連結している。較正データは、製造時に適当な書き込み素子を使ってEPROMあるいはPROMに記録される。書き込み素子は較正に使うコンピュータからデータを受信する。EPROM書き込み素子あるいはPROM書き込み素子はカテーテルのコネクターに接続され、コネクターを通してEPROMあるいはPROMにデジタル信号を入力することによりEPROMあるいはPROMに書き込む。その後、再びEPROMあるいはPROMに書き込みができない。

超小型電子回路がEEPROM素子あるいは不揮発性RAM素子を有している、そのようなこの発明の他の好適実施例では、EEPROM素子あるいは不揮発性RAM素子が従来から知られているタイプの書き込み許可入力を含んでおり、書き込み許可入力をカテーテルの近位端に位置するコネクターの書き込み許可ピンに接続している。較正時、書き込み許可入力を許可し、較正データをマイクロ回路に記録する。その後例えば、書き込み許可ピンを取り除くことにより、あるいはそれをアースに接続することにより、書き込み許可

10

20

30

40

50

入力を禁止する。その結果、さらに較正データをマイクロ回路に記録することができない。

一方、マイクロ回路がEEPROM素子を有している、この発明の好適実施例では、書き込み許可入力を、書き込み保護コマンドを素子に送ることによって禁止しても良い。このコマンドは、可逆的であっても不可逆的であっても良い。

また、この発明の他の好適実施例では、マイクロ回路は、例えばキシコール(Xicor)社製のX76F041パスワードアクセスセキュリティスパーバイザー(PASS(登録商標))シキュアーフラッシュROM素子などのアクセス制御回路を有している。マイクロ回路にパスワードを書き込んであるのが好ましく、その結果、製造時に較正データを生成し記録した後、さらに較正データをマイクロ回路に記録することができない。パスワードを知っている工場で許可された職員は、データを記録することができるという例外はある。10

この発明のいくつかの好適実施例では、マイクロ回路に記録されるデータは較正コードを含んでいる。較正コードは、較正データが変更されあるいは改悪されていないことを確定するように、従来から知られている方法により暗号化されている使用者がカテーテルをコンピュータを有している適當なコンソールに接続するとき、コンピュータは較正コードを読み取り、そのコードを予め書き込まれた値と比較する。コードが所望の予め書き込まれた値と一致していないならば、コンピュータは、カテーテルが適當に較正されていないかもしだれないということを示すメッセージを表示させる。コンピュータは、さらに、所望の予め書き込まれた値と一致するコードを持つカテーテルが接続されるまで、さらなる動作を防ぐことができる。20

較正コードを、不正な関係者による解読を防ぐ方法、例えばパブリックキーやプライベートキーを使うRSA暗号化方式や他の従来から知られている方法を使って暗号化するのが好ましい。RSA暗号化のような方法が使われるとき、品質が劣るかもしだれない不正な代用品を使用できないように、プライベートキーを正規のカテーテルの製造業者だけが知っている。

さらにこの発明の好適実施例では、マイクロ回路に記録されているデータは失効日時を含んでいる。失効日時の後カテーテルを使うことができない。使用者がカテーテルをコンピュータを有しているコンソールに接続するとき、コンピュータは失効日時を読み取り、それから失効日時を、例えばリアルタイムクロック回路が発生させる実際の日時と比較する。30。失効日時が過ぎているならば、コンピュータは、カテーテルをさらに使うことは不適當であることを示すメッセージを表示させる。コンピュータは、さらに、妥当な失効日時を持つカテーテルが接続されるまで、さらなる動作を防ぐことができる。

失効日時は、カテーテルが最初に使われるときに、カテーテルのマイクロ回路に書き込むことにより、コンピュータにより記録される。このようにして、カテーテルが、初めてコンソールに接続されるとき、コンピュータは、失効日時がまだマイクロ回路に記録されていないことを検出し、マイクロ回路に、実際の日時後の予め設定された期間である適當な失効日時を記録する。予め設定された期間は、カテーテルの予想される使用期間に基づいて、製造業者が決めのが好ましい。

マイクロ回路がアクセス制御回路を含んでいる好適実施例では、マイクロ回路が、その記憶域が“読み取りアクセス・書き込み専用”モードで動作可能なように書き込まれている。そのモードは、適當なパスワードを入力することによってのみ変えることができるが、概してシステムの使用者がそのパスワードを利用するることはできない。“読み取りアクセス・書き込み専用”モードでは、ビットを“1”から“0”に変えることにより、記憶域に格納されている数字を減らすことができるが、書き込まれたとおりのマイクロ回路では“0”を“1”に変えることができないので、増やすことはできない。製造時に、記憶域が最大値となるようにセットする、すなわちすべてのビットを“1”にセットするのが好ましい。それから、上述したように、最初に使うときに、コンピュータは、レジスタにある1個以上のビットを“1”から“0”に変えることにより、マイクロ回路に適當な失効日時を書き込む。その後、失効日時をより遅い日に変えることができない(正しいパスワード)4050

ードが最初に入力されないという条件において)。

以上の点に変えて、あるいは以上の点に加えて、上述したようなアクセス制御回路を有しているマイクロ回路を、使用者が改ざんしたり間違ったりしないような方法で、カテーテルが使われた回数及び／又はカテーテルの使用継続時間を突き止めるために使うことができる。カテーテルを使うことができる回数及び／又は時間の長さに対応する記録は、製造時に素子の記録域に格納され、マイクロ回路は、上述したように、記憶域が“読み取りアクセス・書き込み専用”モードで動作可能なように書き込まれているのが好ましい。カテーテルを使う各回及び／又は使用中の一定の時間間隔で、コンピュータは記録域の記録を読み取り、そこにある1個以上のビットを“1”から“0”に変えることによってそれを減らす。記録域に格納されている記録が0に達するとき、あるいは他の予め決められた最小値に達するとき、コンピュータは、コンピュータをさらに使うのに適当ではないということを示すメッセージを使用者に表示させ、好ましくは、適当なカテーテルが接続されるまで、さらなる動作を防ぐ。

10

従って、遠位端及び近位端を有し、電子マイクロ回路を含み、そのマイクロ回路はプローブの較正に関する情報を格納している被験者の体内挿入用プローブがこの発明の好適実施例により提供される。マイクロ回路は較正コードを格納し、較正コードは暗号化されているのが好ましい。

マイクロ回路は使用状況コードを格納し、使用状況コードによりプローブの使用者に対するプローブの有用性を規制し、プローブは、使用状況コードを、プローブの有用性が減少するように変えることができるが増加するように変えることができないアクセス制御回路を含んでいるのが好ましい。マイクロ回路は使用状況コードをその記憶域に格納し、記憶域は読み取りアクセス・書き込み専用モードで動作するようにアクセス回路により制御され、モードはアクセス制御回路にパスワードを入力することにより変わるのが好ましい。使用状況コードはデータ情報を含んでいるのが好ましい。プローブは、プローブの位置あるいは方位に応答する信号を発生させる素子を含み、プローブの較正に関する情報は信号発生素子の較正に関する情報を含んでいるのが好ましい。この素子はプローブの遠位端に隣接しているのが好ましい。

20

信号発生素子は1個以上のコイルを含み、較正に関する情報は1個以上のコイルのうちの少なくとも1個のコイルのゲインに関する情報を含んでいるのが好ましい。さらに、較正に関する情報は1個以上のコイルのうちの少なくとも1個のコイルの角方位に関する情報、及び、その他に、プローブの遠位端を基準とした信号発生素子の位置の変位に関する情報を含んでいるのが好ましい。

30

プローブが絶縁回路を含んでいる、この発明の好適実施例では、較正に関する情報は絶縁回路の非線形性に関する情報を含んでいるのが好ましい。マイクロ回路はプローブの近位端に隣接しているのが好ましい。さらに、プローブは、その近位端にコネクターを含み、マイクロ回路がコネクタに収容されているのが好ましい。

加えて、マイクロ回路は書き込み可能な記憶素子であり、記憶素子はEEPROM素子、不揮発性RAM素子、EPROM素子、フラッシュROM素子あるいはPROM素子を有しているのが好ましい。

さらに、上述したプローブと、コンピュータを含み、プローブからの位置あるいは方位応答信号及びプローブの較正に関する信号を受信し、それらをプローブの位置を決定するために使うコンソールとを含んでいる被験者の体内に位置するプローブの位置決定用装置が、この発明の好適実施例により提供される。

40

マイクロ回路はプローブの近位端に隣接しているのが好ましい。また、プローブはさらにその近位端にコネクターを含み、マイクロ回路はコネクターに収容され、コンソールはさらに接続端子を含み、接続端子はプローブのコネクターと連結できるように構成されているのが好ましい。

マイクロ回路は書き込み可能な記憶素子であり、プローブは書き込み可能なメモリ素子に書き込むことができるように構成されている1個以上の接続を含み、記憶素子はEEPROM素子、不揮発性RAM素子、EPROM素子、フラッシュROM素子あるいはPROM

50

M素子であるのが好ましい。加えて、接続端子は書き込み可能な記憶素子に書き込むための少なくとも1個の接続を無効にする手段を含んでいるのが好ましい。

コンピュータはさらに書き込み可能な記憶素子に書き込むことができるよう構成されているのが好ましい。記憶素子がEPROM素子あるいはPROM素子であるこの発明の好適実施例では、コンソロールはさらにEPROM書き込み装置あるいはPROM書き込み装置を含み、この装置はEPROM素子あるいはPROM素子に書き込むことができるよう構成されているのが好ましい。

さらに、プローブに関する較正データを決定する工程と、マイクロ回路にある較正データを記録するようにプローブにあるマイクロ回路を書き込む工程とを備えた被験者の体内挿入用プローブの較正方法がこの発明の好適実施例により提供される。

この方法はまた較正コードを暗号化する工程と、マイクロ回路に暗号化されたコードを書き込む工程とを含んでいるのが好ましい。この方法はさらに暗号化された較正コードを読み取る工程と、暗号化されたコードが予め決められたコードと一致しないときに、プローブの使用者に知らせるかあるいはプローブの動作を中止する工程とを含んでいるのが好ましい。

マイクロ回路に書き込む工程は使用状況記録を設定する工程を含み、使用状況記録はプローブの最初あるいは最後の使用日及び／又はプローブを再使用することができる回数及び／又はプローブを使うことができる時間の残存期間を示すのが好ましい。プローブを使うとき、使用状況コードを更新するのが好ましい。マイクロ回路に書き込む工程は好ましくはパスワードを設定することにより、使用状況フラグへのアクセスを制限する工程を含み、その結果、その後、使用状況記録を使用者に対するプローブの有用性が減少するが増加しないのが好ましい。較正データは信号発生装置に関し、信号発生装置はプローブの位置あるいは方位に応答する信号を発生させるのが好ましい。信号発生素子はゲインを有し、較正データは素子のゲインに関するデータを含んでいるのが好ましい。以上の点に代えて、あるいは以上の点に加えて、較正データはプローブを基準とした、信号発生素子の角方位に関するデータ及び位置あるいは方位応答信号を発生させる素子の位置変位に関するデータを含んでいるのが良い。

また、上述した好適実施例による、プローブに関する較正データを決定する工程及びプローブにあるマイクロ回路に書き込む工程と、体内に位置するプローブの位置あるいは方位を、位置あるいは方位応答信号及び較正データに基づいて計算する工程とを含むプローブの位置あるいは方位決定方法がこの発明の好適実施例により提供される。

また、暗号化されたコードを読み取る工程と、暗号化されたコードが予め決められたコードと一致していないとき、プローブの使用者に知らせる工程とを含む暗号化されたコードが内部に格納しているプローブの使用状況規制方法がこの発明の好適実施例により提供される。

さらに、暗号化されたコードを読み取る工程と、暗号化されたコードが予め決められたコードと一致していないとき、プローブの動作を止める工程とを含む暗号化されたコードを内部に格納しているプローブの使用状況規制方法がこの発明の好適実施例により提供される。以上の点に代えて、コードがある範囲の値と比較される。その方法は、プローブにある使用状況記録を更新する工程を含むのが好ましい。

また、位置決め可能部と信号発生素子とを有し、信号発生素子がプローブの位置あるいは方位に応答する信号を発生させるプローブを提供する工程と、信号発生素子と位置決め可能部とを1以上の予め決められた位置及び方位に固定して連結する工程と、信号発生素子の周辺で明らかにされており、信号発生素子に位置あるいは方位応答信号を発生させる、予め決められた磁場を加える工程と、信号発生素子が発生させる信号を受信する工程とを含む被験者の体内挿入用プローブの較正方法がこの発明の好適実施例により提供される。較正データの少なくともいくつかを、実質的に均一な磁場をプローブに加えることにより決定するのが好ましい。以上の点に代えて、あるいは以上の点に加えて、較正データの少なくともいくつかを、空間的に変化可能な磁場をプローブに加えることにより決定するのが好ましい。以上の点に代えて、あるいは以上の点に加えて、信号発生素子が発生させる

10

20

30

40

50

位置あるいは方位応答信号は、そこに加えられる磁場の方向成分に比例する大きさを有し、較正データは比例に関するデータを含んでいる。

以上の点に代えて、あるいは以上の点に加えて、較正データは、位置あるいは方位応答信号発生素子の角方位に関するデータを含んでいる。以上の点に加えて、あるいは以上の点に加えて、較正データは、プローブを基準とした位置あるいは方位応答信号発生素子の位置変位に関するデータを含んでいる。

この発明の好適実施例では、その方法は、プローブを加熱する工程、好ましくはほぼ37に加熱する工程を含むのが好ましい。

この発明の好適実施例では、較正データが、プローブに格納されている。

また、3つの実質的に直交する軸及び中心領域を規定し、中心領域において3つの軸の方向に沿って実質的に均一な磁場を発生するように構成された、複数のコイルと、中心領域にプローブの遠位端を固定する手段とを含む内部に位置感知素子を有するプローブの較正用装置がこの発明の好適実施例により提供される。コイルは、3個の直交する、互いに平行なコイルの対を含んでいるのが好ましい。以上の点に代えて、あるいは以上の点に加えて、装置は、プローブを、中心領域において固定した位置及び方位に保持するための鉗子を含んでいるのが好ましい。

さらに、プローブが挿入できるように構成され、それぞれがプローブの異なった予め決められた位置及び方位を規定する複数の端子を含んでいる治具と、異なった予め決められた位置及び方位に対して異った磁場を発生させる複数のコイルとを含む、内部に位置感知素子を有するプローブの較正用装置がこの発明の好適実施例により提供される。

この発明の好適実施例では、装置は、プローブを加熱するヒータを含んでいる。装置は、プローブの温度を検出する温度センサを含んでいるのが好ましい。

また、遠位端及び近位端を有する細長い柔軟な本体と、本体の遠位端に位置する信号発生部と、信号発生部が発生させる信号を外部の受信機に送信する送信機とを含むワイヤレスカテーテルがこの発明の好適実施例により提供される。送信機は外部の送信機からの送信を受信する受信機を含んでいるのが好ましい。上述した装置は、上述した方法によりプローブを較正することができるように較正されているのが好ましい。

この発明は、次の好適実施例についての詳細な説明を図面とともに検討することにより理解されよう。

#### 【図面の簡単な説明】

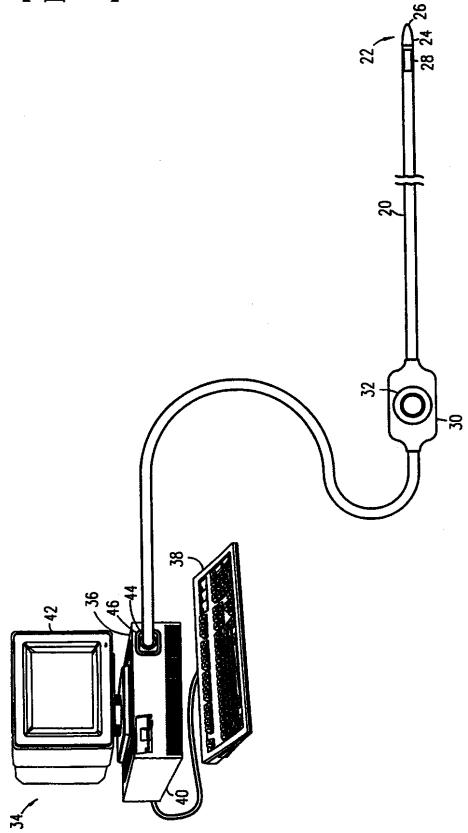

図1はこの発明の好適実施例によるカテーテルを含むシステムの斜視図である。

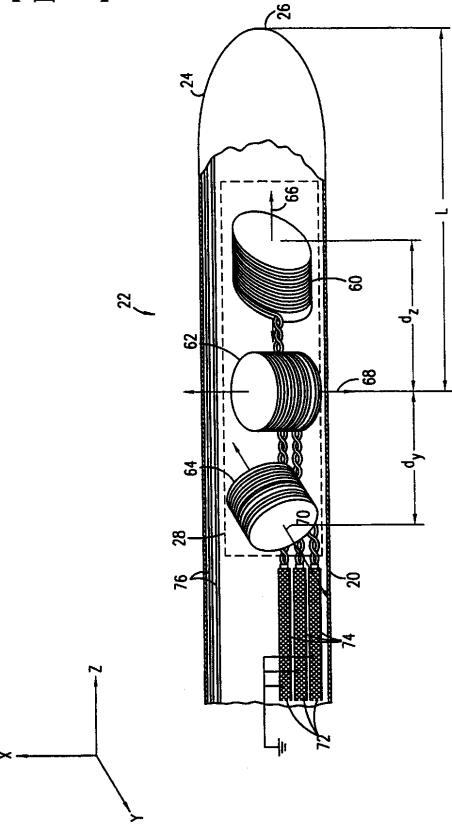

図2は図1に示すカテーテルの遠位端の詳細な断面図である。

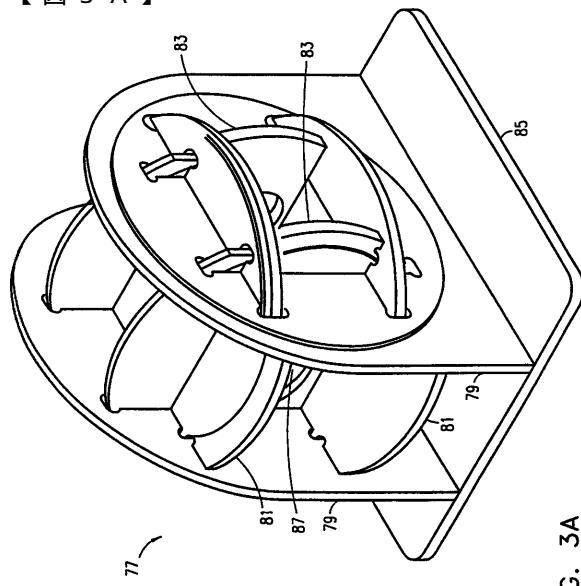

図3Aはこの発明の好適実施例によるカテーテルを較正する際に使用する治具の斜視図である。

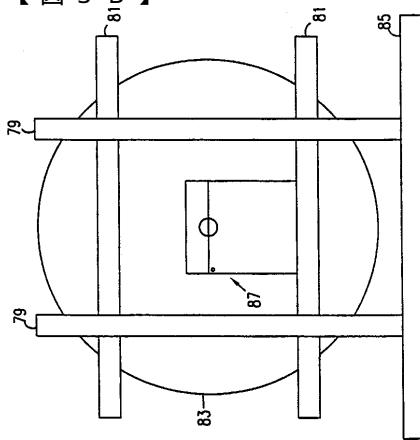

図3Bは図3Aに示す治具の略側面図である。

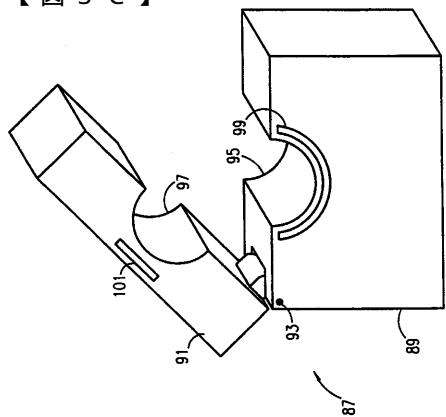

図3Cは図3Aに示す治具と一緒に使用するためのカテーテル鉗子の斜視図である。

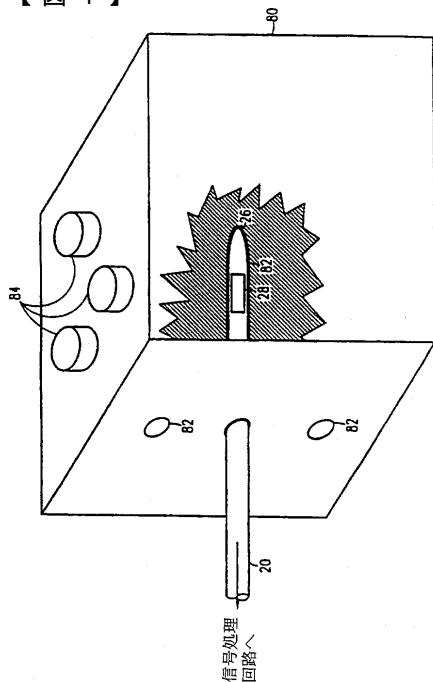

図4はこの発明の好適実施例によるカテーテル較正する際に使用する別の較正治具の部分切取断面図である。

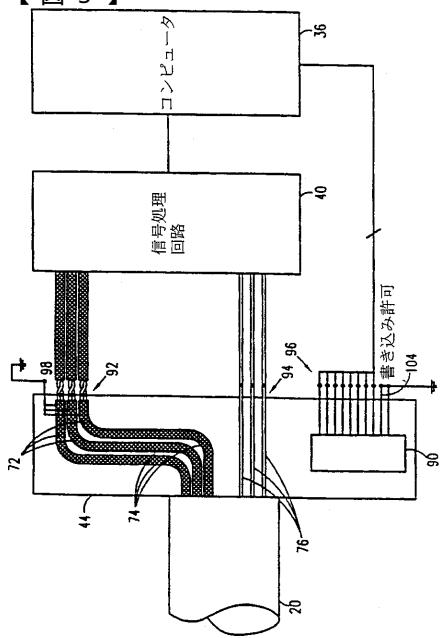

図5はこの発明の好適実施例によるカテーテルの近位端にあるコネクターの詳細な略図である。

#### 好適実施例の詳細な説明

図1はこの発明の好適実施例によるカテーテルシステムを示す図である。このシステムは、人体に挿入するための細長いプローブ、好ましくはカテーテル20を含んでいる。以下に示す好適実施例では、カテーテルに関して説明しているが、この発明はその他のプローブにも同様に適用できるということを理解されたい。

カテーテル20の遠位端22は、遠位側先端26に隣接する位置にある、診断及び/又は治療の役割を果たすための機能部24を含んでいる。機能部24は、例えば、電気生理学的な測定や心臓にある病変領域の電気外科的な切除を行うための電極(図示せず)を有していても良い。このような電極の代わりにあるいはこののような電極に加えて、機能部は、他種のセンサ、あるいは光又は超音波イメージング素子を有していても良い。

10

20

20

30

40

50

カテーテル 20 の遠位端 22 は、さらに体内に位置するカテーテルの位置及び方位を決定するために使う信号を発生させる素子 28 を含んでいる。素子 28 は、機能部 24 に隣接しているのが好ましい。素子 28 と機能部 24との間には、少なくとも較正処理中、固定した位置及び方位関係が存在するのが好ましい。

カテーテル 20 は、外科医がカテーテルを操作するためのハンドル 30 を含み、ハンドル 30 にあるコントローラ 32 により、外科医はカテーテルの遠位端を所望の方向、あるいは所望の位置及び / 又は方位に操縦できるのが好ましい。

図 1 に示されるシステムは、さらにコンソール 34 を有しており、このコンソール 34 により、使用者はカテーテル 20 の機能を観測したり規制したりできる。コンソール 34 は、コンピュータ 36、キーボード 38、一般的にコンピュータ内にある信号処理回路 40 及びディスプレイ 42 を含んでいるのが好ましい。信号処理回路 40 は、一般的に、カテーテル 20 からの信号を受信し、增幅し、ろ波し、デジタル化する。その信号には、位置信号発生素子 28 が発生させる信号が含まれる。カテーテルの位置及び方位を計算するために、コンピュータ 36 は、これらのデジタル化された信号を受信し使用する。

カテーテル 20 は、その近位端でコネクター 44 によりコンソール 34 にある接続端子 46 に連結される。カテーテル 20 は、さらに 1 個以上の絶縁形トランス（図示せず）を含むのが好ましい。絶縁形トランスは、カテーテルの遠位端をコンソール 34 から電気的に絶縁する。絶縁形トランスは、カテーテルのハンドル 30 内に収容されるのが好ましい。次に、この発明の好適実施例によるカテーテル 20 の遠位端の詳細図を示す図 2 を参照する。素子 28 は、3 個の非同心形コイル 60, 62 及び 64 を有している。これらの非同心形コイルは、例えば、第 WO 96/05768 号公報として発行されその開示内容がこの明細書中に組み入れられている国際特許出願第 PCT/US95/01103 号に説明されている。この素子により、位置情報及び方位情報からなる 6 次元の情報を連続的に発生することができる。コイル 60, 62 及び 64 には、それぞれ軸 66, 68 及び 70 がある。これらの軸は、図 2 に示されるように、直交デカルト軸 X, Y 及び Z をそれぞれ規定するのが好ましい。直交デカルト軸 X, Y 及び Z では、Z 軸がカテーテル 20 の長軸に平行であり X 軸及び Y 軸が Z 軸に垂直な面を規定する。各コイルには、互いの間に固定した位置及び方位関係がある。

この発明の好適実施例では、図 2 に示され上述された位置信号発生素子に関して説明しているが、この発明の発明思想が他の位置感知素子を含んだプローブに同様に適用できることを理解されたい。例えば、この発明の好適実施例では、位置信号を発生させるコイルを 1 個有していても良いし、2 個以上有していても良い。このコイルは同心形であっても良いし、非同心形であっても良い。この発明の他の好適実施例では、例えばホール効果素子などの他種の位置感知素子を有していても良い。

図 2 に示されるように、素子 28 は、カテーテル 20 内において、遠位側先端 26 から距離 L の位置に位置づけられている。この明細書では、L をコイル 62 の中心軸 68 から先端 26 に向かう Z 軸に沿った距離として、便宜上定義する。コイル 60 及び 74 のそれぞれの軸 66 及び 70 は、軸 68 からそれぞれ距離  $d_y$  及び  $d_x$  だけ離れている。

時間変化外部磁場をカテーテル 20 の遠位端 22 に加えるとき、コイル 60, 62 及び 64 によりアナログ信号が発生する。そのアナログ信号は、コイルワイヤ 72 によりカテーテルを通して伝達するのが好ましい。これらのアナログ信号の大きさは、例えば、機能部 24 により測定され機能ワイヤ 76 によりカテーテルを通して伝達される電気生理学的信号などの、カテーテル 20 内及びカテーテル 20 周囲にある他の電気信号に比べて一般的に小さい。さらに、また、外部磁場により、コイル 60, 62 及び 64 が発生させるものではない不要な電流が、コイルワイヤ 72 を流れるかもしれない。これらの他の電気信号及び不要な電流により、ノイズ信号あるいは妨害信号が、コイルが発生させる信号と共に現れる場合がある。従って、この発明の好適実施例では、コイルから受信される位置及び方位信号を高 S/N 比に保つように、ワイヤ 72 をより合わせ対として構成する。また、シールド 74 により電磁干渉から遮蔽してもよい。

この発明の別の好適実施例では、図示していないが、カテーテル 20 は、さらに、コイル 10

60, 62 及び 64 に隣接する位置にある 1 個以上のアナログ - デジタル (A / D) 変換器を含んでいる。アナログ - デジタル (A / D) 変換器は、コイルが発生させるアナログ信号をデジタル形式に変換する。この実施例では、コイルの信号はカテーテルを通してデジタル形式で伝達する。機能部 24 により測定される信号を同様にデジタル化しても良い。このようにして、信号を移送するために必要な電線の数がより少なく、信号線によって取られるカテーテルの部分がより少ない。

国際特許出願第 P C T / U S 95 / 01103 号に説明されるように、コンソール 34 にある信号処理回路 40 はコイルワイヤ 72 により伝えられる信号を受信し、それらをコンピュータ 36 に伝達する。コンピュータ 36 は、固定された外部座標空間を基準とした、素子 28 の 3 次元並進位置及び軸 66, 68 及び 70 の回転方位を計算する。遠位側先端 10 26 の実際の位置及び方位は、そのとき、軸 68 によって定義されるような、素子 28 の中心からの先端 26 の距離 L 及び軸 66, 68 及び 70 の方位を考慮して計算される。

カテーテル 20 の製造過程でのずれにより、一般的に、距離 L がカテーテルごとに変わり、先端 26 の位置を計算する際に誤差が生じることが経験的に見出された。さらに、コイル 60 の軸 66 は、一般的に、先端 26 を通して通過するカテーテル 20 の長軸との絶対的な位置関係からずれ、コイル 60 及び 64 のそれぞれの軸 66 及び 70 は、一般的に、軸 66 に対してあるいはお互いに、正確には直交しない。それによって、カテーテルの位置及び方位を決定する再に付加的な誤差を生じる。結局、コイル 60, 62 及び 64 のそれぞれのゲイン及び距離  $d_y$  及び  $d_x$  の変化により、カテーテルの位置及び方位を決定する際に付加的な誤差を生じるかもしれない。

従って、この発明の好適実施例では、カテーテル 20 の位置及び方位を決定するために使う素子 28 を、カテーテルを患者の体内に挿入する前に較正する。この較正を、例えば図 3A, 図 3B 及び図 4 に示される 1 個以上の治具を使って行うのが好ましい。

図 3A 及び図 3B は、コイル 60, 62 及び 64 の直交性からのずれ及びそれぞれのゲインを較正する際に使用する治具 77 の好適実施例を示す図である。治具 77 は、相互に直交した、平行ラジエータコイル 79, 81 及び 83 の対をベース 85 上に搭載して 3 個有している。図示されていないが、ラジエータコイルは、ラジエータコイルに磁場を発生させるラジエータ駆動回路に連結される。各ラジエータコイル対は、コイル対によって規定される平面に実質的に垂直であり、こうして、他の 2 つのラジエータコイル対が発生させる磁場に実質的に直交している磁場を発生させる。

ラジエータコイルは、治具の中心に隣接する領域、すなわち 3 個のラジエータコイル対の間ににおける中心に位置づけられる領域に、予め決められた実質的に均一な磁場を発生させるように構成されている。駆動回路は、3 個のラジエータコイル対が発生させるそれぞれの磁場の大きさが等しいように調整するのが好ましい。

図 3B に示されるように、治具 77 は、さらに治具内に位置づけられる図 3A には見られないカテーテル鉗子アセンブリ 87 をさらに有している。図 3C に示されるように、鉗子アセンブリ 87 は鉗子ベース 89 を含んでいる。鉗子ベース 89 は既知の位置及び方位で、1 個以上のラジエータコイル 79, 81 及び 83 に固定されている。鉗子アセンブリに保持されるカテーテルが治具の中心に隣接する実質的に均一な磁場の領域にあり、カテーテルの長軸が 1 個の平行ラジエータコイル対、例えば図 3B に示されるようにコイル 83 によって規定される平面に実質的に垂直となるように、鉗子アセンブリ 87 を組み立て及び構成するのが好ましい。鉗子カバー 91 は、ヒンジ 93 によりベース 89 に回転可能に取り付けられている。ベース 89 及びカバー 91 は、それぞれ半径が実質的にカテーテル 20 の半径に等しい半円溝 95 及び 97 を含んでいる。

鉗子アセンブリ 89 は、発熱体 99 及び少なくとも 1 個の温度センサ 101 を含み、それを使って、カテーテル 20 の遠位端 22 をカテーテルが挿入される体の温度に実質的に等しい温度に加熱し、較正中、遠位端をその温度に維持するのが好ましい。従来から知られているように、磁場に対するコイル 60, 62 及び 64 の応答が、温度の関数として変化する場合がある。例えば、コイルがフェライトコアに巻かれるとき、そのインダクタンスが温度で変化し、その変化により、素子 28 の較正に誤差を発生させる場合がある。従

10

20

30

40

50

って、遠位端 22 を、一般的に、較正の間中、37 の温度に加熱し及び維持する。ただし、例えば、心臓切開手術の間に一般に誘発されるような低体温の条件下でカテーテルが使われるとき、他の温度が選択されるかもしれない。

カテーテル 20 を較正する際に治具 77 を使うため、カテーテルを溝 95 に挿入し、その長軸を中心回転方位に回転する。図 2 に示される X, Y 及び Z カテーテル軸を、ラジエータコイル対 83, 79 及び 81 によりそれぞれ規定される磁場方向に実質的にそろえるのが好ましい。望ましい回転方位を、例えばカテーテルの外表面にある基準の目印や他の特徴（図示せず）により示しても良い。一方、カテーテルがその長軸を中心回転対称である、この発明の好適実施例では、回転方位は重要ではなく、X 軸及び Y 軸をそろえる必要はない。

カテーテル 20 を溝 95 に挿入し必要に応じてそろえた後、カテーテルを保持するようにカバー 91 を所定の位置に下げる。このようにして、カテーテルを、ラジエータコイル 81, 83 及び 85 が発生させる磁場を基準とした既知の方位に固定する。

それぞれのカテーテルコイル 60, 62 及び 64 のゲイン及び角方位を、続いてラジエータコイル対 79, 81 及び 83 を始動させ、予め決められた既知の磁場を発生させ、カテーテルコイルが発生させる信号の大きさを測定することによって較正する。

まず、コイルのゲインを較正するために、それぞれのカテーテルコイル信号の合計の大きさを、各カテーテルコイル 60, 62 及び 64 に順に応答して各コイル対が発生させる信号の大きさの 2 乗を合計することによって求める。コイル 60, 62 及び 64 の周辺の磁場は、各コイル軸 66, 68 及び 70 に沿って、等しく実質的に均一な成分を持っているので、信号の合計の大きさは、コイル 60, 62 及び 64 のそれの方位及び位置に依存せず、それぞれのコイルのゲインにのみ依存する。このようにして、測定された大きさを標準期待値で割ることによって、測定された信号の合計の大きさを、それぞれのコイル 60, 62 及び 64 に対する規格化因子を決定するために使うことができる。その後、これらのコイルから受信された信号の大きさを、ゲインのずれを訂正するために、それぞれの規格化因子によって多重化しても良い。

さらに、治具 77 は、直交性からのずれを訂正するように、カテーテル 20 を基準としたコイル 60, 62 及び 64 のそれの方位を較正するために使う。各磁場に応答して各コイル 60, 62 及び 64 が発生させる信号の規格化された大きさは、それぞれのコイルの軸 66, 68 及び 70 と加えられた磁場との間の角のコサインに比例する。こうして、ラジエータコイル対 79, 81 及び 83 が加える 3 つの直交磁場の方向に対応する、3 つのそのような角のコサインを、各カテーテルコイル 60, 62 及び 64 に対して求めることができる。上述したように、カテーテル 20 を、X, Y 及び Z カテーテル軸を実質的に 3 つの直交磁場の方向にそろえるようにして鉗子アセンブリ 87 に保持するので、カテーテル軸を基準としたコイルの方位はこうして決定できる。

この発明の好適実施例では、ラジエータコイル対 83 に対応する Z 軸磁場が始動するとき、コイル 60 から受信された信号の規格化された大きさ、 $S_{60}(Z)$  が受信され及び測定される。X 及び Y 軸磁場が同様に作動し、対応する規格化された信号  $S_{60}(X)$  及び  $S_{60}(Y)$  が受信される。 $S_{60}(X)$ 、 $S_{60}(Y)$  及び  $S_{60}(Z)$  を、コイル 60 についてのコイル角較正因子を計算するために使い、コイル角較正因子を、その後、カテーテル 20 に記録し、カテーテルの位置及び方位を決定するために使う。同様の処置を、コイル 62 及び 64 を較正するために使う。

コイル対 79, 81 及び 83 が発生させる磁場は、実質的に直交しており、等しい大きさであるけれども、コイル対が正確に巻かれていないと、直交性及び均一性からのわずかなずれが生じる場合がある。このようなずれが、もし訂正されないならば、カテーテルの較正に誤差が生じる場合がある。従って、この発明の好適実施例では、マスターコイル（図示せず）を治具 77 を較正するために使う。このマスターコイルは、既知のあらかじめ決められた幾何学的な構成及び寸法で、正確に巻かれているのが好ましく、その結果、加えられた磁場に対する感度が、従来から知られている理論的な方法を使って正確に計算できる。

マスター コイルは、既知の予め決められた位置及び方位で、治具 77 の中心に配置される。マスター コイルの軸は実質的にコイル対 79 が発生させる磁場の方向に平行である。コイル対を始動し、それによってマスター コイルに電気信号を発生させる。この信号を、コイル対 79 についての較正因子を決定するために記録し、標準信号値と比較する。この処置をコイル対 81 及び 83 に対して繰り返す。

カテーテル 20 を、カテーテルを較正するために治具 77 に配置するとき、カテーテルのゲイン規格化因子及び角較正因子を決定する前に、最初に、コイル 60, 62 及び 64 から受信される信号を、コイル対 79, 81 及び 83 の較正因子を考慮して訂正する。

1 個のマスター コイルを多種多様な治具を較正するために使うことができ、その結果、較正された治具のすべてが、カテーテルを較正する際に、同一の結果を与えるということを認識されたい。さらに、国際特許出願第 PCT/US95/01103 号に従って、同じマスター コイルを、また、被験者の体内のカテーテルの位置を検出するための磁場を引き起こすラジエータコイルを較正するために使うことができる。

さらに、他の治具及びラジエータコイルを順に較正するために、第 1 のマスター コイルが、追加のマスター コイルを生み出し、そのマスター コイルを較正するために使うことができるということは理解されたい。第 1 のマスター コイルを使って治具を較正した後、第 2 のマスター コイルを同様に治具に配置する。第 2 のマスター コイルが発生させる信号を、上述した治具を較正するための処置を使って測定する。同じ条件において、第 2 のマスター コイルが発生させる信号と第 1 のマスター コイルが発生させる信号との間の相違を、第 2 のマスター コイルについての較正を決定するために使う。これらの較正因子は、この発明の好適実施例に従って、カテーテル 20 に較正因子を格納するために使う素子及び方法に類似の素子及び方法を使って、第 2 のマスター コイルに格納しても良い。

図 4 は、カテーテルの先端 26 を基準としたコイル 60 の変位を較正する際に役立つ治具 80 の好適実施例を示す図である。治具 80 は、カテーテル 20 を挿入できる挿入口 82 を 1 個以上有している。各挿入口 82 は、治具 80 を基準とした、既知の予め決められた深さ及び角方位を持っている。カテーテルを挿入口 82 に十分に挿入すると、カテーテルの遠位側先端 26 は、挿入口の内側端と接する。治具 80 及び挿入口 82 は、カテーテルが挿入口に丁度はまるように組み立てられている。その結果、カテーテルを十分に挿入するとき、その遠位側先端の配置及び角方位が、治具により規定される基準空間に対して正確に決定される。治具 80 は、また、図 3C に示されそれへの言及において説明されるように、発熱体及び 1 個以上の温度センサ（図 4 に図示せず）を含んでいるのが好ましい。治具 80 の好適実施例は、さらに 1 個以上のラジエータコイル 84 を有しており、このラジエータコイル 84 は、素子 28 の周辺に、既知の空間的に変化する磁場を発生させる。これらの磁場により、素子 28 のコイル 60, 62 及び 64 に、図 1 に示されるように、カテーテル 20 を通して信号処理回路 40 に伝達され、これらの回路からコンピュータに伝達される信号が発生する。コンピュータは、コイル 60, 62 及び 64 が発生させるそれぞれの信号の大きさを測定し、その大きさの訂正值をゲイン規格化因子及びコイル角較正因子を使って決定する。ゲイン規格化因子及びコイル角較正因子は、上述したよう决定するのが好ましい。訂正された大きさを、標準期待値と比較する。標準期待値は、コイルの期待された位置における既知の磁場強度に基づいている。訂正され、測定された大きさと標準期待値との間のずれを、変位訂正因子を計算するために使う。変位訂正因子は、それぞれの期待値からの、図 2 に示されるような変位  $L$ 、 $d_y$  及び  $d_x$  のずれに対応する。カテーテル 20 に関する較正データは、従来から知られているさまざまな方法に従って計算できる。例えば、この発明の好適実施例では、カテーテルの遠位側先端 26 の位置及び方位を計算するためにコンピュータにより使われる、ゲイン規格化因子、角較正因子及び変位訂正因子を、参照用テーブルの形で電子的に格納する。

治具 80 についてのこの発明の別の好適実施例では、治具は、治具により規定される基準空間に対して、それぞれが異なった予め決められた位置及び方位にある、複数の挿入口を含んでいる。ラジエータコイル 84 は、被験者の体内のカテーテル 20 の位置及び方位を決定するために外部磁場を発生させるために使われるラジエータコイル（図示せず）が発

10

20

30

40

50

生させる磁場と実質的に同一の磁場を発生させる。さらに、ラジエータコイル 84 は、被験者の体内のカテーテル 20 の位置及び方位を決定するために外部磁場を発生させるために使われるラジエータコイルの相対的な位置及び方位と実質的に同一である相対的な位置及び方位にある治具 80 上に配置されている。

カテーテル 20 が各挿入口 82 に順に挿入される。ラジエータ 84 が発生させる磁場により、素子 28 のコイル 60, 62 及び 64 が、信号処理回路 40 及びコンピュータ 36 に伝達される信号を発生させる。国際特許出願第 P C T / U S 95 / 01103 号に説明される方法に従って、コンピュータは、ゲイン規格化因子及び角較正因子を最初に適用した後、これらの信号を位置データの計算のために使う。ゲイン規格化因子及び角較正因子は、上述のように決定するのが好ましい。計算された素子 28 の位置及び方位を、挿入口 82 内の先端 26 についての既知の予め決められた位置及び方位と比較する。位置及び方位の計算された値と公知の値との間の差を、経験的な変位訂正ベクトル D 及び角訂正ベクトル を計算するために使う。複数の挿入口により規定される複数の位置及び方位に対して計算される D 及び の値を使って、測定される位置及び方位の関数としての D 及び のマップを、治具 80 により規定される位置及び方位の範囲にわたって発生させる。カテーテル 20 が、続いて人体内で使われるとき、先端 26 の実際の正しい位置を決定するために、コンピュータ 36 はこれらの訂正ベクトルを素子 28 が発生させる位置及び方位信号に適用する。

較正ベクトル因子 D 及び は、従来から知られている方法に従って、計算し及び記録できる。例えば、この発明の好適実施例では、位置座標 x, y, z 及び角座標 <sub>1, 2, 3</sub> の多項関数を、最小二乗フィッティングのような従来から知られている方法により D 及び のマップに合わせる。このようにして、得られた多項係数を、電子的に格納し、それから訂正ベクトルを決定する際にコンピュータにより利用する。このような方法の代わりに、ベクトル関数の値それ自身を、参照テーブルの形で電子的に格納し、カテーテルの遠位側先端 26 の位置及び方位を計算するためにコンピュータにより使う方法もある。

いくつかのこの発明の好適実施例では、カテーテル 20 を、絶縁回路によって、例えば上述した図 1 への言及において説明されているような、ハンドル 30 にある 1 個以上の絶縁形トランジスタによって、コンソール 34 から電気的に絶縁している。一般的に、そのような誘電部品及び他の絶縁回路により、それらにより伝達される信号に非線形性が生じ、回路 40 に伝達される信号、特にアナログ信号にひずみが生じる。このような非線形性は、カテーテルの較正時に測定するのが好ましく、それから、カテーテル 20 に記録される較正情報は、絶縁回路により生じる信号の非線形性に関するデータを含んでいるのが好ましい。

この発明の好適実施例では、上述した方法に従ってあるいは従来より知られている他の方法を使って決定される較正訂正関数を、その後、記憶素子に電子的に格納している。その素子は、カテーテル 20 内にあるのが好ましい。カテーテルがコンソール 34 に連結されるとき、この記憶素子はコンソールのコンピュータにアクセス可能となる。

図 5 に概略的に示されるような、この発明の 1 つの好適実施例では、コネクター 44 はデジタルマイクロ回路 90 を含み、カテーテル 20 についての較正訂正関数データを電子的に格納している。マイクロ回路 90 は、EEPROM やフラッシュ ROM を含むのが好ましく、それらの代わりとして、EPROM, PROM, 不揮発性 RAM または従来から知られている他のタイプの書き込み可能な記憶素子を含んでいても良い。カテーテル 20 を較正するとき、その特定の訂正データをコンソールのコネクター 44 に位置づけられるマイクロ回路に格納する。下述するように、マイクロ回路は、コンピュータに簡便にアクセス可能である。

図 5 に示される好適実施例では、コネクター 44 はさらにピン 92, 94, 96 及び 98 を含んでいる。ピンは端子 46 の対応するソケットと結合している。機能ピン 94 は、機能ワイヤ 76 を伝て信号処理回路 40 に伝達される電気生理学的なアナログ信号を信号処理回路に連結する。コイルピン 92 は、コイル 60, 62 及び 64 からコイルワイヤ 72 により伝達される位置及び方位アナログ信号を信号処理回路 40 及びコンピュータ 36

10

20

30

40

50

に連結する。コンピュータ36はカテーテル20の位置及び方位を計算する。コンピュータは、さらに、マイクロ回路90に格納されている較正訂正関数デジタルデータをメモリピン96を経て読み取り、これらのデータをカテーテルの正しい位置及び方位を計算する際に使う。

1個以上の書き込み許可ピン104も同様にマイクロ回路90に連結している。これらのピンは、マイクロ回路に所望の較正データを書き込むことを可能にするために使う。較正時に、書き込み許可入力を許可し、較正データをマイクロ回路に記録する。その後、例えば、書き込み許可ピンを取り除くことにより、あるいは図5に示されるようにそれをアースに接続することにより、書き込み許可入力を禁止する。その結果、さらに、較正データをマイクロ回路に記録することができず、マイクロ回路は読み取り専用モードで作動する。

10

一方、マイクロ回路90がEEPROMを有している、この発明の他の好適実施例では、書き込み許可入力を、書き込み保護コマンドを素子に送ることによって禁止しても良い。このコマンドは、可逆的であっても不可逆的であっても良い。

この発明の他の好適実施例では、マイクロ回路90は、パスワード保証アクセス制御を組み入れている素子を有しており、マイクロ回路への書き込みアクセスを行うためには、適当なパスワードを最初に入力することが必要である。例えば、1つのそのような好適実施例では、マイクロ回路90は、キシコール(Xicor)社製のパスワードアクセスセキュリティスパーバイザ(PASS(登録商標))X76F041シキュアーフラッシュROM素子を有している。以下に説明されるように、マイクロ回路は、製造時に較正データを書き込まれ、その後、書き込み動作が全くできない“読み取りアクセス専用”モード、あるいは較正データと異なるあるデータを素子に書き込むことができる“読み取りアクセス・書き込み専用”モードで動作する。マイクロ回路の動作モードを変えるためには、適当なパスワードを入力する必要がある。一般に、システムの使用者はパスワードを利用できない。

20

この発明の別の好適実施例では、マイクロ回路は、カテーテルのコネクターに収容されるEPROM素子あるいはPROM素子を有している。EPROMあるいはPROMの入出力接続はコネクターのピンに連結されている。較正データは、製造時に、図示されていない適当な書き込み素子を使ってEPROMあるいはPROMに記録される。書き込み素子は、較正に使うデータをコンピュータから受信する。書き込み素子を、カテーテルのコネクター44に接続し、コネクターを通してデジタル信号を入力することにより、EPROMあるいはPROMに書き込む。その後、再び、EPROMあるいはPROMに書き込みができない。

30

この発明のいくつかの好適実施例では、マイクロ回路に記録されているデータは較正コードを含んでいる。較正コードは、較正データが変更されあるいは改悪されていないことを確定するように、従来から知られている方法に従って暗号化されている。較正データは、チェックサムを含むのが好ましい。使用者がカテーテル20をコンソール34に接続するとき、コンピュータは較正コードを読み取り、そのコードを予め書き込まれた値と比較する。そのコードが所望の予め書き込まれた値と一致していないならば、コンピュータは、カテーテルが適当に較正されていないかもしれないということを示すメッセージをディスプレイ42に表示させる。コンピュータは、さらに、所望の予め書き込まれた値と一致するコードを持つカテーテルが接続されるまで、システムに動作をやめさせることができる。

40

較正コードは、不正な関係者による解読を防ぐ方法、例えばパブリックキーやプライベートキーを使うRSA暗号化方式や他の従来から知られている方法を使って暗号化するのが好ましい。RSA暗号化のような方法を使うとき、品質が劣るかもしれない不正な代用品を使用できないように、プライベートキーを、正規のカテーテルの製造業者だけが知っている。

さらに、この発明の好適実施例では、マイクロ回路に記録されているデータは、失効日時を含んでいる。失効日時の後、カテーテルを使うことができない。使用者がカテーテル2

50

0をコンソール34に接続するとき、コンピュータ36は失効日時を読み取り、それから、例えばリアルタイムクロック回路が発生させる実際の日時と比較する。失効日時が過ぎているならば、コンピュータは、カテーテルをさらに使うことは不適当であることを示すメッセージをディスプレイ42に表示させる。コンピュータは、さらに、妥当な失効日時を持つカテーテルが接続されるまで、さらなる動作を防ぐことができる。

失効日時は、カテーテルが最初に使われるときに、カテーテル20のマイクロ回路90に書き込むことにより、コンピュータ36により記録される。このようにして、カテーテル20を、最初にコンソール34に接続するとき、コンピュータ36は、失効日時がまだマイクロ回路90に記録されていないことを検出し、マイクロ回路に、実際の日時後の予め設定された期間である適当な失効日時を記録する。予め設定された期間は、カテーテルの予想される使用期間に基づいて、製造業者が決めのが好ましい。

マイクロ回路90は、例えば上述したX76F041素子などのアクセス制御回路を含む素子を有している、この発明の好適実施例では、マイクロ回路は、その記憶域が“読み取りアクセス・書き込み専用”モードで動作可能なように書き込まれている。そのモードは、適当なパスワードを入力することによってのみ変えることができるが、概してはシステムの使用者がそのパスワードを利用することはできない。“読み取りアクセス・書き込み専用”モードでは、ビットを“1”から“0”に変えることにより、記憶域に格納されている数字を減らすことができるが、書き込まれたとおりのマイクロ回路では“0”を“1”に変えることができないので、増やすことはできない。製造時に、記録域が最大値となるようにセットする、すなわちすべてのビットを“1”にセットするのが好ましい。また、上述したように、カテーテル20を最初に使うときに、コンピュータ36は、レジスタにある1個以上のビットを“1”から“0”に変えることにより、マイクロ回路に適当な失効日時を書き込む。その後、失効日時をより遅い日に変えることができない（正しいパスワードが最初に入力されないという条件において）。

以上の点に変えて、あるいは以上の点に加えて、上述したようなアクセス制御回路を有しているマイクロ回路90を、使用者が改ざんしたり間違ったりしないような方法で、カテーテル20が使われた回数を突き止めるために使うことができる。カテーテル20を使うことができる回数に対応する記録が、製造時に素子の記録域に格納され、マイクロ回路は、上述したように、記憶域が“読み取りアクセス・書き込み専用”モードで動作可能なように書き込まれているのが好ましい。カテーテルが使われる各回では、コンピュータ36は記録域の記録を読み取り、そこにある1個以上のビットを“1”から“0”に変えることによってそれを減らす。記録を構成する全ビットが0に等しくなるとき、あるいは他の予め決められた最小値に達するとき、コンピュータは、コンピュータをさらに使うのに適当ではないということを示すメッセージを使用者に表示させ、好ましくは、適当なカテーテルが接続されるまで、さらなる動作を防ぐ。

同様に、以上の点に変えて、あるいは以上の点に加えて、マイクロ回路90を、カテーテル20の使用継続時間を突き止めるために使うことができる。この場合、カテーテルの使用継続時間に対応する記録が、マイクロ回路の“読み取りアクセス・書き込み専用”的記憶域に格納される。カテーテルを使っている間、一定の予め決められた間隔で、コンピュータ36がその記録を読み取り、そこにある1個以上のビットを“1”から“0”に変えることによってそれを減らす。全体の記録がゼロあるいは他の最小値に達するとき、上述したようにさらなる動作を防止する。上述したように、コイルワイヤ72を伝ってコイル60, 62及び64から伝達される低レベルアナログ信号を、一般的に、機能ワイヤ76にある他のアナログ信号やマイクロ回路90に伝達されるデジタル信号による干渉から保護しなければならない。従って、図5に示されるような、この発明の好適実施例では、コネクター44は電磁シールド74を含んでいる。電磁シールドは、コネクターにあるピン98を経てアースに連結されている。

この発明の別の好適実施例では、シールド74は、雑音消去回路（図示せず）により駆動する活性シールドである。

さらに、マイクロ回路90をコネクター44に位置づけ、コイルワイヤ72にある低レベ

10

20

30

40

50

ルアナログ信号の近傍でデジタル信号を伝える電気導線の長さを最小に保ち、それにより、低レベル信号との電気的な干渉の可能性が減るということは理解されたい。

この発明の好適実施例では、カテーテル 20 は信号処理装置及び／又は計算装置に物理的に接続されていないワイヤレスカテーテルである。正しくは、送受信機をカテーテルの遠位端に取り付け、カテーテルが発生させるすべての電気信号を送受信機により送信する。送受信機は、例えば I R (赤外線) 送信、R F 送信あるいは音響送信などの無線通信方法を使って、信号処理装置及び／又は計算装置と通信する。このように構成する 1 つの利点は、(電気に敏感な) 心臓に挿入されるカテーテルを、容易に(身体に対して) 外側の電源から完全に絶縁し及び／又は電気的にフローティングな状態にすることができるということである。別の利点は、多くのオペレータのうちの 1 人が巻き込まれたり及び／又は間違って身体から引き出すかもしれないケーブル及び電線や配線の引き回し量が減少するということである。また、別の利点は、カテーテル全体を 1 個のユニットとして殺菌することができるので、殺菌及びそのようなカテーテルを無菌状態に維持することが容易であるということである。そのようなカテーテル用の電源は、恒久的にカテーテル内に密閉するのが好ましい。カテーテルを使うとき、電源を始動し、制限時間の間、カテーテルに電力を供給することができる。このような電源に代わるものとして、各回の使用後に再充電できる再充電可能電源があり、この電源により、同じカテーテルを多種多様に使うことができる。

この発明の好適実施例では、送受信機を含むカテーテルの近位端を、オペレータのベルトに取り付ける。カテーテルの遠位端から数フィート離れたカテーテル上に、カテーテルを制御するためのハンドルを配置するのが好ましい。理解できるように、そのようなカテーテルを、体内への物質の注入及び切除に使うとき、ちょっとの間、R F 発生機のような外部の装置に接続するのが好ましい。

上述の好適実施例では、位置及び方位感知装置の較正に関して説明したが、この発明の他の好適実施例において、カテーテル 20、特にマイクロ回路 90 に格納される較正データがカテーテルの他の特徴に関するものであっても良い。例えば、この発明のいくつかの好適実施例では、生理学的なセンサ、アクチュエータまたは治療具に関する較正データをカテーテルに格納している。この発明の別の好適実施例では、カテーテルの遠位端を操縦する際に使う圧電性の動作制御素子のゲインに関する較正データをカテーテルに格納している。

上述した好適実施例は、一例として挙げられており、発明の全般は、請求の範囲によってのみ制限されるということは理解されたい。

10

20

30

【 図 1 】

FIG. 1

【 図 2 】

FIG. 2

【図3A】

FIG. 3A

【 図 3 B 】

FIG. 3B

【図3C】

【図4】

FIG. 3C

FIG. 4

【図5】

FIG. 5

---

フロントページの続き

(72)発明者 ベン ハイム , シュロモ

イスラエル国、 34454 ハイファ、 イエッフェーノフ 101

(72)発明者 フェンスター ,マイヤー<sup>1</sup>

イスラエル国、 49600 ペタック・チクバ、 ブランデ・ストリート 61

審査官 上田 正樹

(56)参考文献 特開平08-000542 (JP, A)

特開平03-004831 (JP, A)

特開平07-171089 (JP, A)

特開平07-171090 (JP, A)

(58)調査した分野(Int.Cl., DB名)

A61B 5/06