(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2016-0140667

(43) 공개일자 2016년12월07일

- (51) 국제특허분류(Int. Cl.)

*H03K 3/012* (2006.01) *G01R 31/28* (2006.01)

*G01R 31/317* (2006.01) *G05B 11/01* (2006.01)

*H03K 19/003* (2006.01) *H03K 3/03* (2006.01)

*H03K 5/00* (2014.01) *H03K 5/01* (2006.01)

- (52) CPC특허분류

*H03K 3/012* (2013.01)

*G01R 31/2882* (2013.01)

- (21) 출원번호 10-2016-7026935

- (22) 출원일자(국제) 2015년03월04일

심사청구일자 없음

- (85) 번역문제출일자 2016년09월28일

- (86) 국제출원번호 PCT/US2015/018785

- (87) 국제공개번호 WO 2015/153048

국제공개일자 2015년10월08일

- (30) 우선권주장

61/973,765 2014년04월01일 미국(US)

14/507,679 2014년10월06일 미국(US)

- (71) 출원인

퀄컴 인코포레이티드

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

- (72) 발명자

리우, 조나단

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775 퀄컴 인코포레이티드 (내)

이브라하모비, 자스민 스마일라

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775 퀄컴 인코포레이티드 (내)

(뒷면에 계속)

- (74) 대리인

특허법인 남앤드남

전체 청구항 수 : 총 27 항

(54) 발명의 명칭 **직접 회로 동적 디-에이징**

### (57) 요 약

직접 회로는 에이징 센서로 에이징을 측정함으로써 회로 에이징을 동적으로 보상한다. 에이징 센서는 에이징 및 언-에이징 컨디션들 둘 다에서 회로 속도들을 측정하기 위해 동일한 회로를 이용한다. 예시적인 에이징 센서는 2개의 지연 라인들을 포함한다. 지연 라인들은 정적 에이징 상태에 있도록 제어되거나, 또는 지연 라인들은 주(뒷면에 계속)

### 대 표 도

파수가 에이징에 의해 느려지는 에이징된 상태 또는 주파수가 에이징에 의해 느려지지 않는 비-에이징된 상태에서 동작할 수 있는 링 오실레이터를 형성하도록 커플링된다. 집적 회로는 동적 전압 및 주파수 스케일링을 위해 에이징 측정들을 이용한다. 동적 전압 및 주파수 스케일링은 에이징 측정들에 기초하여 주기적으로 업데이트되는 동작 주파수 및 대응하는 전압의 테이블을 이용한다. 집적 회로는 테이블을 업데이트하도록 에이징 측정들과 회로 성능 간의 관계에 관한 정보를 이용한다.

## (52) CPC특허분류

*G01R 31/31725* (2013.01)

*G05B 11/01* (2013.01)

*H03K 19/00384* (2013.01)

*H03K 3/0315* (2013.01)

*H03K 5/01* (2013.01)

*H03K 2005/00013* (2013.01)

## (72) 발명자

디펜더퍼, 잔 크리스찬

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775 웰컴 인코포레이티드 (내)

---

## 아우온, 카를로스

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775 웰컴 인코포레이티드 (내)

## 명세서

### 청구범위

#### 청구항 1

집적 회로의 에이징(aging)을 감지하기 위한 회로로서,

제 1 입력 및 제 1 출력을 갖는 제 1 지연 체인;

제 2 입력 및 제 2 출력을 갖는 제 2 지연 체인; 및

상기 제 1 및 제 2 지연 체인들의 회로가 에이징하는 에이징 상태, 에이징된 회로의 지연들에 기초한 주파수로 오실레이팅하는 클록 출력을 생성하도록 상기 제 1 지연 체인이 상기 제 2 지연 체인에 커플링되는 에이징된 오실레이팅 상태, 또는 비-에이징된 회로의 지연들에 기초한 주파수로 오실레이팅하는 클록 출력을 생성하도록 상기 제 1 지연 체인이 상기 제 2 지연 체인에 커플링되는 비-에이징된 오실레이팅 상태로 상기 제 1 지연 체인 및 상기 제 2 지연 체인을 배치하도록 구성된 제어 모듈

을 포함하는,

집적 회로의 에이징을 감지하기 위한 회로.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 지연 체인은 상기 제 1 입력과 상기 제 1 출력 간에 커플링되는 지연 엘리먼트들의 제 1 체인을 포함하고, 상기 제 2 지연 체인은 상기 제 2 입력과 상기 제 2 출력 간에 커플링되는 지연 엘리먼트들의 제 2 체인을 포함하는,

집적 회로의 에이징을 감지하기 위한 회로.

#### 청구항 3

제 2 항에 있어서,

상기 지연 엘리먼트들 각각은 인버터를 포함하는,

집적 회로의 에이징을 감지하기 위한 회로.

#### 청구항 4

제 3 항에 있어서,

각각의 인버터는 직렬로 된 복수의 p-채널 트랜지스터들 및 직렬로 된 복수의 n-채널 트랜지스터들을 포함하는,

집적 회로의 에이징을 감지하기 위한 회로.

#### 청구항 5

제 1 항에 있어서,

상기 에이징 상태는 상기 제 1 지연 체인 및 상기 제 2 지연 체인에 동작 전압을 공급하는 것을 포함하는,

집적 회로의 에이징을 감지하기 위한 회로.

#### 청구항 6

제 5 항에 있어서,

상기 에이징 상태는 추가로, 상기 제 1 입력에 제 1 로직 값 및 상기 제 2 입력에 제 2 로직 값을 공급하는 것을 포함하며,

상기 제 1 로직 값은 상기 제 2 로직 값의 보수인,

집적 회로의 에이징을 감지하기 위한 회로.

#### 청구항 7

제 1 항에 있어서,

상기 에이징된 오실레이팅 상태에서 상기 클록 출력의 오실레이션들의 기간은, 에이징에 의해 느려지는 제 1 지연 체인을 통한 천이(transition)에 대한 지연 및 에이징에 의해 느려지는 제 2 지연 체인을 통한 천이에 대한 지연의 결합을 포함하는,

집적 회로의 에이징을 감지하기 위한 회로.

#### 청구항 8

제 1 항에 있어서,

상기 비-에이징된 오실레이팅 상태에서 상기 클록 출력의 오실레이션들의 기간은, 에이징에 의해 느려지지 않은 제 1 지연 체인을 통한 천이에 대한 지연 및 에이징에 의해 느려지지 않은 제 2 지연 체인을 통한 천이에 대한 지연의 결합을 포함하는,

집적 회로의 에이징을 감지하기 위한 회로.

#### 청구항 9

제 6 항에 있어서,

상기 에이징된 오실레이팅 상태는 상기 제 1 출력과 상기 제 2 출력 간에 선택하는 것 및 선택된 신호를 상기 제 1 입력 및 상기 제 2 입력에 커플링하는 것을 포함하고,

상기 제 1 출력은 상기 제 1 입력이 상기 제 1 로직 값으로 천이한 이후 선택되고, 상기 제 2 출력은 상기 제 2 입력이 상기 제 2 로직 값으로 천이한 이후 선택되는,

집적 회로의 에이징을 감지하기 위한 회로.

#### 청구항 10

제 6 항에 있어서,

상기 비-에이징된 오실레이팅 상태는 상기 제 1 출력과 상기 제 2 출력 간에 선택하는 것 및 선택된 신호를 상기 제 1 입력 및 상기 제 2 입력에 커플링하는 것을 포함하고,

상기 제 1 출력은 상기 제 1 입력이 상기 제 2 로직 값으로 천이한 이후 선택되고, 상기 제 2 출력은 상기 제 2 입력이 상기 제 1 로직 값으로 천이한 이후 선택되는,

집적 회로의 에이징을 감지하기 위한 회로.

### 청구항 11

집적 회로를 디-에이징(de-aging)하기 위한 방법으로서,

안전 전압 및 주파수로 상기 집적 회로의 동작을 초기화하는 단계;

복수의 동작 주파수들에 대한 타겟 성능 센서 측정 값들을 포함하는 계수 테이블의 초기 값들을 이용하여 상기 집적 회로의 동적 전압 및 주파수 스케일링을 인에이블하는 단계;

에이징 센서를 이용하여 상기 집적 회로의 에이징을 감지하는 단계;

에이징 가드 밴드(aging guard band)를 결정하기 위해 센서 에이징과 동작 회로의 에이징 간의 관계를 나타내는 에이징 스케일링 비(aging scaling ratio) 및 상기 동작 회로의 최대 동작 주파수와 전압 간의 관계를 나타내는 전압 대 주파수 스케일링 팩터로 감지된 에이징을 곱하는 것을 포함하여 상기 감지된 에이징에 기초하여 상기 계수 테이블을 업데이트하는 단계; 및

업데이트된 계수 테이블을 이용하여 동적 전압 및 주파수 스케일링을 지속하는 단계

를 포함하는,

집적 회로를 디-에이징하기 위한 방법.

### 청구항 12

제 11 항에 있어서,

상기 집적 회로의 에이징을 감지하는 단계는 에이징에 의해 느려지는 렘 오실레이터의 주파수를 측정하는 단계 및 에이징에 의해 느려지지 않는 렘 오실레이터의 주파수를 측정하는 단계를 포함하는,

집적 회로를 디-에이징하기 위한 방법.

### 청구항 13

제 11 항에 있어서,

상기 감지된 에이징에 기초하여 계수 테이블을 업데이트하는 단계는 에이징으로 인한 센서 오실레이팅 주파수의 퍼센티지 변화로서 표현되는 감지된 에이징을 이용하는,

집적 회로를 디-에이징하기 위한 방법.

### 청구항 14

제 13 항에 있어서,

상기 집적 회로의 에이징을 감지하는 단계는 복수의 에이징 센서들을 측정하는 단계를 포함하고,

상기 에이징으로 인한 센서 오실레이팅 주파수의 퍼센티지 변화는 상기 복수의 에이징 센서들의 측정들에서의 체계적인 랜덤 변동을 나타내는 에이징 에러 분포를 포함하는,

집적 회로를 디-에이징하기 위한 방법.

### 청구항 15

제 11 항에 있어서,

상기 감지된 에이징에 기초하여 계수 테이블을 업데이트하는 단계는,

공급 전압과 성능 센서 측정 간의 관계를 이용하여 상기 계수 테이블의 값에 상기 에이징 가드 대역을 맵핑하는 단계

를 더 포함하는,

집적 회로를 디-에이징하기 위한 방법.

### 청구항 16

제 11 항에 있어서,

상기 집적 회로의 에이징을 주기적으로 감지하는 단계;

주기적으로 감지된 에이징에 기초하여 상기 계수 테이블을 추가로 업데이트하는 단계; 및

추가로 업데이트된 계수 테이블을 이용하여 동적 전압 및 주파수 스케일링을 지속하는 단계

를 더 포함하는,

집적 회로를 디-에이징하기 위한 방법.

### 청구항 17

제 11 항에 있어서,

상기 안전 전압 및 주파수는 최악의-경우의 에이징에 대해 상기 집적 회로의 신뢰 가능한 동작을 허용하는,

집적 회로를 디-에이징하기 위한 방법.

### 청구항 18

집적 회로로서,

상기 집적 회로에서 회로의 에이징을 감지하도록 구성된 에이징 센서 – 상기 에이징 센서는 에이징된 및 언-에이징 컨디션 둘 다의 회로 속도들을 측정하도록 동일한 회로를 이용함 – ; 및

상기 집적 회로에서 이용되는 공급 전압을 제어하도록 구성된 코어 전력 감소 제어기 모듈

을 포함하고,

상기 공급 전압은 복수의 동작 주파수에 대한 타겟 성능 센서 측정 값들을 포함하는 계수 테이블의 값들에 기초하여 제어되고,

상기 코어 전력 감소 제어기 모듈은, 추가로,

에이징 가드 밴드를 결정하기 위해 센서 에이징과 동작 회로의 에이징 간의 관계를 나타내는 에이징 스케일링 비 및 상기 동작 회로의 최대 동작 주파수와 전압 간의 관계를 나타내는 전압 대 주파수 스케일링 팩터로 감지된 에이징을 곱함으로써 상기 감지된 에이징에 기초하여 상기 계수 테이블을 업데이트하도록 구성되는,

집적 회로.

### 청구항 19

제 18 항에 있어서,

상기 에이징 센서는,

제 1 입력 및 제 1 출력을 갖는 제 1 지연 체인;

제 2 입력 및 제 2 출력을 갖는 제 2 지연 체인; 및

상기 제 1 및 제 2 지연 체인들의 회로가 에이징하는 에이징 상태, 에이징된 회로의 지연들에 기초한 주파수로 오실레이팅하는 클록 출력을 생성하도록 상기 제 1 지연 체인이 상기 제 2 지연 체인에 커플링되는 에이징된 오실레이팅 상태, 또는 비-에이징된 회로의 지연들에 기초한 주파수로 오실레이팅하는 클록 출력을 생성하도록 상기 제 1 지연 체인이 상기 제 2 지연 체인에 커플링되는 비-에이징된 오실레이팅 상태로 상기 제 1 지연 체인 및 상기 제 2 지연 체인을 배치하도록 구성된 제어 모듈

을 포함하는,

집적 회로.

## 청구항 20

제 19 항에 있어서,

상기 에이징 상태는 동작 전압을 상기 제 1 지연 체인 및 상기 제 2 지연 체인에 공급하고, 상기 제 1 입력에 제 1 로직 값 및 상기 제 2 입력에 제 2 로직 값을 공급하는 것을 포함하고, 상기 제 1 로직 값은 상기 제 2 로직 값의 보수이며,

상기 에이징된 오실레이팅 상태에서 상기 클록 출력의 오실레이션들의 기간은, 에이징에 의해 느려지는 제 1 지연 체인을 통한 천이에 대한 지연 및 에이징에 의해 느려지는 제 2 지연 체인을 통한 천이에 대한 지연의 결합을 포함하고,

상기 비-에이징된 오실레이팅 상태에서 상기 클록 출력의 오실레이션들의 기간은, 에이징에 의해 느려지지 않은 제 1 지연 체인을 통한 천이에 대한 지연 및 에이징에 의해 느려지지 않는 제 2 지연 체인을 통한 천이에 대한 지연의 결합을 포함하는,

집적 회로.

## 청구항 21

제 18 항에 있어서,

상기 코어 전력 감소 제어기 모듈은, 추가로

안전 전압 및 주파수로 상기 집적 회로의 동작을 초기화하도록;

상기 계수 테이블의 초기 값을 이용하여 상기 집적 회로의 동적 전압 및 주파수 스케일링을 인에이블하도록;

상기 에이징 센서를 이용하여 상기 집적 회로의 에이징을 감지하도록; 그리고

업데이트된 계수 테이블을 이용하여 동적 전압 및 주파수 스케일링을 지속하도록

구성되는,

집적 회로.

## 청구항 22

제 18 항에 있어서,

상기 감지된 에이징에 기초하여 계수 테이블을 업데이트하는 것은 에이징으로 인한 센서 오실레이팅 주파수의 퍼센티지 변화로서 표현되는 감지된 에이징을 이용하고, 상기 집적 회로의 에이징을 감지하는 것은 복수의 에이징 센서들을 측정하는 것을 포함하고, 상기 에이징으로 인한 센서 오실레이팅 주파수의 퍼센티지 변화는 상기 복수의 에이징 센서들의 측정들에서의 체계적인 랜덤 변동을 나타내는 에이징 에러 분포를 포함하는,

집적 회로.

### 청구항 23

집적 회로로서,

상기 집적 회로 내의 회로의 에이징을 감지하기 위한 수단 – 상기 감지하기 위한 수단은,

제 1 입력 및 제 1 출력을 갖는 제 1 지연 체인,

제 2 입력 및 제 2 출력을 갖는 제 2 지연 체인, 및

상기 제 1 및 제 2 지연 체인들의 회로가 에이징하는 에이징 상태, 에이징된 회로의 지연들에 기초한 주파수로 오실레이팅하는 클록 출력을 생성하도록 상기 제 1 지연 체인이 상기 제 2 지연 체인에 커플링되는 에이징된 오실레이팅 상태, 또는 비-에이징된 회로의 지연들에 기초한 주파수로 오실레이팅하는 클록 출력을 생성하도록 상기 제 1 지연 체인이 상기 제 2 지연 체인에 커플링되는 비-에이징된 오실레이팅 상태로 상기 제 1 지연 체인 및 상기 제 2 지연 체인을 배치하도록 구성된 제어 모듈을 포함함 – ; 및

상기 집적 회로에서 이용되는 공급 전압을 제어하도록 구성되는 집적 회로를 디-에이징하기 위한 수단을 포함하고,

상기 공급 전압은 상기 집적 회로에 의해 감지되는 에이징에 적어도 부분적으로 기초하는,

집적 회로.

### 청구항 24

제 23 항에 있어서,

상기 에이징 상태는 동작 전압을 상기 제 1 지연 체인 및 상기 제 2 지연 체인에 공급하고, 상기 제 1 입력에 제 1 로직 값 및 상기 제 2 입력에 제 2 로직 값을 공급하는 것을 포함하고, 상기 제 1 로직 값은 상기 제 2 로직 값의 보수이며,

상기 에이징된 오실레이팅 상태에서 상기 클록 출력의 오실레이션들의 기간은, 에이징에 의해 느려지는 제 1 지연 체인을 통한 천이에 대한 지연 및 에이징에 의해 느려지는 제 2 지연 체인을 통한 천이에 대한 지연의 결합을 포함하고,

상기 비-에이징된 오실레이팅 상태에서 상기 클록 출력의 오실레이션들의 기간은, 에이징에 의해 느려지지 않은 제 1 지연 체인을 통한 천이에 대한 지연 및 에이징에 의해 느려지지 않는 제 2 지연 체인을 통한 천이에 대한 지연의 결합을 포함하는,

집적 회로.

### 청구항 25

제 23 항에 있어서,

상기 디-에이징하기 위한 수단은, 추가로,

안전 전압 및 주파수로 상기 집적 회로의 동작을 초기화하도록;

복수의 동작 주파수들에 대한 타겟 성능 센서 측정 값을 포함하는 계수 테이블의 초기 값을 이용하여 상기 집적 회로의 동적 전압 및 주파수 스케일링을 인에이블하도록;

상기 에이징하기 위한 수단을 이용하여 상기 집적 회로의 에이징을 감지하도록;

감지된 에이징에 기초하여 상기 계수 테이블을 업데이트하도록; 그리고

업데이트된 계수 테이블을 이용하여 동적 전압 및 주파수 스케일링을 지속하도록 구성되는,

집적 회로.

## 청구항 26

제 25 항에 있어서,

상기 디-에이징하기 위한 수단은,

에이징 가드 밴드를 결정하기 위해 센서 에이징과 동작 회로의 에이징 간의 관계를 나타내는 에이징 스케일링 비 및 상기 동작 회로의 최대 동작 주파수와 전압 간의 관계를 나타내는 전압 대 주파수 스케일링 팩터로 감지된 에이징을 곱하는 것을 포함함으로써 상기 감지된 에이징에 기초하여 상기 계수 테이블을 업데이트하도록 구성되는,

집적 회로.

## 청구항 27

제 26 항에 있어서,

상기 감지된 에이징에 기초하여 상기 계수 테이블을 업데이트하는 것은 에이징으로 인한 센서 오실레이팅 주파수의 퍼센티지 변화로서 표현되는 감지된 에이징을 이용하고, 상기 집적 회로의 에이징을 감지하는 것은 복수의 에이징 센서들을 측정하는 것을 포함하고, 상기 에이징으로 인한 센서 오실레이팅 주파수의 퍼센티지 변화는 상기 복수의 에이징 센서들의 측정들에서의 체계적인 랜덤 변동을 나타내는 에이징 에러 분포를 포함하는,

집적 회로.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 집적 회로들에 관한 것으로서, 보다 구체적으로는, 집적 회로 성능을 동적으로 디-에이징하기 위한 시스템들 및 방법들에 관한 것이다.

### 배경 기술

[0002] 집적 회로들은 점점 복잡해지고 있다. 성능과 전력 간의 트레이드-오프들을 개선하기 위해, 집적 회로는 상이한 시간들에 상이한 주파수들 및 상이한 전압들에서 동작할 수 있다. 예를 들어, 집적 회로는 고-성능 모드 및 저-전력 모드를 포함하는 다양한 주파수-전압 모드들에서 동작할 수 있다. 고-성능 모드는 높은 클록 주파수 및 높은 공급 전압을 이용하고, 그에 따라 높은 성능을 제공하지만 높은 전력 소비를 또한 갖는다. 저-전력 모드는 낮은 클록 주파수 및 낮은 공급 전압을 이용하고 그에 따라 낮은 전력 소비를 제공하지만 낮은 성능을 또한 갖는다. 부가적으로, 집적 회로 내의 다양한 블록들은 상이한 주파수들 및 상이한 전압들에서 동작할 수 있다.

[0003] 주어진 클록 주파수를 제공하는 특정 공급 전압은 다양한 컨디션에 기초하여 변동될 수 있다. 예를 들어, 제조 변동들은 전압 및 주파수 간의 상이한 관계들을 갖는 동일한 설계에 따라 생성되는 상이한 집적 회로를 초래할 수 있다. 부가적으로, 집적 회로 내의 회로 특성들의 변동들은 전압 및 주파수 간에 상이한 관계들을 갖는 집적 회로의 상이한 섹션들을 초래할 수 있다. 온도들은 또한 전압과 주파수 간의 관계에 영향을 준다. 또한, 집적 회로의 다양한 모듈들의 동작들에 의존하여 변동될 수 있는 공급 전압들의 강하들이 있을 수 있다. AVS(adaptive voltage scaling)는 집적 회로의 감지된 성능 측정에 기초하여 공급 전압을 제어하는데 이 용될 수 있다.

[0004] 특히 나노미터 기술들에서 디바이스 에이징(device aging)은 집적 회로의 전기 파라미터들의 변화들을 초래한다. 예를 들어, 트랜지스터 임계 전압들은 PBTI(positive bias temperature instability) 및 NBTI(negative bias temperature instability)와 같은 효과들에 의해 증가될 수 있다. 회로들은 일반적으로 에이징에 따라 더 느리게 동작한다. 이는 추가로 공급 전압과 클록 주파수 간의 관계에 영향을 준다. 에이징의 레이트 및 양은 집적 회로의 이용에 따라 변동될 수 있다. 예를 들어, 모바일 전화는 전화가 하루 대부분 동안 대기상태에 있는 사용자에 비해, 사용자가 하루 종일 텍스트보내기, 전화 통화들, 스트리밍 비디오, 및 게임 플레이와 같은 다수의 작업들을 위해 전화를 이용할 때 보다 더 에이징될 수 있다.

[0005] 종래의 에이징 보상 방식들은 디바이스 상의 에이징의 효과를 선형적으로 추정한다. 그러면, 최악의-경우의 시나리오에 기초하여, 디바이스 에이징의 효과들은, 에이징의 전체 효과가 디바이스의 예상된 동작 수명의 말미 근처에서 자신들을 드러내는 경우 디바이스가 그의 설계 요건을 충족하도록 큰 가드 밴드(guard band)를 포함함으로써 참작된다. 이는 보수적 설계를 초래하고 상당한 성능 손실들을 초래할 수 있다.

### 발명의 내용

[0006] 일 양상에서, 집적 회로의 에이징을 감지하기 위한 회로가 제공된다. 회로는, 제 1 입력 및 제 1 출력을 갖는 제 1 지연 체인; 제 2 입력 및 제 2 출력을 갖는 제 2 지연 체인; 및 에이징 상태, 에이징된 오실레이팅 상태, 또는 비-에이징된 오실레이팅 상태로 제 1 지연 체인 및 제 2 지연 체인을 배치하도록 구성된 제어 모듈을 포함한다.

[0007] 일 양상에서, 집적 회로를 디-에이징하기 위한 방법이 제공된다. 방법은, 안전 전압 및 주파수로 집적 회로의 동작을 초기화하는 단계; 복수의 동작 주파수들에 대한 타겟 성능 센서 측정 값들을 포함하는 계수 테이블의 초기 값들을 이용하여 집적 회로의 동적 전압 및 주파수 스케일링을 인에이블하는 단계; 집적 회로의 에이징을 감지하는 단계; 감지된 에이징에 기초하여 계수 테이블을 업데이트하는 단계; 및 업데이트된 계수 테이블을 이용하여 동적 전압 및 주파수 스케일링을 지속하는 단계를 포함한다.

[0008] 일 양상에서, 집적 회로가 제공되며, 이 직적 회로는 집적 회로 내의 회로의 에이징을 감지하도록 구성된 에이징 센서 — 에이징 센서는 에이징 및 언-에이징 컨디션들을 다에서 회로 속도들을 측정하기 위해 동일한 회로를 이용함- ; 및, 집적 회로에서 이용되는 공급 전압을 제어하도록 구성된 코어 전력 감소 제어기 모듈을 포함하고, 공급 전압은 에이징 센서에 의해 감지되는 에이징에 적어도 부분적으로 기초한다.

[0009] 일 양상에서, 집적 회로가 제공되며, 이 집적 회로는, 에이징된 및 비-에이징 컨디션들을 다에서 회로 속도를 측정하도록 동일한 회로를 이용하는, 집적 회로 내의 회로의 에이징을 감지하기 위한 수단; 및 집적 회로에서 이용되는 공급 전압을 제어하도록 구성되는, 집적 회로를 디-에이징하기 위한 수단을 포함하고, 공급 전압은 상기 집적 회로에 의해 감지되는 에이징에 적어도 부분적으로 기초한다.

[0010] 본 발명의 다른 특징들 및 이점들은 예로서 본 발명의 양상들을 예시하는 다음의 설명으로부터 자명해져야 한다.

### 도면의 간단한 설명

[0011] 그 구조 및 동작 둘 다에 관한 본 발명의 세부사항들은 유사한 참조 번호들이 유사한 부분들을 지칭하는 첨부 도면들을 부분적으로 연구함으로써 명확해질 수 있다.

[0012] 도 1은 현재 개시된 실시예에 따라 동적 디-에이징을 갖는 전자 시스템의 기능 블록도이다.

[0013] 도 2는 현재 개시된 실시예에 따라 동적 디-에이징을 갖는 집적 회로의 레이아웃을 예시하는 도면이다.

[0014] 도 3은 현재 개시된 실시예에 따른 성능 센서의 기능 블록도이다.

[0015] 도 4는 현재 개시된 실시예에 따른 에이징 센서의 개략도이다.

[0016] 도 5는 현재 개시된 실시예에 따른 지연 엘리먼트의 개략도이다.

[0017] 도 6은 현재 개시된 실시예에 따른 에이징 센서 제어 모듈의 개략도이다.

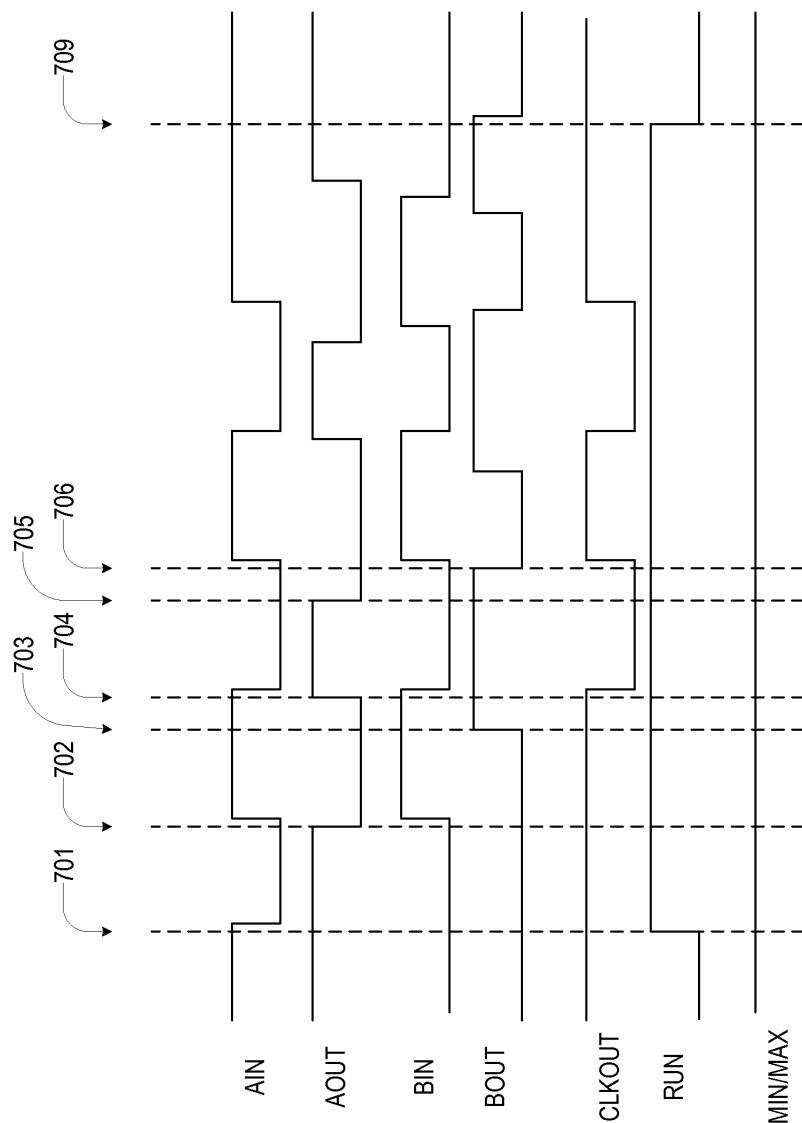

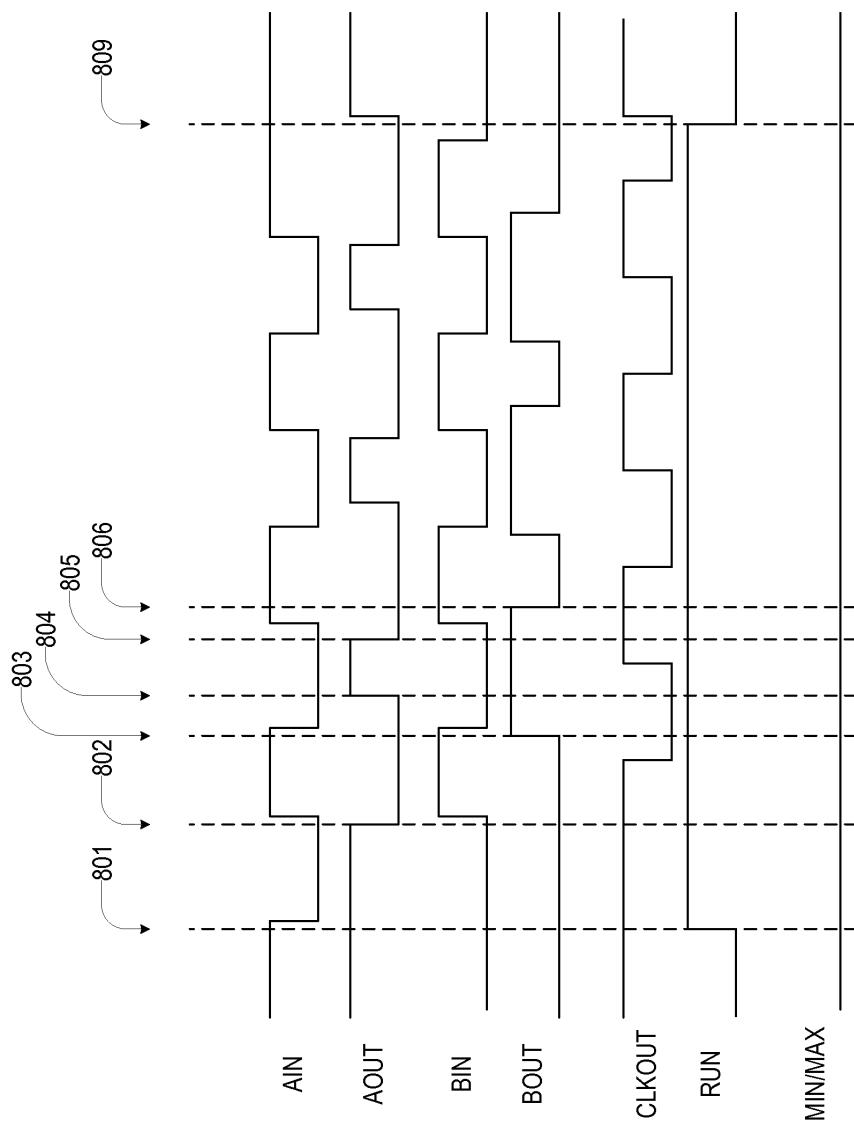

[0018] 도 7 및 도 8은 도 4의 에이징 센서의 동작을 예시하는 파형도들이다.

[0019] 도 9는 현재 개시된 실시예에 따른 동적 디-에이징에 대한 프로세스의 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0012] [0020] 첨부 도면들과 관련하여 아래에서 기술되는 상세한 설명은 다양한 구성들의 설명으로서 의도되며 여기서 설명되는 개념들이 실시될 수 있는 유일한 구성들만을 나타내도록 의도되는 것은 아니다. 상세한 설명은 다양한 개념들의 완전한 이해를 제공하기 위해서 특정 세부사항들을 포함한다. 그러나 이들 개념들은 이들 특정 상세들 없이 실시될 수 있음이 당업자에게 명백할 것이다. 일부 경우들에서, 잘 알려진 구조들 및 컴포넌트들은 그러한 개념들을 모호하게 하는 것을 방지하기 위해 단순화된 형태로 도시된다.

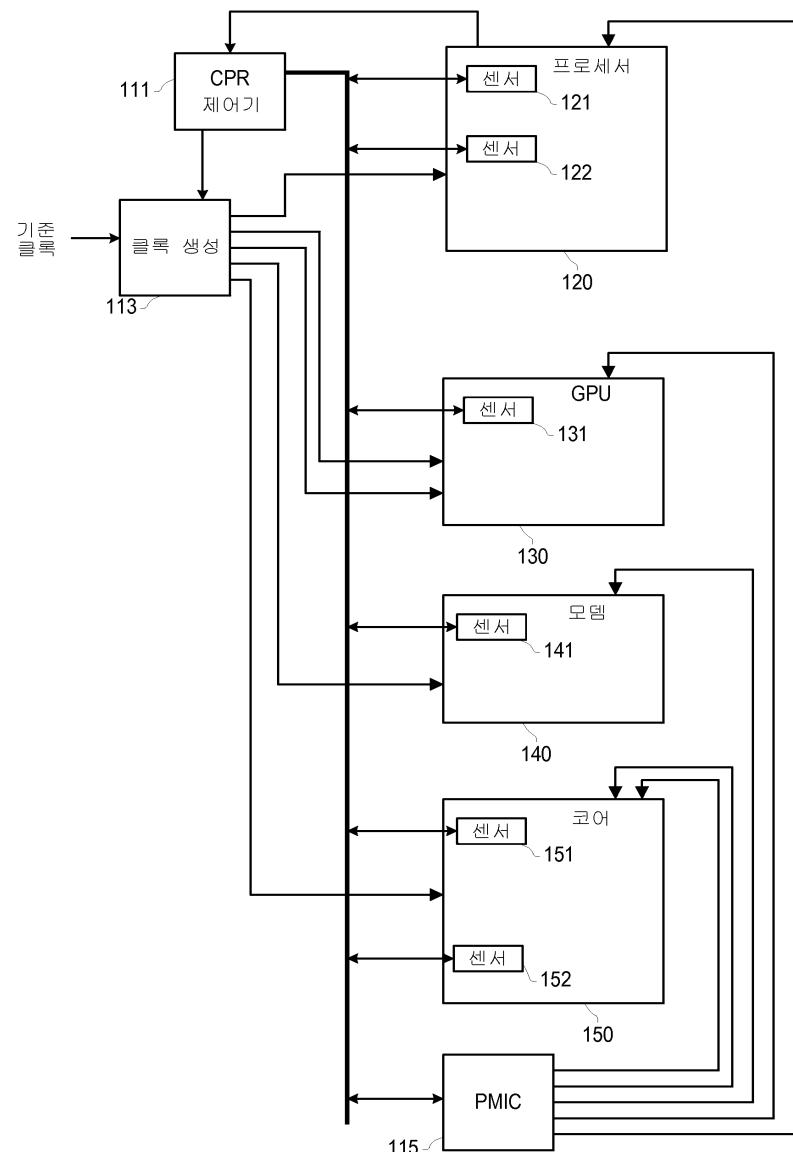

- [0013] [0021] 도 1은 현재 개시된 실시예에 따라 동적 디-에이징을 갖는 전자 시스템의 기능 블록도이다. 시스템은 하나 또는 다수의 집적 회로들을 이용하여 구현될 수 있다. 시스템은 예를 들어, 모바일 전화에서 이용될 수 있다.

- [0014] [0022] 시스템은 시스템에 대한 동작 기능들을 수행하는 다양한 모듈들을 포함한다. 동작이란 용어는 전자 시스템의 주 유틸리티를 제공하도록 고려될 수 있는 기능들을, 보조적인 것으로 고려될 수 있는 그러한 기능들로부터 구분하는데 이용된다. 도 1에서 예시된 예시적인 시스템은 프로세서 모듈(120), 그래픽 프로세싱 유닛(GPU)(130), 모뎀 모듈(140) 및 코어 모듈(150)을 포함한다. 프로세서 모듈(120)은 일반적인 프로그래밍 가능 기능들을 제공할 수 있고; 그래픽 프로세싱 유닛(130)은 그래픽 기능들을 제공할 수 있고; 모뎀 모듈(140)은 통신 기능들, 예를 들어, LTE(long term evolution) 또는 CDMA(code division multiple access) 프로토콜들에 따라 무선 통신들을 제공할 수 있고; 코어 모듈(150)은 다른 모듈들에 의해 제공되지 않는 다양한 기능들을 제공할 수 있다.

- [0015] [0023] 클록 생성 모듈(113)은 기준 클록 입력을 수신하고 하나 또는 그 초과의 클록 신호들을 다른 모듈들에 제공한다. 클록 생성 모듈(113)은 다양한 주파수들의 클록 신호들을 공급하기 위해 분할기들 및 위상 로킹 루프들을 포함할 수 있다. 클록 생성 모듈(113)은 CPR(core power reduction) 제어기 모듈(111)에 의해 제어되는 주파수로 다른 모듈들에 클록들을 공급한다. 클록 생성 모듈(113)의 기능들 중 전부 또는 부분들은 클록 신호들을 이용하는 다양한 모듈들에 로케이팅될 수 있다.

- [0016] [0024] PMIC(power management integrated circuit)(115)는 하나 또는 그 초과의 전압들을 시스템의 다른 모듈들에 공급한다. PMIC(115)는 스위칭 전압 레귤레이터들 및 로우-드롭아웃(low-dropout) 레귤레이터들을 포함할 수 있다. PMIC(115)는 별개의 집적 회로일 수 있다. PMIC(115)에 의해 공급되는 전압들은 또한 코어 전력 감소 제어기 모듈(111)에 의해 제어된다. 시스템들의 모듈들은 하나의 전압 공급기 또는 다수의 전압 공급기들을 가질 수 있고, 다수의 모듈들이 공통 전압 공급기로 동작할 수 있다.

- [0017] [0025] 프로세서 모듈(120), 그래픽 프로세싱 유닛(130), 모뎀 모듈(140) 및 코어 모듈(150)은 성능 센서들을 포함한다. 도 1의 예시적인 시스템에서, 프로세서 모듈(120)은 2개의 성능 센서들(121, 122)을 포함하고; 그래픽 프로세싱 유닛(130)은 성능 센서(131)를 포함하고; 모뎀 모듈(140)은 성능 센서(141)를 포함하고; 코어 모듈(150)은 2개의 성능 센서들(151, 152)을 포함한다. 성능 센서들 각각은 회로 속도를 측정하기 위한 회로를 포함한다. 예를 들어, 성능 센서들은 링 오실레이터들의 오실레이션들을 카운트할 수 있다. 각각의 성능 센서는 또한 에이징 센서를 포함한다. 에이징 센서는 회로 성능에 관한 에이징의 효과를 측정한다. 성능 센서들은 센서에서 회로의 성능 특성들을 측정한다. 집적 회로에서 회로의 성능은 위치, 온도, 전압 강하 및 다른 파라미터들에 따라 변동될 수 있지만, 성능 센서에 의해 측정된 성능은 성능 센서 근처의 유사한 회로의 성능을 추정하는데 이용될 수 있다. 에이징 센서는 일 실시예에서, 에이징 및 언-에이징 컨디션들 둘 다에서 회로 속도들을 측정하기 위해 동일한 회로를 이용한다.

- [0018] [0026] 코어 전력 감소 제어기 회로(111)는 시스템의 모듈들에 의해 이용되는 클록 주파수들 및 공급 전압들을 제어한다. 코어 전력 감소 제어기 모듈(111)은 예를 들어, 프로세서 모듈(120)에 의해 선택된 동작 모드에 기초하여 주파수들 및 전압들을 제어할 수 있다. 일 실시예에서, 프로세서는 동작 주파수들을 선택하고, 코어 전력 감소 제어기 모듈(111)은 공급 전압을 결정한다. 코어 전력 감소 제어기 모듈(111)은 대응하는 모듈들의 성능 센서들로부터의 성능 측정들에 기초하여 그리고 에이징 센서들로부터의 에이징에 기초하여 공급 전압을 결정할 수 있다. 코어 전력 감소 제어기 모듈(111)은, 공급 전압이 선택된 동작 주파수에 대해 필요한 최소 전압과 동일하거나 또는 단지 약간만(예를 들어, 10mV) 초과하도록 공급 전압을 결정할 수 있다. 다른 실시예들에서, 코어 전력 감소 제어기 모듈(111)은 단지 클록 주파수들만을 제어할 수 있다. 시스템은 대안적으로 또는 부가적으로, 성능에 영향을 주는 기관 전압과 같은 다른 파라미터들을 제어할 수 있다. 코어 전력 감소 제어기 모

들(111)의 예시적인 기능들은 도 9에서 예시된 프로세스를 참조하여 추가로 설명될 것이다.

- [0019] [0027] 동적 디-에이징을 포함하지 않는 종래의 시스템들은 가드 밴드량(guard band amount) 만큼 요구되는 최소 전압을 실질적으로 초과하는 값으로 공급 전압을 세팅한다. 가드 밴드량(예를 들어, 100mV)은 다른 것들 중에서도, (임의의 주어진 시간에 크기가 알려지지 않는) 에이징의 효과를 보상하는데 이용된다. 종래의 시스템들에서, 에이징을 위한 가드 밴딩의 양은 고정되고, 심지어 어떠한 에이징도 발생하지 않을 때 시스템의 동작의 시작시에 적용된다. 가드 밴딩은 또한 클록 주파수와 같은 다른 파라미터들과 함께 이용될 수 있다. 본원에서 설명되는 디-에이징 시스템들 및 방법들은 가드 밴딩을 위한 성능 손실을 제거 또는 감소시킬 수 있다.

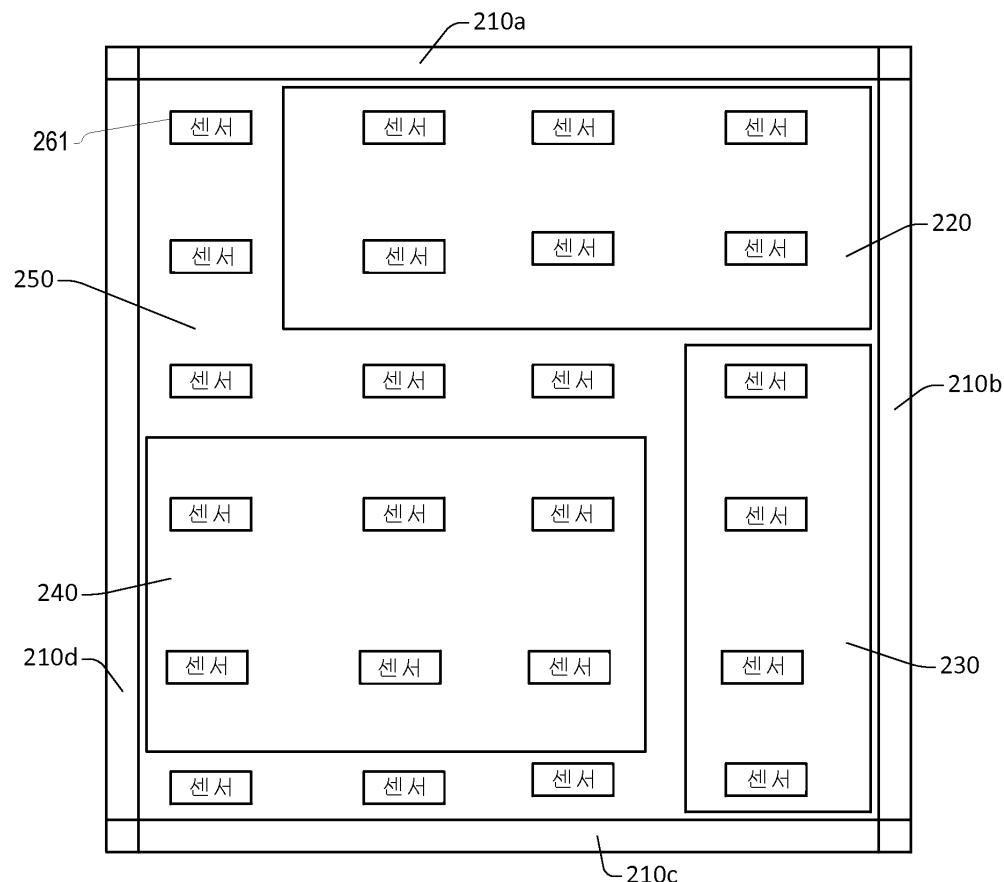

- [0020] [0028] 도 2는 현재 개시된 실시예에 따라 동적 디-에이징을 갖는 집적 회로의 레이아웃을 예시하는 도면이다. 집적 회로는 도 1의 전자 시스템을 구현하는데 이용될 수 있다. 집적 회로는 예를 들어, CMOS(complementary metal-oxide-semiconductor) 프로세스를 이용하여 제조될 수 있다.

- [0021] [0029] 도 2의 집적 회로는 집적 회로의 에지들을 따라 로케이팅되는 4개의 주변 블록들(210)(210a, 210b, 210c, 및 210d)을 포함한다. 집적 회로는, 집적 회로 내부의 대형 블록들인 프로세서 모듈(220), 그래픽 프로세서 모듈(230) 및 모뎀 모듈(240)을 포함한다. 도 1의 시스템의 코어 모듈(150)에 의해 제공된 것들과 같은 집적 회로의 다른 기능들은 집적 회로의 잔여 영역들(250)에 걸쳐 퍼져 있을 수 있다. 도 1의 코어 전력 감소 제어기 모듈(111)은 또한 집적 회로의 잔여 영역들(250)에서 구현될 수 있다.

- [0022] [0030] 집적 회로는 또한 집적 회로 영역에 걸쳐 이격되는 성능 센서들(261)을 포함한다. 도 2가 20개의 성능 센서들을 예시하지만, 집적 회로 구현은 수백 개의 성능 센서들을 포함할 수 있다. 성능 센서들은 예를 들어, 코어 전력 감소 제어기 모듈(111)에 직렬로 연결될 수 있거나, 또는 버스에 의해 연결될 수 있다.

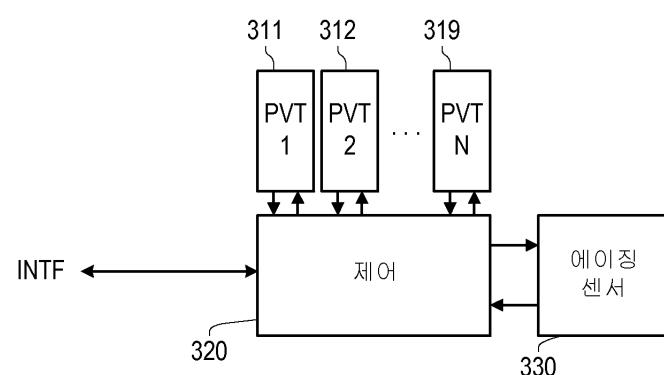

- [0023] [0031] 도 3은 현재 개시된 실시예에 따른 성능 센서의 기능 블록도이다. 성능 센서는 도 1의 성능 센서들(121, 122, 131, 141, 151, 152) 및 도 2의 성능 센서들(261)을 구현하는데 이용될 수 있다.

- [0024] [0032] 도 3의 성능 센서는 다수의 PVT 센서들(311-319)을 포함한다. PVT 센서들(311-319) 각각은 예를 들어, 주파수가 회로 성능을 나타내는 출력을 생성하도록 링 오실레이터를 동작시킴으로써 회로 성능을 측정한다. PVT 센서들(311-319)의 상이한 센서들은 상이한 타입들의 회로들, 예를 들어, 상이한 타입의 트랜지스터들을 갖는 회로들의 성능을 측정할 수 있다. PVT란 명칭은 회로 성능에 주로 영향을 주는 프로세스, 전압 및 온도를 지칭한다.

- [0025] [0033] 성능 센서는 에이징 센서(330)를 포함한다. 에이징 센서(330)는 회로 에이징의 효과를 측정할 수 있다. 에이징 센서(330)는 에이징 상태, 에이징된 오실레이팅 상태, 또는 비-에이징된 오실레이팅 상태에 있게 되도록 (예를 들어, 코어 전력 감소 제어기 모듈(111)에 의해) 제어될 수 있는 지연 라인들을 포함한다. 예시적인 실시예에서, 에이징 상태에서, 지연 라인들은 정적 가동 상태(static powered state)로 유지된다. 지연 라인들은 에이징이 에이징 센서에 의해 감지되는 회로에 의해 이용되는 동일한 공급 전압으로 가동된다. 에이징된 오실레이팅 상태에서, 지연 라인들은 에이징된 회로의 지연들에 기초한 주파수에서 오실레이팅하는 클록 출력을 생성하도록 커플링된다. 비-에이징된 오실레이팅 상태에서, 지연 라인들은 비-에이징된 회로의 지연들에 기초한 주파수에서 오실레이팅하는 클록 출력을 생성하도록 커플링된다. 동일한 트랜지스터들이 에이징된 오실레이팅 상태 및 비-에이징된 오실레이팅 상태 둘 다에서 이용된다.

- [0026] [0034] 성능 센서는 제어 모듈(320)을 포함한다. 제어 모듈(320)은 감지된 성능 측정들을 통신하기 위해 다른 모듈들, 예를 들어, 코어 전력 감소 제어기 모듈(111)에 대한 인터페이스를 제공한다. 제어 모듈(320)은 또한 PVT 센서들(311-319) 및 에이징 센서(330)의 오실레이션들을 카운팅하기 위한 카운터를 포함할 수 있다. 카운터들은 PVT 센서들(311-319) 또는 에이징 센서(330)에서 오실레이터들의 주파수들을 측정하기 위해 알려진 시간 인터벌 동안 카운팅할 수 있다. 제어 모듈(320)은 PVT 센서들(311-319)이 측정들을 수행하지 않을 때 PVT 센서들(311-319)에 대한 전압 공급이 제거되게 할 수 있다. 그러나 에이징 센서(330)는 에이징 상태 동안 가동된 채로 유지될 수 있다.

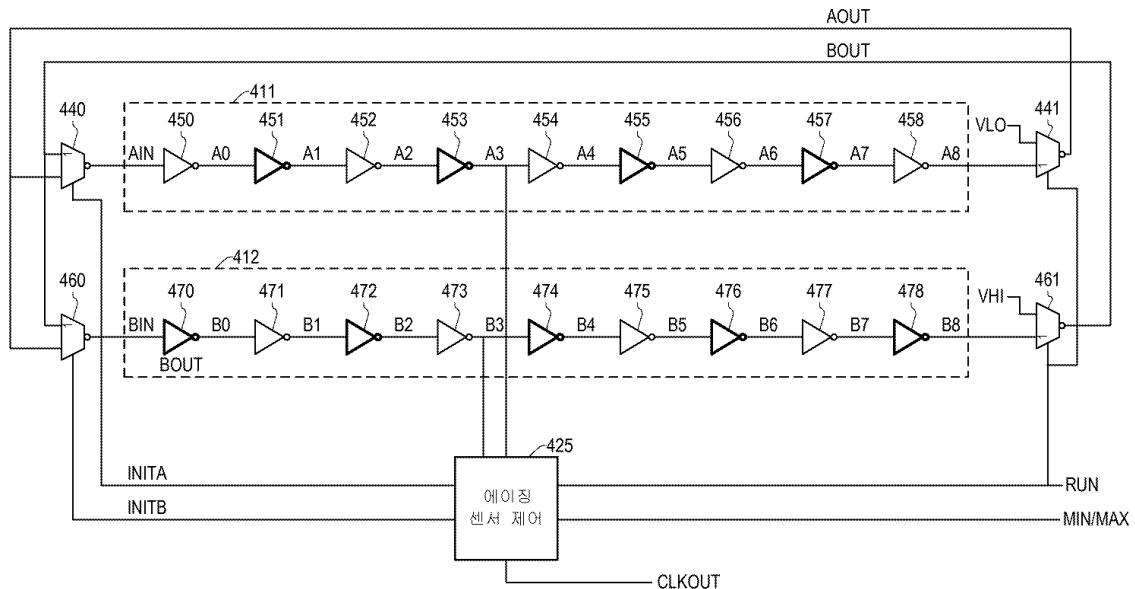

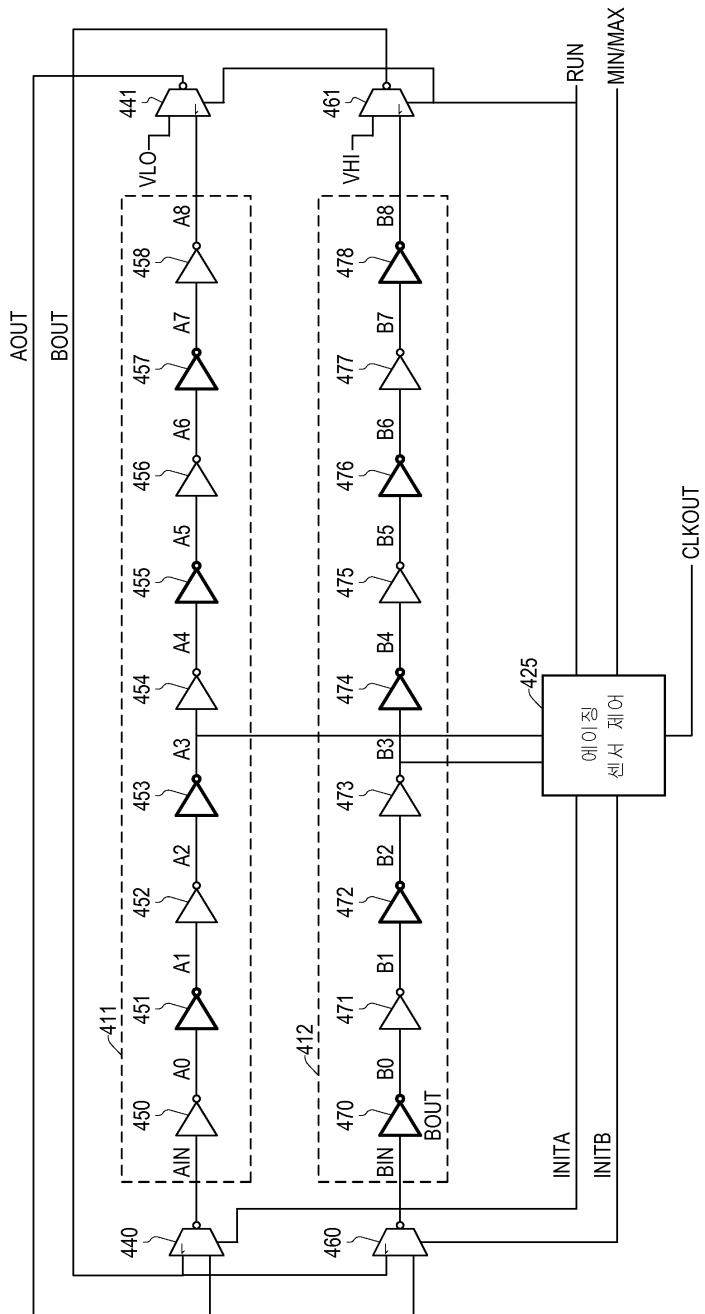

- [0027] [0035] 도 4는 현재 개시된 실시예에 따른 에이징 센서의 개략도이다. 에이징 센서는 도 1의 시스템 및 도 2의 집적 회로에서 이용될 수 있는 도 3의 에이징 센서(330)를 구현할 수 있다.

- [0028] [0036] 도 4의 에이징 센서는 제 1 지연 체인(411) 및 제 2 지연 체인(412)을 포함한다. 제 1 지연 체인(411)은 제 1 입력(AIN)을 수신하고 제 1 출력(A8)을 생성한다. 제 2 지연 체인(412)은 제 2 입력(BIN)을 수신하고 제 2 출력(B8)을 생성한다. 각각의 지연 체인은 지연 엘리먼트들(제 1 지연 체인(411)의 지연 엘리먼트들(450-458) 및 제 2 지연 체인(412)의 지연 엘리먼트들(470-478))의 체인을 포함한다. 예시된 실시예에서, 각각

의 지연 체인은 9개의 지연 엘리먼트들을 포함하고, 지연 엘리먼트들은 인버터들이다.

[0029] [0037] 에이징 센서는 에이징 센서의 기능들을 제어하는 에이징 센서 제어 모듈(425)을 포함한다. 에이징 센서 제어 모듈(425)은 또한 에이징된 회로들 및 비-에이징된 회로들 둘 다의 성능을 나타낼 수 있는 클록 출력(CLKOUT)을 생성한다. 에이징 센서 제어 모듈(425)은 실행(run) 제어 입력(RUN)을 수신한다. 실행 제어 입력이 로우(low)일 때, 에이징 센서는 실행하지 않고(에이징 상태), 지연 체인들(지연 라인들로서 또한 지칭됨)은 지연 엘리먼트들을 에이징하도록 특정 상태로 유지된다. 실행 제어 입력이 하이(high)일 때, 지연 체인들은, 주파수가 에이징에 의해 느려지는(에이징된 오실레이팅 상태) 킹 오실레이터를 형성하도록 커플링되거나, 또는 주파수가 에이징에 의해 느려지지 않는(비-에이징된 오실레이팅 상태) 킹 오실레이터를 형성하도록 커플링된다. 에이징된 오실레이팅 상태 또는 비-에이징된 오실레이팅 상태의 선택은 MIN/MAX 제어 입력에 의해 제어된다.

[0030] [0038] 도 4에서 예시된 실시예에서, 4개의 멀티플렉서들은 지연 체인들을 에이징 상태, 에이징된 오실레이팅 상태 또는 비-에이징된 오실레이팅 상태로 배치하도록 이용된다. 도 4의 에이징 센서에서, 멀티플렉서들은 입력으로부터 출력으로 인버팅한다. 다른 실시예들은 비-인버팅 멀티플렉서들을 이용할 수 있다.

[0031] [0039] 멀티플렉서(441)는 (실행 상태에 있을 때) 제 1 지연 체인의 출력(A8)과 (실행 상태에 있지 않을 때) 정적 로우 전압 중에 선택한다. 멀티플렉서(461)는 (실행 상태에 있을 때) 제 2 지연 체인의 출력(B8)과 (실행 상태에 있지 않을 때) 정적 하이 전압 중에 선택한다.

[0032] [0040] 멀티플렉서(440)는 제 1 지연 체인(411)의 입력(AIN)에 공급하도록 멀티플렉서(441)의 출력(AOUT)과 멀티플렉서(461)의 출력(BOUT) 중에 선택한다. 멀티플렉서(460)는 제 2 지연 체인(412)의 입력(BIN)에 공급하도록 멀티플렉서(441)의 출력(AOUT)과 멀티플렉서(461)의 출력(BOUT) 중에 선택한다. 멀티플렉서(440)에 의해 수행되는 선택은 에이징 센서 제어 모듈(425)에 의해 공급되는 제 1 제어 신호(INITA)에 의해 제어되고, 멀티플렉서(460)에 의해 수행되는 선택은 에이징 센서 제어 모듈(425)에 의해 공급되는 제 2 제어 신호(INITB)에 의해 제어된다.

[0033] [0041] 에이징 상태에서, 제 1 지연 체인(411)의 입력은 제 1 로직 값을 갖고, 제 2 지연 체인(412)에 대한 입력은 제 1 로직 값의 보수인 제 2 로직 값을 갖는다. 도 4의 실시예에서, 제 1 로직 값은 하이이고, 제 2 로직 값은 로우이다.

[0034] [0042] 에이징 상태에서, 멀티플렉서(441)는 로우 전압 입력을 선택하고, AOUT는 하이이고, 멀티플렉서(461)는 하이 전압 입력을 선택하고, BOUT는 로우이다. 에이징 센서 제어 모듈(425)은 하이가 되는 제 1 제어 신호(INITA)를 생성한다. 따라서 멀티플렉서(440)는 (로우인) BOUT를 선택하고 멀티플렉서 출력(AIN)은 하이이다. 에이징 센서 제어 모듈(425)은 로우가 되는 제 2 제어 신호(INITB)를 생성한다. 따라서 멀티플렉서(460)는 (하이인) AOUT를 선택하고 멀티플렉서 출력(BIN)은 로우이다. 이는 제 1 지연 체인(411) 및 제 2 지연 체인(412)이 상보적 출력들을 갖는 교번적인 지연 엘리먼트들을 갖는 상보적인 상태들로 유지하게 한다. 세부적으로, 제 1 지연 체인(411)에서, 제 1 지연 엘리먼트(450)의 출력(A0)은 로우이고, 제 2 지연 엘리먼트(451)의 출력(A1)은 하이이고, 제 3 지연 엘리먼트(452)의 출력(A2)은 로우인 식으로 진행되어 제 9 지연 엘리먼트(458)의 출력(A8)인 로우가 된다. 그리고 제 2 지연 체인(412)에서, 제 1 지연 엘리먼트(470)의 출력(B0)은 하이이고, 제 2 지연 엘리먼트(471)의 출력(B1)은 로우이고, 제 3 지연 엘리먼트(472)의 출력(B2)은 하이인 식으로 진행되어 제 9 지연 엘리먼트(478)의 출력(B8)인 하이가 된다.

[0035] [0043] 지연 엘리먼트들 상의 정적인 전압들은 에이징된 상태로의 천이들이 느려지도록 지연 엘리먼트들을 에이징하는 경향이 있다. 예를 들어, 제 1 지연 엘리먼트(450)의 출력(A0)은 에이징 동안 로우이고, 출력 상의 하강 천이들은 에이징 효과들에 의해 느려질 것이다. 유사하게, 제 2 지연 엘리먼트(451)의 출력(A1)은 에이징 동안 하이이고, 출력 상의 상승 천이들은 에이징 효과들에 의해 느려질 것이다. 상승 및 하강 천이들이 지연 엘리먼트마다 교번하고 에이징에 의해 영향을 받는 천이들은 또한 지연 엘리먼트마다 교번하기 때문에, 전체 지연 체인은 지연 체인으로의 입력 상의 동일한 천이에 대한 에이징에 의해 영향을 받는다. 제 1 지연 체인(411)은 그의 입력 상의 상승 천이들에 대한 에이징에 의해 느려진다. 유사하게, 제 2 지연 체인(412)은 그의 입력 상의 하강 천이들에 대한 에이징에 의해 느려진다.

[0036] [0044] 에이징된 오실레이팅 상태에서, 에이징 센서 제어 모듈(425)은, 그의 입력 상의 상승 천이들에 대한 제 1 지연 체인(411)의 지연 및 그의 입력 상의 하강 천이들에 대한 제 2 지연 체인의 지연을 포함하는 기간에 있어서 지연 체인들이 오실레이팅하도록 제 1 및 제 2 제어 신호들을 제어한다. 에이징된 오실레이팅 상태의 동작은 도 7의 과정도에서 예시된다. 과정들의 시작에서, 실행 제어 입력(RUN)은 로우이고, 지연 체인들은 제 1

지연 체인에 대한 입력(AIN)이 하이이고 제 2 지연 체인에 대한 입력(BIN)이 로우인 에이징 상태에 있다.

[0037] [0045] 시간(701)에서, 실행 제어 입력은 하이로 스위칭하고 MIN/MAX 제어 입력은 하이 이어서, 에이징 센서는 에이징된 오실레이팅 상태에 진입하게 된다. 제 1 제어 신호(INITA)는, 멀티플렉서(440)가 스위칭하고 제 1 지연 체인(411)에 대한 입력(AIN)이 로우로 스위칭하도록 하이로 스위칭한다. 제 1 지연 체인(411)에 대한 입력 상의 하강 천이는 지연 체인을 통해 그리고 멀티플렉서(441)를 통해 AOUT로 전파되며, 이는 시간(702)에서 하강 한다. 이 시간에, 에이징 센서 제어 모듈들(425)로부터의 제 1 및 제 2 제어 신호들은, AOUT가 선택되고 양자의 지연 체인들에 대한 입력들이 상승(멀티플렉서(440) 및 멀티플렉서(460)에 의해 인버팅된 AOUT의 하강)하도록 둘 다 로우이다.

[0038] [0046] 지연 체인들로의 입력들 상의 상승 천이들은 양자의 지연 체인들을 통해 동시에 전파된다. 그의 입력 상의 상승 천이에 대한 제 1 지연 체인(411)의 지연들은 에이징에 의해 느려진다. 그의 입력 상의 상승 천이에 대한 제 2 지연 체인(412)의 지연들은 에이징에 의해 느려지지 않는다. 제 2 지연 체인(412)에 대한 입력 상의 상승은 시간(703)에서 그의 출력으로 전파되고, 제 1 지연 체인(411)에 대한 입력 상의 상승은 시간(704)에서 그의 출력으로 전파된다. 시간(704)과 시간(703) 간의 차이는 에이징의 효과이다. 도 7에서, 지연의 차이는 효과를 명확히 예시하도록 과장된다.

[0039] [0047] 시간(703) 이전에, 에이징 센서 제어 모듈(425)로부터의 제 1 및 제 2 제어 신호들은, 멀티플렉서(440) 및 멀티플렉서(460)가 (상승 입력에 대한 에이징에 의해 영향을 받는 지연 체인으로부터) AOUT를 선택하도록 세팅된다. 따라서, 양자의 지연 체인들에 대한 입력들은 시간(704) 이후 하강(멀티플렉서(440) 및 멀티플렉서(460)에 의해 인버팅되는 AOUT의 상승)한다.

[0040] [0048] 지연 체인들로의 입력들 상의 상승 천이들은 양자의 지연 체인들을 통해 동시에 전파된다. 그의 입력 상의 하강 천이에 대한 제 1 지연 체인(411)의 지연들은 에이징에 의해 느려지지 않는다. 그의 입력 상의 하강 천이에 대한 제 2 지연 체인(412)의 지연들은 에이징에 의해 느려진다. 제 1 지연 체인(411)에 대한 입력 상의 하강은 시간(705)에서 그의 출력으로 전파되고, 제 2 지연 체인(412)에 대한 입력 상의 하강은 시간(706)에서 그의 출력으로 전파된다. 시간(706)과 시간(705) 간의 차이는 에이징의 효과이다.

[0041] [0049] 시간(705) 이전에, 에이징 센서 제어 모듈(425)로부터의 제 1 및 제 2 제어 신호들은, 멀티플렉서(440) 및 멀티플렉서(460)가 (하강 입력에 대한 에이징에 의해 영향을 받는 지연 체인으로부터) BOUT를 선택하도록 세팅된다. 따라서, 양자의 지연 체인들에 대한 입력들은 상승하고 지연 체인들의 하나의 오실레이션은 완료된다. 신호 천이들의 시퀀스는 그 후 시간(702)으로부터 시작하여 설명된 바와 같이 반복된다.

[0042] [0050] 시간(709)에서, 실행 제어 입력은 로우로 스위칭하고 에이징 센서는 에이징 상태로 다시 스위칭한다. 도 7의 에이징된 오실레이팅 상태는 단지 몇 오실레이션들 동안 지속되지만, 접적 회로에서, 에이징된 오실레이팅 상태는 예를 들어, 수백 또는 수천 오실레이션들 동안 지속될 수 있다.

[0043] [0051] 에이징 센서 제어 모듈(425)은 지연 체인들의 중간지점으로부터의 신호들을 이용하여 멀티플렉서(440) 및 멀티플렉서(460)에 대한 그의 제어 신호들 상의 천이들을 시간조절(time)할 수 있다. 예를 들어, 각각의 지연 체인의 제 4 지연 엘리먼트들의 출력들(A3, B3)은 클록 출력(CLKOUT)을 생성하도록 논리적으로 NAND연산될 수 있다. 클록 출력은 그 후 제어 신호들(INITA, INITB)을 생성하는데 이용될 수 있다.

[0044] [0052] 에이징된 오실레이팅 상태(시간(701)으로부터 시간(709)까지)에서, 클록 출력의 기간은 그의 입력 상의 상승 천이들에 대한 제 1 지연 체인의 지연 및 그의 입력 상의 하강 천이들에 대한 제 2 지연 체인의 지연을 결합한다. 이들 경우들 각각은 에이징에 의해 느려져서, 오실레이션의 주파수는 발생한 에이징의 양을 측정하는데 이용될 수 있게 된다.

[0045] [0053] 비-에이징된 오실레이팅 상태에서, 에이징 센서 제어 모듈(425)은, 그의 입력 상의 하강 천이들에 대한 제 1 지연 체인(411)의 지연 및 그의 입력 상의 상승 천이들에 대한 제 2 지연 체인의 지연을 포함하는 기간에 있어서 지연 체인들이 오실레이팅하도록 제 1 및 제 2 제어 신호들을 제어한다. 비-에이징된 오실레이팅 상태의 동작은 도 8의 과정도에서 예시된다. 과정들의 시작에서, 실행 제어 입력(RUN)은 로우이고, 지연 체인들은 제 1 지연 체인에 대한 입력(AIN)이 하이이고 제 2 지연 체인에 대한 입력(BIN)이 로우인 에이징 상태에 있다.

[0046] [0054] 시간(801)에서, 실행 신호는 하이로 스위칭하고 MIN/MAX 제어 신호는 로우이어서, 에이징 센서는 비-에이징된 오실레이팅 상태에 진입하게 된다. 제 1 제어 신호(INITA)는, 멀티플렉서(440)가 스위칭하고 제 1 지연 체인(411)에 대한 입력(AIN)이 로우로 스위칭하도록 로우로 스위칭한다. 제 1 지연 체인(411)에 대한 입력 상

의 하강 천이는 지연 체인을 통해 그리고 멀티플렉서(441)를 통해 AOUT로 전파되며, 이는 시간(802)에서 하강한다. 이 시간에, 에이징 센서 제어 모듈들(425)로부터의 제 1 및 제 2 제어 신호들은, AOUT가 선택되고 양자의 지연 체인들에 대한 입력들이 상승(멀티플렉서(440) 및 멀티플렉서(460)에 의해 인버팅된 AOUT의 하강)하도록 둘 다 로우이다.

[0047] [0055] 지연 체인들로의 입력들 상의 상승 천이들은 양자의 지연 체인들을 통해 동시에 전파된다. 그의 입력 상의 상승 천이에 대한 제 1 지연 체인(411)의 지연들은 에이징에 의해 느려진다. 그의 입력 상의 상승 천이에 대한 제 2 지연 체인(412)의 지연들은 에이징에 의해 느려지지 않는다. 제 2 지연 체인(412)에 대한 입력 상의 상승은 시간(803)에서 그의 출력으로 전파되고, 제 1 지연 체인(411)에 대한 입력 상의 상승은 시간(804)에서 그의 출력으로 전파된다. 시간(804)과 시간(803) 간의 차이는 에이징의 효과이다. 도 8에서, 지연의 차이는 효과를 명확히 예시하도록 과장된다.

[0048] [0056] 시간(803) 이전에, 에이징 센서 제어 모듈(425)로부터의 제어 신호들은, 멀티플렉서(440) 및 멀티플렉서(460)가 (상승 입력에 대한 에이징에 의해 영향을 받지 않은 지연 체인으로부터) BOUT를 선택하도록 세팅된다. 따라서, 양자의 지연 체인들에 대한 입력들은 시간(803) 이후 하강(멀티플렉서(440) 및 멀티플렉서(460)에 의해 인버팅되는 AOUT의 상승)한다.

[0049] [0057] 지연 체인들로의 입력들 상의 상승 천이들은 양자의 지연 라인들을 통해 동시에 전파된다. 그의 입력 상의 하강 천이에 대한 제 1 지연 체인(411)의 지연들은 에이징에 의해 느려지지 않는다. 그의 입력 상의 하강 천이에 대한 제 2 지연 체인(412)의 지연들은 에이징에 의해 느려진다. 제 1 지연 체인(411)에 대한 입력 상의 하강은 시간(805)에서 그의 출력으로 전파되고, 제 2 지연 체인(412)에 대한 입력 상의 하강은 시간(806)에서 그의 출력으로 전파된다. 시간(806)과 시간(805) 간의 차이는 에이징의 효과이다.

[0050] [0058] 시간(805) 이전에, 에이징 센서 제어 모듈(425)로부터의 제어 신호들은, 멀티플렉서(440) 및 멀티플렉서(460)가 (하강 입력에 대한 에이징에 의해 영향을 받지 않은 지연 체인으로부터) AOUT를 선택하도록 세팅된다. 따라서, 양자의 지연 체인들에 대한 입력들은 상승하고 지연 체인들의 하나의 오실레이션은 완료된다. 신호 천이들의 시퀀스는 그 후 시간(802)으로부터 시작하여 설명된 바와 같이 반복된다.

[0051] [0059] 시간(809)에서, 실행 제어 입력은 로우로 스위칭하고 에이징 센서는 에이징 상태로 다시 스위칭한다. 도 8의 비-에이징된 오실레이팅 상태는 단지 몇 오실레이션들 동안 지속되지만, 집적 회로에서, 에이징된 오실레이팅 상태는 예를 들어, 수백 또는 수천 오실레이션들 동안 지속될 수 있다.

[0052] [0060] 에이징 센서 제어 모듈(425)은 에이징된 오실레이팅 상태로부터 설명된 바와 같이 지연 체인들의 중간지점으로부터의 신호들을 이용하여 멀티플렉서(440) 및 멀티플렉서(460)에 대한 그의 제어 신호들 상의 천이들을 시간조절할 수 있다.

[0053] [0061] 비-에이징된 오실레이팅 상태(시간(801)으로부터 시간(809)까지)에서, 클록 출력의 기간은 그의 입력 상의 하강 천이들에 대한 제 1 지연 체인의 지연 및 그의 입력 상의 상승 천이들에 대한 제 2 지연 체인의 지연을 결합한다. 이들 경우들 각각은 에이징에 의해 느려지지 않아서, 오실레이션의 주파수는 발생한 에이징의 양을 표시하는데 이용될 수 있게 된다. 일부 경우들에서, 에이징의 효과는 비-에이징된 오실레이팅 상태의 오실레이션의 주파수를 증가시킬 수 있다.

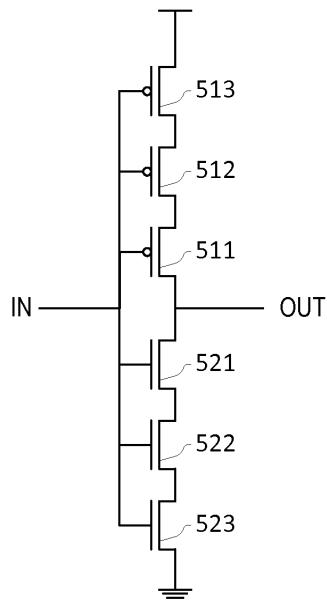

[0054] [0062] 도 5는 현재 개시된 실시예에 따른 지연 엘리먼트의 개략도이다. 지연 엘리먼트는 도 4의 에이징 센서의 지연 체인들의 지연 엘리먼트들을 구현하는데 이용될 수 있다. 도 5의 지연 엘리먼트는 입력(IN)을 수신하고 인버팅된 출력(OUT)을 생성한다.

[0055] [0063] 지연 엘리먼트는, 소스 및 드레인이 전압 공급기와 출력 간에 직렬로 연결되는 3개의 p-채널 트랜지스터들(511, 512, 513)을 포함하는 인버터이다. P-채널 트랜지스터들(511, 512, 513)의 게이트들은 입력에 연결된다. 지연 엘리먼트는 소스 및 드레인이 접지 기준과 출력 간에 직렬로 연결되는 3개의 n-채널 트랜지스터들(521, 522, 523)을 포함한다. n-채널 트랜지스터들(521, 522, 523)의 게이트들은 입력에 연결된다. 트랜지스터들의 직렬로의 이용은, 에이징 센서의 지연 체인들이 더 적은 스테이지들을 가질 수 있도록 지연 엘리먼트의 지연을 증가시킬 수 있다. 예를 들어, 관심의 특정 에이징 효과들에 의존하여 다수의 다른 타입들의 지연 엘리먼트들이 또한 이용될 수 있다.

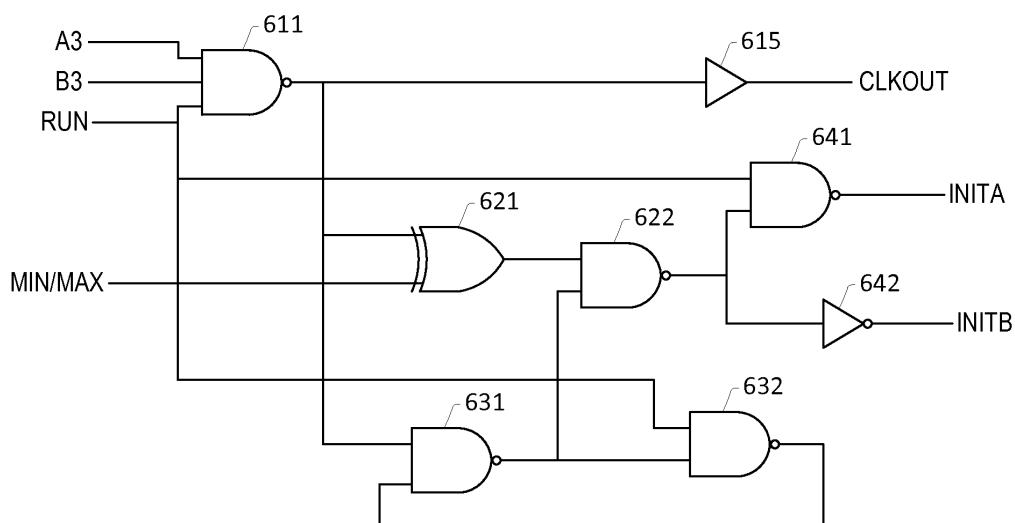

[0056] [0064] 도 6은 현재 개시된 실시예에 따른 에이징 센서 제어 모듈의 개략도이다. 에이징 센서 제어 모듈은 도 4의 에이징 센서의 에이징 센서 제어 모듈(425)을 구현하는데 이용될 수 있다. 도 6에서 예시된 회로는 예시적

이며 동일하거나 유사한 기능들이 다른 방식들로 구현될 수 있다.

- [0057] [0065] 에이징 센서 제어 모듈은 실행 제어 입력(RUN) 및 자연 제인들의 총간지점들(A3, B3)로부터 클록 출력을 생성하도록 NAND 게이트(611) 및 버퍼(615)를 이용한다. NAND 게이트(631) 및 NAND 게이트(632)는, 실행 제어 입력이 로우일 때 초기화되고 클록 출력이 상승할 때 토클링되는 셋-리셋(set-reset) 래치를 형성한다. NAND 게이트(631)의 출력은 로우일 것인 반면에, 실행 제어 입력은 (에이징 상태에서) 로우이고, 그 후 클록 출력의 제 1 하강 에지 상에서 하이로 천이할 것이다.

- [0058] [0066] 배타적-OR 게이트(621)는 MIN/MAX 제어 입력에 의해 결정된 자신의 극성을 갖는 클록 출력에 기초하여 제어 신호들(INITA, INITB)을 토클링하는데 이용된다. 제어 신호들 상의 천이들의 시작(실행 제어 신호의 상승 이후)은 NAND 게이트(622)에 의해 인에이블된다. 제 1 제어 신호(INITA)는, (실행 제어 입력이 로우일 때) 에이징 상태 동안 제 1 제어 신호의 값을 또한 제어하는 NAND 게이트(641)에 의해 버퍼링된다. 제 2 제어 신호(INITB)는 인버터(642)에 의해 버퍼링된다.

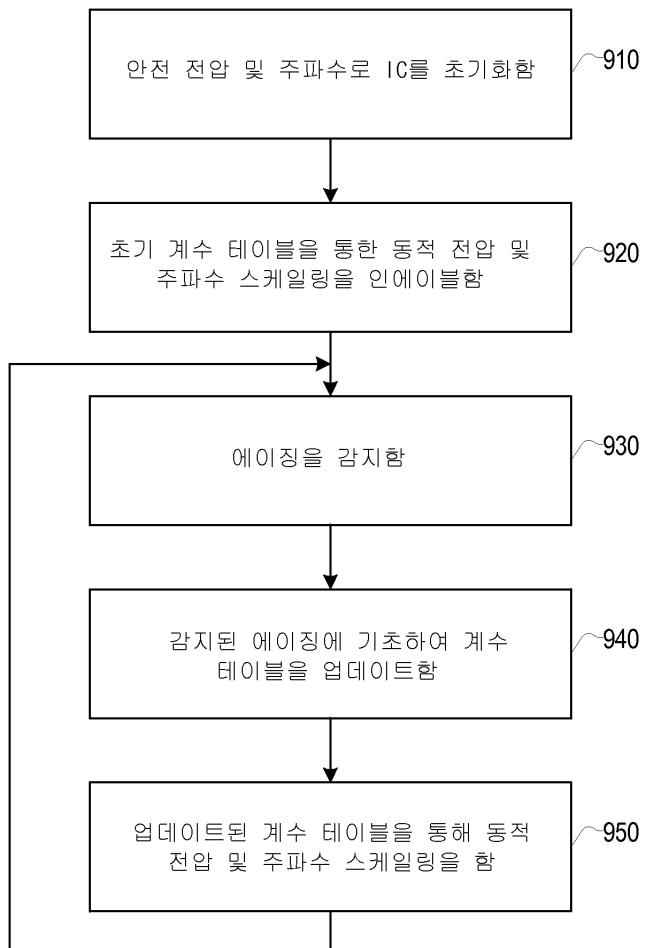

- [0059] [0067] 도 9는 현재 개시된 실시예에 따른 동적 디-에이징에 대한 프로세스의 흐름도이다. 프로세스는, 예를 들어, 도 1의 전자 시스템의 코어 전력 감소 제어기 모듈(111)에 의해 수행될 수 있다.

- [0060] [0068] 프로세스는 에이징 센서, 예를 들어, 도 4의 에이징 센서를 이용한다. 에이징된 오실레이팅 상태의 오실레이션의 주파수( $F_{aged}$ ) 및 비-에이징된 오실레이팅 상태의 오실레이션의 주파수( $F_{non-aged}$ )가 측정되고 연관된 회로의 동작을 디-에이징(에이징에 대한 보상)하는데 이용된다. 센서들은 링 오실레이터들 또는 RO들로서 단축하여 지칭될 수 있다. 프로세스는 에이징 센서에 의해 측정된 에이징과 동작 회로의 에이징 간의 결정된 관계를 이용하여서, 에이징 센서에서 측정된 에이징을 동작 회로의 에이징을 보상하는데 이용될 수 있게 된다. 프로세스는 하나의 도메인(공통 공급 전압을 갖는 동작 회로 모듈)에 대해 더 상세히 설명될 것이지만, 프로세스는 다수의 주파수들에서 각각 동작할 수 있는 다수의 도메인들에 대해 이용될 수 있다는 것이 이해되어야 한다.

- [0061] [0069] 에이징 센서에 의해 측정된 에이징과 동작 회로의 에이징 간의 관계는 실제 집적 회로들의 특징화 테스트에 의해 결정될 수 있다. 예를 들어, 집적 회로들은 다양한 온도들, 주파수들 및 전압들에서 동작하고 에이징 센서들의 성능 및 집적 회로의 동작 모듈들의 성능이 시간에 걸쳐 측정된다.

- [0062] [0070] 프로세스의 설명에서 또는 동적 디-에이징 프로세스에서 이용되는 개념들 및 변수들이 아래에서 정의된다.

- [0063] [0071] ARD(Aging RO Degradation)는 에이징 센서의 링 오실레이터들의 에이징으로 인한 저하를 반영한다. ARD는 에이징으로 인한 센서 오실레이팅 주파수의 퍼센티지 변화로서 센서 에이징을 표현한다. 일 실시예에서,  $ARD = (F_{non-aged} - F_{aged}) / F_{non-aged} + AED$ (퍼센트)이다.  $F_{non-aged}$ 는 트랜지스터 에이징에 민감하지 않은 비-에이징된 오실레이팅 상태의 에이징 센서의 주파수이고;  $F_{aged}$ 는 에이징에 민감한 에이징된 오실레이팅 상태의 에이징 센서의 주파수이며 트랜지스터들이 저하됨에 따라 점진적으로 늦춰질 것이다. 그러므로 ARD는 트랜지스터들이 에이징함에 따라 점진적으로 증가한다. 다수의 에이징 센서들을 갖는 도메인에 대해, ARD는 도메인의 모든 에이징 센서들로부터의 최대 측정값이다.  $ARD >= 0$ 이 되어야 한다. 이는 음의 값을 오프셋하기 위해 AED를 이용하여 달성될 수 있다. 대안적으로 또는 부가적으로, 프로세스는 음의 ARD 값을 0으로 세팅할 수 있다. ARD는 전압 의존적일 수 있고; ARD는 일반적으로 측정 전압이 감소함에 따라 증가한다.

- [0064] [0072] AED(Aging Error Distribution)는 시간 0에서(에이징 이전) ARD의 측정에서의 체계적인 랜덤 변동을 나타낸다. 이상적으로 (시간=0에서) ARD는 0이 되어야 하지만, ARD는 0에 집중되는 분포를 갖는 작은 랜덤값일 수 있다. ARD가 도메인 내의 모든 에이징 센서들로부터의 최대 측정된 값이기 때문에, (시간=0에서) ARD는 음(negative) 대신,  $>= 0$ 이 가능성이 매우 높다. 시간 0에서  $ARD >= 0$ 은 양호하지만, 시간 0에서  $ARD < 0$ 인 경우, AED는 ARD를 가드 밴딩하는데 이용된다. 시간=0에서 프러덕트 특징화(product characterization) 동안, 도메인의 ARD가 음인 경우, 그의 최악의 경우 절댓값은 AED 값을 세팅할 것이다.

- [0065] [0073] ASR(Aging Scaling Ratio)는 연관된 도메인에서 동작 회로들의 에이징과 센서 에이징 간의 관계를 나타낸다. 동작 회로들의 에이징은 이들 회로들의 최대 동작 주파수( $F_{max}$ )의 변화로서 표현될 수 있다. 프로세스는  $ASR = F_{max} 저하 / ARD$ 를 세팅할 수 있다.  $F_{max}$  저하는 특정 컨디션들에 대해 도메인의 회로들의 최대 동작 주파수의 변화의 양이다. 유닛 레벨 ASR 값은 주어진 도메인의 회로들에 대한 ASR 값으로서 이용되는 (HTOL(hight-temperature operating life) 테스트 상에서 이루어진 다수의 판독들 중) 최악의 판독 값을 갖는

프리덕트 HTOL 테스트 유닛들로부터 수집될 수 있다. 하나의 ASR 값은 프리덕트 HTOL 테스트 동안 다수의 판독들로부터 결정될 수 있다. 대안적으로, 다수의 ASR 값들은 예를 들어, 디레이팅 테이블(derating table)에서 이용될 수 있다.

[0066] [0074] 전압 대 주파수 스케일링 팩터는 동작 회로의 최대 동작 주파수와 전압 간의 관계를 나타낸다. 전압 대 주파수 스케일링 팩터는 도메인에서  $1\% F_{max}$ 를 전달하는데 필요한 전압의 증가의 양을 나타내는 VPF(Voltage of Percent  $F_{max}$ )로서 표현될 수 있다. VPF는 프리덕트 특징화로부터 결정될 수 있다. 주어진 도메인에 대해 측정된 최고 VPF 값이 이용되어야 한다. VPF는 전압 의존적일 수 있다. 전압들은 모든 전압들에 대해 이용되는 최고 VPF 값 또는 이용되는 다수의 VPF 값들에 있어서의 범위들로 분할될 수 있다.

[0067] [0075] AGB(Aging Guard Band)는 도메인의 회로들에 대한  $F_{max}$ 를 유지하기 위해 트랜지스터 저하를 보상하는데 필요한 전압 증가의 양이다. 프로세스는  $AGB = VPF * ASR * ARD$ 를 세팅할 수 있다. AGB는 각각의 AR 측정 이후 업데이트될 수 있다. AGB는 전압 의존적일 수 있다. 프로세스는 전압들의 상이한 범위들에 대해 다수의 AGB 값들을 이용할 수 있거나, 또는 다른 전압들에서 이용하기 위해 하나의 AGB 값을 스케일링할 수 있다.

[0068] [0076] ATA(Aging Target Addon)는 다양한 주파수들에서 동작하도록 연관된 동작 모듈들에 대해 어느 성능 센서 측정 값들이 필요한지를 표시하는 계수 테이블을 프로세스가 업데이트하는데 이용할 수 있는, AGB로부터 변환된 값이다. 이 변환은 (전압 면에서 에이징 보상의 양을 표시하는) AGB 값들을 타겟 성능 센서 값들에 맵핑한다. 이 맵핑은 예를 들어, 집적 회로 특징화로부터 획득되는 공급 전압과 성능 센서 측정들 간의 관계를 이용할 수 있다. ATA 값들은 에이징 저하를 보상하기 위해 계수 테이블 값들을 업데이트한다. 예를 들어, 특정 주파수에서 동작하도록 연관된 동작 모듈에 대해 필요한 특정 성능 센서 측정 값을 나타내는 계수 테이블 값이 증가될 수 있다. 위에서 설명된 계수 테이블을 이용하지 않는 시스템에서, ATA 값들의 해석은 생략되거나 그 시스템에 적절한 다른 계산들로 대체될 수 있다.

[0069] [0077] 도 9의 프로세스는, 집적 회로가 위의 디-에이징 정보를 이용하여 어떻게 동작될 수 있는지를 예시한다. 명확한 설명을 위해, 프로세스는 단일 도메인에 대해 설명되지만, 프로세스는 다수의 도메인들의 디-에이징에 대해 이용될 수 있다는 것이 이해되어야 한다.

[0070] [0078] 블록(910)에서, 집적 회로는 안전 전압들 및 주파수로 초기화된다. 전압들 및 주파수들의 이 결합은 모든 예상된 컨디션들 하에서 집적 회로의 신뢰 가능한 동작에 대해 충분한 가드 밴드를 갖는다. 예상된 컨디션들은 집적 회로가 동작을 위해 특정되는 모든 컨디션들을 포함할 수 있다. 안전 전압들 및 주파수들은 최악의 경우의 에이징에 대해 집적 회로의 신뢰 가능한 동작을 허용한다.

[0071] [0079] 블록(920)에서, 프로세스는 계수 테이블에서 초기 값들을 이용하여 집적 회로의 동적 전압 및 주파수 스케일링을 인에이블한다. 계수 테이블은 다양한 동작 주파수들에 대한 타겟 성능 센서 측정 값들을 포함한다. 동적 전압 및 주파수 스케일링 동작의 예는, 성능 센서 측정을 획득하기 위해 성능을 측정하는 것, 대응하는 타겟 성능 센서 측정 값을 획득하도록 정정 테이블의 현재 동작 주파수를 룩 업(look up)하는 것, 및 성능 센서 측정의 상대적 값들 및 타겟 값에 기초하여 전압을 조건부로 조정하는 것을 포함한다. 예를 들어, 성능 센서 측정이 타겟 값 미만인 경우, 전압은 회로 속도를 증가시키도록 상승될 수 있다. 계수 테이블의 초기 값들은 집적 회로의 EOL(end-of-life) 에이징에 대한 충분한 가드 밴딩을 포함한다. 초기 값들은 집적 회로의 특징화에 의해 결정될 수 있다. EOF(end-of-life) 에이징의 가드 밴딩은 초기 ATA 값을 이용함으로써 달성될 수 있다. 프로세스는 그 후 감지된 에이징에 기초하여 디-에이징을 수행하기를 지속한다.

[0072] [0080] 블록(930)에서, 프로세스는 집적 회로의 에이징을 측정한다. 블록(930)은  $ARD = (F_{non-aged} - F_{aged}) / F_{non-aged} + AED$  따라 ARD를 측정하는 것을 포함할 수 있다. 일 실시예에서,  $F_{aged}$ 는  $F_{non-aged}$  이전에 측정된다. 이는 에이징 센서가 측정들을 수행하도록 오실레이팅할 때 발생할 수 있는 에이징의 효과들의 반전(reversal)을 최소화하거나 방지할 수 있다. 프로세스는 그 후  $AGB = VPF * ASR * ARD$ 에 따라 AGB를 계산할 수 있다. AGB는 보통(비-대기) 모드에서 계산된다. 프로세스는 그 후 초기(또는 현재) ATA를 대체하도록 ATA를 계산할 수 있다. 실시예에서, 프로세스는 집적 회로의 특징화에 의해 결정될 수 있는 최대 EOF 값으로 ATA의 양을 제한한다. 다양한 실시예들에서, ARD는 고정된 전압에서 또는 에이징 센서들과 연관된 현재 이용되는 동작 전압들에서 측정될 수 있다.

[0073] [0081] 블록(940)에서, 프로세스는 블록(930)에서 감지된 에이징에 기초하여 계수 테이블을 업데이트한다. 프로세스는 하나의 주파수, 모든 주파수들, 또는 주파수들의 범위에 대해 계수 테이블을 업데이트할 수 있다. 대

안적으로, 프로세스는 동적 전압 및 주파수 스케일링을 인에이블하기 이전에 계수 테이블을 업데이트할 수 있다. 다른 대안에서, 초기화된 동작 주파수에 대한 계수 테이블의 업데이트는 동적 전압 및 주파수 스케일링을 인에이블하고, 그 후 전체 계수 테이블을 업데이트한다.

[0074] [0082] 블록(950)에서, 집적 회로는 블록(940)으로부터의 업데이트된 계수 테이블을 통한 동적 전압 및 주파수 스케일링을 이용하여 동작한다.

[0075] [0083] 주기적으로, 프로세스는 에이징의 효과들에 대해 계수 테이블을 추가로 업데이트하도록 블록들(930 및 940)로 리턴한다. 프로세스는 타이머의 만료에 기초하여 계수 테이블을 업데이트할 수 있다. 업데이트들의 기간은 예를 들어, 1분, 10분 또는 1시간마다 일 수 있다. 업데이트들 간의 기간은 예를 들어, 집적 회로가 에이징함에 따라 업데이트를 덜 빈번하게 하도록 시간에 걸쳐 변할 수 있다. 부가적으로 또는 대안적으로, 프로세스는 집적 회로의 동작 모드 또는 집적 회로의 동작 모듈의 변화에 기초하여 계수 테이블을 업데이트할 수 있다. 예를 들어, 계수 테이블은 동작 모드로부터 대기 모드로(그 반대도 마찬가지임) 집적 회로를 스위칭할 때 업데이트될 수 있다.

[0076] [0084] 동적 디-에이징을 위한 프로세스는 예를 들어, 블록들을 부가하고, 생략하고, 재순서화하거나 변경함으로써 변형될 수 있다. 예를 들어, 프로세스는 클록 주파수들(또는 다른 성능 파라미터들)을 조정함으로써 디-에이징할 수 있다. 이러한 실시예에서, 프로세스는 전압 대 주파수 스케일링 팩터를 이용한 계산들을 생략할 수 있다. 부가적으로, 블록들은 동시에 수행될 수 있다.

[0077] [0085] 본 발명의 실시예들이 특정 실시예들에 대해 위에서 설명되었지만, 본 발명의 다수의 변동들이 가능하다. 예를 들어, 다양한 컴포넌트들의 수는 증가되거나 감소될 수 있다. 설명된 시스템들 및 방법들은 집적 회로에서 가장 중요한 특정 에이징 효과들에 의존하여 변형될 수 있다. 에이징 센서는 집적 회로의 특정 제조 기술에 따라 맞출될 수 있다. 집적 회로는 다수의 에이징 효과들을 측정하도록 다수의 에이징 센서들을 포함할 수 있다. 부가적으로, 다양한 실시예들의 특징들은 위에서 설명된 것들과 상이한 결합들로 결합될 수 있다.

[0078] [0086] 본원에서 개시된 실시예들과 관련하여 설명된 다양한 예시적인 블록들 및 모듈들은 다양한 형태들로 구현될 수 있다는 것을 당업자는 인지할 것이다. 일부 블록들 및 모듈들은 일반적으로 그 기능성의 견지에서 위에서 설명되었다. 이러한 기능성이 어떻게 구현될지는 전체 시스템에 부과되는 설계 제약들에 의존한다. 당업자들은 각각의 특정 애플리케이션에 대해 다양한 방식들로 설명된 기능을 구현할 수 있지만, 이러한 구현 결정들이 본 발명의 범위를 벗어나게 하는 것으로 해석되어서는 안 된다. 또한, 모듈 또는 블록 내의 기능들의 그룹핑은 설명의 용이함을 위한 것이다. 특정 기능들은, 본 발명으로부터 벗어남 없이 하나의 모듈 또는 블록으로부터 이동될 수 있거나 또는 모듈들 또는 블록들에 걸쳐 분배될 수 있다.

[0079] [0087] 본 명세서에 개시된 실시예와 관련하여 설명된 다양한 예시적인 로직 블록들 및 모듈들은, 범용 프로세서, 디지털 신호 프로세서(DSP), 주문형 집적 회로(ASIC), 필드 프로그래밍 가능 게이트 어레이(FPGA), 또는 기타 프로그래밍 가능 로직 디바이스, 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 컴포넌트, 또는 본원에 설명된 기능을 수행하도록 설계된 이들의 임의의 결합으로 구현되거나 수행될 수 있다. 범용 프로세서는 마이크로프로세서일 수 있지만, 대안적으로, 프로세서는 임의의 프로세서, 제어기, 마이크로 제어기, 또는 상태 머신 일 수 있다. 프로세서는 또한 컴퓨팅 장치들의 조합, 예를 들어, DSP와 마이크로프로세서의 조합, 복수의 마이크로프로세서들, DSP 코어와 결합 된 하나 이상의 마이크로프로세서들, 또는 임의의 다른 이러한 구성으로 구현될 수 있다.

[0080] [0088] 본원에 개시된 실시예들과 관련하여 설명된 알고리즘 또는 방법의 단계들은 직접 하드웨어, 프로세서에 의해 실행되는 소프트웨어 모듈, 또는 이 둘의 결합으로 구현될 수 있다. 소프트웨어 모듈은, RAM 메모리, 플래시 메모리, ROM 메모리, EPROM 메모리, EEPROM 메모리, 레지스터들, 하드 디스크, 착탈식 디스크, CD-ROM, 또는 저장 매체의 임의의 다른 형태에 상주할 수 있다. 예시적인 저장 매체는 프로세서에 커플링될 수 있어서, 프로세서는 저장 매체로부터 정보를 관독하고, 그리고 저장 매체에 정보를 기록할 수 있다. 대안적으로, 저장 매체는 프로세서에 통합될 수 있다. 프로세서 및 저장 매체는 ASIC에 상주할 수 있다.

[0081] [0089] 개시된 실시예의 위의 설명은 당업자가 본 발명을 실시하거나 이용할 수 있도록 제공된다. 이들 실시예들에 대한 다양한 변형은 당업자에게 쉽게 명백하게 될 것이며, 본원에서 설명된 일반적인 원리들은 본 발명의 사상 또는 범위를 벗어나지 않고 다른 실시예들에 적용될 수도 있다. 따라서, 본원에서 제시된 설명 및 도면들은 본 발명의 현재 바람직한 실시예를 나타내며, 그에 따라 본 발명에 의해 광의로 고려되는 청구 대상을 대표

한다는 것이 이해될 것이다. 본 발명의 범위는 당업자들에게 명백하게 될 수 있는 다른 실시예들을 완전히 포괄하며, 그에 따라 본 발명의 범위는 첨부된 청구항들 이외의 어떤 것에 의해서도 제한되지 않는다는 것이 추가로 이해된다.

## 도면

### 도면1

## 도면2

## 도면3

도면4

도면5

도면6

도면7

도면8

## 도면9