(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-510145

(P2006-510145A)

(43) 公表日 平成18年3月23日(2006.3.23)

(51) Int.C1.

G 11 C 11/15

(2006.01)

F 1

G 11 C 11/15 140

G 11 C 11/15 150

テーマコード(参考)

審査請求 有 予備審査請求 未請求 (全 24 頁)

(21) 出願番号 特願2004-559798 (P2004-559798)

(86) (22) 出願日 平成15年12月10日 (2003.12.10)

(85) 翻訳文提出日 平成17年8月10日 (2005.8.10)

(86) 國際出願番号 PCT/EP2003/014011

(87) 國際公開番号 WO2004/055821

(87) 國際公開日 平成16年7月1日 (2004.7.1)

(31) 優先権主張番号 10/318,709

(32) 優先日 平成14年12月13日 (2002.12.13)

(33) 優先権主張国 米国(US)

(71) 出願人 501209070

インフィニエオン テクノロジーズ アクチ

エンゲゼルシャフト

ドイツ連邦共和国 81669 ミュンヘ

ン ザンクト マルティン シュトラーセ

53

(71) 出願人 500460058

インターナショナル ビジネス マシーン

ズ コーポレイション

アメリカ合衆国, 10504 ニュー ヨ

ーク州, アーモンク, ニュー オーチャー

ド ロード

(74) 代理人 110000338

特許業務法人原謙三國際特許事務所

最終頁に続く

(54) 【発明の名称】高速磁気メモリ用アーキテクチャ

## (57) 【要約】

磁気メモリ回路は、複数のメモリセルと、1つまたは複数の上記メモリセルに選択的にアクセスするための、上記メモリセルと連結された複数のビット線とを備えている。メモリ回路は、少なくとも1つのビット線プログラミング回路と、第1セットのスイッチとを備え、上記ビット線プログラミング回路は、少なくとも1つのメモリセルの論理状態を書き込むためのプログラミング電流を生成するための電流ソース、および/または、上記プログラミング電流を戻すための電流シンクとして構成可能である。第1セットのスイッチは、メモリセルの少なくとも読み込み動作中は禁止されており、第1セットのスイッチの少なくとも一部は、メモリセルの書き込み動作中に選択的に許可される。第1セットのスイッチの各スイッチは、少なくとも1つのビット線プログラミング回路を、第1制御信号に応じて、ビット線の対応する1つと選択的に連結するように構成されている。メモリ回路は、さらに、少なくとも1つのセンスアンプと第2セットのスイッチとを備えている。第2セットのスイッチは、少なくともメモリセルの書き込み動作中は禁止されて

**【特許請求の範囲】****【請求項 1】**

複数のメモリセルと、

1つまたは複数の上記メモリセルに選択的にアクセスするための、上記メモリセルと連結された複数のビット線と、

少なくとも1つのビット線プログラミング回路と、

第1セットのスイッチと、

少なくとも1つのセンスアンプと、

第2セットのスイッチとを備え、

上記ビット線プログラミング回路は、少なくとも1つのメモリセルの論理状態を書き込むためのプログラミング電流を生成するための電流ソース、および、上記プログラミング電流を戻すための電流シンクの少なくとも1つとして構成可能であり、

上記第1セットのスイッチは、メモリセルの少なくとも読み込み動作中は禁止されており、第1セットのスイッチの少なくとも一部は、メモリセルの書き込み動作中に選択的に許可され、上記第1セットのスイッチの各スイッチは、少なくとも1つのビット線プログラミング回路を、第1制御信号に応じて、ビット線の対応する1つと選択的に連結するよう構成されており、

上記第2セットのスイッチは、メモリセルの少なくとも書き込み動作中は禁止されており、第2セットのスイッチの少なくとも一部は、メモリセルの読み込み動作中に選択的に許可され、上記第2セットのスイッチの各スイッチは、少なくとも1つのセンスアンプを、第2制御信号に応じて、ビット線の対応する1つと連結するよう構成されている、磁気メモリ回路。

**【請求項 2】**

上記第1および第2セットのスイッチの各々は、電界効果トランジスタ(FET)を備えている、請求項1に記載の回路。

**【請求項 3】**

上記第2セットのスイッチの各々にあるFETは、第1セットのスイッチの各々にあるFETよりも少なくとも4分の1小さいようにサイズ決定されている、請求項2に記載の回路。

**【請求項 4】**

複数のメモリセルと、

1つまたは複数の上記メモリセルに選択的にアクセスするための、上記メモリセルと連結された複数のビット線およびワード線と、

少なくとも1つのプログラミング電流ソース/シンクと、

複数の第1スイッチと、

少なくとも1つのセンスアンプと、

複数の第2スイッチとを備え、

上記電流ソース/シンクは、1つまたは複数のメモリセルの論理状態を書き込むためのプログラミング電流を生成するための電流ソース、および、プログラミング電流を戻すための電流シンクの少なくとも1つとして構成可能であり、

上記第1スイッチの各々は、対応するビット線と連結された第1端子と、少なくとも1つのプログラミング電流ソース/シンクと連結された第2端子と、第1制御信号を受信するための少なくとも1つの制御入力部とを備え、上記第1スイッチの各々は、対応するビット線を、少なくとも1つのプログラミング電流ソース/シンクに、第1制御信号に応じて連結し、

上記第2スイッチの各々は、少なくとも1つのセンスアンプの入力部と連結された第1端子と、対応するビット線と連結された第2端子と、第2制御信号を受信するための少なくとも1つの制御入力部とを備え、上記第2スイッチの各々は、対応するビット線を、少なくとも1つのセンスアンプの入力部に、第2制御信号に応じて連結する、磁気メモリ回路。

10

20

30

40

50

**【請求項 5】**

上記第1制御信号は、アドレスを有し、

複数の第1スイッチの少なくとも一部の各々は、制御入力部と連結された復号回路素子を備え、上記復号回路素子は、アドレスを復号し、これに応じて、対応するビット線を、少なくとも1つのプログラミング電流ソース／シンクの出力部に選択的に連結するように構成可能である、請求項4に記載の回路。

**【請求項 6】**

上記第2制御信号は、アドレスを有し、

複数の第2スイッチの少なくとも一部の各々は、制御入力部と連結された復号回路素子を備え、上記復号回路は、アドレスを復号し、これに応じて、対応するビット線を、少なくとも1つのセンスアンプの入力部に選択的に連結するように構成可能である、請求項4に記載の回路。

10

**【請求項 7】**

アドレスを受信するための少なくとも1つの入力部を有する復号器をさらに備え、上記復号器は、第1および第2制御信号を、上記アドレスに応じて生成するように構成可能である、請求項4に記載の回路。

**【請求項 8】**

上記複数の第1スイッチは、同じ次元の複数の下位集合に配置されており、各下位集合は、少なくとも1つのスイッチを備え、

少なくとも1つのプログラミング電流ソース／シンクは、複数の電流ソース／シンクを備え、上記電流ソース／シンクの各々は、対応する下位集合と連結されており、対応するデータ入力部に割り当てられており、複数の電流ソース／シンクの各々の出力部における負荷容量は、低減されている、請求項4に記載の回路。

20

**【請求項 9】**

第3制御信号を受信するための少なくとも1つの制御入力部と複数の出力部とを有する復号器をさらに備え、複数の電流ソース／シンクの少なくとも一部における出力部の各々は、電流ソースの対応する1つの制御入力部と連結されており、復号器は、電流ソースの1つを、制御信号に応じて選択するように構成可能である、請求項8に記載の回路。

**【請求項 10】**

上記複数の電流ソース／シンクの各々は、本質的に相互に一致している、請求項8に記載の回路。

30

**【請求項 11】**

上記複数の電流ソース／シンクの少なくとも一部は、それに対応するメモリセルに近い相対的な近傍に配置されている、請求項8に記載の回路。

**【請求項 12】**

上記複数のメモリセルの少なくとも一部の各々は、磁気トンネル接合（MTJ）装置を備えている、請求項4に記載の回路。

**【請求項 13】**

上記複数の第1スイッチおよび複数の第2スイッチの少なくとも一部の各々は、電界効果トランジスタを備えている、請求項4に記載の回路。

40

**【請求項 14】**

少なくとも1つの第2センスアンプと、

マルチプレクサとをさらに備え、上記マルチプレクサは、第3制御信号を受信するための少なくとも1つの制御入力部と、出力部と、複数のデータ入力部とを備え、データ入力部の各々は、センスアンプの対応する1つの出力部と連結されており、上記マルチプレクサは、センスアンプの1つを、第3制御信号に応じて選択するように構成可能である、請求項4に記載の回路。

**【請求項 15】**

複数のメモリセルと、複数のプログラミング線とを含み、上記複数のプログラミング線は、1つまたは複数のメモリセルに選択的にアクセスするために、メモリセルと動作可能

50

なように連結されている、磁気メモリアレイにおける使用のためのプログラミング回路であって、

上記プログラミング回路は、

複数のスイッチと、

複数の電流ソース／シンクと、

第1復号器とを備え、

上記スイッチの各々は、プログラミング線の対応する1つと連結されており、

上記複数の電流ソース／シンクの各々は、同じ次元の1つまたは複数のスイッチの下位集合と連結されており、1つまたは複数のメモリセルの論理状態を書き込むためのプログラミング電流を生成するための電流ソース、および、プログラミング電流を戻すための電流シンクの少なくとも1つとして構成可能であり、

上記第1復号器は、第1制御信号を受信するための少なくとも1つの制御入力部と複数の出力部とを有し、出力部の各々は、スイッチの対応する1つと連結されており、第1復号器は、スイッチの1つを、第1制御信号に応じて選択するように構成可能であり、

複数のスイッチに関連付けられている全体的な負荷容量は、複数の電流ソース／シンク間に分散されており、その結果、電流ソース／シンクの少なくとも1つの負荷容量が低減される、プログラミング回路。

#### 【請求項16】

第2復号器をさらに備え、上記第2復号器は、第2制御信号を受信するための少なくとも1つの入力部と複数の出力部とを有し、出力部の各々は、電流ソース／シンクの対応する1つと連結されており、上記第2復号器は、1つまたは複数の電流ソース／シンクを、第2制御信号に応じて、選択的に許可および禁止することの少なくとも1つのために構成可能である、請求項15に記載のプログラミング回路。

#### 【請求項17】

上記第2制御信号は、第1制御信号の少なくとも一部を有している、請求項15に記載のプログラミング回路。

#### 【請求項18】

上記電流ソース／シンクの各々は、本質的に相互に一致している、請求項15に記載のプログラミング回路。

#### 【請求項19】

上記複数のスイッチは、複数の電流ソース／シンクに本質的に均等に分散されている、請求項15に記載のプログラミング回路。

#### 【請求項20】

少なくとも1つのセンスアンプと、

複数の第2スイッチとをさらに備え、

第2スイッチの各々は、少なくとも1つのセンスアンプの入力部と連結された第1端子と、プログラミング線の対応する1つと連結された第2端子と、第2制御信号を受信するための少なくとも1つの制御入力部とを備え、第2スイッチの各々は、対応するプログラミング線を、第2制御信号に応じて、少なくとも1つのセンスアンプの入力部と連結する、請求項15に記載のプログラミング回路。

#### 【請求項21】

上記第2制御信号は、アドレスを有し、

第2スイッチの少なくとも1つは、制御入力部と連結された復号回路素子を備え、上記復号回路素子は、アドレスを復号し、それに応じて、対応するプログラミング線を、少なくともセンスアンプの入力部と選択的に連結するように構成可能である、請求項20に記載のプログラミング回路。

#### 【請求項22】

少なくとも1つの磁気メモリ回路を含む集積回路であって、この磁気メモリ回路は、複数のメモリセルと、

1つまたは複数の上記メモリセルに選択的にアクセスするための、上記メモリセルと連

10

20

30

40

50

結された複数のビット線と、

少なくとも1つのビット線プログラミング回路と、

第1セットのスイッチと、

少なくとも1つのセンスアンプと、

第2セットのスイッチとを備え、

上記ビット線プログラミング回路は、少なくとも1つのメモリセルの論理状態を書き込むためのプログラミング電流を生成するための電流ソース、および、上記プログラミング電流を戻すための電流シンクの少なくとも1つとして構成可能であり、

上記第1セットのスイッチは、メモリセルの少なくとも読み込み動作中は禁止されており、第1セットのスイッチの少なくとも一部は、メモリセルの書き込み動作中に選択的に許可され、上記第1セットのスイッチの各スイッチは、少なくとも1つのビット線プログラミング回路を、第1制御信号に応じて、ビット線の対応する1つと選択的に連結するよう構成されており、

上記第2セットのスイッチは、メモリセルの少なくとも書き込み動作中は禁止されており、第2セットのスイッチの少なくとも一部は、メモリセルの読み込み動作中に選択的に許可され、上記第2セットのスイッチの各スイッチは、少なくとも1つのセンスアンプを、第2制御信号に応じて、ビット線の対応する1つと連結するよう構成されている、集積回路。

#### 【請求項23】

上記第1セットのスイッチは、同じ次元にある複数の下位集合に配置されており、各下位集合は、少なくとも1つのスイッチを備え、

少なくとも1つのビット線プログラミング回路は、複数の電流ソース/シンクを備え、電流ソース/シンクの各々は、対応する下位集合と連結されており、対応するデータ入力部に割り当てられており、複数の電流ソース/シンクの各々の出力部における負荷容量は、低減されている、請求項22に記載の集積回路。

#### 【請求項24】

上記少なくとも1つの磁気メモリ回路は、

少なくとも1つの第2センスアンプと、

マルチプレクサとをさらに備え、

上記マルチプレクサは、第3制御信号を受信するための少なくとも1つの制御入力部と、出力部と、複数のデータ入力部とを備え、データ入力部の各々は、センスアンプの対応する1つの出力部と連結されており、上記マルチプレクサは、センスアンプの1つを、第3制御信号に応じて選択するよう構成可能である、請求項22に記載の回路。

#### 【請求項25】

複数のメモリセルと、複数のプログラミング線とを含み、上記複数のプログラミング線は、1つまたは複数のメモリセルに選択的にアクセスするために、メモリセルと動作可能なよう連結されている、磁気メモリアレイにおける使用のための少なくとも1つのプログラミングを含む集積回路であって、

上記プログラミング回路は、

複数のスイッチと、

複数の電流ソース/シンクと、

第1復号器とを備え、

上記スイッチの各々は、プログラミング線の対応する1つと連結されており、

上記複数の電流ソース/シンクの各々は、同じ次元の1つまたは複数のスイッチの下位集合と連結されており、1つまたは複数のメモリセルの論理状態を書き込むためのプログラミング電流を生成するための電流ソース、および、プログラミング電流を戻すための電流シンクの少なくとも1つとして構成可能であり、

上記第1復号器は、第1制御信号を受信するための少なくとも1つの制御入力部と複数の出力部とを有し、出力部の各々は、スイッチの対応する1つと連結されており、第1復号器は、スイッチの1つを、第1制御信号に応じて選択するよう構成可能であり、

10

20

30

40

50

複数のスイッチに関連付けられている全体的な負荷容量は、複数の電流ソース / シンク間に分散されており、その結果、電流ソース / シンクの少なくとも 1 つの負荷容量が低減される、集積回路。

【請求項 26】

上記少なくとも 1 つのプログラミング回路は、

少なくとも 1 つのセンスアンプと、

複数の第 2 スイッチとをさらに備え、

第 2 スイッチの各々は、少なくとも 1 つのセンスアンプの入力部と連結された第 1 端子と、プログラミング線の対応する 1 つと連結された第 2 端子と、第 2 制御信号を受信するための少なくとも 1 つの制御入力部とを備え、第 2 スイッチの各々は、対応するプログラミング線を、第 2 制御信号に応じて、少なくとも 1 つのセンスアンプの入力部と連結する、請求項 25 に記載の集積回路。

10

20

30

【発明の詳細な説明】

【発明の詳細な説明】

【0001】

【政府の権利の明示】

本発明は、米国国防総省の高等研究計画局 (DARPA) によって付与された交付契約番号 MDA 972-99-C-0009 に基づき、政府の支援でなされたものである。政府は本発明に一定の権利を有する。

【0002】

【発明の属する技術分野】

本発明は、概してメモリ回路に関するものであり、より具体的には磁気ランダムアクセスメモリ (MRAM) の書き込み、および、読み込み用の技術に関する。

【0003】

【発明の背景】

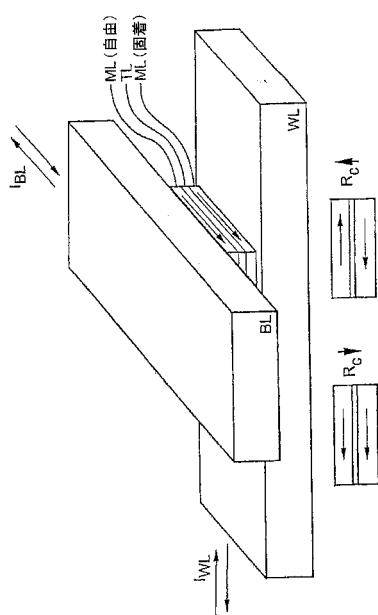

図 1 に、従来の磁気トンネル接合 (MTJ) 装置 100 を示す。MTJ 100 は、典型的には、2 つの導体の交差点に、トンネル障壁 (TL) によって分離されている 2 つの強磁性層 (ML) のスタックを備えている。これらの導体の 1 つは、ワード線 (WL) であり、他方がビット線 (BL) であってもよい。2 つの磁気層の 1 つは、多くの場合、自由磁気層と呼ばれる。自由磁気層の磁気配向は、導体 WL・BL をそれぞれ流れるプログラミング電流  $I_{WL}$ ・ $I_{BL}$  によって生成される磁場を重畳することによって変更できる。

2 つの磁気層 ML の他方は、多くの場合、固着磁気層と呼ばれる。プログラミング電流  $I_{WL}$ ・ $I_{BL}$  は、固着磁気層の磁気配向を変更できない。論理状態 (例えば、「0」ビットまたは「1」ビット) は、一般的に、自由磁気層の配向を固着磁気層に対して相対的に変更することにより MTJ 100 に格納される。2 つの磁気層が、同じ配向を有している場合は、MTJ 100 は、導体 WL と導体 BL との間で測定すると、それに関連する低い抵抗  $R_c$  を典型的には有している。同じく、磁気層が相互に対向する方向に配向されている場合は、MTJ 100 の抵抗  $R_c$  は、一般的に高い。

【0004】

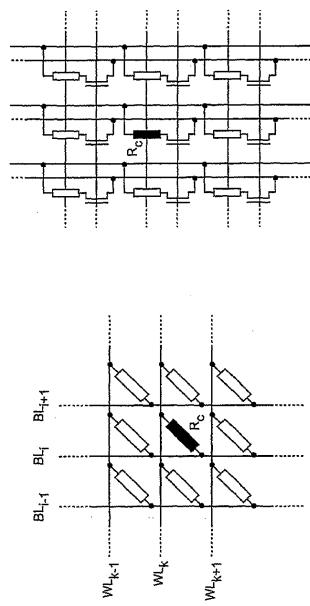

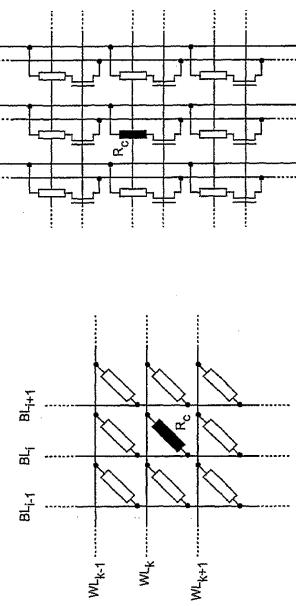

従来の MRAM は、一般的に、アレイ構造に接続された複数の MTJ 装置を備えている。従来の MRAM アレイの 2 つの例を、図 2A および図 2B に示す。図 2A に、交差点アレイを示す。各メモリセルは、ワード線 (例えば、 $WL_{k-1}$ 、 $WL_k$ 、 $WL_{k+1}$ ) と対応するビット線 (例えば、 $BL_{i-1}$ 、 $BL_i$ 、 $BL_{i+1}$ ) との交差点に接続されている単一の MTJ 装置を備えている。MTJ 装置は、図には、代表的な抵抗 (例えば、 $R_c$ ) として記載されている。図 2B に、複数のメモリセルを採用している代替メモリーアキテクチャを示す。各セルは、MTJ 装置と直列に連結された選択トランジスタ (すなわち、1T1MTJ メモリセル) を備えている。選択トランジスタは、読み込み動作中に、対応する MTJ 装置にアクセスするために使用される。MRAM 回路については、さらに詳細に、例えば W. Reohr 他の題名「未来のメモリ (Memories of Tomorrow)」IEEE Circuits and Devices Mag. , 17-27 ページ, 18 卷, 5 号, 2002 年 9 月に記

40

50

載されており、この内容を本願に含む。

【0005】

選択されたメモリセルの論理状態を書き込むため、および、メモリセルアレイのビット線からデータを読み出すために必要なプログラミング電流を印加するために、列選出回路(図示せず)が、典型的には、必要である。この列選出回路は、一般的に、選択されたビット線を、プログラミング回路に接続する。このプログラミング回路は、メモリセルの書き込み動作中に、セルプログラミング電流を供給する。さらに、列選出回路は、セルのプログラムされた論理状態を感知するために、選択されたメモリセルの読み込み動作中に、選択されたビット線をセンスアンプ(図示せず)に接続する。

【0006】

従来のMRAMアレイは、一般的に、MRAMアレイのメモリセルに選択的に書き込むための2つのプログラミング電流(例えば、図1の $I_{BL}$ または $I_{WL}$ )の1つを供給するために、単一の電流ソースを採用している。一般的に、磁気メモリアレイ内では、アレイの1つまたは複数のメモリセルを選択する助けとなるように、1つのワード線電流が要求される。1つまたは複数のビットワードの1つまたは複数のそれぞれのメモリセルのための、1つまたは複数のビット線電流は、メモリセルを0または1論理状態になるように書き込むために要求される。上述のように、メモリアレイ全体に施設されたワード線およびビット線は、書き込みおよび読み込みを行うためのそれぞれプログラミング電流およびセンス電流を、アレイにある選択されたメモリセルへ搬送する。しかしながら、これらのワードおよびビット線の各々は、それらに関連する分布容量を有しており、この分布容量は、ワード線またはビット線の長さの関数として上昇する。選択されたメモリセルに対するプログラミング電流ソースとセンス電流ソースとの間の距離は、特により大きなメモリアレイでは、重要なものである可能性があるので、選択された信号経路にあるワードまたはビット線に関連付けられた対応する負荷容量は、同じく比較的大きいこともある。さらに、読み込みおよび書き込み経路に関連付けられているスイッチング回路素子は、典型的に、全体的な負荷容量に著しく寄与する。この負荷容量は、メモリ装置の速度に悪影響を及ぼす可能性がある。

【0007】

従って、従来のMRAMアレイが示した上記問題に言及する、改善されたMRAMアーキテクチャが必要である。

【0008】

[発明の概要]

本発明が目的とするのは、読み込みおよび/または書き込み動作中に、磁気メモリ回路にあるメモリセルへのアクセス速度を改善する技術である。本発明は、少なくとも一観点では、大きなスイッチング回路素子(例えば、スイッチ、マルチブレクサ(MUX)など)が設けられていることにより、メモリセルと連結されているビット線および/またはワード線への負荷容量を低減できる。なお、上記スイッチング回路は、ビット線およびワード線を通るセンス電流および/またはプログラミング電流を選択的にそれぞれ方向付けるためのビット線およびワード線と、動作可能なように接続されているものである。

【0009】

1つまたは複数のメモリセルの論理状態を感知するための読み込み動作中は、著しくより小さな電流が使用されるので、スイッチを、読み込みおよび書き込みのためにそれぞれ使用される複数の別個の読み込みスイッチおよび書き込みスイッチに分離することによって、読み込みスイッチを、対応する書き込みスイッチよりもかなり小さく作ることができる。より小さなスイッチは、それに関連して容量が著しく低減されており、従って、読み込み動作のスピードが改善される。さらに、プログラミング電流ソースを分散することによって、書き込み動作の速度が著しく改善されることもある。プログラミング電流ソースは、ビット線次元に沿った各データ入力部に対してメモリセルの論理状態を書き込むためのプログラミング電流を、複数の電流ソースに供給する。各電流ソースは、1つまたは複数の対応する書き込みビットスイッチの一群と連結されている。従って、書き込みビット

10

20

30

40

50

スイッチからの負荷容量を、複数の対応する電流ソースに分散できる。このように、1つの電流ソースに全ての負荷容量がかからないので、電流ソースの各々の出力部における容量が低減され、その結果、書き込み動作の速度が改善される。

#### 【0010】

本発明の一観点によれば、磁気メモリ回路は、複数のメモリセルと、1つまたは複数のメモリセルに選択的にアクセスするための、メモリセルと接続されている複数のビット線とを備えている。上記メモリ回路は、少なくとも1つのビット線プログラミング回路と、第1セットのスイッチとを備えている。上記ビット線プログラミング回路は、少なくとも1つのメモリセルの論理状態を書き込むためのプログラミング電流を生成するための電流ソース、および／または、プログラミング電流を戻すための電流シンクとして構成可能である。上記第1セットのスイッチは、メモリセルの少なくとも読み込み動作中は、禁止されており、第1セットのスイッチの少なくとも一部は、メモリセルの書き込み動作中は、選択的に許可されている。第1セットのスイッチの各スイッチは、少なくとも1つのビット線プログラミング回路を、第1制御信号に応じて、ビット線の対応する1つと選択的に連結するように構成されている。メモリ回路は、さらに、少なくとも1つのセンスアンプと、第2セットのスイッチとを備えている。第2セットのスイッチは、メモリセルの少なくとも書き込み動作中は、禁止されており、第2セットのスイッチの少なくとも一部は、メモリセルの読み込み動作中は、選択的に許可されている。第2セットのスイッチの各スイッチは、少なくとも1つのセンスアンプを、第2制御信号に応じて、ビット線の対応する1つと選択的に連結するように構成されている。

10

20

30

#### 【0011】

本発明のこれら、および、その他の目的、特性、および利点は、添付の図に関連して読まれることとなる、その説明的な実施形態についての下記の詳細な説明から明らかになるであろう。

#### 【0012】

##### [発明の詳細な説明]

本発明は、ここでは、例示的な磁気ランダムアクセスメモリ(MRAM)装置について説明する。しかしながら、本発明は、この、または、何らかの特別な磁気メモリ回路、または、アーキテクチャに限定されていない。むしろ、本発明は、より一般的に、磁気メモリ回路にある読み込みおよび／または書き込み信号経路の負荷容量を低減する技術に適用できる。さらに、本発明の実施形態は、ここでは、磁気トンネル接合(MTJ)装置に関連して説明されているが、本発明は、このような装置に限定されず、例えば他の磁気抵抗性メモリ素子などの他の適切な装置も同様に、本発明の磁気メモリアーキテクチャに対して補正して、または、補正せずに採用される。

40

#### 【0013】

当業者には理解されるように、「ワード線」は、一般的に、行または水平方向に配向されており、「ビット線」は、一般的に、列または垂直に方向に配向されていると定義する。しかしながら、ここに記載の本発明の技術は、ワード線および／またはビット線のこの配向または何らかの特定の配向に限定されない。

#### 【0014】

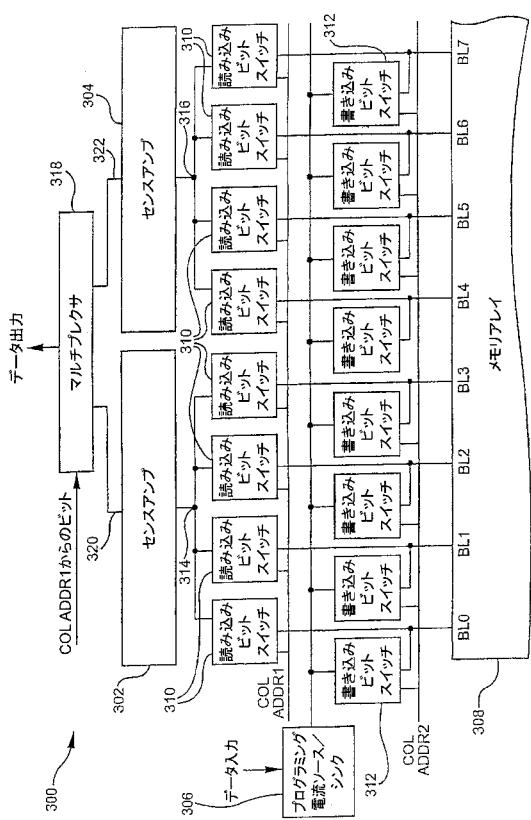

図3に、本発明の技術を実施してもよい説明的な磁気メモリ回路300を示す。この説明的な磁気メモリ回路300は、複数のメモリセル(図示せず)を含むメモリアレイ308を備えている。複数のメモリセルは、従来の方法で(例えば、1T1MTJメモリアレイとして)構成されていてもよく、複数のビット線BL0、BL1、BL2、BL3、BL4、BL5、BL6、BL7などは、メモリアレイ308にあるメモリセルに選択的にアクセスするため、メモリセルと動作可能なように連結されていてもよい。採用されるビット線の数は、少なくとも1つの例としては、メモリアレイ308にあるメモリセルの数および配置に依存している。しかしながら、本発明は、使用されるビット線の数に限定されない。

#### 【0015】

50

高速磁気メモリアーキテクチャを設計するには、任意の読み込み（すなわち、感知）信号経路に関連付けられている容量性負荷を、出来る限り低減することが望ましい。これを達成するための1つの方法は、読み込み信号経路の少なくとも一部を、以下でさらに詳しく説明するように、書き込み信号経路から分離することである。

【0016】

書き込み信号経路は、典型的には、それに関連付けられている大きな負荷容量を有している。その理由の少なくとも1つは、書き込み信号経路と連結されている書き込みビットスイッチ312が存在しているからである。書き込みビットスイッチ312は、各メモリセルの論理状態を書き込むために必要とされることのある大きなプログラミング電流（例えば約2～6ミリアンペア（mA））を処理するに適したようにサイズ決定されている必要がある。書き込みビットスイッチ312は、それぞれ、電圧制御されたスイッチとして機能するトランジスタ（例えばn電界効果トランジスタ（N F E T）など）を備えていてもよい。本発明は、同じく、当業者には理解されるように、代替回路素子（例えばM U X）を書き込みビットスイッチ312を実施するために採用してもよいことを意図するものである。

【0017】

書き込みビットスイッチ312の各々の第1端子（例えば、N F E Tのドレイン端子）は、プログラミング電流ソース／シンク306と連結されていることが好ましい。電流ソース／シンク306は、1つまたは複数の選択されたメモリセルの書き込みのために使用されるプログラミング電流を生成するための出力と、プログラミング電流の方向を制御するデータ入力とを備えていることが好ましい。電流ソース／シンク306は、制御された電流を供給するための電流ソース、または、プログラミング電流を戻すための電流シンクのどちらかとして構成可能である事が好ましい。既に説明したように、プログラミング電流の方向は、メモリセルに書き込まれる論理状態を最終的に決定するものである。書き込みビットスイッチ312の各々の第2端子（例えば、N F E Tのソース端子）は、メモリアレイ308に関連付けられている対応するビット線（例えばB L 0、B L 1、B L 2など）と連結されていることが好ましい。従って、説明的な磁気メモリ回路300では、メモリアレイ308の各ビット線に対して対応する書き込みビットスイッチ312が存在していることが好ましい。

【0018】

説明的な磁気メモリ回路300にある書き込みビットスイッチ312は、プログラミング電流ソース／シンク306の出力を、それに対して提示された1つまたは複数の制御信号に応じて、任意のビット線と選択的に接続するための1つまたは複数の制御入力部を備えているよい。制御信号は、例えば、一部または全体が復号されたアドレス（C O L A D D R 2）を有しているよい。このアドレスは、複数の書き込みビットスイッチ312に対して提示される場合は、例えば任意の書き込みビットスイッチを選択的に起動するための書き込みビットスイッチ312に含まれている復号器などの回路素子（図示せず）によってさらに復号されているよい。このC O L A D D R 2アドレスは、書き込みビットスイッチ312の少なくとも一部が書き込み動作中だけ起動（すなわち許可）されているように、書き込み信号または代替信号または複数の代替信号を含んでいることが好ましい。このような復号素子が書き込みビットスイッチ312に組み込まれていない場合は、書き込みビットスイッチの外側の別個の復号器（図示せず）が、説明的な磁気メモリ回路300に含まれているよい。代替復号構造は、本発明によって同様に意図されている。

【0019】

本発明の一実施形態では、説明的な磁気メモリ回路300が、1つまたは複数のセンスアンプ302・304を備えている。上記センスアンプ302・304は、読み込み対象となっている対応するメモリセルに近い相対的な近傍に位置している。読み込み対象となっているメモリセルは、メモリアレイ308におけるメモリセルの少なくとも一部を代表している。センスアンプ302・304は、複数の読み込みビットスイッチ310を介し

10

20

30

40

50

てメモリセルと選択的に連結されていることが好ましい。説明的な磁気メモリ回路300における読み込みビットスイッチ310は、書き込みビットスイッチ312から分離されており、既述の書き込みビットスイッチ312と整合して機能することが好ましい。しかしながら、本質的により小さな電流（例えば、約50マイクロアンペア（ $\mu$ A））が、読み込み動作中にメモリセルの論理状態を感知するために使用されるので、読み込みビットスイッチ310の各々は、書き込みビットスイッチ312で使用されるトランジスタよりも明らかに小さなトランジスタ（例えば、N F E T）を備えていてもよい。読み込みビットスイッチのトランジスタは、書き込みビットスイッチのトランジスタよりも少なくとも約4分の1だけ小さくサイズ決定されていることが好ましい。従って、説明的な磁気メモリ回路300では、負荷容量が著しく最小化されている。その理由の少なくとも1つは、ドレインおよび／またはソース拡散が、読み込み信号経路に接続されている読み込みビットスイッチにあるトランジスタに関連付けられているからである。

10

20

## 【0020】

書き込みビットスイッチ312と同様に、読み込みビットスイッチ310の各々は、センスアンプの入力ノード314・316を介してそれぞれセンスアンプ302・304の1つと連結された第1端子と、メモリアレイ308にある対応するビット線（B L 0、B L 1など）と連結された第2端子とを備えている。読み込みビットスイッチ310は、1つまたは複数の制御入力部を備えている。この制御入力部は、制御入力部に対して提示された1つまたは複数の制御信号に応じて、対応するセンスアンプを、このセンスアンプに関連付けられている任意のビット線と選択的に接続するためのものである。制御信号は、例えば、全体または一部が復号されたアドレス（C O L A D D R 1）を有してもよい。このアドレス（C O L A D D R 1）は、複数の読み込みビットスイッチ310に提示される場合は、任意のスイッチを選択的に起動するための読み込みビットスイッチ310に含まれる回路素子（図示せず）によってさらに復号されていてもよい。このC O L A D D R 1アドレスは、読み込み動作中だけ読み込みビットスイッチ310が起動（すなわち、許可）されるように、読み込み信号または代替信号または複数の代替信号を含んでいることが好ましい。

20

30

## 【0021】

書き込みビットスイッチ312に関連して既に説明したように、読み込みビットスイッチ310が復号回路素子を備えていない場合、読み込みビットスイッチ310の外側の復号器（図示せず）が、アドレスC O L A D D R 1を復号するために、メモリアーキテクチャ300に含まれていてもよい。同じ復号器は、書き込みビットスイッチ312および読み込みビットスイッチ310の1つまたは複数を選択するための制御信号を生成するように構成可能であってもよい。

40

## 【0022】

説明的な磁気メモリ回路300は、複数のセンスアンプ302・304の1つからデータを選択するためのマルチブレクサ318をさらに備えている。マルチブレクサ318は、複数のデータ入力320・322と、少なくとも1つの制御入力と、少なくとも1つのデータ出力とを備えていることが好ましい。2<sup>n</sup>個の入力のために、マルチブレクサは、nビットの制御信号（アドレス）を受信するためのn個の制御入力を備えていることが好ましい。ただし、nは、0を上回る整数である。データ入力320・322の各々は、対応するセンスアンプ302・304の出力とそれぞれ連結されている。マルチブレクサ318は、少なくとも1つの制御入力に提示された制御信号、または、複数の制御信号に応じて、複数の入力の1つからのデータを送信することが好ましい。制御信号は、既述のように、1つまたは複数の読み込みビットスイッチ310を選択するために使用される例えば、C O L A D D R 1アドレスの少なくとも一部を含んでいてもよい。

40

## 【0023】

センスアンプ302・304は、読み込み対象であるメモリセルに対して限定されている（すなわちより近い近傍に配置できる）ことが好ましいので、全体的な読み込み経路の長さ、および、任意のメモリセルと関連付けられている読み込み経路に接続されている回

50

路の累積的な数を低減でき、その結果、負荷容量がさらに最小化される。負荷容量が低減されると、説明的な磁気メモリ回路300の読み込み動作の速度が改善されることが有利である。さらに、説明的な磁気メモリ回路300は、より対称なビット線配線構造である。このことは、差動センスアンプが採用される場合に特に有利である。差動センスアンプが採用されなければ、不都合なことに、ビット線上のノイズが、ビット線と非対称に連結するであろう。対称なビット線配線を使用することの複数の利点は、例えばReohr他の米国特許第6,269,040号(U.S. Patent No. 6,269,040)に記載されており、本願にその内容を含める。

#### 【0024】

既述のように、本発明の重要な一観点は、読み込み信号経路を、書き込み信号経路から分離することである。書き込み信号経路は、一般的に、それと関連した著しく高い負荷容量を有している。従来行われているように、センスアンプを、プログラミング電流ソースと同じスイッチを介して接続すると、読み込み経路およびセンスアンプ入力部に大きな容量的な負荷が生成される。大きな容量的な負荷は、読み込み動作に関連する感知プロセスを減速する可能性がある。代わりに、複数のセンスアンプ302・304は、別個の読み込みビットスイッチ310を介してビット線と接続されている。上述のように、読み込みビットスイッチ310は、プログラミング電流ソース/シンク306と連結されている書き込みビットスイッチ312よりも明らかに小さくサイズ決定されている。各読み込みビットスイッチ310は、約50μA程度のセンス電流を搬送する必要があるだけである。このように、任意のセンスアンプ302・304に繋がる各読み込み経路にかかる負荷は、より小さな読み込みビットスイッチ310の容量、および、選択されたビット線が寄与する容量のみである。

#### 【0025】

さらに、本発明の説明的なメモリ回路300の利点は、プログラミング電流ソース/シンク306と連結されている書き込みビットスイッチ312とセンスアンプ302・304と連結されている読み込みビットスイッチ310との復号を別々に制御できることである。その結果、任意のセンスアンプに接続されているのとは異なる数のビット線を、プログラミング電流ソース/シンク306に接続できる。その結果、センスアンプの数に比べて、電流ソースの数を低減できることが有利である。キャリブレーション目的のためには、より少数の電流ソースがのぞましく、一方、より多数のセンスアンプは、局部增幅を提供することが有利である。局部增幅は、信号ノイズを緩和し、読み込み経路遅延を最小化する。

#### 【0026】

ビット線に対する近傍を保証する助けとなるように、説明的なメモリ回路300にあるセンスアンプは、ある数のビット線のスライスの上部に直接配置されていてもよい。「スライス」という用語は、ここでは、特別な次元(例えば列)に整列された複数のメモリセルのことを言う。センスアンプをこのように配置することで、本質的に等しい読み込み経路の長さと容量性の負荷とを保証する助けとなる。書き込みビットスイッチおよび/またはセンスアンプは、線抵抗によって影響を受けるプログラミング電流の、または、ノイズ、容量性負荷などによって影響を受ける読み込みアクセス時間の制限に応じて、メモリアレイ308の境界に、またはその境界付近に配置できる。

#### 【0027】

メモリアレイ内に配置されたより多数の磁気メモリセルを使用して、充分なプログラミング歩留りを達成するために、メモリセルの論理状態を書き込むために使用されるプログラミング電流は、所望の電流範囲内に本質的に保持されていることが好ましい。良好に定義された電流範囲内になるようにプログラミング電流を制御することは、目標とされたメモリセルだけがプログラムされ、アレイにある目標とされていない他の全てのメモリセルは本質的に妨害されないということを保証する。このように、アレイにある選択されたメモリセルだけが書き込まれ、選択されたメモリセルは、その論理状態を維持するであろう。

10

20

30

40

50

## 【0028】

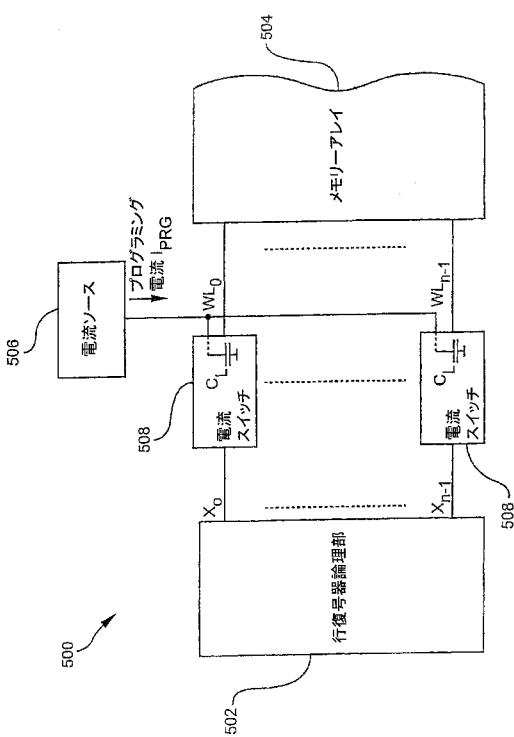

図4に、MRAM装置にある説明的なプログラミング電流経路400を示す。図から明らかのように、説明的な電流プログラミング経路400は、第1電流ソース/シンク402を備えている。この第1電流ソース/シンク402は、第1スイッチ404を介して、導体406の第1端部と接続されている。この導体406は、例えば、メモリアレイにあるワード線(WL)、ビット線(BL)、またはプログラミング線(PRG)を表していてもよい。プログラミング線は、磁気メモリセルの論理状態を書き込むために使用される任意の導体のことである。従って、プログラミング線は、ワード線またはビット線のどちらでもよい。導体406の第2端部は、第2スイッチ408を介して、第2電流ソース/シンク410と連結されていてもよい。電流ソース/シンク402・410は、別の電流シンクに電流を供給するように、または、別の電流ソースからの電流を戻すように、選択的に構成可能であることが好ましい。

10

## 【0029】

導体406の第1端部と連結されている電流ソース/シンク402、および、導体406の第2端部と連結されている電流ソース/シンク410は、ワード線、ビット線またはプログラム線をそれぞれ流れるプログラミング電流 $I_{WL} \cdot I_{BL} \cdot I_{PRG}$ の方向および量を制御することが好ましい。この双方向電流構造は、論理値「0」または論理値「1」を選択されたメモリセルに書き込むために必要である。導体406の1つの端部が、所定の電圧電位(接地でもよい)と固定されている単方向構造も、本発明によって意図される。電流ソース/シンクが複数のスイッチによって共有されていてもよい。

20

## 【0030】

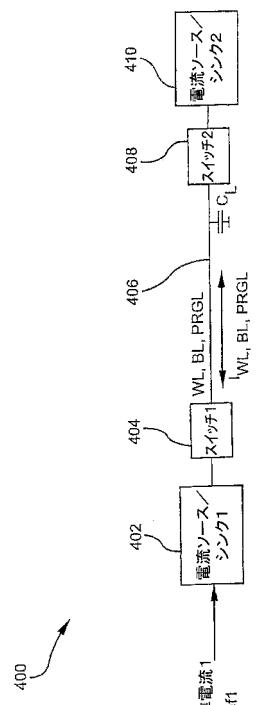

図5に、行復号器502と、行復号器502と連結された複数の電流スイッチ508と、プログラミング電流 $I_{PRG}$ を生成する電流ソース506とを備えるプログラミング回路500を示す。行復号器502は、メモリアレイ504に関連して、n本のワード線 $WL_0 \sim WL_{n-1}$ の1つに沿ったプログラミング電流 $I_{PRG}$ の印加を制御するために使用されてもよい。ただし、nは1を上回る整数である。既述のように、ワード線は、一般的に、行または水平方向に配向されているものと定義し、一方、ビット線は、一般的に、列または垂直方向に配向されているものと定義する。

20

## 【0031】

行復号器502の各出力部 $X_0 \sim X_{n-1}$ は、それぞれに対応する独立した電流スイッチ508を駆動する。電流スイッチ508の各々の第1端子(端子1)は、電流ソース506の出力部と連結されており、各電流スイッチ508の第2端子(端子2)は、メモリアレイ504の対応するワード線( $WL_0 \sim WL_{n-1}$ )と接続されており、各電流スイッチ508の第3端子(端子3)は、行検出器502のそれぞれ対応する出力部 $X_0 \sim X_{n-1}$ と接続されている。電流スイッチ508は、電流ソース506を、行復号器502によって生成される制御信号に応じて、メモリアレイ504の選択されたワード線( $WL_0 \sim WL_{n-1}$ )と選択的に連結する。行復号器502は、一時にただ1つの電流スイッチ508が許可されることを保証する。

30

## 【0032】

プログラミング回路500の1つの欠点は、プログラミング電流パルスの上昇および下降時間が非常に遅いことである。その主な理由は、電流ソース506の出力部に大きな負荷容量が存在しているからである。この大きな負荷容量が生じる原因の少なくとも1つは、電流ソース506の出力部と連結された電流スイッチ508の各々によって寄与される負荷容量 $C_L$ の合計である。既述のように、スイッチ508は、数ミリアンペアのプログラミング電流を処理するために適切にサイズ決定されている必要があり、従って、それに関連して大きな負荷容量 $C_L$ を有している。これらの負荷容量は、プログラミング電流ソース506の出力部に大きなまとまりとなった容量として現れ、電流ソースによって荷電され、同じく、電流シンクによって放電される必要がある。従って、プログラミング電流パルスのそれぞれ上昇および下降時間が著しく長くなり、電力消費も増える。

40

## 【0033】

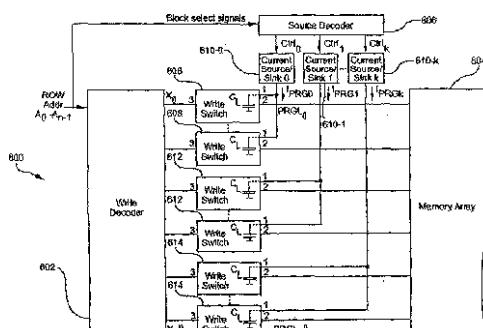

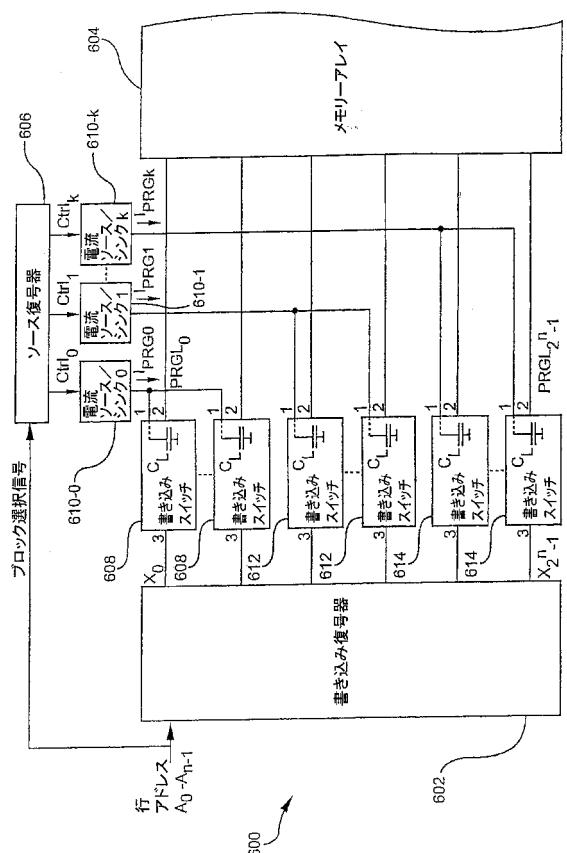

50

図6に、本発明の一観点に基づき、プログラミング電流パルスの上昇および下降時間応答を改善するプログラミング回路600の一例を示す。例示的なプログラミング回路600は、複数のメモリセル（図示せず）を有するメモリアレイ604と、書き込み復号器602とを備え、この書き込み復号器602は、 $n$ ビットの行アドレス（ $A_0 \sim A_{n-1}$ ）を受信するための $n$ 個の入力と、 $2^n$ 個の出力 $X_0 \sim X_{2^n-1}$ とを備えている。ただし、 $n$ は、1より大きい整数である。書き込み復号器602は、入力アドレス $A_0 \sim A_{n-1}$ に応じて、出力 $X_0 \sim X_{2^n-1}$ の1つに制御信号を生成する。本発明と共に使用するために適している復号器は、当業者に知られている。例示的なプログラミング回路600は、ビットまたはワード配向またはその両方に配置されている複数の書き込みスイッチ608・612・614を備え、各下位集合は少なくとも1つのスイッチを含んでいる。他の配向（例えば、対角線の配向）は本発明によって同じく意図されている。書き込みスイッチ608・612・614の各々は、プログラミング電流ソース／シンクと連結された第1端子（端子1）と、メモリアレイ604の対応するプログラミング線（ $PRGL_0 \sim PRGL_{2^n-1}$ ）と連結されている第2端子（端子2）と、書き込み復号器602の対応する出力と連結されている少なくとも1つの制御入力（端子3）とを備えていることが好ましく、書き込みスイッチ608・612・614の合計数は、復号器602の出力の数と等しいことが好ましい。

10

## 【0034】

本発明の一観点によれば、図5に示す電流ソース506の出力部にかかる容量的な負荷を低減するために、つまり、プログラミング電流パルスの上昇および下降時間を短くするために、同じ次元（すなわち、スライス）に沿った書き込みスイッチ608・612・614は、2つまたはそれ以上の下位集合（すなわち、ブロック）に配置されていることが好ましく、各下位集合は、少なくとも1つの書き込みスイッチを含んでいる。例えば、第1下位集合を、書き込みスイッチ608を含むと定義し、第2下位集合を、書き込みスイッチ612を含むと定義し、第3下位集合を、書き込みスイッチ614を含むと定義してもよい。

20

## 【0035】

例示的なプログラミング回路600では、従来は同じ次元の書き込みスイッチと関連付けられているプログラミング電流ソース（図5では506）が、複数の電流ソース／シンク610-0～610-kに分割されている。ただし、kは0を上回る整数である。電流ソース／シンク610-0～610-kは、本質的に相互に一致していることが好ましく、図3に示すプログラミング電流ソース／シンク306と整合するように実施されていてもよい。さらに、電流ソース／シンク610-0～610-kの少なくとも一部は、それと対応するメモリセルに対して近い相対的な近傍に配置されていてもよい。この場合、プログラミング電流経路の長さが短縮され、従って、それに関連する負荷容量がさらに低減される。

30

## 【0036】

各電流ソース／シンク610-0・610-1・610-kは、書き込みスイッチ608・612・614の対応する下位集合とそれぞれ連結されていることが好ましい。各下位集合にある書き込みスイッチの数は、本質的に同じであることが好ましく、従って、書き込みスイッチの負荷容量 $C_L$ 寄与は、電流ソース／シンク間で均等に分散される。例示的なプログラミング回路600は、既述のように、任意の電流ソース／シンクと連結された書き込みスイッチの合計数は、複数の電流ソース／シンクに分散されていてもよいので、特定の電流ソース／シンクの出力に大きな負荷容量がかからないということを保証するように構成されていることが有利である。従って、電流ソース／シンク610-0～610-kの各々は、より少数の書き込みスイッチを駆動し、それゆえ、単一の電流ソース／シンクを採用する場合に駆動する必要がある負荷容量よりも、小さな負荷容量を駆動する。

40

## 【0037】

全ての電流ソース／シンクは、継続的に起動している必要はないので、例示的なプログラ

50

ラミング回路 600 にある電流ソース / シンク 610-0・610-1・610-k の各々は、所望の電流ソース / シンクを、それらに対してそれぞれ提示される制御信号  $C_{tr1_0} \cdot C_{tr1_1} \cdot C_{tr1_k}$  に応じて、選択的に許可するための少なくとも 1 つの制御入力を備えている。制御信号  $C_{tr1_0} \cdot C_{tr1_1} \cdot C_{tr1_k}$  は、例示的なプログラミング回路 600 に含まれるソース復号器 606 によって生成されてもよい。任意の電流ソース / シンクを選択的に起動するための代替回路素子は、同じく、本発明によって意図されているものである。ソース復号器 606 は、行アドレス  $A_0 \sim A_{n-1}$  の少なくとも一部または代替ブロック選択信号を受信するための少なくとも 1 つの入力と、電流ソース / シンク 610-0・610-k の制御入力と連結されている複数の出力とを備えていることが好ましい。

10

## 【0038】

電流ソース / シンク 610-0・610-k と、書き込みスイッチ 608・612・614 と、例示的なプログラミング回路 600 におけるプログラミング線  $PRGL_0 \sim PRGL_{2^n-1}$  を備えるプログラミング電流経路は、図 4 に関連して既に説明したプログラミング電流経路 400 と整合するように構成されていてもよい。従って、図示していないが、プログラミング線  $PRGL_0 \sim PRGL_{2^n-1}$  の各々は、対応する電流ソース / シンクによって終了していることが好ましい。対応する電流ソース / シンクは、制御された電圧電位（例えば、接地）に対する短絡を備えているだけでもよい。双方向電流構造では、電流ソース / シンク 610-0・610-k は、電流ソースまたは電流シンクのどちらかとして選択的に構成可能であってもよい。単方向電流構造では、電流ソース / シンク 610-0・610-1・610-k は、当業者によって理解されるように、対応する群の書き込みスイッチに双方向電流  $I_{PRG0} \cdot I_{PRG1} \cdot I_{PRGk}$  をそれぞれ供給する電流ソースとして構成されていてもよい。

20

## 【0039】

書き込み動作中に、ソース復号器 606 は、選択された書き込みスイッチ（すなわち、書き込み復号器 602 によって許可される選択された書き込みスイッチ）に関連付けられている電流ソース / シンクだけを許可することが好ましい。プログラミング回路 600 は、下位集合のスイッチの数に限定されておらず、任意の下位集合のサイズは、任意の数の書き込みスイッチを基本的に含むことが出来るので、プログラミング電流パルスの上昇および下降時間は、任意のサブセットにおける書き込みスイッチの数および / またはプログラミング回路 600 における下位集合の数を変化させることによって所望通りに制御されてもよい。任意のサブセットまたは複数のサブセットに関連するスイッチの数を、手動、自動（例えば、制御器、または代替制御回路素子（図示せず）によって）、または手動と自動と両方を組み合わせて、本発明のほかの観点に基づいて変更できる。

30

## 【0040】

高精度の書き込み動作を、メモリアレイにある目標とするメモリセルだけに書き込みが成功することと定義してもよい。この高精度の書き込み動作を達成するために、プログラミング電流は、プログラミング電流パルスが選択されたプログラミング線に印加されるとき、厳密に制御されていることが好ましい。プログラミングパルスは、期間が比較的短くてもよく（例えば、ナノ秒（ns）未満）、プログラミング電流経路（図 4 参照）の容量性の負荷  $C_L$  は、速度に関してのみならず、他の要素（例えば、歩留り、信頼性など）に關しても、書き込み動作に対してよりいっそう大きな影響を有していることがある。

40

## 【0041】

再び図 4 を参照すると、容量  $C_L$  は、プログラミング電流経路にある全ての容量のまとめた容量を表している。このプログラミング電流経路は、電流ソースから電流シンクまでに、2 つのスイッチ 404・408 および導体 406 の容量を含んでいる。プログラミング電流パルスのレベルの変化（例えば、電流スパイクなど）は、メモリアレイにある他の目標とされていないメモリセルの論理状態を不都合に妨害する可能性がある。その結果、歩留りと信頼性とが低減される。プログラミング電流パルスのレベルのこのような変化は、容量  $C_L$  が正の供給電圧に、または、正の供給電圧に近い電圧に荷電されている場合

50

に特に生じる可能性がある。正の供給電圧は、VDDのこともあり、従って、例えば大きな電流スイッチ404・408の起動によって突然充電されることもある。

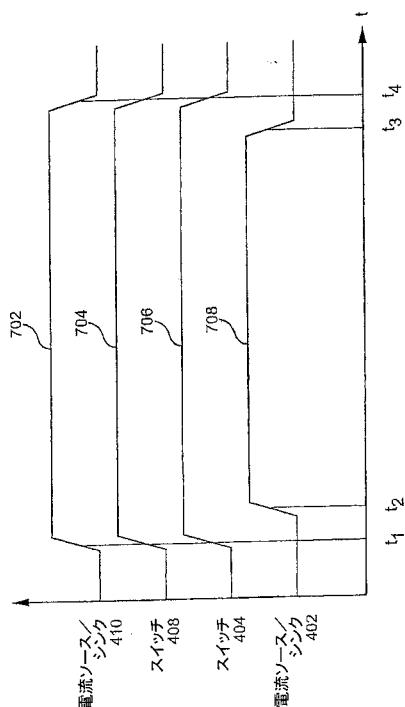

【0042】

プログラミング電流スパイクを低減するために、スイッチ404・408は、図7の例示的なタイミング図に示す説明的な制御信号を用いて許可および/または禁止にされることが好ましい。図7を参照すると、例示的な制御信号702・704・706・708は、それぞれ図4に示す電流ソース/シンク410、第2スイッチ408、第1スイッチ404および電流ソース/シンク402を起動および/または停止するために使用されることが好ましい。代替制御信号も、本願に記載の現在の技術に基づいて、採用してもよい。プログラミング電流(例えば、 $I_{P R G L}$ )は、制御された電流ソースとして構成されていてもよい電流ソース/シンク401から、導体406を通って、電流シンク(例えば、接地への短絡)として構成されていてもよい電流ソース/シンク410へ流れる。

10

20

30

40

【0043】

例えば、第1工程では、電流ソース/シンク410、第2スイッチ408、および第1スイッチ404だけが時間 $t_1$ で起動される。続いて、電流ソース/シンク402が、時間 $t_2$ で起動される。ただし、 $t_2$ は $t_1$ よりも大きい。電流ソース/シンク402は、続いて、プログラミング電流経路を荷電する。プログラミング電流経路は、第1および第2スイッチ404・408と、導体406を備え、 $t_2$ 以降に、休止状態が達成されるまで、指数的に上昇するプログラミング電流を提供する。プログラミング電流経路がその休止状態になるまで荷電するために必要とする時間の量は、プログラミング電流経路に関連する特徴(例えば、分布容量、抵抗などであるが、これに限定はされない)に依存しているであろう。時間 $t_3$ で電流ソース/シンク402が停止される。ただし、 $t_3$ は $t_2$ よりも大きい。プログラミング電流経路に格納された電荷は、接続されたままである電流ソース/シンク410を通って指数的に放電する。プログラミング電流回路を本質的に放電した後、第1スイッチ404、第2スイッチ408および電流ソース/シンク410を時間 $t_4$ で停止できる。ただし、 $t_4$ は $t_3$ よりも大きい。このように、第1および第2スイッチ404・408のスイッチングにそれぞれ関連付けられている電流スパイクは、本質的に回避される。

20

【0044】

磁気メモリ回路および/または本発明の改善されたプログラミング回路の少なくとも一部は、半導体装置に実施されていてもよい。半導体装置は、1つまたは複数のこのような磁気メモリおよび/またはプログラミング回路を備えていてもよい本願で説明した本発明の技術は、個別でも、または組み合わせても、従来の磁気メモリアーキテクチャに対する改良を達成するために使用してもよい。例えば、図6に示す例示的なプログラミング回路を、ビット線プログラミング電流ソース/シンク306と書き込みビットスイッチ312とを有する図3の書き込み回路の代わりに、書き込み経路に関連付けられている負荷容量を低減するために使用してもよい。電流ソースの多様性に対する混乱を避けるために、従来技術は、ビット線次元における各データ入力部に専用の電流ソースを必要とする。これに対し、本発明は、一実施形態では、ビット線次元における各データ入力部のための複数の電流ソース/シンクを必要とする。

30

40

【0045】

本発明の説明的な実施形態は、添付の図を参考にして説明してきたが、本発明は、これらの特定の実施形態に限定されず、当業者によって、添付の請求項の範囲を超えることなく、これに様々な他の変形および補正を行ってもよい。

【図面の簡単な説明】

【0046】

【図1】図1は、従来の磁気トンネル接合装置を示す図式的な図である。

【図2A】図2Aは、従来の交差点メモリアレイの少なくとも一部を示す概略図である。

【図2B】図2Bは、従来の1T1MTJメモリセルアレイの少なくとも一部を説明する概略図である。

50

【図3】図3は、本発明の一観点に基づいて形成された、メモリセルの読み込みおよび/または書き込み用の磁気メモリ回路の一例を示すブロック図である。

【図4】図4は、プログラミング電流経路の一例を説明的に示すブロック図である。

【図5】図5は、磁気メモリアレイにある選択されたメモリセルに対するプログラミング電流の印加を制御するためのプログラミング回路を示すブロック図である。

【図6】図6は、本発明の一観点に基づいて形成された改善されたプログラミング回路の一例を示すブロック図である。

【図7】図7は、本発明の一観点に基づく、磁気メモリ回路における書き込み動作の改善のためのタイミング信号を示すタイミング図である。

【図1】

FIG. 2a Prior Art

FIG. 2b Prior Art

【図3】

【図5】

【図4】

【図6】

【図7】

## 【手続補正書】

【提出日】平成17年8月11日(2005.8.11)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

## 【補正の内容】

【特許請求の範囲】

## 【請求項1】

複数のメモリセルと、

1つまたは複数の上記メモリセルに選択的にアクセスするための、上記メモリセルと連結された複数のビット線(B\_L\_i)と、

少なくとも1つのビット線プログラミング回路(306)と、第1セットのスイッチ(312)と、少なくとも1つのセンスアンプ(302, 304)と、第2セットのスイッチ(310)とを備え、

上記ビット線プログラミング回路は、少なくとも1つのメモリセルの論理状態を書き込むためのプログラミング電流を生成するための電流ソース、および、上記プログラミング電流を戻すための電流シンクの少なくとも1つとして構成可能であり、

上記第1セットのスイッチは、メモリセルの少なくとも読み込み動作中は禁止されており、第1セットのスイッチの少なくとも一部は、メモリセルの書き込み動作中に選択的に許可され、上記第1セットのスイッチ(312)の各スイッチは、少なくとも1つのビット線プログラミング回路(306)を、第1制御信号に応じて、ビット線の対応する1つと選択的に連結するように構成されており、

上記第2セットのスイッチは、メモリセルの少なくとも書き込み動作中は禁止されてお

り、第2セットのスイッチ(310)の少なくとも一部は、メモリセルの読み込み動作中に選択的に許可され、上記第2セットのスイッチ(310)の各スイッチは、少なくとも1つのセンスアンプ(302, 304)を、第2制御信号に応じて、ビット線の対応する1つと連結するように構成されている、磁気メモリ回路(300)。

#### 【請求項2】

上記第1および第2セットのスイッチ(310, 312)の各々は、電界効果トランジスタ(FET)を備えている、請求項1に記載の磁気メモリ回路。

#### 【請求項3】

上記第2セットのスイッチ(310)の各々にあるFETは、第1セットのスイッチ(312)の各々にあるFETよりも少なくとも4分の1小さいようにサイズ決定されている、請求項2に記載の磁気メモリ回路。

#### 【請求項4】

1つまたは複数の上記メモリセルに選択的にアクセスするための、上記メモリセルと連結された複数のワード線(WL)をさらに備え、

上記第1スイッチ(312)の各々は、対応するビット線と連結された第1端子と、少なくとも1つのプログラミング電流ソース/シンクと連結された第2端子と、第1制御信号を受信するための少なくとも1つの制御入力部とを備え、上記第1スイッチの各々は、対応するビット線を、少なくとも1つのプログラミング電流ソース/シンクに、第1制御信号に応じて連結し、

上記第2スイッチ(310)の各々は、少なくとも1つのセンスアンプ(302, 304)の入力部と連結された第1端子と、対応するビット線と連結された第2端子と、第2制御信号を受信するための少なくとも1つの制御入力部とを備え、上記第2スイッチ(310)の各々は、対応するビット線を、少なくとも1つのセンスアンプ(302, 304)の入力部に、第2制御信号に応じて連結する、請求項1に記載の回路。

#### 【請求項5】

上記第1制御信号は、アドレスを有し、

複数の第1スイッチ(312)の少なくとも一部の各々は、制御入力部と連結された復号回路素子を備え、上記復号回路素子は、アドレスを復号し、これに応じて、対応するビット線を、少なくとも1つのプログラミング電流ソース/シンクの出力部に選択的に連結するように構成可能である、請求項4に記載の回路。

#### 【請求項6】

上記第2制御信号は、アドレスを有し、

複数の第2スイッチ(310)の少なくとも一部の各々は、制御入力部と連結された復号回路素子を備え、上記復号回路素子は、アドレスを復号し、これに応じて、対応するビット線を、少なくとも1つのセンスアンプの入力部に選択的に連結するように構成可能である、請求項4に記載の回路。

#### 【請求項7】

アドレスを受信するための少なくとも1つの入力部を有する復号器をさらに備え、上記復号器は、第1および第2制御信号を、上記アドレスに応じて生成するように構成可能である、請求項4に記載の回路。

#### 【請求項8】

上記複数の第1スイッチは、同じ次元の複数の下位集合に配置されており、各下位集合は、少なくとも1つのスイッチを備え、

少なくとも1つのプログラミング電流ソース/シンクは、複数の電流ソース/シンクを備え、上記電流ソース/シンクの各々は、対応する下位集合と連結されており、対応するデータ入力部に割り当てられており、複数の電流ソース/シンクの各々の出力部における負荷容量は、低減されている、請求項4に記載の回路。

#### 【請求項9】

第3制御信号を受信するための少なくとも1つの制御入力部と複数の出力部とを有する復号器をさらに備え、複数の電流ソース/シンクの少なくとも一部における出力部の各々

は、電流ソースの対応する1つの制御入力部と連結されており、復号器は、電流ソースの1つを、制御信号に応じて選択するように構成可能である、請求項8に記載の回路。

【請求項10】

上記複数の電流ソース／シンクの各々は、本質的に相互に一致している、請求項8に記載の回路。

【請求項11】

上記複数の電流ソース／シンクの少なくとも一部は、それに対応するメモリセルに近い相対的な近傍に配置されている、請求項8に記載の回路。

【請求項12】

上記複数のメモリセルの少なくとも一部の各々は、磁気トンネル接合（MTJ）装置を備えている、請求項4に記載の回路。

【請求項13】

上記複数の第1スイッチおよび複数の第2スイッチの少なくとも一部の各々は、電界効果トランジスタを備えている、請求項4に記載の回路。

【請求項14】

少なくとも1つの第2センスアンプと、

マルチプレクサとをさらに備え、上記マルチプレクサは、第3制御信号を受信するための少なくとも1つの制御入力部と、出力部と、複数のデータ入力部とを備え、データ入力部の各々は、センスアンプの対応する1つの出力部と連結されており、上記マルチプレクサは、センスアンプの1つを、第3制御信号に応じて選択するように構成可能である、請求項4に記載の回路。

【請求項15】

複数のメモリセルと、複数のプログラミング線とを含み、上記複数のプログラミング線は、1つまたは複数のメモリセルに選択的にアクセスするために、メモリセルと動作可能なように連結されている、磁気メモリアレイにおける使用のためのプログラミング回路であって、

上記プログラミング回路は、

複数のスイッチと、

複数の電流ソース／シンクと、

第1復号器とを備え、

上記スイッチの各々は、プログラミング線の対応する1つと連結されており、

上記複数の電流ソース／シンクの各々は、同じ次元の1つまたは複数のスイッチの下位集合と連結されており、1つまたは複数のメモリセルの論理状態を書き込むためのプログラミング電流を生成するための電流ソース、および、プログラミング電流を戻すための電流シンクの少なくとも1つとして構成可能であり、

上記第1復号器は、第1制御信号を受信するための少なくとも1つの制御入力部と複数の出力部とを有し、出力部の各々は、スイッチの対応する1つと連結されており、第1復号器は、スイッチの1つを、第1制御信号に応じて選択するように構成可能であり、

複数のスイッチに関連付けられている全体的な負荷容量は、複数の電流ソース／シンク間に分散されており、その結果、電流ソース／シンクの少なくとも1つの負荷容量が低減される、プログラミング回路。

【請求項16】

第2復号器をさらに備え、上記第2復号器は、第2制御信号を受信するための少なくとも1つの入力部と複数の出力部とを有し、出力部の各々は、電流ソース／シンクの対応する1つと連結されており、上記第2復号器は、1つまたは複数の電流ソース／シンクを、第2制御信号に応じて、選択的に許可および禁止することの少なくとも1つのために構成可能である、請求項15に記載のプログラミング回路。

【請求項17】

上記第2制御信号は、第1制御信号の少なくとも一部を有している、請求項15に記載のプログラミング回路。

**【請求項 18】**

上記電流ソース／シンクの各々は、本質的に相互に一致している、請求項15に記載のプログラミング回路。

**【請求項 19】**

上記複数のスイッチは、複数の電流ソース／シンクに本質的に均等に分散されている、請求項15に記載のプログラミング回路。

**【請求項 20】**

少なくとも1つのセンスアンプと、

複数の第2スイッチとをさらに備え、

第2スイッチの各々は、少なくとも1つのセンスアンプの入力部と連結された第1端子と、プログラミング線の対応する1つと連結された第2端子と、第2制御信号を受信するための少なくとも1つの制御入力部とを備え、第2スイッチの各々は、対応するプログラミング線を、第2制御信号に応じて、少なくとも1つのセンスアンプの入力部と連結する、請求項15に記載のプログラミング回路。

**【請求項 21】**

上記第2制御信号は、アドレスを有し、

第2スイッチの少なくとも1つは、制御入力部と連結された復号回路素子を備え、上記復号回路素子は、アドレスを復号し、それに応じて、対応するプログラミング線を、少なくともセンスアンプの入力部と選択的に連結するように構成可能である、請求項20に記載のプログラミング回路。

**【請求項 22】**

請求項1に記載の少なくとも1つの磁気メモリ回路を含む集積回路。

**【請求項 23】**

上記第1セットのスイッチは、同じ次元にある複数の下位集合に配置されており、各下位集合は、少なくとも1つのスイッチを備え、

少なくとも1つのビット線プログラミング回路は、複数の電流ソース／シンクを備え、電流ソース／シンクの各々は、対応する下位集合と連結されており、対応するデータ入力部に割り当てられており、複数の電流ソース／シンクの各々の出力部における負荷容量は、低減されている、請求項22に記載の集積回路。

**【請求項 24】**

上記少なくとも1つの磁気メモリ回路は、

少なくとも1つの第2センスアンプと、

マルチプレクサとをさらに備え、

上記マルチプレクサは、第3制御信号を受信するための少なくとも1つの制御入力部と、出力部と、複数のデータ入力部とを備え、データ入力部の各々は、センスアンプの対応する1つの出力部と連結されており、上記マルチプレクサは、センスアンプの1つを、第3制御信号に応じて選択するように構成可能である、請求項22に記載の回路。

**【請求項 25】**

請求項15に記載の少なくとも1つのプログラミングを含む集積回路。

**【請求項 26】**

上記少なくとも1つのプログラミング回路は、

少なくとも1つのセンスアンプと、

複数の第2スイッチとをさらに備え、

第2スイッチの各々は、少なくとも1つのセンスアンプの入力部と連結された第1端子と、プログラミング線の対応する1つと連結された第2端子と、第2制御信号を受信するための少なくとも1つの制御入力部とを備え、第2スイッチの各々は、対応するプログラミング線を、第2制御信号に応じて、少なくとも1つのセンスアンプの入力部と連結する、請求項25に記載の集積回路。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                      |                                                                                                                                                                                             | International Application No<br>PCT/EP 03/14011                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 G11C11/16                                                                                                                                                                                           |                                                                                                                                                                                             |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                |                                                                                                                                                                                             |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 G11C                                                                                                                    |                                                                                                                                                                                             |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                    |                                                                                                                                                                                             |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal, PAJ                                                                                                  |                                                                                                                                                                                             |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                           |                                                                                                                                                                                             |                                                                                |

| Category *                                                                                                                                                                                                                                       | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                          | Relevant to claim No.                                                          |

| P, X                                                                                                                                                                                                                                             | US 2003/021145 A1 (TRAN LUNG T)<br>30 January 2003 (2003-01-30)                                                                                                                             | 1, 2, 4-7,<br>12, 13,<br>22, 25, 26                                            |

| P, A                                                                                                                                                                                                                                             | the whole document                                                                                                                                                                          | 8-11,<br>14-21,<br>23, 24                                                      |

| A                                                                                                                                                                                                                                                | EP 1 111 619 A (MOTOROLA INC)<br>27 June 2001 (2001-06-27)<br>the whole document                                                                                                            | 1                                                                              |

| A                                                                                                                                                                                                                                                | PATENT ABSTRACTS OF JAPAN<br>vol. 1998, no. 03,<br>27 February 1998 (1998-02-27)<br>& JP 9 306159 A (NIPPON TELEGR & TELEPH CORP &lt;NTT&gt;),<br>28 November 1997 (1997-11-28)<br>abstract | 1                                                                              |

| <input type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                              |                                                                                                                                                                                             | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| * Special categories of cited documents:                                                                                                                                                                                                         |                                                                                                                                                                                             |                                                                                |

| *A* document defining the general state of the art which is not considered to be of particular relevance                                                                                                                                         |                                                                                                                                                                                             |                                                                                |

| *E* earlier document but published on or after the international filing date                                                                                                                                                                     |                                                                                                                                                                                             |                                                                                |

| *L* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)                                                                          |                                                                                                                                                                                             |                                                                                |

| *O* document referring to an oral disclosure, use, exhibition or other means                                                                                                                                                                     |                                                                                                                                                                                             |                                                                                |

| *P* document published prior to the international filing date but later than the priority date claimed                                                                                                                                           |                                                                                                                                                                                             |                                                                                |

| *T* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                              |                                                                                                                                                                                             |                                                                                |

| *X* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                     |                                                                                                                                                                                             |                                                                                |

| *Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |                                                                                                                                                                                             |                                                                                |

| *&* document member of the same patent family                                                                                                                                                                                                    |                                                                                                                                                                                             |                                                                                |

| Date of the actual completion of the international search                                                                                                                                                                                        | Date of mailing of the international search report                                                                                                                                          |                                                                                |

| 10 September 2004                                                                                                                                                                                                                                | 21/09/2004                                                                                                                                                                                  |                                                                                |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5816 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel: (+31-70) 340-2040, Tx: 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                           | Authorized officer<br>Degraeve, L                                                                                                                                                           |                                                                                |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International Application No.

PCT/EP 03/14011

| Patent document cited in search report |    | Publication date |                                  | Patent family member(s)                                                       |  | Publication date                                                                 |

|----------------------------------------|----|------------------|----------------------------------|-------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------|

| US 2003021145                          | A1 | 30-01-2003       | CN<br>EP<br>JP                   | 1399276 A<br>1288959 A2<br>2003059258 A                                       |  | 26-02-2003<br>05-03-2003<br>28-02-2003                                           |

| EP 1111619                             | A  | 27-06-2001       | US<br>CN<br>EP<br>JP<br>SG<br>TW | 6236611 B1<br>1302069 A<br>1111619 A2<br>2001222882 A<br>88805 A1<br>505921 B |  | 22-05-2001<br>04-07-2001<br>27-06-2001<br>17-08-2001<br>21-05-2002<br>11-10-2002 |

| JP 9306159                             | A  | 28-11-1997       |                                  | NONE                                                                          |  |                                                                                  |

---

**フロントページの続き**

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 ゴーグル,ディートマー

アメリカ合衆国 ヴァーモント州 05452 エセックス ジャンクション シャーウッド ス

クエア 125

(72)発明者 ショイアーライン,ロイ エドウィン

アメリカ合衆国 カリフォルニア州 95014 キュパティノ オーチャード ロード 221

45

(72)発明者 レオーア,ウィリアム ロバート

アメリカ合衆国 コネチカット州 06877 リッジフィールド イレヴァン レヴェルズ ロード 111

**【要約の続き】**

おり、第2セットのスイッチの少なくとも一部は、メモリセルの読み込み動作中に選択的に許可される。第2セットのスイッチの各スイッチは、少なくとも1つのセンスアンプを、第2制御信号に応じて、ビット線の対応する1つと選択的に連結するように構成されている。