(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5539104号

(P5539104)

(45) 発行日 平成26年7月2日(2014.7.2)

(24) 登録日 平成26年5月9日(2014.5.9)

(51) Int.Cl.

H01L 27/146 (2006.01)

H01L 31/10 (2006.01)

F 1

H01L 27/14

H01L 31/10A

A

請求項の数 9 (全 12 頁)

(21) 出願番号 特願2010-185289 (P2010-185289)

(22) 出願日 平成22年8月20日 (2010.8.20)

(65) 公開番号 特開2011-91367 (P2011-91367A)

(43) 公開日 平成23年5月6日 (2011.5.6)

審査請求日 平成25年8月8日 (2013.8.8)

(31) 優先権主張番号 特願2009-219218 (P2009-219218)

(32) 優先日 平成21年9月24日 (2009.9.24)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 有嶋 優

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 酒井 誠一郎

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】光電変換装置およびそれを用いた撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型の第1の電荷蓄積領域を含む第1の光電変換素子と、

前記第1の光電変換素子に対して第1方向に沿って配置され、前記第1導電型の第2の電荷蓄積領域を含む第2の光電変換素子と、

前記第1の光電変換素子に対して前記第1方向と交わる第2方向に沿って配置され、前記第1導電型の第3の電荷蓄積領域を含む第3の光電変換素子と、

前記第1の光電変換素子にて生じた信号電荷を読み出すためのトランジスタと、が配置された前記第1導電型と反対導電型の第2導電型の半導体領域を含む半導体基板を有する光電変換装置において、

前記第1の電荷蓄積領域と前記第2の電荷蓄積領域との間の前記第2導電型の半導体領域にイオン注入によって形成され、前記半導体基板の深さ方向において前記トランジスタのチャネル部となる部分よりも深くに位置し、前記第2の方向に沿って配され、第1の幅を有する前記第2導電型の第1の半導体領域と、

前記第1の電荷蓄積領域と前記第2の電荷蓄積領域との間の前記第2導電型の半導体領域にイオン注入によって形成され、前記半導体基板の表面へ投影した時に、前記第2導電型の半導体領域の前記トランジスタが配された領域に配置され、前記半導体基板の深さ方向において前記トランジスタのチャネル部となる部分の下部に位置し、前記第1の幅よりも広く、前記トランジスタのチャネル部となる部分の幅よりも広い第2の幅を有する前記第2導電型の第2の半導体領域と、

10

20

前記第1の電荷蓄積領域と前記第3の電荷蓄積領域との間の前記第2導電型の半導体領域にイオン注入によって形成され、前記半導体基板の深さ方向において前記トランジスタのチャネル部となる部分よりも深くに位置し、前記第1の方向に沿って配され、前記第2の幅よりも狭い第3の幅を有する前記第2導電型の第3の半導体領域と、を有し、

前記半導体基板の表面へ投影した時に、前記第1の半導体領域と前記第3の半導体領域は、格子状に配置し、

前記半導体基板の表面へ投影した時に、前記第2の半導体領域は、前記第1の半導体領域が構成する前記格子の辺の一部である光電変換装置。

**【請求項2】**

前記第2の半導体領域は、前記トランジスタのチャネル部となる部分の長さよりも長い長さを有する請求項1に記載の光電変換装置。 10

**【請求項3】**

前記第1の光電変換素子と、前記第2の光電変換素子は、前記トランジスタを共有化していることを特徴とする請求項1または2に記載の光電変換装置。

**【請求項4】**

前記第1方向と前記第2方向は直交する請求項1乃至3のいずれか1項に記載の光電変換装置。

**【請求項5】**

前記第2の半導体領域は、前記第1の半導体領域と接し、前記第3の半導体領域と接する請求項1乃至4のいずれか1項に記載の光電変換装置。 20

**【請求項6】**

前記半導体基板の表面に投影した時に、

前記第1の半導体領域は、前記第2方向に長辺を有し、

前記第3の半導体領域は、前記第1方向に長辺を有し、

前記第2の半導体領域は、前記格子の交差部に設けられている請求項1乃至5のいずれか1項に記載の光電変換装置。

**【請求項7】**

前記第1の電荷蓄積領域と前記第2の電荷蓄積領域との間ににおいて、前記第1の半導体領域が配されていない領域を有する請求項1乃至6のいずれか1項に記載の光電変換装置。 30

**【請求項8】**

前記トランジスタは、リセットトランジスタおよび增幅トランジスタの少なくとも一方のトランジスタであって、

前記第2の半導体領域は、前記トランジスタのチャネル部となる部分の長さよりも長い長さを有する請求項1乃至7のいずれか1項に記載の光電変換装置。

**【請求項9】**

請求項1乃至8のいずれか1項に記載の光電変換装置と、

前記光電変換装置から出力される信号を処理する信号処理回路と、を有する撮像システム。

**【発明の詳細な説明】**

40

**【技術分野】**

**【0001】**

本件は光電変換装置の分離の構造に関する。

**【背景技術】**

**【0002】**

C C D型やC M O S型の光電変換装置は多くのデジタルスチルカメラやデジタルカムコーダーに用いられている。近年、光電変換装置は画素の縮小化がなされており、それによつて隣接の画素への電荷の混合（クロストーク）への対策が検討されている。

**【0003】**

特許文献1では、隣接する画素間での電荷の混合を防ぐための分離用のバリアとなるP

50

型ウエル領域を、光電変換素子のN型ウエル領域に合わせて深い領域に形成する構成が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003-258232号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に開示されているP型のウエル領域では、画素の縮小化に伴い新たな課題が生じうる。それは、画素が縮小された時に、光電変換素子分離用のウエル領域によって光電変換素子の領域が低減し、光電変換素子の感度が低下してしまう可能性があることである。例えば、光電変換素子分離用のウエル領域が、信号電荷に対して障壁となるP型半導体領域の場合、光電変換素子のN型半導体領域を打ち消してしまう。

10

【0006】

また、光電変換素子分離用のP型ウエル領域の幅を狭くすると、P型ウエル領域を形成する際のイオン注入において不純物が所望の深さに注入されない可能性がある。すると、光電変換素子の周辺に光電変換素子の電荷を読み出すためのトランジスタなどが設けられており、光電変換素子分離用のP型のウエル領域にトランジスタが配置される場合において、トランジスタの閾値にはらつきが生じうる。トランジスタの閾値がばらつくと、ダイナミックレンジが狭くなる等のトランジスタ性能の低下が生じてしまう。

20

【0007】

そこで、本発明においては、光電変換素子の感度を維持しつつ、トランジスタの性能低下を抑制することが可能な光電変換装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の光電変換装置は、第1導電型の第1の電荷蓄積領域を含む第1の光電変換素子と、前記第1の光電変換素子に対して第1方向に沿って配置され、前記第1導電型の第2の電荷蓄積領域を含む第2の光電変換素子と、前記第1の光電変換素子に対して前記第1方向と交わる第2方向に沿って配置され、前記第1導電型の第3の電荷蓄積領域を含む第4の光電変換素子と、前記第1の光電変換素子にて生じた信号電荷を読み出すためのトランジスタと、が配置された前記第1導電型と反対導電型の第2導電型の半導体領域を含む半導体基板を有する光電変換装置において、前記第1の電荷蓄積領域と前記第2の電荷蓄積領域との間の前記第2導電型の半導体領域にイオン注入によって形成され、前記半導体基板の深さ方向において前記トランジスタのチャネル部となる部分よりも深くに位置し、前記第2の方向に沿って配され、第1の幅を有する前記第2導電型の第1の半導体領域と、前記第1の電荷蓄積領域と前記第2の電荷蓄積領域との間の前記第2導電型の半導体領域にイオン注入によって形成され、前記半導体基板の表面へ投影した時に、前記第2導電型の半導体領域の前記トランジスタが配された領域に配置され、前記半導体基板の深さ方向において前記トランジスタのチャネル部となる部分の下部に位置し、前記第1の幅よりも広く、前記トランジスタのチャネル部となる部分の幅よりも広い第2の幅を有する前記第2導電型の第2の半導体領域と、前記第1の電荷蓄積領域と前記第3の電荷蓄積領域との間の前記第2導電型の半導体領域にイオン注入によって形成され、前記半導体基板の深さ方向において前記トランジスタのチャネル部となる部分よりも深くに位置し、前記第1の方向に沿って配され、前記第2の幅よりも狭い第3の幅を有する前記第2導電型の第3の半導体領域と、を有し、前記半導体基板の表面へ投影した時に、前記第1の半導体領域と前記第3の半導体領域は、格子状に配置し、前記半導体基板の表面へ投影した時に、前記第2の半導体領域は、前記第1の半導体領域が構成する前記格子の辺の一部である。

30

【発明の効果】

【0009】

40

50

光電変換素子の感度を維持しつつ、トランジスタの性能低下を抑制することが可能な光電変換装置を提供することが可能となる。

【図面の簡単な説明】

【0010】

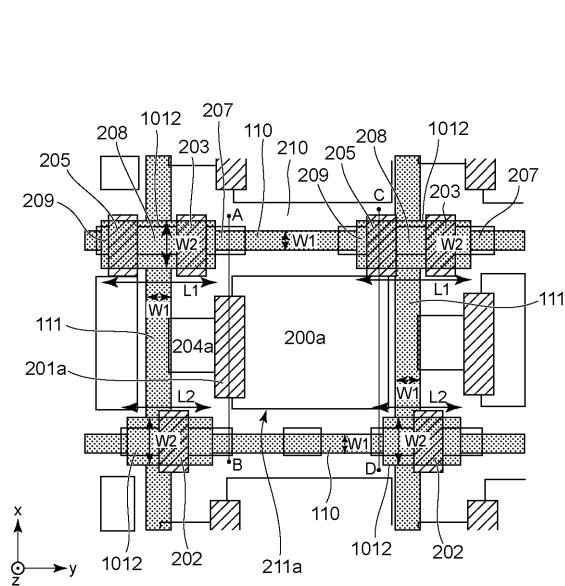

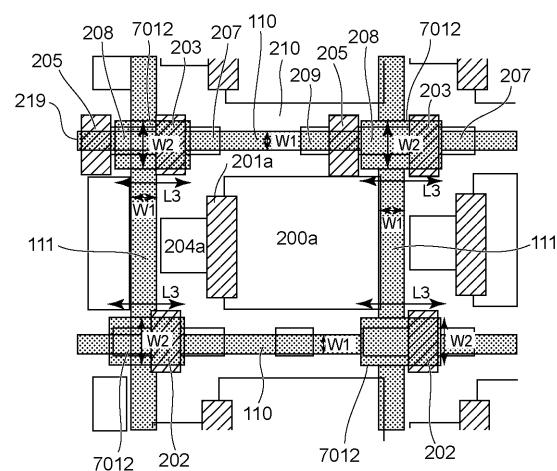

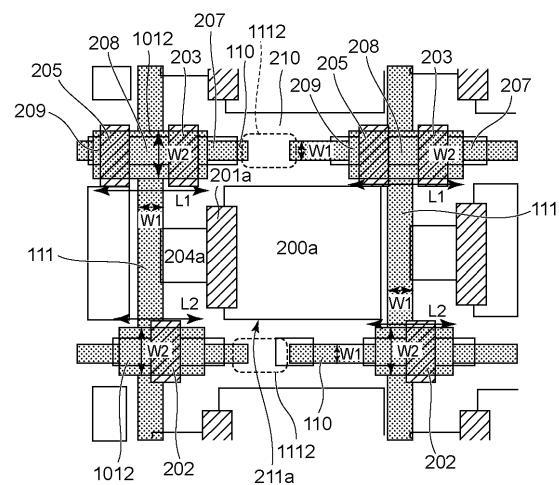

【図1】第1の実施形態における光電変換装置の平面図

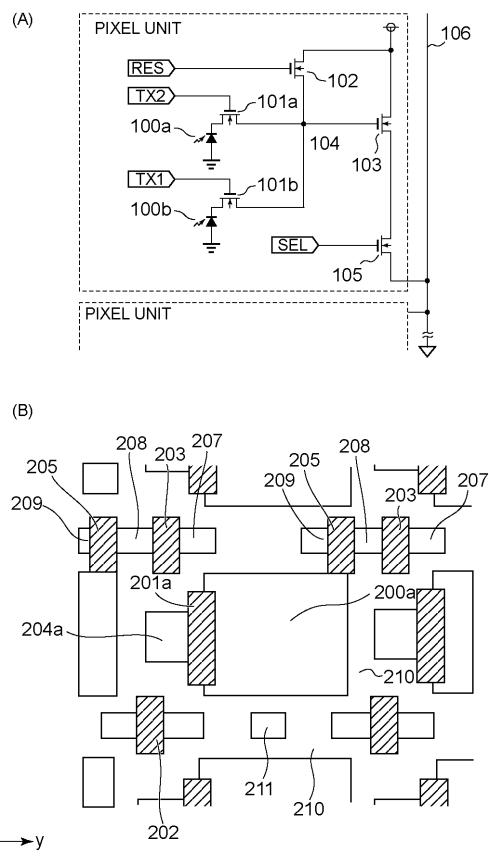

【図2】光電変換装置の画素回路の一例とその平面図

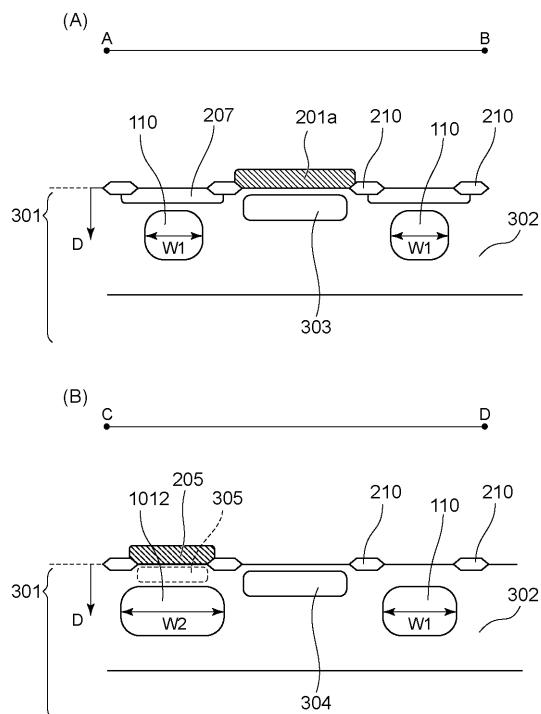

【図3】第1の実施形態における光電変換装置の断面模式図

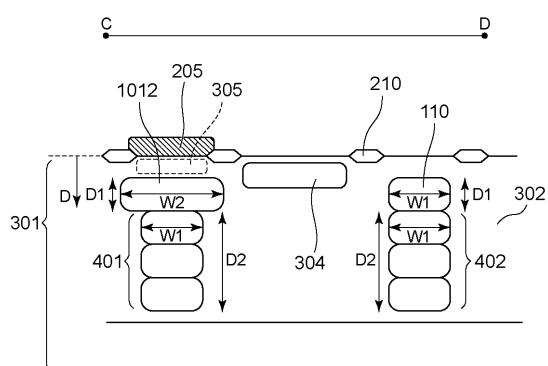

【図4】第2の実施形態における光電変換装置の断面模式図

【図5】第3の実施形態における光電変換装置の平面図

【図6】第4の実施形態における光電変換装置

10

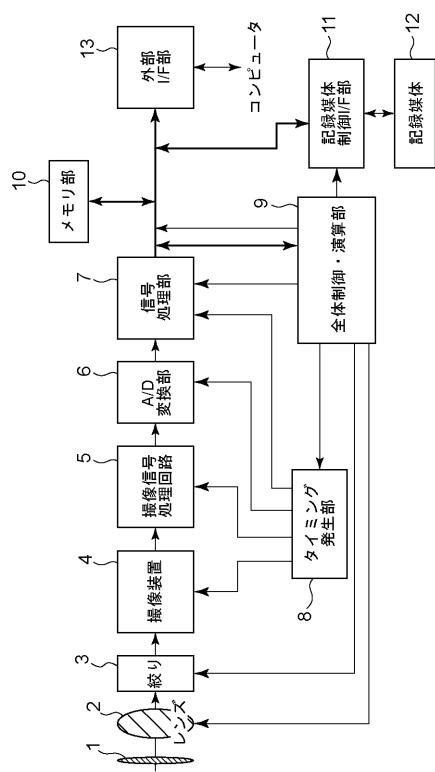

【図7】撮像システムを説明するためのブロック図

【発明を実施するための形態】

【0011】

本発明の光電変換装置は基板と、基板に配された複数の光電変換素子と、光電変換素子にて生じた信号電荷を転送するためのトランジスタと、転送された信号電荷を読み出すための複数のトランジスタと、を有する。複数の光電変換素子は、第1の光電変換素子と、第1の光電変換素子に隣接する第2の光電変換素子とを有する。そして、第1の光電変換素子と第2の光電変換素子との間に配された信号電荷が少数キャリアとなる第1導電型の第1の半導体領域と、転送された信号電荷を読み出すための複数のトランジスタが配された領域に配された第1導電型の第2の半導体領域を有する。この第2の半導体領域は第1導電型の第1の半導体領域よりも幅が広い。

20

【0012】

このような構成を有することで、光電変換素子の感度を維持しつつ、トランジスタの性能低下を抑制することが可能となる。

【0013】

以下、本発明の実施例について図面を用いて詳細に説明する。

【0014】

(画素回路の一例)

まず、本発明が適用される画素回路の一例について説明する。図2(A)は本発明が適用される画素回路の一例を示した回路図であり、図2(B)はその画素回路の1画素分の平面レイアウトを示す平面図である。以下、信号電荷が電子の場合を説明する。

30

【0015】

図2(A)において、画素ユニット(PIXEL UNIT)は、少なくとも2つの画素を有する。画素は少なくとも1つの光電変換素子を有する。図2(A)において、光電変換素子であるフォトダイオード100(100a及び100b)と、転送MOSトランジスタ101(101a及び101b)とを有する。そして、リセットMOSトランジスタ102と、増幅MOSトランジスタ103と、選択MOSトランジスタ105とを有する。つまり、2つの画素、即ち2つのフォトダイオードがリセットMOSトランジスタ102と、増幅MOSトランジスタ103と、選択MOSトランジスタ105とを共有化している。それぞれの転送MOSトランジスタ101はそれぞれの光電変換素子100にて生じた信号電荷を浮遊拡散部104へ転送する。増幅MOSトランジスタ103は浮遊拡散部104の電位に応じた出力を、選択MOSトランジスタ105を介して出力線106へ出力する。増幅MOSトランジスタ103はソースフォロワ回路の一部であり、そのゲート電極は浮遊拡散部104と接続されている。リセットMOSトランジスタ102は、増幅MOSトランジスタ103のゲート電極のノード、すなわち浮遊拡散部104を規定の電位(リセット電位)にリセットする。転送MOSトランジスタ101aには転送制御信号TX1が、転送MOSトランジスタ101bには転送制御信号TX2が供給される。リセットMOSトランジスタ102にはリセット制御信号RESが、選択MOSトランジスタ105には選択制御信号SELが供給される。各制御信号によって上述の信号電荷の読み出しが制御される。光電変換装置には、このような画素ユニットが1次元もしくは2

40

50

次元に配列し、撮像領域を構成している。なお、画素ユニットは2つの画素を有していないなくてもよく、任意の構成が適用可能である。

#### 【0016】

図2(B)は、図2(A)の回路を有する光電変換装置の1画素の平面レイアウトを示す。図2(B)では、図2(A)の101bに対応する光電変換素子200が配置されている。201は転送MOSトランジスタ101bのゲート電極、202はリセットMOSトランジスタ102のゲート電極を示す。203は増幅MOSトランジスタ103のゲート電極、205は選択MOSトランジスタ105のゲート電極、204aは浮遊拡散部である。更に、207は増幅MOSトランジスタのドレイン領域であり、208は増幅MOSトランジスタのソース領域であり、選択MOSトランジスタのドレイン領域である。209は選択MOSトランジスタのソース領域であり図2(A)における出力線106と接続されている。211は半導体領域や半導体基板に電圧を供給するための半導体領域であり、例えばウエルコンタクトである。

#### 【0017】

210は各素子の活性領域を規定する素子分離領域である。本実施形態においては、素子分離領域210にLOCOS (Local oxidation of Silicon) 構造を用いたが、STI (Shallow Trench Isolation) 構造などでもよい。また、素子分離領域210は、信号電荷に対して障壁となるような半導体領域のみが配された構造(拡散分離)などでもよい。素子分離領域210が信号電荷に対して障壁となるような半導体領域のみから構成される場合においては、活性領域は信号電荷に対して障壁となるような半導体領域との境界にて規定されるものとする。図2(B)において、ある活性領域は光電変換素子200aと浮遊拡散部204aとを含み、別の活性領域は各トランジスタのソース領域およびドレイン領域を含む。ここで、画素、即ち画素ユニットは、第1の方向(X軸)および第2の方向(Y軸)に沿って行列状に配されており、第1の方向と第2の方向とは直交するものとする。また、図2(B)において、図2(A)のフォトダイオード101aは光電変換素子200aの第1の方向に沿って配置された隣の光電変換素子に対応する。また、図2(B)において、光電変換素子200aを第1の光電変換素子とし、第1の方向に沿って配置された光電変換素子を第2の光電変換素子とし、第2の方向に沿って配置された光電変換素子は第3の光電変換素子とする。

#### 【0018】

光電変換装置は、図2(A)に示したような回路に限定されるものではなく、更に多くの光電変換素子が増幅MOSトランジスタを共有化するような構成であっても、選択MOSトランジスタを有していない構成であってもよい。また、図2(B)に示したような平面レイアウトに限定されない。また、ここでは信号電荷を電子とし、各MOSトランジスタをNMOSトランジスタとしたが、信号電荷が正孔でPMOSトランジスタであってもよい。また、任意のMOSトランジスタの極性を入れ替えてよい。以下、図面を用いて本発明の実施形態を説明する。

#### 【0019】

##### (第1の実施形態)

本実施形態の光電変換装置について、図1及び図3を用いて説明する。まず、図1(A)は図2(B)の平面図に対応した平面図である。

#### 【0020】

図1では、説明のため、光電変換素子の分離として機能しうる信号電荷に対して障壁となるP型の半導体領域が配置される領域を、図2(B)の平面レイアウトに重ねて示したものである。実際には、P型半導体領域は半導体基板内部に配置されており、図1では半導体基板の表面に各構成を投影した形状を示している。光電変換素子分離として機能しうるP型の半導体領域は、素子分離領域210にも配置されうる。そして、光電変換素子の分離として機能しうるP型の半導体領域は、第1の半導体領域110と、第3の半導体領域111と、第2の半導体領域1012とを含む。第1の半導体領域110は、第2の方向に沿って配置され、光電変換素子200aと第1の方向に隣に配置されている。つまり

10

20

30

40

50

、第1の半導体領域110は、第1の光電変換素子と第2の光電変換素子との間に配置されている。第3の半導体領域111は、第1の方向に沿って配置され、光電変換素子200aと第2の方向に隣に配置されている。つまり、第3の半導体領域111は、第1の光電変換素子と第3の光電変換素子との間に配置されている。半導体基板の表面に配置を投影すると、第1の半導体領域110と第3の半導体領域111とは格子状に配されている。第2の半導体領域1012は、転送された信号電荷を読み出すためのトランジスタが配置された領域に配され、各トランジスタのゲート電極の下部に配されている。また、図1において、第2の半導体領域1012は、各トランジスタのチャネル部と、ソース領域と、ドレイン領域とに渡って配置されている。第1の半導体領域110及び第3の半導体領域111は、幅W1を有する。そして、第2の半導体領域1012は、トランジスタのチャネル部に対応して、チャネル部よりも幅広の幅W2を有し、チャネル部のチャネル長よりも長い長さL1あるいは長さL2を有する。このような構成によって、トランジスタのチャネル部に第1あるいは第3の半導体領域の端部がかかることがなく、トランジスタのチャネル部に一定の第2の半導体領域が配置される。よって、トランジスタの閾値ばらつきの発生が低減される。つまり、隣接する光電変換素子への信号電荷の流入を抑制しつつ、光電変換素子とトランジスタの特性とを維持することが可能となる。

#### 【0021】

なお、第2の半導体領域1012の幅W2は、対応するトランジスタのチャネル幅方向に平行であり、本実施形態では第1の方向に平行である。また、幅W2は、対応するトランジスタのチャネル幅より広い。また、第2の半導体領域1012は、長さL1及び長さL2を有しており、これは対応するトランジスタのチャネル長方向に平行であり、本実施形態では第2の方向に平行である。長さL1及び長さL2は任意であり、少なくとも対応するトランジスタのチャネル長よりも長ければよい。また、本実施例における転送された信号電荷を読み出すためのトランジスタとは、增幅トランジスタ、選択トランジスタ、リセットトランジスタである。

#### 【0022】

次に、図3を用いて、図1に対応する光電変換装置の断面模式図を説明する。図3(A)は図1のAB線に沿った断面模式図であり、図3(B)は図1のCD線に沿った断面模式図である。図3において図1と同様の構成には同一の符号を付し、説明を省略する。

#### 【0023】

図3(A)及び図3(B)において、301はN型の半導体基板であり、302はP型の半導体領域である。半導体基板301は、半導体基板の上にエピタキシャル層を有する構成なども含むものとする。303は、転送トランジスタのゲート電極201aの下部に形成されるチャネル部を示し、304は図1の光電変換素子200aの電荷蓄積領域となるN型半導体領域である。305は選択トランジスタのゲート電極205の下部に形成されるチャネル部である。トランジスタのチャネル部とはトランジスタが動作している時にチャネルが形成されうる領域を示す。矢印Dは半導体基板301の深さ方向を示す。

#### 【0024】

図3(A)及び図3(B)において、第1の半導体領域110は幅W1、深さ方向の長さD1を有し、第2の半導体領域1012は幅W2、深さ方向の長さD1を有する。図3(A)に示すように、トランジスタのソース領域あるいはドレイン領域を通るAB線断面においては、ドレイン領域207の下部に第1の半導体領域110が配置されている。一方、図3(B)に示すように、選択トランジスタのゲート電極205を通るCD線断面においては、選択トランジスタのゲート電極205の下部に第2の半導体領域1012が配置されている。第2の半導体領域1012は選択トランジスタのゲート電極205の下部に形成されるチャネル部305よりも幅が広く、またチャネル部305よりも下部に配置されている。このような構成によって、トランジスタの閾値ばらつきの発生が低減可能となる。

#### 【0025】

チャネル部よりも半導体基板の深い位置に対してイオン注入を行う場合、イオンビーム

10

20

30

40

50

の特性により注入されるイオンの入射角がばらついてしまう場合がある。微細パターンを形成する際に斜めに入射されるイオンの一部は、高アスペクト比のフォトレジストの開口端を通過したり、フォトレジストの側壁で反射したりし、所定の注入エネルギーよりもエネルギーを損失した状態で半導体基板に進入する。このようなエネルギーを損失したイオンは所望の深さに達しない。

#### 【0026】

ここで、もし、チャネル部の下部に配置されうるP型の半導体領域1012を、チャネル幅より細いパターンで形成すると、上述の理由により、所望の深さに達せず、チャネル部にP型の半導体領域が形成されてしまう場合が生じうる。このわずかに配置されるP型半導体領域によって、P型半導体領域302の濃度が向上し、N型のMOSトランジスタの閾値を上げてしまう場合がある。例えば、リセットMOSトランジスタの閾値が上昇すると、浮遊拡散部をリセットすることが困難となる。また、例えば增幅MOSトランジスタの閾値が上昇すると、信号出力時のダイナミックレンジが狭くなる。ここで、チャネル部の下部に配置される半導体領域1012はチャネル部よりも幅広くすることで、エネルギーを損失したイオンが注入されることを抑制することが可能となる。

10

#### 【0027】

なお、本実施形態の光電変換装置は、公知の半導体製造技術によって、例えば、図1に示す第1～第3の半導体領域が配置される領域が開口されたフォトレジストマスクを用いて、イオン注入することによって形成可能である。また、第2の半導体領域と重複する領域を除く第1の半導体領域及び第3の半導体領域を形成し、第2の半導体領域を別の工程で形成してもよい。

20

#### 【0028】

また、本実施形態において、隣接画素への信号電荷の混入量を一定にするため第1の半導体領域110と第3の半導体領域111とは同一の幅W1を有しているが、素子の配置によっては、異なる幅を有する場合もありうる。周囲の画素への信号電荷の漏れ量を一定にすることで、画像信号の補正処理を容易にすることが可能である。なお、第3の半導体領域111の幅は、隣接する浮遊拡散部204の寄生容量を増大させないように設定されると好ましい。

#### 【0029】

また、第2の半導体領域は格子状に配置された第1の半導体領域と第3の半導体領域との交点に配置されることが望ましい。すなわち、転送された信号電荷を読み出すためのトランジスタが、格子状に配置された第1の半導体領域と第3の半導体領域との交点に配置されることが望ましい。このような配置によって、光電変換素子と他の素子との配置の対称性を向上させることができるとなる。また、このような配置によって、周囲の画素への信号電荷の漏れ量のばらつきを低減することができる。

30

#### 【0030】

以上の構成によって、光電変換素子の感度を維持しつつ、トランジスタの性能低下を抑制することが可能な光電変換装置を提供することができる。

#### 【0031】

(第2の実施形態)

40

本実施形態の光電変換装置について図4を用いて説明する。図4は図3(B)に対応する断面模式図であり、図3(B)と同様の構成には、同一の符号を付し、説明を省略する。

#### 【0032】

本実施形態の光電変換装置は、第1の実施形態に比べて、光電変換素子の分離として機能しうる半導体領域が複数からなることが特徴である。つまり、図4において、第2の半導体領域1012の下部に、幅W2よりも狭く、第1の半導体領域と同一の幅W1を有する複数の第4の半導体領域401が配置されている。そして、第1の半導体領域110の下部に、幅W1を有する複数の第5の半導体領域402が配置されている。このような構成においても、トランジスタのチャネル部を覆って第2の半導体領域1012が配置され

50

ているため、トランジスタの性能を維持することが可能となる。

**【0033】**

また、同一の幅W1を有する第4の半導体領域401及び第5の半導体領域402が同一の深さに配置されているため、光電変換素子の深い位置で発生した信号電荷の漏れ量を均一にすることが容易となる。

**【0034】**

なお、本実施形態において、第4の半導体領域401及び第5の半導体領域402は3つ配置されているが、これに限定されるものではない。また、第3の半導体領域1012は1つ配置されているが、複数が深さ方向に配置されていても良い。

**【0035】**

(第3の実施形態)

本実施形態の光電変換装置について図5を用いて説明する。図5は図1に対応する断面模式図であり、図1と同様の構成には、同一の符号を付し、説明を省略する。

**【0036】**

本実施形態の光電変換装置は、第1の実施形態に比べて、第2の半導体領域の長さが短いことが特徴である。つまり、図5において、第2の半導体領域7012は長さL3を有している。長さL3は、対応する図1の第2の半導体領域の長さL1及び長さL2よりも短い。長さL3は、トランジスタのチャネル長よりも長い。つまり、本実施形態の第2の半導体領域7012は、少なくともトランジスタのチャネル部を覆えればよく、図5に示すように、ソース領域あるいはドレイン領域のいずれかを覆っていなくてもよい。また、第1の実施形態においては第2の半導体領域は2つの長さを有していたが、本実施形態においては1つの長さL3のみである。このように長さを1つにすることで、平面レイアウトの対称性が向上し、信号電荷の漏れを均一にすることが可能となる。

**【0037】**

なお、複数のトランジスタのうち、リセットトランジスタ、増幅トランジスタはその閾値の変化が読み出される信号に影響を与えるため、第2の半導体領域によってチャネル部が覆われていることが望ましい。選択トランジスタについては、信号に与える影響が小さいため、第2の半導体領域が配置されておらず、第1あるいは第3の半導体領域が配置されていてもよい。

**【0038】**

(第4の実施形態)

本実施形態の光電変換装置について図6を用いて説明する。図6において、図1と同一の構成には同一の符号を付し、説明を省略する。

**【0039】**

図6の本実施形態の光電変換装置は、幅W1の第1の半導体領域110と、幅W1の第3の半導体領域111と、幅W2の第2の半導体領域1012とを有している。このような構成によって、隣接する光電変換素子への信号電荷の流入を抑制しつつ、光電変換素子とトランジスタの特性とを維持することが可能としている。また、本実施形態の光電変換装置は、第1導電型の半導体領域110を配していない領域1112を有する。このような構成によって、光電変換素子200aから隣接する光電変換素子へ流入する信号電荷を調整することが可能となる。例えば、光電変換素子200aから第1の方向に隣接した光電変換素子へ流入する信号電荷が、光電変換素子200aから第2の方向に隣接した光電変換素子へ流入する信号電荷よりも少ない場合に、それらの信号電荷の量を均一にすることが可能となる。

**【0040】**

また、領域1112を電源あるいはグランドといった固定電位が供給されるソース領域、ドレイン領域、あるいは任意の半導体領域(ウエルコンタクト等)の下部に設けることも可能である。このような構成にすれば、LOCOS等で発生した暗電流をソース領域、ドレイン領域、あるいは半導体領域に排出することも可能である。よって、光電変換素子に流入する暗電流を低減することが可能となる。

10

20

30

40

50

**【0041】****(第5の実施形態)**

本発明の光電変換装置を撮像装置として撮像システムに適用した場合の一実施例について詳述する。撮像システムとして、デジタルスチルカメラやデジタルカムコーダーや監視カメラなどがあげられる。図7に、撮像システムの例としてデジタルスチルカメラに光電変換装置を適用した場合のブロック図を示す。

**【0042】**

図7において、1はレンズの保護のためのバリア、2は被写体の光学像を撮像装置4(光電変換装置)に結像させるレンズ、3はレンズ2を通った光量を可変するための絞りである。6は撮像装置4より出力される撮像信号のアナログ→デジタル変換を行うA/D変換器、7はA/D変換器6より出力された撮像データに各種の補正やデータを圧縮する信号処理部である。そして、図7において、8は撮像装置4、撮像信号処理回路5、A/D変換器6、信号処理部7に、各種タイミング信号を出力するタイミング発生部、9は各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部である。10は画像データを一時的に記憶する為のメモリ部、11は記録媒体に記録または読み出しを行うためのインターフェース部、12は撮像データの記録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体である。そして、13は外部コンピュータ等と通信する為のインターフェース部である。ここで、タイミング発生部やA/D変換器が撮像装置と同一基板上に形成されていてもよい。以上のように、本発明の光電変換装置を撮像システムに適用することが可能である。本発明の光電変換装置を撮像システムに適用することにより、高品質な画像の取得が可能となる。

10

20

**【0043】**

以上述べてきたように、本発明の構成によって、光電変換素子の感度を維持しつつ、トランジスタの性能低下を抑制することが可能な光電変換装置を提供することが可能となる。なお、各実施形態において第1、第3の半導体領域は格子状に配置されているが、素子の配置によるものであり、これに限定されない。また、第1～第3の半導体領域などの半導体領域の深さ方向の長さについても適宜設定可能である。これらの構成および各実施形態は適宜組み合わせ可能である。

30

**【符号の説明】****【0044】**

200a 光電変換素子

201a 転送MOSトランジスタのゲート電極

204a 浮遊拡散部

110 第1導電型の第1の半導体領域

111 第1導電型の第3の半導体領域

1012 第1導電型の第2の半導体領域

【図1】

【図2】

【図3】

【図4】

【 四 5 】

【 四 6 】

【 四 7 】

---

フロントページの続き

(72)発明者 高田 英明

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 小泉 徹

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 川端 康博

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 多賀 和宏

(56)参考文献 特開2004-186408(JP,A)

特開2007-019521(JP,A)

特開2006-319003(JP,A)

特開2005-268814(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H01L 31/10