(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5901771号

(P5901771)

(45) 発行日 平成28年4月13日(2016.4.13)

(24) 登録日 平成28年3月18日(2016.3.18)

(51) Int.Cl.

G06F 12/16 (2006.01)

F 1

G06F 12/16 310A

請求項の数 6 (全 15 頁)

(21) 出願番号 特願2014-528524 (P2014-528524)

(86) (22) 出願日 平成24年8月28日 (2012.8.28)

(65) 公表番号 特表2014-525634 (P2014-525634A)

(43) 公表日 平成26年9月29日 (2014.9.29)

(86) 國際出願番号 PCT/US2012/052687

(87) 國際公開番号 WO2013/033107

(87) 國際公開日 平成25年3月7日 (2013.3.7)

審査請求日 平成27年7月30日 (2015.7.30)

(31) 優先権主張番号 13/222,282

(32) 優先日 平成23年8月31日 (2011.8.31)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595168543

マイクロン テクノロジー, インク.

アメリカ合衆国, アイダホ州 83716

-9632, ポイズ, サウス フェデ

ラル ウエイ 8000

(74) 代理人 100074099

弁理士 大菅 義之

(74) 代理人 100106851

弁理士 野村 泰久

(72) 発明者 プロジェット, グレッグ エー.

アメリカ合衆国, アイダホ州 83686

, ナンパ, アイビー ドライブ 4013

審査官 塩澤 如正

最終頁に続く

(54) 【発明の名称】メモリリフレッシュ法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

其々が複数のページからなる複数のブロックを備えたメモリデバイスの制御方法であつて、

前記複数のブロックのうち、第1のブロックに含まれる第1のページを指定する読み取りコマンドを発行することと、

前記読み取りコマンドが前記第1のブロックに対する所定回数以上の読み取りコマンドか否かを判定することと、

前記読み取りコマンドが前記第1のブロックに対する所定回数以上の読み取りコマンドであると判定された場合に、前記第1のブロック内において特定の一部のページのデータを読み取って、前記一部のページのデータに閾値を超えた数の誤りがあるか否かを判定することと、

前記誤りの数が前記閾値を超える場合、前記第1のブロックに対してリフレッシュ制御を行うための印を付けることと、

を含むメモリデバイスの制御方法。

## 【請求項 2】

前記特定の一部のページは2以上のページからなり、前記2以上のページのいずれか一つのページに前記閾値を超えた数の誤りがあった場合に、前記一部のページのデータに前記閾値を超えた数の誤りがあると判定することを特徴とする請求項1に記載のメモリデバイスの制御方法。

**【請求項 3】**

前記特定の一部のページを含む前記複数のページのデータは其々誤り訂正符号を用いて読み出されるものであって、前記誤り訂正符号により訂正可能となるエラーの数は、前記閾値よりも大きいことを特徴とする請求項 2 に記載のメモリデバイスの制御方法。

**【請求項 4】**

前記印の付けられた前記第 1 のブロックに含まれる前記複数のページのデータをコピーすることと、

コピーされた前記複数のページのデータを再プログラムすることと、

を更に含む請求項 1 に記載のメモリデバイスの制御方法。

**【請求項 5】**

電源投入時に、前記複数のブロックに対して前記印の有無を判定することを更に含み、

前記印の付けられた前記第 1 のブロックに含まれる前記複数のページのデータをコピー

すること及び前記コピーされた前記複数のページのデータを再プログラムすることが共に

前記電源投入時に行われることを特徴とする請求項 4 に記載のメモリデバイスの制御方法

。

**【請求項 6】**

前記コピーされた前記複数のページのデータを再プログラムした後に、前記第 1 のブロ

ックに付けられた前記印を取り除くことを更に含む請求項 4 に記載のメモリデバイスの制

御方法。

**【発明の詳細な説明】**

10

**【技術分野】****【0001】****<優先権出願>**

本出願は、2011年8月31日に出願された米国特許出願第13/222,282号

に基づく優先権の利益を主張するものであり、それが参照によりその全体において本願に組み込まれる。

**【背景技術】****【0002】**

種々のコンピュータシステムおよび電子機器は、不揮発性メモリを用いる。言い換れば、電力が切断されているときでもメモリは記憶されたデータを失わない。これらの不揮発性メモリは再プログラムされ、読み取られ、電子的に消去されることが可能であり、デジタルオーディオプレーヤにおける音楽、デジタルカメラにおける画像、および携帯電話における構成データなどの種々のデータを記憶するのに適している。このようなメモリは、名前の由来の1つが、それが再プログラムされる前に1ブロックのメモリセルの内容を消去するためにフラッシュ作動が使用されることにある、フラッシュメモリとして一般に知られるデバイスを備える。この種類のメモリは、コンパクトフラッシュ（登録商標）メモリカード、USBフラッシュメモリドライブ、および他のこのようなデバイスなどの製品における民生用として包装されることが多い。

30

**【0003】**

フラッシュメモリは、典型的に、いくつかのセルからなり、それぞれが少なくとも2つのデータ状態のうちの1つに対してプログラム可能であり、ここで各データ状態は、1桁（例えば、1ビット）または複数桁のデータなどのデータ値に相当し得る。典型的なフラッシュメモリセルは、メモリセルのソースとドレイン領域との間の電気伝導を制御する浮遊ゲートまたは電荷捕獲などの電気的に遮蔽された電荷貯蔵構造を有する電界効果トランジスタからなる。データは、電荷貯蔵構造に記憶された電荷により表され、伝導性において結果として生じる変化は、ソースとドレイン領域との間で認められる。

40

**【0004】**

電荷貯蔵構造は、メモリセルのソースおよびドレイン領域から制御ゲートを分離する。電荷貯蔵構造上に記憶された電子は、トンネル酸化物などの誘電体により、制御ゲート、ドレイン、およびソースから電気的に絶縁される。メモリセルが特定の電圧を制御ゲート

50

上に設置することにより読み取られる場合、デバイスのソースとドレイン間の電気インピーダンスは、メモリセルの効果的な閾値電圧 ( $V_t$ ) に依存して、電流が流れることを許すか許さないかのどちらかになるであろう。貯蔵された電荷は、制御ゲートにより生成された電界を部分的に無効にするかまたは修正し、メモリセルの効果的な閾値電圧 ( $V_t$ ) における変化をもたらす。メモリセルが、1 または 0 の値などの特定のデータ値に相当する特定のデータ状態にあるかどうかを判定するために、制御ゲートに印加された特定の電圧に応じた電流の有無が感知され用いられ得る。

#### 【0005】

いくつかのフラッシュメモリセルは 3 以上のデータ状態のうちの 1 つに対してプログラム可能であり、マルチレベルのメモリセルと呼ばれることが多い。例えば、4 つの状態のうちいずれかに対してプログラム可能なマルチレベルのメモリセルは、1 セルあたり 2 ビットのデータを記憶することができ、それにより従来のシングルビットのメモリセルに関して記憶可能なデータ量が二倍になる。10

#### 【0006】

メモリセルは、典型的に、行と列の 2 次元配列に設置され、行のメモリセルは、ワード線と呼ばれることが多いアクセス線を介して結合され、また列のメモリセルは、データ線と呼ばれることが多いデータ線に結合される。読み取り用の所定のメモリセルの選択か、プログラミング用（「書き込み」と呼ばれることがある）の所定のメモリセルの選択かのどちらかを行うために、データ読み取りやプログラムの機能中にワード線とビット線が使用される。20

#### 【0007】

メモリセルは、宇宙線や読み取り誘起干渉などの記憶されたデータの正確さに影響し得る種々の要因、およびフラッシュメモリセルの電荷貯蔵構造上に貯蔵された電荷を変更し得る他の要因を受けやすい。導体および絶縁体の誘導電場または磁界、容量結合、および有限抵抗も、ビット線とワード線との間に望ましくない結合あるいは干渉をもたらし得る。。

#### 【0008】

これらの要因のうちのいずれかは、メモリセルの読み取りの正確さを減少し得る。可能なデータ状態の数が増加するにつれて、隣接データ状態間の差異を正確に識別するのがより難しくなるため、これらのような要因は、1 メモリセルあたり 2 つ以上の可能なデータ状態を有するマルチレベルのメモリにおいてなおさら重要になり得る。30

#### 【図面の簡単な説明】

#### 【0009】

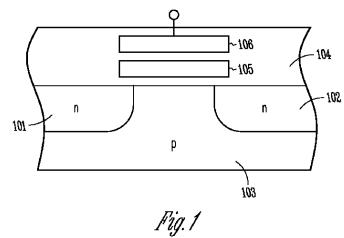

【図 1】本発明のいくつかの実施形態を実行するために用いられてもよい、不揮発性メモリセルの横断面図である。

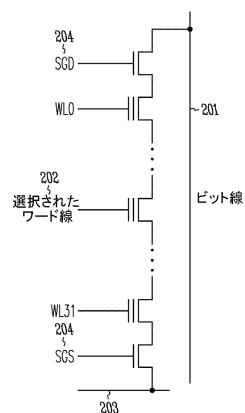

【図 2】本発明のいくつかの実施形態と一致する N A N D フラッシュメモリ構造における不揮発性メモリセルのストリングの概観図である。

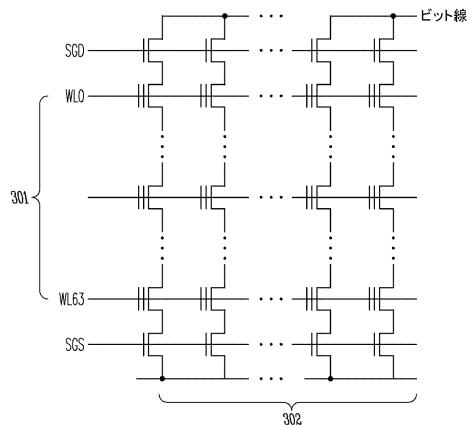

【図 3】本発明のいくつかの実施形態と一致する、1 ブロックの N A N D フラッシュ不揮発性メモリの概観図である。

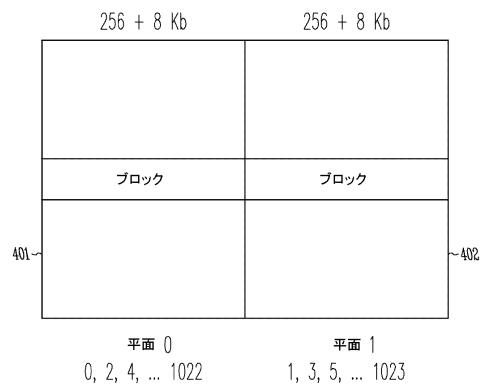

【図 4】本発明のいくつかの実施形態と一致する、不揮発性メモリのブロック図である。40

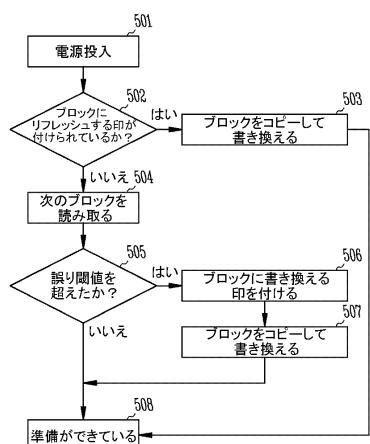

【図 5】本発明のいくつかの実施形態と一致する、電力循環に基づく不揮発性メモリリフレッシュ法を示すフローチャートである。

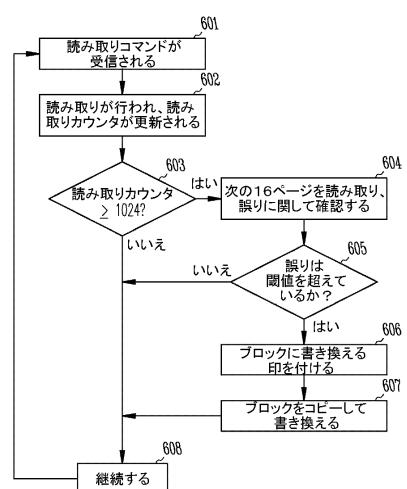

【図 6】本発明のいくつかの実施形態と一致する、バックグラウンド不揮発性メモリリフレッシュ法を示すフローチャートである。

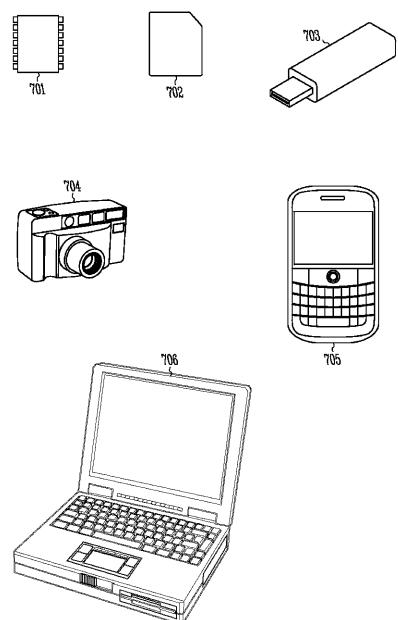

【図 7】本発明のいくつかの実施形態と一致する、不揮発性メモリリフレッシュ法を用いるように動作可能な種々のデバイスを示す。

#### 【発明を実施するための形態】

#### 【0010】

以下の本発明の実施形態の例の詳細な説明において、図面および解説の手段により、特定の本発明の実施形態の例に対する参照がなされる。これらの例は、当業者が本発明を実50

施し、種々の目的または実施形態にどのように適用されることができるかを図示するために役立つように十分に詳細に説明される。本発明の他の実施形態が存在し、本発明の範囲内であり、および論理的、機械的、電気的、および他の変更は、本発明の主題および範囲を逸脱することなくななることができる。本願に記載の本発明の種々の実施形態の特徴または限定は、しかしながら、それらが組み込まれる実施形態の例において不可欠であり、本発明の他の実施形態または本発明を全体として制限せず、および本発明、その要素、動作、および適用に対するいかなる参照も、本発明を全体として制限せず、これらの実施形態の例を画定する役割のみを果たす。以下の詳細な説明は、したがって、本発明の種々の実施形態の範囲を限定せず、これは添付の特許請求の範囲によってのみ画定される。

## 【0011】

10

図1は不揮発性メモリセルの一実施例を示す。ソース101およびドレイン102はP型の半導体材料などの基盤(基板)103の上に形成される。ソース101、ドレイン102、および基盤103は、いくつかの実施形態においてシリコンからなり、リン、ヒ素、またはアンチモンなどの五価電子を有するドーパントによりシリコン内の電子濃度が高まり、またはボロン、ガリウム、インジウム、またはアルミニウムなどの三価電子を有するドーパントにより正孔濃度が高まる。ドーパントは、典型的に、少量、添加され、質量が制御されて、半導体材料における所望の正孔濃度または電子濃度を引き起こし、その結果、ソース101やドレイン102などに余剰の電子が存在する場合には、N型材料となり、基盤材料(基板材料)103などに過剰な正孔が存在する場合には、P型材料となる。

20

## 【0012】

その中に浮遊ゲート105などの電荷貯蔵構造が埋め込まれ、金属または導電ポリシリコンなどの導体からまたは(例えば、窒化物材料から形成される)電荷捕獲から製造される絶縁層104を形成するために、酸化シリコン(SiO<sub>2</sub>)などの絶縁体材料が用いられる。制御ゲート106は同様に、導電材料から形成される。浮遊ゲート105は、メモリセルの別の導電要素には、直接、電気的に結合されないが、絶縁材料104内の「浮遊」である。浮遊ゲート105は、絶縁層104(例えば、二酸化シリコン(SiO<sub>2</sub>)および/または酸化物、窒化物、および酸化物の組み合わせ(ONO))のトンネル誘電部などの絶縁層104の薄い(例えば、10ナノメートル)部分により、ソース101とドレイン102間のP型基盤材料103の領域から分離される。

30

## 【0013】

動作中、電荷貯蔵構造105は、それがメモリセルの他の構成要素から電気的に遮蔽されることにより、電荷を貯蔵できる。電荷貯蔵構造105上で電荷レベルをプログラムするまたは消去することは、電子が、電荷貯蔵構造105を基盤103から分離している誘電体104の一部をトンネルする、ファウラーノルドハイムトンネル現象として知られるトンネリング過程を介して実行され得る。電荷貯蔵構造105を基盤103から分離している誘電体または材料の一部は従来、トンネル誘電体と呼ばれている。

## 【0014】

大部分のフラッシュメモリデバイスは、メモリセルの配列、または動作の読み取り、プログラム、消去に用いられる電気回路に基づき、NORフラッシュまたはNANDフラッシュのどちらかとして分類される。

40

## 【0015】

NORフラッシュメモリにおいてメモリセルをプログラムする一実施例によると、ソース101は接地されることが可能であり、6ボルトなどの供給電圧がドレイン102に印加され得る。一実施形態において、ドレイン電圧はプログラムされるべきメモリセルを識別するのに用いられるビット線を介して印加される。12ボルトなどのより高い電圧がメモリセルの制御ゲート106上にも設定され、正に荷電された制御ゲートに電子を引き寄せるにより、P型基盤内に反転領域を形成させる。ソースとドレインとの電圧差は、P型材料における反転領域との併用で、P型基盤103の反転領域を介して、ソース101とドレイン102との間にかなりの量の電子フローをもたらし、その結果、電子の運動

50

エネルギーと制御ゲート電圧 106 により生成された電界は、トンネル誘電体の全域かつ電荷貯蔵構造 105 の上に高エネルギー（「ホット」としても知られる）電子のファウラー・ノルドハイムトンネル現象をもたらす。

#### 【0016】

電荷貯蔵構造は、それにより、ソース 101 とドレイン 102 の間の基盤 103 の領域上のいずれかの制御ゲートの正電荷の影響に対抗する負電荷を採用し、ワード線を介して制御ゲート 106 に印加されなければならない電圧を引き上げ、P 型基盤材料 103 における反転領域に渡る導電をもたらす。言い換えれば、読み取り動作中に、ワード線の電圧が高電圧（5 ボルトなど）になる場合、プログラム動作中に電荷貯蔵構造 105 上に貯蔵された電子の結果として、セルがより高い閾値電圧によりオンになることはないであろう。制御ゲートに印加された読み取り電圧は、消去されたメモリセルの閾値電圧  $V_t$  より大きいが、プログラムされてしまったセルの基盤 103 における反転領域に渡る伝導が可能になるほど大きくはない。

#### 【0017】

NAND フラッシュにおけるメモリセルのプログラムの一実施例によれば、図 1 のメモリセルのソース 101 とドレイン 102 とが接地されることが可能であり、制御ゲート 106 はおそらく 20 ボルトの電圧になり得る。より高い電圧がメモリセルのソースとドレインとの間で減速する「高温」電子の不在を補うため、この電圧は、NOR フラッシュ法を用いて同一のメモリセルをプログラムするために用いられる 12 ボルトの制御ゲート電圧よりかなり高い。

10

#### 【0018】

NOR フラッシュメモリ電気回路を用いてメモリセルを消去する一実施例によれば、電子の同様のトンネル現象が、メモリセルの電荷貯蔵構造 105 からソース 101 にかけて起こり得る。いくつかの実施形態において、ソース 101 はドレインより深く拡散して消去性能を高める。一実施例によると、正電圧（12 ボルトなど）はソース 101 に印加されることができ、制御ゲート 106 は接地されることができ、消去動作を行うためにドレイン 102 は切断されたままになり得る。ソース 101 上の大きな正電圧は、負に荷電された電子を引き寄せ、それらに絶縁層 104 をトンネルさせ、浮遊ゲート 105 を放置するようにさせる。消去動作中、ソース 101 とドレイン 102 との間には非常にわずかな電流しか流れないと、消去動作の実行はわずかな電流しか必要とせず、比較的少量の電力しか消費しない。

20

#### 【0019】

NAND メモリ構造におけるメモリセルの消去動作の別の実施例によると、ソース 101 とドレイン 102 は浮遊したままになり得るが、基盤材料 103 は、高い正の電圧（20 ボルトなど）になり、負に荷電された電子を引き寄せ、それらを酸化絶縁層 104 を介して電荷貯蔵構造 105 から基盤材料 103 にトンネルさせる。基盤材料 103 におけるチャネル領域が電荷貯蔵構造 105 から電子を受けるため、この方法は「チャネル消去」として知られる場合もある。

30

#### 【0020】

図 1 に示すようなメモリセルは、図 2 に示されるように、ワード線として知られるアクセス線を介して、またビット線として知られるデータ線を介してアドレスされる配列で設置され得る。図 2 は選択的に单一のビット線に結合し得るメモリセルのストリングを含む NAND フラッシュメモリ配列の一部分を示し、ストリング中に示されたメモリセルの各々はワード線 202 を介してさらに選択可能である。

40

#### 【0021】

メモリセル 0 から 31 のストリングは、ストリングの他方の側で、ソース線 203 に選択的に結合し得る。ストリングは、各々の選択トランジスタ 204 の動作を介して、ビット線 201 およびソース線 203 に結合（または、ソース線から遮蔽）され得る。

#### 【0022】

一実施例において、選択された単一レベルのメモリセル 202 の読み取り動作を実行す

50

るために、ワード線と、したがって、選択されたメモリセル 202 の制御ゲートとは、低いが正の電圧レベルに維持されることができる一方、選択されなかつたメモリセルのワード線は十分に高い電圧になることが可能であり、選択されなかつたメモリセルに、個々のメモリセルの電荷貯蔵構造上に存在してもよいいづれの電荷とも無関係に電気を通させる。選択されたメモリセルが荷電されていない電荷貯蔵構造を有する場合、それは制御ゲート上の低い正の電圧レベルの結果として電気を通すであろうが、電荷貯蔵構造が負の電荷を有する場合、それは、セルが電気を通さないように、制御ゲートに印加された低い正の電圧以上にメモリセル 202 の閾値電圧を引き上げるであろう。したがって、メモリセルの電荷貯蔵構造のデータ状態は、例えば、伝導性を監視すること、またはビット線 201 とソース線 203 との間の電流の流れにより判定され得る。

10

#### 【0023】

一実施例において選択されたメモリセル 202 をプログラムするために、ビット線 201 およびソース線 203 は、接地されたビット線 201 およびソース線 203 にストリングを結合する線選択トランジスタ 204 を介して接地され得る。したがって、トランジスタに電気が通るように、選択トランジスタ 204 の制御ゲートは再度、電圧ソースに結合される。プログラムされる過程にないメモリセルの制御ゲートは十分に高い電圧（例えば、10 ボルト）になり、これらのメモリセルの不用意なプログラムを抑制する。選択されたメモリセル 202 の制御ゲートは 20 ボルトなどの十分に高い電圧に結合し、その結果、電子は電荷貯蔵構造上にトンネルする。

#### 【0024】

しかしながら、宇宙線、プログラム誘起外乱、および読み取り誘起外乱などの外部要因は、貯蔵された電荷を徐々に変化させ、読み取り誤りおよび他の否定的影響を発生し得る、プログラムされたメモリセルの閾値電圧  $V_t$  における変動をもたらす。

20

#### 【0025】

図 2 のようなメモリセルのストリングは、そのブロックがフラッシュメモリの最小の消去可能な単位になるようなブロックとして組織化され得る。図 3 は、本発明のいくつかの実施形態を実行するために用いられてもよい 1 ブロックの NAND フラッシュメモリを示す。ここで、301 に示された 64 個の別々のワード線はブロック内のメモリにおける 64 個の別々にアドレス可能な物理的なページを提供し、各ページは誤り訂正符号（ECC）データなどの 4096 バイトのユーザデータと 128 バイトのオーバーヘッドデータ（スペアビットと呼ばれることがある）を記憶し得る。ECC データは、いくつかのメモリ誤りを検出および／または訂正するために用いられ得る。この例示的な実施形態において、したがってブロックは 256 kB のユーザデータに 8 kB のオーバーヘッドデータを加えたものを記憶する。従来のフラッシュメモリデバイスはこのようなブロックを多く含み、例えば、1024 個のブロックのメモリデバイスは、256 MB のユーザデータ記憶を提供する。

30

#### 【0026】

本発明のいくつかの実施形態を実行するために用いられてもよいこのようなメモリデバイスのさらなる詳細な一実施例が、図 3 に示されたブロックなどのブロックの複数の平面図を示す図 4 に示される。ここで、401 で示される平面（プレーン）0 はメモリの偶数のブロックを含む一方、402 で示される平面 1 はメモリの奇数のブロックを含み、合計で 1024 個のブロックを含む。メモリを 2 以上の平面に分割することで、メモリ動作をより早くすることができるが、メモリ動作を、読み取り、プログラム、および偶数、奇数の平面の同時消去に制限し得る。例えば、平面 0 のブロック 0 上で実行された消去動作はまた、平面 1 の消去ブロック 1 も含み、平面 0 のブロック 1022 に対しページをプログラムすることにより、平面 1 のブロック 1023 の対応ページをプログラムすることもできるであろう。

40

#### 【0027】

プログラムミング動作および読み取り動作は、それらが、書き込み動作で、または、読み取り動作のメモリセルのストリングにおける非選択セルに書き込まれつつあるメモリセ

50

ルに対する電圧の印加を含む点において同様であるため、複数の読み取り、プログラム、および／または消去動作は、最終的に、プログラムされたメモリセルのデータ状態に影響し得る。例えば、従来のNANDフラッシュメモリは、1ページあたり数千の読み取りのうちの数十または数百の読み取り後に破損した、そのプログラムされたメモリセルのデータ状態を有することが可能である。

#### 【0028】

いくつかの誤りはメモリに記憶された誤り訂正データを使用して訂正され得るが、より確実で十分なメモリ動作を提供し、マルチビットまたは他の回復不可能な誤りを避けるために発生する読み取り誤りの数を制限することが望ましくなり得る。例えば、図3に示すような64ページまであるメモリブロックは、第64ページが読まれる前に63ページまでを読むためにブロック上で行われる数百万の読み取り動作を有してもよく、その結果、第64ページにおいて回復不可能な読み取り誤りの可能性がかなり大きくなる。10

#### 【0029】

したがって、本発明のいくつかの実施形態は、記憶されたデータの破壊または損失を防ぐために、徐々にメモリをリフレッシュすること（例えば、コピーおよび再プログラム）によりメモリ誤りの発生を減らそうとする。メモリのリフレッシュは、プログラムして以来の時間の経過、読み取り誤り閾値の超過、またはメモリデバイスまたはメモリコントローラの電源投入（直接的な電源投入か、またはメモリデバイスに結合されたメモリコントローラの電源投入などによる間接的な電源投入かのどちらか）などの要因の結果として行われ得る。20

#### 【0030】

さらに詳細な例示的な実施形態において、メモリコントローラは体系的にメモリを読み通して所定の閾値を超えるメモリ誤りのレベルを有するブロックを検出し、誤りが回復不可能になる前にブロックをリフレッシュする。メモリセルがプログラムされる回数を制限することが望ましくなり得るため、不要なプログラムは、最小誤り閾値を超えないければ、データをリフレッシュしないことにより避けられ得る。例えば、誤り訂正データが1ページで24ビットの訂正を可能にする場合は、訂正可能なビットの半分（この例では12ビット）がブロック上で行われたページ読み取り動作における誤りとなると分かったときにのみ、1つのブロックがリフレッシュされてもよい。

#### 【0031】

携帯ゲーム機、スマートフォン、携帯媒体デバイス、および他のそのようなデバイスなどのいくつかのデバイスは、比較的頻繁に、電力循環し（すなわち、電力が供給され、また遮断される）、すべてのメモリをスキャンし潜在的な読み取り誤りを効果的に管理するデバイスの能力が減少する。したがって本発明のいくつかの実施形態は、電力循環を用いて不揮発性メモリ内で誤りを管理し、電力循環を用いるなどして、メモリスキャンおよびリフレッシュ動作をトリガし、非常に細かいレベルでこれらの動作を行う。30

#### 【0032】

単一のメモリ走査およびリフレッシュ動作の影響は、1つの実施例において、ブロックレベルを走査してリフレッシュすることにより最小限にすることが可能となり、その結果、単一のブロックに記憶されたおそらくメガバイトのデータのコピーおよび再プログラムが、例えば、数百ミリ秒のうちに完了し得る。さらなる実施例において、少なくとも1つの異なるブロックは各電源投入に応答して走査され、定期的に必要があれば、確実にメモリのブロックが走査され、リフレッシュされるようにする。40

#### 【0033】

デバイスの動作中、走査は、バックグラウンドタスクとしてブロックごとに継続することが可能であり、いずれかからの必要なリフレッシュが待ち行列に入れられ、バックグラウンドタスクの一部として、またはデバイスの次の電力循環の一部として完了する。電力供給が遮断されると、一実施例におけるデバイス再始動過程は、デバイスからのメモリのブロックに、リフレッシュする印がすでに付けられているかどうかを判定することを含む（例えば、リフレッシュする印が付けられているブロックのリフレッシュが、電力が遮断50

された前に完了していなかった場合など）。この方法は、さらなる実施例において、各ブロックで行われた読み取りを追跡し誤りに関してブロックの数ページを定期的に（例えば、数千の読み取りごとに）確認する追跡メカニズムにより補完され得る。

#### 【0034】

レジスタにおいてまたはメモリ配列自身の一部分などにおいて、誤りに関して確認されつつある最新のブロックの独自性は不揮発性メモリに記憶されることが可能であり、その独自性は、電力循環によりトリガされた、またはバックグラウンドタスクとして行われたブロック確認が、電力循環ごとに同一のブロックで再始動するよりはむしろメモリのすべてを通して進行することを確実にするために用いられ得る。リフレッシュは、ブロックにリフレッシュする印を付けることにより、電力循環を通してさらに追跡されることができ、その結果、待ち行列に入れられたまたは不完全なブロックのリフレッシュは、電源投入シーケンスの一部として、または電源投入シーケンスが完了した後のデバイス動作中に完了され得る。さらなる実施例において、不揮発性メモリは、デバイスまたはブロックごとに読み取られたページの数も記憶することができ、頻繁に再起動するデバイスが、デバイスの電力が遮断されてページ読み取りの数が分からなくなるのではなく電力循環を通して累積された読み取り動作を数えられるようにする。10

#### 【0035】

図5は、本発明の例示的な実施形態と一致する、電源投入シーケンスによりトリガされたメモリ誤りを管理する方法を示すフローチャートである。501において、デバイスに電源が投入され、ブロック情報に関する不揮発性メモリ位置（例えば、レジスタ）を確認すること、またはメモリブロックに関連したフラグを確認することなどにより、メモリのいずれかのブロックがすでにリフレッシュする印が付けられているかどうかを判定することを含む電源投入シーケンスを開始する。502で何らかの方法でメモリブロックにリフレッシュする印が付けられている場合、ブロックに記憶されたデータは、503でコピーされ再プログラムされる。20

#### 【0036】

502でリフレッシュする印が付けられているブロックがない場合、メモリの識別されたブロックが504で読み取られる。いくつかの実施形態において、メモリブロックは、電力循環に基づくメモリリフレッシュにおいて、次の未確認のメモリブロックに対するポインタを検索することにより識別されるため、方法は、各電源投入シーケンスで同一のメモリブロックで再開するよりむしろ、電力循環に渡りメモリを通して進行する。30

#### 【0037】

ブロックが読み取られるとき、1ページあたりの誤りの数はECCを用いて数えられ、505で誤りの数が閾値を超えたかどうかが判定される。さらなる一実施例において、記憶されたECCデータを用いて1ページあたり24ビットまで訂正可能なメモリは、ブロックのいずれのページでも12ビット（例えば、訂正可能な数のビットのおよそ半分）が誤りであり、訂正される必要がある場合、その誤りの許容可能な数を超えている。訂正可能なビット数の3分の1などの他の閾値が、他の実施形態で用いられ得る。閾値は、メモリの寿命内で実施された動作の数またはメモリの年数などの要因に基づき変動し得る。

#### 【0038】

505で誤りの数が読み取り誤りに関して許容可能な閾値を超える場合、ブロックは506でリフレッシュする印を付けられる。その後、ブロックのデータがコピーされ、誤り訂正符号データが訂正可能な誤りを固定させるために用いられ、データは、507で再プログラムされる。デバイスの電源が遮断される、または方法がさもなければコピーおよび再プログラムが507で完了し得る前に妨げられる場合、デバイスが再度、電源投入されると、ブロックのデータが依然としてコピーされ再プログラムされることになるよう（502および503などにおいて）、ブロックには、コピーおよび再プログラムの前にリフレッシュする印が付けられ得る。したがって、この実施例では、506でブロックにリフレッシュする印を付けるフラグは、コピーおよび再プログラムが507で完了するまでは除去されない。4050

**【 0 0 3 9 】**

メモリは、508で、通常の動作の準備ができている。いくつかの実施形態において、電源投入時にメモリブロックにリフレッシュする印が付けられている場合に実行される503のコピーおよび再プログラムは、完了時に準備状態をもたらさないが、その代わり、メモリデバイスの準備ができる前に、少なくとも1つの新しいブロックが準備される504に進み、少なくとも1つの新しいブロックが各通常の電力循環で確実に読み取られるようになり得る。

**【 0 0 4 0 】**

図5に示される方法は、各電力循環で少なくとも1つのブロックが確認またはリフレッシュされるのを確実にするために用いられ得るが、唯一のブロックが、電力循環の一部としてリフレッシュされるように構成されてもよい。典型的なブロックの読み取りは、現状では、いくつかの技術を用いてミリ秒程度かかるが、ブロックの再プログラムは、現状では、数百ミリ秒程度かかるため、数個のブロックの再プログラムは、電源投入シーケンス中に、メモリ有効性を大幅に遅らせ得るであろう。J E D E C フラッシュメモリ標準などのいくつかの標準は、メモリが電源投入後、1秒以内などの所定の期間内に動作の準備をすることを要求する。このため、図5に示された実施例などのいくつかの実施形態は、メモリが正常なアクセス動作の準備ができる前に、唯一のブロックが再プログラムされることを確実にすることなどにより、デバイス開始法の一部として発生するプログラム動作の数を制限し得る。

**【 0 0 4 1 】**

図5の電源投入リフレッシュ法は、さらなる実施例において、図6に示されるようなバックグラウンドメモリリフレッシュ法により補完され得る。このような実施例の1つの方法によれば、601で読み取りコマンドを受信した後に、602で、読み取りが行われ、(例えば、加算カウンタの値を増加させる、または減算カウンタの値を減少させることにより)読み取りカウンタが更新される。読み取りコマンドにより複数ページの読み取りが可能になるため、カウンタは、1ページが読み取られた回数を正しく数えることを確実に維持可能にするなどのコマンドを読み取るのではなく、読み取られたページの数を数え得る。読み取られたページ数が閾値に達すると(例えば、読み取られたページの数が、603で示されるように、1024ページに達すると)、リフレッシュ走査が開始される。例えば、604で、リフレッシュブロックポインタにより識別されたメモリの1ブロックの特定のページ数(例えば、16ページ)が読み取られ、604で、誤りに関して確認される。他の実施形態では、他の適切な読み取り閾値および読み取られるべきページ数が用いられるであろう。

**【 0 0 4 2 】**

604で読み取られたデータの16ページのうちのいずれかが、1ページで12以上の誤りなどの、閾値(すなわち、一定の許容可能な誤りレート)を超える数の誤りを含み、またはECCがそのページ内で24ビットまでを訂正することができる1ページにもっと誤りを含む場合は、リフレッシュブロックポインタにより識別されたブロックは、606で、リフレッシュする印が付けられる。その後、ブロックのデータは、607で示されるように、再プログラム(例えば、ページごとに)に関して、(例えば、バッファメモリに)読み取られコピーされ、訂正されて新しくプログラムされたデータとともにメモリ内に記憶されたデータを更新するなどする。ブロックのデータの再プログラムが成功すると、再プログラムされるべきブロックを示しているフラグは除去される。したがって、次の電力循環が起こる前にそれがうまく完了しない場合、再プログラムされるべきブロックを示しているフラグがまだ設定されることになるため、ブロックのコピーと再プログラムは次の電力循環で繰り返され得る。

**【 0 0 4 3 】**

バックグラウンドリフレッシュ法はその後、608で継続し、ページ読み取りカウンタは(例えば、ゼロに)再設定される。いくつかの実施形態において、読み取られたページの閾値は、特定のメモリ構造での読み取り妨害試験、メモリデバイス密度などの要因、お

10

20

30

40

50

および他のそのような要因に基づくことが可能である。

#### 【0044】

この実施例において、606でブロックにリフレッシュする印が付けられると、ブロック全体がコピーされることになるため、ブロックにおいてリフレッシュ走査の一部として読み取られる必要があるページはもうなくなる。いくつかの実施形態において、摩耗平準化法の一部として、ブロックのデータは物理的なメモリの別のブロック位置に移転し、許容不可能な読み取り誤りレートを有するとすでに判定されたメモリの物理的なブロックのさらなる摩耗を減少させる。

#### 【0045】

この例における606から607のブロックリフレッシュ法は、さらなるリフレッシュ走査読み取りが604で起こる前に完了し、リフレッシュする印が付けられたブロックの累積を防ぐ。別の実施形態において、図6に示される方法は、かろうじて1つのブロックのみがどの時点においてもリフレッシュする印が付けられるように動作する。

10

#### 【0046】

リフレッシュ走査方法の一部として読み取られている最新のブロックおよびページは、いくつかの実施形態において不揮発性メモリからなるメモリに記憶される。したがって、バックグラウンドリフレッシュ法のメモリ位置は電力循環中に失われることはない。さらなる実施例において、バックグラウンドリフレッシュ法の唯一のブロック位置は、それが比較的まれに更新されるため、不揮発性メモリに記憶され、走査するためにブロックの特定の16ページ分を指摘するページ位置は、604で示されるように、揮発性のメモリ（ランダムアクセスメモリまたはRAMなど）に記憶される。デバイスが電力循環を受けると、バックグラウンドリフレッシュ法は、不揮発性メモリで印が付けられたブロックの先頭で再開することになり、ブロックの残りの部分を走査し、バックグラウンドリフレッシュ処理が最近、走査していない不揮発性メモリに進む前に、ブロックのせいぜい一部分の走査を繰り返す。

20

#### 【0047】

誤り閾値レベル、リフレッシュレート、および他のパラメータは、さらなる実施形態において選択されることが可能であり、デバイスのリフレッシュ不足またはリフレッシュ過剰を避ける。訂正不可能な読み取り誤りが発生するかもしれないポイントに誤りを累積させることは、多くの場合、望ましくないものの、不揮発性メモリセルの望ましくない摩耗は、例えば、メモリデバイスの寿命を短縮させるため、不揮発性メモリを頻繁にリフレッシュし過ぎることもまた、多くの場合、望ましくない。

30

#### 【0048】

リフレッシュレートは、ページがリフレッシュされ得る前に発生する訂正不可能な読み取り妨害誤りの機会を減らすためにも選択され得る。一例として、合計で1024ブロック、1ブロックあたり256ページを有する不揮発性メモリを考える。1つのブロックの読み取り妨害が十分可能になるためにそのブロックで1ページあたり100,000の読み取りが必要である場合、1ページあたり100,000の読み取りに、1ブロックあたり256ページを乗じると、ブロック内でおよそ2,600万の読み取りとなり、読み取り妨害イベントが十分に可能になる。1024ブロックで割られた1ブロックあたり2,600万個の読み取りは、読み取り妨害誤りを十分に不可能にするために、1つのブロックが26,000のページ読み取りごとにリフレッシュされるべきであることを示唆する。16,000のページ読み取りごとに1ブロックなどのより速いレートでのリフレッシュは安全性を高める。

40

#### 【0049】

上述のように、読み取りを行うために費やされた時間は、特定のアプリケーションに適することになるリフレッシュパラメータを選択する際、1つの要因となり得る。バックグラウンドリフレッシュ法の一部として、一度にすべてのブロックを読み取るには、現在、約100ミリ秒かかる可能性があり、これは電源投入時には許容できることもあるが動作中には望ましくない。リフレッシュ走査のために一度に単一のページを読み取ることは、

50

現在、約1ミリ秒かかる可能性があるが、16,000のユーザページの読み取りあたり1ブロックがリフレッシュされる上述の実施例においては、64ユーザページの読み取りごとに行われてもよい。同様に、リフレッシュ走査のために16ページを読み取るには、現在、約8ミリ秒かかり、16,000のユーザページの読み取りごとに、ブロック全体をリフレッシュするために、1024のユーザページの読み取りごとに行われてもよい。

#### 【0050】

ブロックの読み取りおよびプログラミングには現在、約500ミリ秒かかるため、誤りに関して確認するためにブロックを読み取る時間と、その後、そのブロックを読み取って再プログラムするための時間を合わせた合計時間は、この実施例では、約600ミリ秒となる。1024ユーザページの読み取りごとのリフレッシュ走査について16ページが読み取られると、そのユーザに対する全影響は、1024ページの読み取りごとに約8msの遅延となり、各ブロックの走査が完了されると不揮発性メモリにおいて活性ブロックアドレスを更新するためには、さらにそれに約2から3msが増加した遅延となるであろう。稀にリフレッシュが必要となる場合には、さらに500msの遅延が発生して、そのブロックをコピーして再プログラムするであろう。これは最も現実的な環境のアプリケーションにおいて一般的でない事象になると予想され、また回復不可能な読み取り誘導メモリ誤りより望ましいため、2分の1の遅延は大体のアプリケーションにとって許容可能でなければいけない。500msの遅延に耐用性がないアプリケーションにとって、ブロックのリフレッシュは、複数の動作に分かれ得る。例えば、16ページを再プログラムする16個の動作は、徐々に、256ページ目のブロックをコピーすることになる一方、いずれかの1つのシステムメモリアクセスに対して約32msの最大遅延のみを発生させる。別の実施例において、メモリデバイスは、通常のメモリアクセスが、ブロックのコピーを妨げ、通常のアクセスを行い、その後、コピーを再開し、通常の動作に対して最小限の遅延を与えるようにしてもよい。

#### 【0051】

いくつかの実施形態においてここに説明されたリフレッシュ法は、フラッシュメモリカードの一部を成すようなメモリデバイスに不可欠なメモリコントローラにより管理され、他の実施形態においてメモリデバイスの外部で実施され、その結果、上述の方法は既成の不揮発性メモリデバイスにより使用され得る。図7は、ここで説明されたような方法を使用するように動作可能な種々のデバイスを示す。

#### 【0052】

701に、フラッシュメモリ集積回路などの不揮発性メモリ集積回路が示される。いくつかの実施形態において、集積回路は積分コントローラを備える一方、他の実施形態において、外部メモリコントローラはメモリリフレッシュ動作を行う。フラッシュメモリカードは同様に702で示され（例えば、セキュアデジタル（SD）メモリカード）、やはり積分コントローラを備えてもよいし、または（例えば、ハードウェア、ファームウェア、および／またはソフトウェアとして具体化されるような）外部コントローラによりリフレッシュされてもよい。

#### 【0053】

多くの場合、サムドライブまたはUSBフラッシュドライブとして知られるフラッシュメモリドライブは703に示され、多くの場合、数十ギガバイト以上の容量の大容量の携帯不揮発性メモリを使用する。消費者はこのようなドライブを頻繁に用いて、コンピュータ間で、保存されたドキュメント、マルチメディアファイルなどのデータを記憶して持ち運ぶ。デジタルカメラは704に示され、多くの場合、ファームウェアおよび他のデータを記憶するための内部フラッシュメモリと、写真、動画、および他のデータを記憶するための（702に示されるような）フラッシュメモリカードとの両方を含む。

#### 【0054】

ここで説明されたようなリフレッシュ法はまた、スマートフォン、携帯ゲーム機、パーソナルデジタルアシスタント（PDA）、または705で示されるような他のこののようなデバイスにおいても用いられる。これらのデバイスは、フラッシュメモリなどの不揮発性

10

20

30

40

50

メモリを用いて、プログラムおよび他のデータを記憶する。不揮発性メモリも、ファームウェアおよび構成データなどのデータの記憶用とソリッドステートドライブ（SSD）用の両方で、706に示されるようなパーソナルコンピュータにおける高性能のオプションとしてますます一般的になってきている。ソリッドステートドライブは、典型的なハードディスクドライブより大幅に性能が優れているため、ソリッドステートドライブを使用することにより、コンピュータの応答性および速度を改善することができ、ブート処理などのタスクの遂行、アプリケーションの起動、または休止状態からの復旧を、エンドユーザにとってはるかに速いものにする。

## 【0055】

図7におけるこれらの電子メモリデバイスは、ここに説明されたリフレッシュ法が、特に示されたデバイスが頻繁な電力循環の影響を受けやすいとき、改善されたメモリの信頼性およびデータの整合性を提供し得る環境を示している。本願では特定の実施形態が図示および説明されたが、同一の目的、構造、または機能を達成するあらゆる配置が、示された特定の実施形態の代わりになり得ることが、当業者には認識されよう。本願は、本願に記載の本発明の実施形態の例のあらゆる適合または変形を網羅することを意図する。本発明が特許請求の範囲、およびその同等物のすべての範囲によってのみ限定されることが意図される。

10

【図1】

Fig.1

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

Fig.7

---

フロントページの続き

(56)参考文献 特開2004-326867(JP,A)

特開2011-128751(JP,A)

特開2009-087509(JP,A)

特開2010-015191(JP,A)

特開平08-279295(JP,A)

米国特許出願公開第2009/0327581(US,A1)

特開2010-067010(JP,A)

特開平09-204367(JP,A)

特開2008-090778(JP,A)

特開2011-107851(JP,A)

特開2010-198219(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 16

G 06 F 12 / 00 - G 06 F 12 / 06